## (19)中华人民共和国国家知识产权局

# (12)发明专利申请

(10)申请公布号 CN 111245232 A (43)申请公布日 2020.06.05

(21)申请号 202010089304.5

(22)申请日 2020.02.12

(71)申请人 西安电子科技大学 地址 710000 陕西省西安市雁塔区太白南路2号

(72)**发明人** 柴常春 姜婵荣 袁冶 杨毅 周伟雄 江帆 陈壮梁

(74)专利代理机构 西安嘉思特知识产权代理事务所(普通合伙) 61230

代理人 李园园

(51) Int.CI.

**HO2M** 3/158(2006.01)

权利要求书4页 说明书13页 附图7页

#### (54)发明名称

一种快速响应同步降压型DC-DC转换器

#### (57)摘要

本发明公开了一种快速响应同步降压型DC-DC转换器,包括:功率级降压环路、并联于所述功率级降压环路、电压转电流电路以及控制电路;其中,功率级降压环路,用于对转换器的输入电压进行降压,得到输出电压;RC采样电路,用于对功率级降压环路中的电感电流进行采样,得到采样电压;电压转电流电路,用于将采样电压转换为采样电流;控制电路,用于根据采样电压、采样电流以及输出电压的反馈电压,控制功率级降压环路内的开关器件周期性的打开和关断,以使功率级降压环路对转换器的输入电压进行降压。本发明实施例提供的快速响应同步降压型DC-DC转换器具有较低的功耗。

1.一种快速响应同步降压型DC-DC转换器,其特征在于,包括:

功率级降压环路、并联于所述功率级降压环路上的RC采样电路、电压转电流电路以及控制电路;

其中,所述功率级降压环路,用于对所述转换器的输入电压进行降压,得到输出电压; 所述RC采样电路,用于对所述功率级降压环路中的电感电流进行采样,得到采样电压; 所述电压转电流电路,用于将所述采样电压转换为采样电流;

所述控制电路,用于根据所述采样电压、所述采样电流以及所述输出电压的反馈电压, 控制所述功率级降压环路内的开关器件周期性的打开和关断,以使所述功率级降压环路对 所述转换器的输入电压进行降压。

2.根据权利要求1所述的转换器,其特征在于,所述开关器件包括:沟道类型不同的两个MOS管:

所述控制电路,包括:带隙基准电路、动态加速电路、第一比较器、自适应导通时间产生电路、RS触发器以及非交叠与驱动电路;

其中,所述带隙基准电路,用于输出带隙基准电压:

所述动态加速电路,用于将所述反馈电压和所述带隙基准电压之间的误差进行放大,得到误差电流;还用于对所述误差电流和所述采样电流做差,并对做差结果进行积分,得到积分电压;

所述第一比较器,用于比较所述采样电压和所述积分电压的大小,输出占空比信号;

所述自适应导通时间产生电路,用于响应于所述RS触发器的第一输出信号,输出占空 比调整信号;其中,当所述第一输出信号为低电平时,所输出的占空比调整信号为:所述自 适应导通时间产生电路对所述输入电压的前馈电压和所述积分电压的大小进行比较的结 果;当所述第一输出信号为高电平时,所输出的占空比调整信号为:所述自适应导通时间产 生电路对所述积分电压和接地电压的大小进行比较的结果;

所述RS触发器,用于根据自身的两个输入端所分别连接的所述占空比信号和所述占空 比调整信号,输出所述第一输出信号;

所述非交叠与驱动电路,用于将所述第一输出信号处理为两个非交叠的MOS管栅控信号;所述两个非交叠的MOS管栅控信号,为控制所述功率级降压环路内的所述两个MOS管周期性的打开和关断的信号。

3.根据权利要求1或2所述的转换器,其特征在于,所述电压转电流电路,包括:MOS管M14、MOS管M15、MOS管M16、MOS管M17、MOS管M18、MOS管M19、MOS管M20、电阻Rt以及第一运算放大器;

其中,MOS管M14的栅极、MOS管M15的栅极、MOS管M15的漏极以及MOS管M18的漏极均相连;

MOS管M16的栅极、MOS管M17的栅极、MOS管M17的漏极以及MOS管M15的源极均相连;

MOS管M18的栅极、MOS管M19的栅极、MOS管M19的漏极以及MOS管M20的漏极均相连;

MOS管M14的源极和MOS管M16的漏极相连:

MOS管M18的源极、MOS管M19的源极,均连接所述转换器的电源电压;

MOS管M16的源极和MOS管M17的源极均接地;

MOS管M20的源极和电阻Rt的非接地端,均连接所述第一运算放大器的反相输入端,电

阻Rt的另一端接地;所述第一运算放大器的同相输入端,连接所述采样电压,构成所述电压转电流电路的输入端;所述第一运算放大器的输出端,连接MOS管M20的栅极;

MOS管M14的漏极,构成所述电压转电流电路的输出端,用于输出所述采样电流;

其中,MOS管M18以及MOS管M19,均为P型MOS管;MOS管M14、MOS管M15、MOS管M16、MOS管M17以及MOS管M20,均为N型MOS管。

4.根据权利要求2所述的转换器,其特征在于,所述非交叠与驱动电路,包括:第一与门、第一或门、第一驱动电路、第二驱动电路、第一延迟电路、第二延迟电路以及电感电流过零检测电路:

其中,所述第一与门和所述第一或门各自的一个输入端均连接所述第一输出信号;所述第一或门的另一个输入端连接所述第二延迟电路的输出端,所述第一与门的另一个输入端连接所述第一延迟电路的输出端;所述第一或门的输出端连接所述第一驱动电路的输入端;所述第一与门的输出端连接所述电感电流过零检测电路的第一个输入端;

所述第一驱动电路的输入端,连接所述第一或门的输出端;所述第一驱动电路的输出端,连接所述第一延迟电路的输入端,还连接所述电感电流过零检测电路的第二个输入端,用于输出所述两个非交叠的MOS管栅控信号中的一个MOS管栅控信号;

所述第二驱动电路的输入端,连接所述电感电流过零检测电路的输出端;所述第二驱动电路的输出端,连接所述第二延迟电路的输入端,用于输出所述两个非交叠的MOS管栅控信号中的另一个MOS管栅控信号;

所述电感电流过零检测电路的第一个输入端,连接所述第一与门的输出端,第二个输入端连接所述第一驱动电路的输出端,第三个输入端连接所述RC采样电路的输入电压;所述电感电流过零检测电路的输出端,连接所述第二驱动电路的输入端。

5.根据权利要求4所述的转换器,其特征在于,所述电感电流过零检测电路,包括:MOS管M29、MOS管M30、MOS管M31、MOS管M32、MOS管M33、MOS管M34、MOS管M35、MOS管M36、MOS管M37、第一反相器、第二反相器、第二与门、第二或门以及第三或门;

其中,MOS管M30的栅极,连接所述RC采样电路的输入电压,构成所述电感电流过零检测电路的第三个输入端;

MOS管M33的源极、MOS管M34的源极以及MOS管M36的源极,均连接所述转换器的电源电压;

MOS管M34的栅极、MOS管M34的漏极、MOS管M33的栅极、MOS管M36的栅极、MOS管M35的栅极以及MOS管M35的漏极均相连;

MOS管M33的漏极、MOS管M29的源极以及MOS管M30的源极均相连;

MOS管M36的漏极,连接所述第一反相器的输入端,并连接MOS管M37的漏极:

MOS管M29的漏极、MOS管M31的栅极、MOS管M31的漏极以及MOS管M32的栅极均相连;

MOS管M30的漏极、MOS管M32的漏极以及MOS管M37的栅极均相连:

MOS管M35的源极、MOS管M29的栅极、MOS管M31的源极、MOS管M32的源极以及MOS管M37的源极,均接地:

所述第一反相器的输出端,连接所述第二与门的一个输入端;所述第二与门的另一个输入端,连接所述第一与门的输出端,构成所述电感电流过零检测电路的第一个输入端;所述第二与门的输出端,连接所述第二或门的一个输入端,并连接所述第二驱动电路的输入

端,构成所述电感电流过零检测电路的输出端;

所述第二或门的另一个输入端,连接所述第三或门的输出端;所述第二或门的输出端, 连接所述第三或门的一个输入端;

所述第二反相器的输入端,连接所述第一驱动电路的输出端,并连接所述第一延迟电路的输入端,构成所述电感电流过零检测电路的第二个输入端;所述第二反相器的输出端,连接所述第三或门的另一个输入端;

其中,MOS管M29、MOS管M30、MOS管M33、MOS管M34以及MOS管M36,均为P型MOS管;MOS管M31、MOS管M32、MOS管M35以及MOS管M37,均为N型MOS管。

6.根据权利要求2所述的转换器,其特征在于,所述动态加速电路,包括:

MOS管M3、MOS管M4、MOS管M5、MOS管M6、MOS管M7、MOS管M8、MOS管M9、MOS管M10、MOS管M11、MOS管M12、MOS管M13以及积分电容:

其中,MOS管M3的源极、MOS管M4的源极以及MOS管M11的漏极均相连;

MOS管M12的栅极、MOS管M12的漏极、MOS管M11的栅极、MOS管M13的栅极以及MOS管M13的漏极均相连:

MOS管M9的栅极、MOS管M9的漏极、MOS管M7的漏极以及MOS管M10的栅极均相连;

MOS管M4的漏极、MOS管M6的栅极、MOS管M6的漏极以及MOS管M8的栅极均相连;

MOS管M3的漏极、MOS管M7的栅极、MOS管M5的栅极以及MOS管M5的漏极均相连;

MOS管M12的源极、MOS管M9的源极、MOS管M11的源极以及MOS管M10的源极,均连接所述转换器的电源电压;

MOS管M13的源极、MOS管M7的源极、MOS管M5的源极、MOS管M6的源极以及MOS管M8的源极,均接地:

MOS管M3的栅极,连接所述反馈电压;MOS管M4的栅极,连接所述带隙基准电压;

MOS管M10的漏极以及MOS管M8的漏极,均与所述积分电容的非接地端相连;

所述积分电容的非接地端,还连接所述电压转电流电路的输出端;所述积分电容的非接地端的电压为所述积分电压,另一端接地;

其中,MOS管M3、MOS管M4、MOS管M9、MOS管M10、MOS管M11以及MOS管M12,均为P型MOS管; MOS管M5、MOS管M6、MOS管M7、MOS管M8以及MOS管M13,均为N型MOS管。

7.根据权利要求2所述的转换器,其特征在于,所述自适应导通时间产生电路,包括:电压控制电流源以及所述电压控制电流源的负载电路:

其中,所述电压控制电流源的控制电压为所述输入电压;所述负载电路包括:MOS管 M24、电容 $C_1$ 以及第二比较器;MOS管M24为N型MOS管;

电容C<sub>1</sub>的非接地端、MOS管M24的漏极以及所述第二比较器的正极输入端相连,构成所述负载电路的非接地端;电容C<sub>1</sub>的另一端和MOS管M24的源极均接地,构成所述负载电路的接地端;

MOS管M24的栅极连接所述第一输出信号;

所述第二比较器的负极输入端连接所述积分电压,所述第二比较器的输出端输出所述 占空比调整信号。

8. 根据权利要求2所述的转换器,其特征在于,所述带隙基准电路所输出的带隙基准电压为采用电流模控制方法所产生的基准电压。

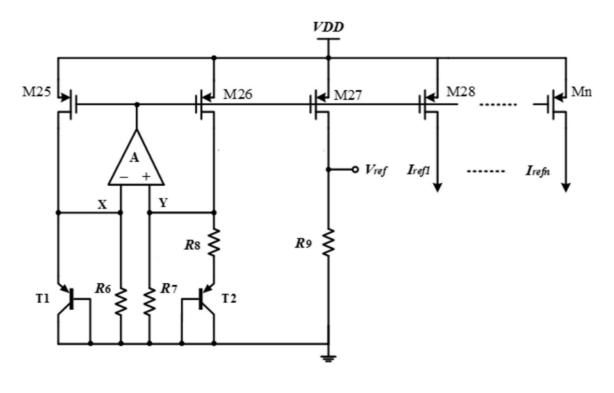

9.根据权利要求2或8所述的转换器,其特征在于,所述带隙基准电路,包括:MOS管M25、MOS管M26、MOS管M27、第二运算放大器、电阻R6、电阻R7、电阻R8、电阻R9、三极管T1以及三极管T2;

其中,MOS管M25的源极、MOS管M26的源极以及MOS管M27的源极,均连接所述转换器的电源电压:

MOS管M25的栅极、MOS管M26的栅极以及MOS管M27的栅极均相连,并与所述第二运算放大器的输出端相连;

MOS管M26的漏极、电阻R7的非接地端以及电阻R8的一端,均连接所述第二运算放大器的同相输入端;电阻R8的另一端连接三极管T2的发射极;

MOS管M25的漏极、三极管T1的发射极以及电阻R6的非接地端,均连接所述第二运算放大器的反相输入端;

三极管T1的基极、三极管T1的集电极、电阻R6的另一端、电阻R7的另一端、三极管T2的基极以及三极管T2的集电极,均接地;

MOS管M27的漏极与电阻R9的非接地端相连,电阻R9的非接地端的电压为所述带隙基准电压;电阻R9的另一端接地;

其中,MOS管M25、MOS管M26以及MOS管M27,均为P型MOS管。

10.根据权利要求9所述的转换器,其特征在于,所述带隙基准电路还包括:用于输出带隙基准电流的多个其他MOS管;所述带隙基准电流,用于为所述转换器中的运算器件提供偏置电流,所述运算器件包括:运算放大器和/或比较器;

其中,每个其他MOS管,均为P型MOS管;每个其他MOS管的栅极,与MOS管M25的栅极、MOS管M26的栅极以及MOS管M27的栅极均相连;每个其他MOS管的源极,均与所述电源电压相连;每个其他MOS管的漏极,均输出一个带隙基准电流。

# 一种快速响应同步降压型DC-DC转换器

#### 技术领域

[0001] 本发明属于开关电源技术领域,具体涉及一种快速响应同步降压型DC-DC转换器。

### 背景技术

[0002] DC-DC转换器为将输入电压转变为固定电压的电压转换器,可分为三类:升压型 DC-DC转换器、降压型DC-DC转换器以及升降压型DC-DC转换器。

[0003] 相关技术中,降压型DC-DC转换器通常在功率级降压环路上串接一个电阻;通过检测该电阻上的电压,实现检测功率级降压环路上的电感电流;转换器内部的控制电路使用该电感电流和转换器的输出电压,控制转换器内部的开关器件周期性的开关,实现对输入电压的降压。

[0004] 然而,由于电流通过电阻后会产生一部分的功耗,这部分功耗将以热量的形式散播到转换器中,故现有的降压型DC-DC转换器的功耗较大。

## 发明内容

[0005] 为了解决现有技术中存在的上述问题,本发明实施例提供了一种快速响应同步降压型DC-DC转换器。

[0006] 本发明要解决的技术问题通过以下技术方案实现:

[0007] 一种快速响应同步降压型DC-DC转换器,包括:

[0008] 功率级降压环路、并联于所述功率级降压环路上的RC采样电路、电压转电流电路以及控制电路;

[0009] 其中,所述功率级降压环路,用于对所述转换器的输入电压进行降压,得到输出电压;

[0010] 所述RC采样电路,用于对所述功率级降压环路中的电感电流进行采样,得到采样电压:

[0011] 所述电压转电流电路,用于将所述采样电压转换为采样电流;

[0012] 所述控制电路,用于根据所述采样电压、所述采样电流以及所述输出电压的反馈电压,控制所述功率级降压环路内的开关器件周期性的打开和关断,以使所述功率级降压环路对所述转换器的输入电压进行降压。

[0013] 在本发明的一个实施例中,所述开关器件包括:沟道类型不同的两个MOS管;

[0014] 所述控制电路,包括:带隙基准电路、动态加速电路、第一比较器、自适应导通时间产生电路、RS触发器以及非交叠与驱动电路:

[0015] 其中,所述带隙基准电路,用于输出带隙基准电压;

[0016] 所述动态加速电路,用于将所述反馈电压和所述带隙基准电压之间的误差进行放大,得到误差电流;还用于对所述误差电流和所述采样电流做差,并对做差结果进行积分,得到积分电压;

[0017] 所述第一比较器,用于比较所述采样电压和所述积分电压的大小,输出占空比信

号;

[0018] 所述自适应导通时间产生电路,用于响应于所述RS触发器的第一输出信号,输出占空比调整信号;其中,当所述第一输出信号为低电平时,所输出的占空比调整信号为:所述自适应导通时间产生电路对所述输入电压的前馈电压和所述积分电压的大小进行比较的结果;当所述第一输出信号为高电平时,所输出的占空比调整信号为:所述自适应导通时间产生电路对所述积分电压和接地电压的大小进行比较的结果;

[0019] 所述RS触发器,用于根据自身的两个输入端所分别连接的所述占空比信号和所述占空比调整信号,输出所述第一输出信号;

[0020] 所述非交叠与驱动电路,用于将所述第一输出信号处理为两个非交叠的MOS管栅控信号;所述两个非交叠的MOS管栅控信号,为控制所述功率级降压环路内的所述两个MOS管周期性的打开和关断的信号。

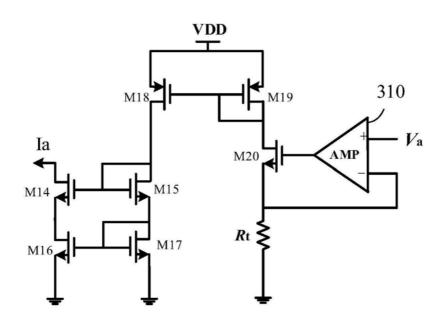

[0021] 在本发明的一个实施例中,所述电压转电流电路,包括:MOS管M14、MOS管M15、MOS管M16、MOS管M17、MOS管M18、MOS管M19、MOS管M20、电阻Rt以及第一运算放大器;

[0022] 其中,MOS管M14的栅极、MOS管M15的栅极、MOS管M15的漏极以及MOS管M18的漏极均相连:

[0023] MOS管M16的栅极、MOS管M17的栅极、MOS管M17的漏极以及MOS管M15的源极均相连;

[0024] MOS管M18的栅极、MOS管M19的栅极、MOS管M19的漏极以及MOS管M20的漏极均相连;

[0025] MOS管M14的源极和MOS管M16的漏极相连:

[0026] MOS管M18的源极、MOS管M19的源极,均连接所述转换器的电源电压;

[0027] MOS管M16的源极和MOS管M17的源极均接地;

[0028] MOS管M20的源极和电阻Rt的非接地端,均连接所述第一运算放大器的反相输入端,电阻Rt的另一端接地;所述第一运算放大器的同相输入端,连接所述采样电压,构成所述电压转电流电路的输入端;所述第一运算放大器的输出端,连接MOS管M20的栅极;

[0029] MOS管M14的漏极,构成所述电压转电流电路的输出端,用于输出所述采样电流;

[0030] 其中,MOS管M18以及MOS管M19,均为P型MOS管;MOS管M14、MOS管M15、MOS管M16、MOS管M17以及MOS管M20,均为N型MOS管。

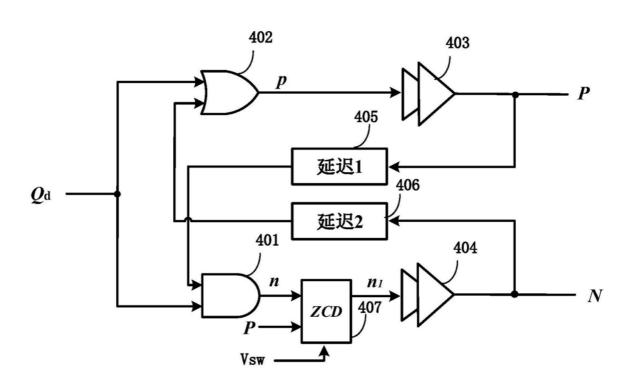

[0031] 在本发明的一个实施例中,所述非交叠与驱动电路,包括:第一与门、第一或门、第一驱动电路、第二驱动电路、第一延迟电路、第二延迟电路以及电感电流过零检测电路;

[0032] 其中,所述第一与门和所述第一或门各自的一个输入端均连接所述第一输出信号;所述第一或门的另一个输入端连接所述第二延迟电路的输出端,所述第一与门的另一个输入端连接所述第一延迟电路的输出端;所述第一或门的输出端连接所述第一驱动电路的输入端;所述第一与门的输出端连接所述电感电流过零检测电路的第一个输入端;

[0033] 所述第一驱动电路的输入端,连接所述第一或门的输出端;所述第一驱动电路的输出端,连接所述第一延迟电路的输入端,还连接所述电感电流过零检测电路的第二个输入端,用于输出所述两个非交叠的MOS管栅控信号中的一个MOS管栅控信号;

[0034] 所述第二驱动电路的输入端,连接所述电感电流过零检测电路的输出端;所述第二驱动电路的输出端,连接所述第二延迟电路的输入端,用于输出所述两个非交叠的MOS管栅控信号中的另一个MOS管栅控信号;

[0035] 所述电感电流过零检测电路的第一个输入端,连接所述第一与门的输出端,第二

个输入端连接所述第一驱动电路的输出端,第三个输入端连接所述RC采样电路的输入电压;所述电感电流过零检测电路的输出端,连接所述第二驱动电路的输入端。

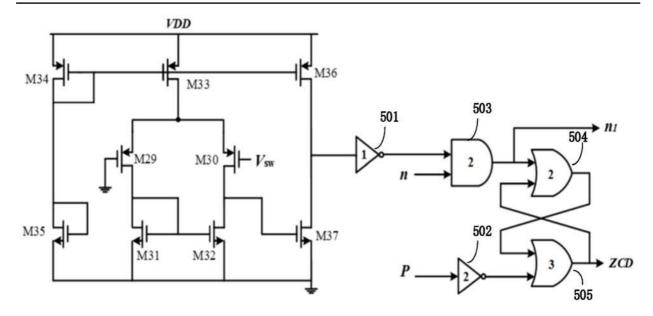

[0036] 在本发明的一个实施例中,所述电感电流过零检测电路,包括:MOS管M29、MOS管M30、MOS管M31、MOS管M32、MOS管M33、MOS管M34、MOS管M35、MOS管M36、MOS管M37、第一反相器、第二反相器、第二与门、第二或门以及第三或门;

[0037] 其中,MOS管M30的栅极,连接所述RC采样电路的输入电压,构成所述电感电流过零检测电路的第三个输入端;

[0038] MOS管M33的源极、MOS管M34的源极以及MOS管M36的源极,均连接所述转换器的电源电压;

[0039] MOS管M34的栅极、MOS管M34的漏极、MOS管M33的栅极、MOS管M36的栅极、MOS管M35的栅极以及MOS管M35的漏极均相连:

[0040] MOS管M33的漏极、MOS管M29的源极以及MOS管M30的源极均相连;

[0041] MOS管M36的漏极,连接所述第一反相器的输入端,并连接MOS管M37的漏极;

[0042] MOS管M29的漏极、MOS管M31的栅极、MOS管M31的漏极以及MOS管M32的栅极均相连;

[0043] MOS管M30的漏极、MOS管M32的漏极以及MOS管M37的栅极均相连;

[0044] MOS管M35的源极、MOS管M29的栅极、MOS管M31的源极、MOS管M32的源极以及MOS管M37的源极,均接地;

[0045] 所述第一反相器的输出端,连接所述第二与门的一个输入端;所述第二与门的另一个输入端,连接所述第一与门的输出端,构成所述电感电流过零检测电路的第一个输入端;所述第二与门的输出端,连接所述第二或门的一个输入端,并连接所述第二驱动电路的输入端,构成所述电感电流过零检测电路的输出端:

[0046] 所述第二或门的另一个输入端,连接所述第三或门的输出端;所述第二或门的输出端,连接所述第三或门的一个输入端;

[0047] 所述第二反相器的输入端,连接所述第一驱动电路的输出端,并连接所述第一延迟电路的输入端,构成所述电感电流过零检测电路的第二个输入端;所述第二反相器的输出端,连接所述第三或门的另一个输入端;

[0048] 其中,MOS管M29、MOS管M30、MOS管M33、MOS管M34以及MOS管M36,均为P型MOS管;MOS管M31、MOS管M32、MOS管M35以及MOS管M37,均为N型MOS管。

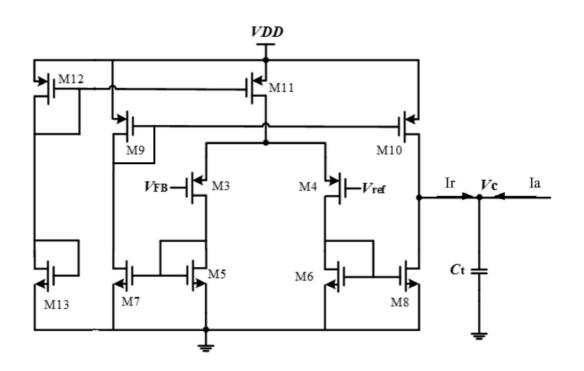

[0049] 在本发明的一个实施例中,所述动态加速电路,包括:

[0050] MOS管M3、MOS管M4、MOS管M5、MOS管M6、MOS管M7、MOS管M8、MOS管M9、MOS管M10、MOS管M11、MOS管M12、MOS管M13以及积分电容;

[0051] 其中,MOS管M3的源极、MOS管M4的源极以及MOS管M11的漏极均相连;

[0052] MOS管M12的栅极、MOS管M12的漏极、MOS管M11的栅极、MOS管M13的栅极以及MOS管M13的漏极均相连;

[0053] MOS管M9的栅极、MOS管M9的漏极、MOS管M7的漏极以及MOS管M10的栅极均相连;

[0054] MOS管M4的漏极、MOS管M6的栅极、MOS管M6的漏极以及MOS管M8的栅极均相连;

[0055] MOS管M3的漏极、MOS管M7的栅极、MOS管M5的栅极以及MOS管M5的漏极均相连:

[0056] MOS管M12的源极、MOS管M9的源极、MOS管M11的源极以及MOS管M10的源极,均连接所述转换器的电源电压;

[0057] MOS管M13的源极、MOS管M7的源极、MOS管M5的源极、MOS管M6的源极以及MOS管M8的源极,均接地:

[0058] MOS管M3的栅极,连接所述反馈电压;MOS管M4的栅极,连接所述带隙基准电压;

[0059] MOS管M10的漏极以及MOS管M8的漏极,均与所述积分电容的非接地端相连;

[0060] 所述积分电容的非接地端,还连接所述电压转电流电路的输出端;所述积分电容的非接地端的电压为所述积分电压,另一端接地;

[0061] 其中,MOS管M3、MOS管M4、MOS管M9、MOS管M10、MOS管M11以及MOS管M12,均为P型MOS管:MOS管M5、MOS管M6、MOS管M7、MOS管M8以及MOS管M13,均为N型MOS管。

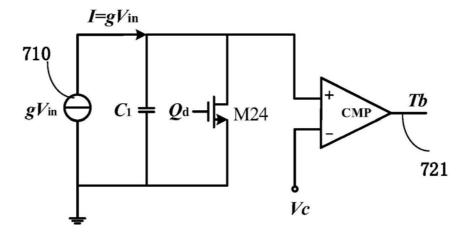

[0062] 在本发明的一个实施例中,所述自适应导通时间产生电路,包括:电压控制电流源以及所述电压控制电流源的负载电路;

[0063] 其中,所述电压控制电流源的控制电压为所述输入电压;所述负载电路包括:MOS 管M24、电容C1以及第二比较器;MOS管M24为N型MOS管;

[0064] 电容 $C_1$ 的非接地端、MOS管M24的漏极以及所述第二比较器的正极输入端相连,构成所述负载电路的非接地端;电容 $C_1$ 的另一端和MOS管M24的源极均接地,构成所述负载电路的接地端;

[0065] MOS管M24的栅极连接所述第一输出信号;

[0066] 所述第二比较器的负极输入端连接所述积分电压,所述第二比较器的输出端输出所述占空比调整信号。

[0067] 在本发明的一个实施例中,所述带隙基准电路所输出的带隙基准电压为采用电流模控制方法所产生的基准电压。

[0068] 在本发明的一个实施例中,所述带隙基准电路,包括:MOS管M25、MOS管M26、MOS管M27、第二运算放大器、电阻R6、电阻R7、电阻R8、电阻R9、三极管T1以及三极管T2;

[0069] 其中,MOS管M25的源极、MOS管M26的源极以及MOS管M27的源极,均连接所述转换器的电源电压:

[0070] MOS管M25的栅极、MOS管M26的栅极以及MOS管M27的栅极均相连,并与所述第二运算放大器的输出端相连:

[0071] MOS管M26的漏极、电阻R7的非接地端以及电阻R8的一端,均连接所述第二运算放大器的同相输入端;电阻R8的另一端连接三极管T2的发射极;

[0072] MOS管M25的漏极、三极管T1的发射极以及电阻R6的非接地端,均连接所述第二运算放大器的反相输入端;

[0073] 三极管T1的基极、三极管T1的集电极、电阻R6的另一端、电阻R7的另一端、三极管T2的基极以及三极管T2的集电极,均接地:

[0074] MOS管M27的漏极与电阻R9的非接地端相连,电阻R9的非接地端的电压为所述带隙 基准电压:电阻R9的另一端接地:

[0075] 其中,MOS管M25、MOS管M26以及MOS管M27,均为P型MOS管。

[0076] 在本发明的一个实施例中,所述带隙基准电路还包括:用于输出带隙基准电流的 多个其他MOS管;所述带隙基准电流,用于为所述转换器中的运算器件提供偏置电流;所述 运算器件包括:运算放大器和/或比较器;

[0077] 其中,每个其他MOS管,均为P型MOS管:每个其他MOS管的栅极,与MOS管M25的栅极、

MOS管M26的栅极以及MOS管M27的栅极均相连;每个其他MOS管的源极,均与所述电源电压相连;每个其他MOS管的漏极,均输出一个带隙基准电流。

[0078] 本发明实施例提供的一种快速响应同步降压型DC-DC转换器中,采用RC采样电路对功率级降压环路的电感电流进行采样;由于RC采样电路是并联于功率级降压环路上的,可以随功率级降压环路的工作周期一起工作,因此,在前半个工作周期内,RC采样电路的电容被充电,在后半个周期内,电容又将充好的电回馈给功率级降压环路;这样,在整个工作周期内,RC采样电路不会给功率级降压环路增加额外的功率损耗。因此,本发明实施例提供的快速响应同步降压型DC-DC转换器的功耗较低。

[0079] 并且,本发明实施例提供的快速响应同步降压型DC-DC转换器中,电压转电流电路将RC采样电路的采样电压转换为采样电流;由于采样电压和采样电流中均包含有全周期的电感电流信息,且电感电流可以实时地反映功率级降压环路上的负载等变化信息,故控制电路根据采样电压、采样电流以及输出电压的反馈电压,控制功率级降压环路内的开关器件周期性的打开和关断实现降压时,可以同步的对功率级降压环路的工作状态进行快速的响应。

[0080] 以下将结合附图及实施例对本发明做进一步详细说明。

## 附图说明

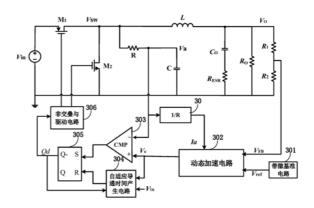

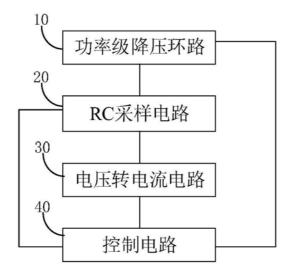

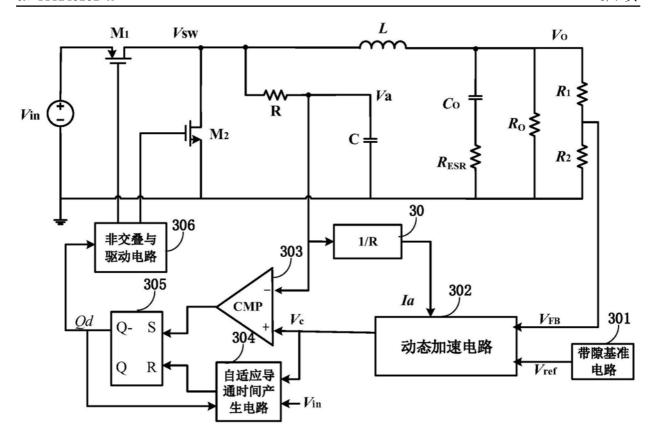

[0081] 图1是本发明实施例提供的一种同步降压型DC-DC转换器的结构示意图;

[0082] 图2(a) 是图1所示转换器中的功率级降压环路的结构示意图;

[0083] 图2(b) 是图1所示转换器中的控制电路的结构示意图;

[0084] 图2(c)是图1所示转换器中的电压转电流电路的结构示意图;

[0085] 图3是图1所示转换器的详细的结构示意图。

[0086] 图4是图2(b) 所示控制电路中的非交叠与驱动电路的结构示意图;

[0087] 图5是图4所示非交叠与驱动电路中的电感电流过零检测电路的结构示意图:

[0088] 图6是图2(b) 所示控制电路中的动态加速电路的结构示意图;

[0089] 图7是图2(b) 所示控制电路中的自适应导通时间产生电路的结构示意图:

[0090] 图8是图7所示动态加速电路中的电压控制电流源的结构示意图:

[0091] 图9是图2(b) 所示控制电路中的一种带隙基准电路的结构示意图;

[0092] 图10是图2(b) 所示控制电路中的另一种带隙基准电路的结构示意图;

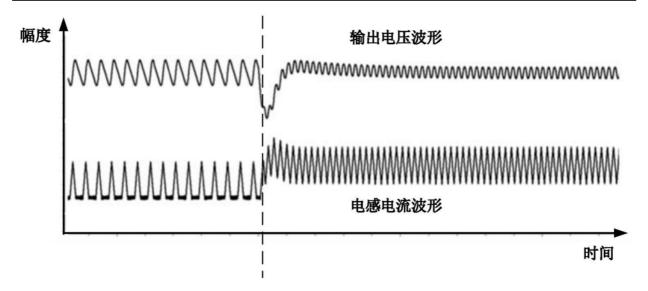

[0093] 图11示例性的示出了是本发明实施例提供的转换器的输出电压和电感电流在不同负载情况下的波形。

#### 具体实施方式

[0094] 下面结合具体实施例对本发明做进一步详细的描述,但本发明的实施方式不限于此。

[0095] 为了降低降压型DC-DC转换器的功耗,本发明实施例提供了一种同步降压型DC-DC 转换器,如图1所示,该转换器可以包括:

[0096] 功率级降压环路10、并联于功率级降压环路上的RC采样电路20、电压转电流电路30以及控制电路40;

[0097] 其中,功率级降压环路10,用于对转换器的输入电压进行降压,得到输出电压;

[0098] RC采样电路20,用于对功率级降压环路10中的电感电流进行采样,得到采样电压:

[0099] 电压转电流电路30,用于将采样电压转换为采样电流;

[0100] 控制电路40,用于根据采样电压、采样电流以及输出电压的反馈电压,控制功率级降压环路10内的开关器件周期性的打开和关断,以使功率级降压环路10对转换器的输入电压进行降压。

[0101] 需要说明的是,图1所示的结构示意图中,各电路模块之间的连线,仅仅用于表示电路模块间具有连接关系,并不表示具体的电路连接方式;为了方案清楚及布局清晰,后续对转换器中各电路模块之间具体的电路连接方式进行说明。

[0102] 可以理解的是,该转换器中具有三条反馈通路将功率级降压环路的信息反馈给控制电路;其中,第一条反馈通路:RC采样电路20对功率级降压环路10中的电感电流进行采样,将采样电压反馈给控制电路;第二条反馈通路:RC采样电路20对功率级降压环路10中的电感电流进行采样,得到采样电压,电压转电流电路30进一步将采样电压转换为采样电流反馈给控制电路40;第三条反馈通路:反馈给控制电路40的反馈电压。由于电感电流实时地反映了功率级降压环路上的负载等变化信息,故将包含电感电流信息的采样电压和采样电流反馈给控制电路40,可以使控制电路40响应于这些变化信息,同步的控制功率级降压环路10中的开关器件的打开和关断,确保转换器的瞬态响应速度。

[0103] 还可以理解的是,由于采样电压和采样电流均包含有电感电流信息,故控制电路 40的控制方式属于 $I^2$ 控制。相应的,该转换器属于 $I^2$ 控制buck变换器。

[0104] 本发明实施例提供的一种快速响应同步降压型DC-DC转换器中,采用RC采样电路对功率级降压环路的电感电流进行采样;由于RC采样电路是并联于功率级降压环路上的,可以随功率级降压环路的工作周期一起工作,因此,在前半个工作周期内,RC采样电路的电容被充电后,在后半个周期内,电容又将充好的电放回馈给功率级降压环路;这样,在整个工作周期内,RC采样电路不会给功率级降压环路增加额外的功率损耗。因此,本发明实施例提供的快速响应同步降压型DC-DC转换器的功耗较低。

[0105] 并且,本发明实施例提供的快速响应同步降压型DC-DC转换器中,电压转电流电路将RC采样电路的采样电压转换为采样电流;由于采样电压和采样电流中均包含有全周期的电感电流信息,且电感电流可以实时地反映功率级降压环路上的负载等变化信息,故控制电路根据采样电压、采样电流以及输出电压的反馈电压,控制功率级降压环路内的开关器件周期性的打开和关断实现降压时,可以同步的对功率级降压环路的工作状态进行快速的响应。

[0106] 为了方案清楚,下面对转换器中的各电路模块进行详细说明。

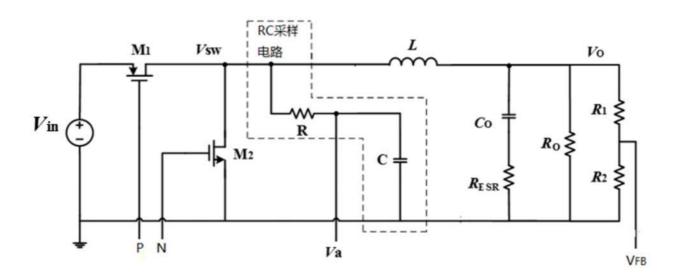

[0107] 首先,对转换器中的功率级降压环路进行详细说明。如图2(a)所示,功率级降压环路10由沟道类型不同的两个MOS管以及输出电路组成。

[0108] 其中,两个MOS管即是功率级降压环路中的开关器件,分别为一个P型MOS管M1和一个N型MOS管M2;图2(a)中,符号P表示控制电路控制MOS管M1周期性打开和关断时的MOS管栅控信号;符号N表示控制电路控制MOS管M2周期性打开和关断时的MOS管栅控信号。此外,Vin表示转换器的输入电压;Vo表示功率级降压环路10的输出电压,即转换器的输出电压。

[0109] 输出电路由电感L、电阻R1、电阻R2、电阻Ro以及电容Co组成,电阻Resr表示电容Co

的等效串联电阻。其中,电感L便是功率级降压环路10中的电感。可以理解的是,由于电感L串接于功率级降压环路10中,故电感L上的电流便是功率级降压环路10上的电流。另外,V<sub>FB</sub>表示功率级降压环路10的输出电压Vo的反馈电压。

[0110] 另外,图2中的虚线框内还示出了与功率级采样环路并联的RC采样电路;从图2中可以看到,该RC采样电路20由电阻R和电容C组成,Vsw表示该RC采样电路的输入电压,可以理解的是,Vsw也可以表示输出电路的输入电压;Va则表示RC采样电路对电感L上的电流进行采样得到的采样电压。

[0111] 在实际应用中,由于输出电路中的电感L通常体积较大,故输出电路通常被设置为转换器的片外电路;这样,转换器内部的电路模块可以包括:沟道类型不同的两个MOS管、RC 采样电路、电压转电流电路以及控制电路。

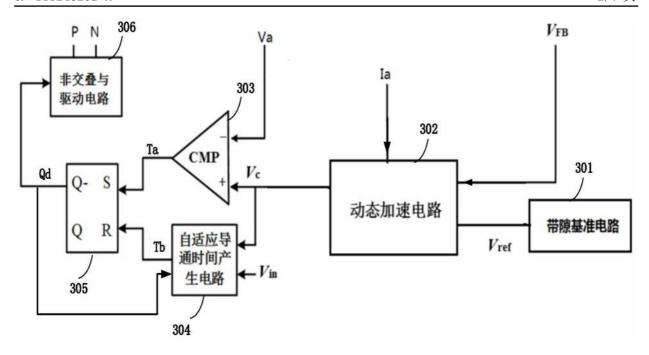

[0112] 然后,对转换器中的控制电路进行详细说明。如图2(b)所示,该控制电路可以包括:带隙基准电路301、动态加速电路302、第一比较器303、自适应导通时间产生电路304、RS 触发器305以及非交叠与驱动电路306。

[0113] 其中,带隙基准电路301,用于输出带隙基准电压Vref。

[0114] 动态加速电路302,用于将反馈电压V<sub>FB</sub>和带隙基准电压Vref之间的误差进行放大,得到误差电流,后续使用Ir表示该误差电流;动态加速电路302还用于对误差电流Ir和采样电流Ia做差,并对做差结果进行积分,得到积分电压Vc;可以理解的是,该动态加速电路302中,包含有跨导运算放大器和积分电路;并且,该积分电压Vc中,既包含有反馈电压V<sub>FB</sub>的信息,又包含有采样电流Ia的信息。

[0115] 第一比较器303,用于比较采样电压Va和积分电压Vc的大小,输出占空比信号Ta;可以理解的是,该占空比信号,不仅包含有反馈电压V<sub>FB</sub>的信息和采样电流Ia的信息,还包含有采样电压Va的信息。

[0116] 自适应导通时间产生电路304,用于响应于RS触发器305在Q-端输出的第一输出信号Qd,输出占空比调整信号Tb;其中,当第一输出信号Qd为低电平时,所输出的占空比调整信号Tb为:自适应导通时间产生电路对输入电压Vin的前馈电压和积分电压Vc的大小进行比较的结果;当第一输出信号Qd为高电平时,所输出的占空比调整信号Tb为:自适应导通时间产生电路对积分电压Vc和接地电压的大小进行比较的结果;其中,自适应导通时间产生电路303内部包含有从所连接的输入电压Vin中获取前馈电压的电路。

[0117] RS触发器305,用于根据自身的两个输入端所分别连接的占空比信号Ta和占空比调整信号Tb,输出第一输出信号Qd;其中,RS触发器305的S输入端连接占空比信号Ta,RS触发器305的R输入端连接占空比调整信号Tb。

[0118] 非交叠与驱动电路306,用于将第一输出信号Qd处理为两个非交叠的MOS管栅控信号P和N;这两个非交叠的MOS管栅控信号,为控制功率级降压环路内的MOS管M1和MOS管M2周期性的打开和关断的信号。这里,所谓的两个非交叠的MOS管栅控信号P和N是指:MOS管栅控信号P和MOS管栅控信号N之间具有一段非交叠时间;这样,可以防止两个功率管在切换开关状态的过程中因同时导通而造成输入电压Vin被短接到地。

[0119] 可以理解的是,由于采样电压Vc中包含了反馈电压VFB的信息,而反馈电压VFB又包含了输出电压Vo的信息,因此,自适应导通时间产生电路302响应于RS触发器305输出的第一输出信号Qd,能够根据输入电压Vin以及输出电压Vo的变化,自适应地调整所输出的占空

比调整信号的内容;这样,RS触发器305最终输出的第一输出信号Qd,便能够达到根据输入电压Vin以及输出电压Vo的变化而自适应变化的效果;相应的,非交叠与驱动电路306根据第一输出信号Qd处理得到的两个非交叠的MOS管栅控信号P和N,也能够达到根据输入电压Vin以及输出电压Vo的变化而自适应矫正的效果。这样,整个转换器在连续导通工作模式下工作时,能够保持较为恒定的开关频率,具有较高的抗干扰性。这里,连续导通工作模式是指MOS管M1和MOS管M2交替导通、电感电流恒大于0时的工作模式。

[0120] 然后,对转换器中的电压转电流电路进行详细说明,如图2(c)所示,该电压转电流电路可以包括:MOS管M14、MOS管M15、MOS管M16、MOS管M17、MOS管M18、MOS管M19、MOS管M20、电阻Rt以及第一运算放大器310;

[0121] 其中,MOS管M14的栅极、MOS管M15的栅极、MOS管M15的漏极以及MOS管M18的漏极均相连:

[0122] MOS管M16的栅极、MOS管M17的栅极、MOS管M17的漏极以及MOS管M15的源极均相连;

[0123] MOS管M18的栅极、MOS管M19的栅极、MOS管M19的漏极以及MOS管M20的漏极均相连;

[0124] MOS管M14的源极和MOS管M16的漏极相连;

[0125] MOS管M18的源极、MOS管M19的源极,均连接转换器的电源电压VDD:

[0126] MOS管M16的源极和MOS管M17的源极均接地;

[0127] MOS管M20的源极和电阻Rt的非接地端,均连接第一运算放大器310的反相输入端,电阻Rt的另一端接地;第一运算放大器310的同相输入端,连接采样电压Va,第一运算放大器310的同相输入端,构成该电压转电流电路的输入端;第一运算放大器310的输出端,连接MOS管M20的栅极;

[0128] MOS管M14的漏极输出采样电流Ia,构成该电压转电流电路的输出端;

[0129] 其中,MOS管M18以及MOS管M19,均为P型MOS管;MOS管M14、MOS管M15、MOS管M16、MOS管M17以及MOS管M20,均为N型MOS管。

[0130] 为了方案清楚,图3示例性的示出了转换器的详细的结构示意图。其中,功率级降压环路与图2(a)所示电路相同,控制电路与图2(c)所示电路相同;电压转电流电路30使用标有"1/R"的方框进行表示,可以理解的是"1/R"表示的是电压除以电阻等于电流的含义;基于图3所示电路可见,本发明实施例提供的转换器,为一种I<sup>2</sup>控制buck变换器。

[0131] 下面,进一步对控制电路中的各个电路子模块进行详细说明。

[0132] 首先,对控制电路中的非交叠与驱动电路进行说明。如图4所示,非交叠与驱动电路,可以包括:第一与门401、第一或门402、第一驱动电路403、第二驱动电路404、第一延迟电路405、第二延迟电路406以及电感电流过零检测电路407;图4中,ZCD表示零电流检测的含义。

[0133] 其中,第一与门401和第一或门402各自的一个输入端均连接第一输出信号Qd;第一或门402的另一个输入端连接第二延迟电路406的输出端,第一与门401的另一个输入端连接第一延迟电路405的输出端;第一或门402的输出端连接第一驱动电路403的输入端;第一与门401的输出端连接电感电流过零检测电路407的第一个输入端;其中,第一与门401的输出端所输出的信号用n来表示,第一或门402的输出端所输出的信号用p来表示;

[0134] 第一驱动电路403的输入端,连接第一或门402的输出端;第一驱动电路403的输出端,连接第一延迟电路405的输入端,还连接电感电流过零检测电路407的第二个输入端,用

于输出两个非交叠的MOS管栅控信号中的一个MOS管栅控信号P:

[0135] 第二驱动电路404的输入端,连接电感电流过零检测电路407的输出端;第二驱动电路404的输出端,连接第二延迟电路406的输入端,用于输出两个非交叠的MOS管栅控信号中的另一个MOS管栅控信号N;其中,电感电流过零检测电路407的输出端所输出的信号使用n<sub>1</sub>来表示;

[0136] 电感电流过零检测电路407的第一个输入端,连接第一与门401的输出端,第二个输入端连接第一驱动电路403的输出端,第三个输入端连接RC采样电路的输入电压Vsw;电感电流过零检测电路407的输出端,连接第二驱动电路404的输入端。

[0137] 可以理解的是,对第一输出信号Qd进行延时后,分别经过第一与门401和第一或门402便可以产生两个初始的非交叠的栅控信号;并且,为了防止电感电流下降到零时,因MOS管M2未关断而发生的电流倒流的情况,在用于产生MOS管栅控信号N的电路分支中,引入电感电流过零检测电路,从而将电感电流过零检测电路407输出的信号与两个初始的非交叠的栅控信号结合,得到最终的两个非交叠的MOS管栅控信号P和N。这样,当电感电流接近零时,可以强行将MOS管M2关断,避免电流倒流。此时,转换器从连续导通工作模式进入到非连续导通工作模式;这里,连续导通工作模式和非连续导通工作模式的区别在于:连续导通工作模式中,MOS管M1和MOS管M2交替导通,这样,转换器在整个工作周期内,电感电流都是大于0的,而在非连续导通工作模式中,存在一段MOS管M1和MOS管M2同时关断的时间,因此,转换器在整个工作周期内,有一部分时间电感电流为0。其中,电感电流接近零是在转换器轻载的情况时产生的,此时,转换器的负载电流较低。

[0138] 其中,在非连续导通工作模式下,当MOS管M1关断且MOS管M2关断时,输出电压Vo由输出电路中的电容Co放电产生;由于输出电压Vo下降至输出电压的额定值的时间比较长,故可以延长转换器的工作周期;相应的,距离MOS管M1再次打开的时间被拉长,整个转换器的开关频率被降低,进一步地降低了转换器的功耗。

[0139] 其中,如图5所示,非交叠与驱动中的电感电流过零检测电路可以包括:MOS管M29、MOS管M30、MOS管M31、MOS管M32、MOS管M33、MOS管M34、MOS管M35、MOS管M36、MOS管M37、第一反相器501、第二反相器502、第二与门503、第二或门504以及第三或门505;

[0140] 其中,MOS管M30的栅极,连接RC采样电路的输入电压Vsw,构成电感电流过零检测电路的第三个输入端;

[0141] MOS管M33的源极、MOS管M34的源极以及MOS管M36的源极,均连接转换器的电源电压VDD;

[0142] MOS管M34的栅极、MOS管M34的漏极、MOS管M33的栅极、MOS管M36的栅极、MOS管M35的栅极以及MOS管M35的漏极均相连:

[0143] MOS管M33的漏极、MOS管M29的源极以及MOS管M30的源极均相连;

[0144] MOS管M36的漏极,连接第一反相器501的输入端,并连接MOS管M37的漏极;

[0145] MOS管M29的漏极、MOS管M31的栅极、MOS管M31的漏极以及MOS管M32的栅极均相连;

[0146] MOS管M30的漏极、MOS管M32的漏极以及MOS管M37的栅极均相连;

[0147] MOS管M35的源极、MOS管M29的栅极、MOS管M31的源极、MOS管M32的源极以及MOS管M37的源极,均接地:

[0148] 第一反相器501的输出端,连接第二与门503的一个输入端;第二与门503的另一个

输入端,连接第一与门的输出端,构成电感电流过零检测电路的第一个输入端;第二与门503的输出端,连接第二或门504的一个输入端,并连接第二驱动电路的输入端,构成电感电流过零检测电路的输出端;

[0149] 第二或门504的另一个输入端,连接第三或门505的输出端;第二或门504的输出端,连接第三或门505的一个输入端;

[0150] 第二反相器502的输入端,连接第一驱动电路的输出端,并连接第一延迟电路的输入端,构成电感电流过零检测电路的第二个输入端;第二反相器502的输出端,连接第三或门505的另一个输入端;

[0151] 其中,MOS管M29、MOS管M30、MOS管M33、MOS管M34以及MOS管M36,均为P型MOS管;MOS管M31、MOS管M32、MOS管M35以及MOS管M37,均为N型MOS管。

[0152] 图5中,MOS管M34的栅极与MOS管M36的栅极的连线穿过MOS管M33,代表MOS管M33的栅极与MOS管M34的栅极、MOS管M36的栅极均相连,该连线规则同样适于其他附图。

[0153] 可以理解的是,当电感电流下降到零时,MOS管M1与MOS管M2的公共节点电压Vsw大于零,因此,在电感电流过零检测电路中,可以通过比较Vsw和接地电压的大小,控制输出端输出的信号n1的高低电平。另外,为了避免电感电流过零检测电路输出错误的控制信号,将MOS管M1的MOS管栅控信号引入电感电流过零检测电路中,使得当MOS管M1开启时,电感电流过零检测电路输出恒为低电平,确保了电路的准确性与稳定性。

[0154] 另外,在进行电路仿真的时候,通过观察第三或门505的输出端的信号,可以确定转换器从连续导通工作模式进入非连续导通工作模式的时机,图5中,该信号使用ZCD进行表示。

[0155] 然后,对控制电路中的动态加速电路进行说明。如图6所示,该动态加速电路,可以包括:

[0156] MOS管M3、MOS管M4、MOS管M5、MOS管M6、MOS管M7、MOS管M8、MOS管M9、MOS管M10、MOS管M11、MOS管M12、MOS管M13以及积分电容Ct:

[0157] 其中,MOS管M3的源极、MOS管M4的源极以及MOS管M11的漏极均相连;

[0158] MOS管M12的栅极、MOS管M12的漏极、MOS管M11的栅极、MOS管M13的栅极以及MOS管M13的漏极均相连:

[0159] MOS管M9的栅极、MOS管M9的漏极、MOS管M7的漏极以及MOS管M10的栅极均相连;

[0160] MOS管M4的漏极、MOS管M6的栅极、MOS管M6的漏极以及MOS管M8的栅极均相连;

[0161] MOS管M3的漏极、MOS管M7的栅极、MOS管M5的栅极以及MOS管M5的漏极均相连;

[0162] MOS管M12的源极、MOS管M9的源极、MOS管M11的源极以及MOS管M10的源极,均连接转换器的电源电压VDD:

[0163] MOS管M13的源极、MOS管M7的源极、MOS管M5的源极、MOS管M6的源极以及MOS管M8的源极,均接地:

[0164] MOS管M3的栅极,连接反馈电压VFB;MOS管M4的栅极,连接带隙基准电压Vref;

[0165] MOS管M10的漏极以及MOS管M8的漏极,均与积分电容Ct的非接地端相连;

[0166] 积分电容Ct的非接地端,还连接电压转电流电路的输出端;积分电容的非接地端的电压为积分电压,另一端接地;

[0167] 其中,MOS管M3、MOS管M4、MOS管M9、MOS管M10、MOS管M11以及MOS管M12,均为P型MOS

管:MOS管M5、MOS管M6、MOS管M7、MOS管M8以及MOS管M13,均为N型MOS管。

[0168] 可以理解的是,图6中,在积分电容Ct左侧部分各MOS管组成的电路,将反馈电压 $V_{PB}$ 和带隙基准电压 $V_{ref}$ 之间的误差进行放大,得到误差电流 $I_{r}$ ;另外,积分电容Ct的非接地端连接电压转电流电路的输出端所输出的采样电流 $I_{a}$ ;这样,误差电流 $I_{r}$ 和采样电流 $I_{a}$ 做差后的电流在积分电容Ct上充电,生成了积分电压 $V_{c}$ 。

[0169] 然后,对控制电路中的自适应导通时间产生电路进行说明。如图7所示,该自适应导通时间产生电路可以包括:

[0170] 电压控制电流源710以及电压控制电流源的负载电路:

[0171] 其中,电压控制电流源的控制电压为输入电压Vin,故电压控制电流源产生的电流 I可以表示为gVin,g为电压控制电流源的控制系数;负载电路包括:MOS管M24、电容C<sub>1</sub>以及 第二比较器721;其中,MOS管M24为N型MOS管。

[0172] 电容C<sub>1</sub>的非接地端、MOS管M24的漏极以及第二比较器721的正极输入端相连,构成负载电路的非接地端;电容C<sub>1</sub>的另一端和MOS管M24的源极均接地,构成负载电路的接地端;

[0173] MOS管M24的栅极连接第一输出信号Qd;

[0174] 第二比较器721的负极输入端连接积分电压Vc,第二比较器的输出端输出占空比调整信号Tb。

[0175] 可以理解的是,电压控制电流源产生的电流I流向电容 $C_1$ 的非接地端后,会在电容  $C_1$ 上进行充电;当第一输出信号Qd为低电平时,MOS管M24关断,第二比较器721比较的是电 容 $C_1$ 的非接地端的电压和积分电压Vc的大小;当第一输出信号Qd为高电平时。MOS管M24导通,电容 $C_1$ 上的积分电压被短接到地,第二比较器721比较的接地电压和积分电压Vc的大小。

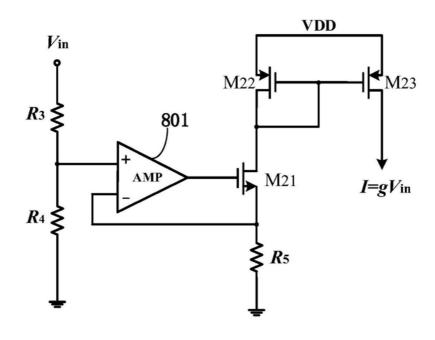

[0176] 其中,电压控制电流源的电路结构存在多种。示例性的,如图8所示,电压控制电流源可以包括:电阻R3、电阻R4、电阻R5、MOS管M21、MOS管M22、MOS管M23以及第三运算放大器801:

[0177] 其中,电阻R3的一端与输入电压Vin相连,电阻R3的另一端与电阻R4的非接地端,均连接第三运算放大器801的同相输入端;电阻R4的另一端接地;

[0178] MOS管M21的源极和电阻R5的非接地端,均连接第三运算放大器801的反相输入端; 电阻R5的另一端接地;

[0179] 第三运算放大器801的输出端连接MOS管M21的栅极;

[0180] MOS管M21的漏极、MOS管M22的栅极、MOS管M22的漏极以及MOS管M23的栅极均相连;

[0181] MOS管M22的源极和MOS管M23的源极,均连接转换器的电源电压VDD;MOS管M23的漏极输出的电流便为电压控制电流源所输出的电流I:

[0182] 其中,MOS管M22和M23为P型MOS管,MOS管M21为N型MOS管。

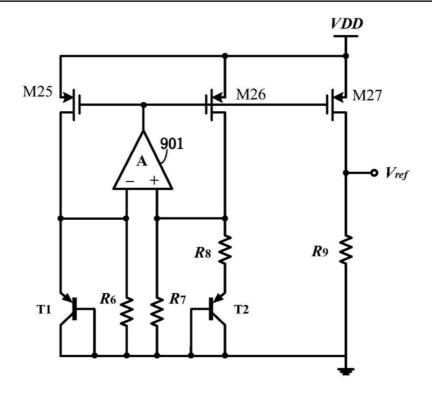

[0183] 在一种可选的方案中,控制电路中的带隙基准电路所输出的带隙基准电压Vref,可以是采用电流模控制方法所产生的基准电压。示例性的,如图9所示,该带隙基准电路可以包括:MOS管M25、MOS管M26、MOS管M27、第二运算放大器901、电阻R6、电阻R7、电阻R8、电阻R9、三极管T1以及三极管T2:

[0184] 其中,MOS管M25的源极、MOS管M26的源极以及MOS管M27的源极,均连接转换器的电源电压VDD;

[0185] MOS管M25的栅极、MOS管M26的栅极以及MOS管M27的栅极均相连,并与第二运算放大器901的输出端相连:

[0186] MOS管M26的漏极、电阻R7的非接地端以及电阻R8的一端,均连接第二运算放大器901的同相输入端;电阻R8的另一端连接三极管T2的发射极;

[0187] MOS管M25的漏极、三极管T1的发射极以及电阻R6的非接地端,均连接第二运算放大器901的反相输入端;

[0188] 三极管T1的基极、三极管T1的集电极、电阻R6的另一端、电阻R7的另一端、三极管T2的基极以及三极管T2的集电极,均接地;

[0189] MOS管M27的漏极与电阻R9的非接地端相连,电阻R9的非接地端的电压为带隙基准电压Vref;电阻R9的另一端接地;

[0190] 其中,MOS管M25、MOS管M26以及MOS管M27,均为P型MOS管。

[0191] 该带隙基准电路中,三极管T1的基极发射极电压具有负温度系数;三极管T2与三极管T1的面积不同,即三极管T2与三极管T1工作在不同的电流密度;这样,三极管T1的基极发射极电压和三极管T2的基极发射极电压的压差具有正温度系数;将三极管T1的基极发射极电压和该压差按照预定的比例系数进行叠加,便可以得到与温度无关的零温度系数的带隙基准电压。在具体设计电路时,该比例系数可以通过电阻R6、电阻R7与电阻R8的阻值来控制;其中,电阻R6的阻值与电阻R7的阻值相等。

[0192] 另外,可以理解的是,在转换器中,上述的各个运算放大器和各个比较器,如第一运算放大器、第二运算放大器、第三放大器以及第一比较器等运算器件还具有工作时所需的偏置电路;在一种可选的方案中,转换器中的运算器件的偏置电路可以由带隙基准电路提供。此时,如图10所示,带隙基准电路还可以包括:用于输出带隙基准电流的多个其他MOS管M28~Mn;该带隙基准电流,用于为转换器中的运算器件提供偏置电流;

[0193] 其中,每个其他MOS管,均为P型MOS管;每个其他MOS管的栅极,与MOS管M25的栅极、MOS管M26的栅极以及MOS管M27的栅极均相连;每个其他MOS管的源极,均与电源电压VDD相连;每个其他MOS管的漏极,均输出一个带隙基准电流Irefn;n大于等于1。

[0194] 可以理解的是,由带隙基准电路所产生的带隙基准电流同样也是零温度系数的电流。

[0195] 本发明实施例中,转换器的输出电压和电感电流在不同负载情况下的波形可以如图11所示。图11中,虚线左边是转换器在轻载时的输出电压波形和电感电流波形,虚线右边是转换器在重载时的输出电压波形和电感电流波形。其中,在轻载时,转换器工作在连续导通工作模式下,重载时,转换器工作在非连续导通工作模式下;从图11可以看到,本发明实施例提供的快速响应同步降压型DC-DC转换器,在两种工作模式下的开关频率均比较稳定;且在非连续导通工作模式时的开关频率较低,转换器的功耗相应较低。

[0196] 以上,为对本发明实施例提供的快速响应同步降压型DC-DC转换器进行的详细说明。

[0197] 需要说明的是,术语"第一"、"第二"仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的器件的数量。在本发明实施例的描述中,"多个"的含义是两个或两个以上,除非另有明确具体的限定。

[0198] 尽管在此结合各实施例对本申请进行了描述,然而,在实施所要求保护的本申请

过程中,本领域技术人员通过查看所述附图、公开内容、以及所附权利要求书,可理解并实现所述公开实施例的其他变化。在权利要求中,"包括"(comprising)一词不排除其他组成部分或步骤,"一"或"一个"不排除多个的情况。单个处理器或其他单元可以实现权利要求中列举的若干项功能。相互不同的从属权利要求中记载了某些措施,但这并不表示这些措施不能组合起来产生良好的效果。

[0199] 以上内容是结合具体的优选实施方式对本发明所作的进一步详细说明,不能认定本发明的具体实施只局限于这些说明。对于本发明所属技术领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干简单推演或替换,都应当视为属于本发明的保护范围。

图1

图2 (a)

图2 (b)

图2(c)

图3

图4

图5

图6

图7

图8

图9

图10

图11