#### (19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第6065536号 (P6065536)

(45) 発行日 平成29年1月25日(2017.1.25)

(24) 登録日 平成29年1月6日(2017.1.6)

| (51) Int.Cl. | F 1                          |          |                     |

|--------------|------------------------------|----------|---------------------|

| HO1L 25/07   | <b>(2006.01)</b> HO 1        | L 25/04  | С                   |

| HO1L 25/18   | <b>(2006.01)</b> HO 1        | L 29/80  | Н                   |

| HO1L 21/338  | ( <b>2006.01)</b> HO 1       | L 29/80  | G                   |

| HO1L 29/778  | (2006.01)                    |          |                     |

| HO1L 29/812  | (2006.01)                    |          |                     |

|              |                              |          | 請求項の数 5 (全 12 頁)    |

| (21) 出願番号    | 特願2012-251074 (P2012-251074) | (73) 特許権 | 者 000106276         |

| (22) 出願日     | 平成24年11月15日 (2012.11.15)     |          | サンケン電気株式会社          |

| (65) 公開番号    | 特開2014-99535 (P2014-99535A)  |          | 埼玉県新座市北野3丁目6番3号     |

| (43) 公開日     | 平成26年5月29日 (2014.5.29)       | (74)代理人  | 100097113           |

| 審查請求日        | 平成27年10月1日 (2015.10.1)       |          | 弁理士 堀 城之            |

|              |                              | (74)代理人  | 100162363           |

|              |                              |          | 弁理士 前島 幸彦           |

|              |                              | (72) 発明者 | 田坂 泰                |

|              |                              |          | 埼玉県新座市北野三丁目6番3号 サンケ |

|              |                              |          | ン電気株式会社内            |

|              |                              | (72) 発明者 | 町田 修                |

|              |                              |          | 埼玉県新座市北野三丁目6番3号 サンケ |

審査官 秋山 直人

ン電気株式会社内

最終頁に続く

# (54) 【発明の名称】半導体装置

## (57)【特許請求の範囲】

# 【請求項1】

ゲート電極の電圧によって1対の主電極間に流れる電流のオン・オフが制御されるスイッチング素子が形成されIII族窒化物半導体からなる半導体層で構成されたスイッチング素子チップと、前記スイッチング素子の制御を行う制御用ICが形成され前記スイッチング素子チップとは別体とされた制御用ICチップとが、同一のパッケージ内に設けられた構成を具備する半導体装置であって、

前記スイッチング素子チップと前記制御用ICチップとを上面に搭載<u>し接地電位とされ</u>たリードフレームを具備し、

\_\_\_ 前記スイッチング素子における前記電流は、前記スイッチング素子チップを構成する半 導体層の面内方向を流れ、

前記パッケージ内において、前記リードフレームの上面側で、

前記スイッチング素子チップにおける前記ゲート電極と、前記スイッチング素子チップにおける1対の主電極のうちの接地電位に近い側の電極が印加される主電極と、がそれぞれ前記制御用ICチップと接続されたことを特徴とする半導体装置。

#### 【請求項2】

前記スイッチング素子はHEMT (High Electron Mobility Transistor)であることを特徴とする請求項1に記載の半導体装置。

## 【請求項3】

前記制御用ICチップには温度センサが搭載され、前記制御用ICチップは、前記温度

センサによって検知された温度に応じて前記ゲート電極の電位を制御して前記スイッチング素子チップにおいて流れる前記電流を遮断する動作を行うことを特徴とする請求項1<u>又</u>は2に記載の半導体装置。

#### 【請求項4】

前記ゲート電極の電位を制御するために外部から入力された入力信号が入力され、当該入力信号における立ち上がり及び/又は立ち下がり速度を変化させた出力信号を出力して前記ゲート電極に印加するスイッチング速度調整回路が、前記制御用ICチップに設けられたことを特徴とする請求項1から請求項3までのいずれか1項に記載の半導体装置。

#### 【請求項5】

前記スイッチング速度調整回路には、前記制御用ICチップの主電源と接続された1対の端子のうちの少なくとも一方と抵抗を介して接続されるスイッチング速度調整端子が設けられ、

前記スイッチング速度調整<u>回路</u>は、前記入力信号によってスイッチング制御されることによって、前記スイッチング速度調整端子を前記ゲート電極に接続する動作を行うことを特徴とする請求項4に記載の半導体装置。

#### 【発明の詳細な説明】

#### 【技術分野】

#### [0001]

本発明は、半導体層の面内方向に駆動電流が流されて動作するパワー半導体素子を用いたIPM(Intelligentt Power Module)の構造に関する。

#### 【背景技術】

#### [0002]

近年、大電流をスイッチングする動作を行うパワー半導体素子として、III族室化物化合物半導体(GaN:Gallium Nitride 等)を用いたものが使用されており、例えばGaN系のHEMT(High Electron MobilityTransistor)は、特に大電力で動作することができるため、特に好ましく使用されている。HEMTにおいては、例えばGaN等からなる半導体層の表面にソース電極、ドレイン電極が形成され、ソース電極とドレイン電極間の電流が半導体層の面内方向で流れ、この電流のオン・オフがやはり表面に形成されたゲート電極の電位で制御される。

### [0003]

このような、GaN系のHEMTの特にソース電極とドレイン電極間には高電圧が印加されて動作するため、これを内蔵する半導体モジュール(半導体装置)には、高い耐湿性や耐電圧性が要求される。特許文献1には、特にこうしたHEMTチップを実装する半導体モジュールの構造が記載されている。

# [0004]

この半導体モジュールにおいては、HEMTが形成された半導体チップ(HEMTチップ)の表面が樹脂層の多層構造で覆われ、更に全体が樹脂層で封止されている。この構造によって、長期間にわたり高い信頼性でこの半導体モジュールを使用することができる。

#### [0005]

また、一般に、大電力で動作するスイッチング素子をより安全に使用する際には、スイッチング素子と、制御用ICとが組み合わせて使用されたIPM(IPM:Intelligent Power Module)の形態で使用される場合が多い。制御用ICは、スイッチング素子に異常が発生した場合、例えば温度が異常に上昇した場合には、強制的にスイッチング素子をオフし、電流を遮断させる動作を行う。これによって、このスイッチング素子を安全に使用することができる。

# [0006]

こうしたIPMの構成は、例えば、特許文献 2 に記載されている。この構成においては、通常は、シリコンで構成されたスイッチング素子(パワーMOSFET、IGBT(Insulated Gate Bipolar Transistor)等)が形成されたスイッチング素子チップと、制御用ICが形成された制御用ICチップとは、別体で製

10

20

30

40

造される。発熱量の大きなスイッチング素子チップの放熱性と、制御用ICチップによる制御性を両立させるように、各々が異なるリードフレームに搭載されている。制御用ICチップには温度センサが搭載され、その温度が異常に上昇した場合には、強制的にスイッチング素子をオフする。これにより、スイッチング素子を安全かつ高い信頼性をもって使用することができる。

## 【先行技術文献】

#### 【特許文献】

# [0007]

【特許文献1】特開2012-164937号公報

【特許文献 2 】特開 2 0 1 1 - 1 9 9 1 6 1 号公報

#### 【発明の概要】

【発明が解決しようとする課題】

#### [0008]

ここで、制御用ICチップは通常のICと同様の構成をもつため、通常はシリコンで構成される。これに対して、前記の通り、HEMT(スイッチング素子)チップは、化合物半導体で構成される。IPMにおいては、こうした2つのチップを同一のパッケージ内に搭載し、接続する必要がある。

#### [0009]

しかしながら、高電圧が印加されて動作するHEMTチップと、これに比べて低電圧で精密な動作を行う制御用ICチップが形成されたシリコンチップとを同一のパッケージ内に搭載することは容易ではない。

#### [0010]

特に、HEMTにおいては、一般にはノーマリーオン型が容易に製造されるのに対して、ノーマリーオフ型を製造することは困難である。このため、HEMTをオン動作させるためのゲート電圧(閾値)は、シリコンのパワーMOSFET等と比べると低い。一方で、HEMTにおけるドレイン電極には、前記の通り、高電圧が印加される。こうした場合においては、そのスイッチング動作におけるノイズの影響は大きくなる。特に、別体のチップに形成された制御用ICからHEMTのゲート電圧を制御する場合には、この影響は大きくなる。

# [0011]

このため、大電力で動作するスイッチング素子チップと、制御用ICチップとを同時に搭載した半導体装置において、高い信頼性を得ることは困難であった。特に、スイッチング素子としてHEMTを用いた場合には、高い信頼性を得ることは困難であった。

#### [0012]

本発明は、かかる問題点に鑑みてなされたものであり、上記問題点を解決する発明を提供することを目的とする。

# 【課題を解決するための手段】

#### [0013]

本発明は、上記課題を解決すべく、以下に掲げる構成とした。

本発明の半導体装置は、ゲート電極の電圧によって1対の主電極間に流れる電流のオン・オフが制御されるスイッチング素子が形成され I I I 族窒化物半導体からなる半導体層で構成されたスイッチング素子チップと、前記スイッチング素子の制御を行う制御用 I C が形成され前記スイッチング素子チップとは別体とされた制御用 I C チップとが、同一のパッケージ内に設けられた構成を具備する半導体装置であって、前記スイッチング素子チップと前記制御用 I C チップとを上面に搭載し接地電位とされたリードフレームを具備し、前記スイッチング素子における前記電流は、前記スイッチング素子チップを構成する半導体層の面内方向を流れ、前記パッケージ内において、前記リードフレームの上面側で、前記スイッチング素子チップにおける前記ゲート電極と、前記スイッチング素子チップにおける1対の主電極のうちの接地電位に近い側の電極が印加される主電極と、がそれぞれ前記制御用 I C チップと接続されたことを特徴とする。

10

20

30

40

本発明の半導体装置において、前記スイッチング素子はHEMT(High Electron Mobility Transistor)であることを特徴とする。

本発明の半導体装置において、前記制御用ICチップには温度センサが搭載され、前記制御用ICチップは、前記温度センサによって検知された温度に応じて前記ゲート電極の電位を制御して前記スイッチング素子チップにおいて流れる前記電流を遮断する動作を行うことを特徴とする。

本発明の半導体装置は、前記ゲート電極の電位を制御するために外部から入力された入力信号が入力され、当該入力信号における立ち上がり及び / 又は立ち下がり速度を変化させた出力信号を出力して前記ゲート電極に印加するスイッチング速度調整回路が、前記制御用ICチップに設けられたことを特徴とする。

本発明の半導体装置において、前記スイッチング速度調整回路には、前記制御用ICチップの主電源と接続された1対の端子のうちの少なくとも一方と抵抗を介して接続されるスイッチング速度調整端子が設けられ、前記スイッチング速度調整<u>回路</u>は、前記入力信号によってスイッチング制御されることによって、前記スイッチング速度調整端子を前記ゲート電極に接続する動作を行うことを特徴とする。

#### 【発明の効果】

#### [0014]

本発明は以上のように構成されているので、大電力で動作するスイッチング素子チップと、制御用ICチップとを同時に搭載した半導体装置において、高い信頼性を得ることができる。

【図面の簡単な説明】

#### [0015]

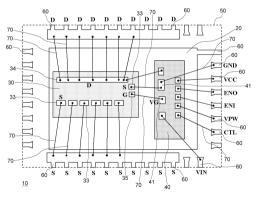

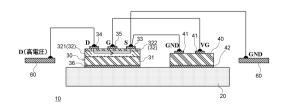

- 【図1】本発明の実施の形態に係る半導体装置の構成を示す上面透視図である。

- 【図2】本発明の実施の形態に係る半導体装置の構成を模式的に示す断面図である。

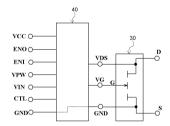

- 【図3】本発明の実施の形態に係る半導体装置において用いられる端子を模式的に示す構成図である。

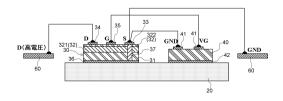

- 【図4】本発明の実施の形態に係る半導体装置の変形例の構成を模式的に示す断面図である

- 【図5】本発明の実施の形態に係る半導体装置において用いられるスイッチング速度調整回路(制御用IC)の構成の例を示す図である。

- 【図6】スイッチング速度調整回路の入力信号VINと出力信号VGの関係を示す図である。

【発明を実施するための形態】

## [0016]

以下、本発明の実施の形態となる半導体装置について説明する。この半導体装置においては、化合物半導体で構成され、スイッチング素子が形成されたチップ(スイッチング素子ップ)と、シリコンで構成され、制御用ICが形成されたチップ(制御用ICチップ)とが、同一のリードフレームに搭載される。

# [0017]

図1は、この半導体装置(半導体モジュール)10の上面透視図であり、図2は、その断面を模式的に示す図、図3は、この内部で構成される端子の構成を模式的に示す図である。この半導体装置10においては、単一のリードフレーム20が用いられ、その上面に、HEMTチップ(スイッチング素子チップ)30と制御用ICチップ40が搭載されている。なお、図2(断面図)は、断面構造を模式的に示しており、HEMTチップ30、制御用ICチップ40の上の各電極、各リードの配置は図1とは異なって示されている。

# [0018]

HEMTチップ30は、例えば特許文献1に記載されたものと同様である。図2に示されるように、HEMTチップ30においては、基板31上にIII族窒化物半導体層32が形成され、窒化物半導体層32中にHEMTが形成されている。窒化物半導体層32は、電子走行層321とバリア層322で構成される。窒化物半導体層32の表面(図2に

10

20

30

40

おける上面)に、ソース電極33、ドレイン電極34、ゲート電極35が形成されている。その動作時には、通常はソース電極33が接地電位とされ、ドレイン電極34に高電圧(10V以上)が印加される。図2に示されるように、1対の主電極となるソース電極33・ドレイン電極34間における電子走行層321中のチャネルのオン・オフがゲート電極35の電位によって制御される。すなわち、このHEMTチップ30においては、動作電流は窒化物半導体層32の面内方向(図2における横方向)に流れる。チャネルがオンとされる電位(閾値)は、正電位であるものとする。すなわち、このHEMTは、ノーマリーオフ型とされており、ゲート電極35のソース電極33に対する電位VGがhighレベルの場合にオン、1owレベルの場合にオフとなる。

## [0019]

基板31は、例えば特開2011-18844号公報に記載されるように、導電性のものを用いることができる。こうした基板31の材料としては、導電性のシリコン、SiC、GaN等の単結晶を用いることができる。また、基板31の裏面(図2における下面)には、基板裏面電極36が形成されている。一般に、基板裏面電極36(基板31)とソース電極33とは同電位(接地電位)とされる。基板裏面電極36は、導電性接着剤によってリードフレーム20に接合されている。

#### [0020]

制御用ICチップ40は、シリコンで構成され、HEMTチップ30と別体とされる。制御用ICチップ40は、通常のシリコンICチップと同様の構造を具備し、その上面側には、MOSFETを用いた通常の制御回路が形成されており、この制御回路に用いられる制御用電極41がその表面に複数形成されている。制御用電極41は図2においては2つのみ示されているが、実際には図1、3に示されるように、用途、接続に応じて多数が形成されている。また、制御用ICチップ40の裏面にも、制御用ICチップ裏面電極42が形成されている。

#### [0021]

図1に示されるように、この半導体装置10は、矩形体形状のモールド層50底面の4方の端部にリード60が設けられたQFN(Quad For Non-Lead)型とされる。ただし、図1の構成においては、左端面側におけるリード60は使用されておらず、上端面側、石端面側、下端面側のリード60のみがHEMTチップ30又は制御用ICチップ40の端子と接続されている。HEMTチップ30における各電極、制御用ICチップ40における制御用電極41、リード60との間は、上面側においてボンディングワイヤ70によって接続されている。なお、図1においては、右端面側の一番上のリード60は、リードフレーム20と一体化されている。この半導体装置10の大きさは、上記のモールド層50と等しく、例えば8mm×8mm×(厚さ)0.85mm程度である。

## [0022]

ここで、図3に示されるように、HEMTチップ30において設けられた端子は、ドレイン電極34に対応する端子D、ソース電極33に対応する端子S、ゲート電極35に対応する端子Gである。

#### [0023]

一方、制御用ICチップ40に設けられた端子は、VCC、ENO、ENI、VPW、VIN、CTL、GND、VGである。ここで、端子VCCはこの制御用ICチップの主電源となる電圧の供給端子であり、端子GND(接地電位)間と端子VCC間に例えば5Vの直流電圧が主電源として印加される。端子VINは、HEMTのオン・オフを制御するための外部入力端子である。後述するように、端子VINに入力された入力信号(VIN)に対して制御用ICチップ40が出力した出力信号VGがHEMTの端子G(ゲート電極35)に直接入力される。

#### [0024]

端子ENI、ENOは、保護機能に関わる端子である。ENIは、この保護機能をEnableとする信号を入力する端子であり、ENOは、保護回路が機能してHEMTチップを強制的にオフする場合(例えば後述するような温度上昇があった場合)にその検出信号

10

20

30

40

を出力する端子である。端子VPW、CTLはスイッチング速度調整端子であり、これを用いてHEMTのスイッチング速度(VGの立ち上がり、立ち下がり速度)を制御することができる。

#### [0025]

図2に示されるように、この半導体装置10においては、図2における下側が、リードフレーム20によって一定電位(接地電位)とされる。このため、HEMTチップ30においては、基板裏面電極36を介して基板31も接地電位とされ、制御用ICチップ40の裏面側も制御用ICチップ裏面電極42を介して接地電位とされる。また、図1に示されるように、上側においても、ソース電極33は、ボンディングワイヤ70を介して制御用ICチップ40における制御用電極41と接続される。この制御用電極41は、やはリボンディングワイヤ70を介して右端面側のGND端子(リード60)と接続されている。このため、図2の構造においては、HEMTチップ30、制御用ICチップ40の裏面側全体が接地電位とされ、かつ上面側においてもソース電極33及びこれと接続された箇所が接地電位とされる。

#### [0026]

最も高電位とされる端子 D(ドレイン電極 3 4)に接続されたリード 6 0 は、図 1 における上端面側の複数のリード 6 0 に接続される。また、端子 D は、1 本のボンディングワイヤ 7 0 を介して制御用 I C チップ 4 0 における一つの制御用電極 4 1 にも接続される。接地電位とされる端子 S(ソース電極 3 3)に接続されたリード 6 0、あるいは端子 G N D となるリード 6 0 は、下端面側、あるいは右端面側に設けられ、端子 D に接続されたリード 6 0 と離されて設置され、これらの間には充分な沿面距離が確保されるため、端子 D と端子 S 間における耐圧は確保される。なお、端子 D、 S を介して大電流が流されるために、これらの端子とリード 6 0 との接続には、複数のボンディングワイヤ 7 0 が並列に用いられる。

#### [0027]

一方、この半導体装置10における動作電流のオン・オフを直接制御するVGは、VINを入力として制御用ICチップ40で生成され、HEMTチップ30側のゲート電極35にボンディングワイヤ70を介して入力される。HEMTチップ30におけるゲート電極35、制御用ICチップ40における端子VG(制御用電極41)の位置を近接させることによって、このボンディングワイヤ70を短くすることができる。

#### [0028]

VGは、HEMTのスイッチング動作を直接制御する電圧であるために、この半導体装置10においては、最も精密な制御が要求され、ノイズの影響を最も除去すべき信号電圧である。特に、HEMTがノーマリーオフ型でありその閾値が低い場合には、VGの制御には高い精度が要求される。

#### [0029]

図1~3の構成においては、HEMTチップ30、制御用ICチップ40の裏面側全体が接地電位に保たれ、かつHEMTチップ30の上面側においては、必要最小限の部分(ドレイン電極34、ゲート電極35及びこれらと接続された部分)のみがこれと異なる電位とされる。また、HEMTチップ30におけるゲート電極35と制御用ICチップ40におけるVG端子(制御用電極41)の位置を近接させ、ボンディングワイヤ70を短くすることによって、ノイズの影響を低減することができる。また、図1に示されるように、ソース電極33及びGND端子と接続され接地電位とされたボンディングワイヤ70が、このVG端子と接続されたボンディングワイヤ70と近接している。

#### [0030]

このため、この半導体装置10においては、モールド層50で封止された部分の中で、ゲート電極35及びこれに接続されたボンディングワイヤ70に対するシールド構造が形成され、VGに対するノイズの影響が低減される。すなわち、VGの制御が高精度となり、HEMTの閾値が小さな場合でも、安定した動作が可能となる。

# [0031]

50

10

20

30

また、大電流が流されるHEMTチップ30は、動作時に発熱する。この場合において、HEMTチップ30の温度上昇が異常となった場合、例えば所定の温度を超えた場合、あるいは温度上昇率が所定の値を超えた場合は、HEMTの動作電流を強制的に遮断することが有効である。この点については、特許文献2と同様である。

#### [0032]

この場合において、図1の構成のように、制御用ICチップ40をHEMTチップ30と近接させて単一のリードフレーム20の上に搭載した構成は、HEMTチップ30の温度を素早く正確に検知するという観点から有効である。こうした場合には、温度センサを制御用ICチップ40に搭載し、検知された温度によって、VINに関わらずVGをオフ(1ow)とすることによって、強制的にHEMTをオフすることができ、より安全にこの半導体装置10を使用することができる。

[0033]

また、同様に、ドレイン電極34に過電圧が供給された場合、すなわち、ソース電極33に対するドレイン電極34の電圧VDSが所定の値を超えた場合には、VINに関わらずVGをオフ(低電位)し、強制的にHEMTをオフすることによっても、この半導体装置10をより安全に使用することができる。このため、図1に示されるように、ドレイン電極34は、ボンディングワイヤ70によって制御用ICチップ40の一つの制御用電極41(ドレイン電圧検知用端子)に接続される。ここで、ドレイン電圧検知用端子の入力インピーダンスを充分高くし、この端子を電圧検知のためのみに用いれば、VDSが高い場合でもボンディングワイヤ70には大電流が流れない設定とすることができ、このために1本のボンディングワイヤ70のみを用いることができる。

[0034]

上記の構成によって、高い信頼性をもってこの半導体装置10を使用することができる

[0035]

なお、上記の例においては、HEMTチップ30における基板31は導電性であり、その電位がソース電極33と等しいものとしたが、これらを異ならせることもできる。すなわち、基板31の電位をソース電極33の電位と独立に制御することもできる。この場合においては、HEMTチップ30側において基板31とソース電極33とを接続せず、リードフレーム20の電位を基板31の電位とし、例えば図1における右端面側の一番上のリード60を、基板31の電位を入力するための端子として使用することができる。

[0036]

こうした場合においても、一般に、HEMTを良好に動作させる際に基板31に設定される電位はVDS等と比べて無視できる程度に低電位とされる(接地電位に近い)ために、上記と同様の効果を奏することは明らかである。

[0037]

更に、HEMTチップ30における基板31が絶縁性である場合においても、リードフレーム31側(HEMTチップ30、制御用ICチップ40の裏面側)が一様に接地電位となるために、シールドとして機能する点は上記と同様である。このため、やはり上記と同様の効果を奏することは明らかである。こうした場合には、基板31としては、サファイア、半絶縁性(ノンドープ)のシリコン、SiC等の単結晶を用いることもできる。すなわち、上記の構成は、基板31の種類によらず有効である。

[0038]

この場合、例えば特開2011-18844号公報に記載されたように、バリア層32 2、電子走行層321、基板31を貫通する貫通電極37を用いて、ソース電極33と基 板裏面電極36、リードフレーム31とを電気的に接続することもできる。図4は、この 場合における断面を図2に対応させて示した図である。こうした場合においても、上記の 構成が有効であることは明らかである。あるいは、基板31を導電性として、バリア層3 22、電子走行層321を貫通し、ソース電極33と基板31とを接続した貫通電極を用 いることもできる。 10

20

30

40

#### [0039]

ここで、前記の通り、この半導体装置10においては、VGの制御の精度を高めることができ、HEMTのスイッチング動作を高精度で行うことができる。この際、制御用ICチップ40(制御用IC)を以下の構成とすることによって、VGに与えるノイズの影響を更に低減することができる。

#### [0040]

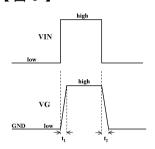

前記の通り、HEMTのスイッチング動作を制御するために、この半導体装置10に外部から入力される信号はVINである。ただし、実際にHEMTのゲート電極35に入力される電圧VGは、VINを基にして制御用ICチップ40が生成する。VGは、制御用ICチップ40におけるスイッチング速度調整回路によって、後述する図6上に示すようなVINの波形に対して、パルスの立ち上がり速度、立ち下がり速度が調整された波形VGが出力される。

#### [0041]

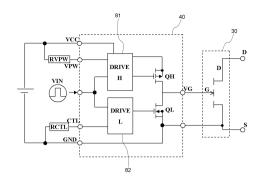

このスイッチング速度調整回路について説明する。このスイッチング速度調整回路においては、VINが入力され、かつ端子VPW、CTLが用いられる。このスイッチング速度調整回路を用いた場合の構成の例を図5に示す。ここで、制御用IC回路チップ40には、実際にはスイッチング速度調整回路以外の回路も構成されているが、ここではスイッチング速度調整回路とこれに関連する端子のみが記載されている。

#### [0042]

図5において、端子VPWは抵抗RVPWを介して主電源を供給する端子の一方である端子VCCに接続され、端子CTLは抵抗RCTLを介して主電源を供給する端子の他方である端子GND(接地電位)に接続される。RVPW、RCTLは、この半導体装置10の外部において設けられ、端子VPW、CTLは、スイッチング速度調整端子として用いられ、前者はVGの立ち上がり速度の調整に、後者は立ち下がり速度の調整に用いられる

## [0043]

図5におけるスイッチング速度調整回路は、H側ドライブ回路ブロック81で制御されるpチャネルMOSFET(QH)、L側ドライブ回路ブロック82で制御されるnチャネルMOSFET(QL)とで構成される。この際、VINにオン信号が入力されると(HEMTをオンする場合に相当)、QHはオンとなり、QLはオフとなる。その結果、VGはQHのソース電位と等しくなる。この際にRVPWの定数値でH側ドライブ回路ブロック81の特性が調整され、QHのスイッチング特性が制御されるため、VGの立ち上がり時間を設定することができる。

## [0044]

一方、VINにオフ信号が入力されると(HEMTをオフする場合に相当)、QHはオフとなり、QLはオンとなる。その結果、VGはQLのソース電位、すなわち接地電位と等しくなる。この際にRCTLの定数値でL側ドライブ回路ブロック82の特性が調整され、QLのスイッチング特性が制御されるため、VGの立ち下がり時間を設定することができる。

#### [0045]

また、VINがオフ信号入力の状態で維持された場合には、VGはGND(接地電位)に維持される。このため、例えばVINに外部のノイズが重畳した場合でも、HEMTのゲート電極35に直接入力する電圧であるVGを適正に保つことができる。以上より、この回路を用いた場合において、入力されるVINと出力されるVGの関係を図6に示す。ここで、VINにおける1owからhighへの立ち上がり時間、highから1owへの立ち下がり時間は、それぞれ無視できるものとする。

#### [0046]

RVPW、RCTLの抵抗値は、半導体装置10の外部において、利用者が任意にこれらを独立に設定して接続することができる。  $t_1$ 、  $t_2$ を大きくした場合にはノイズの影響は小さくすることができるが、スイッチング動作の速度は低くなるために、高速動作に

10

20

30

40

は適さない。このため、RVPW、RCTLの抵抗値(定数)は、この半導体装置 100 使用状況に応じて設定された  $t_1$ 、  $t_2$  の値に応じて決定することができる。

#### [0047]

例えば、立ち上がり動作におけるノイズの影響が問題にならないために、  $t_1$  は伸ばさずに  $t_2$  のみを伸ばしたい場合には、 R V P W = 0 とすればよい。図 5 の回路では、 R V P W の定数値が大きくなれば  $t_1$  が長くなり、この定数値が小さくなれば  $t_1$  が短くなる設定とした。逆に、立ち下がり動作におけるノイズの影響が問題にならないために、  $t_1$  のみを伸ばし  $t_2$  を伸ばさない場合には、 R C T L = 0 とすればよい。ここで、 R C T L の定数値と  $t_2$  の関係は、 R V P W の定数値と  $t_1$  の関係と同様の設定とした。こうした設定は、 半導体装置 1 0 の外部において利用者が容易に行うことができる。この設定は、 この半導体装置 1 0 が用いられる環境等に応じて、 H E M T のスイッチング動作に及ぼすノイズの影響が小さくなるように、利用者が適宜行うことができる。

#### [0048]

また、通常の p チャネル M O S F E T である Q H 、 n チャネル M O S F E T である Q L 、 H 側ドライブ回路 ブロック 8 1 、 L 側ドライブ回路 ブロック 8 2 は、シリコンで構成された制御用 I C チップ 4 0 内に容易に形成することができる。このため、図 5 に示された構成のスイッチング速度調整回路を内蔵する制御用 I C チップ 4 0 を容易に製造することができ、これを半導体装置 1 0 に搭載することができる。

#### [0049]

その他、制御用ICチップにおけるVPW端子とVG端子、CTL端子とVG端子とを上記と同様にVINのhigh、lowに応じて切り替えて接続できる構成であれば、図5に示された以外の構成の回路によっても、同様にt<sub>1</sub>、t<sub>2</sub>を設定することができる。

#### [0050]

なお、図5の構成において、立ち上がり速度のみを調整する場合にはVPW端子、立ち下がり速度のみを調整する場合にはCTL端子のみをそれぞれ設ければ、HEMTを適正にスイッチング動作させるVGを生成することができる。

#### [0051]

こうしたスイッチング速度調整回路は、スイッチング動作に対するノイズの影響の少な い上記の半導体装置10において特に有効である。

# [0052]

なお、上記の例においては、HEMTチップ30が用いられていたが、基板側を接地電位(あるいは接地電位に近い低電位)とされて動作し、VGによって同様にスイッチング動作が制御される半導体素子が形成されたスイッチング素子チップであれば、同様の効果を奏することは明らかである。こうした半導体素子としては、例えば、パワーMOSFETやIGBTのように半導体層の厚さ方向に主電流が流される縦型の素子ではなく、半導体層の面内方向に主電流が流される横型のMESFET(MEtal Semiconductor Field Effect Transistor)や、横型のMOSFET等がある。また、半導体層を構成する材料も、III族窒化物半導体に限定されず、SiC、シリコン等を用いた場合でも同様である。

#### [0053]

また、上記の構成では、スイッチング素子チップと制御用ICチップがそれぞれ1個ずつリードフレームに搭載されたものとしたが、同様の構成をもつスイッチング素子チップが複数搭載された場合でも同様の効果を奏することは明らかである。制御用ICチップを複数搭載した場合においても同様である。

#### [0054]

また、上記の構成では、この半導体装置(半導体モジュール)がQFN型であるものとした。QFN型の半導体モジュール(パッケージ)は、小型化が可能であることや、挿入ピン等の寄生インダクタンスの影響が排除されるため、特に上記のようなスイッチング素子を搭載する場合には好ましく用いられる。しかしながら、リードが取り出される形態は、上記の効果を奏する限りにおいて任意であり、DIP(Double Inline

10

20

30

40

Package)型等、任意の形態とすることができる。

# 【符号の説明】

## [0055]

- 10 半導体装置(半導体モジュール)

- 20 リードフレーム

- 30 HEMTチップ(スイッチング素子チップ)

- 3 1 基板

- 32 窒化物半導体層(半導体層)

- 3 3 ソース電極

- 3 4 ドレイン電極

- 3 5 ゲート電極

- 36 基板裏面電極

- 37 貫通電極

- 40 制御用ICチップ

- 4 1 制御用電極

- 42 制御用ICチップ裏面電極

- 50 モールド層

- 60 リード

- 70 ボンディングワイヤ

- 8 1 H側ドライブ回路ブロック

- 82 L側ドライブ回路ブロック

- 3 2 1 電子走行層

- 3 2 2 バリア層

# 【図1】

# 【図2】

# 【図3】

# 【図4】

10

# 【図5】

# 【図6】

# フロントページの続き

# (56)参考文献 特開2009-206204(JP,A)

特開2002-009219(JP,A)

特開2010-244977(JP,A)

特開2011-199161(JP,A)

特開平11-346147(JP,A)

# (58)調査した分野(Int.CI., DB名)

H01L 25/07

H01L 21/338

H01L 25/18

H01L 29/778

H01L 29/812