# (19) 대한민국특허청(KR) (12) 특허공보(B1)

(51) Int. CI.<sup>5</sup> G05B 13/00 (45) 공고일자 1992년06월29일

(11) 공고번호 92-005279

| (21) 출원번호  | 특1989−0014321          | (65) 공개번호    | 특1990−0006837       |

|------------|------------------------|--------------|---------------------|

| (22) 출원일자  | 1989년 10월05일           | (43) 공개일자    | 1990년05월09일         |

| (30) 우선권주장 | 63-251254 1988년 10월05일 | 일본(JP)       |                     |

| (71) 출원인   | 가부시끼가이샤 도시바 아          | 오이 죠이찌       |                     |

|            | 일본국 가나가와껭 가와사끼시        | ㅣ 사이와이구 호리가요 | P쪼오 72              |

|            |                        |              |                     |

| (72) 발명자   | 히로이 가즈오                |              |                     |

|            | 일본국 도오교오도 후쮸시 도        | 시바쪼오 1 가부시까기 | <b>ト이샤 도시바 후</b> 쮸고 |

|            | 오조오 내                  |              |                     |

| (74) 대리인   | 문기상, 조기호               |              |                     |

|            |                        |              |                     |

## 심사관 : 허상무 (책자공보 제2833호)

### (54) 디지탈 제어시스템 및 그에 의한 PID 연산수행방법

#### 요약

내용 없음.

#### 叫班도

# 도1

## 명세서

[발명의 명칭]

디지탈 제어시스템 및 그에 의한 PID 연산수행방법

[도면의 간단한 설명]

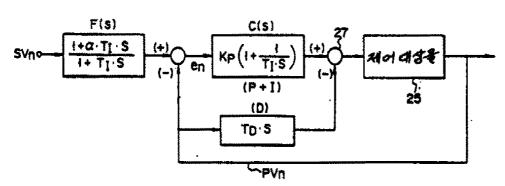

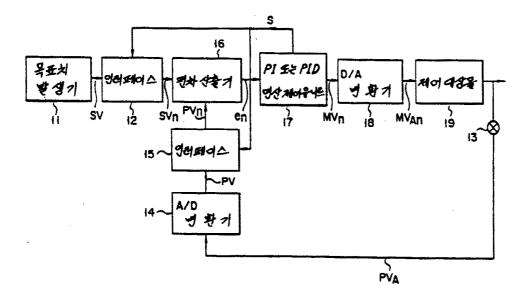

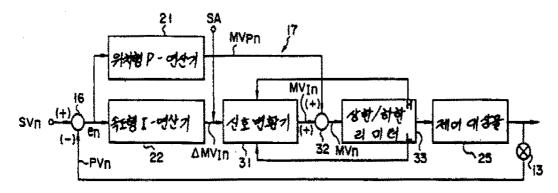

제1도는 종래의 위치형(position-type) PID 디지탈 제어기의 개통도.

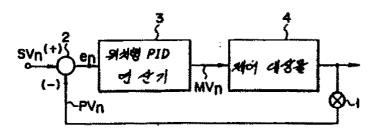

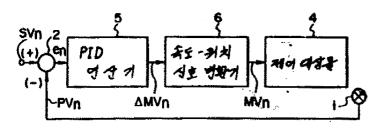

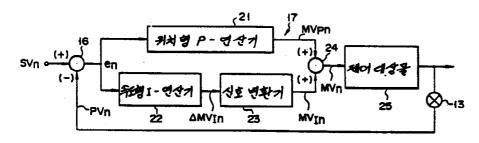

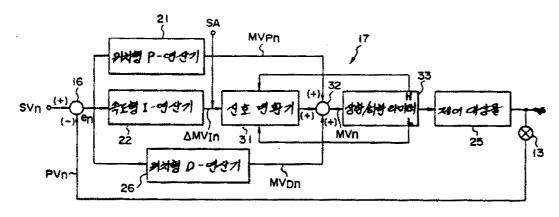

제2도는 종래의 속도형(speed-type) PID 디지탈 제어기의 개통도.

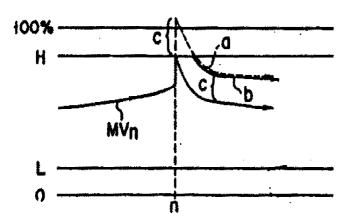

제3도는 제2도의 제어기에 의한 조작출력치(manipulation output value)의 목표치에 대한 변화방식을 나타내는 그래프.

제4도는 본 발명의 제1일실시예에 의한 디지탈 제어기의 개통도.

제5도는 제1일실시예에 조합된 PID 연산유니트(operation unit)를 나타내는 개통도.

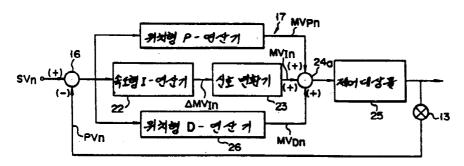

제6도는 본 발명의 제2실시에에 의한 디지탈 제어기에 조합된 또다른 PID 연산유니트를 나타내는 개통도.

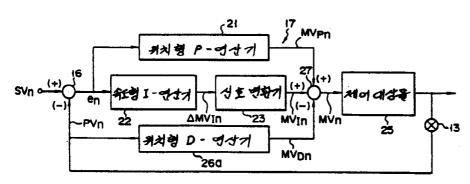

제7도는 제6도의 PID 연산유니트 대신에 사용가능한 제2실시예의 PID 연산유니트를 나타내는 개통도.

제8도는 제6도의 PID 연산유니트 대신에 조합 가능하며, 이 PID 연산유니트내에서의 신호 제어방식을 설명하는 제2실시예의 또 다른 PID 연산유니트를 나타내는 개통도.

제9도는제6도의 PID 연산유니트 대신에 조합 가능하며, 이 PID 연산유니트내에서의 신호제어방식을 설명하는, 제2실시예의 다른 한 PID 연산유니트를 나타내는 개통도.

제10도는 제6도의 PID 연산유니트 대신에 조합 가능하며, 이 PID 연산유니트와 조합 사용된, 목표치 필터(desired Value filter)를 설명하는 제2실시예의 또 다른 PID 연산유니트를 나타내는 개통도.

제11도는 전달함수(transmission function)항내의, PID 연산유니트의 성분들과 상기 목표치 필터를 나타내는 도면.

[발명의 상세한 설명]

본 발명은 PID-연산의 각항의 특성에 따라, 위치형 및 속도형 연산으로 PID(P ; Proportional(비례), I ; Integral(적분), D : Derivative(미분))연산을 행하는 디지탈 제어시스템에 관한 것이다.

제어는 두 범주, 즉 아날로그 PID 연산식 제어기와 디지탈 PID 연산식 제어기로 분류된다.

최근에는, 아날로그 PID 연산식 제어기가 널리 사용되고 있다.

아날로그 연산식 제어시스템은 하기 PID 기본공식을 사용하여 PID 연산을 행한다 :

$$MV = K_P \left(e^{\frac{1}{T_o}} \int e^{-dt} + T_o \frac{de}{dt}\right) + MV_o \qquad (1)$$

식에서, MV는 조작출력치를 e를 편차를,  $K_P$ 는 비례이득을,  $T_1$ 는 적분동작 시간을,  $T_0$ 는 미분시간을,  $MV_0$ 는 조작출력치의 초기치를 각각 나타낸다.

최근, 전자컴퓨터의 광범위한 사용 및 신호의 고속처리에 기인하여, 디지탈 연산식 제어시스템의 사용이 증가되고 있다. 디지탈 연산식 제어시스템에는 위치형 연산시스템과 속도형 연산시스템이 있다.

위치형 연산시스템은 각 샘플링(sampling)기간 I중에 PID 연산을 행하므로써, 조작출력치 MV 교 얻으며, 여기서 n은 샘플링기간에 대응하는 정수이다. 더욱 구체적으로는, 상기 위치형 연산시스템의 PID 연산 공식은 하기 방정식(2)으로 나타낼 수 있다.

$$MV_n = K_P \{e_n + \frac{\tau}{T_r} \sum_{i=1}^{N} e_i + \frac{TD}{r} e_n - e_{n-1}\} + MV_0$$

.....(2)

속도형 연산시스템은, 각 샘플링 기간중 발생하는 MV의 변량 △MV n 을 인지하여, 이것을 1기간 전샘플링기간에서 얻어진 출력치 MV n-1 에 기산하므로써, 샘플링기간에 대한 출력치 MV n 을 얻는다. 더욱 구체적으로는, 상기 속도형 연산시스템의 PID 연산 공식은 하기 방정식(3a) 및 (3b)로 나타낼 수있다;

$$\Delta MV_n = K_P \{ (e_n - e_n - 1 + \frac{\tau}{T_1} e_n + \frac{TD}{r} e_n (-2e_{n-1} + e_{n-2}) \}$$

(3a)

$$MV_n = MV_{n-1} + \Delta MV_n$$

.....(3b)

상기 방정식(2), (3a) 및 (3b)는 상기 기본 공식(1)로부터 유도된다.

상기 방정식 (2) 및 (3a)에서  $e_n$  , $e_{n-1}$  및  $e_{n-2}$  는 현재 샘플링기간, 1기간전 샘플링기간 및 2기간 전샘플링기간중에서 발생된 편차를 각각 나타낸다. 방정식(2), (3a) 및 (3b)로 부터 이해할 수 있듯이, 상기 속도형 연산시스템은 하기의 관점에서 위치형 연산시스템보다 유리하다.

- (1) 상기 방정식(3a) 및 (3b)에는 ∑항이 없으므로 속도형 연산시스템이 행하는 동작이 쉽다.

- (2) 수동 또는 자동식 속도형 연산시스템의 경우, 수동동작에서 자동동작으로 전환된 후에  $MV_{n-1}$  에 따라 대상물을 제어하고,  $\triangle MV_n$  을  $\triangle MV_{n-1}$  에 가하는 기능이 갖추어져 있다.

연산모드의 전환을 고려한, 1기간전 샘플링기간에서 얻어진 출력치, 즉 MV<sub>n-1</sub> 의 조정이 불필요하다. 그러므로 연산모드를 수동에서 자동으로 전환하는 것이 쉽고 자연스럽다.

(3) 상기 속도형 연산시스템은, △MV n 이 한정되는 경우 또 그 이득차가 조정되는 경우에 한에서, 정밀 PID 제어를 성취할 수 있다. 그러므로, 상기 시스템은 다른 산술 연산 장치와 함께 쓸수 있다. 다시 말해서, 상기 시스템은 자체내에 발생된 신호들뿐만 아니라, 다른 연산장치에 의한 신호에 대해서도 쉽게 연산을 행할 수 있다.

상술한 장점들 때문에, 실제로 가장 많이 사용되는 직접 디지탈 제어(DDC)시스템은 속도형이다.

종래의 두가지 즉, 위치형 및 속도형 디지탈 제어기를 각각 제1도 및 제2도를 참조하여 상세히 설명 한다.

제1도의 위치형 PID 제어기는 방정식(2)에 준한 연산을 행하도록 설계되어 있다. 제1도에 나타낸 바와 같이, 상기 제어기는 제어치 PV, 검출용 검출기(1)와, 목표치 SV, 에서 검출기(1)에 의해 검출된 PV,를 감하여 편차 e,을 산출하는 편차계산기(2)와, 방정식(2)와 상기 편차 e,에 준하여 PID 연산을 행하므로써, 조작치 MV,을 얻는 위치형 PID 연산소자(3)을 포함한다. 상기 장치(3)는 상기 MV,치를 대상물(4)에 공급하여, SV,이 PV,과 동치가 되도록 상기 대상물(4)를 제어한다.

제2도에 설명된 속도형 PID 제어기는 방정식(3a) 및 (3b)에 준하여 연산을 수행하도록 설계되어 있다. 제2도에 나타낸 바와같이, 상기 속도형 PID 제어기는, 제어치 PV, 검출용 검출기(1)와, 목표치 SV,에서 상기 검출기(1)에 의해 검출된 PV, 치를 감하여 편차 e,을 산출하는 편차산출기(2)와, 상기 편차 e,와 방정식(3a)에 준하여 PID 연산을 행하므로써 MV, 치의 변량 △MV,을 얻는 속도형 PID 연산기와, 상기 변량 △MV,을 수신하여 방정식(3b)에 준한 연산을 행하므로써 변량 △MV,을 MV 심하으로 변환시키는 속도-위치신호변환기(6)을 포함한다. 상기 변환기(6)는 상기MV, 치를 대상물(4)에 공급하여 SV,이 PV,과 동치가 되도록 대상물(4)를 제어한다. 조작치MV,의 상한 및 하한 즉, H및

L은 상기 속도-위치 신호변환기(6)에 세트(set)된다.

상기 위치형 PID 디지탈 제어기(제1도 참조)는 몇가지 관점에서 결함이 있다. 첫째로, 방정식(2)가 ∑항을 내포하고 있어서, 저속에서만 연산한다. 둘째로, 수동-자동모드 전환시 반드시 행해져야 하는 범프리스 스위칭(bumpless switching) 즉, 범프발생이 없는 전환조작이 복잡하다. 세째로, 상기제어기는 기타 연산장치에 의해 프로세스된 신호에 대해 복잡한 연산을 행하여야 한다.

하기의 관점에서, 상기 속도형 PID 디지탈 제어기(제2도 참조)가 역시 불리하다. 제3도에 나타난 바와 같이 목표치 SV, 이 시간 n에서 변경되는 경우, 출력치 MV AP 을 파선곡선 a로 나타낸 것처럼 제어하여야 한다. 상기 SV, 치가 시간 n에서 변경되고, C치만큼 상기 상한 H를 초과하여 상승되는 경우, 상기 출력치 MV, 을 실선곡선 b로 나타낸 것과 같이 제어해주어야 한다. 즉, 상기 제어기는 MV, 치를 상한 H로 신속히 감소시키도록, D연산을 행하여야 한다. / 이러한 특수한 제어 즉, MVn 치를 상한 H로 급격한 감소를 실행시키는 것은 어렵다. 성공적으로 실행된다할지라도, 보일러(boiler)에 적용할 수는 없다. 이것을 보일러 제어에 사용하는 경우에는, 연소실내로 공기 또는 연료를 공급하는 밸브의 개방이 과도하게되어, 불완전연소를 야기하여 결국에는 폭발할 가능성이 커진다. 상기 속도성 PID 제어기는 안정성 및 안전성의 면에서 불리한 것이다.

본 발명의 제1목적은, PID 연산항의 특성에 따라 PID 연산에 대해 위치형 PID 연산 또는 속도형 PID 연산을 행하는 디지탈 제어기를 제공하는데 있다.

본 발명의 제2목적은, 목표치가 변경될 때 D 연산을 억제하므로써 제어시스템의 악기능 또는 불안정한 기능을 방지하는 디지탈 제어기를 제공하는데 있다.

본 발명의 제3목적은, 출력제어치가 상한을 초과하여 증가할때 또는 하한 미만으로 감소할때 적절한 I-연산출력치를 얻으며, 대상물의 I 제어중 리세트 와인드업(reset wind up)의 발생을 방지하는 디지탈 제어기를 제공하는데 있다.

본 발명의 제4목적은, 안정성있고 신뢰성있는 PID 제어를 감안한, PID-연산항의 특성에 따라 디지탈 연산을 행하는 방법을 제공하는데 있다.

본 발명에 의하면, PI 또는 PID 제어연산은 편차 즉, 목표치와 실제 제어치 P의차이에 준하여 행해 진다. 속도형 I 제어연산은 상기 편차에 따라, I-연산항(tern)에 준하여 행해지므로써, I-제어연산 출력치를 얻는다. 한편, 위치형 P 제어연산 또는 위치형 PD제어연산은 각각 상기 편차에 따라 P-연 산 항 또는 PD-연산항에 준하여 행해지므로써, 위치형 P 제어연산과 위치형 PD제어연산을 얻는다.

상기 위치형 I-신호는 상기 위치형 P 제어연산출력치 또는 위치형 PD 제어 연산출력치에 가산되어, 조작출력치를 얻는다. 상기와 같이 얻어진 조작출력치는 대상물에 적용되어 대상물이 조작출력치에 의해 제어된다.

속도형 I 제어연산은 상기 편차에 따라 I-연산항에 준하여 행해지므로써, I-제어연산출력치를 얻는다. 이 I-제어연산출력치는 위치형 I 신호로 변환된다. 한편, 위치형 P 제어연산은 P-연산항에 준하여 행해지므로써 위치형 P제어연산이 얻어지며, 위치형 D 제어연산은 제어치에 따라 D-연산항에 준하여 행해지므로써 위치형 D 제어연산을 얻는다.

상기 위치형 D제어연산은, 목표치의 변경에 의해 D제어치가 상, 하한을 초과하여 증가될때 문제발생가능성을 배제시킨다.

상기 위치형 I 신호, 위치형 P 제어연산출력치 및 상기 위치형 D제어연산출력치가 합산되어 한 조작 출력치를 제공한다. 이 조작출력치가 대상물에 공급되어, 대상물이 상기 조작출력치에 따라 제어된 다.

PI 제어연산은 상기 편차에 따라, P-연산항, 및 I -연산항에 준하여 행해지므로써, I-연산출력치를 얻으며, 또는 PID 제어연산이 상기 편차에 따라, PD-연산항 및 I-연산항에 준하여 행해지므로써, I -연산출력치를 얻는다. 전자의 경우, I-제어연산출력치는 속도-위치 신호변환수단(speed-position signal conberting means)에 의해 위치형 I 신호로 변환되며, 위치형 I 신호는 P-연산항으로부터 얻어진 P-연산출력치에 가산된다. 이들 항의 합계는 상한/하한 한정수단(limiting means)에 입력되어, 조작출력치를 발생한다. 후자의 경우, I-연산출력치가 속도-위치신호변환수단에 의해, 위치형 I -신호로 변환되며, 이 위치형 I 신호는 PD-연산항으로부터 얻어진 PD-연산항으로부터 얻어진 PD-제어연산출력치에 가산된다. 이들 항들의 합게는 상한/하한 한정수단에 입력되어 조작출력치를 발생한다. 어느 경우이든, 상한 및 하한은 상기 상한/하한 한정수단에 세트된다.

상기 한정수단은, 입력치신호가 상한을 초과할때는 상한치를 속도-위치신호 변화수단에 공급하고, 입력치 신호가 하한 미만으로 떨어질때는 하한치를 거기에 공급한다. 다시 말해서, 상기 한정수단은 속도형 I 제어연산출력치의 크기를 제한한다.

그러므로, PI -연산항 또는 PID-연산항으로부터 I -연산항이 유도되고, 상기 속도형 제어연산이 이 I -연산항에 준하여 행해지는 경우, 상기 I -연산항은 ∑-연산항을 갖지 않게된다. 이 결과로, 본 발명에 의한 디지탈 제어기는 고속으로 연산하여 단 기간내에 PID 제어치를 얻으며, 연산모드의 전 환시 트랜스퍼를 범프가 발생되지 않게 쉽게 행할 수 있고, 다른 장치에 의한 신호에 대한 연산을 행할 수 있다.

본 발명의 다른 한 태양에 의하면, 위치형 제어연산은 목표치와 실제 제어치의 차이, 즉, 편차에 의하지 않고, 대상물로부터 공급되는 제어치에 따라 D-연산항에 준하여 행해진다. 그러므로, D-연산은 목표치의 변경에 의해 영향을 받지 않는다. 다시 말해서, D-연산항은 악기능과 디지탈 제어기의 불 안정한 연산을 야기하지 않는다.

본 발명의 또 다른 태양에 의하면, I-연산항이 PID-연산항으로부터 유도되어, 속도형 제어연산에 의

해 속도형 I 신호로 변환되고, 최종적으로, 속도-위치 신호변환수단에 의해 위치형 I 신호로 변환된다. 한편, PD-연산항, 즉 PID-연산항의 잔여부분은 위치형으로 조정되어, 위치형 PD 제어연산으로변환된다. 한편, PD-연산항, 즉 PID-연산항의 잔여부분은 위치형으로 조정되어, 위치형 PD제어연산으로변환된다. 위치형 I 신호와 위치형 PD 제어연산이 가산되어, I 신호치와 PD 제어연산출력치의합계가 상, 하한이 미리 설정된 상한/하한 한정수단에 입력된다.

상기 합계치가 상한치를 초과하는 경우, 그 상한치가 신호변환수단에 세트된다. 합계치가 하한치에 미달되는 경우, 그 하한치가 상기 신호변환수단에 세트된다. 그러므로, 상기 속도형 I 제어동작 출력치가, 그 크기가 상기 신호변환수단에 세트된 상한 및 하한의 범위내에 속하는 한, 대상물을 연속적으로 제어한다. 또한 대상물의 I 연산중 리세트 와인드 업(reset wind-up)되는 경우가 발생치 않는다.

본 발명의 실시예들을 설명하기에 앞서, PID 제어원리와, PID 제어에 포함되는 신호 프로세싱 (processing)방법을 설명한다.

방정식(3)에서, P-연산항은  $K_P \cdot e$ , I-연산항은( $K_P \cdot T_1$ )  $\int$  edt, D-연산항은  $K_P \cdot T_0 \cdot (de/dt)$ 이다. P-연산항은 현재 편차 e에 비례하며, I-연산항은 이전에 얻어진 편차들의 적분치에 비례하고, D-연산항은 차후의 편차 변경률에 비례함을 명백히 알 수 있다. 각 연산항은 상기 방정식에 준하여 제어역활을 행한다. 상기 I-연산항은 부정의적이다. e=0일때는 P-연산항은 0이다. 상기 편차 e가 변환되지 않는한, D-연산항은 0이다 P 및 D-연산항은 영 스탠다드(standard)이다. 결과적으로, 신호 프로세싱에는 하기의 제약이 따른다. 속도형 신호들은 I-연산항의 산출에 고려하지 않을 수 있으나, 반면 D-연산항 및 P-연산항의 산출에는 고려하지 않을 수 없다. 왜냐하면, 상기 속도형 신호를 무시하는 경우, 편차가 0이거나 또는 변화가 없을때에 P-연산항 및 D-연산항은 0이 될 수 없기때문이다.

본 발명자들은 PID제어에 포함된 신호들을 여러방법으로 프로세싱하면서 실험을 반복실시하였으며, P-연산항, I-연산항 및 D-연산항의 특성을 연구하였다.

그 결과를 하기 표에 나타낸다.

[표 1]

| ul ÷ | 항                            | 위 | 치  | 형 | 속 도 형 |   | 형    | <b>ə</b> l —                             |

|------|------------------------------|---|----|---|-------|---|------|------------------------------------------|

| 번 호  |                              | Р | I  | D | P     | I | D    | 참 고                                      |

| 1    | P 제어로만 가능한가?                 | Y | 74 |   | N     |   |      | 속도형은 비한정적임                               |

| 2    | P연산범위 감소?                    | Y |    |   | N     |   |      | 속도형 경우의 범위초과 감소                          |

| 3    | I연산은 용이한가?                   |   | N  |   |       | Y |      | 속도형의 경우 매우 용이함                           |

| 4    | I연산에서 리세트 와인드업이<br>방지되는가?    |   | N  |   |       | Y |      |                                          |

| 5    | D연산 범위초과감소?                  |   |    | Y |       |   | N    | 속도형 경우의 범위초과감소                           |

| 6    | 수동-자동전환시 범프없는<br>트랜스퍼가 용이한가? |   | N  |   |       | Y | п    | 속도형의 경우 MV <sub>n-1</sub> 이 현재<br>조작출력치임 |

| 7    | 복합연산을 행하기가 용이한<br>가?         |   | N  |   |       | Y | W. W | 속도형의 경우, 변량만이 제<br>한되며, 이득조정됨            |

|      | 평 가                          | Y | N  | Y | N     | Y | N    |                                          |

# 주: Y=예, N=아니오.

표 1로부터 명백히 이해할 수 있듯이, P-연산항, I-연산항 및 D-연산항의 특성은 위치형 연산시스템 및 속도형 제어연산시스템과 다르다. 본 발명에 의하면, 각 연산항들은, 표 1에 나타난 평가결과에따라, 위치형 연산시스템과 속도형 연산시스템을 적절히 사용한다.

본 발명에 의한 디지탈 제어기를 첨부도면을 참조하여 상세히 설명한다.

제4도는 본 발명의 제1실시예에 의한 디지탈 제어기를 나타낸다. 도면에 나타난 바와 같이, 상기 디지탈 제어기는 목표치 발생기(11), 인터페이스(interface)(12), 검출기(13), 아날로그-디지탈(A/D) 변환기(14), 인터페이스(15), 편차산출기(16), PI 또는 PID 연산제어유니트(17)및 디지탈-아날로그(D/A)변환기(18)를 포함한다.

상기 목표치 발생기(11)는 목표치 SV를 발생하도록 설계한다. 발생기(11)는 통상의 메모리 또는 프로그램 셋팅기(program setting device) 또는 디지탈 데이타 발생기등이다. 통상의 메모리를 발생기(11)로서 사용하면, 이 메모리로부터 소정의 주기로 상기 목표치가 독출된다. 프로그램 셋팅기를 발생기(11)로서 사용하면, 이 메모리로부터 소정의 주기로 상기 목표치가 독출된다. 프로그램 셋팅기를 발생기(11)로서 사용하면, 이 장치는 소정기간 경과시마다 목표치 SV를 출력한다. 디지탈 데이타 발생기를 상기 발생기(11)로서 사용하면, 이 발생기가 자동으로 또는 수동연산될때에, 목표치를 발

생한다. 상기 인터페이스(12)는 PI 연산제어유니트(17)로부터 공급되는 샘플링 신호 S에 응답하여, 발생기(11)로부터 상기 목표치 SV를 수신하며, 현재 목표치 SV 등 출력한다. 상기 검출기(13)는, D/A 변환기(18)에 접속되어 있고, 디지탈 제어기에 의해 제어되는 대상물(19)로부터 공급되는 아날 로그 제어치 PV 를 검출한다. 또는, 상기 검출기(13)는 각 샘플링 기간중 아날로그 제어치 PV 를 검 출한다. 상기 A/D변환기(14)는 상기 검출기(13)으로부터 공급되는 아날로그 제어치 PV 를 수신하며, PV 차를 디지탈 제어치 PV로 변환시킨다.

상기 인터페이스(15)는 한 메모리를 갖는다. 이것은 PI 연산제어유니트(17)로부터 공급되는 샘플링신호 S에 응답하여, A/D변환기(14)로부터 디지탈 제어치 PV를 수신한다. 수신된 PV치는 수 기간동안상기 메모리내에 기억된다. 상기 디지탈 제어치 PV는 인터페이스(15)로부터 독출되어, 제어치 PV , 처럼 상기 편차산출기(16)에 입력된다.

상기 편차산출기(15)는 두 인터페이스(12) 및 (15)의 출력 즉, SVn 및 PVn 을 수신한다. 편차산출기 (16)은 목표치 SVn 으로부터 상기 제어치 PVn 을 감하여, 현재 편차 en 을 구한다. 이 편차 en 은 PI 연산제어유니트(17)에 공급된다. 이 PI 연산제어유니트(17)는 P-연산항 및 I-연산항에 따라, 위치형시스템 또는 속도형 시스템에 준하여, PI 연산을 행하므로써, 조작출력치 MVn 을 얻는다. 이 출력치 MVn 은 상기 D/A 변환기(18)에 입력된다. 이 D/A 변환기는 상기 출력치(MVn)를 아날로그 출력치 MVn 으로 변환시키고, 이 출력치는 대상물(19)에 공급되어 대상물(19)를 제어한다.

제5도는 PI 연산제어유니트(17)를 보다 상세히 나타낸다. 이 PI-연산유니트(17)는 유속제어시스템 또는 압력제어시스템 용도에 적합하다. 간소화를 위해, 각 샘플링기간 r중, 디지탈 목표치 SV n 과 디지탈 제어치 PV n 을 상기 편차산출기(16)에 입력하는 것이 바람직한 것으로 보인다. 편차산출기(16)는 현재 목표치 SV n 에서 현재 제어치 PV n 을 감하여, 샘플링 기간중에 형성된 현재 편차 e n 을 얻는다. 이 편차 e n 은 PI 연산제어유니트(17)에 공급된다. 이 유니트(17)은 P-연산항 및 I-연산항의 특성에 따라 표 1에 준하여, 그리고 현재 편차 e n 에 준하여, 위치형 PI-연산 또는 속도형 PI 연산을 행한다.

제5도에 나타난 바와 같이, PI 연산제어유니트(17)는 위치형 P-제어연산기(21), 속도형 I-제어연산기(22), 속도-위치신호변환기(23) 및 가산기 유니트(24)를 포함한다. 상기 위치형 P-연산기(21)는 현재 편차 e n 에 준하여 위치형 P 연산을 행하도록 설계된다. 상기 속도형 I-제어연산기(22)는, 현재 편차 e n 에 준하여 속도형 I-연산을 행하므로써 속도형 I 연산신호를 얻도록 설계된다. 상기 신호변환기(23)은 상기 속도형 I 연산신호를 위치형 I 신호로 변환시킨다. 상기 가산기 유니트(24)는 대상물(25)에 결합되며, 위치형 P-연산기의 출력 MV Pn 을 속도-위치신호변환기(23)의 출력 MV In 에 가산하므로써, 조작출력치 MVn 을 얻는다.

제4 및 제5도에 나타난 디지탈 제어기의 연산을 하기에 설명한다. 우선, 편차산출기(16)가 현재 목표치 SV  $_{n}$  에서 제어치 PV  $_{n}$  을 감하여, 샘플링기간중 형성된 현재 편차( $e_{n}$ )를 얻는다. 이 편차  $e_{n}$  은 상기 위치형 P-제어연산기(21)과 속도형 I-제어연산기(22)에 공급된다. P-제어연산기(21)는 하기 연산을 행하여 위치형  $MV_{Pn}$  을 얻는다.

| $e_{P} = K_{P} \cdot e_{n} \cdot \cdots \cdot \cdot$ |

|------------------------------------------------------------------------------------------------------------------------------------------------|

|------------------------------------------------------------------------------------------------------------------------------------------------|

한편 속도형 I-제어연산기(22)는, 하기 동작을 행하여, 속도형 I 출력치 △WV』을 얻는다 :

$$\Delta_{\text{MV}_{1n}}=K_P \cdot (\tau / T_1)e_n$$

.....(5)

속도형 I 출력치 △MV In 은 상기 속도-위치신호변환기(23)에 입력된다. 상기 신호변환기(23)는 하기 연산을 행하여 위치형 I 출력치 MVIn 을 얻는다 :

$$\mathsf{MV}_{\mathsf{In}} = \mathsf{MV}_{\mathsf{In}-1} = \Delta \mathsf{MV}_{\mathsf{In}} \qquad \cdots \qquad (6)$$

상기 위치형 P 출력치  $MV_{Pn}$  과 위치형 I 출력치  $MV_{In}$  은 가산기 유니트(24)에 입력된다. 가산기 유니트(24)는 하기 연산을 행하여 조작출력치  $MV_{In}$ 을 얻는다 :

$$MV_n = MV_{Pn} = MV_{In}$$

.....(7)

상기 조작출력치 MV n 은 대상물(15)에 공급되어, SV n 이 PV n 과 동치가 될때까지 대상물(15)를 제어한다.

전술한 바와 같이, 제4 및 제5도의 디지탈 제어기에서는, P-연산항 및 I-연산항이 위치형 연산 및 속도형 연산에 각각 종속된다. 그러므로, 본 디지탈 제어기는 몇가지 장점을 갖는다. 첫째로, 편차 e n 이 단계적으로 변화하고, P연산출력치가 범위초과(over-range)되는 경우, 범위초과 P-연산출력치가 전혀 감소하지 않는다. 따라서, 제어방해가 미약하며, PI 제어의 신뢰성이 높다. 둘째로는, I-연산항이 PI 연산항과 속도형 연산에 종속된 연산항으로부터 유도되기때문에 I 연산이 평이하며, 고속으로 행해질 수 있다. 셋째로는, 각 샘플링 기간중 얻어진 변량 △MV In 만을 제한하기에 충분하므로, 적분기간으로부터 리세트 와인드업이 발생되지 않는다. 또한, 수동모드에서 자동모드로, 또는 그 반대로 연산모드를 전환할때 트랙스퍼를 범프가 발생되지 않게 용이하게 성취할 수 있다.

제6도는 PID 연산시스템이자 본 발명의 제2실시예인 다른 디지탈 제어기를 나타낸다. 제6도의 PID

연산시스템은 온도 제어시스템 또는 레벨 제어시스템의 제어에 적합한 조작출력치 MV . 을 발생하도록 설계된다.

제6도로부터 명백히 이해할 수 있듯이, PID 연산유니트(17)는 위치형 P-제어연산(21), 속도형 I-제어연산기(22), 신호변환기(23), 가산기 유니트(24a) 및 위치형 D-제어연산기(26)를 포함한다.

제2실시예의 연산을 하기에 설명한다. 편차산출기(16)가 제2실시예에서도 역시 사용되며, 이것이 목표치 SVn에서 제어치 PVn을 감하여 편차 en을 얻는다. 이 편차 en은 위치형 P-제어연산기(21), 속도형 I-제어연산기(22) 및 위치형 D-제어연산기(26)에 공급된다. 위치형 P-제어연산기(21)는 편차 en에 준하여 방정식(4)의 연산을 행하여 위치형 P-연산출력치 MVn을 얻는다. 상기 속도형 I-제어연산기(22)는 편차 en에 준하여 방정식(5)의 연산을 행하므로써, 속도형 I-연산출력치  $\triangle$ MVn을 얻는다. 이  $\triangle$ MVn 치는 속도-위치신호변환기(23)에 입력된다. 이 신호변환기(23)은 방정식(6)의 연산을 행하여, 위치형 I-신호 MVn을 얻는다.

한편, 위치형 D-제어연산기(26)는 편차 e n 에 준하여, 하기 연산을 행하므로써, 위치형 D-출력치 MVnn 을 얻는다 :

$MV_{Pn}$ = $KP \cdot (T_D/\tau) \cdot (e_n-e_n-e_{n-1})$ ....(8)

상기 제어연산기(21), (23) 및 (26)에 의한 출력치는 상기 가산기 유니트(24a)에 입력된다. 이 가산기 유니트(24a)는 이 입력치에 준하여 하기 연산을 행하므로써 조작출력치 MV。을 얻는다.

$MV_n = MV_{Pn} + MV_{In} + MV_{Dn} + MV_{Dn}$

상기 조작출력치 MV n 은 대상물(25)에 공급되어, PV n 치가 목표치 SV n 과 동치가 될때까지 대상물(25)이 제어된다.

이론적으로, 제2실시예에서 사용된 D-연산항은 완전 미분항, 즉  $K_P(T_D/r)=K_P \cdot SOIC$ . 그러나, 대부분의 경우, 실제 D-연산항은 완전 미분항이 아니다. 즉  $(K_P \cdot T_D \cdot S)/(1+^m \cdot T_D \cdot S)$ 이며, 식에서  $T_D \cdot D$  미분시간,  $(1/^m)$ 은 미분이득,  $T_D \cdot D$  대부분의 경우  $(1/^m)$ 0은 마분이득,  $T_D \cdot D$  이 연산자(Lapice operator)이다. 그러므로, 상기 위치형 D-제어연산기(26)가 불완전 미분을 행하는 경우, 그 출력치  $\Delta_{MVD}$  은 하기와 같게 된다 :

$$MV_{Dn} = \frac{n \cdot T_D}{\tau + \eta \cdot T_D} MV_{Dn-1} + \frac{K_P \cdot T_D}{\tau + \eta \cdot T_D} (e_n - e_{n-1}) \qquad \cdots (10)$$

그러므로, 상기 디지탈 제어기는 제5도의 PI 연산유니트를 갖는 디지탈 제어기와 동일한 잇점을 얻는다. 또한, 범위초과 P-제어연산출력치와 범위초과 D-제어연산출력치는, 조금이라도 발생하는 경우라도, 감소되지 않는다. 상기 디지탈 제어기, 즉, 본 발명의 제2실시예는 안전하고 신뢰성있는 PID 제어를 행한다.

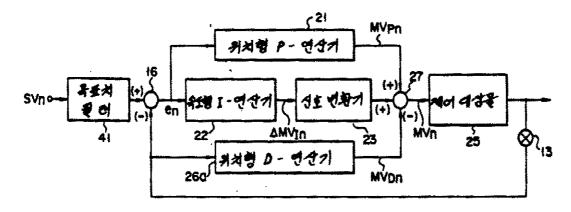

제7도는 제6도의 PID 연산시스템 대신에, 제2실시예에서 사용될 수 있는 다른 D 연산시스템을 설명한다. 제7도의 PID 연산시스템은, 위치형 D-제어연산기(26a)이 제5 및 제6도에 설명된 연산시스템에서처럼, 편차 en에 준하지 않고 제어치 PVn에 준하여 위치형 D-연산을 행하는 것만을 제외하고는, 제6도의 PID 연산시스템과 동일하다.

통상, D-연산이 편차 e, 에 준하여 행해지는 경우, 목표치 SV,과 PV, 이 변하면, D-연산출력치가 변한다.

그러므로, 신뢰성있는 프로세스제어를 얻으려면 유도항(deri-vative term)을 조정한다. 그러나, 목표치 SV, 의 변경에 따라 편차 e, 이 크게 변하는 경우, 미분이 과도히 행해지므로, 필연적으로 조작연산출력치가 과도출력(over-shooting)된다.

본 발명에 의하면, 목표치 SV<sub>n</sub> 의 변량은 무시되며, 위치형 D-연산은 제어치 PV<sub>n</sub> 에 준하여 행해진다. 그러므로 상기 조작출력치의 과도출력이 발생하지 않으며, 제7도의 PID 연산유니트를 갖 는 디지탈 제어기는 안전하고 신뢰성있는 PID 제어를 얻는다.

제8도는 제6도에서 설명된 PID 연산시스템 대신에, 본 발명의 제2실시예에서 사용될 수 있는 다른 PI연산시스템을 나타낸다. 제8도의 PI 연산시스템은, 대상물(25)의 가변조건에 따라 필요한 경우, 조작출력치 MV, 뿐만 아니라 I-연산출력치를 제한하도록 설계된다. 제8도에 설명된 바와 같이, 상기 PI 연산시스템 위치형 P-제어연산기(21), 속도형 I-제어연산기(22), 속도-위치신호변환기(31), 가산기 유니트(32), 및 상한/하한 리미터(limiter)(33)을 포함한다.

상기 신호변환기(31)은 두가지 기능을 행한다 : (i) 속도형 I-제어연산기(22)의 출력치를 위치형 I-신호를 변환시키는 기능을 행하며, (ii) 상기 상한/하한 리미터(33)에 의해 세트된 상한 H 및 하한 L에 따라 위치형 I-신호의 출력치를 한정하는 기능을 행한다. 가산기 유니트(32)는 상기 제어연산기(21) 및 (31)의 출력들을 가산하여, 조작출력치 MV 등 얻는데 사용된다. 상한 H 및 하한 L은 외부에서 상한/하한 리미터(33)에 세트된다. 리미터(33)는 가산기 유니트(32)로부터의 조작출력치 MV 등 이 상한 H를 초과할 때, 이 출력치를 상한 H로 감소시키며, MV 등 치가 하한 L에 미달될때, MV 를 하

한 L에 유지시킨다.

제8도에 나타난 PI 제어유니트의 연산을 하기에 설명한다. 편차산출기(16)는 목표치 SV  $_{n}$  에서 제어치 PV  $_{n}$  을 감하여, 편차 e  $_{n}$  을 구한다. 편차 e  $_{n}$  은 위치형 P-제어연산기(21)와 속도형 I-제어연산기(22)에 입력된다. 위치형 P-제어연산기(21)는 편차 e  $_{n}$  에 준하여 방정식(4)의 연산을 행하여, 위치형 P-연산출력치 MV  $_{Pn}$  치를 구한다. 이 MV  $_{Pn}$  치는 가산기 유니트(32)에 입력된다. 속도형 I-제어연산기(22)는 편차 e  $_{n}$  에 준하여 방정식(5)의 연산을 행하여, 속도형 I-연산출력치  $\Delta$ MV  $_{In}$  치를 구한다. 이  $\Delta$ MV  $_{In}$  치는 신호변환기(31)에 입력된다. 신호변환기(31)는,  $\Delta$ MV  $_{In}$  치를 한정하지 않으며 이  $\Delta$ MV  $_{In}$  치를 위치형 I-신호로 변환시킨다. I-신호는 상기 가산기 유니트(32)에 입력된다.

가산기 유니트(32)는 MV<sub>Pn</sub> 치와 MV<sub>In</sub> 치를 가산하여, 조작출력치 MV<sub>n</sub> 을 얻는다. 이 조작출력치 MV<sub>n</sub> 은 상한/하한 리미터(33)에 입력된다. 상한/하한 리미터(33)는 MV<sub>n</sub> 치가 상한 H을 초과할때 조작출력치 MV<sub>n</sub> 을 상한 H로 감소시키며, MV<sub>n</sub> 치가 하한 L에 미달될때 MV<sub>n</sub> 치를 하한 L에 유지시킨다. 상기와 같이 프로세스된 조작출력치 MV<sub>n</sub>는 대상물(25)에 공급한다.

상기 조작출력치 MV n 이 상한 H보다 크거나, 하한 L 보다 작을 때 △MV n 치가 제한되지 않은 경우, 조작출력치 MV n 이 I-신호 MV n 과 함께 점차적으로 증가하여, 결국 리세트 와인드업을 야기시킨다. 리세트 와인드업을 방지하기 위하여, 조작출력치 MV n 이 상한 H에 유지되거나 하한 L로 감소될 때, 적분을 멈출수 있다. 이 경우 대부분의 경우, 적분성분에 앞서 나타나는 MV n 치의 비례성분 또는 미분성분의 변화에 기인하여, MV n 치가 상한 H를 초과하여 유지되거나, 하한 L에 미달되어 유지된다. 따라서, 변화될 적분 출력치는, 조작출력치가 상한 H 또는 하한 L에 도달될때까지, 그대로 유지된다. 결과적으로, MV n 치의 적분성분이 버려진다.

제8도의 PI 연산시스템에서는, 조작출력치 MV  $_{n}$  이 상한/하한 리미터(33)에 세트된 상한 H 또는 하한 L 에 도달하면, 상한 H 또는 하한 L이 신호변환기(31)에 세트된다. 이후, 신호변환기(31)에 의한 I-신호 MV  $_{ln}$  출력치가 상한 H 또는 하한 L에 도달될때까지 적분이 행해지므로써 리세트 와인드업이 방지된다.

그러므로, 제8도의 PI 연산시스템을 갖는 디지탈 제어기는 조작출력치 MV, 이 상한 H 또는 하한 L에 도달하는 순간에 적분이 멈추는 디지탈 제어기에 비해, 하기의 관점에서 유리하다. 첫째로, I-신호 MV, 치가, 조작출력치 MV, 이 상한 H에 도달된후 상한 H 이하로 감소하거나, 하한 L에 도달한 후 하한 L 이상에 유지되는 경우에도, 연속적분에 의한 적정치를 갖기 때문에, 상기 제어기는 대상물의 변환에 정확하게 동조하여 대상물을 제어할 수 있다. 둘째로, 신호변환기(32)에, 출력치 MV, 이 상한 H에 유지될 때 상한 H가 세트되거나 또는 조작출력치 MV, 이 하한 L에 유지될때 하한 L이 세트되기 때문에, 속도형 신호 SA가 순방향 공급제어(fee-forward control)도중 I-신호에 가산될 때 I-신호 MV, 치의 유지되는 부분이 감소된다. I-신호의 상기 버려지는 부분의 감소때문에, 디지탈 제어기는 리세트 와인드업을 방지할 수 있을 뿐만 아니라, 신뢰성을 갖춘 개선된 제어를 달성할 수 있다.

제9도는 제6도의 PID 연산유니트 대신에, 본 발명의 제2실시예에서 사용될 수 있는 PID 연산시스템을 나타낸다.

제9도의 PID 연산시스템은, 위치형 D-연산 제어소자(26)이 사용된 것만을 제외하고는, 제8도의 유니트와 동일하다.

상기 유니트는 제8도의 PID 연산시스템과 동일한 방법으로 연산하여 동일한 잇점을 얻는다.

제10도는 제6도의 PID 제어시스템 대신에, 본 발명의 제2실시예에서 사용될 수 있는 다른 PID 연산시스템의 개략도이다. 제6~9도의 PID 연산시스템과 마찬가지로, 이 유니트는 각 연산항의 특성에 따라, P-연산항, I-연산항 및 D-연산항에 준하여 위치형 또는 속도형 연산을 행한다.

제10도로부터 이해할 수 있듯이 상기 PID 연산시스템은 목표치 필터(41)가 인터페이스(12)(제4도 참조)와 편차산출기(16)사이에 접속되는 점에서, 제6~9도에 설명된 것들과 다르다.

제10도의 PID 연산유니트는 제어상수를 P-연산항 및 I-연산항에 가산하여, 조작출력치, MV 에 대한 외부방해 영향을 제어하도록 설계된다. 더욱 구체적으로는, 목표치 필터(41)의 변수가 외부방해의 크기에 따라 두 값 사이에서 전환되어 상기 제어상수만을 변환시키기 때문에, 대상물(25)가 거의 적정하게 제어된다.

제10도의 제어시스템은 제11도의 전달함수에 의해 표시될 수 있다. P-연산항에 대한 목표치 SV , 의 변화의 영향은 하기와 같이 주어진다.

$$F(S) \cdot C(S) = \frac{I + \alpha \cdot T_{1} \cdot S}{1 + T_{1} \cdot S} \cdot K_{P} (1 + \frac{1}{T_{1} \cdot S})$$

$$= \frac{1 + \alpha \cdot T_{1} \cdot S}{1 + T_{1} \cdot S} \cdot K_{P} \cdot \frac{1 + T_{1} \cdot S}{T_{1} \cdot S}$$

$$= K_{P} (\alpha + \frac{1}{T_{1} \cdot S})$$

#### (57) 청구의 범위

#### 청구항 1

목표치(SVn)로부터 대상물(25)의 제어치(PVn)을 감하여 편차(en)를 얻는 편차산출수단(16); 상기 편차산출수단(16)에 의해 얻어진 편차(en)에 준하여 위치형 P-연산을 행하는 위치형 P-제어연산수단(21); 상기 편차산출수단(16)에 의해 얻어진 편차(en)에 준하여 속도형 I-연산을 행하는 속도형 I-제어연산수단(22); 상기 속도형 I-제어연산수단(22)의 속도형 I-연산출력치를 위치형 I-신호로 변환시키는 신호변환수단(23) 및 상기 신호변환수단(23)에 의해 얻어진 위치형 I-신호와 상기 위치형 P-제어연산수단(21)에 의해 얻어진 위치형 P-연산출력치를 가산하여 대상물(25)에 공급될 조작출력치(MVn)를 구하는 가산기수단(24)을 포함하는 것이 특징인 디지탈 제어기.

#### 청구항 2

목표치(SVn) 로부터 대상물(25)의 제어치(PVn)을 감안하여 편차(en)를 얻는 편차산출수단(16); 상기 편차산출수단(16)에 의해 얻어진 편차(en)에 준하여 위치형 P-연산을 행하는 위치형 P-제어연산수단(21); 상기 편차산출수단(16)에 의해 얻어진 편차(en)에 준하여 속도형 I-연산을 행하는 속도형 I-제어연산수단(22)의 속도형 I-연산출력치를 위치형 I-신호로 변환시키는 신호변환수단(23); 상기 편차산출수단(16)에 의해 얻어진 편차(en)에 준하여 위치형 D-연산을 행하는 위치형 D-제어연산수단(26) 및 상기 위치형 D-제어연산수단(26)에 의해 얻어진 위치형 D-연산출력치와, 상기 신호변환수단(23)에 의해 얻어진 위치형 I-신호와 상기 위치형 P-제어연산수단(21)에 의해 얻어진 위치형 P-연산출력치를 가산하여 대상물(25)에 공급될 조작출력치(MVn)를 구하는 가산기수단(24a)을 포함하는 것이 특징인 디지탈 제어기.

#### 청구항 3

목표치(SVn) 로부터 대상물(25)의 제어치(PVn)을 감하여 편차(en)를 얻는 편차산출수단(16); 상기 편차산출수단(16)에 의해 얻어진 편차(en)에 준하여 위치형 P-연산을 행하는 위치형 P-제어연산수단(21); 상기 편차산출수단(16)에 의해 얻어진 편차(en)에 준하여 속도형 I-연산을 행하는 속도형 I-제어연산수단(22); 상기 속도형 I-제어연산수단(22)의 속도형 I-연산출력치를 위치형 I-신호로 변환시키는 신호변환수단(23); 상기 제어치(PVn)에 준하여 위치형 D-연산을 행하는 위치형 D-제어연산수단(26a)의해 얻어진 위치형 I-신호와 상기 위치형 P-제어연산수단(21)에 의해 얻어진 위치형 D-연산출력치를 가산하여 대상물(25)에 공급될 조작출력치(MVn)를 구하는 가산기수단(27)을 포함하는 것이 특징인 디지탈 제어기.

# 청구항 4

목표치(SVn)로부터 대상물(25)의 제어치(PVn)을 감하여 편차(en)를 얻는 편차산출수단(16) ; 상기 편 차산출수단(16)에 의해 얻어진 편차(en)에 준하여 위치형 P-연산을 행하는 위치형 P-제어연산수단 (21) ; 상기 편차산출수단(16)에 의해 얻어진 편차(en)에 준하여 속도형 I-연산을 행하는 속도형 I-제어연산수단(22) ; 상기 속도형 I-제어연산수단(22)의 속도형 I-연산출력치를 위치형 I-신호로 변 환시키는 신호변환수단으로서 이 수단(31)에 상한(H)이 세트될때 상한(H)에서의 위치형 I-신호의 크 기를 유지시키는 이 수단(31)에 하한(L)이 세트될때 하한(L)에서의 위치형 I-신호의 크기를 유지시 신호변환수단(31) ; 상기 신호변환수단(31)에 의해 얻어진 위치형 I-신호와 상기 위치형 P-제 어연산수단(21)에 의해 얻어진 위치형 P-연산출력치를 가산하여 조작출력치(Mn)를 구하는 가산기수 단(32) 및 상기 편차산출수단(16)에 의해 얻어진 편차(e,)에 준하여 속도형 I-연산을 행하는 속도형 I-제어수단(22) ; 상기 속도형 I-제어연산수단(22)의 속도형 I-연산출력치를 위치형 I-신호로 변환 시키는 신호변환수단으로서 이 수단(31)에 상한(H)이 세트될때 상한(H)에서의 위치형 I-신호의 크기 를 유지시키며 이 수단(31)에 하한(L)이 세트될때 하한(L)에서의 위치형 I-신호의 크기를 유지시키 는 신호변환수단(31) ; 상기 편차산출수단(16)에 의해 얻어진 편차(en)에 준하여 위치형 D-연산을 행하는 위치형 D-제어연산수단(26) ; 상기 위치형 D-제어연산수단(26)에 의해 얻어진 위치형 D-연산 출력치와 상기 신호변환수단(31)에 의해 얻어진 위치형 I-신호와 상한(H) 및 하한(L)을 갖으며, 조 작출력치(MVn)가 상한(H)보다 클때, 상기 가산기수단(32)에 의해 얻어진 조작출력치를 상기 상한 (H)에 유지시키고 상기 상한(H)를 상기 가산기수단(32)에 세트하며, 상기 조작출력치(MVn)가 하한 (L)보다 작을때 조작출력치(MV。)를 하한(L)에 유지시키며 상기 조작출력치(MV。)를 대상물(25)에 공급 하는 상한/하한 리미터수단(33)을 포함하는 것이 특징인 디지탈 제어기.

#### 청구항 5

목표치(SV<sub>n</sub>)로부터 대상물(25)의제어치(PV<sub>n</sub>)을 감하여 편차(e<sub>n</sub>)를 얻는 편차산출수단(16) ; 상기 편차산출수단(16)에 의해 얻어진 편차(e<sub>n</sub>)에 준하여 위치형 P-연산을 행하는 위치형 P-제어연산수단(21); 상기 위치형 P-제어연산수단(21)에 의해 얻어진 위치형 P-연산출력치를 가산하여 조작출력치(MV<sub>n</sub>)를 구하는 가산기 수단(32) 및 상한(H) 및 하한(I)을 갖으며 이 조작출력치가 상한(H)보다 클때 상기 가산기 수단(32)에 의해 얻어진 조작출력치(MV<sub>n</sub>)를 상한(H)에 유지시키고 이 상한(H)를 상기 가산기수단(32)에 세트하며 상기 조작출력치(MV<sub>n</sub>)가 하한(L)보다 작을때, 상기 조작출력치(MV<sub>n</sub>)를 하한(L)에 유지시키며, 상기 조작출력치(MV<sub>n</sub>)를 대상물(25)에 공급하는 상한/하한 리미터수단을 포함하는 것이 특징인 디지탈 제어기.

## 청구항 6

목표치(SVn)에서 대상물(25)의 제어치(PVn)을 감하여 얻어진 편차를 소거하여 제어치(PVn)가 대상물(25)에 공급되도록 PI 연산 또는 PID 연산을 행하는 디지탈 제어기에 의해 PID 연산을 행하는 방법에 있어서, I-연산항을 PI-연산항 또는 PID-연산항으로부터 독립시키는 단계와 ; 상기 I-연산항에 준하여 속도형 연산을 행하므로써 속도형 I-연산출력치를 얻는 단계와 ; 상기 속도형 I-연산출력치를 위치형 I-신호로 변환시키는 단계와 ; 상기 위치형 I-신호를 P-연산출력치 또는 PD-연산출력치에 가산하여 상기 조작출력치(MVn)을 얻는 단계를 포함하는 것이 특징인 디지탈 제어기에 의한 PID 연산수행방법.

### 도면

# 도면1

도면2

도면3

도면4

# 도면5

# 도면6

도면7

# 도면8

도면9

도면10

도면11