# (19) 国家知识产权局

# (12) 发明专利

(10) 授权公告号 CN 110531125 B (45) 授权公告日 2022.05.17

(21) 申请号 201910435481.1

(22) 申请日 2019.05.23

(65) 同一申请的已公布的文献号 申请公布号 CN 110531125 A

(43) 申请公布日 2019.12.03

(30) 优先权数据

107117637 2018.05.23 TW 108116979 2019.05.16 TW

(73) 专利权人 旺矽科技股份有限公司 地址 中国台湾新竹县竹北市中和街155号

(72) 发明人 黄建名 黄则修 简志忠 杨惠彬 刘家宏 黄朝敬 林松柏 王千魁

(74) 专利代理机构 北京律诚同业知识产权代理 有限公司 11006

专利代理师 王玉双 张燕华

(51) Int.CI.

GO1R 1/073 (2006.01)

GO1R 1/067 (2006.01)

**GO1R** 31/28 (2006.01)

(56) 对比文件

CN 103675369 A.2014.03.26

CN 101346633 A, 2009.01.14

CN 104793026 A, 2015.07.22

CN 104076172 A,2014.10.01

CN 101341412 A, 2009.01.07

CN 102478590 A, 2012.05.30

CN 101467051 A,2009.06.24

CN 101755216 A,2010.06.23

US 2011063066 A1,2011.03.17

审查员 苗文

权利要求书2页 说明书7页 附图5页

#### (54) 发明名称

空间转换器、探针卡及其制造方法

本发明公开一种空间转换器、探针卡及其制 造方法。所提出的空间转换器与探针卡适用于探 测晶圆,所述晶圆包含多个晶粒,各晶粒可与集 成电路载板封装成集成电路芯片,且所述集成电 路载板的上表面与下表面之间具有一电路布局。 所述空间转换器包含增厚层体与第一多层体。增 厚层体包含多个中间连接区块,第一多层体设置 于增厚层体的下表面。第一多层体包含彼此间隔 排列的多个空间转换区块,且各空间转换区块包 含彼此相对的第一上接触区与第一下接触区,各 第一上接触区分别电性连接于各中间连接区块。 彼此相对的第一上接触区与第一下接触区之间 四 具有一电路布局,且各空间转换区块的电路布局 相同于所述集成电路载板的电路布局。此外,相 邻二第一下接触区沿一轴向具有间距D,各第一 下接触区沿上述轴向具有宽度W,其中D=n×W, 且n为大于或等于2的正整数。

- 1.一种空间转换器,适用于一探针卡,所述探针卡适用于探测一晶圆,所述探针卡包含一电路板以及一探针头,所述空间转换器设置于所述电路板以及所述探针头之间,所述晶圆包含多个晶粒,各所述晶粒可与一集成电路载板封装成一集成电路芯片,所述集成电路载板的上表面与下表面之间具有一电路布局,其特征在于所述空间转换器包含:

- 一增厚层体,包含多个中间连接区块;

- 一第一多层体,利用多层有机工艺技术形成于所述增厚层体的下表面,包含彼此间隔排列的多个空间转换区块,各所述空间转换区块包含彼此相对的一第一上接触区与一第一下接触区,各所述第一上接触区分别电性连接于各所述中间连接区块,彼此相对的所述第一上接触区与所述第一下接触区之间具有一电路布局,且各所述空间转换区块的电路布局至少有70%以上等同于所述集成电路载板的电路布局;相邻二所述第一下接触区沿一轴向具有一间距D,各所述第一下接触区沿所述轴向具有一宽度W,其中D=n×W,且n大于1;及

所述增厚层体包含一核心层体与一第二多层体,所述多个中间连接区块位于所述核心层体,所述第一多层体形成于所述核心层体的下表面,所述第二多层体利用多层有机工艺技术形成于所述核心层体的上表面,包含彼此间隔排列的多个延伸电连接区块,各所述延伸电连接区块包含彼此相对的一第二上接触区与一第二下接触区,各所述第二下接触区分别电性连接于各所述中间连接区块。

- 2.根据权利要求1所述的空间转换器,其特征在于,更包含一强化层,设置于所述第二 多层体面向所述核心层体的表面或背向所述核心层体的表面。

- 3.根据权利要求1所述的空间转换器,其特征在于,更包含多个空接触点,设置于各所述多个第二上接触区的周围。

- 4.根据权利要求3所述的空间转换器,其特征在于,两个相邻的所述第二上接触区之间的区域为一空间间隔区,所述多个空接触点设置在所述空间间隔区。

- 5.根据权利要求4所述的空间转换器,其特征在于,所述空间间隔区更具有一电子元件放置区。

- 6.根据权利要求1所述的空间转换器,其特征在于,所述核心层体与所述第二多层体的总厚度大于0.3mm。

- 7.根据权利要求1所述的空间转换器,其特征在于,所述多个空间转换区块的数量为偶数。

- 8.根据权利要求7所述的空间转换器,其特征在于,更包含多个空接触区,各所述空接触区包含多个空接触点,所述第二多层体的上表面呈矩形,所述多个空接触区布设在所述第二多层体的上表面的四个角落及重心。

- 9.根据权利要求7所述的空间转换器,其特征在于,更包含多个空接触区,各所述空接触区包含多个空接触点,所述第二多层体的上表面呈矩形,所述多个空接触区布设在所述第二多层体的上表面的重心及以重心为基准沿一X轴向与一Y轴向延伸而与所述第二多层体的上表面周缘交会的四个区块。

- 10.根据权利要求7所述的空间转换器,其特征在于,更包含多个空接触区,各所述空接触区包含多个空接触点,所述第二多层体的上表面呈矩形,所述多个空接触区布设在所述第二多层体的上表面的四个角落、重心、及以重心为基准沿一X轴向与一Y轴向延伸而与所述第二多层体的上表面周缘交会的四个区块。

- 11.根据权利要求1所述的空间转换器,其特征在于,各所述空间转换区块的第一下接触区的接触点分布比所述第一上接触区的接触点分布更密集。

- 12.一种探针卡,其特征在于,所述探针卡包含:

如权利要求1至11任一项所述的空间转换器;

- 一电路板,设置于所述增厚层体的上表面;及

- 一探针头,电性连接于所述第一多层体的各所述空间转换区块的第一下接触区。

- 13.一种空间转换器的制造方法,所制造出的空间转换器适用于一探针卡,所述探针卡适用于探测一晶圆,所述晶圆包含多个晶粒,各所述晶粒可与一集成电路载板封装成一集成电路芯片,所述集成电路载板的上表面与下表面之间具有一电路布局,其特征在于,所述方法包含:

获取所述集成电路载板的电路布局;

提供一核心层体,包含多个中间连接区块;及

以多层有机工艺技术逐层于所述核心层体的二表面分别形成一第一多层体与一第二多层体,所述第一多层体包含彼此间隔排列的多个空间转换区块,各所述空间转换区块包含彼此相对的第一上接触区与第一下接触区,各所述第一上接触区分别电性连接于各所述中间连接区块,彼此相对的所述第一上接触区与所述第一下接触区之间具有一电路布局,且各所述空间转换区块的电路布局至少有70%以上等同于所述集成电路载板的电路布局;相邻二所述第一下接触区沿一轴向具有一间距D,各所述第一下接触区沿所述轴向具有一宽度W,其中D=n×W,且n大于1;所述第二多层体包含彼此间隔排列的多个延伸电连接区块,各所述延伸电连接区块包含彼此相对的第二上接触区与第二下接触区,各所述第二下接触区分别电性连接于各所述中间连接区块。

14.一种探针卡的制造方法,所制造出的探针卡适用于探测一晶圆,所述晶圆包含多个晶粒,各所述晶粒可与一集成电路载板封装成一集成电路芯片,所述集成电路载板的上表面与下表面之间具有一电路布局,其特征在于,所述方法包含:

获取所述集成电路载板的电路布局;

提供包含有多个中间连接区块的一核心层体;

以多层有机工艺技术逐层于所述核心层体的二表面分别形成一第一多层体与一第二多层体,所述第一多层体包含彼此间隔排列的多个空间转换区块,各所述空间转换区块包含彼此相对的第一上接触区与第一下接触区,各所述第一上接触区分别电性连接于各所述中间连接区块,彼此相对的所述第一上接触区与所述第一下接触区之间具有一电路布局,且各所述空间转换区块的电路布局至少有70%以上等同于所述集成电路载板的电路布局;相邻二所述第一下接触区沿一轴向具有一间距D,各所述第一下接触区沿所述轴向具有一宽度W,其中D=n×W,且n大于1;所述第二多层体包含彼此间隔排列的多个延伸电连接区块,各所述延伸电连接区块包含彼此相对的第二上接触区与第二下接触区,各所述第二下接触区分别电性连接于各所述中间连接区块;

电性连接一电路板于所述第二多层体的各所述延伸电连接区块的第二上接触区;及电性连接一探针头于所述第一多层体的各所述空间转换区块的第一下接触区。

# 空间转换器、探针卡及其制造方法

#### 技术领域

[0001] 本发明涉及一种空间转换器、探针卡及其制造方法。

### 背景技术

[0002] 传统的集成电路芯片的制造方法是先在晶圆上形成多个晶粒,然后将晶圆进行切割而形成多个独立的晶粒,各个独立的晶粒再分别予以封装而成。晶粒本身依据功能的不同而可以有不同的尺寸,功能复杂的晶粒的尺寸通常比较大,晶粒上的接触点的数量也较多,因此接触点的间距通常甚窄。功能较简单的晶粒上的接触点虽然较少,但因为晶粒的尺寸也比较小,因此接触点的间距也同样甚窄。因此,一般的晶粒难以与电路板直接进行电性连接。

[0003] 为了让晶粒中的电路能够和电路板进行电性连接,必须将晶粒上的接触点的空间分布予以放大,此步骤称之为空间转换(space transform)。空间转换通常是通过将晶粒焊接于集成电路载板上来实现。集成电路载板具有上表面与下表面,其上表面的上接触点的空间分布与对应晶粒的接触点的空间分布相同,下表面的下接触点的分布则较为宽裕,上表面与下表面之间则存在一电路布局将上表面的上接触点与下表面的下接触点予以电性连接。如此一来,晶粒上的接触点的空间分布便得以通过集成电路载板而放大。

[0004] 晶粒在与集成电路载板结合前,通常必须经过检测程序,例如通过探针卡进行针测(probing test)。为了能够对晶圆上的晶粒进行探测,探针卡上的探针分布也必须与晶粒上的接触点分布相同,因此探针同样也会有紧凑的分布。如同前面所述,晶粒上的接触点因为紧凑分布所以难以直接与电路板电性连接,同样地,紧凑分布的探针也会有难以直接与测试电路板进行电性连接的问题,因此探针同样也必须经过「空间转换器」进行空间转换始能与测试电路板电性连接。

[0005] 空间转换器如同集成电路载板般具有上表面与下表面,其中与探针相连接的下表面具有与探针分布相同的紧凑的接触点分布,朝向测试电路板的上表面则具有较宽裕的接触点分布。空间转换器的上表面与下表面之间同样通过一电路布局来将上表面的接触点与下表面的接触点相互电性连接。

[0006] 传统半导体测试业者在进行探针分布的空间转换时,均只考量空间转换器的下表面的探针分布必须与晶粒上的接触点分布相同,以及上表面的接触点分布必须能够和测试电路板进行电性连接,均未考量到空间转换器的上下二表面之间的电路布局设计可能对晶粒电性测试表现的影响。由于晶粒必须进一步与集成电路载板连接后予以封装成集成电路芯片,因此晶粒在进行测试时的电性表现不见得与其被封装成集成电路芯片之后的电性表现一致。

#### 发明内容

[0007] 有鉴于此,本发明的目的在于提出一种空间转换器,适用于一探针卡,探针卡适用于探测包含有多个晶粒的一晶圆。各晶粒可与集成电路载板封装成集成电路芯片,集成电

路载板的上表面与下表面之间具有一电路布局。所述空间转换器包含:一增厚层体,包含多个中间连接区块;及一第一多层体,设置于增厚层体的下表面,包含彼此间隔排列的多个空间转换区块,各空间转换区块包含彼此相对的第一上接触区与第一下接触区,各第一上接触区分别电性连接于各中间连接区块,彼此相对的第一上接触区与第一下接触区之间具有一电路布局,且各空间转换区块的电路布局相同于集成电路载板的电路布局;相邻二第一下接触区沿一轴向具有一间距D,各第一下接触区沿轴向具有一宽度W,其中D=n×W,且n为大于或等于2的正整数。

[0008] 本发明还提出一种探针卡,包含:上述空间转换器;一电路板,设置于增厚层体的上表面;及一探针头,电性连接于第一多层体的各空间转换区块的第一下接触区。

[0009] 本发明还提出一种空间转换器的制造方法,所制造出的空间转换器适用于一探针卡,探针卡适用于探测一晶圆,晶圆包含多个晶粒,各晶粒可与一集成电路载板封装成一集成电路芯片,集成电路载板的上表面与下表面之间具有一电路布局,探针卡的制造方法包含:获取集成电路载板的电路布局;提供包含有多个中间连接区块的一核心层体;以多层有机工艺技术逐层于核心层体的二表面分别形成一第一多层体与一第二多层体,第一多层体包含彼此间隔排列的多个空间转换区块,各空间转换区块包含彼此相对的第一上接触区与第一下接触区,各第一上接触区分别电性连接于各中间连接区块,彼此相对的第一上接触区与第一下接触区之间具有一电路布局,且各空间转换区块的电路布局相同于集成电路载板的电路布局;相邻二第一下接触区沿一轴向具有一间距D,各第一下接触区沿轴向具有一宽度W,其中D=n×W,且n为大于或等于2的正整数;第二多层体包含彼此间隔排列的多个延伸电连接区块,各延伸电连接区块包含彼此相对的第二上接触区与第二下接触区,各第二下接触区分别电性连接于各中间连接区块。

[0010] 本发明还提出一种探针卡的制造方法,所制造出的探针卡适用于探测包含有多个晶粒的晶圆,各晶粒可与集成电路载板封装成集成电路芯片,集成电路载板的上表面与下表面之间具有一电路布局,探针卡的制造方法包含:获取集成电路载板的电路布局;提供包含有多个中间连接区块的一核心层体;以多层有机工艺技术逐层于核心层体的二表面分别形成一第一多层体与一第二多层体,第一多层体包含彼此间隔排列的多个空间转换区块,各空间转换区块包含彼此相对的第一上接触区与第一下接触区,各第一上接触区分别电性连接于各中间连接区块,彼此相对的第一上接触区与第一下接触区之间具有一电路布局,且各空间转换区块的电路布局相同于集成电路载板的电路布局;相邻二第一下接触区沿一轴向具有一间距D,各第一下接触区沿轴向具有一宽度W,其中D=n×W,且n为大于或等于2的正整数;第二多层体包含彼此间隔排列的多个延伸电连接区块,各延伸电连接区块包含彼此相对的第二上接触区与第二下接触区,各第二下接触区分别电性连接于各中间连接区块;电性连接一电路板于第二多层体的各延伸电连接区块的第二上接触区;及电性连接一探针头于第一多层体的各空间转换区块的第一下接触区。

[0011] 由于上述空间转换器的电路布局设计成与集成电路载板的电路布局相同,使得整体测试条件更贴近晶粒被封装成集成电路芯片时的状态,所得到的测试结果也更贴近真实,可靠度也更高。

[0012] 以下结合附图和具体实施例对本发明进行详细描述,但不作为对本发明的限定。

# 附图说明

| [0013] | 图1为本发明一实施例的示意图(一);             |         |                |         |

|--------|--------------------------------|---------|----------------|---------|

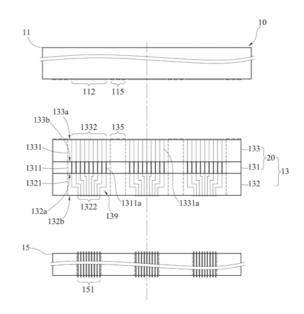

| [0014] | 图2为本发明一实施例的示意图(二);             |         |                |         |

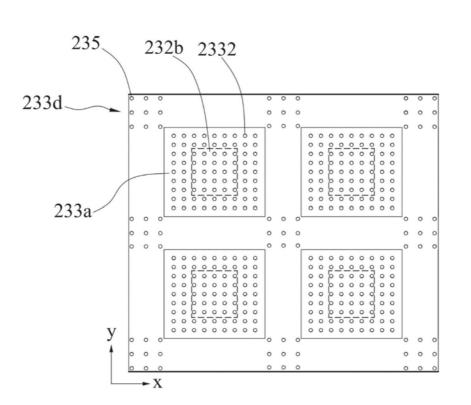

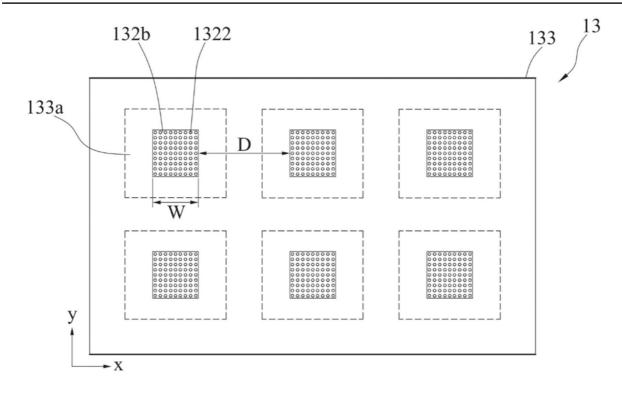

| [0015] | 图3为本发明一实施例的空间转换器的仰视图;          |         |                |         |

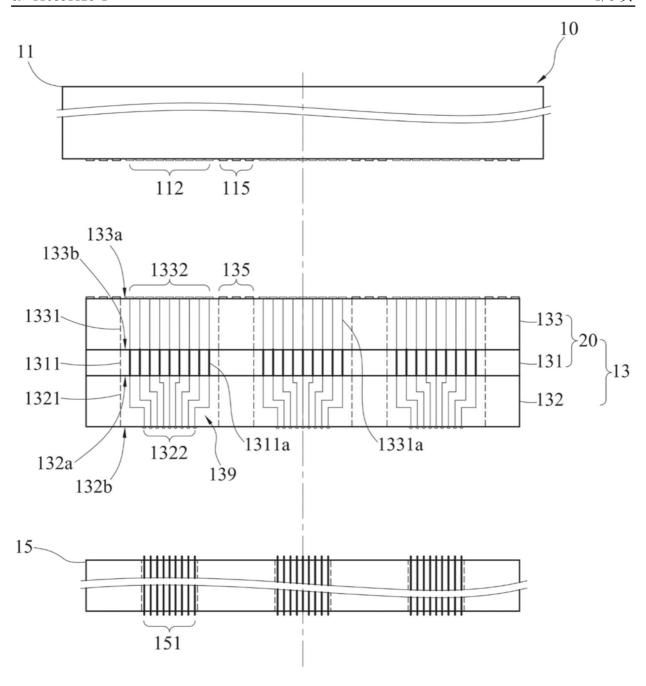

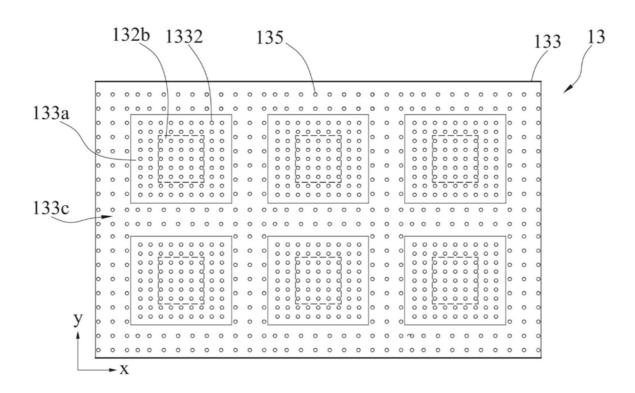

| [0016] | 图4为本发明一实施例的空间转换器的俯视图;          |         |                |         |

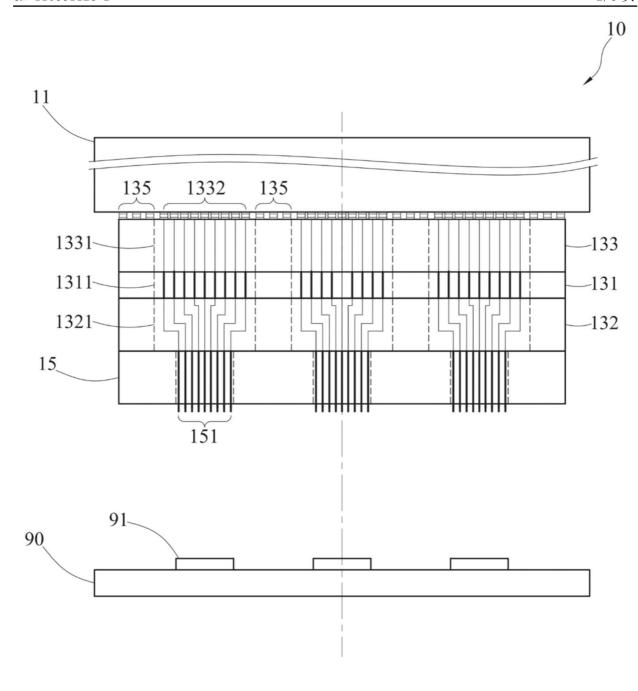

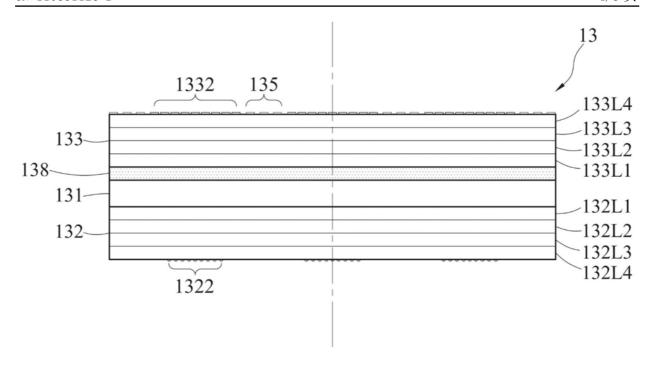

| [0017] | 图5为本发明另一实施例的示意图;               |         |                |         |

| [0018] | 图6为本发明的一例示空间转换器的空接触区的分布示意图(一); |         |                |         |

| [0019] | 图7为本发明的一例示空间转换器的空接触区的分布示意图(二); |         |                |         |

| [0020] | 图8为本发明的一例示空间转换器的空接触区的分布示意图(三)。 |         |                |         |

| [0021] | 其中,附图                          | 图标记     |                |         |

| [0022] | 10                             | 探针卡     | 11             | 电路板     |

| [0023] | 112                            | 电接触点    | 115            | 空接触点    |

| [0024] | 13                             | 空间转换器   | 131            | 核心层体    |

| [0025] | 1311                           | 中间连接区块  | 1311a          | 电连接通道   |

| [0026] | 132                            | 第一多层体   | 1321           | 空间转换区块  |

| [0027] | 132a                           | 第一上接触区  | 132b           | 第一下接触区  |

| [0028] | 1322                           | 下接触点    | $132L1 \sim 4$ | 基层      |

| [0029] | $133L1 \sim 4$                 | 基层      | 133            | 第二多层体   |

| [0030] | 133a                           | 第二上接触区  | 133b           | 第二下接触区  |

| [0031] | 133c                           | 空间间隔区   | 1331           | 延伸电连接区块 |

| [0032] | 1331a                          | 电连接通道   | 1332           | 上接触点    |

| [0033] | 135                            | 空接触点    | 138            | 强化层     |

| [0034] | 139                            | 电路布局    | 15             | 探针头     |

| [0035] | 151                            | 探针      | 20             | 增厚层体    |

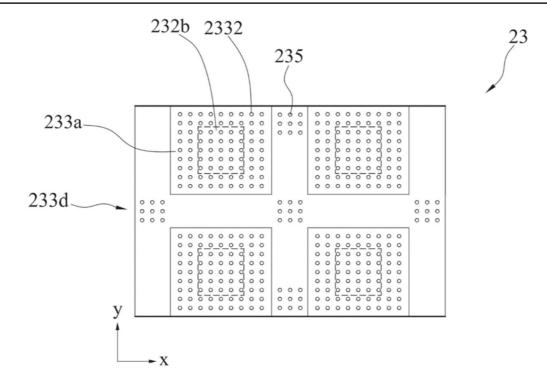

| [0036] | 23                             | 空间转换器   | 232b           | 第一下接触区  |

| [0037] | 233                            | 第二多层体   | 233a           | 第二上接触区  |

| [8800] | 233d                           | 空接触区    | 2332           | 上接触点    |

| [0039] | 235                            | 空接触点    | 90             | 晶圆      |

| [0040] | 91                             | <b></b> | D              | 间距      |

| [0041] | W                              | 宽度      |                |         |

#### 具体实施方式

[0042] 下面结合附图对本发明的结构原理和工作原理作具体的描述:

[0043] 请参照图1与图2,分别为本发明的一实施例的示意图(一)与示意图(二),其绘示出一探针卡10,包含电路板11、电性连接于电路板11的空间转换器13、以及电性连接于空间转换器13的探针头15。为方便说明空间转换器13的结构,上述探针卡10的各元件并未按实际比例绘制。实际上电路板11的厚度大于空间转换器13的厚度。

[0044] 探针卡10适用于对晶圆90上的多个晶粒91进行针测。晶圆90经切割而得到个别的晶粒91之后,各个晶粒91可以进一步与相匹配的集成电路载板(图未示)共同封装成集成电

路芯片。用来和晶粒91相结合的集成电路载板本身具有一电路布局,用以将集成电路载板的上表面的各个接触点电性连接于下表面的各个接触点。当晶粒91焊接于集成电路载板的上表面时,通过集成电路载板的空间转换,晶粒91便能够以具有较宽裕空间分布的集成电路载板的下表面的接触点来与外界的电路板作电性连接。

[0045] 空间转换器13包含增厚层体20与第一多层体132。本实施例的增厚层体20包含核心层体131以及第二多层体133,但在另一实施例中,增厚层体20本身可以只包含核心层体131而没有第二多层体133。核心层体131为一具有硬度的基材,核心层体131的硬度大于第一多层体132。核心层体131包含多个中间连接区块1311,各个中间连接区块1311包含有多个通过机械钻孔方式所形成的多个电连接通道1311a。

[0046] 第一多层体132包含彼此间隔排列的多个空间转换区块1321,各个空间转换区块1321包含彼此相对的第一上接触区132a与第一下接触区132b。各第一上接触区132a分别电性连接于核心层体131的各中间连接区块1311,彼此相对的第一上接触区132a与第一下接触区132b之间具有一电路布局139,且各空间转换区块1321的电路布局139相同于集成电路载板的电路布局。但在另一实施例中,各空间转换区块1321的电路布局139至少70%以上等同于集成电路载板的电路布局。之所以会有差异(小于30%)是因为在此实施例中,空间转换区块1321的电路布局139可以增加例如具有回授(Loopback)测试功能的电路、电容等。

[0047] 增厚层体20的第二多层体133设置于核心层体131的上表面。第二多层体133包含彼此间隔排列的多个延伸电连接区块1331,各延伸电连接区块1331包含彼此相对的第二上接触区133a与第二下接触区133b,各第二下接触区133b分别电性连接于各中间连接区块1311。在本实施例中,第二多层体133的上表面即相当于增厚层体20的上表面。

[0048] 以上是本发明的一实施例的空间转换器13的具体结构,若进一步将电路板11电性连接于第二多层体133的各延伸电连接区块1331的第二上接触区133a,以及将探针头15电性连接于第一多层体132的各空间转换区块1321的第一下接触区132b,即构成可对晶圆90的多个晶粒91进行针测的探针卡10。

[0049] 请进一步参照图3与图4,分别为本发明的一实施例的空间转换器13的仰视图与俯视图。如图3所示,空间转换器13的相邻二第一下接触区132b沿一轴向(例如x轴方向)具有一间距D,各个第一下接触区132b沿X轴向具有一宽度W,且待测晶圆上各个待测装置(DUT,Device Under Test)之间的切割道宽度为C(图未示),其中D=n×W+(n+1)C,且n为正整数。当n=1的时候,间距D为一个DUT的宽度(相当于第一下接触区132b沿X轴向的宽度)W加上DUT沿X轴向二侧的两个切割道的宽度C;当n=2的时候,间距D为二个DUT的宽度加上DUT沿X轴向二侧的三个切割道的宽度C,依此类推。图3所绘示的即为n=2的实施例。之所以限定相邻二第一下接触区132b之间的间距D=n×W+(n+1)C,是为了因应当待测晶圆上的待测晶粒(或待测装置)的排列甚密时,由于探针排列密度有其先天限制,因此必须采取跳DUT(Device Under Test)的测试方式。亦即位于同一轴向上的连续相邻两待侧晶粒(甚至是连续相邻的三个以上的晶粒)在同一测试步骤中,只有一个会被测试探针卡所测试。进一步来说,探针排列密度有其先天限制是指空间转换器13有其先天限制,第一下接触区132b的下接触点1322经由空间转换之后对应第二上接触区133a的上接触点1332,上接触点1332才能与电路板11电性连接,因此每一个第一下接触区132b需要配合一个对应的第二上接触区133a,空间转换器13在对应一个待测晶粒的范围时,应该以一个空间转换区块1321作为考

量,所以空间转换器13在下表面必须采取跳DUT的空间布局方式。

[0050] 承上,倘若单就空间转换器13本身进行观察,可通过第一下接触区132b的尺寸来得知DUT沿特定轴向的宽度W。但若是不知悉空间转换器13所对应的待侧晶圆的DUT图案,仍无法得知DUT沿特定轴向二侧的切割道的宽度C,也就是仅能观察到D= $n\times W$ ,n>1,但所属技术领域中具有通常知识者仍可了解当知悉空间转换器13所对应的待侧晶圆的DUT沿特定轴向二侧的切割道的宽度C时,D将会满足D= $n\times W$ +(n+1)C,且n为正整数。

[0051] 上述是本发明的一实施例的空间转换器13的具体结构,若进一步将一电路板11电性连接于空间转换器13的增厚层体20的上表面,以及将一探针头15电性连接于空间转换器13的下表面,即可构成可用来对晶圆90的多个晶粒91进行针测的探针卡10。如图1与图2所示,电路板11朝向空间转换器13的表面设置有多个相对于第二上接触区133a的上接触点1332的电接触点112,以及相对于第二上接触区133a的空接触点135的空接触点115。相对应的上接触点1332与电接触点112之间可以通过锡球电性连接在一起。同样地,探针头15上的多根探针151也可以通过锡球个别地电性连接于相对应的第一多层体132的下接触点1322。

[0052] 在此需特别强调的是,本实施例的空间转换器13的第一多层体132与第二多层体133是以ML0工艺所制成,且第一多层体132的电路布局139与待测试的晶粒91所适用的集成电路载板的电路布局相同。藉此可以让整体测试条件可以更贴近晶粒91被封装成集成电路芯片时的状态,所得到的测试结果也更加贴近真实,而增加测试结果的可信度。

[0053] 请参照图5,为本发明另一实施例的示意图。在本发明的另一实施例中,第一多层体132与第二多层体133的层数相同,均包含四个基层,其中第一多层体132包含四个基层132L1~132L4,第二多层体133包含四个基层133L1~133L4。倘若第一多层体132与第二多层体133的层数不同,则空间转换器13容易发生板翘的情况,导致上表面的上接触点1332或者是下表面的下接触点1322不共平面,进而造成探针卡10良率不佳或者寿命减少。此外,空间转换器13的第二多层体133面向核心层体131的表面还可以设置有一强化层138,其可增加空间转换器13整体的强度。当强化层138本身使用铜或者其他导电材料制成时,在电路上还以可作为整体的接地平面(ground plane)或者电源平面(power plane)之用。除此之外,强化层138也可以改设置在背向核心层体131的表面,或者是同时设置在面向核心层体131的表面以及背向核心层体131的表面,甚至也可以设置在第二多层体133的任意二个基层之间。核心层体131是以玻璃纤维作为骨干并填充胶体制成,因此厚度会较第一多层体132的四个基层132L1~132L4其中的一厚。

[0054] 在本实施例中,空间转换器13的第二多层体133的上接触点1332定义出一上接触点空间分布,空间转换器13的第一多层体132的下接触点1322则定义出一下接触点空间分布,其中下接触点空间分布会比上接触点空间分布来得更密。所谓「更密」的意思是指每单位面积的接触点的数量较多,或者是相邻二接触点之间的距离较近,即空间转换器13的上接触点空间分布在空间转换器13的内部电路进行空间转换成下接触点空间分布。在本实施例中,空间转换器13的第二多层体133的电连接通道1331a与核心层体131的电连接通道1311a均为垂直穿孔,表示在第二多层体133及核心层体131并没有前述空间转换的状况,空间转换的布局方式只有在第一多层体132发生。

[0055] 请参照图4,本实施例的探针卡10的第二上接触区133a周围或者是相邻两个第二上接触区133a之间是为一空间间隔区133c。空间间隔区133c中可以进一步设置空接触点

135。本实施例的空接触点135并没有电性连接于探针卡10的测试电子回路中,设置空接触点135的其中一个目的是当电路板11与空间转换器13通过锡球进行回焊(reflow)工艺连接在一起时,位于空接触点135上的锡球可作为支撑结构,也就是用来增加空间转换器13与电路板11之间的连接界面的支撑强度。此外,也可以使各锡球平均分配应力,避免在上接触点1332的区域内单独过度承受应力而造成锡球破裂的情况发生。在一实施例中,空间间隔区133c除了设置空接触点135之外,也可以视需求规划出至少一电子元件放置区以设置IC芯片。此外,IC芯片与第二多层体133之间的电接触点也可以包含一个以上的空接触点135。

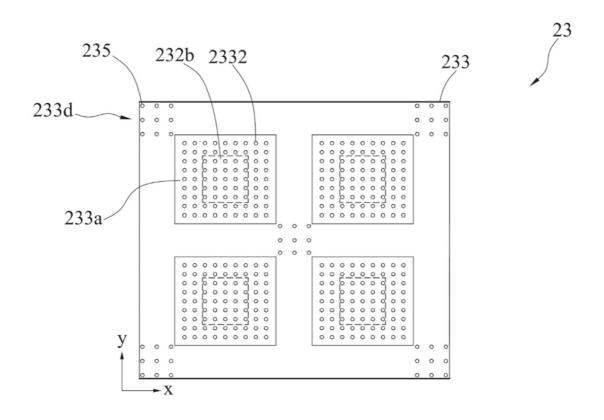

[0056] 请参照图6,其绘示出一例示空间转换器23的空接触区233d于第二多层体233的上表面上的分布。第二多层体233包含四个第二上接触区233a,分别对应于四个第一下接触区232b。在此实施例中,第二多层体233的上表面包含多个(图中为五个)空接触区233d,每个空接触区233d包含多个空接触点235。如图6所示,空接触区233d分别位在四个角落以及第二多层体233的上表面的重心。

[0057] 请参照图7,第二多层体233的空接触区233d也可以个别设置在第二多层体233的上表面的重心、以及以重心为基准沿X轴向与Y轴向延伸而与第二多层体233的上表面边缘交会的四个区块,这些空接触区233d的连线构成相互正交的二条直线。此外,在本实施例中,空接触区233d的空接触点235的间距和第二上接触区233a的上接触点2332的间距相同。[0058] 请参照图8,第二多层体233的空接触区233d除了可以设置在四个角落以及第二多层体233的上表面的重心之外,还可以同时设置在以第二多层体233的上表面的重心为基准沿X轴向与Y轴向延伸到第二多层体233的上表面的边缘的四个区域。

[0059] 在一实施例中,核心层体131与第二多层体133二者的厚度总和可以大于0.3mm,以达到特定的结构强度。在一实施例中,第一多层体132的空间转换区块1321的数量为偶数。

本发明的另一实施例是为上述空间转换器13的制造方法,所述空间转换器13的制 造方法包含以下所述的步骤,但不限于必须依照以下步骤的先后顺序来制造,兹说明如下。 首先先取得所欲测试的芯片所使用的集成电路载板的电路布局。然后提供如图1 所示的包含有多个中间连接区块1311的核心层体131,其中中间连接区块1311包含有多个 利用机械钻孔方式所形成的多个电连接通道1311a。请参照图5,利用多层有机工艺技术 (Multi-layer Organic, MLO) 于核心层体131的二表面分别形成第一多层体132的子层 132L1以及第二多层体133的子层133L1。然后利用激光在第一多层体132的子层132L1上预 备作为空间转换区块1321的位置形成多个穿孔,以及在第二多层体133的子层133L1上预备 作为延伸电连接区块1331的位置形成多个穿孔。然后,继续以ML0工艺形成子层132L2以及 子层133L2;同样地,也必须利用激光在子层132L2上预备作为空间转换区块1321的位置形 成穿孔,以及在子层133L2上预备作为延伸电连接区块1331的位置形成多个穿孔。依此类推 直到第一多层体132的层数满足需求 (例如具有四个子层132L1~132L4) 以及第二多层体 133的层数满足需求(例如具有四个子层133L1~133L4)为止。其中,第一多层体132的子层 132L1~132L4上的穿孔会相互连通,只要在穿孔内形成导电材质(例如铜或银)便可形成导 电线路,而每个空间转换区块1321的所有导电线路便构成电路布局139。同理,每个延伸电 连接区块1331也会具有多个导电线路,且每个导电线路分别连通于中间连接区块1311的各 个电连接通道1311a。

[0062] 承上,所制造出的第一多层体132包含彼此间隔排列的多个空间转换区块1321,各

空间转换区块1321包含彼此相对的第一上接触区132a与第一下接触区132b,且各个第一上接触区132a分别电性连接于核心层体131的各中间连接区块1311。彼此相对的第一上接触区132a与第一下接触区132b之间具有电路布局139。如图3所示,相邻二个第一下接触区132b沿一轴向(例如x轴)具有一间距D,各第一下接触区132b沿同一轴向具有一宽度W,其中D=n×W,且n必须是大于或等于2的正整数。此外,各空间转换区块1321的电路布局139必须实质相同或者至少有70%以上等同于待测芯片所搭配使用的集成电路载板的电路布局。这边指的电路布局相同,是指客户提供集成电路载板的电路布局,根据空间转换器13与集成电路载板使用材料的差异,可以对阻抗线路匹配进行微调,例如线宽、线距等。

[0063] 本发明的另一实施例是为探针卡10的制造方法,所述探针卡10的制造方法除了包含上述空间转换器13的制造方法所包含的步骤之外,还进一步包含电性连接一电路板11于空间转换器13的第二多层体133的各延伸电连接区块1331的第二上接触区133a,以及电性连接一探针头15于第一多层体132的各空间转换区块1321的第一下接触区132b。

[0064] 上述各实施例包含以下共同特点: (一) 空间转换器13的相邻二个第一下接触区132b沿一轴向具有一间距D,各第一下接触区132b沿同一轴向具有一宽度W,其中D=n×W,且n为大于或等于2的正整数;以及(二) 各空间转换区块1321的电路布局139必须相同于待测试的晶粒91所搭配使用的集成电路载板的电路布局。(三) 实验显示单纯只使用第一多层体132作为空间转换器,一旦与电路板11以BGA工艺结合会有平整度不佳的情况发生。通过将第一多层体132与增厚层体20相结合,整体强度大幅上升,与电路板11以回焊工艺结合后也不会发生平整度不佳的情况。

[0065] 当然,本发明还可有其它多种实施例,在不背离本发明精神及其实质的情况下,熟悉本领域的技术人员当可根据本发明作出各种相应的改变和变形,但这些相应的改变和变形形都应属于本发明所附的权利要求的保护范围。

图1

图3

图4

图5

图6

图7