## (19)中华人民共和国国家知识产权局

# (12)发明专利申请

(10)申请公布号 CN 110138350 A (43)申请公布日 2019. 08. 16

(21)申请号 201910359157.6

(22)申请日 2019.04.30

(71)申请人 杭州中科微电子有限公司 地址 310053 浙江省杭州市高新(滨江)区 江南大道3850号创新大厦1001室

(72)发明人 罗彦彬 钱敏 金玉花 甘业兵

(74)专利代理机构 上海旭诚知识产权代理有限 公司 31220

代理人 郑立

(51) Int.CI.

HO3F 3/213(2006.01)

*H03F 3/24*(2006.01)

HO3F 3/195(2006.01)

*H03F* 1/02(2006.01)

HO3F 1/26(2006.01)

权利要求书1页 说明书4页 附图3页

#### (54)发明名称

一种带谐波抑制电路的功率放大器

#### (57)摘要

本发明公开了一种带谐波抑制电路的功率 放大器,涉及无线通信与射频集成电路领域,包 括输入匹配网络、键合线、偏置电路、输入晶体 管、cascode晶体管,串联谐振网络,并联谐振网 络和负载匹配网络。其中,输入匹配网络的一端 与输入晶体管的栅极相连接,另一端与输入信号 相连接;键合线的一端与输入晶体管的源级相连 接,另一端与芯片参考地相连接。本发明利用串 联谐振网络和并联谐振网络滤除信号的二次、三 次等高次谐波信号,再通过负载匹配网络驱动负 载天线并将射频信号发射出去,其电路结构简单 且集成度高,能提高功率放大器的线性度、效率 和发射功率等性能。

- 1.一种带谐波抑制电路的功率放大器,其特征在于,包括输入匹配网络、键合线、偏置电路、输入晶体管、cascode晶体管、串联谐振网络、并联谐振网络和负载匹配网络,其中,输入匹配网络的一端与输入晶体管的栅极相连接,另一端与射频输入相连接;键合线的一端与输入晶体管的源级相连接,另一端与芯片参考地相连接。

- 2.如权利要求1所述的带谐波抑制电路的功率放大器,其特征在于,所述输入晶体管的源级通过所述键合线连接到参考地电位,所述输入匹配网络与所述键合线共同实现功率放大器的输入阻抗匹配。

- 3.如权利要求2所述的带谐波抑制电路的功率放大器,其特征在于,所述键合线的打线根数与打线长度都可以调节,用以满足所述芯片对阻抗匹配和稳定性的要求。

- 4.如权利要求1所述的带谐波抑制电路的功率放大器,其特征在于,所述偏置电路分别与所述输入晶体管和所述cascode晶体管的栅极相连接,并为所述输入晶体管和所述cascode晶体管提供偏置电压。

- 5.如权利要求4所述的带谐波抑制电路的功率放大器,其特征在于,所述输入晶体管与 所述cascode晶体管均采用的是深N肼的射频CMOS晶体管。

- 6.如权利要求1所述的带谐波抑制电路的功率放大器,其特征在于,所述串联谐振网络一端与所述cascode晶体管的漏端相连接,另一端连接参考地电位,用于将谐波信号短路到地。

- 7.如权利要求1所述的带谐波抑制电路的功率放大器,其特征在于,所述串联谐振网络由两组电容电感串联组成,通过滤除二次及三次谐波信号来提高线性度。

- 8. 如权利要求1所述的带谐波抑制电路的功率放大器,其特征在于,所述并联谐振网络一端与所述cascode晶体管的漏端相连接,另一端与所述负载匹配网络相连接,用于滤除谐波信号。

- 9.如权利要求1所述的带谐波抑制电路的功率放大器,其特征在于,所述负载匹配网络一端与所述并联谐振网络连接,另一端与50 Ω负载天线相连接,用于将天线负载匹配到所述功率放大器输出最大功率的最佳负载。

- 10.如权利要求9所述的带谐波抑制电路的功率放大器,其特征在于,所述负载匹配网络由隔直电容和并联到地的电感组成。

# 一种带谐波抑制电路的功率放大器

#### 技术领域

[0001] 本发明涉及无线通信与射频集成电路领域,尤其涉及一种带谐波抑制电路的功率放大器。

### 背景技术

[0002] 射频功率放大器是无线发射机中的核心电路模块之一,要求输出大功率给外部负载。功率放大器通常是无线发射机中功耗最大的模块,为了降低功耗,延长电池寿命,要求它具有较高的效率。此外,随着通信技术的发展,信道容量急剧增加,各个不同的无线系统之间的干扰增加,对发射信号的谐波有一定的要求,不能干扰其它系统的工作,同时功率放大器在输出最大功率时要防止发生幅度失真,对功率放大器的线性度和谐波抑制提出了很高的要求。

[0003] 目前在功率放大器的设计中提出了很多优化线性度的方法,功率放大器一般都会有非线性失真。当输入信号增大时输出信号也会增大,由于非线性会产生一系列谐波信号,这些谐波成分功率可能会非常大的影响到基波信号的发射性能,因此抑制谐波信号成为提高功率放大器线性度的重要措施。目前应用比较广泛的是使用微带传输线,在负载匹配网络的输入端之前引入短路传输线或者开路传输线进行高次谐波的抑制,应用中会使用各种 \\n\长度的传输线,准确的传输线模型比较依赖于工艺制作加工,而且一般传输线的面积比较大,使得利用此方法进行谐波抑制的功率放大器面积比较大,不利于集成度的降低,性能也不稳定,导致功率放大器的批量生产受到限制。

[0004] 因此,本领域的技术人员致力于开发一种能够抑制谐波信号,同时又利于集成且性能稳定的功率放大器。

#### 发明内容

[0005] 有鉴于现有技术的上述缺陷,本发明所要解决的技术问题是如何防止功率放大器 在输出最大功率时产生幅度失真,同时又有利于功率放大器的集成,且性能稳定易于批量 生产。

[0006] 为实现上述目的,本发明提供了一种带谐波抑制电路的功率放大器,其特征在于,包括输入匹配网络、键合线、偏置电路、输入晶体管、cascode晶体管、串联谐振网络、并联谐振网络和负载匹配网络,其中,输入匹配网络的一端与输入晶体管的栅极相连接,另一端与射频输入相连接;键合线的一端与输入晶体管的源级相连接,另一端与芯片参考地相连接。[0007] 进一步地,所述输入晶体管的源级通过所述键合线连接到参考地电位,所述输入

[0007] 进一步地,所述输入晶体管的源级通过所述键合线连接到参考地电位,所述输入 匹配网络与所述键合线共同实现功率放大器的输入阻抗匹配。

[0008] 进一步地,所述键合线的打线根数与打线长度都可以调节,用以满足所述芯片对阻抗匹配和稳定性的要求。

[0009] 进一步地,所述偏置电路分别与所述输入晶体管和所述cascode晶体管的栅极相连接,并为所述输入晶体管和所述cascode晶体管提供偏置电压。

[0010] 进一步地,所述输入晶体管与所述cascode晶体管均采用的是深N肼的射频CMOS晶体管。

[0011] 进一步地,所述串联谐振网络一端与所述cascode晶体管的漏端相连接,另一端连接参考地电位,用于将谐波信号短路到地。

[0012] 进一步地,所述串联谐振网络由两组电容电感串联组成,通过滤除二次及三次谐波信号来提高线性度。

[0013] 进一步地,所述并联谐振网络一端与所述cascode晶体管的漏端相连接,另一端与所述负载匹配网络相连接,用于滤除谐波信号。

[0014] 进一步地,所述负载匹配网络一端与所述并联谐振网络连接,另一端与50 Ω 负载 天线相连接,用于将天线负载匹配到所述功率放大器输出最大功率的最佳负载。

[0015] 进一步地,所述负载匹配网络由隔直电容和并联到地的电感组成。

[0016] 本发明的有益技术效果为:

[0017] 1、本发明集成了芯片内输入与负载匹配,将应用中的芯片外元器件个数降到最少,提高了集成度,降低了使用成本。

[0018] 2、本发明的谐波抑制网络使用了串联谐振网络和并联谐振网络,并通过控制芯片到封装的键合线长度来调节谐振频率,可以有效地抑制二次、三次以及其它高次谐波,大大提高功率放大器的线性度,输出功率等性能。

[0019] 3、本发明降低了电路的复杂度,建模简单,易于调整电路参数达到电路的设计要求。

#### 附图说明

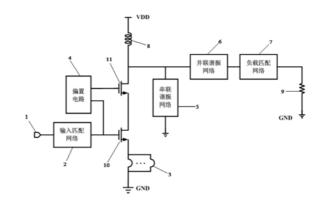

[0020] 图1是本发明的一个较佳实施例的电路结构框图;

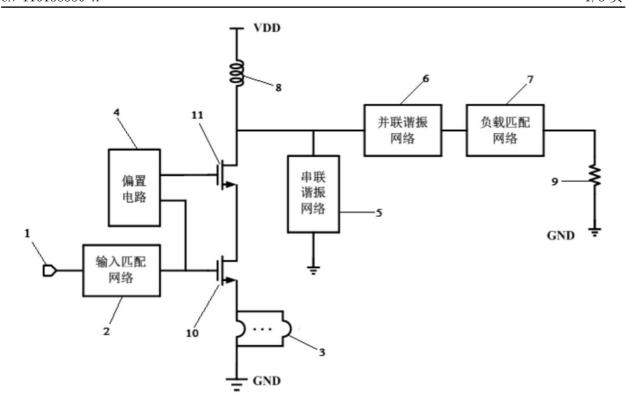

[0021] 图2是本发明的一个较佳实施例的电路原理图:

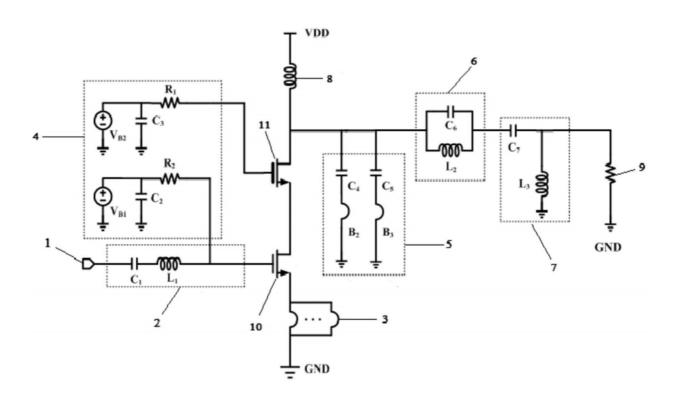

[0022] 图3是本发明的一个较佳实施例的串联谐振网络的阻抗仿真图:

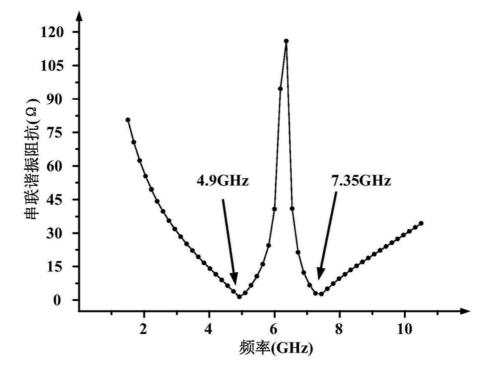

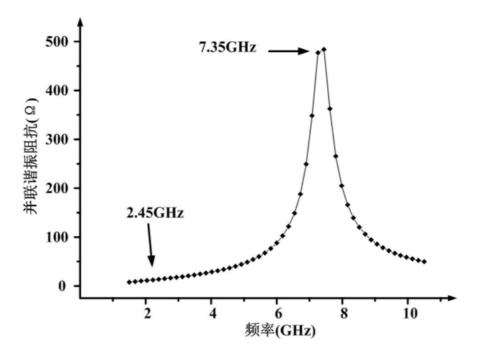

[0023] 图4是本发明的一个较佳实施例的并联谐振网络的阻抗仿真图;

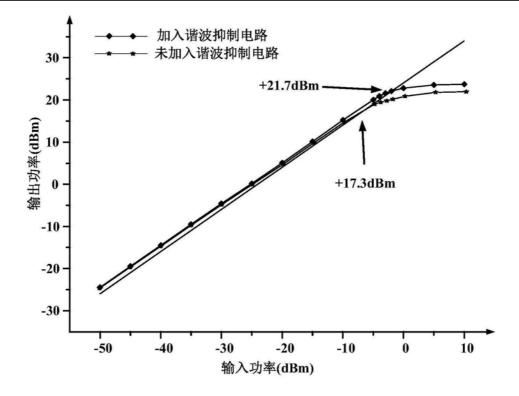

[0024] 图5是本发明的一个较佳实施例的功率放大器的输出功率随输入功率的仿真变化曲线图。

[0025] 其中:1-射频输入端,2-输入匹配网络,3-键合线(Bonding wire),4-偏置电路,5-串联谐振网络,6-并联谐振网络,7-负载匹配网络,8-Choke电感,9-负载天线,10-输入晶体管,11-cascode晶体管。

#### 具体实施方式

[0026] 以下参考说明书附图介绍本发明的优选实施例,使其技术内容更加清楚和便于理解。本发明可以通过许多不同形式的实施例来得以体现,本发明的保护范围并非仅限于文中提到的实施例。在附图中,结构相同的部件以相同数字标号表示,各处结构或功能相似的组件以相似数字标号表示。

[0027] 如图1所示,一种带谐波抑制电路的功率放大器,主要包括射频输入端1、输入匹配网络2、键合线3、偏置电路4、串联谐振网络5、并联谐振网络6、负载匹配网络7、Choke电感8、负载天线9、输入晶体管10和cascode晶体管11。输入匹配网络2的一端连接射频输入端1,而

另一端连接输入晶体管10的栅极,输入晶体管10的源级通过键合线3连接到参考地电位,输入匹配网络2与键合线3共同实现功率放大器的输入阻抗匹配,并保证功率放大器的稳定性。偏置电路4分别与输入晶体管10和cascode晶体管11的栅极相连接,为输入晶体管10和cascode晶体管11提供偏置电压。串联谐振网络5一端与cascode晶体管11的漏端相连接,另一端连接参考地电位,将谐波信号短路到地。并联谐振网络6一端与cascode晶体管11的漏端相连接,另一端与负载匹配网络7相连接,用于抑制谐波信号的传输。负载匹配网络7一端与并联谐振网络连接,另一端与负载天线9相连接,用于将天线的50Ω阻抗匹配到功率放大器能输出最大功率的最佳负载。

[0028] 如图2所示,输入匹配网络2由隔直电容C1和片上电感L1组成,输入晶体管10的源级与键合线3相连接,会在输入端产生一个正实部阻抗,再通过电感L1将输入端的虚部谐振在工作频率,进而使得输入阻抗得到良好地匹配。键合线3的打线根数,打线长度均会影响输入阻抗值和功率放大器的稳定性,因此本发明的实施案例中将键合线3的打线根数与打线长度设置为可调节,以满足实际芯片对阻抗匹配和稳定性的要求,即在设计电路版图时预留了一定数量的焊盘(Pad)可用于后续实际测试时决定打线的情况。

[0029] 偏置电路4为输入晶体管10和cascode晶体管11提供直流电压偏置,主要由产生偏置电压 $V_{B1}$ 和 $V_{B2}$ 的电压基准源(图中未画出,用电压源代替 $V_{B1}$ 和 $V_{B2}$ )、以及两个RC低通滤波器组成。其中图中未画出的电压基准源需要在宽电源电压下工作,并提供低温漂系数,和稳定可靠的偏置电压 $V_{B1}$ 、 $V_{B2}$ 。两个RC低通滤波器功能相同,用于隔离偏置电路4和功率放大器的放大管,避免偏置电路的噪声影响,以及功率放大器的大信号对偏置电路的影响。电阻和电容的取值一般比较大,但也需考虑大电阻热噪声对功率放大器的影响,其中, $R_1$ 和 $C_3$ 组成的RC低通滤波器用于cascode晶体管11,而 $R_2$ 和 $C_2$ 组成的RC低通滤波器用于输入晶体管10。

[0030] 输入晶体管10与cascode晶体管11提供信号放大作用,由于在射频领域对晶体管的要求比较高,一般采用的是射频性能较好的深N肼射频晶体管,同时深N肼管的噪声隔离度也非常好。本实施例中输入晶体管10采用的是线宽较小的射频管,可以达到更高的速度,有更好的射频性能,对信号的处理会有非常明显的优势;cascode晶体管11采用的是厚栅以及长线宽的射频晶体管。由于功率放大器一般处理的是大信号,在cascode晶体管11的漏端瞬时电压会达到两倍的电源电压,此时很可能会击穿射频晶体管,采用厚栅晶体管可以大大地增加它的击穿耐压值,使得功率放大器的射频晶体管更加安全可靠,同时cascode晶体管的速度对功率放大器影响不会很大。因此,此种晶体管类型的组合可以达到非常好的效果。

[0031] 串联谐振网络5有两组电容电感串联组成,用于滤除二次及三次谐波信号,提高线性度。由于电感电容串联的谐振网络在谐振频率处是低阻甚至可以认为是短路。实际应用中,芯片内部的焊盘到封装的键合线3可以等效为一个Q值比较高的电感,与电容串联后即可组成串联谐振腔。其中,C4和B2组成了二次谐波信号的抑制电路,而C5和B3组成了三次谐波信号的抑制电路。由于键合线的长度以及工艺的偏差可能会使得谐振频率产生偏差,因此键合线B2和B3的打线可以设置灵活些,跟键合线3类似,打线长度与打线根数均是可以调节的,在设计芯片版图时需要预留一定数量的焊盘,同时串联的电容可做一些调整与修调。由于二次和三次谐波信号对功率放大器的输出信号影响最大,因此在本实施例中只加入了二阶和三阶谐波抑制电路,同理,在其他更高要求的应用实例中,可以并联四阶及更高阶的

谐波抑制电路以达到抑制高次谐波信号的目的。

[0032] 并联谐振网络6由电感L2和电容C6组成一个并联谐振腔。理论上并联谐振腔在谐振频率的阻抗是非常大的,可以近似于开路,然后由于实际使用的电感Q值有限,谐振频率的阻抗也是有限的。其中电感L2为片上电感,Q值不高但电感值会比键合线要准确些,谐振频率会比较准确同时谐振频率处的带宽也会比较大,阻抗偏小,不过可以满足对谐波信号抑制的要求。由于三次谐波信号对基频信号的影响最大,甚至由于非线性三次谐波信号会阻塞基频信号的输出,因此本实例中的并联谐振网络6的谐振频率设定为三次谐波信号对应的频率,进一步抑制三次谐波信号的输出。由于谐振腔的Q值较低,该抑制电路对二次谐波信号也是有一定的抑制作用。同理,在更高要求的发射机中,可以通过级联更多的并联谐振网络,并将对应的谐振频率设定为高次谐波信号对应的频率即可抑制更多高次谐波信号对基频信号的影响。

[0033] 负载匹配网络7由隔直电容 $C_7$ 和并联到地的电感 $L_3$ 组成。大电容 $C_7$ 主要是用于隔离直流信号的作用,因为cascode晶体管11的漏端电压基本上为电源电压,后级有自己的直流偏置电压,考虑后级电路的连接需要将两个直流偏置相隔离。而本实例中的功率放大器中的最佳匹配负载为容性负载,根据SMITH圆图的分析可知,只要一个电感即可将天线的50  $\Omega$ 负载匹配到最佳负载的位置,由于对电感的感值要求比较高,对Q值要求却不那么高,因此本实施例仍然采用片上电感 $L_3$ 来实现负载匹配网络。同理,不同的实施例的最佳负载可能会存在差异,匹配网络也会有所不同,但并不会改变本发明提出的功率放大器的结构。

[0034] 如图3所示,当本实施例中对应的工作频率为2.45GHz时,串联谐振网络的阻抗仿真图中可以明显看到两个凹点,对应的阻抗几乎为零,可以近似认为短路到地了,而对应的频率分别为4.9GHz和7.35GHz,即工作频率的二倍与三倍频率的地方。这么小的阻抗可以将对应频率的谐波信号短路到地,从而减小谐波信号对输出基频信号的影响,同时在2.45GHz的位置上阻抗还是比较大的,该谐波抑制电路对基频信号的损失比较小。

[0035] 如图4所示,本实例中对应的工作频率为2.45GHz,并联谐振网络6的谐振频率应该设置在三倍频率处,即7.35GHz。如图,在7.35GHz的位置出现了谐振点,对应的阻抗非常大,这么大的阻抗使得三次谐波信号无法传输到输出端从而被很好的抑制掉了。同时基频信号的的位置阻抗基本为零,因此该并联谐振网络可以很好的抑制高次谐波而不会影响基频信号的传输。

[0036] 图5为加入谐波抑制/不加入谐波抑制电路时,功率放大器的输出功率随输入功率的仿真变化曲线图。衡量功率放大器线性度性能最常用的指标是1dB压缩点,因此图5对应的就是功率放大器的1dB压缩点仿真曲线图。如图所示,加入谐波抑制电路时本实例功率放大器的输出1dB压缩点可以达到+21.7dBm,而不加入谐波抑制电路时本实例功率放大器的输出1dB压缩点仅仅为+17.3dBm,这对于许多应用而言是满足不了要求的,因此本发明提出的谐波抑制电路对本实施例的功率放大器有非常好的谐波抑制效果,明显地改善了功率放大器的线性度性能,同时还提高了功率放大器的最大输出功率和发射效率。

[0037] 以上详细描述了本发明的较佳具体实施例。应当理解,本领域的普通技术无需创造性劳动就可以根据本发明的构思作出诸多修改和变化。因此,凡本技术领域中技术人员依本发明的构思在现有技术的基础上通过逻辑分析、推理或者有限的实验可以得到的技术方案,皆应在由权利要求书所确定的保护范围内。

图1

图2

图3

图4

图5