## (19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第4252537号 (P4252537)

(45) 発行日 平成21年4月8日(2009.4.8)

(24) 登録日 平成21年1月30日(2009.1.30)

| (51) Int.Cl. |                |            | FΙ   |       |      |

|--------------|----------------|------------|------|-------|------|

| HO1L         | 21/8246        | (2006.01)  | HO1L | 27/10 | 444B |

| HO1L         | <i>2</i> 7/105 | (2006.01)  | HO1L | 27/10 | 651  |

| HO1L         | 21/8242        | (2006.01)  | HO1L | 27/10 | 681F |

| HO1L         | 27/108         | (2006.01)  | HO1L | 27/10 | 481  |

| HO1L         | 27/10          | (2006, 01) |      |       |      |

請求項の数 9 (全 18 頁)

(21) 出願番号 特願2004-562848 (P2004-562848) (86) (22) 出願日 平成14年12月25日 (2002.12.25) (86) 国際出願番号 PCT/JP2002/013485 (87) 国際公開番号 W02004/059736 (87) 国際公開日 平成16年7月15日 (2004.7.15) 審査請求日 平成17年1月27日 (2005.1.27) ||(73)特許権者 308014341

富士通マイクロエレクトロニクス株式会社 東京都新宿区西新宿二丁目7番1号

||(74)代理人 100091672

弁理士 岡本 啓三

||(72)発明者 佐次田 直也

神奈川県川崎市中原区上小田中4丁目1番 1号 富士通株式会社内

審査官 柴山 将隆

(56)参考文献 特開昭63-248137(J P, A) 特開昭61-026227(J P, A) 特開2002-289793(J P, A )

(54) 【発明の名称】半導体装置の製造方法

## (57)【特許請求の範囲】

## 【請求項1】

半導体基板の上方に第1の絶縁膜を形成する工程と、

前記第1の絶縁膜の上に下部電極と<u>強誘電体膜又は高</u>誘電体膜と上部電極とを有するキャパシタを形成する工程と、

前記キャパシタを被覆する第2の絶縁膜を形成する工程と、

前記第2の絶縁膜を形成した後、前記半導体基板の裏面に<u>キャパシタにかかる応力が小</u>さくなるように応力制御絶縁膜を形成する工程と

を有することを特徴とする半導体装置の製造方法。

## 【請求項2】

前記第2の絶縁膜及び前記応力制御絶縁膜は、ともに同じ圧縮応力、又は同じ引張応力を有することを特徴とする請求項1記載の半導体装置の製造方法。

## 【請求項3】

前記第2の絶縁膜及び前記応力制御絶縁膜は、それぞれ2層以上の多層構造を有することを特徴とする請求項1又は2に記載の半導体装置の製造方法。

#### 【請求項4】

前記第2の絶縁膜及び前記応力制御絶縁膜はシリコンを含む絶縁膜の単層又は多層構造であることを特徴とする請求項1万至3の何れか一に記載の半導体装置の製造方法。

## 【請求項5】

前記第2の絶縁膜及び前記応力制御絶縁膜を化学気相成長により成膜することを特徴と

する請求項1乃至4の何れか一に記載の半導体装置の製造方法。

## 【請求項6】

前記第2の絶縁膜及び前記応力制御絶縁膜を400 以下の成膜温度で形成することを 特徴とする請求項5記載の半導体装置の製造方法。

#### 【請求項7】

前記第2の絶縁膜及び前記応力制御絶縁膜を同じ化学気相成長法及び成膜条件で成膜することを特徴とする請求項5又は6に記載の半導体装置の製造方法。

## 【請求項8】

前記第1の絶縁膜を形成する工程の前に、前記半導体基板の上にトランジスタを形成する工程を有することを特徴とする<u>請求項1乃至7</u>の何れかーに記載の半導体装置の製造方法。

10

#### 【請求項9】

前記下部電極上に複数のキャパシタが形成されており、前記下部電極は前記複数のキャパシタについて共通となっていることを特徴とする<u>請求項8</u>記載の半導体装置の製造方法

【発明の詳細な説明】

#### 【技術分野】

### [0001]

本発明は、半導体装置の製造方法に関し、より詳しくは、キャパシタを有する半導体装置の製造方法に関する。

20

### 【背景技術】

#### [0002]

電源を切っても情報を記憶することができる不揮発性メモリとして、フラッシュメモリや強誘電体メモリ(FeRAM)が知られている。

## [0003]

フラッシュメモリは、絶縁ゲート型電界効果トランジスタ(IGFET)のゲート絶縁膜中に埋め込んだフローティングゲートを有し、記憶情報となる電荷をフローティングゲートに蓄積することによって情報を記憶する。情報の書込、消去にはゲート絶縁膜を通過するトンネル電流を流す必要があり、比較的高い電圧を必要とする。

[0004]

30

40

50

FeRAMは、強誘電体のヒステリシス特性を利用して情報を記憶する強誘電体キャパシタを有している。強誘電体キャパシタにおいて上部電極と下部電極の間に形成される強誘電体膜は、上部電極及び下部電極の間に印加する電圧に応じて分極を生じ、印加電圧の極性を反転すれば、自発分極の極性も反転する。この自発分極の極性、大きさを検出すれば情報を読み出すことができる。

#### [00005]

FeRAMは、フラッシュメモリに比べて低電圧で動作し、省電力で高速の書き込みができるという利点がある。

## [0006]

FeRAMのメモリセルは、例えば文献1(特開2001-60669号公報)に記載されているように、シリコン基板に形成されたMOSトランジスタと、シリコン基板及びMOSトランジスタ上に形成された第1の層間絶縁膜と、第1の層間絶縁膜上に形成された強誘電体キャパシタと、強誘電体キャパシタ及び第1の層間絶縁膜上に形成された第2の層間絶縁膜と、第1及び第2の層間絶縁膜に形成されたホール内に埋め込まれてMOSトランジスタに接続される導電性プラグと、導電性プラグと強誘電体キャパシタの上部電極を接続する第1の配線パターンと、第1の配線パターン及び第2の層間絶縁膜の上に形成された第3の層間絶縁膜と、第3の層間絶縁膜上に形成された第2の配線パターンとを有している。

## [0007]

ところで、第1の配線パターンをアルミニウムから形成する場合には、第1の配線パタ

ーンの引張応力によって強誘電体キャパシタの残留分極特性が劣化する。これを改善するため、強誘電体キャパシタを構成する強誘電体膜のキュリー点を超える温度でアルミニウム膜を加熱して引張応力を緩和した後に、アルミニウム膜をパターニングして配線パターンを形成することが、文献 2 (特開 2 0 0 1 - 3 6 0 2 5 号公報)に記載されている。

## [0008]

また、強誘電体キャパシタに対して引張応力となるように層間絶縁膜を形成することが 文献3(特開平11-330390号公報)に記載されている。

## [0009]

さらに、キャパシタを形成する前に基板表面に形成したSiN膜の組成及び膜厚と同じ組成及び膜厚を有するSiN膜を基板の裏面に形成することにより、基板の反りを抑える方法が文献4(特開平6-188249号公報)に記載されている。

#### [0010]

文献1によれば、強誘電体キャパシタを覆う層間絶縁膜は、圧縮 (compressive) 応力が強く、自らが膨張しようとする方向の力が働く。従って、強誘電体キャパシタの上に層間絶縁膜を複数重ねて形成する場合、成膜毎に、強誘電体キャパシタには収縮力が加わることになり、強誘電体キャパシタを劣化させる。

#### [0011]

また、文献 2 によれば、第 1 の配線パターン同士の隙間には依然として層間絶縁膜が存在するので、第 1 の配線パターンの応力の如何に関わらず、層間絶縁膜の圧縮応力が強誘電体キャパシタを劣化させるという問題は残っている。

### [0012]

また、文献 3 によれば、引張応力を有する層間絶縁膜は水分量が多く、水分により強誘電体キャパシタを劣化させてしまうという別の問題が生じてしまう。

#### [0013]

さらに、文献4の方法では、ウエハ内でキャパシタにかかる応力のばらつきが大きく、 均一な応力調整が難しいことが本願発明者の調査で分かった。

## 【発明の開示】

## [0014]

本発明の目的は、層間絶縁膜に覆われるキャパシタの特性を良好に、かつ均一に維持し、或いは向上させることができる半導体装置の製造方法を提供することにある。

### [0015]

上記した課題は、半導体基板の上方に第1の絶縁膜を形成する工程と、前記第1の絶縁膜の上に下部電極と<u>強誘電体膜又は高</u>誘電体膜と上部電極とを有するキャパシタを形成する工程と、前記キャパシタを被覆する第2の絶縁膜を形成する工程と、前記第2の絶縁膜を形成した後、前記半導体基板の裏面に<u>キャパシタにかかる応力が小さくなるように</u>応力制御絶縁膜を形成する工程とを有することを特徴とする半導体装置の製造方法によって解決される。

## [0016]

本発明によれば、キャパシタを被覆する第2の絶縁膜を形成した後に、基板の裏面に応力制御絶縁膜を成膜している。例えば、第2の絶縁膜と同じ圧縮応力、又は同じ引張応力を有するように応力制御絶縁膜を形成する。これにより、第2の絶縁膜によって生じる応力が緩和されるとともに、均一な応力調整が可能となり、その結果キャパシタの特性を良好に、かつ均一に維持でき、或いはその向上を図ることができる。本願発明者の実験によれば、本願発明を、強誘電体のキャパシタ絶縁膜を備えたFeRAMの製造方法に適用したとき、スイッチングチャージの特性及びそのばらつきの向上を図ることができた。

## [0017]

さらに、ウエハ全体として応力を低減することができるので、プレーナ構造のFeRAMに顕著に生じていた所謂端劣化を防止することができる。端劣化とは、複数のキャパシタに共通する下部電極上の端部のキャパシタの誘電体膜の側部に応力が集中することによってキャパシタ特性が劣化しやすくなるという現象をいう。これは、TEOSを原料とし

10

20

30

40

て形成される絶縁膜をキャパシタ上に形成した場合に起こることがある。

## [0018]

また、本願発明では、特に、第2の絶縁膜と応力制御絶縁膜とに同じ圧縮応力を付与することができるが、この場合、水分含有量の少ない、良質な絶縁膜でキャパシタを被覆することができるため、好ましい。

#### [0019]

また、半導体基板の裏面に形成した応力制御絶縁膜は、不要であれば除去することができる。この場合、第2の絶縁膜を貫通するホールを通してキャパシタの上部電極と接続する配線を第2の絶縁膜上に形成する工程よりも後に、応力制御絶縁膜を除去するとよい。これは、エッチングによりキャパシタの上部電極の上方の第2の絶縁膜に形成したホールを通して、キャパシタの誘電体膜の膜質を改善するために、高温でアニールする工程が行われるが、このアニールが終了した後ではそれ以上の高温の熱処理工程はなく、かつ第2の絶縁膜上に配線を形成した後では、応力制御絶縁膜を除去しても一旦調整した応力の変化が少ないからである。

【発明を実施するための最良の形態】

#### [0020]

以下に、本発明の実施形態を図面に基づいて説明する。

#### [0021]

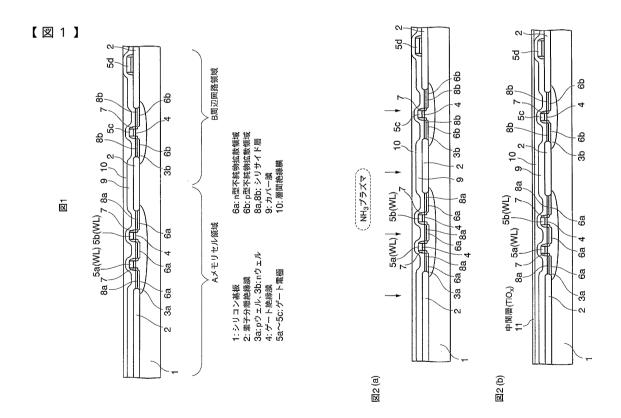

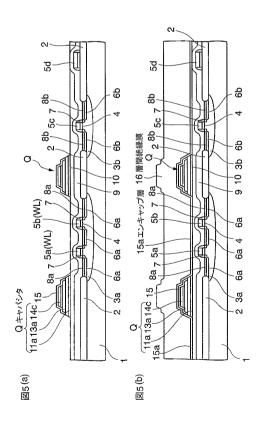

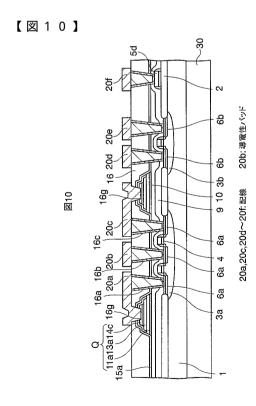

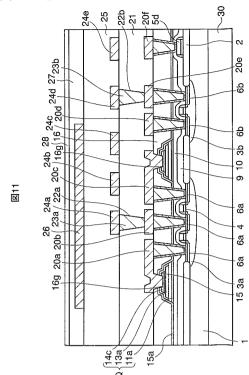

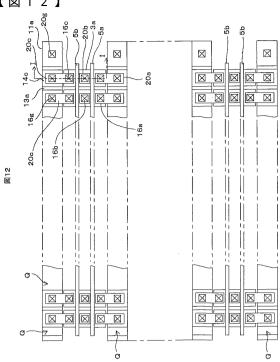

図1~図11は、本発明の実施形態に係るプレーナ構造のFeRAMの製造工程を示す 断面図である。

[0022]

図1に示す構造を形成するまでの工程について説明する。

#### [0023]

まず、図1に示すように、n型又はp型のシリコン(半導体)基板1表面に素子分離絶縁膜2をLOCOS(Local Oxidation of Silicon)法により形成する。素子分離絶縁膜2としては、LOCOS法により形成される構造の他に、STI(Shallow Trench Isolation)構造を採用してもよい。

#### [0024]

そのような素子分離絶縁膜2を形成した後に、シリコン基板1のメモリセル領域Aと周辺回路領域Bにおける所定の活性領域(トランジスタ形成領域)にp型不純物、n型不純物を選択的に導入して、pウェル3a及びnウェル3bを形成する。なお、周辺回路領域BではCMOSを形成するためにnウェル3bのみならず、pウェル(不図示)も形成される。

[0025]

その後、シリコン基板1の活性領域表面を熱酸化して、ゲート絶縁膜4となるシリコン酸化膜を形成する。

[0026]

次に、シリコン基板 1 の上側全面に非晶質又は多結晶のシリコン膜を形成し、次いで、不純物のイオン注入によりシリコン膜を低抵抗化する。その後に、シリコン膜をフォトリソグラフィ法により所定の形状にパターンニングして、ゲート電極 5 a , 5 b , 5 c 及び配線 5 d を形成する。

[0027]

メモリセル領域 A では、1つの p ウェル3 a 上には2つのゲート電極5 a ,5 b がほぼ平行に間隔をおいて配置され、図の紙面に垂直な方向に延びている。それらのゲート電極5 a ,5 b はワード線WLの一部を形成している。

## [0028]

次に、メモリセル領域 A において、ゲート電極 5 a , 5 b の両側の p ウェル 3 a 内に n 型不純物をイオン注入して、 n チャンネル M O S トランジスタのソース / ドレインとなる 3 つの n 型不純物拡散領域 6 a を形成する。これと同時に、周辺回路領域 B の p ウェル (不図示)にも n 型不純物拡散領域を形成する。

10

20

30

40

## [0029]

続いて、周辺回路領域Bにおいて、nウェル3bのうちゲート電極5cの両側にp型不 純物をイオン注入して、pチャネルMOSトランジスタのソース / ドレインとなるp型不 純物拡散領域6bを形成する。

## [0030]

続いて、シリコン基板 1 の全面に絶縁膜を形成した後、その絶縁膜をエッチバックしてゲート電極 5 a ~ 5 c の両側部分にのみ側壁絶縁膜 7 として残す。その絶縁膜として、たとえば C V D (Chemical Vapor Deposition)法により酸化シリコン (SiO<sub>2</sub>)を形成する。

## [0031]

さらに、ゲート電極 5 a ~ 5 c と側壁絶縁膜 7 をマスクに使用して、 p ウェル 3 a 内に再び n 型不純物イオンを注入することにより、 n 型不純物拡散領域 6 a を L D D 構造にし、更に n ウェル 3 b 内に再び p 型不純物イオンを注入することにより p 型不純物拡散領域 6 b も L D D 構造とする。

## [0032]

なお、 n 型不純物と p 型不純物の打ち分けは、レジストパターンを使用して行われる。

#### [0033]

以上のように、メモリセル領域Aでは、pウェル3aとゲート電極5a,5bとその両側のn型不純物拡散領域6a等によってn型MOSFETが構成され、また、周辺回路領域Bでは、nウェル3bとゲート電極5cとその両側のp型不純物拡散領域6b等によってp型MOSFETが構成される。

### [0034]

次に、全面に高融点金属膜、例えば、Ti、Coの膜を形成した後に、この高融点金属膜を加熱してn型不純物拡散領域6a、p型不純物拡散領域6bの表面にそれぞれ高融点金属シリサイド層8a,8bを形成する。その後、ウェットエッチにより未反応の高融点金属膜を除去する。

## [0035]

次に、プラズマ C V D 法により、シリコン基板 1 の全面にカバー膜 9 として酸窒化シリコン (SiON) 膜を約 2 0 0 n mの厚さに形成する。さらに、T E O S ガスを用いるプラズマ C V D 法により、第 1 の層間絶縁膜 1 0 として二酸化シリコン (SiO<sub>2</sub>)をカバー膜 9 上に約 1 . 0  $\mu$  mの厚さに成長する。なお、T E O S ガスを用いるプラズマ C V D 法により形成される絶縁膜を、以下に、P E - T E O S 膜ともいう。

## [0036]

続いて、第1の層間絶縁膜10上面を化学的機械研磨(СМР; Chemical Mechanical Polishing)法により研磨して平坦化する。

## [0037]

次に、図 2 (a) に示す構造を形成するまでの工程を説明する。

## [0038]

まず、アンモニア( $NH_3$ )ガスのプラズマにより、平坦化された第1の層間絶縁膜10表面を改質する。なお、 $NH_3$ ガスのプラズマにより絶縁膜の表面を改質する処理を、以下  $ICNH_3$ プラズマ処理ともいう。

## [0039]

この工程における $NH_3$ プラズマ処理の条件として、例えば、チャンバ内に導入される $NH_3$ のガス流量を 350 sccm、チャンバ内の圧力を 1 Torr、基板温度を 400 、基板に供給される 13.56 MHzの高周波電源のパワーを 100 W、プラズマ発生領域に供給される 350 kHzの高周波電源のパワーを 55 W、電極・第 10 の層間絶縁膜間の距離を 350 mil s、プラズマ照射時間を 60 秒に設定する。

## [0040]

その後に、図2(b) に示すように、第1の層間絶縁膜10の上に自己配向性を有する物質からなる中間層(自己配向層)11を形成する。中間層11は例えば次のような工程により形成される。

10

20

30

40

## [0041]

まず、DCスパッタ法によって厚さ 2 0 n m のチタン(Ti) 膜を第 1 の層間絶縁膜 1 0 上に形成し、続いて、RTA (rapid thermal annealing) によりTi 膜を酸化して酸化チタン(TiO $_x$ ) 膜を形成し、このTiO $_x$ 膜を中間層 1 1 とする。

## [0042]

Ti 膜の酸化条件として、例えば、基板温度を 700 、酸化時間を 60 秒間、酸化雰囲気中の酸素  $(0_2)$  とアルゴン (Ar) をそれぞれ 1%、 99% に設定する。なお、Ti 膜は酸化されずにそのままの状態で中間層 11 として使用されてもよい。

#### [0043]

この中間層11は、この後に形成される第1の導電膜の配向強度を高める要素と、さらに第1の導電膜の上に成膜されるPZT系強誘電体膜中のPbが下層へ拡散するのをブロックする働きがある。また、中間層11は、次に形成される第1の導電膜12と第1の層間絶縁膜10との密着性を向上する働きもある。

## [0044]

中間層11を構成する自己配向性を有する物質としては、Tiの他に、アルミニウム(AI)、シリコン(Si)、銅(Cu)、タンタル(Ta)、窒化タンタル(TaN)、イリジウム(Ir)、酸化イリジウム(IrO<sub>x</sub>)、プラチナ(Pt)などがある。以下の実施形態においても、中間層はこれらのいずれかの材料から選択される。

#### [0045]

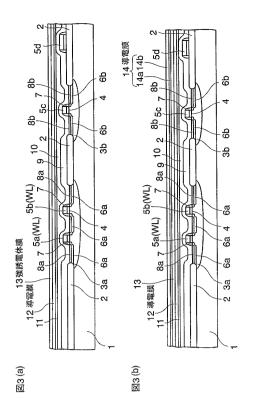

次に、図3(a)に示す構造を形成するまでの工程を説明する。

### [0046]

まず、中間層11上に、第1の導電膜12としてPt膜をスパッタ法で175nmの厚さに成膜する。Pt膜の成膜条件として、Arガス圧を0.6Pa、DCパワーを1kW、基板温度を100 に設定する。ターゲットはプラチナである。

#### [0047]

なお、第1の導電膜12として、イリジウム、ルテニウム、酸化ルテニウム、酸化ルテニウムストロンチウム( $SrRuO_3$ )等の膜を形成しても良い。本実施形態及び以下の実施形態において、第1の導電膜は自己配向性を有する物質から構成する。

## [0048]

次に、スパッタリング法により、 $\underline{PZT((Pb(Zr_{1-x}Ti_x)O_3)}$ にランタン(La)が添加された  $PLZT(lead\ lanthanum\ zirconate\ titanate; (Pb_{1-3x/2}La_x)(Zr_{1-y}Ti_y)O_3)) 膜を第1の導電膜12の上に100~300nm、例えば240nmの厚さに形成し、これを強誘電体膜13として使用する。なお、<math>PLZT膜にはカルシウム(Ca)$ とストロンチウム(Sr)を添加することもある。

## [0049]

続いて、酸素雰囲気中にシリコン基板 1 を置き、R T A によって P L Z T 膜を結晶化する。その結晶化の条件として、例えば、基板温度を 5 8 5 、処理時間を 2 0 秒間、昇温速度を 1 2 5 /secに設定し、酸素雰囲気に導入される $0_2$ とArの割合を 2 . 5 %と 9 7 . 5 %とする。

## [0050]

強誘電体膜 1 3 の形成方法としては、上記したスパッタ法の他にスピンオン法、ゾルゲル法、MOD (Metal Organic Deposition)法、MOCVD法がある。また、強誘電体膜 1 3 の材料としてはPLZTの他に、PZT、SrBi $_2$ (Ta $_x$ Nb $_{1-x}$ ) $_2$ O $_9$ (但し、0 < x 1)、Bi $_4$ Ti $_2$ O $_{12}$ などがある。なお、DRAMを形成する場合には、上記の強誘電体材料に代えて(BaSr)TiO $_3$ (BST)、チタン酸ストロンチウム(STO)等の高誘電体材料を使用すればよい。

#### [0051]

次に、図 3 (b) に示すように、強誘電体膜 1 3 上に第 2 の導電膜 1 4 を形成する。第 2 の導電膜 1 4 は、以下の 2 ステップによって形成される。

## [0052]

50

10

20

30

まず、強誘電体膜 1 3 上に、第 2 の導電膜 1 4 の下側導電層 1 4 a として酸化イリジウム ( $IrO_x$ ) 膜をスパッタリング法により 2 0 ~ 7 5 n m、例えば 5 0 n m の厚さに形成する。その後、酸素雰囲気内で R T A により強誘電体膜 1 3 の結晶化と下側導電層 1 4 a へのアニール処理とを行う。 R T A の条件として、基板温度を 7 2 5 、処理時間を 1 分間とするとともに、酸素雰囲気に導入される $O_2$ と $O_3$ と $O_4$ 0割合をそれぞれ 1 % と 9 9 % とする。

#### [0053]

続いて、第2の導電膜14の上側導電層14bとして酸化イリジウム(IrO<sub>x</sub>)膜を下側 導電層14a上にスパッタリング法により100~300nm、例えば200nmの厚さ に形成する。

[0054]

なお、第2の導電膜14の上側導電層14bとして、プラチナ膜又は酸化ルテニウムストロンチウム(SRO)膜をスパッタ法により形成してもよい。

[0055]

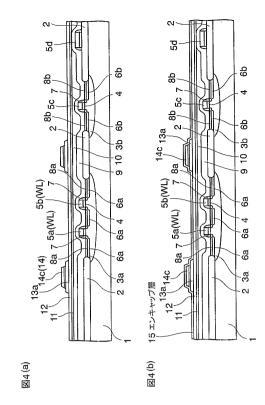

次に、図4(a)に示す構造を形成するまでの工程を説明する。

[0056]

まず、上部電極平面形状のレジストパターン(不図示)を第2の導電膜14上に形成した後に、そのレジストパターンをマスクに使用して第2の導電膜14をエッチングし、残された第2の導電膜14のパターンをキャパシタの上部電極14cとして使用する。

[0057]

そして、そのレジストパターンを除去した後に、650、60分間の条件で、強誘電体膜13を酸素雰囲気中でアニールする。このアニールは、第2の導電膜14の上側導電層14bのスパッタリング時及び第2の導電膜14のエッチング時に強誘電体膜13に入ったダメージを元に回復させるために行われる。

[0058]

続いて、メモリセル領域Aにおいてキャパシタ上部電極14c及びその周辺にレジストパターン(不図示)を形成した状態で、強誘電体13をエッチングし、これにより上部電極14cの下に残った強誘電体膜13をキャパシタの誘電体膜13aとして使用する。

[0059]

そして、レジストパターン(不図示)を除去した状態で強誘電体膜13を窒素酸素雰囲気中でアニールする。例えばこのアニールは、強誘電体膜13及びその下の膜に吸収された水分等を脱ガスするために行われる。

[0060]

次に、図 4 (b) に示すように、上部電極 1 4 c、誘電体膜 1 3 a 及び第 1 の導電膜 1 2 の上に、第 1 のエンキャップ層 1 5 としてAI  $_2$ O $_3$ 膜をスパッタリング法により 5 0 n m の厚さに常温下で形成する。この第 1 のエンキャップ層 1 5 は、還元され易い誘電体膜 1 3 a を水素から保護して、水素がその内部に入ることをブロックするために形成される。

[0061]

なお、第1のエンキャップ層15として、PZT膜、PLZT膜または酸化チタンを成膜してもよい。エンキャップ層としての $AI_2O_3$ 膜、PZT膜、PLZT膜または酸化チタン膜は、MOCVDにて成膜しても良く、またスパッタリングとMOCVDといった2つの方法により形成した積層膜にしても良い。第1のエンキャップ層15が積層膜の場合は、キャパシタの劣化を考慮して、スパッタリングで $AI_2O_3$ 膜を先に形成することが好ましい。

[0062]

その後に、酸素雰囲気中で550、60分間の条件で、第1のエンキャップ層15を熱処理してその膜質を改善する。

[0063]

次に、第1のエンキャップ層15の上にレジスト(不図示)を塗布し、これを露光、現像して上部電極14c及び誘電体膜13aの上と、その周辺に下部電極平面形状に残す。 そして、レジスト膜をマスクに使用して、第1のエンキャップ層15、第1の導電膜12 10

20

30

40

及び中間層11をエッチングし、これにより残った第1の導電膜12のパターンをキャパシタの下部電極11aとして使用する。なお、中間層11も下部電極11aを構成する。エンキャップ層15、第1の導電膜12及び中間層11のエッチングは、塩素、臭素などのハロゲン元素を用いたドライエッチングにより行われる。

## [0064]

レジストを除去した後に、上部電極 1 4 c、誘電体膜 1 3 a 等を酸素雰囲気中で 3 5 0 、 3 0 分間の条件でアニールする。これは、後工程で形成される膜のはがれ防止を目的としている。

## [0065]

これにより、図 5 (a) に示すように、第 1 の層間絶縁膜 1 0 の上には、下部電極 1 1 a (第 1 の導電膜 1 2 / 中間層 1 1)、誘電体膜 1 3 a、上部電極 1 4 c (第 2 の導電膜)からなるキャパシタ Q が形成されることになる。

#### [0066]

次に、図 5 (b) に示す構造を形成するまでの工程を説明する。

## [0067]

まず、第 2 のエンキャップ層 1 5 a としてAI  $_2$ O $_3$  膜をスパッタリング法により 2 0 n m の厚さに成膜して、キャパシタQ及び第 1 の層間絶縁膜 1 0 を覆う。第 2 のエンキャップ層 1 5 a として、第 1 のエンキャップ層 1 5 で採用される他の材料を用いてもよい。続いて、酸素雰囲気中で 6 5 0 、 6 0 分間の条件で、強誘電体膜 1 3 a をアニールしてダメージから回復させる。

### [0068]

続いて、エンキャップ層 1 5 a の上に、第 2 の層間絶縁膜 1 6 として膜厚 1 5 0 0 n m の $SiO_2$ 膜を C V D 法により成膜する。第 2 の層間絶縁膜 1 6 の成長は、成膜ガスとしてシラン( $SiH_4$ )やポリシラン化合物( $Si_2F_6$ , $Si_3F_8$ , $Si_2F_3CI$ 等)および $SiF_4$ を用いても良いし、 T E O S を用いても良い。成膜方法である C V D 法は、プラズマ励起(ECR 法: Electron cyclotron Resonance、ICP法: Inductively Coupled Plasma、HDP: High Density Plasma、EMS: Electron Magneto-Sonic)や、熱励起、レーザー光による励起方式でも良い。プラズマ C V D 法を用いた第 2 の層間絶縁膜 1 6 の成膜条件の一例を以下に示す。

## [0069]

TEOSガス流量・・・460sccm

He (TEOSのキャリアガス)流量・・・480 sccm

O<sub>2</sub>流量・・・7 0 0 sccm

圧力・・・9.0 Torr

高周波電源の周波数・・・13.56 М Н z

高周波電源のパワー・・・400W

成膜温度・・・390

次に、図 6 (a) に示すように、第 2 の層間絶縁膜 1 6 の成膜方法及び条件と同じ成膜方法及び条件で、シリコン基板 1 の裏面に膜厚 1 5 0 0 n m の SiO<sub>2</sub>膜からなる応力制御絶縁膜 3 0 を成膜する。

## [0070]

その後、図 6 (b) に示すように、第 2 の層間絶縁膜 1 6 上面を C M P 法により平坦化する。第 2 の層間絶縁膜 1 6 の表面の平坦化は、上部電極 1 4 c の上面から 4 0 0 n m の厚さとなるまで行われる。この C M P 法による平坦化の際に使用されるスラリー中の水分や、その後の洗浄時に使用される洗浄液中の水分は、第 2 の層間絶縁膜 1 6 表面に付着したりその内部に吸収される。

## [0071]

そこで、真空チャンバ(不図示)中で温度390 で第2の層間絶縁膜16を加熱することにより、その表面および内部の水分を外部に放出させる。このような脱水処理の後に、第2の層間絶縁膜16を加熱しながらN20 プラズマに曝して脱水とともに膜質を改善する。これにより、後工程での加熱と水によるキャパシタの劣化が防止される。そのような

10

20

30

40

脱水処理とプラズマ処理は同じチャンバ(不図示)内において行ってもよい。そのチャンバ内には、シリコン基板 1 を載せる支持電極とこれに対向する対向電極が配置され、対向電極には高周波電源が接続可能な状態となっている。そして、チャンバ内に $N_2$ Oガスを導入した状態で、対向電極に高周波電源を印加し、電極間に $N_2$ Oプラズマを発生させて絶縁膜の $N_2$ Oプラズマ処理を行う。その $N_2$ Oプラズマ処理によれば、絶縁膜の少なくとも表面には窒素が含まれる。そのような方法は以下の工程において採用されてもよい。脱水処理に続くプラズマ処理の際には $N_2$ Oプラズマを使用することが好ましいが、NOプラズマ、 $N_2$ プラズマ等を使用してもよく、このことについては後述する工程でも同様である。なお、脱水処理の基板温度とプラズマ処理の基板温度はほぼ同じとなる。

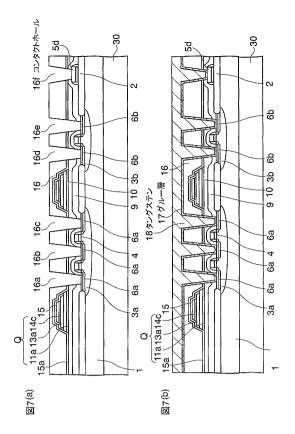

#### [0072]

次に、図 7 (a) に示すように、レジストパターン(不図示)を用いるフォトリソグラフィ法により第 1 の層間絶縁膜 1 0、第 2 のエンキャップ層 1 5 a、第 2 の層間絶縁膜 1 6及びカバー膜 9 をエッチングして、メモリセル領域 A の不純物拡散層 6 a の上にそれぞれコンタクトホール 1 6 a~ 1 6 cを形成すると同時に、周辺回路領域 B の不純物拡散層 6 b の上にコンタクトホール 1 6 d , 1 6 e を形成し、また、素子分離絶縁層 2 上の配線 5 d 上にコンタクトホール 1 6 f を形成する。

## [0073]

第 2 の層間絶縁膜 1 6 、第 2 のエンキャップ層 1 5 a 、第 1 の層間絶縁膜 1 0 、カバー膜 9 は、CF系ガス、例えばCHF $_3$ にCF $_4$ 、Arを加えた混合ガスを用いてエッチングされる。

## [0074]

次に、図 7 (b) に示すように、第 2 の層間絶縁膜 1 6 の上とコンタクトホール 1 6 a ~ 1 6 f の内面を前処理するために、R F (高周波) エッチングを行った後、それらの上にスパッタリング法によりチタン (Ti) 膜を 2 0 n m、窒化チタン (TiN) 膜を 5 0 n m連続で成膜し、これらの膜をグルー層 1 7 とする。さらに、六フッ化タングステンガス (WF 6)、アルゴン、水素の混合ガスを使用する 1 7 とする。ならに、六フッ化タングステンガス (W) 膜 1 8 を形成する。なお、タングステン膜 1 8 の成長初期にはシラン (SiH<sub>4</sub>) ガスも使用する。タングステン膜 1 8 は、各コンタクトホール 1 6 a ~ 1 6 f を完全に埋め込む厚さ、例えばグルー層 1 7 の最上面上で 1 0 n m程度とする。

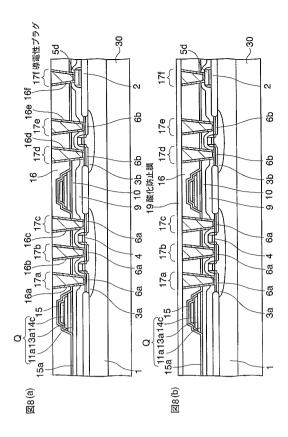

## [0075]

続いて、図 8 (a) に示すように、第 2 の層間絶縁膜 1 6 上面上のタングステン膜 1 8 とグルー層 1 7 を C M P 法により除去し、各コンタクトホール 1 6 a ~ 1 6 f 内にのみ残す。これにより、コンタクトホール 1 6 a ~ 1 6 f 内のそれぞれのタングステン膜 1 8 とグルー層 1 7 を導電性プラグ 1 7 a ~ 1 7 f として使用する。

## [0076]

その後に、コンタクトホール 1 6 a ~ 1 6 f 形成後の洗浄処理、 C M P 後の洗浄処理等の工程で第 2 の層間絶縁膜 1 6 表面に付着したり、その内部に浸透したりした水分を除去するために、再び、真空チャンバ中で 3 9 0 の温度で第 2 の層間絶縁膜 1 6 を加熱して水を外部に放出させる。このような脱水処理の後に、第 2 の層間絶縁膜 1 6 を加熱しながら $N_2$ 0プラズマに曝して、膜質を改善するアニールを、例えば 2 分間行う。

## [0077]

次に、図 8 (b) に示すように、第 2 の層間絶縁膜 1 6 上と導電性プラグ 1 7 a ~ 1 7 f 上にタングステンの酸化防止膜 1 9 としてプラズマ C V D 法によりSiON膜を約 1 0 0 n m の厚さに成膜する。

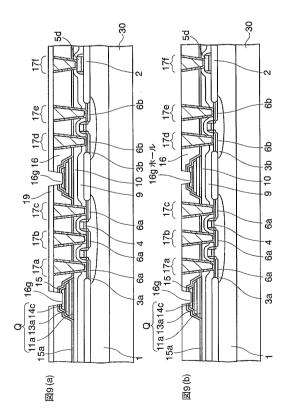

## [0078]

次に、図9(a) に示すように、レジストパターン(不図示)をマスクに使用して上部電極 1 4 c 上の第 2 の層間絶縁膜 1 6 及びエンキャップ層 1 5 , 1 5 a をエッチングしてホール 1 6 g を形成する。同時に、ワード線W L の延在方向で上部電極 1 4 c からはみ出している下部電極 1 1 a 上にもホールを形成する。なお、図9(a)では下部電極 1 1 a 上のホールを図示していないが、図12中、符号 2 0 g で示す。

## [0079]

10

20

30

10

20

30

40

50

そのエッチングは、CF系ガス、例えばCHF $_3$ にCF $_4$ とArを加えた混合ガスを用いてエッチングされる。その後、レジストパターンは除去される。

## [0800]

その後に、図 9 (a) に示した状態で、酸素雰囲気中、 5 5 0 、 6 0 分間のアニールを行い、ホール 1 6 g を通して誘電体膜 1 3 a の膜質を改善する。この場合、酸化され易いタングステンからなる導電性プラグ 1 7 a ~ 1 7 f は、酸化防止膜 1 9 で覆われているため、酸化されない。

## [0081]

次に、図9(b) に示すように、第2の層間絶縁膜16上と導電性プラグ17a~17f 上にあった酸化防止膜19をエッチバック法によりエッチングし、導電性プラグ17a~ 17fを露出させる。その場合、導電性プラグ17a~17fの上端は、第2の層間絶縁膜16から上に露出する。

#### [0082]

続いて、導電性プラグ 1 7 a ~ 1 7 f 及び上部電極 1 4 c が露出した状態で、 R F エッチング法によりそれらの表面を約 1 0 n m エッチング (SiO $_2$ 換算) して清浄面を露出させる。

## [0083]

その後に、第2の層間絶縁膜16、導電性プラグ17a~17f上に、アルミニウムを含む4層構造の導電膜をスパッタ法により形成する。その導電膜は、下から順に、膜厚150nmの窒化チタン膜、膜厚550nmの銅含有(0.5%)アルミニウム膜、膜厚5nmのチタン膜、膜厚150nmの窒化チタン膜である。

#### [0084]

### [0085]

メモリセル領域 A において、第 1 の配線 2 0 a は、 p ウェル 3 a の一側方にある上部電極 1 4 c にホール 1 6 g を通して接続され、かつ上部電極 1 4 c に最も近い p ウェル 3 a 上の導電性プラグ 1 7 a に接続される。第 2 の配線 2 0 c は、 p ウェル 3 a の他側方にある上部電極 1 4 a にホール 1 6 g を通して接続され、かつ上部電極 1 4 c に最も近い p ウェル 3 a 上の導電性プラグ 1 7 c に接続される。導電性パッド 2 0 b は、 p ウェル 3 a の中央の上に形成された導電性パッド 1 7 b の上に島状に形成される。第 3 ~ 第 5 の配線 2 0 d ~ 2 0 f は、周辺回路領域 B における導電性プラグ 1 7 d ~ 1 7 f に接続される。

## [0086]

この工程により形成された配線20a、20cと、導電性パッド20bと、キャパシタ及びトランジスタの平面的な配置関係を示すと、図12のようになる。図10は、図12のI・I線に沿う断面図に相当する。図12に示すように、連続して帯状に延びた下部電極11a上に誘電体膜13aも連続して帯状に延び、上部電極14cは一つの誘電体膜13a上に間隔を置いて複数形成されている。他の符号で示すものは、図1乃至図10中の同じ符号で示すものと同じである。

#### [0087]

次に、図11に示す構造を形成するまでの工程を説明する。

## [0088]

まず、第1~第5の配線20a,20c,20d~<u>20f</u>と導電性パッド20bの上に 第3の層間絶縁膜21を形成した後に、第3の層間絶縁膜21の上面をCMPにより平坦 化する。

## [0089]

ついで、マスク (不図示)を使用して第3の層間絶縁膜21 にビアホール22 a,22 bを形成する。ビアホール22 a,22 bは、メモリセル領域Aのpウェル3 aの上の導 電性パッド20bの上や、周辺回路領域Bの配線20eの上、その他の位置に形成される

#### [0090]

さらに、ビアホール 2 2 a , 2 2 b 内に、TiN層とW層からなるビア 2 3 a 、 2 3 b を 形成する。それらのビア 2 3 a , 2 3 b は、ビアホール 2 2 a , 2 2 b 内と第 3 の層間絶 縁膜 2 1 上にTiN層とW層をスパッタ<u>法とC V D 法</u>により形成した後に、第 3 の層間絶縁 膜 2 1 上からTiN層とW層を C M P により除去し、これによりビアホール 2 2 a , 2 2 b 内にビア 2 3 a , 2 3 b を残すことによって形成される。

#### [0091]

続いて、第3の層間絶縁膜21上に二層目の配線24a~24eを形成した後に、第3の層間絶縁膜21及び二層目の配線24a~24eの上に第4の層間絶縁膜25を形成する。さらに、第4の層間絶縁膜25を平坦化した後に、第4の層間絶縁膜25上に、アルミニウムよりなる導電パターン26を形成する。その後に、第4の層間絶縁膜25及び導電パターン26の上に、酸化シリコンよりなる第1のカバー絶縁膜27と窒化シリコンよりなる第2のカバー絶縁膜28を順に形成する。

#### [0092]

その後、表面に樹脂等により保護膜(不図示)を形成する。なお、基板の厚さを調整する必要がある場合、保護膜を形成した後、バックグラインダ処理により基板裏面を削る。 以上によりFeRAMの基本的な構造が形成される。

## [0093]

なお、応力制御絶縁膜30はそのまま残してチップ化してもよいし、図10の配線20 a 等や導電性パッド20bを形成する工程の後であって、バックグラインダ処理により基板裏面を削る工程の前までのどの工程でも、バックグラインダ処理などにより除去することができる。応力制御絶縁膜30を除去した場合でも、キャパシタの誘電体膜の膜質改善のためのアニールが終了した後は以降の工程でそれ以上の高温で熱処理する工程はなく、かつ配線20a等を形成した後であれば、以降の工程であまり大きな応力がかかる工程はないため、基板に対して小さい応力を維持できるからである。

#### [0094]

上記した実施形態により形成されたキャパシタQは、その特性が従来よりも改善された

## [0095]

そこで、上記した実施形態により形成されたキャパシタQの特性を調査した結果について、以下に詳細に説明する。なお、以下に述べる層間絶縁膜及び応力制御絶縁膜は原則的に酸化シリコン膜である。場合により、他の種類の絶縁膜、例えば窒化シリコン膜、酸窒化シリコン膜、アルミナ膜などを用いてもよい。

## [0096]

まず、上記した工程によって表面(S) 裏面(R)という順序で第2の層間絶縁膜16及び応力制御絶縁膜30を形成した本実施形態に係るFeRAMを用意する。さらに、比較試料として、表面(S)のみに層間絶縁膜を形成したFeRAMと、表面(S) 裏面(R)表面(S)という順序で薄い層間絶縁膜、厚い応力制御絶縁膜、及び厚い層間絶縁膜を形成したFeRAMと、裏面(R)表面(S)という順序で応力制御絶縁膜及び層間絶縁膜を形成したFeRAMと、裏面(R)表面(S)という順序で応力制御絶縁膜及び層間絶縁膜を形成したFeRAMとを用意する。

## [0097]

比較試料の層間絶縁膜及び応力制御絶縁膜の成膜方法及び成膜条件は、上記した本実施形態の第2の層間絶縁膜16及び応力制御絶縁膜30の成膜方法及び成膜条件と同じとする。但し、表面(S) 裏面(R) 表面(S)の試料では、表面に薄い層間絶縁膜と厚い層間絶縁膜を2層成膜しているが、2層の層間絶縁膜の膜厚を他の試料の一層の層間絶縁膜の膜厚と同じとした。

## [0098]

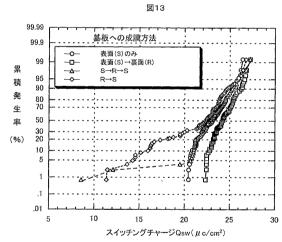

図13は、上記各FeRAMについてキャパシタQのスイッチングチャージ(Qsw)分

10

20

30

40

布を調査した結果を示すグラフである。図13の縦軸は累積発生率(%)を示し、横軸は 線型目盛りで表したスイッチングチャージ(Qsw)(μC/cm²)を示す。

#### [0099]

図中、 印は、表面(S)のみに層間絶縁膜を形成したFeRAMに係る特性を示し、 印は、上記した工程によって表面(S) 裏面(R)という順序で層間絶縁膜及び応力制御絶 縁膜を形成した本実施形態のFeRAMに係る特性を示し、 印は、表面(S) 裏面(R) 表面(S)という順序で層間絶縁膜、応力制御絶縁膜、及び層間絶縁膜を形成したFeR AMに係る特性を示し、 印は、裏面(R) 表面(S)という順序で応力制御絶縁膜及び層間絶縁膜を形成したFeRAMに係る特性を示す。

#### [0100]

図13によれば、表面(S) 裏面(R)という順序で成膜した本実施形態のFeRAM(印)の場合、表面のみに成膜したFeRAM( 印)の場合と比べて、1  $\mu$  C / c  $m^2$  以上スイッチングチャージ(Qsw)特性が向上するとともに、ばらつきも13%から9.97%に改善した。

## [0101]

また、裏面(R) 表面(S)という順序で成膜したFeRAM( 印)の場合、スイッチングチャージ(Qsw)の分布が低い方に広がり、ばらつきが36%と悪化した。

#### [0102]

以上のように、本実施形態の半導体装置の製造方法によれば、キャパシタを被覆する第2の層間絶縁膜16を形成した後に、シリコン基板1の裏面に応力制御絶縁膜30を成膜しているので、第2の層間絶縁膜16の応力を緩和することができるとともに、均一な応力の調整を行うことができる。その結果、スイッチングチャージをはじめとするキャパシタの特性を良好に、かつ均一に維持でき、或いはその向上を図ることができる。

#### [0103]

さらに、ウエハ全体として応力を低減することができるので、プレーナ構造のFeRAMに顕著に生じていた所謂端劣化を防止することができた。端劣化とは、複数のキャパシタに共通する下部電極11a上の端部のキャパシタの誘電体膜13aの側部に応力が集中することによってキャパシタ特性が劣化しやすくなる現象をいう。これは、TEOSを原料として形成される絶縁膜をキャパシタ上に形成した場合に起こることがある。

## [0104]

また、第2の層間絶縁膜16の応力と同じタイプの応力を応力制御絶縁膜30に付与すればよいため、膜中の水分含有量により相互に逆の応力となるように膜応力を調整する必要がなく、第2の層間絶縁膜16及び応力制御絶縁膜30としてともに、水分含有量の少ない、例えば圧縮応力を有する良質な絶縁膜を用いることができる。

## [0105]

以上、実施の形態によりこの発明を詳細に説明したが、この発明の範囲は上記実施の形態に具体的に示した例に限られるものではなく、この発明の要旨を逸脱しない範囲の上記 実施の形態の変更はこの発明の範囲に含まれる。

## [0106]

例えば、上記の実施形態では、キャパシタQの上部からキャパシタQの下部電極11aと下部電極11a下のトランジスタとの接続をとることを特徴とするプレーナ構造のFeRAMに関して説明したが、キャパシタの下部電極11a直下から導電性プラグを介して直接下部電極11a下のトランジスタとの接続をとることを特徴とするスタック構造のFeRAMにも適用可能である。

#### [0107]

また、第2の層間絶縁膜16及び応力制御絶縁膜30の成膜方法及び成膜条件は、積層構造や使用材料、その他を考慮して適宜選択できる。

### [0108]

また、上記の実施形態では、キャパシタ直上の第2の層間絶縁膜16の応力の影響が最も大きいので、主としてキャパシタ直上の第2の層間絶縁膜16に対して、その応力を相

10

20

30

40

殺するにように、応力制御絶縁膜30の成膜方法及び成膜条件を第2の層間絶縁膜16の成膜方法及び成膜条件と同じにしている。しかし、実際には、配線層20a等や導電性パッド20b、第3及び第4の層間絶縁膜21、25の応力の影響があるので、応力制御絶縁膜30の成膜方法及び成膜条件は、第2の層間絶縁膜16の成膜方法及び成膜条件と同じにする必要はなく、最終的にキャパシタにかかる応力が小さくなるように適宜選択することができる。

#### [0109]

また、第2の層間絶縁膜16及び応力制御絶縁膜30をそれぞれ $SiO_2$ 膜単層で構成しているが、それぞれ $SiO_2$ 膜の代わりに、シリコン窒化膜、アルミナ膜等の単層で構成することも可能である。

10

20

30

40

50

## [0110]

また、第2の層間絶縁膜16及び応力制御絶縁膜30をそれぞれ単層で構成しているが、それぞれ同じ種類の絶縁膜又は異なる種類の絶縁膜からなる2層以上の多層構造で構成することも可能である。

## [0111]

また、第2の層間絶縁膜16及び応力制御絶縁膜30を成膜温度390 条件の化学的気相成長方法で形成しているが、400 以下であって、成膜可能な成膜温度条件の化学的気相成長方法で形成することが可能である。

## [0112]

以上述べたように本発明によれば、キャパシタを被覆する第2の絶縁膜を形成した後に、基板の裏面に応力制御絶縁膜を成膜している。これにより、第2の絶縁膜によって生じる応力が緩和されるとともに、均一な応力調整が可能となり、その結果キャパシタの特性を良好に、かつ均一に維持でき、或いはその向上を図ることができる。

[0113]

さらに、ウエハ全体として応力を低減することができるので、プレーナ構造のFeRA Mに顕著に生じていた所謂端劣化を防止することができる。

#### [0114]

以上、本発明の特徴をまとめると以下の通り列挙される。

付記1.半導体基板の上方に第1の絶縁膜を形成する工程と、

前記第1の絶縁膜上に下部電極と誘電体膜と上部電極とを有するキャパシタを形成する 工程と、

前記キャパシタを被覆する第2の絶縁膜を形成する工程と、

前記第2の絶縁膜を形成した後、前記半導体基板の裏面に応力制御絶縁膜を形成する工程と

を有することを特徴とする半導体装置の製造方法。

付記 2 . 前記第 2 の絶縁膜及び前記応力制御絶縁膜は、ともに同じ圧縮応力、又は同じ引張応力を有することを特徴とする付記 1 記載の半導体装置の製造方法。

付記3.前記第2の絶縁膜及び応力制御絶縁膜は、それぞれ2層以上の多層構造を有する ことを特徴とする付記1又は2記載の半導体装置の製造方法。

付記4.前記第2の絶縁膜及び応力制御絶縁膜はシリコンを含む絶縁膜の単層又は多層構造であることを特徴とする付記1乃至3の何れか一に記載の半導体装置の製造方法。

付記 5 . 前記第 2 の絶縁膜及び応力制御絶縁膜を化学気相成長法により成膜することを特徴とする付記 1 乃至 4 の何れか一に記載の半導体装置の製造方法。

付記 6 . 前記第 2 の絶縁膜及び応力制御絶縁膜を 4 0 0 以下の成膜温度で形成することを特徴とする付記 5 記載の半導体装置の製造方法。

付記 7 . 前記第 2 の絶縁膜及び応力制御絶縁膜を同じ化学気相成長法及び成膜条件で成膜 することを特徴とする付記 5 又は 6 に記載の半導体装置の製造方法。

付記8.前記キャパシタの誘電体膜の材料は強誘電体であることを特徴とする付記1万至7の何れかーに記載の半導体装置の製造方法。

付記9.前記第1の絶縁膜を形成する工程の前に、前記半導体基板の上にトランジスタを

<u>形成する工程を有することを特徴とする付記1乃至8の何れか一に記載の半導体装置の製</u>造方法。

付記 1 0 . 前記下部電極上に複数のキャパシタが形成されており、前記下部電極は前記複数のキャパシタについて共通となっていることを特徴とする付記 9 記載の半導体装置の製造方法。

付記 1 1 . 前記キャパシタの下部電極は前記誘電体膜及び上部電極で覆われていないコンタクト領域を有し、前記第 2 の絶縁膜を形成した後に、前記トランジスタの上方に前記第 1 及び第 2 の絶縁膜を貫通する第 1 のホールを形成する工程と、

<u>前記コンタクト領域の上方に前記第2の絶縁膜を貫通する第2のホールを形成する工程</u>と、

<u>前記キャパシタの上部電極の上方に前記第2の絶縁膜を貫通する第3のホールを形成する工程と、</u>

前記第1及び第2のホールを介して前記下部電極と前記トランジスタとを接続する配線 を前記第2の絶縁膜上に形成する工程と、

前記第3のホールを介して前記上部電極と前記トランジスタとを接続する配線を前記第2の絶縁膜上に形成する工程と

を有することを特徴とする付記9又は10記載の半導体装置の製造方法。

付記12.前記キャパシタの下部電極直下の第1の絶縁膜を貫通するホールを介して前記下部電極と前記トランジスタとが接続されており、前記第2の絶縁膜を形成した後に、前記キャパシタの上部電極の上方に前記第2の絶縁膜を貫通する第4のホールを形成する工程と、前記第4のホールを介して前記上部電極と接続する配線を前記第2の絶縁膜上に形成する工程とを有することを特徴とする付記9又は10の何れかーに記載の半導体装置の製造方法。

付記 1 3 . 前記キャパシタを形成する工程の後に、前記キャパシタをアニールする工程を 有することを特徴とする付記 1 1 又は 1 2 記載の半導体装置の製造方法。

付記 1 4 . 前記キャパシタをアニールする工程は、前記キャパシタの上部電極の上方に前記第 2 の絶縁膜を貫通する第 3 又は第 4 のホールを形成する工程の後であって、該第 3 又は第 4 のホールを通して酸素雰囲気中で行われることを特徴とする付記 1 3 記載の半導体装置の製造方法。

付記 1 5 . 前記配線を形成する工程よりも後に、前記応力制御絶縁膜を除去する工程を有することを特徴とする付記 1 1 乃至 1 4 の何れか一に記載の半導体装置の製造方法。

【図面の簡単な説明】

[0115]

- 【図1】本発明の実施形態に係る半導体装置の製造工程を示す断面図(その1)である。

- 【図2】(a)、(b) は、本発明の実施形態に係る半導体装置の製造工程を示す断面図(その2)である。

- 【図3】(a)、(b) は、本発明の実施形態に係る半導体装置の製造工程を示す断面図(その3)である。

- 【図4】(a)、(b) は、本発明の実施形態に係る半導体装置の製造工程を示す断面図(その4)である。

- 【図5】(a)、(b) は、本発明の実施形態に係る半導体装置の製造工程を示す断面図(その5)である。

- 【図6】(a)、(b) は、本発明の実施形態に係る半導体装置の製造工程を示す断面図(その6)である。

- 【図 7 】(a)、(b) は、本発明の実施形態に係る半導体装置の製造工程を示す断面図(その 7 )である。

- 【図8】(a)、(b) は、本発明の実施形態に係る半導体装置の製造工程を示す断面図(その8)である。

- 【図9】(a)、(b) は、本発明の実施形態に係る半導体装置の製造工程を示す断面図(その9)である。

10

20

30

40

【図10】本発明の実施形態に係る半導体装置の製造工程を示す断面図(その10)である。

【図11】本発明の実施形態に係る半導体装置の製造工程を示す断面図(その11)である。

【図12】本発明の実施形態に係る半導体装置の製造方法により形成されるキャパシタ及びトランジスタと配線や導電性パッドとの配置関係を示す平面図である。

【図13】本発明の実施形態に係る半導体装置の製造方法により作成されたFeRAMのキャパシタのスイッチングチャージ分布を示すグラフである。

【図11】

【図12】

【図13】