# (12) UK Patent Application (19) GB (11) 2 192 488 (13) A

(43) Application published 13 Jan 1988

(21) Application No 8716261

(22) Date of filing 10 Jul 1987

(30) Priority data

(31) 61/162128

(32) 11 Jul 1986

(33) JP

(71) Applicant Canon Kabushiki Kaisha,

(Incorporated in Japan),

30-23-chome Shimomaruko, Ohta-ku, Tokyo, Japan

(72) Inventors

Mahito Shinohara,

Takao Yonehara

(74) Agent and/or Address for Service

Beresford & Co., 2-5 Warwick Court, High Holborn,

London WC1R5DJ

(51) INT CL<sup>4</sup> H01L 27/14 // 31/10

(52) Domestic classification (Edition J)

H1K 11A3 11B4 11C1B 11C4 11D 1AA9 1BC 1CA 1EB 1FL

4C14 5B2 5B5 9B1 9B1A 9D1 9E ECX

(56) Documents cited

GBA 2044996 EPA10132076 US 4517733 US 4471371

(58) Field of search

H1K

Selected US specifications from IPC sub-class H01L

# (54) Photoelectric conversion apparatus

(57) Aphotoelectric conversion apparatus comprising a transistor (103,104,106) having a main area (106) of one conductive type semiconductor and a control area (104) of an opposite conductive type semiconductor, and a capacitor (109,104) for controlling the potential of the control area (104) in floating state in which carriers produced optically are stored in the control area by controlling the potential of the control area via the capacitor. The apparatus comprises a multilayered structure in which switching device (115) for setting the control area to a desired potential is formed on a layer (113) different from that on which the transistor and capacitor are formed to save space. This switching device may be an MOS transistor, a diode, or a bipolar transistor.

FIG. 1A

FIG. 1B

FIG. 3A 111 108 116 117 110 115 114-113 -10'9 p 102 107 104 106 n--103 -101 n -112

FIG. 3B

FIG. 10B

FIG. 11A

FIG. 12

FIG. 13

q|q

FIG. 14

GB 2 192 488 A

1

#### **SPECIFICATION**

#### Photoelectric conversion apparatus

## 5 BACKGROUND OF THE INVENTION

Field of the invention

This invention relates to a photoelectric conversion apparatus having an electric charge storage area, the electric potential of which is controlled via a capacitor.

### 10 Related background art

10

15

20

25

30

5

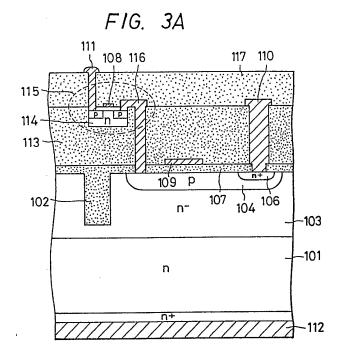

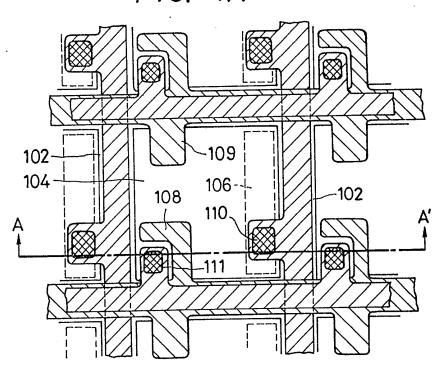

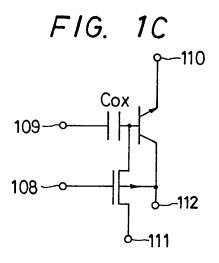

Figure 1A is a schematic plan view of one example of a photoelectric conversion apparatus disclosed in Laid-Open European Application No. 132076. Figure 1B is a cross-sectional view taken along the line A-A' of Figure 1A. Figure 1C is an equivalent circuit diagram of the apparatus.

In Figures 1A and 1B, photoelectric conversion cells are arranged on an n-silicon substrate 101 in which 15 each cell is electrically isolated from adjacent cells by a cell separation area 102 of SiO₂, Si₃N₄ or poly-silicon or the like.

Each cell has the following structure: p-areas 104 and 105 are formed by doping p-type impurities, for example, of boron into an n<sup>-</sup>-area 103 of low impurity density formed using epitaxial techniques, or the like, and an n<sup>+</sup>-area 106 is formed in p-area 104 using impurity diffusion techniques, ion implantation techniques 20 or the like.

The p-areas 104 and 105 are a source of a drain area of a p-channel MOS transistor while p-areas 104 and n<sup>+</sup>-106 are a base and an emitter, respectively, of an npn-bipolar transistor. The p-area 104 is both the source of the p-channel MOS transistor and the base of an npn-bipolar transistor.

Formed on n<sup>-</sup>-area 103, on which the respective areas are thus formed, is an oxide film 107 on which are 25 formed the gate electrode 108 of a p-channel MOS transistor and a capacitor electrode 109 having a predetermined area. Capacitor electrode 109 opposes p-area 104 with oxide film 107 formed therebetween to form a capacitor.

In addition, an emitter electrode 110 connected to n<sup>+</sup>-area 106, an electrode 111 connected to p-area 105 and a collector electrode 112 on the back of substrate 101 with an ohmic contact area disposed therebetween are 30 formed.

The basic operation of this device will now be described. Assume first that the p-area 104 which is the base of the bipolar transistor is at an initial negative potential. Light enters p-area 104 to produce electron-positive hole pairs, the positive holes of which are stored in p-area 104 to raise the potential of p-area 104 in the positive direction.

# (Storage operation)

35

35

45

Thereafter, emitter electrode 110 is rendered floating and a positive read voltage pulse is applied to capacitor electrode 109. This causes the potential of p-area 104 which is the base of the transistor to rise to thereby apply a forward bias across the base and emitter. This causes a current, corresponding to a change in 40 the base potential during storage operation, to flow through the emitter and collector. Therefore, an electric 40 signal corresponding to the quantity of incident light appears on the floating emitter electrode 110 (reading operation). At this time, the quantity of electric charges stored in the base of p-area 104 do not substantially decrease, so that the same optical information can be read repeatedly.

A refresh operation to eliminate positive holes stored in p-area 104 will now be described.

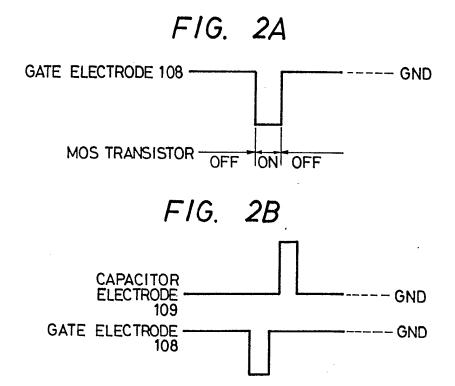

Figures 2A and 2B are diagrams of voltage waveforms illustrating the refresh operation. As shown in Figure 2A, the MOS transistor is turned on only when a negative voltage higher than the threshold value is applied to gate electrode 108.

In Figure 2B, in order to perform the refresh operation, emitter electrode 110 is grounded and electrode 111 is put at a ground potential. First, a negative voltage is applied to gate electrode 101 to turn on the p-channel 50 MOS transistor. This causes the potential of p-base area 104 to be a constant value in spite of the level of the 50 storage potential. Thereafter, a refresh positive voltage pulse is applied to capacitor electrode 109 to forwardly bias p-area 104 relative to n<sup>+</sup>-area 106 to thereby eliminate the stored positive holes through the grounded emitter electrode 110. When the refresh pulse falls, p-area 104 is returned to its initial negative potential (refresh operation). As just mentioned above, since the potential of p-base area 104 is at a fixed potential by 55 the MOS transistor, and a refresh pulse is then applied to nullify the remaining electric charges, a new storage operation can be performed without depending on the previously stored potential. Thus, the remaining charges can be nullified rapidly, thereby resulting in high speed operation. Thereafter, similarly, the respective

However, a problem with this device is that a bipolar transistor and a MOS transistor are formed in a single 60 sensor cell, so that there are many terminals formed and it is difficult to obtain a minuter structure in the conventional arrangement.

# Summary of the invention

storage, read and refresh operations will be repeated.

The main object of this invention is to provide a photoelectric conversion apparatus which eliminates the 65 above conventional problems.

65

25

30

109 to nullify the remaining charges in p-base area 104.

Another object of this invention is to provide a photoelectric conversion apparatus comprising a transistor having a main electrode area of one conductive type semiconductor and a control electrode area of an opposite conductive type semiconductor, and a capacitor for controlling the potential of the control electrode area in floating state in which carriers produced optically are stored in the control electrode area by controlling the potential of the control electrode area via the capacitor, comprising: a multilayered structure in which switching means for setting the control electrode area to a desired potential is formed on a layer different from that on which the transistor and capacitor are formed. Brief description of the drawings Figure 1A is a schematic plan view of a conventional photoelectric conversion apparatus, Figure 1B is a 10 cross-sectional view taken along the line A-A' of Figure 1A, and Figure 1C is an equivalent circuit diagram of the apparatus: Figure 2A is a voltage waveform diagram illustrating the operation of a MOS transistor, and Figure 2B is a voltage waveform diagram for illustrating the refresh operation; Figure 3A is a schematic cross-sectional view of one embodiment of a photoelectric conversion apparatus 15 according to this invention, and Figure 3B is an equivalent circuit diagram of the apparatus; Figure 4A is an equivalent circuit diagram of a second embodiment of this invention and Figure 4B is a voltage waveform diagram for illustrating the refresh operation; Figure 5A is an equivalent circuit diagram of a third embodiment of this invention and Figure 5B is a voltage 20 waveform diagram for illustrating the refresh operation; 20 Figure 6A is an equivalent circuit diagram of a fourth embodiment of this invention and Figure 6B is a voltage waveform diagram for illustrating the refresh operation; Figure 7 is a graph for illustration of the relationship between the size of nucleus rc and free energy G in the process of forming thin film; Figures 8A and 8B are illustrations of the selective deposition method; 25 Figure 9 is a graph showing the change with lapse of time of nucleation density (ND) on the deposition surface of SiO<sub>2</sub> and the deposition surface of silicon nitride; Figures 10A to 10D are illustrations of the formation steps showing a first embodiment of the method for forming crystal relating to the present invention; Figures 11A and 11B are perspective views of the substrate in Figures 10a to 10D; 30 Figure 12 is a graph showing the relationship between the flow rate of SiH<sub>4</sub> and NH<sub>3</sub> and the composition ratio of Si and N in the silicon nitride film formed; Figure 13 is a graph showing the relationship between Si/N composition ratio and nucleation density; Figure 14 is a graph showing the relationship between the injected amount of Si ions and nucleations 35 Figures 15A-15C are illustrations of the steps of forming a single crystal silicon and a transistor in the embodiments of this invention. Detailed description of preferred embodiments Embodiments of this invention will now be described in more detail with reference to the drawings. 40 Figure 3A is a schematic cross-sectional view of one embodiment of a photoelectric conversion apparatus according to this invention, and Figure 3B is an equivalent circuit diagram of the apparatus. Like parts are given the same reference numeral in Figure 1 showing the prior art and in Figure 3. In Figure 3A, an n<sup>-</sup>-epitaxial layer 103 is formed on an n-substrate 101. Formed in area 103 is a p-base area 45 104 surrounded by a device separating area 102. The p-base area 104 has an n<sup>+</sup>-emitter area 106 formed 45 therein. Formed on n<sup>-</sup>-eptaxial layer 103, on which the various areas are formed, are an insulating layer 107 on which a capacitor electrode 109 is formed opposite to p-base area 104. Formed on such bipolar transistor as a lower layer is an insulating layer 113 of SiO<sub>2</sub> or the like having a 50 recess in which an n-type single crystal silicon 114 is grown using a single crystal growth method to be 50 described in more detail later. A contact hole is formed in n<sup>+</sup>-emitter area 106 to form emitter electrode 110. Formed on the single crystal silicon layer 114, formed by single crystal growth method are a gate oxide film, a gate electrode 108 and a source and a drain area to form a MOS transistor 115. The drain area is connected by a lead 116 to the lower p-base area 104. Formed on MOS transistor 115 is a passivation film 117 with the 55 source area of MOS transistor 115 being connected to electrode 111. 55 An equivalent circuit of this embodiment having such structure is shown in Figure 3B. If an electrode connected to n-type silicon layer 114 which is the substrate of MOS transistor 115 is formed and connected to electrode 112, the circuit will become the same as the prior art one. Therefore, the respective basic storage, read and refresh operations of this embodiment are the same as the prior art example as mentioned already 60 above. Namely, in the fresh operation, when MOS transistor 115 is first turned on, the electric charges in 60 p-base area 104 are eliminated from electrode 111 grounded via lead 116 and MOS transistor 115. After the p-base area 104 is thus set to a fixed potential, a refresh positive voltage pulse is applied to capacitor electrode

If the electrode connected to n-type silicon layer 114 and electrode 111 are connected to each other, a 65 simplified structure will be obtained which permits a refresh operation similar to the above refresh operation.

10

15

20

25

30

35

40

45

50

55

60

65

This arrangement also has the advantage of allowing the excess charges stored in p-base area 104 to escape. This served to prevent the occurence of blooming when the area sensor is constructed.

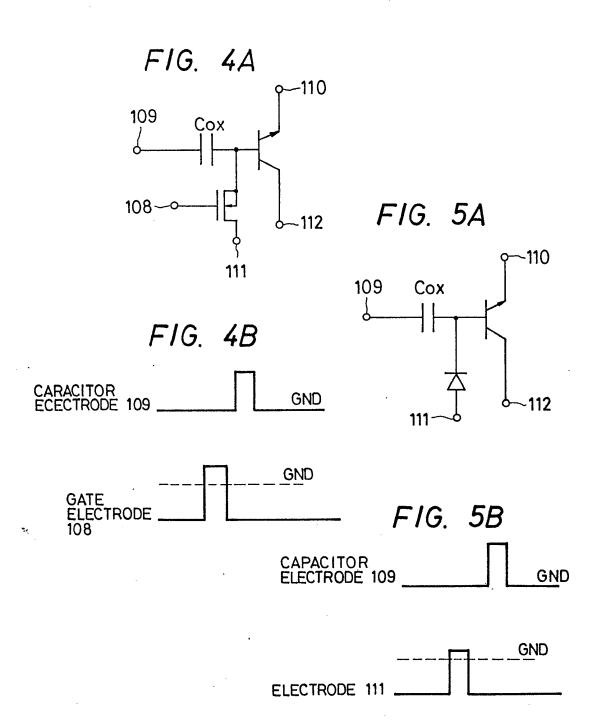

Figure 4A is an equivalent circuit diagram of a second embodiment of this invention and Figure 4B shows a a voltage waveform produced during the refresh operation.

This embodiment is obtained by replacing MOS transistor 115 in Figure 3A with an n-channel MOS transistor. Namely, the other structure is the same as that of the first embodiment.

Since the transistor is of n-channel type, it is off when the gate electrode 108 potential is negative, while it is on only when the gate potential is higher than its threshold, as shown in Figure 4B. Also, in this case, the refresh operation is performed, as described above.

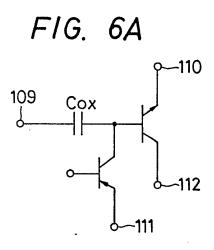

Figure 5A is an equivalent circuit diagram of a third embodiment of this invention and Figure 5B illustrates the voltage waveform produced during the refresh operation.

In this embodiment, a diode is formed instead of MOS transistor 115. Namely, in Figure 1A, a single crystal silicon is grown in a recess in insulating layer 113 to form a pn-junction. A lead 116 is connected to the n-area and electrode 111 is connected to the p-area.

According to this structure, even if the potential of p-base area 104 is raised during read operation, a negative potential is applied to electrode 111 to thereby backwardly bias the diode, so that the stored charges in p-base area 104 are maintained. On the other hand, during refresh operation, first, a voltage higher than the base level is applied to electrode 111 to forwardly bias the diode to thereby set the potential of p-base area 104 at a fixed value. Thereafter, a positive refresh voltage pulse is applied to capacitor electrode 109 to nullify the 20 remaining charges.

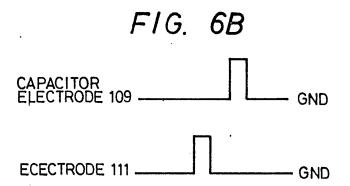

Figure 6A is an equivalent circuit diagram of a fourth embodiment of this invention and Figure 6B is a diagram of a voltage waveform produced during refresh operation.

In this embodiment, a pnp-bipolar transistor is used instead of MOS transistor 115. Namely, a pnp-bipolar transistor is formed on a single crystal silicon layer 114 using a regular process, the p-collector area is connected by a lead 116 to p-base area 104 and the p-emitter area is connected to electrode 111. The n-base area is grounded.

In this arrangement, during read operation, electrode 111 is at ground level and the pnp-bipolar transistor is not turned on although the potential of p-base area 104 is raised.

During refresh operation, a positive voltage pulse is first applied to electrode 111 to turn on the pnp-bipolar 30 transistor to thereby set p-base area 104 to a fixed potential. Thereafter, a positive refresh voltage pulse is applied to capacitor electrode 109 to nullify the charges remaining in p-base area 104.

A single crystal growth method which grows a single crystal silicon in a recess in insulating layer 113 will now be described in detail.

For better understanding of the present invention, first the general process for forming a thin film of metal 35 for semiconductor is explained.

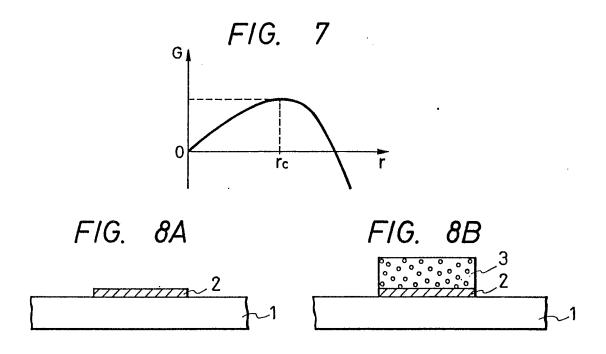

When the deposition surface is made of a material different in kind from the flying atom, particularly an amorphous material, the flying atoms are diffused freely on the substrate surface, or again evaporated (released). As the result of collision mutually between the atoms, a nucleus is formed and when its size becomes the size  $rc = 2 \sigma / gc$  at which its free energy G becomes the maximum (critical nucleus), G is reduced and the nucleus continues to grow stably three-dimensionally to become shaped in an island. The nucleus with the size exceeding rc is called stable nucleus, and unless otherwise particularly noted, "nucleus" in the following basic description of the present invention refers to this "stable nucleus". Also, among "stable nucleus", those with small r are called "initial nucleus".

The free energy generated by formation of nucleus is represented as follows:

G= $4\pi f(\theta)(\sigma o r^2 + 1/3 \cdot g v \cdot r^3)$  $f(\theta)=1/4(2-3\cos\theta+\cos^2\theta)$

wherein,

45

55

50

r=radius curvature of nucleus

θ=contact angle of nucleus

θ=contact angle of nucleus

gv=free energy per unit deposition

σo=surface energy between nucleus and vacuum.

Figure 7 shows the manner in which G is changed. In the same figure, the radius of curvature of the stable uncleus when G is at the maximum value of rc.

Thus, nuclei grow to become shaped in islands, and further grow whereby contact mutually between islands progresses until sometimes coalescence occurs and via a network structure, it becomes finally a continuous film to cover completely over the substrate surface. Following such a process, a thin film is deposited on the substrate.

In the deposition process as described above, the density of nucleus formed per unit area of the substrate surface, the size of nucleus and the nucleation speed are determined depending on the state of the system of deposition, and particularly the interaction between the flying atoms and the substrate surface material is an 65 important factor. Also, a specific crystal direction grows in parallel to the substrate due to anisotropy relative

10

25

30

40

45

ĵ

to the crystal surface of the interface energy at the interface between the deposited material and the substrate, and when the substrate is amorphous, the crytal direction within the substrate plane is not constant. For this reason, grain boundaries are formed by collision mutually between nuclei or islands, and particularly in the case of collision mutually between islands with some sizes or greater, grain boundaries are formed as such rather than occurrence of coalescence. Since the grain boundaries formed are difficulty movable in the solid phase, the grain sizes are determined at that point.

Next, the selective deposition method for forming a deposited film selectively on the deposition surface is to be described. The selective deposition method is a method in which a thin film is formed selectively on the substrate by utilizing the differences between the materials in factors influencing nucleus formation in the thin film forming process such as surface energy, attachment coefficient, release coefficient, surface diffusion speed, etc.

Figures 8A and 8B are illustrations of the selective deposition method. First, as shown in Figure 2A on the substrate 1, a thin film 2 comprising a material different in the above factors from the substrate 1 is formed at a desired portion. And, when deposition of a thin film comprising an appropriate material is effected under appropriate deposition conditions, a thin film 3 grows only on the thin film 2, whereby it is possible to give rise 15 to a phenomenon that no growth occurs on the substrate 1. By utilizing this phenomenon, the thin film 3 formed self-matchingly can be grown, whereby it becomes possible to omit the lithographic step by use of a resist as practiced in the prior art.

As the material for enabling deposition according to such selective formation method, for example SiO<sub>2</sub>

20 may be used as the substrate 1, Si, GaAs, silicon nitride as the thin film 2 and Si, W, GaAs, InP, etc., as the thin film 3 to be deposited.

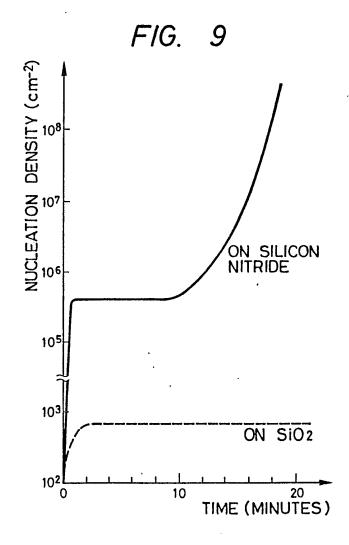

Figure 9 is a graph showing the change with lapse of time of nucleation density on the deposited surface of  $SiO_2$  and the deposited surface of silicon nitride.

As shown in the same graph, soon after initiation deposition, the nucleation density on  $SiO_2$  is saturated at  $10^3$  cm<sup>-2</sup> or less, and the value is not substantially changed even after 20 minutes.

In contrast, on silicon nitride (Si<sub>3</sub>N<sub>4</sub>), it is once saturated at about 4×10<sup>5</sup> cm<sup>-2</sup> or less, is not substantially changed 10 minutes thereafter, but is abruptly increased thereafter. This measurement example shows the case in which SiCl<sub>4</sub> gas is diluted with H<sub>2</sub> and deposited according to the CVD method under the conditions of a pressure of 170 Torr and a temperature of 1000°C. Otherwise, the same action can be obtained by use of SiH<sub>4</sub>, SiH<sub>2</sub>Cl<sub>2</sub>, SiHCl<sub>3</sub>, SiF<sub>4</sub>, etc., as the reaction gas, and controlling the pressure, temperature, etc. Also, the vacuum vapor deposition can be employed.

In this case, nucleation on  $SiO_2$  poses substantially no problem, but by addition of HCl gas into the reaction gas, nucleation on  $SiO_2$  can be further suppressed to make deposition of Si on  $SiO_2$  perfectly zero.

Such a phenomenon depends greatly on the difference in adsorption coefficient, release coefficient, surface 35 diffusion coefficient, etc., relative to Si of the material surface of SiO<sub>2</sub> and silicon nitride, but the fact that SiO<sub>2</sub> itself is etched by the reaction of SiO<sub>2</sub> with Si atom itself to form silicon monooxide with higher vapor pressure, while no such etching phenomenon occurs on silicon nitride may be also considered to be a cause to effect selective deposition (T. Yonehara, S. Yoshioka, S. Miyazawa, Journal of Applied Physics 53, 6839, 1982).

Thus, by selecting SiO<sub>2</sub> and silicon nitride as the materials of the deposition surface and silicon as the material to be deposited, sufficiently great nucleation density difference as shown in the same graph can be obtained. Here, although SiO<sub>2</sub> is desirable as the material for the deposition surface, this is not limitative and sufficiently practical nucleation density difference can be obtained even by use of SiO<sub>x</sub> (0<x<2).

Of course, the present invention is not limited to these materials, but the difference in nucleation density 45 ( $\Delta$ ND) may be sufficiently 10<sup>3</sup>-fold or more in density of nuclei as shown by the same graph, and sufficient selective formation of deposited film can be done with the materials as examplified below.

As another method for obtaining this nucleation density difference ( $\Delta ND$ ), ions of Si or N may be injected locally into the SiO<sub>2</sub> surface to form a region having excessive Si or N.

The present invention utilizes selective deposition based on such nucleation density difference (\( \D \)) and,

50 by forming sufficiently finely so that a single nucleus may grow on the deposition surface of a different kind of

material having sufficiently greater nucleation density than the material of the deposition surface, a single

crystal can be grown selectively only at the site where such fine different kind of material exists.

In this connection, since selective growth of a single crystal is determined depending on the electron state of the deposition surface, particularly the state of dangling bonds, the material with lower nucleation density (for example, SiO<sub>2</sub>) is not required to be a bulk material, but it may be formed only on the surface of any desired material, substrate, etc., to form the above deposited surface.

In the following, the present invention is described in detail by referring to the drawings.

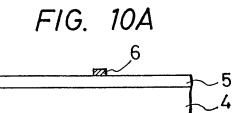

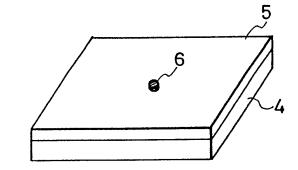

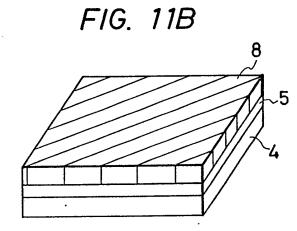

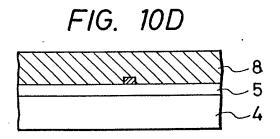

Figures 10A to 10D are illustrations of the formation steps following a first embodiment of the method for forming crystal relating to the present invention, and Figures 11A and 11B are perspective views of the substrate in Figures 10A and 10D. First, as shown in Figure 10A and Figure 10A, on the substrate 4, a thin film 5 [deposition surface (S<sub>NDS</sub>)] with small nucleation density which enables selective deposition is formed and a material different from the material forming the thin film 5 with greater nucleation density is deposited thinly, followed by patterning according to lithography, etc., to form sufficiently finely deposition surface 6 (S<sub>NDL</sub>) (or called "Seed") comprising a different kind of material. However, the size, the crystal structure and the

65 composition of the substrate 4 may be any desired ones, and a substrate having a functional device formed

65

GB 2 192 488 A

5

10

15

20

25

30

35

40

45

thereon prepared according to conventional semiconductor technique may be employed. Also, the deposition surface (S<sub>NDL</sub>) 6 comprising a different kind of material is also inclusive of modified regions having excessive Si or N formed by ion implantation of Si or N into the thin film 5 as described above.

Next, by selection of appropriate deposition conditions, a single crystal of a thin film material is formed only 5 on the deposition surface (S<sub>NDL</sub>) 6. That is, the deposition surface (S<sub>NDL</sub>) 6 is required to be formed sufficiently finely so that only a single nucleus may be formed thereon. The size of the deposition surface (S<sub>NDL</sub>) 6, which may differ depending on the kind of the material, may be several microns or less. Further, the nucleus grows while maintaining a single crystal structure to become a single crystal grain 7 in shape of an island as shown in Figure 10B. For forming an island-shaped single crystal grain 7, it is desirable to determine the conditions so that no nucleation may occur at all on the thin film 5, as already mentioned.

The island-shaped single crystal grain 7 further grows while maintaining the single crystal structure with the deposition surface ( $S_{NDL}$ ) 6 as the center (lateral overgrowth), whereby it can cover over the whole thin film 5 as shown in Figure 10C (single crystal 7A).

Subsequently, if necessary, the single crystal 7A is flattened by etching or polishing, and a single crystal 15 layer 8 capable of forming a desired device can be formed on the thin film 5 as shown in Figure 10D and Figure 11B.

For forming thus the thin film 5 forming the nonnucleation surface (S<sub>NDS</sub>) on the substrate 4, any desired material can be used for the substrate 4 which is the supporting member. Further, in such a case, even when the substrate 4 may be one having a functional device, etc., formed thereon according to conventional semiconductor technique, the single crystal layer 8 can be easily formed thereon.

In the above embodiment, the nonnucleation surface  $(S_{NDS})$  is formed of thin film 5, but a subtrate comprising a material with small nucleation density (ND) enabling selective nucleation may be used as such and nucleation surfaces  $(S_{NDL})$  may be provided at any desired positions to form single crystal layers similarly thereon.

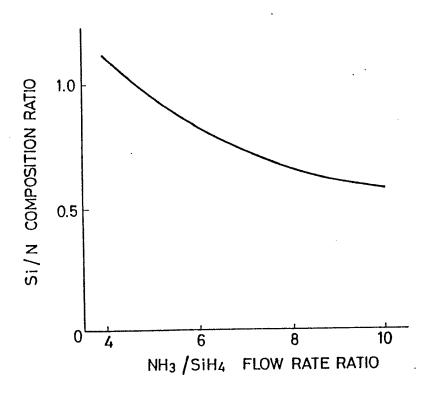

25 Figure 12 is a graph showin an example of the relationship between the flow rate ratio of SiH<sub>4</sub> and NH<sub>3</sub> and the composition ratio of Si and N in the silicon nitride film formed.

The deposition conditions at this time were RF output of 175 W, substrate temperature of 380°C and the flow rate of NH<sub>3</sub> gas was varied with the SiH<sub>4</sub> gas flow rate being fixed at cc/min. As shown in the same graph, by varying the gas flow rate ratio of NH<sub>3</sub>/SiH<sub>4</sub> from 4 to 10, the Si/N ratio in the silicon nitride film was found to be varied from 1.1 to 0.58 according to Auger's electron spectrophotometry.

On the other hand, the composition of the silicon nitride film formed according to the reduced pressure CVD method by introducing  $SiH_2Cl_2$  gas and  $NH_3$  gas under the conditions of a reduced pressure of 0.3 Torr and a temperature of about 800°C was found to be  $Si_3N_4$  (Si/N=0.75) which is approximately the stoichiometric ratio

Also, the silicon nitride film formed by heat treatment at about 1200°C in ammonia or N<sub>2</sub> (hot nitrification method) can be obtained with a composition further approximate to the stoichiometric ratio, since the formation method is performed under thermal equilibrium.

By use of silicon nitrides formed by the various methods as described above as the material for forming nucleation surface (S<sub>NDL</sub>) with higher nucleation density than SiO<sub>2</sub>, the above nucleus of Si can be grown on the nucleation surface (S<sub>NDL</sub>) comprising silicon nitride to form Si single crystal based on the nucleation density (ΔND) corresponding to the chemical composition ratio of silicon nitride.

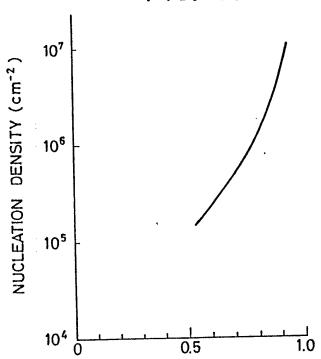

Figure 13 is a graph showing the relationship between Si/N composition ratio and nucleation density (ΔND). As shown in the same graph, by varying the chemical composition ratio of the silicon nitride film, the nucleation density of the Si single crystal nucleus formed thereon changes to a great extent. The nucleation conditions in the graph shown in Figure 13 correspond to the case when Si single crystal nucleus was formed by reacting SiCl<sub>4</sub> gas reduced to 175 Torr with H<sub>2</sub> at 1000°C. Of course, another graph will be obtained if nucleation conditions such as gas species, pressure, temperature, etc., are changed.

The phenomenon that the nucleation density thus changes according to the chemical composition ratio of silicon nitride affects the size (area) of the nucleation surface (S<sub>NDL</sub>) when employing silicon nitride as the material for forming the nucleation surface (S<sub>NDL</sub>) which is formed sufficiently finely to the extent that a single nucleus may be grown. That is, when employing silicon nitride having a composition with great nucleation density (ND) only a single crystal can be formed on the nucleation surface (S<sub>NDL</sub>) by forming the nucleation surface (S<sub>NDL</sub>) extremely finely as compared with the silicon nitride with relatively smaller nucleation density (ND). Such a point is applicable as a similar tendency for other materials for forming nucleation surface (S<sub>NDL</sub>). Accordingly, in the present invention, for accomplishing its objects effectively, it is desirable to select a nucleation density (ND) and a size of nucleation surface (S<sub>NDL</sub>) formed of silicon nitride, etc., capable of forming only a single crystal suitably as desired. For example, under the nucleation condition for obtaining a nucleation density (ND) of about 10<sup>5</sup> cm<sup>-2</sup> or less, it is possible to form selectively, only a single nucleus, if the size of the nucleation surface (S<sub>NDL</sub>) comprising silicon nitride is about 4 μm or less. The Si/N ratio in that case

(Formation of nucleation surface  $(S_{NDL})$  by ion implantation)

60 is about 0.5.

As another method for realizing nucleation density difference when forming Si single crystal nucleus, ion implantation of Si, N, P, B, F, Ar, He, C, As, Ga, Ge, etc., may be effected locally onto the surface comprising 65 SiO<sub>2</sub> which is a material for forming nonnucleation surface (S<sub>NDS</sub>) with smaller nucleation density to form a

60

55

modified region with a desired size on the SiO<sub>2</sub> surface, and utilize this modified region as the nucleation surface (S<sub>NDL</sub>) with greater nucleation density (ND).

For example, the SiO<sub>2</sub> layer surface is covered with a photoresist layer and the desired portions are exposed, developed and dissolved to have the SiO<sub>2</sub> layer surface exposed.

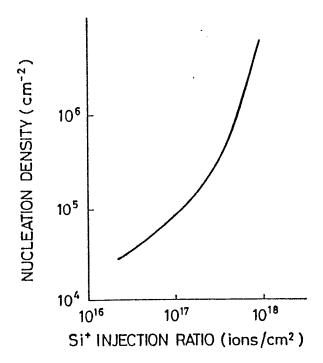

Subsequently, by use of SiF<sub>4</sub> gas as the source gas, Si ions are implanted onto the SiO<sub>2</sub> layer surface exposed at 10 keV at a density of 1×10<sup>16</sup>~1×10<sup>18</sup> cm<sup>-2</sup>. The projected flying distance in this case is 114 Å, and the Si concentration on the exposed surface of SiO<sub>2</sub> layer reaches about 10<sup>22</sup> cm<sup>-3</sup> or less. Since the SiO<sub>2</sub> layer is originally amorphous, the modified layer made excessively enriched in Si by implantation of Si ions is also amorphous.

For formation of a modified region, ion implantation can be effected with the use of a resist as the mask, but 10 it is also possible to inject a narrowed Si ion beam selectively at a desired position on the SiO2 layer surface within a desired area without use of a resist mark by use of converged ion beam technique.

After having thus effected Si ion implantation, by peeling of the resist on the remaining portion, Si-excessive modified region is formed on the SiO<sub>2</sub> layer surface at a desired position with a desired size. On 15 the modified region of the SiO₂ layer surface having such modified region formed, Si single crystal is permitted to grow in vapor phase.

Figure 14 is a graph showing the relationship between amount of Si ions implanted and nucleation density

As shown in the same graph, it can be understood that nucleation density (ND) is increased as the amount 20 of Si<sup>+</sup> implanted is more.

Accordingly, by forming a modified region sufficiently finely, only a single nucleus of Si can be grown with the modified region being as the nucleation surface (S<sub>NDL</sub>), whereby a single crystal can be grown as described above.

It can be easily accomplished by patterning of a resist or narrowing of beam of the converged ion beam to 25 form sufficiently finely the modified region to the extent that only a single nucleus may grow.

(Method for formation of Si single crystal nucleus other than CVD)

For growth of single crystal by selective nucleation of Si, not only the CVD method, but also the method by evaporation of Si into vacuum (<10<sup>-6</sup> Torr) with an electron gun and deposition on a heated substrate may be 30 used. Particularly, in the MBE (Molecular Beam Epitaxy) method which performs vapor deposition in ultra-high vacuum (<10<sup>-9</sup> Torr), it has been known that Si beam begins to react with SiO<sub>2</sub> at a substrate temperature of 900°C or higher, whereby no nucleation of Si occurs on SiO₂ at all (T. Yonehara, S. Yoshioka and S. Miyazawa, Journal of Applied Physics 53, 10, p. 6839, 1983).

By utilizing this phenomenon, single crystal nuclei of Si can be formed with perfect selectivity on the fine 35 silicon nitride regions permitted to exist in spots on the  $SiO_2$  layer, and single crystal Si can be grown thereon. 35 The single crystal growth conditions as preferable example at this time may be, for example, a vacuum degree of 10<sup>-8</sup> Torr or lower, Si beam intensity of 9.7×10<sup>14</sup> atoms/cm<sup>2</sup>.sec, and a substrate temperature of 900°C~1000°C.

In this case, through the reaction  $SiO_2 + Si \rightarrow 2SiO \uparrow$ , a reaction product of SiO with a remarkably high vapor 40 pressure is formed, and etching of SiO<sub>2</sub> itself with Si through this evaporation occurs.

In contrast, no such etching phenomenon as mentioned above occurs on silicon nitride, but nucleation of Si single crystal and growth of single crystal occur.

Accordingly, as the material for forming nucleation surface (S<sub>NDI</sub>) with high nucleation density (ND), tantalum oxide  $(Ta_2O_5)$ , silicon nitride oxide (SiON), etc., can be also used other than silicon nitride to obtain 45 the same effect. That is, by forming the above nucleation surface (S<sub>NDI</sub>) with these materials in fine areas, single crystals of Si can be permitted to grow similarly.

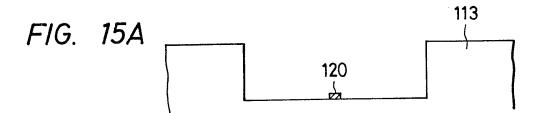

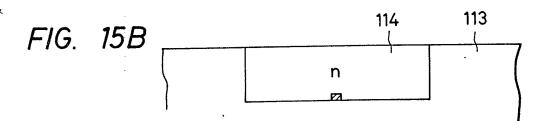

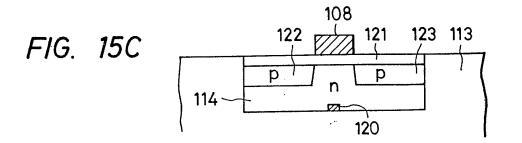

As described above, a single crystal silicon layer is formed in each of recesses in insulating layers 113 of the embodiments by using the single crystal growth method as described above. Figures 15A-15C illustrate the steps of forming a single crystal silicon and forming a transistor in the respective embodiments.

50 In Figure 15A, a recess is formed in insulating layer 113 of SiO<sub>2</sub> by etching and a small area of a different material 120 (here, Si<sub>3</sub>N<sub>4</sub>) is formed in the recess.

Then, an n-type impurity gas is mixed to grow a single crystal silicon to fill the recess with n-type single crystal silicon as shown in Figure 15B, and the resulting area is flattened to form n-type single crystal silicon layer 114.

As shown in Figure 15C, a gate oxide film 121 is then formed on single silicon layer 114, and gate electrode 108 is patterned with a material such as polysilicon or the like.

P type impurity ions are then implanted using gate electrode 108 as a mask and source and drain areas 122 and 123 are then formed by subsequent thermal treatment.

As described above in detail, according to this embodiment, switching means for setting the control 60 electrode area to a desired potential is formed on a layer different from that on which a transistor and a capacitor are formed, so that accomplishment of a minuter structure can be expedited although many terminals must be provided thereon, thereby providing a device of increased density and resolution.

It is to be noted that switching means in this invention includes semiconductor switching devices such as field effect transistors, bipolar transistors or pn-junction diodes.

20

15

25

30

40

45

50

55

15

20

#### **CLAIMS**

- A photoelectric conversion apparatus comprising a transistor having a main electrode area of one conductive type semiconductor and a control electrode area of an opposite conductive type semiconductor,

and a capacitor for controlling the potential of the control electrode area in floating state in which carriers produced optically are stored in the control electrode area by controlling the potential of the control electrode area via the capacitor, comprising:

- a multilayered structure in which switching means for setting the control electrode area to a desired potential is formed on a layer different from that on which the transistor and capacitor are formed.

- A photoelectric conversion apparatus of claim 1, wherein the switching means include semiconductor switching means formed on an insulating layer.

- 3. A photoelectric conversion apparatus of claim 2, wherein the semiconductor switching means includes a insulating gate type transistor.

- 4. A photoelectric conversion apparatus of claim 2, wherein the semiconductor switching means includes 15 a pn-junction diode.

- 5. A photoelectric conversion apparatus of claim 2, whrein the semiconductor switching means includes a bipolar transistor.

- 6. A photoelectric converter comprising a transistor responsive to received light energy to produce charge carriers, the transistor having a control electrode region in which the carriers are accumulated in response to the received light energy and further comprising means for controlling the potential of the control electrode region, the controlling means being formed on a layer of semiconductor material different from that on which the said transistor is formed.

- 7. A photoelectric converter substantially as hereinbefore described with reference to: Figures 3a and 3b; Figures 4a and 4b; Figures 5a and 5b; or Figures 6a and 6b.

- A photoelectric converter according to any preceding claim as made by a method as described with reference to Figures 7 to 15c.