## (19) **日本国特許庁(JP)**

(51) Int. C1.

# (12) 特 許 公 報(B2)

$\mathbf{F} \mathbf{L}$

(11)特許番号

特許第4025301号 (P4025301)

(45) 発行日 平成19年12月19日(2007.12.19)

(24) 登録日 平成19年10月12日 (2007.10.12)

| (51) 1111.01. | 1 1                           |                         |

|---------------|-------------------------------|-------------------------|

| GO1R 31/28    | <b>(2006.01)</b> GO1R         | 31/28 V                 |

| HO1L 21/822   | <b>(2006.01)</b> GO1R         | 31/28 E                 |

| HO1L 27/04    | <b>(2006.01)</b> HO1L         | 27/04 T                 |

| HO1L 21/82    | ( <b>2006.01)</b> HO1L        | 21/82 T                 |

| GO6F 11/22    | (2006.01) GO6F                | 11/22 3 1 O F           |

|               |                               | 請求項の数 6 (全 15 頁) 最終頁に続く |

| (21) 出願番号     | 特願2004-21723 (P2004-21723)    | (73) 特許権者 000003078     |

| (22) 出願日      | 平成16年1月29日 (2004.1.29)        | 株式会社東芝                  |

| (65) 公開番号     | 特開2004-239903 (P2004-239903A) | 東京都港区芝浦一丁目1番1号          |

| (43) 公開日      | 平成16年8月26日 (2004.8.26)        | (73) 特許権者 390009531     |

| 審査請求日         | 平成16年1月29日 (2004.1.29)        | インターナショナル・ビジネス・マシーン     |

| (31) 優先権主張番号  | 10/358, 461                   | ズ・コーポレーション              |

| (32) 優先日      | 平成15年2月4日 (2003.2.4)          | INTERNATIONAL BUSIN     |

| (33) 優先権主張国   | 米国 (US)                       | ESS MASCHINES CORPO     |

|               |                               | RATION                  |

| 前置審査          |                               | アメリカ合衆国10504 ニューヨーク     |

|               |                               | 州 アーモンク ニュー オーチャード      |

|               |                               | ロード                     |

|               |                               | (74) 代理人 100058479      |

|               |                               | 弁理士 鈴江 武彦               |

|               |                               |                         |

|               |                               | 最終頁に続く                  |

(54) [発明の名称] 電子回路試験用回路、電子回路試験装置、および電子回路試験方法

## (57)【特許請求の範囲】

#### 【請求項1】

複数の擬似ランダムデータパターンに重み付けするとともに、これら各重み付けされた 擬似ランダムデータパターンの信号をテストされる電子回路に入力する電子回路試験用回 路であって、

<u>少なくとも1つの前記擬似ランダムデータパターンの信号が入力される少なくとも1つ</u>の入力側論理ゲートと、

<u>この入力側論理ゲートに入力される前記擬似ランダムデータパターンの前記信号と同じ信号および前記入力側論理ゲートから出力される信号が入力されるとともに、入力された前記各信号のうちのいずれか一方を選択して出力する少なくとも1つの入力側マルチプレ</u>クサと、

<u>この入力側マルチプレクサから出力される前記信号を選択するための選択信号を前記入</u> 力側マルチプレクサに入力する少なくとも1つの制御回路と、

前記入力側論理ゲートに入力される前記各擬似ランダムデータパターンの前記信号と同 じ信号および入力側マルチプレクサから出力される前記信号が入力されるとともに、入力 された前記各信号のうちのいずれか一方を選択して出力する第 1 のマルチプレクサと、

<u>この第1のマルチプレクサから出力される前記信号が一方の入力に入力される出力側論</u>理ゲートと、

<u>この出力側論理ゲートから出力される前記信号および外部入力から入力される信号が入</u>力されるとともに、入力された前記各信号のうちのいずれか一方を選択して前記電子回路

に入力する出力側マルチプレクサと、

前記第1のマルチプレクサから出力される前記信号を決定するための重み選択信号を選択出力から前記第1のマルチプレクサに入力するとともに、前記出力側マルチプレクサから出力される前記信号を決定するための重み選択信号を追加出力から前記出力側マルチプレクサに入力し、かつ、前記側出力論理ゲートが有する他方の入力に接続された他の出力を有する重み付けチャンネル回路と、

を具備することを特徴とする電子回路試験用回路。

## 【請求項2】

前記第1のマルチプレクサは、nを1以上の整数とする2<sup>n</sup>対1のマルチプレクサであることを特徴とする請求項1に記載の電子回路試験用回路。

【請求項3】

複数の擬似ランダムデータパターンを発生させて出力する擬似ランダムバイナリー数発 生装置と、

この擬似ランダムバイナリー数発生装置とテストされる電子回路との間に設けられており、前記各擬似ランダムデータパターンが入力されるとともに入力された前記各擬似ランダムデータパターンに重み付けして前記電子回路に入力するプログラム可能な重み付けされたランダムパターン発生装置と、

前記電子回路に入力された前記各重み付けされた擬似ランダムデータパターンおよび前記電子回路の内部の誤り状態に応じて前記電子回路が発生させた複数の出力データパターンが入力されるとともに、これら各出力データパターンを特異な記号に圧縮するデータ圧縮装置と、

を具備してなり、前記ランダムパターン発生装置の内部には、

<u>少なくとも1つの前記擬似ランダムデータパターンの信号が入力される少なくとも1つ</u>の入力側論理ゲートと、

<u>この入力側論理ゲートに入力される前記擬似ランダムデータパターンの前記信号と同じ信号および前記入力側論理ゲートから出力される信号が入力されるとともに、入力された前記各信号のうちのいずれか一方を選択して出力する少なくとも1つの入力側マルチプレ</u>クサと、

<u>この入力側マルチプレクサから出力される前記信号を選択するための選択信号を前記入力側マルチプレクサに入力する少なくとも1つの制御回路と、</u>

前記入力側論理ゲートに入力される前記各擬似ランダムデータパターンの前記信号と同 じ信号および入力側マルチプレクサから出力される前記信号が入力されるとともに、入力 された前記各信号のうちのいずれか一方を選択して出力する第1のマルチプレクサと、

<u>この第1のマルチプレクサから出力される前記信号が一方の入力に入力される出力側論</u>理ゲートと、

<u>この出力側論理ゲートから出力される前記信号および外部入力から入力される信号が入力されるとともに、入力された前記各信号のうちのいずれか一方を選択して前記電子回路</u>に入力する出力側マルチプレクサと、

前記第1のマルチプレクサから出力される前記信号を決定するための重み選択信号を選択出力から前記第1のマルチプレクサに入力するとともに、前記出力側マルチプレクサから出力される前記信号を決定するための重み選択信号を追加出力から前記出力側マルチプレクサに入力し、かつ、前記側出力論理ゲートが有する他方の入力に接続された他の出力を有する重み付けチャンネル回路と、

を備えてなり、前記ランダムデータパターン発生装置に入力された前記各擬似ランダムデータパターンに重み付けするとともに、これら各重み付けされた擬似ランダムデータパターンの信号を前記電子回路に入力する電子回路試験用回路が設けられている、ことを特徴とする電子回路試験装置。

## 【請求項4】

前記第1のマルチプレクサは、 n を 1 以上の整数とする 2 <sup>n</sup> 対 1 のマルチプレクサであることを特徴とする請求項 3 に記載の電子回路試験装置。

10

30

20

50

#### 【請求項5】

複数の擬似ランダムデータパターンを発生させ、

これら各擬似ランダムデータパターンに電子回路試験用回路を用いて重み付けし、

<u>これら各重み付けされた擬似ランダムデータパターンの信号をテストされる電子回路に</u> 入力し、

<u>入力された前記各信号および前記電子回路内部の誤り状態に応じて前記電子回路が発生</u>させた出力データパターンを特異な記号に圧縮し、

<u>この圧縮された記号と前記電子回路が適正な状態で発生すると予想された記号とを比較</u> することにより、前記電子回路の内部の欠陥を検出する電子回路試験方法であって、

前記電子回路試験用回路は、

<u>少なくとも1つの前記擬似ランダムデータパターンの信号が入力される少なくとも1つ</u>の入力側論理ゲートと、

<u>この入力側論理ゲートに入力される前記擬似ランダムデータパターンの前記信号と同じ信号および前記入力側論理ゲートから出力される信号が入力されるとともに、入力された前記各信号のうちのいずれか一方を選択して出力する少なくとも1つの入力側マルチプレクサと、</u>

<u>この入力側マルチプレクサから出力される前記信号を選択するための選択信号を前記入</u>力側マルチプレクサに入力する少なくとも 1 つの制御回路と、

前記入力側論理ゲートに入力される前記各擬似ランダムデータパターンの前記信号と同じ信号および入力側マルチプレクサから出力される前記信号が入力されるとともに、入力された前記各信号のうちのいずれか一方を選択して出力する第 1 のマルチプレクサと、

<u>この第1のマルチプレクサから出力される前記信号が一方の入力に入力される出力側論</u>理ゲートと、

<u>この出力側論理ゲートから出力される前記信号および外部入力から入力される信号が入力されるとともに、入力された前記各信号のうちのいずれか一方を選択して前記電子回路</u>に入力する出力側マルチプレクサと、

前記第1のマルチプレクサから出力される前記信号を決定するための重み選択信号を選択出力から前記第1のマルチプレクサに入力するとともに、前記出力側マルチプレクサから出力される前記信号を決定するための重み選択信号を追加出力から前記出力側マルチプレクサに入力し、かつ、前記側出力論理ゲートが有する他方の入力に接続された他の出力を有する重み付けチャンネル回路と、

<u>を具備してなる</u>ことを特徴とする電子回路試験方法。

### 【請求項6】

前記第 1 のマルチプレクサは、 n を 1 以上の整数とする 2  $^{n}$  対 1 のマルチプレクサであることを特徴とする請求項 5 に記載の電子回路試験方法。

【発明の詳細な説明】

### 【技術分野】

### [0001]

本発明は、集積電子回路の試験に係り、特に集積電子回路の機能性を試験するための自己試験回路および試験方法が組み込まれた集積電子回路<u>を試験するための電子回路試験用</u>回路、電子回路試験装置、および電子回路試験方法に関する。

【背景技術】

## [0002]

単体の超大規模集積回路(VLSI)半導体素子は、例えば、AND、OR、NAND、NOR、あるいはXORゲートを含む互いに接続された数千の論理ゲートを備えている。そのようないかなる集積回路にとって製造プロセスの重要な部分は、集積回路内に含まれた各論理ゲートの機能性を検証することである。それぞれの論理ゲートの機能性を検証することは、限られた数の集積回路用の入力/出力(I/O)端子、および多数の論理ゲートの各入力と各出力との間の複雑な相互接続により、困難になるおそれがある。多くの場合、集積回路内の多数のチャンネルは、I/O端子を共有している。

10

20

30

50

## [0003]

半導体素子内に備えられた集積回路の機能性テストを行っている間、素子内の論理ゲートに入力される複数の 0 と 1 との連続からなる所定のデジタルデータパターンを、集積回路の入力は受け取る。これに応答して、各論理ゲートは各入力データパターンを処理し、結果として、集積回路は、各入力データパターンおよび各論理ゲートの機能性に依る、再び複数の 0 と 1 との連続からなる出力データパターンを発生させる。出力データパターンが予想された出力データパターンと一致しないときは、各論理ゲートのうちの少なくとも 1 個の論理ゲートに誤りが生じたことが分かる。

### [0004]

多くの集積回路は、純粋なランダムな入力データパターンを用いるテストが困難な論理ゲート構造を含んでいる。そのような論理ゲート構造の一例として、ANDゲートがある。ANDゲートにおける欠陥が検出される確率は、ANDゲートに対する入力数が増えるに連れて減少する。初めに、ANDゲートの欠陥を検査するためには、ANDゲートから出力される信号を1とするために、全てのANDゲートの入力は1の入力ディジットを受け取らなければならない。次に、ANDゲートの正しい機能を果たすことが正しいことを確かめるために、ANDゲートの入力の1つは殆ど1とされるべきである。それゆえに、集積回路に入力されるデータパターンを構成するビットは、それぞれのANDゲートの入力に入力されなければならない様々なビットの変換を容易にするように構成されなければならない。

### [00005]

乱数発生テストの制限を処理するために、 0 か 1 の発生の確率を変更するテスト方法は発展してきた。これらのテスト方法は、要求された論理ゲートの特定のテストを実行するように、重み付けされた乱数発生装置を用いてランダムな入力データパターンに重み付けする。重み付けされた乱数発生装置は、重み付けされたランダムな入力パターンをテスト中に集積回路に出力する。重み付け因子が正の数である場合、重み付けされたランダムな入力パターンの中で、入力ディジットが 0 である確率は重み付け因子の 2 分の 1 倍を掛けたものであり、そして入力ディジットが 1 である確率は 1 から重み付け因子の 2 分の 1 倍を引いたものである。このように、重み付け因子は 0 か 1 の発生の確率として表現される。重み付け因子は、集積回路への入力数および素子内部の論理ゲートの数とタイプに依存して選択される。さらに、重み付け因子は、論理回路の中に欠陥が存在しないという確信を受けることができる水準を伴ったテストにより、時間とコストの効率の良さを促進するように選択される。

#### 【発明の開示】

【発明が解決しようとする課題】

## [0006]

集積回路の機能性テストに対する一つの選択肢は、あらゆる予想された出力データパターンを発生することを期待して、素子の入力への多数のデータパターンの供給に関係している。しかしながら、そのようなテスト処理は、多数の入力データパターンを発生させて入力する必要があるため、極めて長いテスト時間を必要とするおそれがある。

## [0007]

他の選択肢は、欠陥のある論理ゲートを見分けることを期待して、集積回路の入力に対するランダムなデータパターンの供給に関係している。論理回路から出力された評価されたデータパターンは、予想された出力データパターンと再び比較される。しかしながら、ランダムなデータパターンの供給に関連する1つの問題は、論理回路の一部のみしかテストされないことであり、そしてそれゆえに、集積回路は欠陥を検出されないまま有する可能性がある。多数のランダムな入力データパターンを集積回路の入力に供給することは、より多くの論理ゲートがテストされる可能性を増大させる。しかしながら、増大した多くの入力データパターンは全体のテスト時間を長時間化させ、そしてこのため、集積回路の製造コスト全体が増大する。

## [0008]

20

30

20

30

40

50

本発明は、以上説明したような課題を解決するためになされたものであり、その目的とするところは、複数個の論理回路を備える集積回路の試験に係る時間およびコストを低減することができる<u>電子回路試験用回路、電子回路試験装置、および電子回路試験方法</u>を提供することにある。

### 【課題を解決するための手段】

### [0009]

本発明の一態様に係る電子回路試験用回路は、複数の擬似ランダムデータパターンに重 み付けするとともに、これら各重み付けされた擬似ランダムデータパターンの信号をテス トされる電子回路に入力する電子回路試験用回路であって、少なくとも1つの前記擬似ラ ンダムデータパターンの信号が入力される少なくとも1つの入力側論理ゲートと、この入 力側論理ゲートに入力される前記擬似ランダムデータパターンの前記信号と同じ信号およ び前記入力側論理ゲートから出力される信号が入力されるとともに、入力された前記各信 号のうちのいずれか一方を選択して出力する少なくとも1つの入力側マルチプレクサと、 この入力側マルチプレクサから出力される前記信号を選択するための選択信号を前記入力 側マルチプレクサに入力する少なくとも1つの制御回路と、前記入力側論理ゲートに入力 される前記各擬似ランダムデータパターンの前記信号と同じ信号および入力側マルチプレ クサから出力される前記信号が入力されるとともに、入力された前記各信号のうちのいず れか一方を選択して出力する第1のマルチプレクサと、この第1のマルチプレクサから出 力される前記信号が一方の入力に入力される出力側論理ゲートと、この出力側論理ゲート から出力される前記信号および外部入力から入力される信号が入力されるとともに、入力 された前記各信号のうちのいずれか一方を選択して前記電子回路に入力する出力側マルチ プレクサと、前記第1のマルチプ<u>レクサから出力される前記信号を決定するための重み選</u> 択信号を選択出力から前記第1のマルチプレクサに入力するとともに、前記出力側マルチ プレクサから出力される前記信号を決定するための重み選択信号を追加出力から前記出力 側マルチプレクサに入力し、かつ、前記側出力論理ゲートが有する他方の入力に接続され た他の出力を有する重み付けチャンネル回路と、を具備することを特徴とするものである

## [0010]

また、本発明の他の態様に係る電子回路試験装置は、複数の擬似ランダムデータパター ンを発生させて出力する擬似ランダムバイナリー数発生装置と、この擬似ランダムバイナ リー数発生装置とテストされる電子回路との間に設けられており、前記各擬似ランダムデ ータパターンが入力されるとともに入力された前記各擬似ランダムデータパターンに重み 付けして前記電子回路に入力するプログラム可能な重み付けされたランダムパターン発生 装置と、前記電子回路に入力された前記各重み付けされた擬似ランダムデータパターンお よび前記電子回路の内部の誤り状態に応じて前記電子回路が発生させた複数の出力データ パターンが入力されるとともに、これら各出力データパターンを特異な記号に圧縮するデ ータ圧縮装置と、を具備してなり、前記ランダムパターン発生装置の内部には、少なくと <u>も1つの前記擬似ランダムデータパターンの信号が入力される少なくとも1つの入力側論</u> 理ゲートと、この入力側論理ゲートに入力される前記擬似ランダムデータパターンの前記 信号と同じ信号および前記入力側論理ゲートから出力される信号が入力されるとともに、 入力された前記各信号のうちのいずれか一方を選択して出力する少なくとも1つの入力側 マルチプレクサと、この入力側マルチプレクサから出力される前記信号を選択するための 選択信号を前記入力側マルチプレクサに入力する少なくとも1つの制御回路と、前記入力 側論理ゲートに入力される前記各擬似ランダムデータパターンの前記信号と同じ信号およ び入力側マルチプレクサから出力される前記信号が入力されるとともに、入力された前記 各信号のうちのいずれか一方を選択して出力する第1のマルチプレクサと、この第1のマ ルチプレクサから出力される前記信号が一方の入力に入力される出力側論理ゲートと、こ の出力側論理ゲートから出力される前記信号および外部入力から入力される信号が入力さ れるとともに、入力された前記各信号のうちのいずれか一方を選択して前記電子回路に入 <u>力する出力側マルチプレクサと、前記第1のマルチプレクサから出力される前記信号を決</u> 定するための重み選択信号を選択出力から前記第1のマルチプレクサに入力するとともに、前記出力側マルチプレクサから出力される前記信号を決定するための重み選択信号を追加出力から前記出力側マルチプレクサに入力し、かつ、前記側出力論理ゲートが有する他方の入力に接続された他の出力を有する重み付けチャンネル回路と、を備えてなり、前記ランダムデータパターン発生装置に入力された前記各擬似ランダムデータパターンに重み付けするとともに、これら各重み付けされた擬似ランダムデータパターンの信号を前記電子回路に入力する電子回路試験用回路が設けられている、ことを特徴とするものである。

[0011]

さらに、本発明のまた他の態様に係る電子回路試験方法は、複数の擬似ランダムデータ パターンを発生させ、これら各擬似ランダムデータパターンに電子回路試験用回路を用い て重み付けし、これら各重み付けされた擬似ランダムデータパターンの信号をテストされ る電子回路に入力し、入力された前記各信号および前記電子回路内部の誤り状態に応じて 前記電子回路が発生させた出力データパターンを特異な記号に圧縮し、この圧縮された記 号と前記電子回路が適正な状態で発生すると予想された記号とを比較することにより、前 記電子回路の内部の欠陥を検出する電子回路試験方法であって、前記電子回路試験用回路 は、少なくとも1つの前記擬似ランダムデータパターンの信号が入力される少なくとも1 つの入力側論理ゲートと、この入力側論理ゲートに入力される前記擬似ランダムデータパ ターンの前記信号と同じ信号および前記入力側論理ゲートから出力される信号が入力され るとともに、入力された前記各信号のうちのいずれか一方を選択して出力する少なくとも 1つの入力側マルチプレクサと、この入力側マルチプレクサから出力される前記信号を選 択するための選択信号を前記入力側マルチプレクサに入力する少なくとも1つの制御回路 と、前記入力側論理ゲートに入力される前記各擬似ランダムデータパターンの前記信号と 同じ信号および入力側マルチプレクサから出力される前記信号が入力されるとともに、入 力された前記各信号のうちのいずれか一方を選択して出力する第1のマルチプレクサと、 この第1のマルチプレクサから出力される前記信号が一方の入力に入力される出力側論理 ゲートと、この出力側論理ゲートから出力される前記信号および外部入力から入力される 信号が入力されるとともに、入力された前記各信号のうちのいずれか一方を選択して前記 電子回路に入力する出力側マルチプレクサと、前記第1のマルチプレクサから出力される 前記信号を決定するための重み選択信号を選択出力から前記第1のマルチプレクサに入力 するとともに、前記出力側マルチプレクサから出力される前記信号を決定するための重み 選択信号を追加出力から前記出力側マルチプレクサに入力し、かつ、前記側出力論理ゲー トが有する他方の入力に接続された他の出力を有する重み付けチャンネル回路と、を具備 <u>してなることを特徴とするものである。</u>

[0012]

本発明の他の態様は、本発明を実施するために熟考されたベストモードを簡潔に説明することにより本発明の代表的な形態を示すとともに説明する以下の詳細な説明から、この技術の中のこれらの技術に対して容易かつ明確になる。本発明は、全く本発明からはずれることなく、他の異なる実施形態に有用であるとともに、その幾つかの細部は様々な点において修正可能であるしたがって、図および説明は、本質的に実例とみなされるとともに、限定的なものではない。

【発明の効果】

[0013]

本発明によれば、複数個の論理回路を備える集積回路の試験に係る時間およびコストを低減することができる。

【発明を実施するための最良の形態】

[0014]

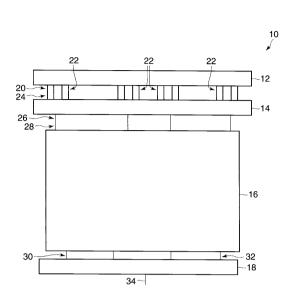

図1は、擬似ランダムパターン発生技術を利用する典型的な自己テスト内蔵論理("LBIST")テスト構成10のブロックダイアグラムである。LBISTテスト構成10 は、MSIRおよび並列シフトレジスタ連続発生装置を用いる自己テスト("STUMPS")と呼ばれるスキャンパス構造とも呼ばれる。STUMPS構造は、多数のチップシ

20

30

20

30

40

50

ステムを高速スループットでテストするための組込み型の構造である。LBISTテスト構成 10 は、線形フィードバックシフトレジスタ("LFSR")12、プログラム可能な重み付けされたランダムパターン発生装置("PWR")14、テストされる集積回路16、および多入力シフトレジスタ("MISR")18を含んでいる。 LFSR12からの出力20は、1グループが4つの出力線22からなる4つの出力のグループから構成され、16個の各出力線22はそれぞれPWR14の16個の各入力24に対応して接続されている。PWR 14 は、集積回路 16 の4つの入力28に対応して接続された4つの出力26を有する。集積回路 16 は、MISR 18 の4つの入力32に対応して接続された4つの出力30を有する。MISR18は、1つの出力34を有する。

#### [0015]

図 1 において、LFSR 1 2 は 1 6 個の出力 2 0 <u>(出力線 2 2 )</u>のみを有するものとして描かれて<u>いる。また、</u>PWR 1 4 は 1 6 個の入力 2 4 と 4 つの出力 2 6 のみを有するものとして描かれて<u>いる。また、</u>テストされる集積回路 1 6 は 4 つの入力 2 8 と 4 つの出力 3 0 とを有するものとして描かれて<u>いる。</u>そして M I S R 1 8 は 4 つの入力 3 2 と 1 つの出力 3 4 のみを有するものとして描かれてい<u>る。しかし、</u>LFSR 1 2 、PWR 1 4 、テストされる集積回路 1 6 、および M I S R 1 8 のいずれも、 それらが有する各入力 2 4 , 2 8 , 3 2 および各出力 2 0 ( 2 2 ), 2 6 , 3 0 , 3 4 の数はより少なくても構わない し、あるいはより多くても構わない。

### [0016]

<u>LBISTテスト構成10の</u>作動中は、LFSR12は、LFSR<u>12</u>から出力されてPWR14に入力される擬似ランダムデータパターンを発生させる擬似ランダムバイナリー数発生装置として作動する。PWR<u>14</u>はLFSR<u>12</u>からの擬似ランダムデータパターンに重み付けする。この結果として生じる重み付けされた擬似ランダムデータパターンは、PWR<u>14</u>から出力されてテストされる集積回路16に入力される。テストされる集積回路<u>16</u>内に含まれた論理ゲートの誤り状態に応じた出力データパターンおよび集積回路<u>16</u>内に含まれた計理が一トの誤り状態に応じた出力データパターンを発生させる。この結果として生じる出力データパターンを発生させる。この結果として生じる出力データパターンは、テストされる集積回路<u>16</u>から出力されてMISR18に入力される、MISR<u>18</u>は、テストされる集積回路<u>16</u>からの出力データパターンを、テストされる集積回路<u>16</u>からの出力データパターンを、テストされる集積回路<u>16</u>から出力されて解析されるとともに予想された記号と比較される。このように、評価されるとともに予想された記号を解析した後、テストされる集積回路 16が誤っているかどうかが決定される。

## [0017]

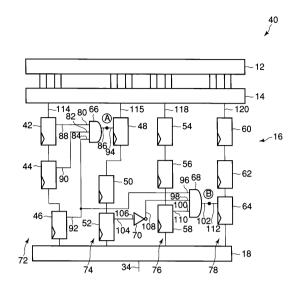

以上議論したように、欠陥のある論理ゲートをテストするための努力は、例えば、ANDゲートのように、特定のタイプの論理ゲートに対してより難しくなる。図 2 は、 $\frac{第1}{2}$   $\frac{1}{2}$   $\frac{1$

#### [0018]

第 1 の A N D ゲート 6 6 は、 3 つの入力 8 0 <u>, 8 2 ,</u> 8 4 と 1 つの出力 8 6 を有する。 第 1 のカラム 7 2 内の 3 つの直列接続された<u>各</u>フリップフロップ 4 2 ~ 4 6 のそれぞれの アウトプット <u>8 8 , 9 0 , 9 2</u> は、第 1 の A N D ゲート <u>6 6</u> の各入力 <u>8 0 , 8 2 , 8 4</u> の うちの1つに接続されている。特に、第1のフリップフロップ <u>42</u>の出力 88は第1の AND ゲート <u>66</u>の第1の入力 80に接続され、第2のフリップフロップ <u>44</u>の出力 90は 第1の AND ゲート <u>66</u>の第2の入力 82に接続され、そして第3のフリップフロップ <u>4</u>6の出力 92は第1の AND ゲート <u>66</u>の第3の入力 84に接続されている。第1の AND ゲートの出力 <u>86</u>は、第2のカラム 74内の第4のフリップフロップ 48の入力 94に 接続されている。

### [0019]

## [0020]

#### [0021]

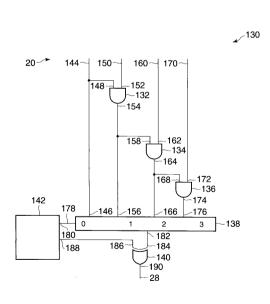

図 3 は、第 1 の A N D ゲート 1 3 2、第 2 の A N D ゲート 1 3 4、第 3 の A N D ゲート 1 3 6、4 対 1 マルチプレクサ 1 3 8、 X O R ゲート 1 4 0、および重み付けチャンネル回路 1 4 2 を含む、前述した 従来の P W R 1 4 に 含まれている回路構成 1 3 0 のブロックダイアグラムである。前述した L F S R 1 2 の第 1 の出力 1 4 4 は、4 対 1 マルチプレクサの第 1 の入力 1 4 6 および第 1 の A N D ゲート 1 3 2 の 一方の入力 1 4 8 に接続されている。 L F S R 1 2 の第 2 の出力 1 5 0 は、第 1 の A N D ゲート 1 3 2 の他方の入力 1 5 2 に接続されている。第 1 の A N D ゲート 1 3 2 の出力 1 5 4 は、4 対 1 マルチプレクサの第 2 の入力 1 5 6 および第 2 の A N D ゲート 1 3 4 の 一方の入力 1 5 8 に接続されている。 L F S R 1 2 の第 3 の出力 1 6 0 は、第 2 の A N D ゲート 1 3 4 の他方の入力 1 6 2 に接続されている。第 2 の A N D ゲート 0 出力 1 6 4 は、4 対 1 マルチプレクサの第 3 の入力 1 6 6 および第 3 の A N D ゲート 1 3 6 の他方の入力 1 7 2 に接続されている。第 3 の A N D ゲート 0 出力 1 7 4 は、4 対 1 マルチプレクサの第 4 の入力 1 7 6 に接続されている。第 3 の A N D ゲートの出力 1 7 4 は、4 対 1 マルチプレクサの第 4 の入力 1 7 6 に接続されている。

## [0022]

4対1マルチプレクサ<u>138</u>の2本の選択線(1本のみ図示)178は、重み付けチャンネル回路142の選択出力(1つのみ図示)180に接続されている。4対1マルチプレクサ<u>138</u>の出力182は、XORゲート140の<u>一方</u>の入力184に接続されている。XORゲートの<u>他方</u>の入力186は、重み付けチャンネル回路<u>142</u>の他の出力188に接続されている。さらに、図3において図1を参照すると、XORゲートの出力190は、テストされる集積回路16の入力28に接続されている。

## [0023]

40

20

20

30

40

50

以上簡単に述べたように、図3に描かれた回路構成130は、PWR14の一部のみを表す。図3に描かれた回路構成130はLFSR12からの4本の出力線22<u>(144, 150, 160, 170)</u>およびテストされる集積回路16の1つの入力チャンネル28に対応して1つずつ接続される。このため、PWR14には図3に描かれた回路構成13<u>0が4つ</u>含まれるであろう。それゆえに、回路構成<u>130</u>の数は、変えることができるとともに、LFSR<u>12</u>からの出力20の数およびテストされる<u>集積回路16</u>への入力チャンネル28の数に依存する。

## [0024]

<u>なお、</u>第1、第2、および第3の<u>各</u>ANDゲート132<u>,134,</u>136、4対1マルチプレクサ138、ならびにXORゲート140は、多数の商業上利用できる電子部品から望ましいものが選択される。

#### [0025]

図3に描かれた回路構成130は、その作動中は、擬似ランダム4ビットデータパター ンをLFSR12から受け取る。4ビットのそれぞれが0か1になる確率は2分の1であ る。それゆえに、LFSR12から出力されて4対1マルチプレクサ138の第1の入力 146が受け取る第1のビットが1である確率は2分の1である。また、LFSR12か ら出力されて第1のANDゲート132の一方の入力148に入力される第1のビットが 1となる確率は2分の1であるとともに、LFSR12から出力されて第1のANDゲー ト132の他方の入力152に入力される第2のビットが1となる確率は2分の1である 。このため、第1のANDゲート132から出力されて4対1マルチプレクサ138の第 2の入力156に入力される信号が1となる確率は4分の1である。また、第1のAND ゲート132から出力されて第2のANDゲート134の一方の入力158に入力される 信号が1となる確率は4分の1であるとともに、LFSR<u>12</u>から出力されて第2のAN Dゲート134の他方の入力162に入力される第3のビットが1となる確率は2分の1 である。このため、第2のANDゲート134から出力されて4対1マルチプレクサ13 8の第3の入力166に入力される信号が1となる確率は8分の1である。また、第2の A N D ゲート 1 3 4 から出力されて第 3 の A N D ゲート 1 3 6 の一方の入力 1 6 8 に入力 される信号が1となる確率は4分の1であるとともに、LFSR<u>12</u>から出力されて第3 のANDゲート136の他方の入力172に入力される第4のビットが1となる確率は2 分の1である。このため、第3のANDゲート136から出力されて4対1マルチプレク サ138の第4の入力176に入力される信号が1となる確率は16分の1である。

## [0026]

4 対 1 マルチプレクサ 1 3 8 の出力 1 8 2 から出力される信号は、重み付けチャンネル回路 1 4 2  $\underline{0}$  2 つの選択出力 1 8 0 (1 本のみを図示) から出力され  $\underline{C}$  4 対 1 マルチプレクサ 1 3 8  $\underline{0}$  2 本の選択線 1 7 8 (1 本のみを図示) に入力され 3 2 つの重み選択信号によって制御される。 2 本の選択線上の重み選択信号が(0 , 0 ) 、(0 , 1 ) 、(1 , 0 ) 、あるいは (1 , 1 ) であると、4 対 1 マルチプレクサ 1 3 8 の出力 1 8 2 から出力される信号は、それぞれ4 対 1 マルチプレクサ 1 3 8 の第 1 、第 2 、第 3 、あるいは第 4 の 各入力 1 4 6 , 1 5 6 , 1 6 6 , 1 7 6 によって受け取られた信号のいずれかになる。このように、重み選択信号が(0 , 0 ) 、(0 , 1 ) 、(1 , 0 ) 、あるいは(1 , 1 ) であると、4 対 1 マルチプレクサ 1 3 8 の出力 1 8 2 における信号が 1 となる確率は、それぞれ 2 分の 1 、4 分の 1 、8 分の 1 、あるいは 1 6 分の 1 である。

## [0027]

図 3 に描かれた重み付けチャンネル回路 1 4 2 はまた、 その他方の出力 1 8 8 から X O R  $\underline{\mathcal{F}}$   $\underline{\mathcal{F}}$   $\underline{\mathcal{F}}$  1 4 0 の  $\underline{\mathcal{F}}$  の入力 1 8 6 によって受け取られる単一のビット制御信号を出力する。 X O R  $\underline{\mathcal{F}}$   $\underline{$

30

40

50

<u>0</u>の出力 1 9 0 における信号が 1 となる確率は、それぞれ 2 分の 1 、 4 分の 1 、 8 分の 1 、 あるいは 1 6 分の 1 である。さらに、単一のビット制御信号が 1 であるとともに、選択線信号が (0,0)、(0,1)、(1,0)、あるいは (1,1)であると、XORFート 1 4 0 の出力 1 9 0 における信号が 1 となる確率は、それぞれ 2 分の 1 、 4 分の 3 、 8 分の 7 、 あるいは 1 6 分の 1 5 である。

#### [0028]

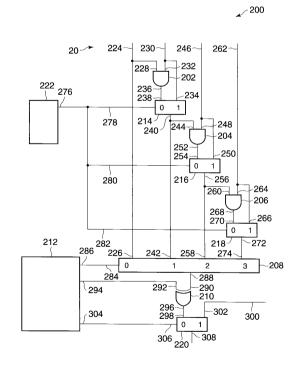

図4は、本発明の一実施形態に係るPWR14に含まれる回路構成200のブロックダイアグラムである。図3の回路構成130と同様に、図4の回路構成200は第1のANDゲート202、第2のANDゲート204、第3のANDゲート206、4対1マルチプレクサ208、XORゲート210、および重み付けチャンネル回路212を含む。さらに、図4に描かれた回路構成200は、第1の2対1マルチプレクサ214、第2の2対1マルチプレクサ216、第3の2対1マルチプレクサ218、第4の2対1マルチプレクサ220、および制御回路222を含む。

### [0029]

## [0030]

第1、第2、第3、および第4の各2対1マルチプレクサ214,216,220、ならびに制御回路222は、あらゆる様々なタイプの電子構成部品から望ましいものが選択されればよい。代わりの実施形態では、図4の回路構成200に含まれる構成部品は、単体の電子素子(図示せず)内に収容される。

## [0031]

LFSR12の第1の出力224は、4対1マルチプレクサ208の第1の入力226 および第1のANDゲート202の一方の入力228に接続される。LFSR12の第2 の出力 2 3 0 は、第 1 の A N D ゲート 2 0 2 の他方の入力 2 3 2 および第 1 の 2 対 1 マル チプレクサ214の第2の入力234に接続される。第1のANDゲート202の出力2 3 6 は、第 1 の 2 対 1 マルチプレクサ 2 0 8 の第 1 の入力 2 3 8 に接続される。第 1 の 2 対 1 マルチプレクサ 2 0 8 の出力 2 4 0 は、 4 対 1 マルチプレクサ 2 0 8 の第 2 の入力 2 4 2 および第 2 の A N D ゲート 2 0 4 の一方の入力 2 4 4 に接続される。 L F S R 1 2 の 第 3 の出力 2 4 6 は、第 2 の A N D ゲート 2 0 4 の他方の入力 2 4 8 および第 2 の 2 対 1 マルチプレクサ 2 1 6 の第 2 の入力 2 5 0 に接続される。第 2 の A N D ゲート 2 0 4 の出 力252は、第2の2対1マルチプレクサ216の第1の入力254に接続される。第2 の 2 対 1 マルチプレクサ 2 1 6 の出力 2 5 6 は、 4 対 1 マルチプレクサ 2 0 8 の第 3 の入 力 2 5 8 および第 3 の A N D ゲート 2 0 6 の <u>一方</u>の入力 2 6 0 に接続される。 L F S R <u>1</u> 2 の第 4 の出力 2 6 2 は、第 3 の A N D ゲート 2 0 4 の他方の入力 2 6 4 および第 3 の 2 対1マルチプレクサ218の第2の入力266に接続される。第3のANDゲート206 の出力268は、第3の2対1マルチプレクサ218の第1の入力270に接続される。 第 3 の 2 対 1 マルチプレクサ 2 1 8 の出力 2 7 2 は、 4 対 1 マルチプレクサ 2 0 8 の第 4 の入力274に接続される。制御回路222の出力276は、第1の2対1マルチプレク サ 2 1 4 の選択線 2 7 8 、第 2 の 2 対 1 マルチプレクサ 2 1 6 の選択線 2 8 0 、および第 3の2対1マルチプレクサ218の選択線282に接続される。

## [0032]

図4に描かれた一実施形態の回路構成200ではたった1つの制御回路222が挿入されているが、さらなる実施形態(図示せず)では1つ以上の制御回路を含んでもよい。それらさらなる実施形態では、各制御回路は1つ以上の2対1マルチプレクサの選択線に接続されても構わない。このように、選択線上の信号が各2対1マルチプレクサごとに異な

る実施形態があっても構わない。

## [0033]

4対1マルチプレクサ<u>208</u>の2本の選択線(1本のみ図示)284は、重み付けチャンネル回路212の選択出力(1つのみ図示)286に接続されている。4対1マルチプレクサ<u>208</u>の出力288は、XORゲート210の<u>一方</u>の入力290に接続されている。XORゲート<u>210</u>の他方の入力292は、重み付けチャンネル回路<u>212</u>の他の出力294に接続されている。XORゲート<u>210</u>の出力296は、第4の2対1マルチプレクサ<u>220</u>の第1の入力298に接続されている。外部入力300は、第4の2対1マルチプレクサ<u>220</u>の第2の入力302に接続されている。重み付けチャンネル回路<u>212</u>の追加出力304は、第4の2対1マルチプレクサ<u>220</u>の選択線306に接続されている。さらに、<u>図4において</u>図1を参照すると、第4の2対1マルチプレクサ<u>220</u>の出力308は、テストされる集積回路16の入力28に接続されている。

#### [0034]

図4に描かれた回路構成200は、その作動中は、LFSR12からの擬似ランダム4ビットデータパターンを受け取る。4対1マルチプレクサ<u>208</u>の各入力226,242,258<u>,274</u>が受け取る信号が1となる確率は、それぞれ、第1、第2、および第3の<u>各</u>2対1マルチプレクサ214,216,218の<u>各</u>選択線278,280,282上の選択信号に依存する。第1、第2、および第3の<u>各</u>2対1マルチプレクサ<u>214,216,218</u>の各選択線<u>278,280,282</u>上の選択信号が0である場合、第1、第2、および第3の各ANDゲート202,206の各出力236,252<u>,268</u>は、それぞれ、4対1マルチプレクサ208の第2、第3、および第4の各入力242,258<u>,274</u>に、それぞれ接続される。このように、4対1マルチプレクサ<u>208</u>そしてまたXORゲート210から出力される信号の確率は、図3に描かれた回路構成130のものと同じである。

## [0035]

図4の回路構成 200は、第4の2対1マルチプレクサ220<u>の出力308</u>から出力された信号は、重み付けチャンネル回路 212<u>の追加出力304</u>から出力されて第4の2対1マルチプレクサ<u>220</u>の選択線306に入力される出力選択信号に依存するという、さらなる特徴を有している。第4の2対1マルチプレクサ<u>220</u>の選択線<u>306</u>に入力される出力選択信号が0であると、XORゲート2100出力296から出力される信号は、第4の2対1マルチプレクサ<u>220の第1の入力298</u>を介して接続されて、第4の2対1マルチプレクサ<u>220の出力308</u>から出力される。第4の2対1マルチプレクサ<u>22</u>0の選択線<u>306</u>に入力される出力選択信号が1であると、外部入力300上の信号は、第4の2対1マルチプレクサ<u>220</u>の第2の入力302を介して接続されて、第4の2対1マルチプレクサ220の出力308から出力される。

## [0036]

第1、第2、および第3の各2対1マルチプレクサ214,216<u>,218</u>の各選択線278,280<u>,282</u>上の信号がそれぞれ1である場合、LFSR12から出力される第2、第3、および第4のそれぞれのビットは、それぞれ第1、第2、および第3の各2対1マルチプレクサ214,216<u>,218</u>を介して、4対1マルチプレクサ208の第2、第3、および第4の各入力242,258<u>,274</u>にそれぞれ接続される。上述したように、LFSR<u>12</u>から出力される4つのビットのそれぞれが0か1となる確率は2分の1である。このように、LFSR<u>12</u>から出力されて4対1マルチプレクサ<u>208</u>の第1、第2、第3、および第4の各人力226,242,258<u>,274</u>で受け取られる第1、第2、第3、および第4の各ビットが、それぞれ1である確率は、2分の1である。これにより、4対1マルチプレクサ<u>208</u>の選択線(1本を図示)284に入力される信号の状態に拘らず、4対1マルチプレクサ<u>208</u>の選択線(1本を図示)284に入力される信号の状態に拘らず、4対1マルチプレクサ<u>208</u>から出力される信号が1となる確率は、2分の1である。それとともに、XORゲート210から出力される信号に拘らず、2分の1である。

20

30

40

## [0037]

以上議論したように、図4の回路構成200中の第4の2対1マルチプレクサ<u>220</u>の出力308から出力される信号は、重み付けチャンネル回路<u>212</u>の追加出力304から出力されて第4の2対1マルチプレクサ<u>220</u>の選択線306に入力される信号に依存する。第4の2対1マルチプレクサ<u>220</u>の選択線<u>306</u>に入力される信号が0である場合、XORゲート210<u>の出力296</u>から出力される信号は、第4の2対1マルチプレクサ220の出力308から出力される。このように、第4の2対1マルチプレクサ<u>220</u>の出力308から出力される。このように、第4の2対1マルチプレクサ<u>220</u>の選択線<u>306</u>に入力される信号が0であると、XORゲート<u>210の出力296</u>から出力される信号が1となる確率は、2分の1である。対照的に、第4の2対1マルチプレクサ<u>220</u>の選択線<u>306</u>に入力される信号が1であると、XORゲート<u>210の出力296</u>から出力される信号が1となる確率は、2分の10元の300上に現われる信号になるとともに、第4の2対1マルチプレクサ<u>220の出力308</u>から出力される信号が1となる確率は、外部入力300上に現われる信号が1となる確率に依存する。

#### [0038]

このように、第4の2対1マルチプレクサ220<u>の出力308</u>から出力される信号が1となる確率は、重み付けチャンネル回路212の選択出力286および他の出力294からそれぞれ出力される信号、ならびに第1、第2、および第3の各2対1マルチプレクサ214,216<u>,218</u>の各選択線278,280<u>,282</u>にそれぞれ入力される信号と同様に、重み付けチャンネル回路212の追加出力304から出力される信号に依存する。それゆえに、図4に描かれた回路構成200は、選択的に1となる確率を有する出力信号を有利に提示する。このように、本発明に係る一実施形態によれば、テストされる電子回路(集積回路)16の誤りの補償範囲を増大させることにより、I/Oチャンネルを横切ってテストされる電子回路16に渡されるテスト信号を発生させるにあたり、より大きな適応性を提供する。

## [0039]

## [0040]

それとともに、図4の回路構成200は、コンピュータ(図示せず)が制御回路222、重み付けチャンネル回路212、および外部入力300を制御できるという点で有利である。なぜなら、回路構成200はコンピュータにより制御可能であるので、回路構成200によって発生させられてテストされる電子回路16に与えられるパターンは、テストの要求を満足させるために修正可能となるからである。

## [0041]

さらには、様々な技術におけるこれらの技術に対して、この中の発明自身は他の課題や他の応用への適応に対する解決策を提案するものである。本実施形態は、それゆえに実例としての全ての点において考慮されなければならないとともに、限定されるものではない。本発明の範囲は、それらの実施形態には限定されるものではなく、その代わりに添えられたクレームにより、それらの法的に権利を与えられたクレームと同等の最大限の範囲とともに決定されなければならないものである。

## 【図面の簡単な説明】

## [0042]

【図1】STUMPS構造のブロックダイアグラム。

20

30

30

- 【図2】多数の入力ANDゲートを有するテスト中の回路を含むSTUMPS構造のブロックダイアグラム。

- 【図3】従来のプログラム可能な重み付けされたランダムパターン発生装置に含まれる回路構成のブロックダイアグラム。

- 【図4】本発明に係るプログラム可能な重み付けされたランダムパターン発生装置に含まれる回路構成の一実施形態に係るブロックダイアグラム。

### 【符号の説明】

[0043]

1 0 ... L B I S T テスト構成 (電子回路試験装置)、 1 2 ... L F S R (線形フィードバッ クシフトレジスタ)、14... P W R (プログラム可能な重み付けされたランダムパターン 発生装置)、16…テストされる集積回路(電子回路)、18…MISR(多入力シフト レジスタ)、200...PWRに含まれる回路構成(電子回路試験用回路)、202...第1 のANDゲート(他の論理ゲート)、204…第2のANDゲート(他の論理ゲート)、 206…第3のANDゲート(他の論理ゲート)、208…4対1マルチプレクサ(2<sup>n</sup> 対1のマルチプレクサ、第1のマルチプレクサ)、210…XORゲート(出力論理ゲー ト)、212…重み付けチャンネル回路、214…第1の2対1マルチプレクサ(他のマ ルチプレクサ)、216…第2の2対1マルチプレクサ(他のマルチプレクサ)、218 ... 第 3 の 2 対 1 マルチプレクサ ( 他のマルチプレクサ ) 、 2 2 0 ... 第 4 の 2 対 1 マルチプ レクサ(出力マルチプレクサ)、2222…制御回路(少なくとも1つの制御回路)、22 8 ... 第 1 の A N D ゲートの 1 つの入力 (他の論理ゲートの 1 つの入力)、 2 3 6 ... 第 1 の ANDゲートの出力(他の論理ゲートの出力)、244…第2のANDゲートの1つの入 力(他の論理ゲートの1つの入力)、252…第2のANDゲートの出力(他の論理ゲー トの出力)、260…第3のANDゲートの1つの入力(他の論理ゲートの1つの入力) 2 6 8 ... 第 3 の A N D ゲートの出力 ( 他の論理ゲートの出力 ) 、 2 7 8 ... 第 1 の 2 対 1 マルチプレクサの選択線(他のマルチプレクサの選択線)、280…第2の2対1マルチ プレクサの選択線(他のマルチプレクサの選択線)、282…第3の2対1マルチプレク サの選択線(他のマルチプレクサの選択線)、284…4対1マルチプレクサの選択線( 第 1 のマルチプレクサの選択線)、 2 8 6 ... 重み付けチャンネル回路の選択線出力、 2 8 8 ... 4 対 1 マルチプレクサの出力 (第 1 のマルチプレクサの出力)、 2 9 0 ... X O R ゲー トの1つの入力(出力論理ゲートの1つの入力)、292…XORゲートの他の入力(出 力論理ゲートの他の入力)、294…重み付けチャンネル回路の他の出力、296…XO R ゲートの出力(出力論理ゲートの出力)、298...第4の2対1マルチプレクサの1つ の入力(出力マルチプレクサの1つの入力)、300…外部入力、302…第4の2対1 マルチプレクサの他の入力(出力マルチプレクサの他の入力)、304…重み付けチャン ネル回路の追加出力、306…第4の2対1マルチプレクサの選択線(出力マルチプレク サの選択線)

【図1】

【図2】

【図3】

【図4】

### フロントページの続き

(51) Int.CI. F I

G 0 6 F 11/22 3 3 0 F G 0 6 F 11/22 3 6 0 A

(74)代理人 100091351

弁理士 河野 哲

(74)代理人 100088683

弁理士 中村 誠

(74)代理人 100108855

弁理士 蔵田 昌俊

(74)代理人 100084618

弁理士 村松 貞男

(74)代理人 100092196

弁理士 橋本 良郎

(72)発明者 桐生 直樹

アメリカ合衆国、 カリフォルニア州、 サンノゼ、 リンコン・サークル 1060

(72)発明者 ルイス・ブシャード

アメリカ合衆国、 テキサス州、 オースチン、 バーネットロード 11400

## 審査官 森 雅之

(56)参考文献 米国特許第05983380(US,A)

特許第2584172(JP,B2)

特許第3950798(JP,B2)

(58)調査した分野(Int.CI., DB名)

G01R 31/28

G06F 11/22

H01L 21/82

H01L 27/04