# (19) 대한민국특허청(KR)

# (12) 등록특허공보(B1)

(51) 국제특허분류(Int. Cl.)

**H01L 21/768** (2006.01) **H01L 21/28** (2006.01) **H01L 23/48** (2006.01)

(21) 출원번호 **10-2012-0101147**

(22) 출원일자 **2012년09월12일** 심사청구일자 **2017년09월12일**

(65) 공개번호 **10-2014-0034602**

(43) 공개일자 **2014년03월20일**

(56) 선행기술조사문헌 JP05094993 A\* (뒷면에 계속) (45) 공고일자 2018년12월26일

(11) 등록번호 10-1932660

(24) 등록일자 2018년12월19일

(73) 특허권자

## 삼성전자 주식회사

경기도 수워시 영통구 삼성로 129 (매탄동)

(72) 발명자

#### 박재화

경기 용인시 수지구 포은대로 219, 302동 901호 (상현동, 서원마을현대아이파크아파트3단지)

#### 무과지

경기 화성시 영통로50번길 14, 202동 1003호 (반 월동, 신동탄두산위브아파트)

#### 박볏륨

서울 강남구 남부순환로395길 30, 3동 102호 (대 치동, 국제아파트)

(74) 대리인

리앤목특허법인

전체 청구항 수 : 총 15 항

심사관 : 김종희

## (54) 발명의 명칭 TSV 구조를 구비한 집적회로 소자 및 그 제조 방법

## (57) 요 약

집적회로 소자는 반도체 구조물과, 상기 반도체 구조물을 관통하는 TSV (through-silicon-via) 구조를 포함한다. 상기 TSV 구조는 도전성 플러그, 상기 도전성 플러그와 이격되어 배치되고 상기 도전성 플러그를 포위하는 제1 도전성 배리어막, 및 상기 도전성 플러그와 상기 제1 도전성 배리어막과의 사이에 개재되어 있는 절연 박막을 포함한다.

## 대 표 도 - 도1a

(56) 선행기술조사문헌

JP2005026405 A\*

JP2008085126 A\*

JP2010016377 A\*

US20080113505 A1\*

\*는 심사관에 의하여 인용된 문헌

## 명 세 서

## 청구범위

#### 청구항 1

반도체 구조물과,

상기 반도체 구조물을 관통하는 TSV (through-silicon-via) 구조와,

상기 반도체 구조물의 제1 표면 위에 형성된 제1 도전층과,

상기 반도체 구조물의 제1 표면의 반대측인 제2 표면 위에 형성된 제2 도전층을 포함하고,

상기 TSV 구조는

도전성 플러그,

상기 도전성 플러그와 이격되어 배치되고 상기 도전성 플러그를 포위하는 제1 도전성 배리어막, 및

상기 도전성 플러그와 상기 제1 도전성 배리어막과의 사이에 개재되어 있는 절연 박막을 포함하고,

상기 제1 도전층은 상기 도전성 플러그의 일단 및 상기 제1 도전성 배리어막의 일단에 접해 있고,

상기 제2 도전층은 상기 도전성 플러그의 타단 및 상기 제1 도전성 배리어막의 타단에 접해 있고,

상기 도전성 플러그 및 상기 제1 도전성 배리어막은 상기 제1 도전층 및 제2 도전층을 통해 상호 전기적으로 연결되어 있는 것을 특징으로 하는 집적회로 소자.

#### 청구항 2

제1항에 있어서,

상기 도전성 플러그는 제1 금속을 포함하고,

상기 제1 도전성 배리어막은 상기 제1 금속과는 다른 제2 금속을 포함하는 것을 특징으로 하는 집적회로 소자.

## 청구항 3

제1항에 있어서,

상기 반도체 구조물과 제1 도전성 배리어막과의 사이에 개재되어 있는 비아 절연막을 더 포함하는 것을 특징으로 하는 집적회로 소자.

## 청구항 4

제3항에 있어서,

상기 절연 박막의 두께는 상기 비아 절연막의 두께보다 더 얇은 것을 특징으로 하는 집적회로 소자.

## 청구항 5

삭제

## 청구항 6

삭제

## 청구항 7

삭제

### 청구항 8

제1항에 있어서,

상기 도전성 플러그는

상기 절연 박막에 의해 포위되고 상기 반도체 구조물을 관통하는 금속 플러그와,

상기 금속 플러그와 상기 절연 박막과의 사이에서 상기 금속 플러그의 외부 측벽을 포위하는 제2 도전성 배리어막을 포함하는 것을 특징으로 하는 집적회로 소자.

## 청구항 9

제8항에 있어서,

상기 제1 도전성 배리어막은 상기 TSV 구조의 길이 방향을 따라 균일한 두께를 가지고,

상기 제2 도전성 배리어막은 상기 TSV 구조의 길이 방향을 따라 가변적인 두께를 가지는 것을 특징으로 하는 집 적회로 소자.

## 청구항 10

접속 단자를 가지는 패키지 기판과,

상기 패키지 기판 위에 적층된 반도체 칩을 포함하고,

상기 반도체 칩은 반도체 기판과, 상기 반도체 기판을 관통하는 TSV (through-silicon-via) 구조와, 상기 반도체 기판의 제1 표면 위에 형성된 제1 도전층과, 상기 패키지 기판과 상기 반도체 칩과의 사이에서 이들을 상호 전기적으로 연결시키기 위하여 상기 반도체 기판의 상기 제1 표면의 반대측인 제2 표면 위에 형성된 제2 도전층을 포함하고,

상기 TSV 구조는

상기 접속 단자에 연결되어 있는 도전성 플러그,

상기 도전성 플러그와 이격되어 상기 도전성 플러그를 포위하고 상기 접속 단자에 연결되어 있는 제1 도전성 배리어막, 및

상기 도전성 플러그와 상기 제1 도전성 배리어막과의 사이에 개재되어 있는 절연 박막을 포함하고,

상기 제1 도전층은 상기 도전성 플러그의 일단 및 상기 제1 도전성 배리어막의 일단에 접해 있고,

상기 제2 도전층은 상기 도전성 플러그의 타단 및 상기 제1 도전성 배리어막의 타단에 접해 있고,

상기 도전성 플러그 및 상기 제1 도전성 배리어막은 상기 제1 도전층 및 제2 도전층을 통해 상호 전기적으로 연결되어 있는 것을 특징으로 하는 집적회로 소자.

#### 청구항 11

삭제

## 청구항 12

삭제

#### 청구항 13

반도체 구조물에 비아홀 (via hole)을 형성하는 단계와,

상기 비아홀의 내벽을 덮는 비아 절연막을 형성하는 단계와,

상기 비아홀 내에서 상기 비아 절연막 위에 제1 도전성 배리어막을 형성하는 단계와,

상기 비아홀 내에서 상기 제1 도전성 배리어막 위에 절연 박막을 형성하는 단계와,

상기 비아홀 내에서 상기 절연 박막 위에 상기 제1 도전성 배리어막과 이격되어 있는 도전성 플러그를 형성하는 단계와, 상기 반도체 구조물의 제1 표면 위에 상기 도전성 플러그의 일단 및 상기 제1 도전성 배리어막의 일단에 접하는 제1 도전층을 형성하는 단계와,

상기 반도체 구조물의 제1 표면의 반대측인 제2 표면 위에, 상기 도전성 플러그의 타단 및 상기 제1 도전성 배리어막의 타단에 접하는 제2 도전층을 형성하는 단계를 포함하고,

상기 도전성 플러그 및 상기 제1 도전성 배리어막은 상기 제1 도전층 및 제2 도전층을 통해 상호 전기적으로 연결되어 있는 것을 특징으로 하는 집적회로 소자의 제조 방법.

### 청구항 14

제13항에 있어서.

상기 비아 절연막은 상기 비아홀 내에서 제1 두께를 가지도록 형성되고.

상기 절연 박막은 상기 비아홀 내에서 상기 제1 두께 보다 작은 제2 두께를 가지도록 형성되는 것을 특징으로 하는 집적회로 소자의 제조 방법.

### 청구항 15

제13항에 있어서,

상기 제1 도전성 배리어막은 상기 비아홀의 길이 방향을 따라 균일한 두께를 가지도록 형성되는 것을 특징으로 하는 집적회로 소자의 제조 방법.

#### 청구항 16

제13항에 있어서,

상기 절연 박막은 상기 비아홀의 길이 방향을 따라 균일한 두께를 가지도록 형성되는 것을 특징으로 하는 집적 회로 소자의 제조 방법.

#### 청구항 17

제13항에 있어서,

상기 도전성 플러그를 형성하는 단계는

상기 비아홀 내에서 상기 절연 박막 위에 제2 도전성 배리어막을 형성하는 단계와,

상기 비아홀 내에서 상기 제2 도전성 배리어막 위에 금속 플러그를 형성하는 단계를 포함하는 것을 특징으로 하는 집적회로 소자의 제조 방법.

#### 청구항 18

제17항에 있어서,

상기 제2 도전성 배리어막은 상기 비아홀의 입구 근방에서보다 상기 비아홀의 저면 근방에서 더 작은 두께를 가지도록 형성되는 것을 특징으로 하는 집적회로 소자의 제조 방법.

#### 청구항 19

반도체 기판 내에 비아홀을 형성하는 단계와,

상기 비아홀의 내벽을 덮는 비아 절연막을 형성하는 단계와,

상기 비아홀 내에서 상기 비아 절연막 위에 도전성 플러그, 상기 도전성 플러그와 이격되어 상기 도전성 플러그를 포위하는 제1 도전성 배리어막, 및 상기 도전성 플러그와 상기 제1 도전성 배리어막과의 사이에 개재되어 있는 절연 박막을 포함하는 TSV (through-silicon-via) 구조를 형성하는 단계와,

상기 도전성 플러그의 일단으로부터 상기 제1 도전성 배리어막의 일단까지 연장되어 있는 제1 도전층을 상기 TSV 구조의 일측에 형성하는 단계와,

상기 도전성 플러그의 타단으로부터 상기 제1 도전성 배리어막의 타단까지 연장되어 있는 제2 도전층을 상기

TSV 구조의 타측에 형성하는 단계를 포함하고,

상기 도전성 플러그 및 상기 제1 도전성 배리어막은 상기 제1 도전층 및 제2 도전층을 통해 상호 전기적으로 연결되어 있는 것을 특징으로 하는 집적회로 소자의 제조 방법.

## 청구항 20

제19항에 있어서,

상기 TSV 구조를 형성하는 단계는 상기 비아 절연막의 두께보다 작은 두께를 가지는 상기 절연 박막을 형성하는 단계를 포함하는 것을 특징으로 하는 집적회로 소자의 제조 방법.

## 발명의 설명

#### 기술분야

[0001] 본 발명의 기술적 사상은 집적회로 소자 및 그 제조 방법에 관한 것으로, 특히 TSV (through-silicon-via) 구조를 구비한 집적회로 소자 및 그 제조 방법에 관한 것이다.

## 배경기술

[0002] 하나의 반도체 패키지 내에 복수의 반도체 칩을 탑재하는 3D (3-dimensional) 패키지의 개발이 활발해짐에 따라, 기판 또는 다이(die)를 관통하여 수직으로 전기적 접속을 형성하는 TSV (through-silicon-via) 기술이 매우 중요하게 인식되고 있다. 3D 패키지의 성능 및 신뢰도를 향상시키기 위하여는, Cu 콘택 플러그를 포함하는 TSV 구조에서 Cu 확산 현상에 따른 문제점을 해결하고 안정적인 동작 특성 및 높은 신뢰성을 제공할 수 있는 소자의 형성 기술이 필요하다.

## 발명의 내용

#### 해결하려는 과제

- [0003] 본 발명의 기술적 사상이 이루고자 하는 기술적 과제는, 반도체 기판을 관통하는 TSV 구조에서, 상기 TSV 구조를 구성하는 금속 플러그와 상기 반도체 기판과의 전위차로 인해 상기 TSV 구조로부터 금속 이온이 반도체 기판 내부로 확산되는 현상을 방지할 수 있는 구조를 가지는 집적회로 소자를 제공하는 것이다.

- [0004] 본 발명의 기술적 사상이 이루고자 하는 다른 기술적 과제는 TSV 구조를 구성하는 금속 플러그와 반도체 기판과 의 전위차로 인해 상기 TSV 구조로부터 금속 이온이 반도체 기판 내부로 확산되는 현상을 방지할 수 있는 구조를 가지는 집적회로 소자의 제조 방법을 제공하는 것이다.

## 과제의 해결 수단

- [0005] 본 발명의 기술적 사상에 의한 일 양태에 따른 집적회로 소자는 반도체 구조물과, 상기 반도체 구조물을 관통하는 TSV (through-silicon-via) 구조를 포함한다. 상기 TSV 구조는 도전성 플러그, 상기 도전성 플러그와 이격되어 배치되고 상기 도전성 플러그를 포위하는 제1 도전성 배리어막, 및 상기 도전성 플러그와 상기 제1 도전성 배리어막과의 사이에 개재되어 있는 절연 박막을 포함한다.

- [0006] 본 발명의 기술적 사상에 의한 다른 양태에 따른 집적회로 소자는 접속 단자를 가지는 패키지 기판과, 상기 패키지 기판 위에 적충되어 있고, 반도체 기판과, 상기 반도체 기판을 관통하는 TSV 구조를 포함하는 적어도 하나의 반도체 칩을 포함하고, 상기 TSV 구조는 도전성 플러그, 상기 도전성 플러그와 이격되어 상기 도전성 플러그를 포위하는 제1 도전성 배리어막, 및 상기 도전성 플러그와 상기 제1 도전성 배리어막과의 사이에 개재되어 있는 절연 박막을 포함한다.

- [0007] 본 발명의 기술적 사상에 의한 일 양태에 따른 집적회로 소자의 제조 방법에서는, 반도체 구조물에 비아홀을 형성한다. 상기 비아홀의 내벽을 덮는 비아 절연막을 형성한다. 상기 비아홀 내에서 상기 비아 절연막 위에 제1 도전성 배리어막을 형성한다. 상기 비아홀 내에서 상기 제1 도전성 배리어막 위에 절연 박막을 형성한다. 상기비아홀 내에서 상기 절연 박막 위에 상기 제1 도전성 배리어막과 이격되어 있는 도전성 플러그를 형성한다.

- [0008] 본 발명의 기술적 사상에 의한 다른 양태에 따른 집적회로 소자의 제조 방법에서는, 반도체 기판 내에 비아홀을 형성한다. 상기 비아홀의 내벽을 덮는 비아 절연막을 형성한다. 상기 비아홀 내에서 상기 비아 절연막 위에 도

전성 플러그, 상기 도전성 플러그와 이격되어 상기 도전성 플러그를 포위하는 제1 도전성 배리어막, 및 상기 도전성 플러그와 상기 제1 도전성 배리어막과의 사이에 개재되어 있는 절연 박막을 포함하는 TSV 구조를 형성한다. 상기 도전성 플러그의 일단으로부터 상기 제1 도전성 배리어막의 일단까지 연장되어 있는 제1 도전층을 상기 TSV 구조의 일측에 형성한다.

# 발명의 효과

[0009] 본 발명의 기술적 사상에 의한 집적회로 소자는 TSV 구조에서는 절연 박막을 사이에 두고 이격되어 있는 금속 플러그 및 도전성 배리어막을 포함한다. 상기 TSV 구조에서 상기 금속 플러그 및 도전성 배리어막에 연결되어 있는 배선을 통해 상기 TSV 구조에 전압이 인가될 때 상기 금속 플러그 및 도전성 배리어막이 상호 등전위로 될 수 있다. 따라서, TSV 구조의 금속 플러그와 반도체 기판과의 사이에 전위차가 발생하는 경우에도 상기 금속 플러그 주위에는 상기 금속 플러그와 등전위를 갖는 도전성 배리어가 존재하므로, 상기 TSV 구조로부터 반도체 기판 내부로의 금속 이온의 확산을 전기적으로 차폐할 수 있다.

## 도면의 간단한 설명

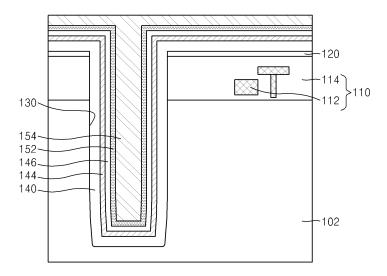

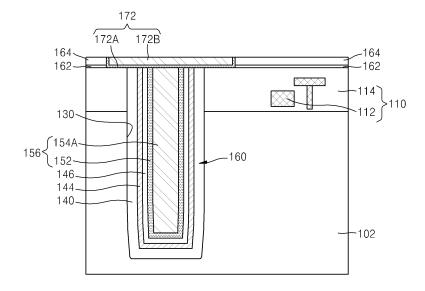

[0010] 도 1a는 본 발명의 기술적 사상에 의한 일 실시예에 따른 집적회로 소자를 설명하기 위한 단면도이다.

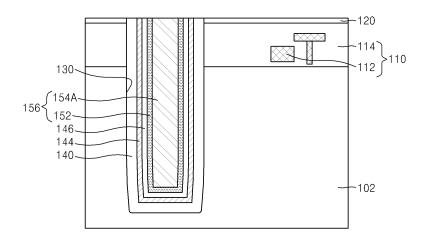

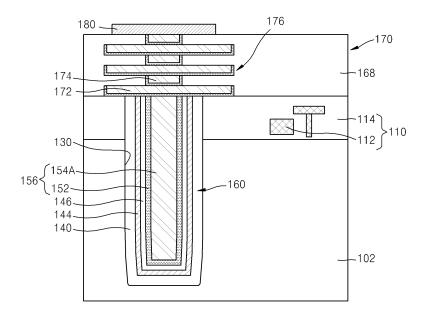

도 1b는 본 발명의 기술적 사상에 의한 다른 실시예에 따른 집적회로 소자를 설명하기 위한 단면도이다.

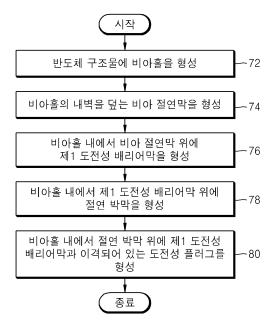

도 2는 본 발명의 기술적 사상에 의한 실시예들에 따른 집적회로 소자의 제조 방법을 설명하기 위한 플로차트이다.

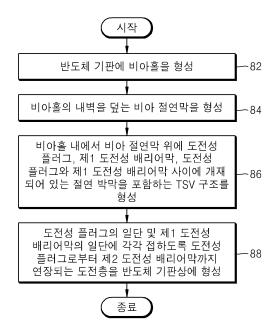

도 3은 본 발명의 기술적 사상에 의한 다른 실시예들에 따른 집적회로 소자의 제조 방법을 설명하기 위한 플로 차트이다.

도 4a 내지 도 4n은 본 발명의 기술적 사상에 의한 일 실시예에 따른 집적회로 소자의 제조 방법을 설명하기 위하여 공정 순서에 따라 도시한 단면도들이다.

도 5는 본 발명의 기술적 사상에 의한 실시예들에 따른 집적회로 소자의 요부 구성을 도시한 단면도이다.

도 6은 본 발명의 기술적 사상에 의한 실시예들에 따른 집적회로 소자의 요부 구성을 도시한 단면도이다.

도 7은 본 발명의 기술적 사상에 의한 실시예들에 따른 집적회로 소자의 요부 구성을 도시한 단면도이다.

도 8은 본 발명의 기술적 사상에 의한 실시예들에 따른 집적회로 소자의 요부 구성을 도시한 단면도이다.

도 9는 본 발명의 기술적 사상에 의한 실시예들에 따른 집적회로 소자의 요부 구성을 도시한 단면도이다.

도 10a 내지 도 10k는 본 발명의 기술적 사상에 의한 일 실시예에 따른 집적회로 소자의 제조 방법을 설명하기 위한 단면도들이다.

도 11은 본 발명의 기술적 사상에 의한 실시예들에 따른 집적회로 소자의 요부 구성을 보여주는 단면도이다.

도 12는 본 발명의 기술적 사상에 의한 실시예들에 따른 집적회로 소자의 요부 구성을 보여주는 단면도이다.

도 13은 본 발명의 기술적 사상에 의한 실시예들에 따른 집적회로 소자의 요부 구성을 보여주는 평면도이다.

도 14는 본 발명의 기술적 사상에 의한 실시예들에 따른 집적회로 소자의 요부 구성을 보여주는 다이어그램이다.

#### 발명을 실시하기 위한 구체적인 내용

[0011] 이하, 첨부 도면을 참조하여 본 발명의 실시예들을 상세히 설명한다. 도면상의 동일한 구성요소에 대해서는 동일한 참조부호를 사용하고, 이들에 대한 중복된 설명은 생략한다.

[0012] 본 발명의 실시예들은 당해 기술 분야에서 통상의 지식을 가진 자에게 본 발명을 더욱 완전하게 설명하기 위하여 제공되는 것으로, 아래의 실시예들은 여러 가지 다른 형태로 변형될 수 있으며, 본 발명의 범위가 아래의 실시예들로 한정되는 것은 아니다. 오히려, 이들 실시예는 본 개시를 더욱 충실하고 완전하게 하며 당업자에게 본 발명의 사상을 완전하게 전달하기 위하여 제공되는 것이다.

[0013] 본 명세서에서 제1, 제2 등의 용어가 다양한 부재, 영역, 층들, 부위 및/또는 구성 요소들을 설명하기 위하여

사용되지만, 이들 부재, 부품, 영역, 층들, 부위 및/또는 구성 요소들은 이들 용어에 의해 한정되어서는 안 됨은 자명하다. 이들 용어는 특정 순서나 상하, 또는 우열을 의미하지 않으며, 하나의 부재, 영역, 부위, 또는 구성 요소를 다른 부재, 영역, 부위 또는 구성 요소와 구별하기 위하여만 사용된다. 따라서, 이하 상술할 제1 부재, 영역, 부위 또는 구성 요소는 본 발명의 가르침으로부터 벗어나지 않고서도 제2 부재, 영역, 부위 또는 구성 요소를 지칭할 수 있다. 예를 들어, 본 발명의 권리 범위로부터 이탈되지 않은 채 제1 구성 요소는 제2 구성 요소로 명명될 수 있다.

- [0014] 달리 정의되지 않는 한, 여기에 사용되는 모든 용어들은 기술 용어와 과학 용어를 포함하여 본 발명 개념이 속하는 기술 분야에서 통상의 지식을 가진 자가 공통적으로 이해하고 있는 바와 동일한 의미를 지닌다. 또한, 통상적으로 사용되는, 사전에 정의된 바와 같은 용어들은 관련되는 기술의 맥락에서 이들이 의미하는 바와 일관되는 의미를 갖는 것으로 해석되어야 하며, 여기에 명시적으로 정의하지 않는 한 과도하게 형식적인 의미로 해석되어서는 아니 될 것임은 이해될 것이다.

- [0015] 어떤 실시예가 달리 구현 가능한 경우에 특정한 공정 순서는 설명되는 순서와 다르게 수행될 수도 있다. 예를 들어, 연속하여 설명되는 두 공정이 실질적으로 동시에 수행될 수도 있고, 설명되는 순서와 반대의 순서로 수행될 수도 있다.

- [0016] 첨부 도면에 있어서, 예를 들면, 제조 기술 및/또는 공차에 따라, 도시된 형상의 변형들이 예상될 수 있다. 따라서, 본 발명의 실시예들은 본 명세서에 도시된 영역의 특정 형상에 제한된 것으로 해석되어서는 아니 되며, 예를 들면 제조 과정에서 초래되는 형상의 변화를 포함하여야 한다.

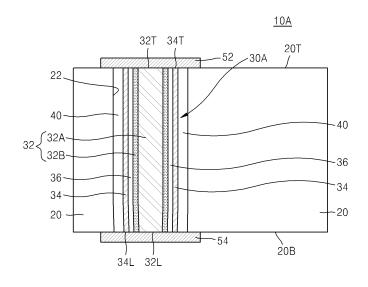

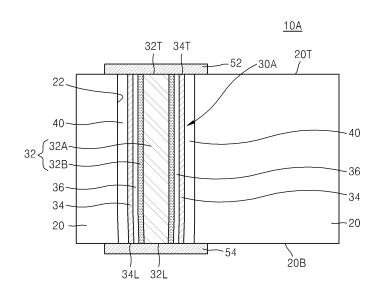

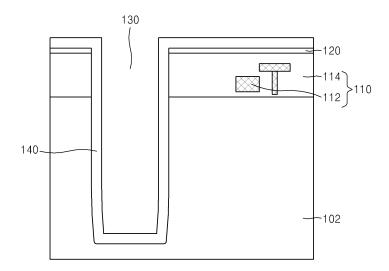

- [0017] 도 1a는 본 발명의 기술적 사상에 의한 일 실시예에 따른 집적회로 소자(10A)를 설명하기 위한 단면도이다.

- [0018] 도 1a를 참조하면, 집적회로 소자(10A)는 반도체 구조물(20)과, 상기 반도체 구조물(20)에 형성된 비아홀(22)을 통해 상기 반도체 구조물(20)을 관통하는 TSV (through-silicon-via) 구조(30A)를 포함한다.

- [0019] 상기 TSV 구조(30A)는 도전성 플러그(32)와, 상기 도전성 플러그(32)와 이격된 위치에서 상기 도전성 플러그 (32)를 포위하는 제1 도전성 배리어막(34)을 포함한다. 상기 도전성 플러그(32)와 상기 제1 도전성 배리어막 (34)과의 사이에는 절연 박막(36)이 개재되어 있다.

- [0020] 상기 도전성 플러그(32)는 상기 반도체 구조물(20)을 관통하는 금속 플러그(32A)와, 상기 금속 플러그(32A)의 외부 측벽을 포위하면서 상기 반도체 구조물(20)을 관통하는 제2 도전성 배리어막(32B)을 포함한다. 상기 제2 도전성 배리어막(32B)은 상기 금속 플러그(32A)와 절연 박막(36)과의 사이에 개재되어 있다. 일부 실시예들에서, 상기 제2 도전성 배리어막(32B)은 생략될 수 있으며, 상기 금속 플러그(32A)와 상기 절연 박막(36)이 직접 접촉할 수 있다.

- [0021] 상기 금속 플러그(32A)는 제1 금속을 포함하고, 상기 제1 도전성 배리어막(34) 및 제2 도전성 배리어막(32A)은 각각 상기 제1 금속과는 다른 금속을 포함할 수 있다.

- [0022] 일부 실시예들에서, 상기 금속 플러그(32A)는 Cu 또는 W을 포함할 수 있다. 예를 들면, 상기 금속 플러그(32A)는 Cu, CuSn, CuMg, CuNi, CuZn, CuPd, CuAu, CuRe, CuW, W, 또는 W 합금으로 이루어질 수 있으나, 이에 제한되는 것은 아니다.

- [0023] 상기 금속 플러그(32A)의 측벽을 포위하는 제2 도전성 배리어막(32B)은 W, WN, WC, Ti, TiN, Ta, TaN, Ru, Co, Mn, WN, Ni, 또는 NiB 중에서 선택되는 적어도 하나의 물질을 포함하는 단일막 또는 다중막으로 이루어질 수 있다. 일부 실시예들에서, 상기 제2 도전성 배리어막(32B)은 PVD (physical vapor deposition) 공정 또는 CVD (chemical vapor deposition) 공정에 의해 형성될 수 있다. 다른 일부 실시예들에서, 상기 제2 도전성 배리어막(32B)은 ALD (atomic layer deposition) 공정에 의해 형성될 수도 있다.

- [0024] 일부 실시예들에서, 상기 제2 도전성 배리어막(32B)은 상기 TSV 구조(30A)의 길이 방향을 따라 대략 균일한 두 께를 가질 수 있다. 여기서, TSV 구조(30A)의 길이 방향은 반도체 구조물(20)의 제1 표면(20T)으로부터 그 반대 측인 제2 표면(20B) 까지의 최단 길이 방향을 의미한다. 본 명세서에서, 비아홀(22)의 길이 방향과 TSV 구조(30A)의 길이 방향은 동일한 의미로 사용된다.

- [0025] 상기 제1 도전성 배리어막(34)은 비교적 낮은 배선 저항을 가지는 도전층으로 이루어질 수 있다. 예를 들면, 상기 제1 도전성 배리어막(34)은 W, WN, Ti, TiN, Ta, TaN, 및 Ru 중에서 선택되는 적어도 하나를 포함하는 단일 막 또는 다중막으로 이루어질 수 있다. 예를 들면, 상기 제1 도전성 배리어막(34)은 TaN/W, TiN/W, 또는 WN/W로 이루어지는 다중막으로 이루어질 수 있다. 상기 제1 도전성 배리어막(34)은 약 50 ~ 1000 Å의 두께를 가질 수

있다. 일부 실시예들에서, 상기 제1 도전성 배리어막(34)은 상기 TSV 구조(30A)의 길이 방향을 따라 대략 균일한 두께를 가질 수 있다. 상기 제1 도전성 배리어막(34)은 ALD (atomic layer deposition) 공정 또는 CVD 공정에 의해 형성될 수 있다.

- [0026] 상기 절연 박막(36)은 상기 도전성 플러그(32)를 포위하는 실린더형 구조를 가진다. 상기 절연 박막(36)은 산화막, 질화막, 절연성 금속 산화막, 고유전막, 폴리머, 또는 이들의 조합으로 이루어질 수 있다. 상기 절연 박막(36)은 TSV 구조(30A)의 길이 방향을 따라 대략 균일한 두께를 가지는 고밀도 박막으로 형성될 수 있다. 예를 들면, 상기 절연 박막(36)은 ALD 공정에 의해 얻어지는 박막으로 이루어질 수 있다.

- [0027] 상기 절연 박막(36)은 실리콘 산화막보다 높은 유전 상수를 가지는 고유전막으로 이루어질 수 있다. 예를 들면, 상기 절연 박막(36)은 약 10 내지 25의 유전 상수를 가질 수 있다. 일부 실시예들에서, 상기 절연 박막(36)은 하프늄 산화물(HfO), 하프늄 실리콘 산화물(HfSiO), 하프늄 산화물(HfSiON), 하프늄 실리콘 산화 질화물(HfSiON), 란타늄 산화물(LaO), 란탄늄 알루미늄 산화물(LaAlO), 지르코늄 산화물(ZrO), 지르코늄 실리콘 산화물(ZrSiO), 지르코늄 산화 질화물(ZrON), 지르코늄 실리콘 산화물(ZrSiON), 타탈륨 산화물(TaO), 타타늄 산화물(TiO), 바륨 스트론튬 티타늄 산화물(BaSrTiO), 바륨 티타늄 산화물(BaTiO), 스트론튬 티타늄 산화물(SrTiO), 이트륨 산화물(YO), 알루미늄 산화물(AlO), 또는 납 스칸듐 탄탈륨 산화물(PbScTaO) 중에서 선택되는 적어도 하나의 물질로 이루어질 수 있다.

- [0028] 집적회로 소자(10A)는 상기 반도체 구조물(20)과 제1 도전성 배리어막(34)과의 사이에 개재되어 있는 비아 절연막(40)을 더 포함한다. 상기 비아 절연막(40)은 상기 반도체 구조물(20)과 상기 TSV 구조(30A)를 이격시킨다.

- [0029] 상기 비아 절연막(40)은 산화막, 질화막, 탄화막, 폴리머, 또는 이들의 조합으로 이루어질 수 있다. 일부 실시 예들에서, 상기 비아 절연막(40)을 형성하기 위하여 CVD 공정을 이용할 수 있다. 상기 비아 절연막(40)은 약 500 ~ 2500 Å의 두께를 가지도록 형성될 수 있다.

- [0030] 상기 절연 박막(36)은 상기 제1 도전성 배리어막(34)을 사이에 두고 상기 비아 절연막(40)과 이격되어 있다. 상기 TSV 구조(30A) 내에서의 저항을 최소화하기 위하여, 상기 절연 박막(36)의 두께는 가능한 한 얇게 형성할 수 있다. 일부 실시예들에서, 상기 절연 박막(36)의 두께는 상기 비아 절연막(40)의 두께보다 더 얇다. 일부 실시예들에서, 상기 절연 박막(36)은 약 50 ~ 1000 Å의 두께를 가질 수 있다.

- [0031] 상기 반도체 구조물(20)의 제1 표면(20T) 위에는 상기 도전성 플러그(32)의 일단(32T) 및 상기 제1 도전성 배리어막(34)의 일단(34T)에 각각 접해 있는 제1 도전층(52)이 형성되어 있다. 상기 반도체 구조물(20)의 제2 표면(20B) 위에는 상기 도전성 플러그(32)의 타단(32L) 및 상기 제1 도전성 배리어막(34)의 타단(34L)에 각각 접해 있는 제2 도전층(54)이 형성되어 있다. 상기 TSV 구조(30A)에 전압이 인가될 때 상기 도전성 플러그(32) 및 상기 제1 도전성 배리어막(34)이 상호 등전위로 될 수 있도록 상기 도전성 플러그(32) 및 상기 제1 도전성 배리어막(34)은 각각 상기 제1 도전층(52) 및 제2 도전층(54)을 통해 상호 전기적으로 연결되어 있다.

- [0032] 상기 제1 도전층(52) 및 제2 도전층(54)은 각각 금속으로 이루어질 수 있다. 상기 도전성 플러그(32) 및 제1 도전성 배리어막(34)이 각각 상기 제1 도전층(52) 및 제2 도전층(54)에 연결되어 있으므로, 상기 제1 도전층(52) 및 제2 도전층(54) 중 어느 하나의 도전층으로부터 상기 도전성 플러그(32)에 공급되는 전압은 상기 도전성 플러그(32) 및 제1 도전성 배리어막(34)으로 동시에 공급되어 상기 도전성 플러그(32) 및 제1 도전성 배리어막(34)은 등전위 상태로 될 수 있다. 예를 들면, 상기 도전성 플러그(32)가 Cu 이온과 같이 전위차에 의해 쉽게 확산되는 금속 이온을 포함하는 경우, 절연 박막(36)을 사이에 두고 상기 도전성 플러그(32)와 등전위를 갖는 제1 도전성 배리어막(34)이 상기 도전성 플러그(32)를 포위하고 있으므로, 상기 도전성 플러그(32)로부터 금속 이온이 전위차에 의해 반도체 구조물(20) 내부로 확산되는 것을 전기적으로 차폐할 수 있다. 따라서, 금속 이온이 전위차에 의해 상기 반도체 구조물(20) 내부로 확산됨으로써 발생될 수 있는 문제들, 예를 들면 트랜지스터 등과 같은 단위 소자들의 동작 특성의 열화, 비아 절연막(40) 내부까지 확산된 금속 이온들이 비아 절연막(40) 내에서 트랩 사이트로 작용함으로써 약기되는 TSV 구조(30A)의 신뢰성 저하 등과 같은 문제점들을 방지할 수 있다.

- [0033] 일부 실시예들에서, 상기 반도체 구조물(20)은 반도체 기판, 예를 들면 실리콘 기판으로 이루어질 수 있다. 그리고, 상기 TSV 구조(30A)는 상기 반도체 기판에 의해 포위되는 측벽을 가질 수 있다.

- [0034] 다른 일부 실시예들에서, 상기 반도체 구조물(20)은 반도체 기판과, 상기 반도체 기판을 덮는 충간절연막을 포함할 수 있다. 상기 TSV 구조(30A)를 구성하는 도전성 플러그(32), 절연 박막(36), 및 제1 도전성 배리어막(34)은 각각 상기 반도체 기판 및 충간절연막을 관통할 수 있다. 상기 TSV 구조(30A)는 상기 반도체 기판에 의해

포위되는 측벽 부분과, 상기 충간절연막에 의해 포위되는 측벽 부분을 가질 수 있다.

- [0035] 또 다른 일부 실시예들에서, 상기 반도체 구조물(20)은 반도체 기판과, 상기 반도체 기판을 덮는 층간절연막과, 상기 층간절연막을 덮는 금속층간절연막을 포함할 수 있다. 상기 TSV 구조(30A)를 구성하는 도전성 플러그(32), 절연 박막(36), 및 제1 도전성 배리어막(34)은 각각 상기 반도체 기판, 층간절연막, 및 금속층간절연막을 관통할 수 있다. 그리고, TSV 구조(30A)의 도전성 플러그(32), 절연 박막(36), 및 제1 도전성 배리어막(34)은 상기 반도체 기판에 의해 포위되는 측벽 부분과, 상기 층간절연막에 의해 포위되는 측벽 부분과, 상기 금속층간절연막에 의해 포위되는 측벽 부분을 가질 수 있다.

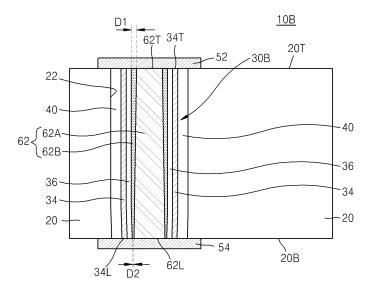

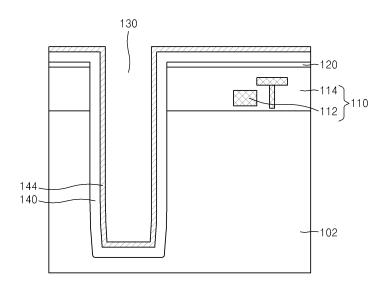

- [0036] 도 1b는 본 발명의 기술적 사상에 의한 다른 실시예에 따른 집적회로 소자(10B)를 설명하기 위한 단면도이다. 도 1b에서, 도 1a에서와 동일한 참조 부호는 동일 부재를 나타내며, 따라서 여기서는 이들에 대한 상세한 설명은 생략한다.

- [0037] 도 1b를 참조하면, 집적회로 소자(10B)는 반도체 구조물(20)과, 상기 반도체 구조물(20)에 형성된 비아홀(22)을 통해 상기 반도체 구조물(20)을 관통하는 TSV 구조(30B)를 포함한다.

- [0038] 상기 TSV 구조(30B)는 도전성 플러그(62), 상기 도전성 플러그(62)와 이격된 위치에서 상기 도전성 플러그(62)를 포위하는 제1 도전성 배리어막(34), 및 상기 도전성 플러그(62)와 상기 제1 도전성 배리어막(34)과의 사이에 개재되어 있는 절연 박막(36)을 포함한다.

- [0039] 상기 도전성 플러그(62)는 상기 반도체 구조물(20)을 관통하는 금속 플러그(62A)와, 상기 금속 플러그(62A)의 외부 측벽을 포위하면서 상기 반도체 구조물(20)을 관통하는 제2 도전성 배리어막(62B)을 포함한다.

- [0040] 상기 제1 도전성 배리어막(34)은 상기 반도체 구조물(20)의 제1 표면(20T)으로부터 제2 표면(20B)에 이르기까지 TSV 구조(30B)의 길이 방향을 따라 대략 균일한 두께를 가질 수 있다. 예를 들면, 상기 제1 도전성 배리어막(34)은 약 50 ~ 1000 Å의 범위 내에서 선택되는 두께를 가질 수 있다. 이와 같이, 상기 비아홀(22)의 길이 방향을 따라 균일한 두께를 가지는 상기 제1 도전성 배리어막(34)을 형성하기 위하여 ALD 공정을 이용할 수 있다.

- [0041] 상기 제2 도전성 배리어막(62B)은 상기 반도체 구조물(20)의 제1 표면(20T) 측으로부터 제2 표면(20B) 측에 가까워질수록 점차 얇아지는 두께를 가진다. 예를 들면, 상기 제2 도전성 배리어막(62B)은 상기 비아홀(22) 내에서 상기 반도체 구조물(20)의 제1 표면(20T) 측 입구 부근에서는 약 100 ~ 1000 Å의 제1 두께(D1)를 가지고, 상기 비아홀(22) 내에서 상기 반도체 구조물(20)의 제2 표면(20B) 측 입구 부근에서는 약 0 ~ 50 Å의 제2 두 께(D2)를 가질 수 있다. 이와 같이 비아홀(22)의 길이 방향을 따라 가변적인 두께를 가지는 상기 제2 도전성 배리어막(62B)을 형성하기 위하여 PVD 공정을 이용할 수 있다.

- [0042] 도 2는 본 발명의 기술적 사상에 의한 실시예들에 따른 집적회로 소자의 제조 방법을 설명하기 위한 플로차트이다. 이하의 설명에서, 도 1a 및 도 1b를 참조하여 설명한 구성 요소들에 대하여는 중복 설명을 생략한다.

- [0043] 도 1a 및 도 1b와 도 2를 참조하면, 공정 72에서, 반도체 구조물(20)에 비아홀(22)을 형성한다.

- [0044] 공정 74에서, 상기 비아홀(22)의 내벽을 덮는 비아 절연막(40)을 형성한다. 상기 비아 절연막(40)을 형성하기 위하여 저온 CVD 공정 또는 PECVD (plasma enhanced CVD) 공정을 행할 수 있다.

- [0045] 공정 76에서, 상기 비아홀(22) 내에서 상기 비아 절연막(40) 위에 제1 도전성 배리어막(34)을 형성한다. 상기 제1 도전성 배리어막(34)을 형성하기 위하여, 비교적 저온에서 균일한 두께를 가지는 저저항의 고밀도 박막을 형성할 수 있는 ALD 공정 또는 CVD 공정을 이용할 수 있다. 상기 제1 도전성 배리어막(34)은 상기 반도체 구조 물(20)의 제1 표면(20T)으로부터 제2 표면(20B)에 이르기까지 비아홀(22)의 길이 방향을 따라 대략 균일한 두께를 가지도록 형성될 수 있다.

- [0046] 공정 78에서, 상기 비아홀(22) 내에서 상기 제1 도전성 배리어막(34) 위에 절연 박막(36)을 형성한다. 상기 절연 박막(36)은 상기 비아 절연막(40)보다 작은 두께를 가지도록 형성된다. 상기 절연 박막(36)을 형성하기 위하여 ALD 공정 또는 CVD 공정을 이용할 수 있다.

- [0047] 공정 80에서, 상기 비아홀(22) 내에서 상기 절연 박막(36) 위에 상기 제1 도전성 배리어막(34)과 이격되어 있는 도전성 플러그(32 또는 62)를 형성한다.

- [0048] 일부 실시예들에서, 도 1a에 예시한 바와 같이, 상기 비아홀(22)의 길이 방향을 따라 대략 균일한 두께를 가지는 제2 도전성 배리어막(32B)과, 상기 제2 도전성 배리어막(32B) 위에 남아 있는 상기 비아홀(22)의 남은 공간을 채우는 금속 플러그(32A)를 포함하는 도전성 플러그(32)를 형성할 수 있다.

- [0049] 다른 일부 실시예들에서, 도 1b에 예시한 바와 같이, 상기 비아홀(22)의 길이 방향을 따라 가변적인 두께를 가지는 상기 제2 도전성 배리어막(62B)과, 상기 제2 도전성 배리어막(62B) 위에 남아 있는 상기 비아홀(22)의 남은 공간을 채우는 금속 플러그(62A)를 포함하는 도전성 플러그(62)를 형성할 수 있다.

- [0050] 도 3은 본 발명의 기술적 사상에 의한 다른 실시예들에 따른 집적회로 소자의 제조 방법을 설명하기 위한 플로 차트이다. 이하의 설명에서, 도 1a 및 도 1b를 참조하여 설명한 구성 요소들에 대하여는 중복 설명을 생략한다.

- [0051] 도 1a 및 도 1b와 도 3을 참조하면, 공정 82에서, 반도체 기판에 비아홀(22)을 형성한다. 상기 반도체 기판은 도 1a 및 도 1b에 예시한 반도체 구조물(20)을 구성할 수 있다.

- [0052] 공정 84에서, 도 2의 공정 74에서와 같은 방법으로, 상기 비아홀(22)의 내벽을 덮는 비아 절연막(40)을 형성한다.

- [0053] 공정 86에서, 상기 비아홀(22) 내에서 상기 비아 절연막(40) 위에 TSV 구조(30A 또는 30B)를 형성한다.

- [0054] 일부 실시예들에서, 도 1a에 예시한 바와 같이, 상기 비아홀(22)의 길이 방향을 따라 대략 균일한 두께를 가지는 제2 도전성 배리어막(32B)을 포함하는 도전성 플러그(32), 상기 도전성 플러그(32)와 이격된 위치에서 상기 도전성 플러그(32)를 포위하는 제1 도전성 배리어막(34), 및 상기 도전성 플러그(32)와 상기 제1 도전성 배리어막(34)과의 사이에 개재되어 있는 절연 박막(36)을 포함하는 TSV 구조(30A)를 형성할 수 있다.

- [0055] 다른 일부 실시예들에서, 도 1b에 예시한 바와 같이, 상기 비아홀(22)의 길이 방향을 따라 가변적인 두께를 가지는 제2 도전성 배리어막(62B)을 포함하는 도전성 플러그(62), 상기 도전성 플러그(62)와 이격된 위치에서 상기 도전성 플러그(62)를 포위하는 제1 도전성 배리어막(34), 및 상기 도전성 플러그(62)와 상기 제1 도전성 배리어막(34)과의 사이에 개재되어 있는 절연 박막(36)을 포함하는 TSV 구조(30B)를 형성할 수 있다.

- [0056] 공정 88에서, 상기 도전성 플러그(32 또는 62)의 일단(32T 또는 62T) 및 상기 제1 도전성 배리어막(34)의 일단 (34T)에 각각 접하도록 상기 도전성 플러그(32 또는 62)로부터 상기 제1 도전성 배리어막(34)까지 연장되는 제1 도전층(52)을 상기 반도체 기판 위에 형성한다.

- [0057] 일부 실시예들에서, 상기 도전성 플러그(32 또는 62)의 타단(32L 또는 62L) 및 상기 제1 도전성 배리어막(34)의 타단(34L)에 각각 접하도록 상기 도전성 플러그(32 또는 62)로부터 상기 제1 도전성 배리어막(34)까지 연장되는 제2 도전층(54)을 상기 반도체 기판 위에 더 형성할 수 있다.

- [0058] 이하, 도 1a 및 도 1b에 예시한 집적회로 소자(10A, 10B)와, 도 2 및 도 3에 각각 예시한 집적회로 소자의 제조 방법들에 대하여 보다 구체적인 예를 들어 상세히 설명한다.

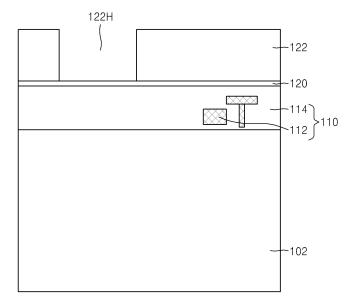

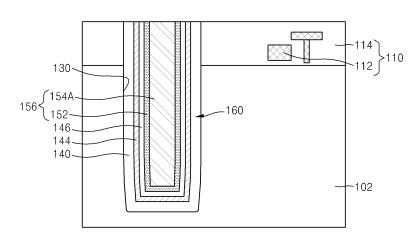

- [0059] 도 4a 내지 도 4n은 본 발명의 기술적 사상에 의한 일 실시예에 따른 집적회로 소자(100) (도 4n 참조)의 제조 방법을 설명하기 위하여 공정 순서에 따라 도시한 단면도들이다.

- [0060] 도 4a를 참조하면, 기판(102)상에 FEOL (front-end-of-line) 구조(110)를 형성하고, 상기 FEOL 구조(110) 위에 제1 연마 정지층(120)을 형성한 후, 상기 제1 연마 정지층(120) 위에 마스크 패턴(122)을 형성한다. 상기 마스크 패턴(122)에는 상기 제1 연마 정지층(120)의 상면을 일부 노출시키는 홀(122H)이 형성되어 있다.

- [0061] 일부 실시예들에서, 상기 기판(102)은 반도체 웨이퍼이다. 적어도 일 실시예에서, 상기 기판(102)은 Si (silicon)을 포함한다. 다른 일부 실시예에서, 상기 기판(102)은 Ge (germanium)과 같은 반도체 원소, 또는 SiC (silicon carbide), GaAs (gallium arsenide), InAs (indium arsenide), 및 InP (indium phosphide)와 같은 화합물 반도체를 포함할 수 있다. 적어도 하나의 실시예에서, 상기 기판(102)은 SOI (silicon on insulator) 구조를 가질 수 있다. 예를 들면, 상기 기판(102)은 BOX 층 (buried oxide layer)을 포함할 수 있다. 일부 실시예들에서, 상기 기판(102)은 도전 영역, 예를 들면 불순물이 도핑된 웰 (well), 또는 불순물이 도핑된 구조물을 포함할 수 있다. 또한, 상기 기판(102)은 STI (shallow trench isolation) 구조와 같은 다양한 소자분리 구조를 가질 수 있다.

- [0062] 상기 FEOL 구조(110)는 다양한 종류의 복수의 개별 소자 (individual devices)(112)와 충간절연막(114)을 포함한다. 상기 복수의 개별 소자(112)는 다양한 미세 전자 소자 (microelectronic devices), 예를 들면 MOSFET (metal-oxide-semiconductor field effect transistor), 시스템 LSI (large scale integration), CIS (CMOS imaging sensor) 등과 같은 이미지 센서, MEMS (micro-electro-mechanical system), 등동 소자, 수동 소자 등을 포함할 수 있다. 상기 복수의 개별 소자(112)는 상기 기판(102)의 도전 영역에 전기적으로 연결될 수 있다. 또한, 상기 복수의 개별 소자(112)는 각각 상기 충간절연막(114)에 의해 이웃하는 다른 개별 소자들과 전기적으

로 분리될 수 있다.

- [0063] 일부 실시예에서, 상기 제1 연마 정지층(120)은 실리콘 질화막으로 이루어질 수 있다. 상기 제1 연마 정지층 (120)은 약 200 ~ 1000 Å의 두께를 가지도록 형성될 수 있다. 상기 제1 연마 정지층(120)을 형성하기 위하여 CVD 공정을 이용할 수 있다.

- [0064] 상기 마스크 패턴(122)은 포토레지스트 재료로 이루어질 수 있다.

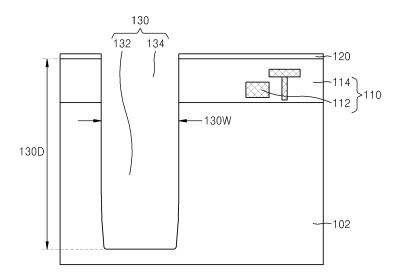

- [0065] 도 4b를 참조하면, 상기 마스크 패턴(122) (도 4a 참조)을 식각 마스크로 이용하여 상기 제1 연마 정지층(120) 및 층간절연막(114)을 식각하고, 이어서 상기 기판(102)을 식각하여 비아홀(130)을 형성한다. 상기 비아홀(130)은 상기 기판(102)에 소정 깊이로 형성된 형성된 제1 홀(132)과, 상기 제1 홀(132)에 연통되도록 상기 층간절 연막(114)을 관통하여 형성된 제2 홀(134)을 포함한다.

- [0066] 상기 비아홀(130)을 형성하기 위하여 이방성 식각 공정 또는 레이저 드릴링 (laser drilling) 기술을 이용할 수 있다. 일부 실시예들에서, 상기 비아홀(130)은 기판(102)에서 약 10 戶 또는 그 이하의 폭(130W)을 가지도록 형성될 수 있다. 일부 실시예에서, 상기 비아홀(130)은 상기 충간절연막(114)의 상면으로부터 약 50 ~ 100 戶 의 보이(130D)를 가지도록 형성될 수 있다. 그러나, 상기 비아홀(130)의 폭 및 깊이는 상기 예시된 바에 제한되는 것은 아니며, 필요에 따라 다양한 치수로 형성될 수 있다. 상기 비아홀(130)의 제1 홀 (132) 부분에서 상기 기판(102)이 노출되고, 상기 비아홀(130)의 제2 홀(134) 부분에서 상기 충간절연막(114)이 노출된다.

- [0067] 상기 비아홀(130)이 형성된 후, 상기 마스크 패턴(122)을 제거하여 상기 제1 연마 정지층(120)의 상면을 노출시킨다.

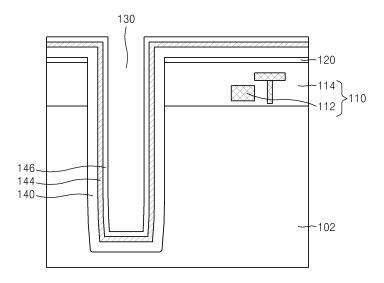

- [0068] 도 4c를 참조하면, 상기 비아홀(130)의 내부 측벽 및 저면을 덮는 비아 절연막(140)을 형성한다.

- [0069] 상기 비아 절연막(140)은 상기 비아홀(130) 내부에서 노출되는 기판(102)의 표면 및 충간절연막(114)의 표면과, 상기 제1 연마 정지충(120)의 표면을 대략 균일한 두께로 덮도록 형성될 수 있다. 일부 실시예들에서, 상기 비아 절연막(140)은 산화막, 질화막, 탄화막, 폴리머, 또는 이들의 조합으로 이루어질 수 있다. 일부 실시예들에서, 상기 비아 절연막(140)을 형성하기 위하여 저온 CVD 공정 또는 PECVD 공정을 이용할 수 있다. 상기 비아 절연막(140)은 약 1500 ~ 2500 Å의 두께를 가지도록 형성될 수 있다.

- [0070] 도 4d를 참조하면, 상기 비아홀(130)의 내부 및 외부에서 상기 절연막(138) 위에 제1 도전성 배리어막(144)을 형성한다.

- [0071] 상기 제1 도전성 배리어막(144)은 상기 비아홀(130) 내에서 실린더형 구조를 가질 수 있다. 일부 실시예들에서, 상기 제1 도전성 배리어막(144)은 비교적 낮은 배선 저항을 가지는 도전층으로 이루어질 수 있다. 예를 들면, 상기 제1 도전성 배리어막(144)은 W, WN, Ti, TiN, Ta, TaN, 및 Ru 중에서 선택되는 적어도 하나를 포함하는 단일막 또는 다중막으로 이루어질 수 있다. 예를 들면, 상기 제1 도전성 배리어막(144)은 TaN/W, TiN/W, 또는 WN/W로 이루어지는 다중막으로 이루어질 수 있다. 상기 제1 도전성 배리어막(144)은 약 50 ~ 1000 Å의 두께를 가지도록 형성될 수 있다.

- [0072] 도 4d에 예시된 바와 같이, 상기 제1 도전성 배리어막(144)은 비아홀(130)의 내부 측벽을 대략 균일한 두께로 덮도록 형성될 수 있다. 이를 위하여, 상기 제1 도전성 배리어막(144)을 ALD 공정 또는 CVD 공정을 이용하여 형성할 수 있다.

- [0073] 도 4e를 참조하면, 상기 비아홀(130)의 내부 및 외부에서 상기 제1 도전성 배리어막(144) 위에 절연 박막(146)을 형성한다.

- [0074] 상기 절연 박막(146)은 상기 비아홀(130)의 내부 측벽을 대략 균일한 두께로 덮는 고밀도 박막으로 이루어질 수 있다. 상기 절연 박막은 ALD 공정 또는 CVD 공정을 이용하여 형성할 수 있다. 상기 절연 박막(146)은 약 50 ~ 1000 Å의 두께를 가지도록 형성될 수 있다.

- [0075] 상기 절연 박막(146)은 상기 비아홀(130) 내에서 실린더형 구조를 가질 수 있다. 상기 절연 박막(146)은 산화막, 질화막, 금속 산화막, 고유전막, 폴리머, 또는 이들의 조합으로 이루어질 수 있다. 상기 절연 박막(146)을 구성하는 재료에 대한 보다 상세한 사항은 도 1a를 참조하여 절연 박막(36)에 대하여 설명한 바를 참조한다.

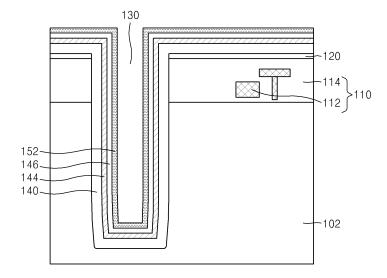

- [0076] 도 4f를 참조하면, 상기 비아홀(130)의 내부 및 외부에서 상기 절연 박막(146) 위에 제2 도전성 배리어막(152)을 형성한다.

- [0077] 상기 제2 도전성 배리어막(152)을 형성하기 위하여 PVD 공정 또는 CVD 공정을 이용할 수 있다.

- [0078] 상기 제2 도전성 배리어막(152)은, 도 1a에 예시된 제2 도전성 배리어막(32B)과 유사하게, 상기 비아홀(130)의 길이 방향을 따라 대략 균일한 두께를 가지도록 형성될 수 있다. 그러나, 이에 한정되는 것은 아니다. 다른 일부 실시예들에서, 도 1b에 예시된 제2 도전성 배리어막(62B)과 유사하게, 비아홀(130)의 입구측으로부터 비아홀(130)의 저면에 가까워질수록 점차 얇아지는 두께를 가지도록 형성될 수 있다. 예를 들면, 상기 제2 도전성 배리어막(152)은 상기 비아홀(130) 내부에서 상기 비아홀(130)의 입구측에서는 약 100 ~ 1000 Å의 두께를 가지고, 상기 비아홀(130)의 저면 부근에서는 약 0 ~ 50 Å의 두께를 가지도록 형성될 수도 있다. 이와 같이 비아홀(130)의 길이 방향을 따라 가변적인 두께를 가지는 상기 제2 도전성 배리어막(152)을 형성하기 위하여 PVD 공정을 이용할 수 있다.

- [0079] 상기 제2 도전성 배리어막(152)은 1 종의 물질로 이루어지는 단일막 또는 적어도 2 종의 물질을 포함하는 다중 막으로 이루어질 수 있다. 일부 실시예에서, 상기 제2 도전성 배리어막(152)은 W, WN, WC, Ti, TiN, Ta, TaN, Ru, Co, Mn, WN, Ni, 또는 NiB 중에서 선택되는 적어도 하나의 물질을 포함할 수 있다.

- [0080] 도 4g를 참조하면, 상기 제2 도전성 배리어막(152) 위에 상기 비아홀(130)의 남은 공간을 채우는 금속막(154)을 형성한다.

- [0081] 상기 금속막(154)은 상기 비아홀(130)의 내부 및 외부에서 상기 제2 도전성 배리어막(152)을 덮도록 형성될 수 있다.

- [0082] 일부 실시예들에서, 상기 금속막(154)을 형성하기 위하여 전기 도금 공정을 이용할 수 있다. 보다 구체적으로 설명하면, 먼저 상기 제2 도전성 배리어막(152)의 표면에 금속 시드층(도시 생략)을 형성한 후, 전기도금 공정에 의해 상기 금속 시드층으로부터 금속막을 성장시켜, 상기 제2 도전성 배리어막(152) 위에 상기 비아홀(130)을 채우는 금속막(154)을 형성한다. 상기 금속 시드층은 Cu, Cu 합금, Co, Ni, Ru, Co/Cu, 또는 Ru/Cu로 이루어질 수 있다. 상기 금속 시드층을 형성하기 위하여 PVD 공정을 이용할 수 있다. 상기 금속막(154)의 주 재료는 Cu 또는 W로 이루어질 수 있다. 일부 실시예들에서, 상기 금속막(154)은 Cu, CuSn, CuMg, CuNi, CuZn, CuPd, CuAu, CuRe, CuW, W, 또는 W 합금으로 이루어질 수 있으나, 이에 제한되는 것은 아니다. 상기 전기도금 공정은 각각 약 10 ~ 65 ℃의 온도하에서 행해질 수 있다. 예를 들면, 상기 전기도금 공정은 각각 상온에서 행해질 수도 있다. 상기 금속막(154)이 형성된 결과물을 약 150 ~ 450 ℃의 온도하에서 어닐링할 수 있다.

- [0083] 도 4h를 참조하면, 상기 제1 연마 정지층(120)을 스토퍼 (stopper)로 이용하여 상기 금속막(154)을 포함하는 도 4f의 결과물을 CMP (chemical mechanical polishing) 공정에 의해 연마하여, 상기 제1 연마 정지층(120)을 노출시킨다.

- [0084] 그 결과, 상기 비아 절연막(140), 제1 도전성 배리어막(144), 절연 박막(146), 제2 도전성 배리어막(152), 및 도전막(154) 중 비아홀(130)의 외부에 있던 부분은 제거되고, 상기 비아홀(130) 내에서 상기 제2 도전성 배리어막(152) 위에는 상기 도전막(154)의 일부인 금속 플러그(154A)가 남게 된다. 상기 제2 도전성 배리어막(152) 및 금속 플러그(154A)로 구성되는 도전성 플러그(156)는 상기 비아홀(130) 내에서 상기 절연 박막(146)을 사이에 두고 상기 제1 도전성 배리어막(144)과 이격되어 있다.

- [0085] 도 4i를 참조하면, 상기 비아홀(130) 내에 금속 플러그(154A)가 형성된 결과물을 열처리한다. 그 결과, 상기 금속 플러그(154A)를 구성하는 금속 입자들이 상기 열처리로 인하여 성장하여 금속 플러그(154A)의 노출 표면에서 러프니스 (roughness)가 열화될 수 있다. 상기 열처리에 의해 성장된 금속 입자들 중 비아홀(130)의 외부로 돌출된 부분들을 CMP 공정에 의해 제거한다. 이 때, 상기 제1 연마 정지층(120) (도 4h 참조)도 제거되어 상기 FEOL 구조(110)의 층간절연막(114)의 상면이 노출된다.

- [0086] 상기 열처리는 약 400 ~ 500 ℃의 온도하에서 행해질 수 있다.

- [0087] 상기 비아홀(130) 내에는 상기 제1 도전성 배리어막(144), 절연 박막(146), 및 도전성 플러그(156)를 포함하는 TSV 구조(160)가 남게 된다.

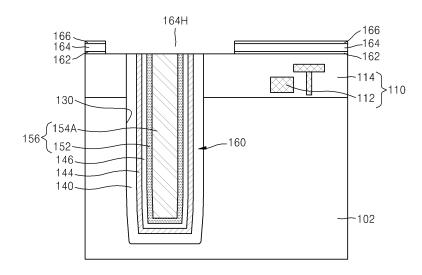

- [0088] 도 4j를 참조하면, 상기 TSV 구조(160)를 포함하는 도 4i의 결과물을 세정한 후, 상기 층간절연막(114) 위에 제 2 연마 정지층(162), 금속층간절연막(164), 및 제3 연마 정지층(166)을 차례로 형성하고, 이들을 패터닝하여 상기 비아홀(130)의 입구측에서 상기 TSV 구조(160)의 상면 및 그 주변을 노출시키는 금속 배선용 홀(164H)을 형성한다.

- [0089] 상기 제2 연마 정지층(162)은 상기 금속 배선용 홀(164H)을 형성할 때, 식각 스토퍼로 이용될 수 있다.

- [0090] 상기 금속 배선용 홀(164H)을 통해 상기 TSV 구조(160), 상기 TSV 구조(160)의 외부 측벽을 감싸는 비아 절연막 (140), 및 상기 충간절연막(114)의 일부가 노출된다. 일부 실시예들에서, 상기 금속 배선용 홀(164H)을 통해 상기 TSV 구조(160)의 상면만 노출되도록 상기 금속 배선용 홀(164H)을 형성할 수도 있다.

- [0091] 일부 실시예들에서, 상기 금속층간절연막(164)은 TEOS (tetra-ethyl-ortho-silicate)로 이루어질 수 있다. 상기 제2 연마 정지층(162) 및 제3 연마 정지층(166)은 실리콘 산화질화막으로 이루어질 수 있다. 상기 제2 연마 정지층(162), 금속층간절연막(164), 및 제3 연마 정지층(166) 각각의 두께는 필요에 따라 임의로 결정될 수 있다.

- [0092] 도 4k를 참조하면, 상기 금속 배선용 홀(164H) 내부에 금속 배선층(172)을 형성한다.

- [0093] 상기 금속 배선층(172)은 배선용 배리어막(172A) 및 배선용 금속층(172B)이 차례로 적층된 구조를 가진다.

- [0094] 일부 실시예들에서, 상기 금속 배선층(172)을 형성하기 위하여, 먼저 상기 금속 배선용 홀(164H) 내부 및 상기 제3 연마 정지층(166) (도 4j 참조) 위에 상기 배선용 배리어막(172A) 형성을 위한 제1 막과, 상기 배선용 금속 층(172B) 형성을 위한 제2 막을 차례로 형성한 후, 상기 제3 연마 정지층(166)을 스토퍼로 이용하여 상기 제1 막 및 제2 막이 형성된 결과물을 CMP 공정에 의해 연마하고, 상기 제3 연마 정지층(166)을 제거하여 상기 금속 충간절연막(164)의 상면을 노출시킨다. 그 결과, 상기 금속 배선용 홀(164H) 내부에 상기 배선용 배리어막(172A) 및 배선용 금속층(172B)이 남게 된다.

- [0095] 일부 실시예들에서, 상기 배선용 배리어막(172A)은 Ti, TiN, Ta, 또는 TaN 중에서 선택되는 적어도 하나의 물질을 포함한다. 일부 실시예들에서, 상기 배선용 배리어막(172A)을 형성하기 위하여 PVD 공정을 이용할 수 있다. 상기 배선용 배리어막(172A)은 약 1000 ~ 1500 Å의 두께를 가지도록 형성될 수 있다.

- [0096] 일부 실시예들에서, 상기 배선용 금속층(172B)은 Cu를 포함한다. 상기 배선용 금속층(172B)을 형성하기 위하여, 상기 배선용 배리어막(172A)의 표면에 Cu 시드층을 형성한 후, 전기도금 공정에 의해 상기 Cu 시드층으로부터 Cu 층을 성장시키고, 상기 Cu 층이 형성된 결과물을 어닐링하는 공정을 수행할 수 있다.

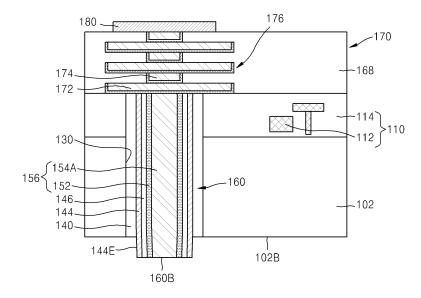

- [0097] 도 41을 참조하면, 도 4j 및 도 4k를 참조하여 설명한 상기 금속 배선층(172) 형성 공정과 유사한 방법으로 상기 금속 배선층(172) 위에 상기 금속 배선층(172)과 동일한 적층 구조를 가지는 콘택 플러그(174)를 형성한다. 그 후, 도 4j 및 도 4k를 참조하여 설명한 상기 금속 배선층(172) 형성 공정과, 상기 콘택 플러그(174) 형성 공정을 교대로 복수 회 행하여, 복수의 금속 배선층(172) 및 복수의 콘택 플러그(174)가 하나씩 교대로 연결되어 있는 관통 전극용 다층 배선 패턴(176)을 형성한다.

- [0098] 일부 실시예들에서, 상기 다층 배선 패턴(176)이 형성될 때, 상기 기판(102)상의 다른 영역에서도 상기 복수의 금속 배선층(172) 및 복수의 콘택 플러그(174) 중에서 선택되는 적어도 일부와 동시에 형성되는 금속 배선층 및 콘택 플러그를 포함하는 다른 다층 배선 패턴들(도시 생략)이 형성될 수 있다. 그 결과, 상기 FEOL 구조(110) 위에는 복수의 제2 연마 정지층(162) 및 금속층간절연막(164)으로 이루어지는 금속층간절연막 구조(168)와, 상기 금속층간절연막 구조(168)에 의해 절연되는 부분을 포함하는 복수의 다층 배선 패턴을 포함하는 BEOL (backend-of-line) 구조(170)가 얻어진다. 상기 BEOL 구조(170)는 상기 FEOL 구조(110)에 포함되는 개별 소자들을 상기 기판(102) 위에 형성되는 다른 배선들과 연결시키기 위한 복수의 배선 구조들을 포함하도록 형성될 수 있다. 일부 실시예들에서, 상기 BEOL 구조(170)는 상기 배선 구조들과 그 하부의 다른 구조물들을 외부 충격이나 습기로부터 보호하기 위한 시일 링(seal ring)을 더 포함하도록 형성될 수 있다.

- [0099] 그 후, 상기 다층 배선 패턴(176)에 전기적으로 연결되는 콘택 패드(180)를 상기 금속층간절연막 구조(168) 위에 형성한다.

- [0100] 상기 금속층간절연막 구조(168)은 상기 복수의 금속 배선층(172)을 서로 이격시키는 역할을 한다. 상기 복수의 금속 배선층(172) 및 복수의 콘택 플러그(174)는 각각 금속층간절연막 구조(168)에 의해 동일 레벨에서 서로 이 웃하는 다른 배선들과 전기적으로 분리될 수 있다.

- [0101] 도 41에서, 상기 다층 배선 패턴(176)이 3 개의 금속 배선층(172) 및 3 개의 콘택 플러그(174)를 포함하는 것으로 예시되어 있으나, 이는 설명의 간략화를 위하여 예시한 것에 불과한 것으로, 본 발명 기술적 사상의 범위가이에 한정되는 것은 아니다. 또한, 도 41에 도시된 상기 다층 배선 패턴(176)에서 금속 배선층(172) 및 콘택 플러그(174)의 연결 구조는 예시에 불과하며, 본 발명의 범위가 도 41에 예시된 구조에 한정되는 것은 아니다.

- [0102] 일부 실시예들에서, 상기 복수의 금속 배선층(172) 및 복수의 콘택 플러그(174)는 각각 W, Al, 또는 Cu 중에서 선택되는 적어도 하나의 금속을 포함할 수 있다. 일부 실시예들에서, 상기 복수의 금속 배선층(172) 및 복수의 콘택 플러그(174)는 서로 동일한 재료로 구성될 수 있다. 다른 일부 실시예들에서, 상기 복수의 금속 배선층 (172) 및 복수의 콘택 플러그(174) 중 적어도 일부가 서로 다른 재료를 포함하도록 구성될 수도 있다.

- [0103] 일부 실시예들에서, 상기 금속층간절연막 구조(168) 내에는 상기 다층 배선 패턴(176)과 동일 레벨에 형성되는 다른 복수의 다층 배선 패턴들(도시 생략)이 형성된다. 또한, 상기 금속층간절연막(162) 위에는 상기 콘택 패드 (180)와 동일 레벨에 형성되는 다른 복수의 콘택 패드들(도시 생략)이 형성된다.

- [0104] 도 4m을 참조하면, 상기 기판(102)을 그 저면으로부터 일부 제거하여 상기 TSV 구조(160)의 저면(160B)을 노출시킨다.

- [0105] 상기 TSV 구조(160)의 저면(160B)에는 상기 제1 도전성 배리어막(144)의 일부와 상기 도전성 플러그(156)의 일부가 함께 노출된다.

- [0106] 도 4m에 예시된 바와 같이, 기판(102)의 저면(102B)으로부터 상기 TSV 구조(160)의 저면(160B)이 상대적으로 돌출되도록 상기 기판(102)의 일부를 제거할 수 있다. 일부 실시예에서, 상기 기판(102)을 그 저면으로부터 일부 제거하기 위하여 CMP 공정, 에치백 공정, 또는 이들의 조합을 이용할 수 있다.

- [0107] 상기 기판(102)이 그 저면으로부터 일부 제거된 후, 상기 비아홀(130)은 상기 기판(102) 및 층간절연막(114)을 관통하는 관통홀이 된다. 상기 기판(102)의 저면(102B)으로부터 상기 비아 절연막(140)의 일부와 상기 TSV 구조 (160)의 일부가 함께 돌출될 수 있다. 상기 TSV 구조(160)의 저면(160B)이 노출된 후, 상기 TSV 구조(160) 중 기판(102)의 저면(102B)으로부터 돌출된 부분 주위에서 상기 TSV 구조(160)를 포위하고 있는 비아 절연막(140)을 등방성 식각 또는 이방성 식각 공정을 이용하여 제거하여, 상기 제1 도전성 배리어막(144)의 단부(144E) 측 벽을 일부 노출시킨다.

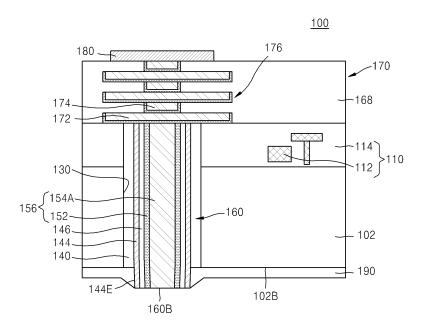

- [0108] 도 4n을 참조하면, 상기 TSV 구조(160)의 저면(160B) 주위에서 기판(102)의 저면(102B)을 덮는 백사이드 절연막 (190)을 형성하여 집적회로 소자(100)를 형성한다.

- [0109] 일부 실시예들에서, 상기 백사이드 절연막(190)은 스핀 코팅 공정 또는 스프레이 공정에 의해 형성될 수 있다. 상기 백사이드 절연막(190)은 폴리머로 이루어질 수 있다. 일부 실시예들에서, 상기 백사이드 절연막(190)을 형성하기 위하여, 상기 기판(102)의 저면(102B)과 상기 TSV 구조(160)의 저면(160B)을 덮는 폴리머막을 형성한후, 상기 폴리머막을 일부 에치백하여 상기 TSV 구조(160)의 저면(160B)을 노출시킬 수 있다.

- [0110] 도 4n에 예시한 반도체 소자(100)에서, 상기 TSV 구조(160)는 기판(102)에 의해 포위되는 측벽 부분과, 상기 FEOL 구조(110)의 층간절연막(114)에 의해 포위되는 측벽 부분을 가진다. 상기 기판(102) 및 FEOL 구조(110)는 도 1a에 예시한 반도체 구조물(20)에 대응되고, 상기 TSV 구조(160)는 도 1a에 예시한 TSV 구조(30A)에 대응될 수 있다. 상기 TSV 구조(160)의 저면(160B)에는 도전층 (도시 생략)이 연결될 수 있다. 일부 실시예들에서, 상기 도전층은 도 1a 및 도 1b에 예시한 제1 도전층(52) 또는 제2 도전층(54)에 대응될 수 있다.

- [0111] 도 4n에 예시한 반도체 소자(100)에서, 상기 제2 도전성 배리어막(152)이 비아홀(130)의 길이 방향을 따라 대략 균일한 두께를 가지는 것으로 예시되었으나, 본 발명의 기술적 사상의 범위 내에서 상기 제2 도전성 배리어막(152)은 비아홀(130)의 길이 방향을 따라 가변적인 두께를 가질 수도 있다.

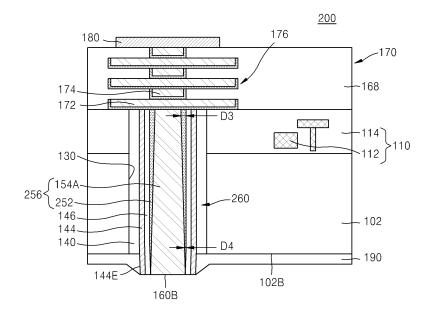

- [0112] 도 5는 본 발명의 기술적 사상에 의한 실시예들에 따른 집적회로 소자(200)의 요부 구성을 도시한 단면도이다. 도 5에 있어서, 도 4a 내지 도 4n에서와 동일한 참조 부호는 동일한 부재를 나타내며, 따라서 여기서는 중복을 피하기 위하여 이들에 대한 상세한 설명을 생략한다.

- [0113] 상기 집적회로 소자(200)에서, TSV 구조(260)는, 비아홀(130)의 내부에서 층간절연막(114)의 상면에 인접한 부분에서의 두께(D3)보다 기판(102)의 저면(102B)에 인접한 부분에서의 두께(D4)가 더 작은 제2 도전성 배리어막(252)을 가지는 도전성 플러그(256)를 포함하는 것을 제외하고, 도 4n에 예시한 TSV 구조(160)와 동일한 구성을 가진다.

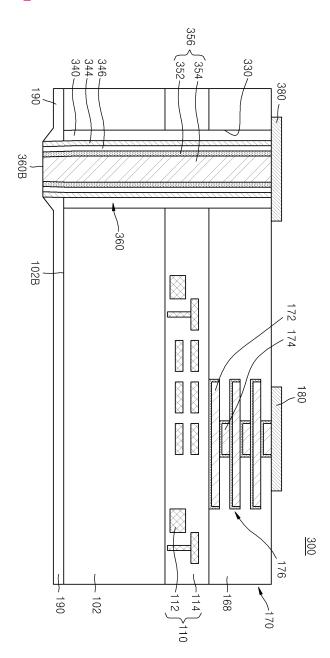

- [0114] 도 6은 본 발명의 기술적 사상에 의한 실시예들에 따른 집적회로 소자(300)의 요부 구성을 도시한 단면도이다. 도 6에 있어서, 도 4a 내지 도 4n에서와 동일한 참조 부호는 동일한 부재를 나타내며, 따라서 여기서는 중복을 피하기 위하여 이들에 대한 상세한 설명을 생략한다.

- [0115] 도 6을 참조하면, 집적회로 소자(300)에서, TSV 구조(360)는 그 측벽이 비아 절연막(340)에 의해 포위된 상태로

상기 기판(102), FEOL 구조(110)의 층간절연막(114), 및 BEOL 구조(170)의 금속층간절연막 구조(168)를 관통하도록 형성된다.

- [0116] 상기 TSV 구조(360)는 도전성 플러그(356), 상기 도전성 플러그(356)와 이격된 위치에서 상기 도전성 플러그 (356)를 포위하는 제1 도전성 배리어막(344), 및 상기 도전성 플러그(356)와 상기 제1 도전성 배리어막(344)과 의 사이에 개재되어 있는 절연 박막(346)을 포함한다.

- [0117] 상기 도전성 플러그(356)는 상기 기판(102), FEOL 구조(110)의 충간절연막(114), 및 BEOL 구조(170)의 금속충 간절연막 구조(168)를 관통하는 제2 도전성 배리어막(352)과, 상기 제2 도전성 배리어막(352)에 의해 포위되는 금속 플러그(354)를 포함한다. 상기 도전성 플러그(356)는 절연 박막(346)을 사이에 두고 상기 제1 도전성 배리어막(344)과 이격되어 있다. 일부 실시예들에서, 상기 제2 도전성 배리어막(352)은 생략될 수 있다.

- [0118] 상기 TSV 구조(360)는 기판(102)에 의해 포위되는 부분과, FEOL 구조(110)의 충간절연막(114)에 의해 포위되는 부분과, BEOL 구조(170)의 금속충간절연막 구조(168)에 의해 포위되는 부분을 포함한다.

- [0119] 상기 TSV 구조(360)를 형성하기 위하여 다음과 같은 일련의 공정들을 행할 수 있다.

- [0120] 먼저, 도 4a를 참조하여 설명한 바와 같은 방법으로 FEOL 구조(110)를 형성한 후, 도 4j 내지 도 4l을 참조하여 설명한 바와 같은 방법으로 다층 배선 패턴(176) 및 금속층간절연막 구조(168)를 포함하는 BEOL 구조(170)를 형성한다.

- [0121] 그 후, 상기 금속층간절연막 구조(168), 층간절연막(114), 및 기판(102)을 차례로 식각하여 비아홀(330)을 형성하고, 도 4a 내지 도 4i를 참조하여 비아 절연막(340) 및 TSV 구조(160)를 형성하는 공정에 대하여 설명한 바와 유사한 방법으로, 상기 비아홀(330) 내에 비아 절연막(340) 및 TSV 구조(360)를 형성한다. 그 후, 다층 배선 패턴(176)에 전기적으로 연결 가능한 콘택 패드(180)와, 상기 TSV 구조(360)에 전기적으로 연결 가능한 콘택 패드(380)를 형성한다. 상기 TSV 구조(360)의 제1 도전성 배리어막(344)의 일부와, 상기 도전성 플러그(156)의 일부가 상기 콘택 패드(380)에 접촉된다.

- [0122] 그 후, 도 4m 및 도 4n을 참조하여 설명한 바와 같은 방법으로 상기 TSV 구조(360)의 저면(360B)을 노출시킨 후, 기판(102)의 저면(120B)을 덮는 백사이드 절연막(190)을 형성하여 집적회로 소자(300)를 형성한다.

- [0123] 상기 TSV 구조(360)에 대한 보다 상세한 사항은 도 4a 내지 도 4n을 참조하여 TSV 구조(160)에 대하여 설명한 바와 대체로 동일하다.

- [0124] 도 6에 예시한 반도체 소자(300)에서, 제2 도전성 배리어막(352)이 비아홀(330)의 길이 방향을 따라 대략 균일 한 두께를 가지는 것으로 예시되었으나, 본 발명의 기술적 사상의 범위 내에서 상기 제2 도전성 배리어막(352)은 비아홀(330)의 길이 방향을 따라 가변적인 두께를 가질 수도 있다.

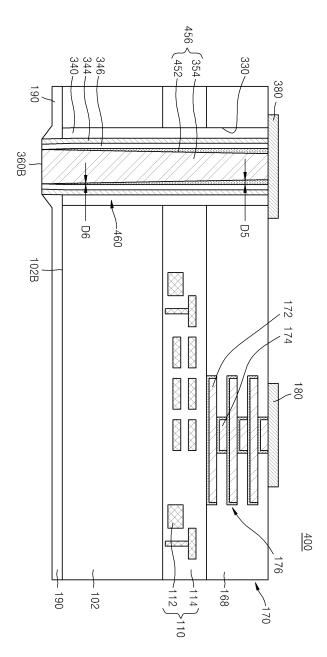

- [0125] 도 7는 본 발명의 기술적 사상에 의한 실시예들에 따른 집적회로 소자(400)의 요부 구성을 도시한 단면도이다. 도 7에 있어서, 도 4a 내지 도 4n 및 도 6에서와 동일한 참조 부호는 동일한 부재를 나타내며, 따라서 여기서는 중복을 피하기 위하여 이들에 대한 상세한 설명을 생략한다.

- [0126] 상기 집적회로 소자(400)에서, TSV 구조(460)는, 비아홀(330)의 내부에서 BEOL 구조(170)의 금속층간절연막 구조(168)의 상면에 인접한 부분에서의 두께(D5)보다 기판(102)의 저면(102B)에 인접한 부분에서의 두께(D6)가 더작은 제2 도전성 배리어막(452)을 가지는 도전성 플러그(456)를 포함하는 것을 제외하고, 도 6에 예시한 집적회로 소자(300)의 TSV 구조(360)와 동일한 구성을 가진다.

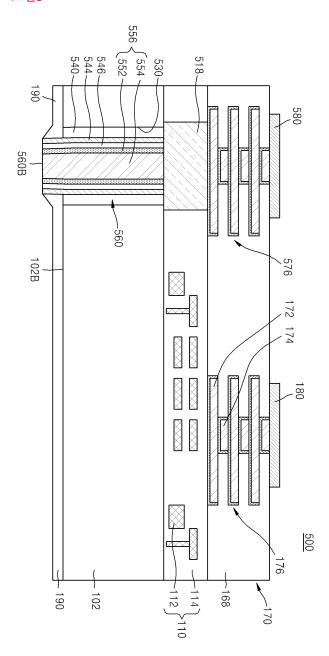

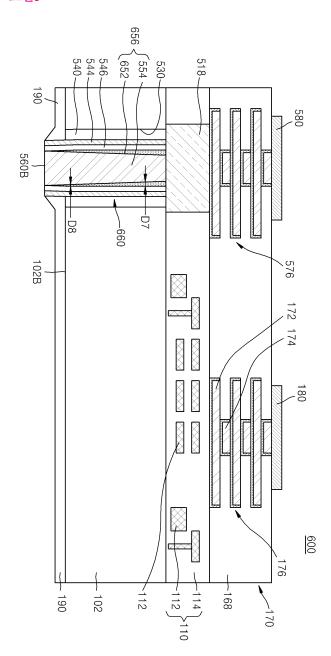

- [0127] 도 8은 본 발명의 기술적 사상에 의한 실시예들에 따른 집적회로 소자(500)의 요부 구성을 도시한 단면도이다. 도 8에 있어서, 도 4a 내지 도 4n에서와 동일한 참조 부호는 동일한 부재를 나타내며, 따라서 여기서는 중복을 피하기 위하여 이들에 대한 상세한 설명을 생략한다.

- [0128] 도 8을 참조하면, 집적회로 소자(500)에서, TSV 구조(560)는 그 측벽이 비아 절연막(340)에 의해 포위된 상태로 상기 기판(102)을 관통하도록 형성된다.

- [0129] 상기 TSV 구조(560)는 상기 FEOL 구조(110)보다 더 낮은 레벨에 형성된다. 상기 TSV 구조(560)는 도전성 플러그 (556), 상기 도전성 플러그(556)와 이격된 위치에서 상기 도전성 플러그(556)를 포위하는 제1 도전성 배리어막 (544), 및 상기 도전성 플러그(556)와 상기 제1 도전성 배리어막(544)과의 사이에 개재되어 있는 절연 박막 (546)을 포함한다.

- [0130] 상기 도전성 플러그(556)는 상기 기판(102)을 관통하는 제2 도전성 배리어막(552)과, 상기 제2 도전성 배리어막(552)에 의해 포위되는 금속 플러그(554)를 포함한다. 상기 도전성 플러그(556)는 절연 박막(546)을 사이에 두고 상기 제1 도전성 배리어막(544)과 이격되어 있다. 일부 실시예들에서, 상기 제2 도전성 배리어막(552)은 생략될 수 있다. 상기 TSV 구조(560)는 기판(102)에 의해 포위되는 측벽을 가진다.

- [0131] 상기 TSV 구조(560)를 형성하기 위하여 다음과 같은 일련의 공정들을 행할 수 있다.

- [0132] 먼저, 기판(102) 위에 FEOL 구조(110)를 형성하기 전에, 상기 기판(102)에 비아홀(530)을 형성한 후, 도 4a 내지 도 4i를 참조하여 설명한 바와 유사한 방법으로 상기 비아홀(530) 내에 비아 절연막(540)과, 상기 비아 절연막(540)에 의해 포위되는 TSV 구조(560)를 형성한다.

- [0133] 상기 TSV 구조(560)가 형성된 상기 기판(102)상에 도 4a를 참조하여 설명한 바와 같은 FEOL 구조(110)를 형성한다. 상기 FEOL 구조(110)는 상기 TSV 구조(560)에 전기적으로 연결 가능한 배선 구조(518)를 더 포함한다. 상기 TSV 구조(560)의 제1 도전성 배리어막(544)의 일부와, 상기 도전성 플러그(556)의 일부가 상기 콘택 패드(380)에 접촉된다. 상기 배선 구조(518)는 복수의 도전층 및 복수의 콘택 플러그를 포함하는 다층 배선 구조를 가질수 있다. 그러나, 상기 배선 구조(518)에 대한 구체적인 형상은 위에서 설명한 바에 제한되는 것은 아니며, 본 발명의 기술적 사상의 범위 내에서 다양한 배선 구조를 가질 수 있다.

- [0134] 그 후, 도 4j 내지 도 4l을 참조하여 설명한 바와 같은 방법으로 다층 배선 패턴(176) 및 금속층간절연막 구조 (168)를 포함하는 BEOL 구조(170)를 형성한다. 본 예에서, 상기 BEOL 구조(170)는 상기 배선 구조(518)를 통해 상기 TSV 구조(560)에 전기적으로 연결 가능한 다층 배선 패턴(576)을 더 포함한다. 그 후, 금속층간절연막 구조(168) 위에 다층 배선 패턴(176, 576)에 전기적으로 연결 가능한 콘택 패드(180, 580)를 형성한다.

- [0135] 그 후, 도 4m 및 도 4n을 참조하여 설명한 바와 같은 방법으로 상기 TSV 구조(560)의 저면(560B)을 노출시킨후, 기판(102)의 저면(120B)을 덮는 백사이드 절연막(190)을 형성하여 집적회로 소자(500)를 형성한다.

- [0136] 상기 TSV 구조(560)에 대한 보다 상세한 사항은 도 4a 내지 도 4n을 참조하여 TSV 구조(160)에 대하여 설명한 바와 대체로 동일하다.

- [0137] 도 8에 예시한 반도체 소자(500)에서, 제2 도전성 배리어막(552)이 비아홀(530)의 길이 방향을 따라 대략 균일한 두께를 가지는 것으로 예시되었으나, 본 발명의 기술적 사상의 범위 내에서 상기 제2 도전성 배리어막(552)은 비아홀(530)의 길이 방향을 따라 가변적인 두께를 가질 수도 있다.

- [0138] 도 9는 본 발명의 기술적 사상에 의한 실시예들에 따른 집적회로 소자(600)의 요부 구성을 도시한 단면도이다. 도 9에 있어서, 도 4a 내지 도 4n 및 도 8에서와 동일한 참조 부호는 동일한 부재를 나타내며, 따라서 여기서는 중복을 피하기 위하여 이들에 대한 상세한 설명을 생략한다.

- [0139] 상기 집적회로 소자(600)에서, TSV 구조(660)는, 비아홀(530)의 내부에서 기판(102)의 상면(102T)에 인접한 부분에서의 두께(D7)보다 기판(102)의 저면(102B)에 인접한 부분에서의 두께(D8)가 더 작은 제2 도전성 배리어막 (652)을 가지는 도전성 플러그(656)를 포함하는 것을 제외하고, 도 8에 예시한 집적회로 소자(500)의 TSV 구조 (560)와 동일한 구성을 가진다.

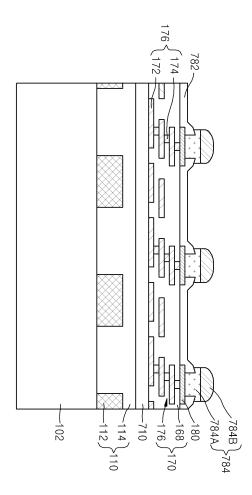

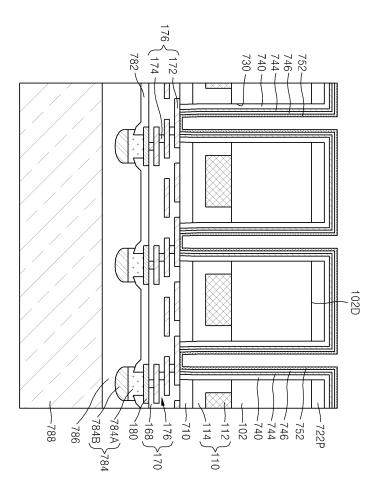

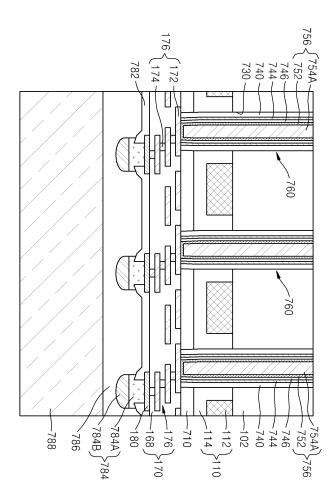

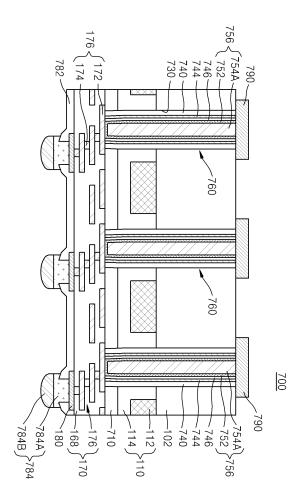

- [0140] 도 10a 내지 도 10k는 본 발명의 기술적 사상에 의한 일 실시예에 따른 집적회로 소자(700) (도 10k 참조)의 제조 방법을 설명하기 위한 단면도들이다. 도 10a 내지 도 10k에 있어서, 도 4a 내지 도 4n에서와 동일한 참조 부호는 동일한 부재를 나타내며, 따라서 여기서는 중복을 피하기 위하여 이들에 대한 상세한 설명을 생략한다.

- [0141] 도 10a를 참조하면, 기판(102)상에 복수의 개별 소자(112) 및 충간절연막(114)을 포함하는 FEOL 구조(110)를 형성하고, 상기 FEOL 구조(110) 위에 식각 정지층(710)을 형성하고, 상기 식각 정지층(710) 위에 BEOL 구조(170)를 형성한다. 상기 BEOL 구조(170)는 금속층간절연막 구조(168) 및 복수의 다층 배선 패턴(176)을 포함한다. 상기 복수의 다층 배선 패턴(176)은 각각 복수의 금속 배선층(172) 및 복수의 콘택 플러그(174)로 이루어진다.

- [0142] 상기 금속층간절연막 구조(168) 위에 복수의 콘택 패드(180)를 형성하고, 상기 BEOL 구조(170) 위에 패시베이션 층(782) 및 복수의 범프(784)를 형성한다. 도 10a에서, 상기 복수의 범프(784)는 각각 제1 금속층(784A) 및 제2 금속층(784B)의 적층 구조를 가지는 것으로 예시되었으나, 본 발명의 기술적 사상은 이에 한정되는 것은 아니며, 다양한 구조를 가지는 범프(784)를 형성할 수 있다.

- [0143] 도 10b를 참조하면, 기판(102)에서 상기 복수의 범프(784)가 형성되어 있는 표면에 접착 코팅층(786)을 인가하고, 상기 접착 코팅층(786)을 부착 재료로 이용하여 상기 복수의 범프(784)가 형성된 기판(102)을 상기 웨이퍼

지지 기판(788)상에 탑재한다.

- [0144] 다른 일부 실시예에서, 도 10b의 결과물을 얻기 위하여, 상기 접착 코팅층(786)이 부착되어 있는 웨이퍼 지지 기판(788)에 상기 복수의 범프(784)가 형성된 기판(102)을 부착할 수도 있다.

- [0145] 상기 기판(102) 중 상기 웨이퍼 지지 기판(788)으로 덮인 측의 반대 측인 기판(102)의 백사이드(102D)가 외부에 노출되어 있다.

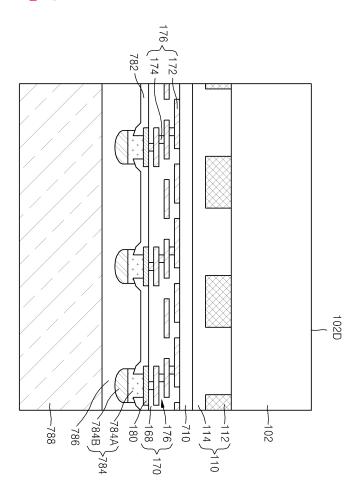

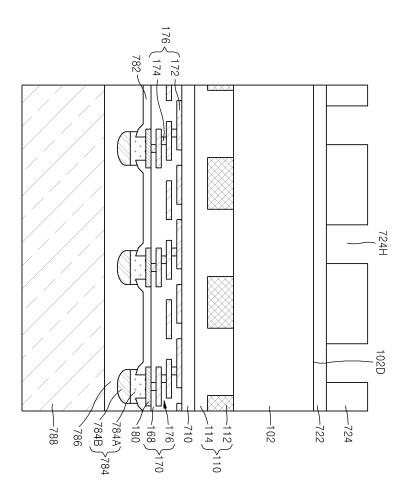

- [0146] 도 10c를 참조하면, 기판(102)의 백사이드(102D) 위에 하드마스크층(722)을 형성한 후, 상기 하드마스크층(722) 위에 마스크 패턴(724)을 형성한다.

- [0147] 일부 실시예들에서, 상기 하드마스크충(722)은 실리콘 질화막으로 이루어진다. 상기 하드마스크충(722)은 약 200 ~ 1000 Å의 두께를 가지도록 형성될 수 있다.

- [0148] 상기 마스크 패턴(724)에는 상기 하드마스크층(722)의 상면을 일부 노출시키는 복수의 홀(724H)이 형성되어 있다. 일부 실시예들에서, 상기 마스크 패턴(724)은 포토레지스트 재료로 이루어진다.

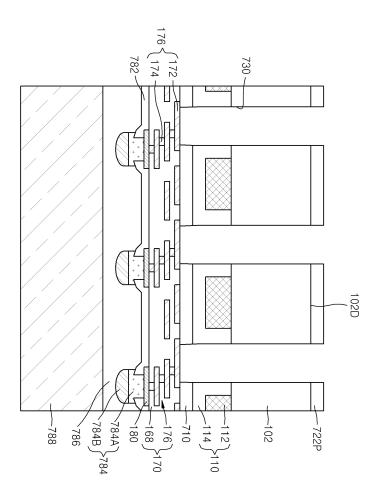

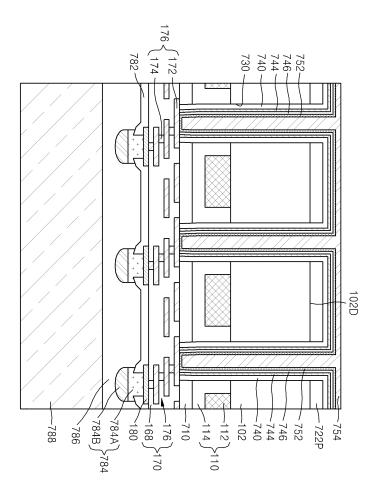

- [0149] 도 10d를 참조하면, 상기 마스크 패턴(724)(도 10c 참조)을 식각 마스크로 이용하여 상기 하드마스크층(722)을 식각하여 하드마스크 패턴(722P)을 형성하고, 상기 마스크 패턴(724) 및 하드마스크 패턴(722P)을 식각 마스크로 이용하여 기판(102) 및 식각 정지층(710)을 식각하여 금속 배선층(172)을 노출시키는 복수의 비아홀(730)을 형성한다. 상기 복수의 비아홀(730)은 상기 기판(102) 및 상기 FEOL 구조(110)의 층간절연막(114)을 관통하여 연장되는 형상을 가진다.

- [0150] 상기 복수의 비아홀(730)을 형성하기 위하여 이방성 식각 공정 또는 레이저 드릴링 기술을 이용할 수 있다. 일부 실시예에서, 상기 복수의 비아홀(730)을 형성하기 위한 충간절연막(114)의 식각시 식각 정지충(710)을 이용하여 식각 종료점을 결정할 수 있다. 상기 복수의 비아홀(730)은 약 10 ㎞ 또는 그 이하의 폭과, 약 50 ~ 100 ㎞ 깊이를 가질 수 있다. 그러나, 상기 복수의 비아홀(730)의 폭 및 깊이는 예시된 바에 제한되는 것은 아니며, 필요에 따라 다양한 치수로 형성될 수 있다.

- [0151] 상기 복수의 비아홀(730)이 형성된 후, 상기 마스크 패턴(724)(도 10c 참조)을 제거하여 상기 하드마스크 패턴 (722P)의 상면을 노출시킨다.

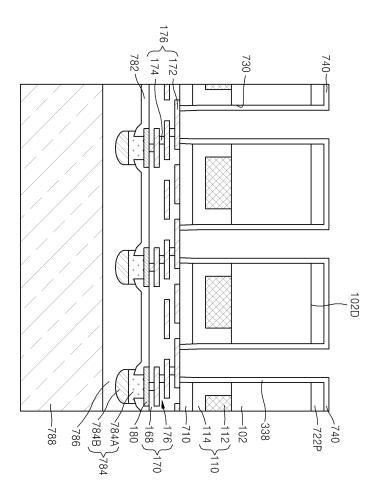

- [0152] 도 10e를 참조하면, 상기 복수의 비아홉(730)의 내부 측벽을 덮는 복수의 비아 절연막(740)을 형성한다.

- [0153] 일부 실시예들에서, 상기 비아 절연막(740)을 형성하기 위하여, 먼저 복수의 비아홀(730)의 내벽과 기판(102)의 백사이드(102D)를 덮는 절연막(도시 생략)을 형성한 후, 복수의 비아홀(730) 내부에서 상기 복수의 금속 배선층 (172)이 노출되도록 상기 절연막 중 일부를 이방성 이온 에칭 공정에 의해 제거하는 공정을 수행할 수 있다. 상기 절연막은 CVD 공정에 의해 형성할 수 있다. 일부 실시예들에서, 상기 복수의 비아 절연막(740)에 대한 보다 상세한 사항은 도 4c를 참조하여 비아 절연막(140)에 대하여 설명한 바를 참조한다.

- [0154] 도 10f를 참조하면, 상기 복수의 비아홀(730) 내부 및 외부에서 상기 복수의 비아 절연막(740) 위에 복수의 제1 도전성 배리어막(744)을 형성한다.

- [0155] 상기 복수의 제1 도전성 배리어막(744)을 형성하기 위하여, 상기 복수의 비아 절연막(740)이 형성된 결과물의 노출 표면 위에 배리어층(도시 생략)을 형성한 후, 상기 복수의 비아홀(730) 내부에서 상기 복수의 금속 배선층 (172)이 노출되도록 상기 배리어층 중 일부를 이방성 이온 에칭 공정에 의해 제거하는 공정을 수행할 수 있다.

- [0156] 상기 복수의 금속 배선층(172)에는 각각 상기 복수의 제1 도전성 배리어막(744)의 일부가 접촉한다. 상기 복수의 제1 도전성 배리어막(744)에 대한 보다 상세한 사항은 도 4d를 참조하여 제1 도전성 배리어막(144)에 대하여 설명한 바를 참조한다.

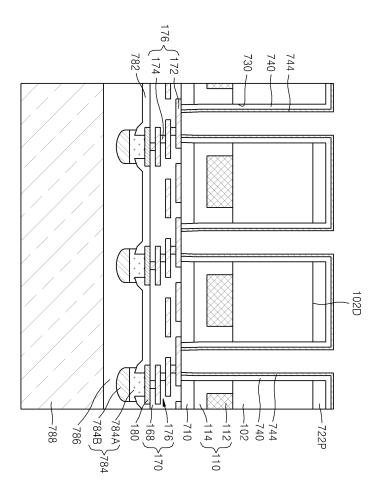

- [0157] 도 10g를 참조하면, 상기 복수의 제1 도전성 배리어막(744)을 덮는 복수의 절연 박막(746)을 형성한다. 상기 복수의 비아홀(730) 내부에서 상기 복수의 절연 박막(746)을 통해 상기 복수의 금속 배선층(172)이 노출된다.

- [0158] 상기 복수의 절연 박막(746)에 대한 보다 상세한 사항은 도 4e를 참조하여 절연 박막(146)에 대하여 설명한 바를 참조한다.

- [0159] 도 10h를 참조하면, 도 4f를 참조하여 설명한 제2 도전성 배리어막(152) 형성 공정과 유사한 방법으로, 상기 복수의 절연 박막(746) 및 복수의 금속 배선층(172) 위에 제2 도전성 배리어막(752)을 형성한다.

- [0160] 일부 실시예들에서, 상기 제2 도전성 배리어막(752)은 상기 비아홀(730) 내에서 대략 균일한 두께를 가지도록

형성될 수 있다. 다른 일부 실시예들에서, 상기 제2 도전성 배리어막(752)은 상기 비아홀(730) 내부에서 가변적인 두께를 가지도록 형성될 수 있다. 예를 들면, 상기 제2 도전성 배리어막(752)은 상기 비아홀(370)의 입구측근방에서의 두께가 상기 비아홀(730)의 저면측 근방에서의 두께보다 더 클 수 있다. 일부 실시예들에서, 상기제2 도전성 배리어막(752)의 형성 공정은 생략 가능하다.

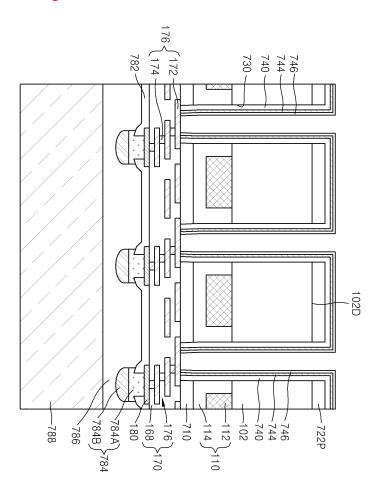

- [0161] 도 10i를 참조하면, 도 4g를 참조하여 도전막(154) 형성 방법에 대하여 설명한 바와 같은 방법으로 상기 제2 도 전성 배리어막(752) 위에 도전막(754)을 형성한다.

- [0162] 상기 제2 도전성 배리어막(752)을 형상하지 않은 경우, 상기 도전막(754)은 상기 복수의 금속 배선층(172)과 직접 접촉하도록 형성된다.

- [0163] 도 10j를 참조하면, 도 4h 및 도 4i를 참조하여 설명한 바와 유사한 방법으로, 상기 하드마스크 패턴(722P) (도 10i 참조)을 스토퍼로 이용하여 상기 금속막(754)을 포함하는 도 10i의 결과물을 연마하고, 상기 하드마스크 패턴(722P)을 제거하여 기판(102)을 노출시키고, 복수의 비아홀(730) 내에 상기 제2 도전성 배리어막(752) 및 금속 플러그(754A)로 구성되는 도전성 플러그(756)를 형성한다. 상기 도전성 플러그(756)에 대한 보다 상세한 사항은 도 4h 및 도 4i를 참조하여 도전성 플러그(156)에 대하여 설명한 바를 참조한다.

- [0164] 상기 복수의 비아홀(730) 내에는 각각 상기 제1 도전성 배리어막(744), 절연 박막(746), 및 도전성 플러그(75 6)를 포함하는 복수의 TSV 구조(760)가 남게 된다.

- [0165] 도 10k를 참조하면, 상기 복수의 비아홀(730) 각각의 입구측에서 상기 복수의 TSV 구조(760)에 전기적으로 연결 가능한 복수의 콘택 패드(790)를 형성한다. 상기 복수의 TSV 구조(760)에서 상기 제1 도전성 배리어막(744) 및 도전성 플러그(756)는 절연 박막(746)에 의해 상호 이격되어 있으며, 상기 제1 도전성 배리어막(744) 및 도전성 플러그(756)는 각각 상기 콘택 패드(790)에 접한다.

- [0166] 그 후, 상기 웨이퍼 지지 기판(788) 및 접착 코팅층(786) (도 10j 참조)을 제거하고 복수의 범프(784)를 노출시켜 집적회로 소자(700)를 얻는다.

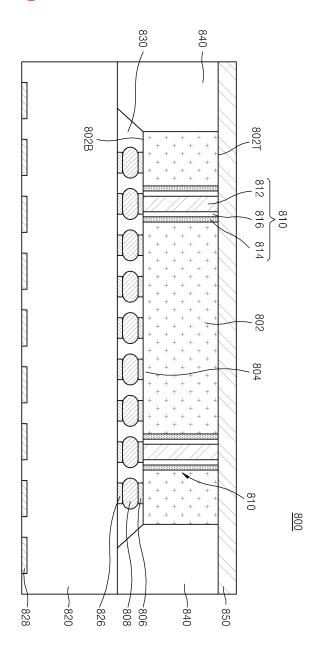

- [0167] 도 11은 본 발명의 기술적 사상에 의한 실시예들에 따른 집적회로 소자(800)의 요부 구성을 보여주는 단면도이다.

- [0168] 도 11을 참조하면, 집적회로 소자(800)는 반도체 다이(802)를 포함한다. 상기 반도체 다이(802)는 아날로그 또는 다지탈 회로를 구비한 활성 영역(804)을 포함한다. 상기 반도체 다이(802)의 활성 영역(804)상에 형성된 복수의 콘택 패드(806)에는 복수의 솔더 범프(808)가 연결되어 있다.

- [0169] 상기 반도체 다이(802)에는 상기 반도체 다이(802)를 관통는 복수의 TSV 구조(810)가 형성되어 있다. 상기 복수의 TSV 구조(810)는 비아 절연막(도시 생략)에 의해 상기 반도체 다이(802)의 활성 영역과 전기적으로 분리될수 있다.

- [0170] 상기 복수의 TSV 구조(810)는 도전성 플러그(812)와, 상기 도전성 플러그(812)와 이격되어 상기 도전성 플러그 (812)를 포위하는 실린더형의 도전성 배리어막(814)과, 상기 도전성 플러그(812)와 상기 도전성 배리어막(814)과의 사이에 개재되어 있는 실린더형의 절연 박막(816)을 포함한다.

- [0171] 상기 복수의 TSV 구조(810)에서, 도전성 플러그(812) 및 도전성 배리어막(814)은 각각 상기 반도체 다이(802)의 일측(802T)으로부터 타측(802B)까지 연장되어 상기 복수의 콘택 패드(806)를 통해 상기 복수의 솔더 범프(808)에 전기적으로 연결된다.

- [0172] 상기 반도체 다이(802)는 기판(820)상에 장착되어 있다. 상기 기판(820)의 양측에는 복수의 콘택 패드(826, 828)가 형성되어 있다. 상기 복수의 솔더 범프(808)는 상기 기판(820)의 일측에 형성된 복수의 콘택 패드(826)에 연결되어 있다. 상기 복수의 TSV 구조(810)의 도전성 플러그(812) 및 도전성 배리어막(814)이 각각 상기 솔더 범프(808)를 통해 상기 기판(820)의 콘택 패드(826)에 전기적으로 연결된다.

- [0173] 상기 반도체 다이(802)와 상기 기판(820)과의 사이에는 에폭시 수지 또는 무기 재료로 이루어지는 언더필 (underfill) 재료층(830)이 채워져 있다. 상기 복수의 콘택 패드(806, 826) 및 복수의 솔더 범프(808)가 상기 언더필 재료층(830)에 의해 보호될 수 있다.

- [0174] 상기 기판(820) 상에서 상기 반도체 다이(802)의 양측에는 몰딩 화합물층(840)이 퇴적되어 있다. 상기 몰딩 화합물층(840)은 절연 물질로 이루어진다. 상기 몰딩 화합물층(840)에 의해 외부 환경 또는 오염물로부터 상기 반도체 다이(802)를 보호함 수 있다.

- [0175] 상기 반도체 다이(802) 위에는 도전층(850)이 형성되어 있다. 상기 도전층(850)은 상기 복수의 TSV 구조(810)를 통해 상기 기판(820)의 콘택 패드(826)에 전기적으로 연결될 수 있다. 상기 도전층(850)은 금속 또는 금속 함유 물질로 이루어질 수 있다. 상기 복수의 TSV 구조(810)의 도전성 플러그(812) 및 도전성 배리어막(814)이 각각 상기 도전층(850)에 전기적으로 연결된다.

- [0176] 일부 실시예들에서, 상기 도전층(850)은 EMI (electromagnetic interference), RFI (radio frequency interference) 등과 같은 소자간 간섭을 차단하기 위한 도전성 실드층 (conductive shielding layer)으로 사용될 수 있다.

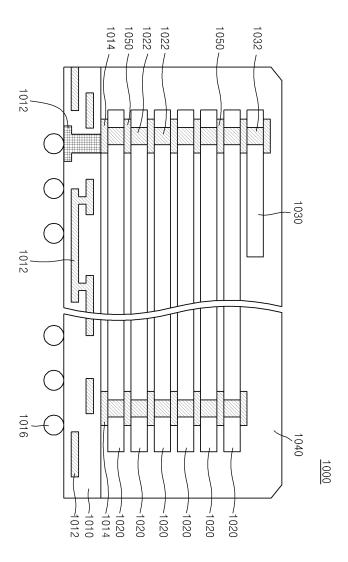

- [0177] 도 12는 본 발명의 기술적 사상에 의한 실시예들에 따른 집적회로 소자(1000)의 요부 구성을 보여주는 단면도이다.

- [0178] 도 12를 참조하면, 집적회로 소자(1000)는 패키지 기판(1010)상에 차례로 적층된 복수의 반도체 칩(1020)을 포함한다. 상기 복수의 반도체 칩(1020)상에 제어 칩(control chip)(1030)이 연결되어 있다. 상기 복수의 반도체 칩(1020)과 제어 칩(1030)의 적층 구조는 패키지 기판(1010)상에서 열경화성 수지와 같은 밀봉재 (encapsulant)(1040)로 밀봉되어 있다. 도 12에는 6 개의 반도체 칩(1020)이 수직으로 적충된 구조를 예시하였으나, 상기 반도체 칩(1020)의 개수 및 적층 방향이 예시된 바에 제한되는 것은 아니다. 상기 반도체 칩(1020)의 개수는 필요에 따라 6 개 보다 더 적거나 더 많게 결정될 수 있다. 상기 복수의 반도체 칩(1020)은 패키지 기판(1010)상에 수평 방향으로 배열될 수도 있고, 수직 방향 실장 및 수평 방향 실장을 조합한 연결 구조로 배열될 수도 있다. 일부 실시예들에서, 상기 제어 칩(1030)은 생략 가능하다.

- [0179] 상기 패키지 기판(1010)은 연성 인쇄회로기판 (flexible printed circuit board), 경성 인쇄회로기판(rigid printed circuit board), 또는 이들의 조합으로 이루어질 수 있다. 상기 패키지 기판(1010)은 기판 내부 배선 (1012) 및 접속 단자(1014)를 구비한다. 상기 접속 단자(1014)는 상기 패키지 기판(1010)의 일면에 형성될 수 있다. 상기 패키지 기판(1010)의 다른 면에는 솔더 볼(1016)이 형성되어 있다. 상기 접속 단자(1014)는 상기 기판 내부 배선(1012)을 통하여 상기 솔더 볼(1016)에 전기적으로 접속된다. 일부 실시예에서, 상기 솔더 볼 (1016)은 도전성 범프 (conductive bump) 또는 LGA (lead grid array)로 대체될 수 있다.

- [0180] 상기 복수의 반도체 칩(1020) 및 제어 칩(1030) 각각의 TSV 구조(1022, 1032)는 범프와 같은 연결 부재(1050) 에 의해 상기 패키지 기판(1010)의 접속 단자(1014)에 전기적으로 연결될 수 있다. 일부 실시예들에서, 상기 제어 칩(1030)에서 TSV 구조(1032)가 생략될 수 있다.

- [0181] 상기 복수의 반도체 칩(1020) 및 제어 칩(1030) 중 적어도 하나는 도 1a 내지 도 11을 참조하여 설명한 바와 같은 집적회로 소자(10A, 10B, 100, 200, 300, 400, 500, 600, 700, 800) 중 적어도 하나를 포함한다. 상기 복수의 TSV 구조(1022, 1032) 중 적어도 하나는 각각 도 1a 내지 도 11을 참조하여 설명한 바와 같은 집적회로 소자(10A, 10B, 100, 200, 300, 400, 500, 600, 700, 800)에 각각 포함된 TSV 구조들 중 어느 하나의 구조를 가질수 있다.

- [0182] 상기 복수의 반도체 칩(1020)은 각각 시스템 LSI, 플래쉬 메모리, DRAM, SRAM, EEPROM, PRAM, MRAM, 또는 RRAM을 포함할 수 있다. 상기 제어 칩(1030)은 SER/DES (serializer/deserializer) 회로와 같은 로직 회로들을 포함할 수 있다.

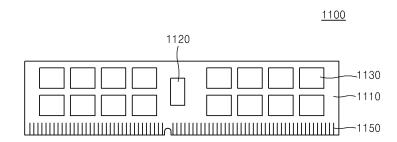

- [0183] 도 13은 본 발명의 기술적 사상에 의한 실시예들에 따른 집적회로 소자(1100)의 요부 구성을 보여주는 평면도이다.

- [0184] 집적회로 소자(1100)는 모듈 기판(1110)과, 상기 모듈 기판(1110)에 장착된 제어 칩(1120) 및 복수의 반도체 패키지(1130)를 포함한다. 상기 모듈 기판(1110)에는 복수의 입출력 단자(1150)가 형성되어 있다.

- [0185] 상기 복수의 반도체 패키지(1130)는 도 1a 내지 도 12를 참조하여 설명한 바와 같은 집적회로 소자(10A, 10B, 100, 200, 300, 400, 500, 600, 700, 800, 1000) 중 적어도 하나를 포함한다.

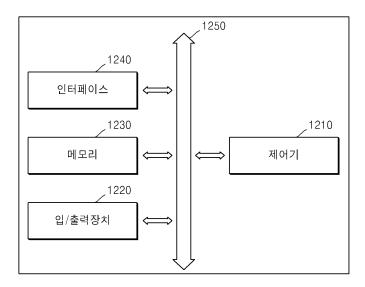

- [0186] 도 14는 본 발명의 기술적 사상에 의한 실시예들에 따른 집적회로 소자(1200)의 요부 구성을 보여주는 다이어그램이다.

- [0187] 상기 집적회로 소자(1200)는 제어기(1210), 입/출력 장치(1220), 메모리(1230), 및 인터페이스(1240)를 포함한다. 상기 집적회로 소자(1200)는 모바일 시스템 또는 정보를 전송하거나 전송받는 시스템일 수 있다. 일부 실시예에서, 상기 모바일 시스템은 PDA (personal digital assistant), 휴대용 컴퓨터, 웹 타블렛, 무선 폰, 모바

일 폰, 디지털 뮤직 플레이어, 또는 메모리 카드 중 적어도 하나이다.

- [0188] 일부 실시예들에서, 상기 제어기(1210)는 마이크로프로세서, 디지털 신호 프로세서, 또는 마이크로콘트롤러 (micro-controller)이다.

- [0189] 상기 입/출력 장치(1220)는 집적회로 소자(1200)의 데이터 입출력에 이용된다. 상기 집적회로 소자(1200)는 상기 입/출력 장치(1220)를 이용하여 외부 장치, 예를 들면 개인용 컴퓨터 또는 네트워크에 연결될 수 있고, 상기 외부 장치와 상호 데이터를 교환할 수 있다. 일부 실시예에서, 상기 입/출력 장치(1220)는 키패드 (keypad), 키보드 (keyboard), 또는 표시 장치 (display)이다.

- [0190] 일부 실시예들에서, 상기 메모리(1230)는 상기 제어기(1210)의 동작을 위한 코드 및/또는 데이터를 저장한다. 다른 실시예들에서, 상기 메모리(1230)는 상기 제어기(1210)에서 처리된 데이터를 저장한다. 상기 제어기(1210) 및 메모리(1230) 중 적어도 하나는 도 1a 내지 도 13를 참조하여 설명한 바와 같은 집적회로 소자(10A, 10B, 100, 200, 300, 400, 500, 600, 700, 800, 1000, 1100) 중 적어도 하나를 포함한다.

- [0191] 상기 인터페이스(1240)는 상기 집적회로 소자(1200)와, 다른 외부 장치와의 사이에서 데이터 전송 통로 역할을 한다. 상기 제어기(1210), 입/출력 장치(1220), 메모리(1230), 및 인터페이스(1240)는 버스(1250)를 통하여 서로 통신할 수 있다.

- [0192] 상기 집적회로 소자(1200)는 모바일 폰, MP3 플레이어, 네비게이션 (navigation) 시스템, 휴대용 멀티미디어 재생기 (portable multimedia player: PMP), 고상 디스크 (solid state disk: SSD), 또는 가전 제품 (household appliances)에 포함될 수 있다.

- [0193] 이상, 본 발명을 바람직한 실시예를 들어 상세하게 설명하였으나, 본 발명은 상기 실시예에 한정되지 않고, 본 발명의 기술적 사상 및 범위 내에서 당 분야에서 통상의 지식을 가진 자에 의하여 여러가지 변형 및 변경이 가능하다.

## 부호의 설명

[0194] 10A, 10B, 100, 200, 300, 400, 500, 600, 700, 800, 1000, 1100, 1200: 집적회로 소자, 20: 반도체 구조물, 22: 비아홀, 30A, 30B: TSV 구조, 32: 도전성 플러그, 32A: 금속 플러그, 32B: 제2 도전성 배리어막, 34: 제1 도전성 배리어막, 36: 절연 박막, 40: 비아 절연막, 52: 제1 도전층, 54: 제2 도전층.

#### 도면

## 도면1a

# 도면1b

## 도면4a

# *도면4b*

# 도면4c

# *도면4d*

# *도면4e*

# *도면4f*

# 도면4g

# *도면4*h

# *도면4i*

# 도면4j

# *도면4k*

# 도면4回

# 도면4n

# 도면10a

# 도면10b

# 도면10c

# 도면10d

# 도면10e

# 도면10f

# 도면10g

# 도면10h

# 도면10i

# 도면10j

# 도면10k

도면11

도면13

# <u>1200</u>