## (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2011-66070 (P2011-66070A)

(43) 公開日 平成23年3月31日(2011.3.31)

千葉県袖ヶ浦市上泉1280番地

最終頁に続く

| (51) Int.Cl. | F 1                          |                    | テーマコード (参考)       |

|--------------|------------------------------|--------------------|-------------------|

|              |                              | 21 /20             | , , , , , , ,     |

| HO1L 21/20   | (2006.01) HO 1 I             |                    | 4 K O 2 9         |

| HO1L 29/786  | •                            | 29/78 618B         | 5 F 1 O 3         |

| HO1L 21/336  | <b>(2006.01)</b> HO 1        | 29/78 618A         | 5 F 1 1 O         |

| HO1L 21/363  | <b>(2006.01)</b> HO 1 I      | 29/78 618F         | 5F152             |

| C23C 14/34   | (2006.01) HO11               | <u> </u>           |                   |

|              | 審査請求                         | 卡請求 請求項の数 16 O     | L (全 14 頁) 最終頁に続く |

| (21) 出願番号    | 特願2009-213381 (P2009-213381) | (71) 出願人 000183646 |                   |

| (22) 出願日     | 平成21年9月15日 (2009.9.15)       | 出光興産株              | 式会社               |

|              |                              | 東京都千代              | 田区丸の内3丁目1番1号      |

|              |                              | (74)代理人 100086759  |                   |

|              |                              | 弁理士 渡              | 初一夏平              |

|              |                              | (74)代理人 100112977  | ~ B !             |

|              |                              | ` '                | n <b>5</b> 7      |

|              |                              | 弁理士 田              | 中有子               |

|              |                              | (74)代理人 100141944  | ·                 |

|              |                              | 弁理士 佐              | <b>驟</b> 猛        |

|              |                              | │(72)発明者 笠見 雅司     |                   |

|              |                              | 千葉県袖ヶ              | 浦市上泉1280番地        |

|              |                              | (72)発明者 矢野 公規      |                   |

|              |                              | I ' '              | 浦市上泉1280番地        |

|              |                              | (72) 発明者 井上 一吉     |                   |

(54) 【発明の名称】多結晶薄膜、その成膜方法、及び薄膜トランジスタ

# (57)【要約】 (修正有)

【課題】十分に結晶化された多結晶薄膜を提供する。

【解決手段】インジウム元素及び酸素元素を含有した非晶質膜をスパッタリング装置で成膜し加熱することで、 X 線回折測定において 2 が 2 5 d e g ~ 3 5 d e g の範囲に観測される(2 2 2 )配向のロッキングカーブの半値全幅が 0 . 4 d e g 以下である多結晶薄膜を形成する。又、金属酸化物をスパッタリングによって成膜するに際し、プラズマの照射を 2 ~ 5 秒間隔として成膜しその後結晶化する。

【選択図】なし

#### 【特許請求の範囲】

## 【請求項1】

インジウム元素及び酸素元素を含有し、X線回折測定において 2 が 2 5 d e g ~ 3 5 degの範囲に観測される(222)配向のロッキングカーブの半値全幅が0.4deg 以下である多結晶薄膜。

(2)

# 【請求項2】

前記( 2 2 2 )配向のロッキングカーブの半値全幅が 0 . 3 d e g 以下である請求項 1 に記載の多結晶薄膜。

## 【請求項3】

金属酸化物をスパッタリングによって成膜するに際し、プラズマの照射を2~5秒間隔 として成膜する工程と、

前記工程で得た膜を結晶化する工程とを有する、請求項1又は2に記載の多結晶薄膜の 成膜方法。

# 【請求項4】

前記プラズマ照射の照射軸を、成膜対象に対し45~90°とする請求項3に記載の多 結晶薄膜の成膜方法。

## 【請求項5】

前記成膜工程時の、チャンバ内の排気圧力を 5 × 1 0 <sup>- 4</sup> ~ 1 × 1 0 <sup>- 3</sup> P a とする請 求項3又は4に記載の多結晶薄膜の成膜方法。

# 【請求項6】

前記成膜工程時に、アルゴン、酸素、水素、水蒸気及び窒素から選択されるいずれかの 1 つ以上の導入ガスを用い、スパッタ圧を 0 . 1 ~ 0 . 6 × 1 0 <sup>- 1</sup> P a とする請求項 3 ~5のいずれかに記載の多結晶薄膜の成膜方法。

#### 【請求項7】

金属酸化物をスパッタリングによって成膜するに際し、スパッタリングチャンバ内の排 気圧力を 5 × 1 0 <sup>- 4</sup> ~ 1 × 1 0 <sup>- 3</sup> P a とする多結晶薄膜の成膜方法。

## 【請求項8】

金属酸化物をスパッタリングによって成膜するに際し、アルゴン、酸素、水素、水蒸気及 び窒素から選択されるいずれかの1つ以上の導入ガスを用い、スパッタ圧を0.1~0. 6 × 1 0 <sup>- 1</sup> P a とする多結晶薄膜の成膜方法。

## 【請求項9】

前記成膜工程時のスパッタリング出力を、50~150W/4インチ とする請求項3 ~8のいずれかに記載の多結晶薄膜の成膜方法。

## 【 請 求 項 1 0 】

前記成膜工程時の酸素濃度を5~20体積%とする請求項3~9のいずれかに記載の多 結晶薄膜の成膜方法。

# 【請求項11】

前記金属酸化物が、金属酸化物を構成する全金属原子に対しインジウム原子を0.1~ 100原子%含有する請求項3~10のいずれかに記載の多結晶薄膜の成膜方法。

# 【請求項12】

前記結晶化工程が、前記成膜工程で得た膜を、酸素10~40体積%及び窒素10~8 0体積%を含む混合ガス雰囲気下にて、150~450 で0.1~1200分間熱処理 する工程である請求項3~11のいずれかに記載の多結晶薄膜の成膜方法。

# 【請求項13】

前 記 結 晶 化 工 程 の 前 後 に 、 プ ラ ズ マ ア ッ シ ン グ 処 理 及 び / 又 は U V オ ゾ ン 照 射 処 理 す る 工程を有する、請求項12に記載の多結晶薄膜の成膜方法。

#### 【請求項14】

請 求 項 3 ~ 1 3 の い ず れ か の 成 膜 方 法 に よ り 成 膜 さ れ た 多 結 晶 薄 膜 を 有 す る 薄 膜 ト ラ ン ジスタ。

# 【請求項15】

20

10

30

チャンネルエッチ型の薄膜トランジスタである請求項14に記載の薄膜トランジスタ。

# 【請求項16】

エッチストッパー型の薄膜トランジスタである請求項14に記載の薄膜トランジスタ。 【発明の詳細な説明】

【技術分野】

# [0001]

本発明は、多結晶薄膜、その成膜方法、薄膜トランジスタ及びその製造方法に関する。

#### 【背景技術】

#### [0002]

近年、表示装置の発展は目覚ましく、液晶表示装置やEL表示装置等、種々の表示装置がパソコンやワープロ等のOA機器へ活発に導入されている。これらの表示装置は、いずれも表示素子を透明導電膜で挟み込んだサンドイッチ構造を有している。

#### [00003]

上記の表示装置を駆動させる薄膜トランジスタ(TFT)等のスイッチング素子には、現在、シリコン系の半導体膜が主に使用されている。それは、シリコン系薄膜は安定性、及び加工性が良く、また、スイッチング速度が速い等の特徴があるためである。このシリコン系薄膜は、一般に化学蒸気析出法(CVD)法により作製されている。

#### [0004]

しかしながら、シリコン系薄膜が非晶質の場合、スイッチング速度が比較的遅く、高速な動画等を表示する場合は画像を表示できないという難点を有している。また、結晶質のシリコン系薄膜の場合には、スイッチング速度は比較的速いが、結晶化するために800以上の高温や、レーザーによる加熱等が必要であり、製造時に多大なエネルギーと工程を要する。また、シリコン系の薄膜は、電圧素子としても性能は優れているものの、電流を流した場合、その特性の経時変化が問題となっている。

#### [00005]

シリコン系薄膜よりも安定性に優れるとともに、ITO膜と同等の光透過率を有する透明半導体膜を得るための材料等として、酸化インジウム、酸化ガリウム及び酸化亜鉛からなるスパッタリングターゲットや、酸化亜鉛と酸化マグネシウムからなる透明半導体薄膜が提案されている(例えば、特許文献1)。酸化インジウム、酸化ガリウム及び酸化亜鉛、又は酸化亜鉛と酸化マグネシウムからなる透明半導体膜は、弱酸でのエッチング性が非常に早いという特徴がある。しかしながら、金属薄膜のエッチング液でもエッチングされるため、透明半導体膜上の金属薄膜をエッチングする場合に、半導体膜も同時にエッチングされてしまうことがある。そのため、透明半導体膜上の金属薄膜だけを選択的にエッチングする場合には不適であった。

# [0006]

一方、酸化インジウムの結晶質を含む膜、特に多結晶膜は、酸素欠損を生成しやすく、成膜時の酸素分圧を上げたり、酸化処理等をしても、キャリアー密度を 2 × 1 0 <sup>+ 1 7</sup> c m <sup>- 3</sup> にすることが困難と考えられていた。そのために、半導体膜又は T F T としての試みはほとんどなされていなかった。

# [0007]

また、特許文献2には酸化インジウムに正2価の金属酸化物を含有させたビックスバイト構造を有する酸化インジウム半導体膜が記載されている。正2価の金属酸化物を含有させることにより、キャリアー濃度を低減する試みがなされている。しかしながら、正2価の金属酸化物の場合、ビックスバイト構造のエネルギーバンド構造のバンドギャップ内に不純物順位を形成することがあり、これが、移動度を低下させる場合がある。

# [0008]

特許文献3には、結晶質の酸化インジウム薄膜を用いた薄膜トランジスタが記載されている。しかしながら、チャンネル部分のトラップ密度が高くなる場合があった。このため、S値を十分に低減できないことや、ノーマリーオンのトランジスタになる等の問題があった。また、薄膜中のトラップ密度が高いと、トラップによりオフ電流値が十分低減でき

10

20

30

00

40

ないという問題があった。

この点について、特許文献3では酸化インジウム薄膜の膜厚を20nmとすることによ り、オフ電流値が低減できることが記載されている。しかしながら、膜厚を20nmに制 御して、均一に、かつ大面積に成膜することは技術的に難しい。そのため、TFTの特性 がばらつく原因となる可能性があった。

# [00009]

また、特許文献3には、酸化インジウムからなる活性層(チャネル層)を備えたTFT の製造方法が記載されている。具体的に、アモルファスの酸化インジウム膜に熱処理して 結晶化するTFTの製造法が記載されている。この方法で得られるTFTは、FET特性 を 有 し て い る 。 し か し 、 結 晶 化 が 不 十 分 で あ る た め 半 導 体 薄 膜 の キ ャ リ ア ー 密 度 が 十 分 低 減できていない。そのため、FET特性ではノーマリーオンを示している。結晶化が不十 分であることは、XRDスペクトルから考察される(222)配向面のピークの半値幅が 広いことから把握できる。

【先行技術文献】

【特許文献】

[ 0 0 1 0 ]

【特許文献1】特開2004-119525号公報

【特許文献2】国際公開2007/058248号パンフレット

【特許文献3】特開2008-130814号公報

【発明の概要】

【発明が解決しようとする課題】

[0011]

本発明の目的は、十分に結晶化された多結晶薄膜を提供することである。

【課題を解決するための手段】

[ 0 0 1 2 ]

本発明者らは、スパッタリングによる成膜を間欠的にすることで、均一かつ平坦な非晶 質のIn ヵ0 ぇ薄膜の成膜ができ、この薄膜を加熱結晶化することにより、TFT用薄膜 として優れた性能を有する多結晶薄膜が得られることを見出し、本発明を完成させた。

本発明によれば、以下の多結晶薄膜、その成膜方法、及び薄膜トランジスタが提供され る。

1.インジウム元素及び酸素元素を含有し、X線回折測定において2 が25deg~3 5 d e g の範囲に観測される(2 2 2 )配向のロッキングカーブの半値全幅が 0 . 4 d e g以下である多結晶薄膜。

2 . 前記( 2 2 2 ) 配向のロッキングカーブの半値全幅が 0 . 3 d e g 以下である 1 に記 載の多結晶薄膜。

3.金属酸化物をスパッタリングによって成膜するに際し、プラズマの照射を2~5秒間 隔として成膜する工程と、

前記工程で得た膜を結晶化する工程とを有する、1又は2に記載の多結晶薄膜の成膜方

4 . 前記プラズマ照射の照射軸を、成膜対象に対し45~90°とする3に記載の多結晶 薄膜の成膜方法。

5 . 前記成膜工程時の、チャンバ内の排気圧力を 5 × 1 0 <sup>- 4</sup> ~ 1 × 1 0 <sup>- 3</sup> P a とする 3又は4に記載の多結晶薄膜の成膜方法。

6.前記成膜工程時に、アルゴン、酸素、水素、水蒸気及び窒素から選択されるいずれか の 1 つ以上の導入ガスを用い、スパッタ圧を 0 . 1 ~ 0 . 6 × 1 0 <sup>- 1</sup> P a とする 3 ~ 5 のいずれかに記載の多結晶薄膜の成膜方法。

7.金属酸化物をスパッタリングによって成膜するに際し、スパッタリングチャンバ内の 排気圧力を5×10・4~1×10・3 Раとする多結晶薄膜の成膜方法。

8.金属酸化物をスパッタリングによって成膜するに際し、アルゴン、酸素、水素、水蒸 気及び窒素から選択されるいずれかの1つ以上の導入ガスを用い、スパッタ圧を0.1~

10

20

30

40

- 0 . 6 × 1 0 <sup>- 1</sup> P a とする多結晶薄膜の成膜方法。

- 9. 前記成膜工程時のスパッタリング出力を、 50 ~ 150 W / 4 インチ とする 3 ~ 8 のいずれかに記載の多結晶薄膜の成膜方法。

- 10.前記成膜工程時の酸素濃度を5~20体積%とする3~9のいずれかに記載の多結晶薄膜の成膜方法。

- 11.前記金属酸化物が、金属酸化物を構成する全金属原子に対しインジウム原子を0.

- 1 ~ 1 0 0 原子 % 含有する 3 ~ 1 0 のいずれかに記載の多結晶薄膜の成膜方法。

- 12.前記結晶化工程が、前記成膜工程で得た膜を、酸素10~40体積%及び窒素10~80体積%を含む混合ガス雰囲気下にて、150~450 で0.1~1200分間熱処理する工程である3~11のいずれかに記載の多結晶薄膜の成膜方法。

- 13.前記結晶化工程の前後に、プラズマアッシング処理及び/又はUVオゾン照射処理 する工程を有する、12に記載の多結晶薄膜の成膜方法。

- 1 4 . 上記 3 ~ 1 3 のいずれかの成膜方法により成膜された多結晶薄膜を有する薄膜トランジスタ。

- 1 5 . チャンネルエッチ型の薄膜トランジスタである1 4 に記載の薄膜トランジスタ。

- 16.エッチストッパー型の薄膜トランジスタである14に記載の薄膜トランジスタ。

## 【発明の効果】

[ 0 0 1 3 ]

本発明により、十分に結晶化された多結晶薄膜が提供できる。この薄膜は、キャリアー密度を十分に低減しているため、TFTに使用することにより、高移動度かつノーマリーオフであるTFTが得られる。

【図面の簡単な説明】

[0014]

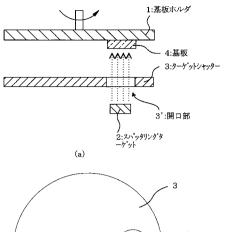

- 【図1】公転プラズマ法を利用したスパッタリングによる成膜方法を説明するための概念図であり、(a)はスパッタリング装置の真空チャンバ内を図示したものであり、(b)はターゲットシャッターの概略上面図である。

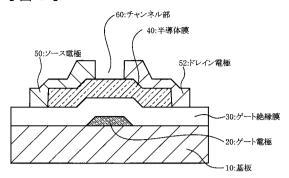

- 【図2】本発明の薄膜トランジスタの実施形態を示す概略断面図である。

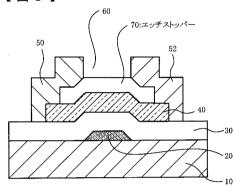

- 【 図 3 】 本 発 明 の 薄 膜 ト ラ ン ジ ス タ の 他 の 実 施 形 態 を 示 す 概 略 断 面 図 で あ る 。

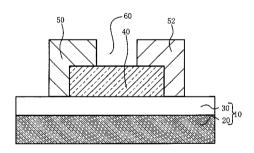

- 【図4】実施例1で作製した薄膜トランジスタの概略断面図である。

- 【 図 5 】 実 施 例 1 で 作 製 した 薄 膜 の ( 2 2 2 ) 配 向 の ロ ッ キ ン グ カ ー ブ で あ る 。

- 【 図 6 】 実 施 例 5 で 作 製 した 薄 膜 の ( 2 2 2 ) 配 向 の ロ ッ キ ン グ カ ー ブ で あ る 。

- 【図7】実施例6で作製した薄膜の(222)配向のロッキングカーブである。

- 【発明を実施するための形態】

- [0015]

本発明の多結晶薄膜は、インジウム元素及び酸素元素を含有し、 X 線回折測定においてロッキングカーブの 2 5 d e g ~ 3 5 d e g の範囲に観測される( 2 2 2 )配向の半値全幅が 0 . 4 d e g 以下であることを特徴とする。本条件を満たす薄膜は、結晶性のよい半導体膜である。

ここで、ロッキングカーブはRigaku社製SmartLabにより測定し、(222)配向ピークの半値全幅を算出して求めたものである。半値幅は、まずロッキングカーブの25deg~35degの範囲でバックグラウンドを差し引き、その後、Lorentz型関数、Gauss型関数、Voigt型関数のいずれかを用いて、ピークをフィットしたものの半値全幅である。

バックグラウンドを差し引く方法としては、例えば、バックグラウンドを関数で表現し、ロッキングカーブのグラフの値から差し引く方法、基板のXRDスペクトルの測定値をロッキングカーブのグラフの値から差し引く方法等が挙げられる。

[0016]

ロッキングカーブの配向ピークの半値全幅は、結晶性、均一性を示し、幅が狭いほど結晶性の高い均一な多結晶であることを示している。そのため、酸化インジウム結晶に見られる(222)配向ピークの半値全幅は0.3deg以下であることが好ましい。

10

20

30

40

### [0017]

本発明の多結晶薄膜は、例えば、金属酸化物をスパッタリングによって成膜するに際し、成膜対象へのプラズマの照射を間欠的にすることにより成膜し、その後、加熱することにより得ることができる。具体的に、スパッタの照射を 2 ~ 5 秒間隔として成膜する工程と、この工程で得た膜を結晶化する工程と、を有する成膜方法によって得ることができる

成膜工程としては、例えば、金属酸化物からなるスパッタリングターゲットを使用した公転プラズマ法による成膜が採用できる。

# [0018]

図1は公転プラズマ法を利用したスパッタリングによる成膜方法を説明するための概念図である。図1(a)はスパッタリング装置の真空チャンバ内を図示したものであり、(b)はターゲットシャッターの概略上面図である。チャンバ内には、円板状の基板ホルダー1があり、円板の中心を軸として回転するように設置されている。基板ホルダー1に対向する位置にスパッタリングターゲット2が設置されている。基板ホルダー1とスパッタリングターゲット2の間には、ターゲットシャッター3が設けられている。ターゲットシャッター3は、ターゲット1をプラズマにてスパッタすることで発生するスパッタ粒子の進行方向や堆積箇所を制御するものである。

# [0019]

本装置では、基板ホルダー1に取り付けられた基板4は、ホルダー1の回転により円軌道を描いて移動する(公転)。そのため、基板はターゲットシャッター3の開口部3<sup>1</sup>上を一定の周期で通過することになる。基板がターゲットシャッターの開口部付近上に位置するときのみ、スパッタ粒子が基板に到達し、堆積することになる。尚、図1(a)の点線矢印はスパッタ粒子の進行方向を示している。

#### [0020]

本発明では、スパッタの照射を 2 ~ 5 秒間隔として成膜する。例えば、上記の装置では、基板ホルダー 1 の回転速度やターゲットシャッター 3 の開口部 3 'の形状を調整することにより、照射時間を制御する。照射時間は 2 ~ 5 秒間とし、照射間(未照射時間)を 1 ~ 1 5 秒間とする。

基板にスパッタ粒子を堆積させて、薄膜を形成する。膜の厚さは用途等を考慮して適宜調整すればよいが、通常、薄膜トランジスタ用途では10nm~60nmが好ましく、20nm~50nmがより好ましく、20nm~40nmがさらに好ましく、特に好ましくは20nm~30nmである。半導体層の膜厚が10nm以下は工業的に均一な薄膜を得ることが難しく、また60nm以上では成膜時間が長くなり、薄膜トランジスタの性能が低下する。

## [ 0 0 2 1 ]

本発明ではスパッタ照射の照射軸を、成膜対象に対し30°~90°とすることが好ましく、さらに45°~90°が好ましく、特に90°(垂直、図1(a)の点線矢印方向)とすることが好ましい。これにより均一でターゲットとの組成ズレが少ない薄膜を得ることができる。

#### [0022]

成膜工程前の、チャンバ内の排気圧力は  $5 \times 10^{-4} \sim 8 \times 10^{-3}$  Paとすることが好ましく、ちらに、  $8 \times 10^{-4} \sim 7 \times 10^{-3}$  Paとすることが好ましく、特に  $1 \times 10^{-3} \sim 5 \times 10^{-3}$  Paとすることが好ましい。これにより、成膜直後に均一な非晶質膜を得ることができ、加熱処理後に結晶性の良い半導体薄膜を得ることができる。排気圧力が  $5 \times 10^{-4}$  Pa未満では、成膜時に低質な結晶が生成してしまうことがあり、加熱処理後も均一な多結晶膜が得られない可能性がある。また排気圧力が  $8 \times 10^{-3}$  Pa超では基板から薄膜が剥離してしまう可能性がある。

#### [0023]

成膜工程時におけるスパッタガスは、アルゴン、酸素、水素、水蒸気及び窒素から選択される1つ又は2つ以上の導入ガスを用いることが好ましい。また、スパッタ圧は0.1

10

20

30

40

$\sim 0.6 \times 10^{-1} Pa とすることが好ましい。$

また、成膜工程時のスパッタリング出力は、 5 0 ~ 1 5 0 W / 4 インチ とすることが 好ましい。

成膜工程時の酸素濃度は5~20体積%とすることが好ましい。

# [0024]

ターゲットである金属酸化物は、金属酸化物を構成する全金属原子に対しインジウム原子を0.1~100原子%含有するものが好ましい。例えば、酸化インジウムや、酸化インジウムに対して、酸化亜鉛(ZnO)を0.1wt%~8wt%含有するもの、酸化インジウムに対して、酸化ガリウム( $Ga_2O_3$ )を0.1wt%~8wt%含有するもの、酸化インジウムに対して、酸化銅(CuO)を0.05wt%~7wt%含有するもの等が挙げられる。

[0025]

上述した成膜工程で得た膜は非晶質(アモルファス)であり、加熱等により結晶化させることにより、本発明の多結晶薄膜を得る。結晶化には、酸素の存在下にランプアニ ル 装置、レーザーアニール装置、熱風加熱装置、接触加熱装置等を用いることができる。

本発明では、上述した成膜工程で形成したアモルファス薄膜を結晶化させることにより、XRDスペクトルから見られる半値幅が狭く、結晶性の良い半導体膜が得られる。

[0026]

結晶化工程としては、成膜工程で得た膜を、酸素10~40体積%及び窒素10~80体積%を含む混合ガス雰囲気下にて、加熱処理することが好ましい。処理温度は150~450 が好ましい。150 未満では、半導体膜が十分に結晶化しない場合があり、450 超では、基板や半導体膜にダメージを与える場合がある。熱処理温度は、180~350 がさらに好ましく、特に200 ~300 が好ましい。

処理時間は0.1~1200分間が好ましい。熱処理時間が0.1分未満では、熱処理時間が短すぎて膜の結晶化が不十分となる場合があり、1200分超では時間が掛かりすぎ生産的ではない。熱処理時間は、1分~600分がさらに好ましく、特に5分~60分が好ましい。

[0027]

本発明では、結晶化工程の前後に、プラズマアッシング処理及び / 又は U V オゾン照射処理することが好ましい。これにより、パターニング、保護膜(又はエッチストッパー)等の各作製工程により、半導体膜中の酸素が抜け、キャリアー密度が低下することを防ぐことができる。

[0028]

尚、本発明の薄膜は、成膜時の薄膜表面の温度を、40~60 である高温域と、35以下である低温域とに制御し、これら温度域を交互に繰り返して成膜することによっても得ることができる。この成膜方法では、反跳アルゴンによるダメージによってスパッタ粒子となったインジウム元素と酸素元素の、基板上における結合阻害を低減できる。そのため、良質な非晶質膜を形成でき、これを加熱処理することで多結晶薄膜を形成することが期待できる。

ここで、基板上に成膜された薄膜の表面温度は、例えば、四線式白金測温抵抗体を使用した電位差計四端子抵抗測定法や、赤外線放射測定による温度センサーにより測定できる

[0029]

成膜工程においては、高温域での成膜を 0 . 1 ~ 3 秒間、好ましくは 0 . 5 ~ 2 秒間とし、低温域での成膜を 1 ~ 1 0 秒間、好ましくは 1 . 5 ~ 5 秒間とし、高温域での成膜と低温域での成膜を交互に繰り返すことが好ましい。

高温域及び低温域について、例えば、成膜対象にプラズマを照射することで、高温域の 条件を形成することができ、プラズマの照射を停止することで低温域の条件を形成できる

また、スパッタリングターゲットの背面にマグネットを配置し、これを揺動させること

10

20

30

40

によっても、高温域と低温域を変動させることができる。

この場合、マグネットの揺動の周期は15秒~45秒とすることが好ましく、特に、15秒~30秒とすることが好ましい。

#### [0030]

また、本発明の薄膜は、金属酸化物をスパッタリングによって成膜するに際し、スパッタリングチャンバ内の排気圧力を  $5\times10^{-4}\sim1\times10^{-3}$  Paとすることによっても成膜できる。

さらに、金属酸化物をスパッタリングによって成膜するに際し、アルゴン、酸素、水素、水蒸気及び窒素から選択されるいずれかの1つ以上の導入ガスを用い、スパッタ圧を 0 . 1 ~ 0 . 6 × 1 0 <sup>- 1</sup> P a とすることによっても成膜できる。

## [0031]

本発明の多結晶薄膜は、薄膜トランジスタの構成層に好適に使用できる。以下、薄膜トランジスタに適用した例を説明する。

## [0032]

図2は、本発明の薄膜トランジスタの実施形態を示す概略断面図である。

薄膜トランジスタは、基板10及び絶縁膜30の間にゲート電極20を挟持しており、ゲート絶縁膜30上には半導体膜40が活性層として積層されている。さらに、半導体膜40の端部付近を覆うようにしてソース電極50及びドレイン電極52がそれぞれ設けられている。半導体膜40、ソース電極50及びドレイン電極52で囲まれた部分にチャンネル部60を形成している。

尚、図2の薄膜トランジスタはいわゆるチャンネルエッチ型薄膜トランジスタである。 本発明の薄膜トランジスタは、チャンネルエッチ型薄膜トランジスタに限定されず、本技術分野で公知の素子構成を採用できる。例えば、エッチストッパー型の薄膜トランジスタでもよい。

#### [0033]

図3は、本発明の薄膜トランジスタの他の実施形態を示す概略断面図である。尚、上述した薄膜トランジスタと同じ構成部材には同じ番号を付し、その説明を省略する。

薄膜トランジスタは、エッチストッパー型の薄膜トランジスタである。薄膜トランジスタは、チャンネル部60を覆うようにエッチストッパー70が形成されている点を除き、上述した薄膜トランジスタと同じ構成である。半導体膜40の端部付近及びエッチストッパー70の端部付近を覆うようにしてソース電極50及びドレイン電極52がそれぞれ設けられている。

### [0034]

本発明の薄膜トランジスタは、半導体膜40に上述した本発明の多結晶薄膜を使用している。この薄膜は、キャリアー密度を十分に低減しているため、トランジスタに使用することにより、高移動度かつノーマリーオフとなる。

### [ 0 0 3 5 ]

本発明の薄膜トランジスタにおいて、基板、ゲート電極、ゲート絶縁膜、ソース・ドレイン電極等の構成部材は、公知のものが使用でき、特に限定されない。

例えば、各電極にはA1、Cu、Au等の金属薄膜が使用でき、ゲート絶縁膜には、酸化シリコン膜、酸化ハフニウム膜等の酸化物薄膜を使用できる。

#### [0036]

本発明の薄膜トランジスタは、上述した成膜工程でアモルファス薄膜(多結晶薄膜の前駆体)を成膜する成膜工程と、この膜を結晶化する工程を含む。尚、ゲート電極、ゲート絶縁膜、ソース・ドレイン電極等の構成部材は、公知の方法により形成できる。

# [0037]

例えば、基板上にA1、Cu、Au等の金属薄膜からなるゲート電極を形成し、その上に、酸化シリコン膜、酸化ハフニウム膜等からなる酸化物薄膜をゲート絶縁膜として形成する。その上に、金属マスクを装着して必要な部分だけに上述した本発明の製造方法により金属酸化物からなるアモルファス膜を形成する。その後、金属マスクを用いて、必要部

10

20

30

40

分にソース・ドレイン電極を形成することで、薄膜トランジスタを製造することができる

## [0038]

本発明の薄膜トランジスタの製造方法では、アモルファス薄膜の形成後、薄膜を結晶化する。結晶化工程は、酸化処理を兼ねていてもよい。

アモルファス薄膜の結晶化には、酸素の存在下にランプアニ ル装置、レーザーアニール装置、熱風加熱装置、接触加熱装置等を用いることができる。処理条件は、上述した多結晶薄膜の結晶化工程と同様である。

尚、アモルファス薄膜の結晶化は、膜の形成後、すぐに実施してもよく、また、ソース・ドレイン電極等、他の構成部材の形成後に実施してもよい。

[0039]

本発明の製造方法は、特に、チャンネルエッチ型の薄膜トランジスタの製造方法に適している。本発明の多結晶薄膜は結晶質であるため、A1等の金属薄膜からソース・ドレイン電極及びチャンネル部を形成する方法として、フォトリソグラフィを使用したエッチング工程を採用できる。即ち、金属薄膜を除去するエッチング液では、半導体膜(多結晶薄膜)はエッチングされず、金属薄膜を選択的にエッチングできる。尚、エッチストッパー型の薄膜トランジスタの製造方法であってもよい。

# 【実施例】

# [0040]

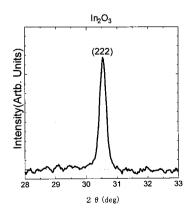

# 実施例1

( A ) 薄膜トランジスタの作製

図4に示す逆スタガ型のチャンネルエッチ型の薄膜トランジスタを作製した。

1 0 0 n m 厚みの熱酸化膜(SiO<sub>2</sub> 膜)付きの導電性シリコン基板(KSTワールド社製) 1 0 を使用した。熱酸化膜がゲート絶縁膜 3 0 として機能し、導電性シリコン部(n 型高ドープSi)がゲート電極 2 0 として機能する。

ゲート絶縁膜30上に、酸化インジウムターゲット(純度99.9%)を用いて、公転プラズマスパッタリング法で50nmの半導体膜40を成膜した。

尚、公転プラズマスパッタリング装置は新港精機製(チャンバサイズ1100mm×480mm)を使用し、以下の条件で成膜した。

# [ 0 0 4 1 ]

・スパッタの形式:図1(a)に示す装置を使用し、基板を基板ホルダー中心を軸として公転(公転速度:6rpm)させ、スパッタを間欠照射した。照射時間は2~5秒間とし、照射間を1~15秒間とした。

- ・基板に対するプラズマの照射角:90°

- チャンバ内の排気圧力: 5 × 1 0 <sup>- 4</sup> P a

- ・スパッタガス: Ar

- ・スパッタ圧:1.2×10<sup>-1</sup>Pa

- ・プラズマ出力: R F 1 0 0 W / 4

- ・ターゲットと基板間の距離 ( T S 距離 ) : 1 0 c m

- ・基板温度(ホルダー側):室温

- ・成膜速度:5 nm/min

- 連続成膜時間:10分間

# [0042]

半導体膜40を所望の形状にパターニングした。レジストとしてOFPR 800(東京応化工業製)を使用し、塗布、プレベーク(80、5分)、露光した。現像後、ポストベーク(120、5分)し、硝酸第二セリウムアンモニウム(CAN)にてエッチングした。

パターニングした半導体膜40を、大気下300 で60分熱処理して結晶化した。

## [ 0 0 4 3 ]

その後、半導体膜の上端部周辺及び側部に、リフトオフにてTi(50nm)/Au(

20

10

30

30

40

1 0 0 n m) / T i ( 5 0 n m)からなるソース電極及びドレイン電極を形成した。尚、レジストにはO F P R 8 0 0を使用し、各電極層は

RFスパッタ法で形成した。

このようにしてソース・ドレイン電極間間隙 ( L ) が 1 0 μm、幅 ( W ) が 2 0 μmである図 4 の構成を有する薄膜トランジスタを作製した。

[0044]

(B) 半導体膜の評価

石英ガラス基板上に、上記(A)の公転スパッタリングと同じ条件にて半導体膜を形成した。その後、熱風加熱炉内で、空気中、300 で60分間熱処理した。得られた半導体膜のX線回折(XRD)測定をしたところ、酸化インジウムの結晶ピークが観察された。これにより、半導体膜が結晶質であることが確認できた。

10

[0045]

実施例2

[0046]

実施例3

実施例 1 において、ソース・ドレイン電極間間隙(L)を20μmとし、実施例 2 と同様にアニール処理した他は、実施例 1 と同様にして薄膜トランジスタを作製し、半導体膜を評価した。

20

[0047]

実施例4

ソース・ドレイン電極の幅(W)を 1 0 0 μ m とした他は、実施例 3 と同様にして薄膜トランジスタを作製し、半導体膜を評価した。

[0048]

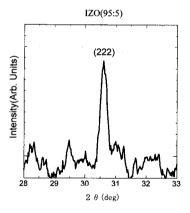

実施例5

実施例1において、酸化インジウムターゲットに代えて、酸化インジウム・酸化亜鉛(IZO:登録商標)ターゲット(In<sub>2</sub>O<sub>3</sub>:95wt%、ZnO:5wt%)を用い、実施例2と同様にアニール処理した他は、実施例1と同様にして薄膜トランジスタを作製し、半導体膜を評価した。

30

[0049]

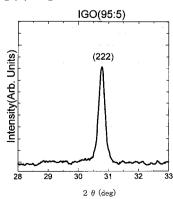

実施例6

実施例 1 において、酸化インジウムターゲットに代えて、酸化インジウム・酸化ガリウム(IGO)ターゲット(In $_2$ О $_3$ : 9 5 w t %、Ga $_2$ О $_3$ : 5 w t %)を用い、実施例 2 と同様にアニール処理した他は、実施例 1 と同様にして薄膜トランジスタを作製し、半導体膜を評価した。

[0050]

評価

上記実施例1-6で作製した薄膜トランジスタについて、オンオフ(on/off)比、オフ電流、電界効果移動度(μ)S値及び閾値電圧(Vth)を評価した。半導体パラメーターアナライザー(ケースレーインスツルメンツ社製4200SCS)を用い、室温、遮光環境下(シールドボックス内)で測定した。尚、ドレイン電圧(Vd)は1Vとした。

40

また、半導体膜のX線回折により、結晶性又は非晶性について評価した。結果を表 1 に示す。また、薄膜の(2 2 2 )配向のロッキングカーブから求めた半値全幅及び薄膜形成時における薄膜表面の温度を表 2 に示す。

図 5 - 7 に実施例 1 , 5 , 6 で作製した薄膜の(2 2 2 ) 配向のロッキングカーブを示す。尚、実施例 2 - 4 のロッキングカーブは実施例 1 と同様である。

[0051]

# 【表1】

|              | 実施例1                 | 実施例2                   | 実施例3                        | 実施例4                      | 実施例 5                  | 実施例6                   |

|--------------|----------------------|------------------------|-----------------------------|---------------------------|------------------------|------------------------|

| ターゲットの種類     | $In_20_3$            | $In_2O_3$              | $\mathrm{In}_2\mathrm{O}_3$ | $\operatorname{In}_2 0_3$ | 0ZI                    | 091                    |

| 半導体膜の性状      | 結晶性                  | 結晶性                    | 結晶性                         | 結晶性                       | 結晶性                    | 結晶性                    |

| 直前アニール処理     | 無し                   | 64                     | 48                          | \$1                       | \$ P                   | \$0                    |

| on/off 比     | $1.00\times10^{11}$  | 1. $80 \times 10^{11}$ | $4.03\times10^{10}$         | $1.05 \times 10^{11}$     | $5.30 \times 10^{8}$   | $1.00 \times 10^{9}$   |

| Off 電流(A)    | $1.00\times10^{-14}$ | $2.80 \times 10^{-15}$ | $5.30 \times 10^{-15}$      | 7. $80 \times 10^{-15}$   | $2.90 \times 10^{-13}$ | $1.00 \times 10^{-14}$ |

| 移動度 (cm²/Vs) | 40.3                 | 20.6                   | 24.6                        | 12.6                      | 25.3                   | 41.3                   |

| S 值 (V/dec.) | 0.4                  | 0.4                    | 0.3                         | 0.3                       | 0.3                    | 1.1                    |

| Vth (V)      | 2.7                  | -0.8                   | 0.3                         | -2.9                      | 5.7                    | 0.5                    |

[ 0 0 5 2 ]

10

20

30

# 【表2】

|       | t°∽ク位置 | 半値全幅   | 低温時*1の | 高温時*1の  |  |

|-------|--------|--------|--------|---------|--|

|       |        |        | 薄膜表面温度 | 薄膜表面温度  |  |

| 実施例 1 | 30. 5° | 0. 26° | 31.0℃  | 40. 2℃  |  |

| 実施例 2 | 30. 5° | 0. 26° | 31.0℃  | 40. 2℃  |  |

| 実施例3  | 30. 5° | 0. 26° | 31. 0℃ | 40. 2℃  |  |

| 実施例4  | 30. 5° | 0. 26° | 31. 0℃ | 40. 2°C |  |

| 実施例 5 | 30. 6° | 0. 21° | 30. 5℃ | 40. 0℃  |  |

| 実施例 6 | 30.8°  | 0. 25° | 31. 5℃ | 40. 3℃  |  |

\*1:高温時の薄膜表面温度とは、基板へのスパッタ粒子照射時の最高温度を、低温時の薄膜表面温度とは、未照射時の最低温度を意味する。

## 【産業上の利用可能性】

[0053]

本発明の多結晶薄膜は、薄膜トランジスタ、半導体メモリー、発光ダイオード素子、レーザー素子等の構成部材として好適である。

本発明の薄膜トランジスタは、ディスプレイ用パネル、RFIDタグ、X線ディテクタ パネル・指紋センサー・フォトセンサー等のセンサー等に好適に使用できる。

# 【符号の説明】

# [0054]

- 1 基板ホルダー

- 2 スパッタリングターゲット

- 3 ターゲットシャッター

- 3 ' 開口部

- 4 基板

- 10 基板

- 20 ゲート電極

- 3 0 ゲート絶縁膜

- 40 半導体膜(多結晶膜)

- 5 0 ソース電極

- 52 ドレイン電極

- 60 チャンネル部

- 70 エッチストッパー

10

20

30

【図1】

(b)

【図2】

【図3】

【図4】

【図6】

【図5】

【図7】

# フロントページの続き

| (51) Int.CI.       |         |      | FΙ   |         |       |      |       |      | テーマコード(参考) |

|--------------------|---------|------|------|---------|-------|------|-------|------|------------|

|                    |         |      | (    | 230     | 14/   | 34   |       | Ν    |            |

|                    |         |      | (    | 230     | 14/   | 34   |       | R    |            |

|                    |         |      | ŀ    | H 0 1 I | _ 29/ | 78   | 6 2 7 | G    |            |

|                    |         |      | ŀ    | H 0 1 I | _ 29/ | 78   | 6 2 0 |      |            |

|                    |         |      |      |         |       |      |       |      |            |

| F ターム(参考) 4K029 AA | 06 AA24 | BA45 | BB07 | CA05    | CA06  | DC05 | EA03  | EA05 | FA01       |

| G <i>A</i>         | 01 GA02 | JA02 |      |         |       |      |       |      |            |

| 5F103 AA           | 08 BB22 | BB38 | DD30 | GG02    | HH03  | LL13 | NN05  | NN10 | PP03       |

| RF                 | 05      |      |      |         |       |      |       |      |            |

| 5F110 A            | 01 BB01 | BB09 | CC07 | DD05    | EE02  | EE03 | EE08  | FF01 | FF02       |

| FF                 | 23 GG01 | GG06 | GG13 | GG17    | GG25  | GG28 | GG29  | GG43 | HK02       |

| H                  | 03 HK04 | HK22 | HK33 | NN12    | PP01  | PP02 | PP03  | PP10 | PP13       |

| PF                 | 26 PP31 | PP38 | QQ14 |         |       |      |       |      |            |

| 5F152 A            | 07 AA08 | BB03 | CC08 | CD13    | CE01  | CE08 | CE16  | CE24 | CE28       |

| CE                 | 42 CE47 | EE14 | EE16 | FF01    | FF11  | FF21 | FF24  | FF36 | FF37       |

| FF                 | 39 LL10 | MM04 | NN03 | NP13    | NQ01  | NQ07 | NQ13  | NQ17 |            |