(19) RÉPUBLIQUE FRANÇAISE

## INSTITUT NATIONAL DE LA PROPRIÉTÉ INDUSTRIELLE

**PARIS**

11) N° de publication :

2 639 494

(à n'utiliser que pour les commandes de reproduction

(21) N° d'enregistrement national :

88 14989

(51) Int CI<sup>5</sup>: H 04 L 1/00, 12/28; H 04 B 15/00

## DEMANDE DE BREVET D'INVENTION

Α1

- (22) Date de dépôt : 18 novembre 1988.

- (30) Priorité :

71) Demandeur(s): Société dite: THOMSON-CSF. société anonyme. — FR.

- Date de la mise à disposition du public de la demande : BOPI « Brevets » n° 21 du 25 mai 1990.

- 60 Références à d'autres documents nationaux apparentés :

- (72) Inventeur(s): Didier Pirez, Thomson-CSF, SCPI.

- 73) Titulaire(s):

- (74) Mandataire(s): G. Lincot, Thomson-CSF, SCPI.

- (54) Procédé et dispositif de restitution de signaux numériques affectés d'interférence intersymbole.

- 67) Le domaine de l'invention est celui de la restitution de la valeur d'origine de symboles numériques, notamment de symboles binaires, qui ont subi le phénomène dit d'interférence intersymbole.

L'objectif de l'invention est en conséquence de fournir un procédé et un dispositif de restitution de faible complexité et applicable dans les cas où la valeur d'origine du symbole courant reste prépondérante à la réception.

Cet objectif est atteint à l'aide d'un procédé caractérisé en ce qu'il consiste à effectuer la décision de la valeur du symbole reçu à l'aide d'un seuil de décision variable, en fonction de la valeur desdits symboles adjacents, et en ce que ledit seuil est défini comme étant la moyenne des valeurs des symboles adjacents, pondérées par des coefficients représentatifs de l'interférence intersymbole.

## PROCEDE ET DISPOSITIF DE RESTITUTION DE SIGNAUX NUMERIQUES AFFECTES D'INTERFERENCE INTERSYMBOLE

Le domaine de l'invention est celui de la restitution de la valeur d'origine de symboles numériques, notamment de symboles binaires, qui ont subi le phénomène dit d'interférence intersymbole.

L'interférence intersymbole se traduit par le fait que, à la réception, la valeur de chaque symbole reçu est fonction non seulement de la valeur d'origine du symbole, mais encore, dans une mesure plus ou moins grande, de la valeur des symboles adjacents.

L'interférence intersymbole peut avoir plusieurs causes.

Au nombre des causes de l'interférence intersymbole, il faut notamment compter les effets secondaires des chaînes de filtrage de signaux numériques.

En outre, dans un certain nombre d'applications, la création d'interférence intersymbole dans un signal numérique est délibérée. Ainsi, les techniques de modulation à "phase continue" consistent à moduler un signal à enveloppe constante par un train de symboles binaires, de façon que la variation de phase due à un élément binaire soit étalée sur plusieurs éléments binaires successives. Ce type de modulation est notamment utilisé lorsqu'on souhaite réduire l'encombrement spectral du signal modulé.

L'un des problèmes importants rencontrés en relation avec l'interférence intersymbole est la restitution de la valeur d'origine de chaque élément du train numérique, par exemple en sortie de chaine de filtrage, ou à la démodulation.

On connaît notamment deux procédés de redressement de l'interférence intersymbole.

Selon un premier procédé connu, on utilise un dispositif d'égalisation par filtrage. Il s'agit en général d'un filtre FIR (Filtre à réponse impulsionnelle finie), placé à la sortie d'une chaine de filtrage productrice d'interférence intersymbole. Les caractéristiques du filtre de correction sont choisies de façon que le produit de convolution de sa fonction de transfert avec la fonction de transfert de la chaine

15

10

5

20

25

30

restitue le signal numérique d'origine. Le démodulateur décrit dans la demande de brevet français n° 8304982 au nom du même déposant, utilise un tel système pour supprimer l'interférence intersymbole derrière un filtrage adapté à la modulation, dans le cas de modulations de fréquence à phase contrôlée.

Toutefois, filtre d'égalisation type đe ce généralement muni de prises (espacées d'un symbole) présentes ne constitue donc souvent qu'une fini. Il nombre filtre qui annulerait totalement d'un approximation d'autant intersymbole, approximation l'interférence mauvaise que le nombre de prises est faible.

De plus, ce procédé existant présente l'inconvénient de diminuer le rapport signal à bruit, du fait que sa fonction de transfert est dans la plupart des cas celle d'un filtre passehaut.

On connaît également un second procédé de restitution de signaux affectés d'interférence intersymbole comme décrit dans la demande de brevet française  $n^{\rm o}$  8307798 déposée le 10 mai 1983 au nom du même déposant.

Le principe de fonctionnement de ce procédé connu est d'utiliser au mieux l'information contenue dans le signal reçu en ne prenant la décision sur le symbole n qu'après avoir observé le signal aux instants n+1, n+2, .... n+L, L étant le retard de la décision.

type appliquant ce dispositifs Les structure optimale général de la s'approchent en restitution. La demande de brevet citée décrit l'utilisation d'un algorithme de VITERBI pour explorer tous les scénarios possibles d'interférence intersymbole à partir des valeurs du signal reçu, et effectuer la décision retardée sur la valeur du scénario d'interférence fonction du symbole courant en fournissant un résultat théorique le plus proche de la réalité.

Bien entendu, l'inconvénient de ces systèmes est leur complexité.

L'objectif de l'invention est en conséquence de fournir un procédé et un dispositif de restitution de la valeur d'origine de signaux numériques affectés d'interférence intersymbole, qui soient de faible complexité, et puissent convenir à des situations où le phénomène d'interférence

15

10

5

20

25

30

intersymbole n'est pas trop important. Plus précisément, l'invention doit pouvoir s'appliquer dans les cas où la valeur d'origine du symbole courant reste prépondérante à la réception.

5

Un autre objectif de l'invention est de permettre une restitution du signal numérique d'origine qui soit compatible avec des dispositifs de démodulation de signaux modulés en évasion de fréquence. Dans ce type de situation, chaque bloc reçu doit pouvoir être restitué dans son intégralité, malgré l'interférence intersymbole, y compris bien entendu pour les tous premiers et les tous derniers symboles du bloc.

10

Un objectif complémentaire de l'invention est de fournir un procédé et un dispositif limitant la dégradation du rapport signal sur bruit dans la chaine de réception.

15

Ces objectifs, ainsi que d'autres qui apparaitront par la suite, sont atteints à l'aide d'un procédé de restitution de la valeur d'origine de signaux numériques binaires affectés d'interférence intersymbole, et dont le signal reçu peut être modélisé, à chaque période bit, essentiellement comme une combinaison linéaire du bit source correspondant avec les bits sources précédent et suivant dans la séquence numérique source,

20

procédé caractérisé en ce qu'il consiste à effectuer la décision de la valeur du bit reçu à l'aide d'un seuil de décision, variable en fonction de la valeur desdits bits précédent et suivant.

25

De façon plus générale, l'invention a pour objet un procédé de restitution de la valeur d'origine de signaux numériques affectés d'interférence intersymbole, et dont le signal reçu peut être modélisé, à chaque période bit, comme étant une combinaison linéaire du symbole source correspondant et des symboles sources adjacents,

30

procédé caractérisé en ce qu'il consiste à effectuer la décision de la valeur du symbole reçu à l'aide d'un seuil de décision variable, en fonction de la valeur desdits symboles adjacents.

35

De façon avantageuse, ladite valeur des symboles adjacents précédents, bit précédent respectivement, est la valeur décidée pour le signal reçu à la période bit précédente, et la valeur des symboles adjacents suivants, bit suivant

respectivement, est temporairement pré-décidée, à partir du signal reçu à la période bit suivante, avec un seuil de décision nul.

Avantageusement, ledit seuil est défini comme étant la moyenne des valeurs des symboles adjacents, bits adjacents respectivement, pondérées par des coefficients représentatifs de la combinaison linéaire de modélisation.

L'invention a également pour objet un dispositif de restitution de signaux numériques binaires affectés d'interférence intersymbole, et dont le signal reçu peut être modélisé, à chaque période bit, essentiellement comme une combinaison linéaire du bit source correspondant avec le bit source précédent et le bit source suivant dans la séquence numérique source,

dispositif caractérisé en ce qu'il comprend :

- des moyens de retardement du bit courant reçu, pendant la durée d'une période bit ;

- des moyens de mémorisation de la valeur décidée pour le bit reçu précédent ;

- des moyens de choix du seuil de décision de la valeur du bit courant retardé, en fonction de la valeur reçue du bit suivant et de la valeur mémorisée du bit reçu précédent ;

- des moyens de comparaison dudit bit courant reçu retardé avec ledit seuil choisi, lesdits moyens de comparaison fournissant en sortie la valeur décidée pour ledit bit courant reçu.

Dans un mode de réalisation spécifique de l'invention, ledit dispositif est destiné à être utilisé dans un démodulateur de signal transmis en évasion de fréquence, chacun des blocs de données sources étant précédé et suivi d'un motif connu du récepteur, et est caractérisé en ce qu'il comporte :

- des moyens de génération d'un signal de bloc indiquant si le bit courant reçu appartient ou non à un bloc de données ;

- des moyens de forçage de la valeur décidée pour le bit courant reçu à une valeur prédéterminée, lorsque ledit signal de bloc indique que le signal courant reçu n'appartient pas à un bloc de données.

15

10

5

20

25

30

D'autres caractéristiques et avantages de l'invention apparaîtront à la lecture suivante de la description d'un mode de réalisation préférentielle de l'invention, donné à titre illustratif et non limitatif, et des dessins annexés dans lesquels :

5

10

15

20

25

30

35

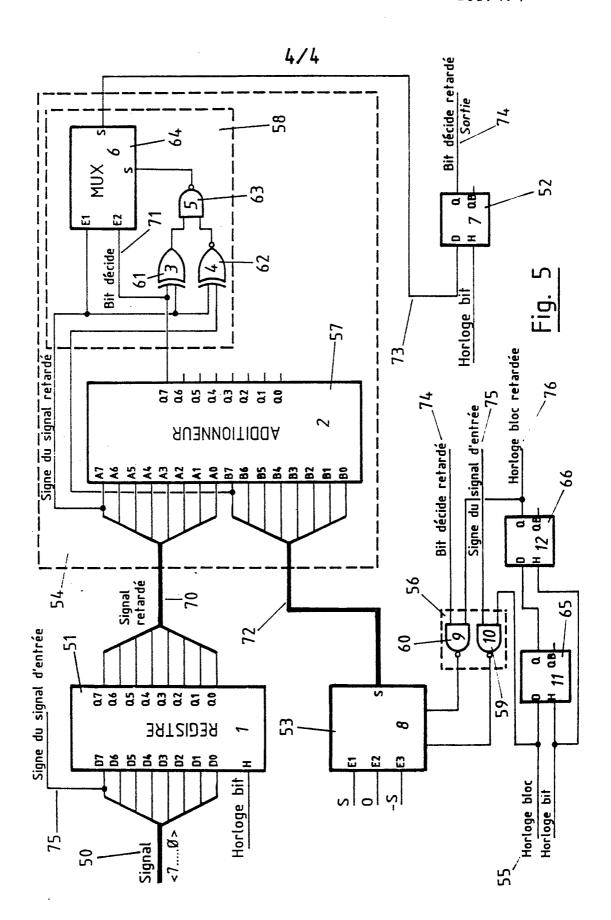

- la figure 1 est un schéma bloc illustrant les fonctions mises en oeuvre dans un mode de réalisation du procédé, selon l'invention, de restitution de la valeur d'origine d'un signal numérique binaire dont chaque bit reçu est affecté d'interférence avec le bit précédent et le bit suivant;

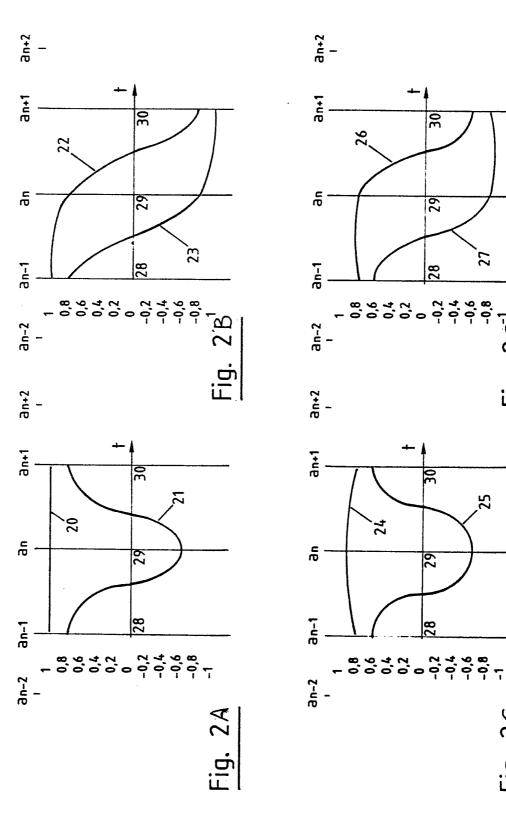

- la figure 2 est constituée par quatre diagrammes 2A, 2B, 2C, 2D illustrant l'intérêt de prendre un seuil de décision variable pour la restitution d'un signal numérique binaire affecté d'interférence intersymbole;

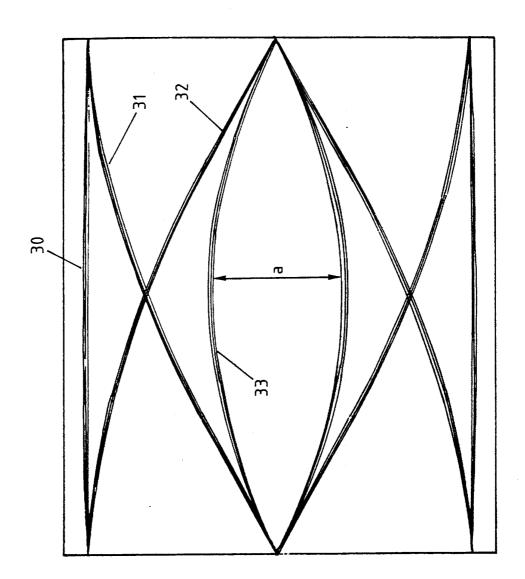

- la figure 3 est un diagramme de l'oeil illustrant un type de signal d'interférence intersymbole compatible avec le procédé de restitution mis en oeuvre par le mode de réalisation préférentielle décrit ;

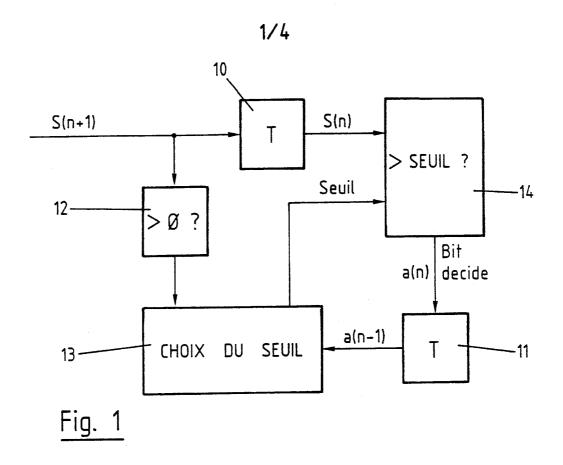

- la figure 4 représente deux diagrammes 4A, 4B, illustrant le principe de faire précéder chaque bloc de données, en cas de transmission en évasion de fréquence, par un motif connu du récepteur, pour fiabiliser le décodage de l'interférence intersymbole à seuil de décision variable, suivant l'invention ;

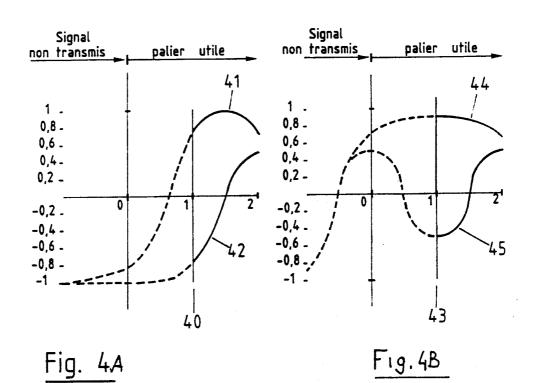

- la figure 5 est un schéma illustrant un mode préférentiel de réalisation matérielle d'un circuit mettant en oeuvre le procédé de l'invention.

Le procédé et le dispositif décrits ci-après s'appliquent à un signal dont la valeur à l'instant de décision dépend de trois symboles consécutifs. Ceci signifie que le symbole courant reçu dépend de la valeur du symbole reçu précédent et du symbole reçu suivant, et que donc l'influence des autres symboles est nulle ou peut-être négligée.

Dans les exemples présentés, l'influence est supposée s'exercer de façon symétrique en ce qui concerne les symboles extrêmes (symbole précédent et symbole suivant). Toutefois, il est parfaitement envisageable de concevoir des situations où la modélisation de l'interférence intersymbole conduit à définir

des coefficients de pondération différents pour le bit précédent et pour le bit suivant.

La mise en équation des hypothèses retenues s'exprime par  $s(n) = A \ a(n-1) + B \ a(n) + A \ a(n+1)$ , dans laquelle :

- s(n) est la valeur du signal reçu;

- a(n) est la valeur du bit source ;

- a(n-1) est la valeur du bit source précédent,

- a(n+1) est la valeur du bit source suivant ;

- A est un coefficient réel positif, commun aux bits sources précédent et suivant ;

- B est le coefficient réel positif appliqué au bit source courant,

avec B > 0.5 et B + 2 A = 1.

5

10

15

20

25

30

35

a(n), a(n-1) et a(n+1) sont les symboles modulants d'origine et prennent les valeurs +1 et -1.

Par hypothèse, et en suivant la modélisation présentée ci-dessus, le signal s(n) reçu prend une valeur comprise entre +1 et -1, qui dépend de façon prépondérante de la valeur d'origine a(n) du symbole, mais également, dans une certaine mesure, de la valeur des symboles modulants adjacents a(n-1) et a(n+1).

L'idée à la base de l'invention est d'effectuer la décision sur la valeur d'origine a(n) (soit +1, soit -1), en comparant le signal reçu s(n) non pas à un seuil nul, mais à un seuil variable en fonction de la valeur des symboles adjacents.

Pour illustrer cette situation, supposons tout d'abord que l'on doive décider de la valeur du symbole a(n) et que l'on connaisse les valeurs des deux symboles adjacents. Plusieurs cas sont possibles :

- dans le cas où a(n-1) et a(+1) sont tous les deux positifs, les valeurs possibles pour s(n) sont :

- 1, si a(n) est lui aussi positif ;

2A-B dans le cas contraire.

On voit donc que le seuil de décision doit se situer à S = (1+2A-B)/2 = 2A, (moyenne des valeurs possibles) de façon à optimiser la décision.

- dans le cas où les symboles extrêmes sont de signes opposés, les valeurs possibles pour s(n) sont B et -B, et donc le seuil de décision reste à zéro.

- dans le troisième cas, c'est-à-dire lorsque a(n-1) et a(n+1) sont tous les deux négatifs on prend évidemment un seuil de décision égal à -2A.

Ces différentes situations sont illustrées dans les quatre diagrammes de la figure 2.

Pour chacun de ces diagrammes, on a placé le seuil de décision S pour la valeur d'origine du signal  $a_n$ , qui est affecté d'interférence intersymbole avec les bits adjacents  $a_{n-1}$  et  $a_{n+1}$ .

Chaque diagramme représente la valeur que prend le signal reçu S(n) lorsque  $a_n$  prend la valeur 1 (courbes 20, 22, 24, 26), et -1 (courbes 21, 23, 25, 27).

On trouvera en table 1 les valeurs retenues pour  $a_{n-2}$  ,  $a_{n-1},\ a_{n-1}\ a_{n-2}$  dans chacun des quatre diagrammes.

15

25

30

35

10

. 5

| m  | 7 | D  | т | _ | 1 |

|----|---|----|---|---|---|

| Τ. | н | .6 | Ŀ | Ŀ |   |

|    |     | ε  | n-2 | $a_{n-1}$ | a <sub>n+1</sub> | a <sub>n+2</sub> | s   |

|----|-----|----|-----|-----------|------------------|------------------|-----|

|    | Fig | 2A | 1   | 1         | 1                | 1                | 0,2 |

| 20 | Fig | 2B | 1   | 1         | -1               | -1               | 0   |

|    | Fig | 2C | -1  | 1         | 1                | -1               | 0,2 |

|    | Fig | 2D | -1  | 1         | -1               | 1                | 0   |

Les instants d'échantillonnage sont, sur chaque diagramme, 28, 29, 30.

A l'instant d'échantillonnage 29, la valeur optimale du seuil S de décision de la valeur d'origine du bit  $\mathbf{a}_n$  se trouve dans la dernière colonne de la table 1.

On constate donc qu'il est intéressant de prévoir un procédé de décodage de signal numérique affecté d'interférence intersymbole, dont le seuil de décision soit variable.

Les configurations dans lesquelles  $a_{n-1}=-1$  sont symétriques des configurations des figures 2A à 2D.

L'ensemble de ces situations peut également être visualisé sur le diagramme de l'oeil de la figure 3.

La portion 30 correspond à la situation où a(n-1) = a(n+1) = 1.

Les portions 37 et 32 correspondent aux cas où les bits a(n-1) et a(n+1) sont de signes contraires.

La portion 33 est relative au cas où a(n-1) = a(n+1) = 0.

Sur le diagramme de l'oeil de la figure 3, l'ouverture a de l'oeil est la traduction du fait que la valeur d'origine du bit  $a_n$  est prépondérante dans l'équation de modélisation (c'est-à-dire le coefficient B > 0,5).

Le problème posé par la mise en oeuvre du procédé tel qu'il a été exposé jusqu'à présent est bien évidemment qu'on ne connaît jamais la valeur d'origine du bit a(n+1) lorsque l'on doit décider de la valeur de a(n).

Selon l'invention, on surmonte la difficulté en effectuant une prédécision sur la valeur de a(n+1) avec un seuil de décision nul. La valeur définitive de a(n+1) sera ensuite déterminée à l'itération suivante :

La condition B supérieure stricte à 0,5 intervient à nouveau ici pour permettre de prendre cette prédécision, qui est d'autant meilleure que B est grand.

Le synoptique du dispositif de l'invention est représenté en figure 1.

On dispose d'un registre 10 permettant de retarder le signal reçu S(n) de la valeur d'une période bit ; d'une case mémoire 11 permettant de mémoriser le bit a(n-1) décidé à la période précédente ; d'un multiplexeur 13 permettant de choisir entre les seuils + S, - S et 0 ; d'un premier comparateur 12 réalisant la prédécision sur la valeur du bit suivant reçu S(n+1), et d'un second comparateur 14 pour prendre la décision sur le bit reçu courant S(n).

L'invention se propose également de fournir une solution dans le cas où la transmission des données est effectuée par blocs (transmission en évasion de fréquence).

Un problème se pose dans ce cas pour décider la valeur du premier et du dernier bit de chaque bloc de données, du fait que ces deux bits n'ont qu'un seul bit adjacent.

Selon l'invention, on résoud le problème en faisant précéder et suivre le bloc de données, à la modulation, d'un motif connu du récepteur. Les symboles composant ce motif ne font pas partie du bloc de données et ne sont donc pas transmis, mais ils interviennent dans la forme d'onde reçue.

Deux exemples sont fournis en figures 4A, 4B.

15

10

5

20

25

30

En figure 4A, la valeur a(0) = -1 et la valeur a(2) = 1. On effectue à l'instant d'échantillonnage 40 la décision sur la valeur de a(1). Les courbes 41 et 42 correspondent respectivement à S(n) lorsque a(1) = 1, et a(1) = -1. Le seuil de décision est ici égal à 0.

En revanche, dans le cas de la figure 4B où la valeur a(0) est 1, le seuil de décision sur la valeur de a(1) à l'instant d'échantillonnage 43 est 0,2, c'est-à-dire la moyenne entre les valeurs prises par les deux courbes S(n) 44, 45.

On constate donc l'importance d'insérer, à la modulation, un motif a(0) connu du récepteur, de façon à optimiser la valeur du seuil de décision dans le récepteur.

La figure 5 présente un exemple de circuit pour un mode de réalisation préférentiel de l'invention mettant en oeuvre le procédé.

Le signal 50 d'entrée est supposé représenté sur 8 bits en complément à 2.

Un premier registre 51 constitue une bascule de retard, et alimente un circuit additionneur 57 qui reçoit également en entrée la valeur S du seuil courant de décision fourni par le multiplexeur 53. Le circuit additionneur 57 fait partie d'un module 54 de décision de la valeur du bit courant, qui contient également un sous-module 58 de contrôle des dépassements de l'additionneur.

Ce module comprend deux circuits NOR exclusif 61 et 62, un circuit NAND 63 et un multiplexeur 64.

Une bascule D 52 conserve la valeur du bit décidé à la période du bit précédente.

La gestion des bits d'extrémité, dans des blocs de données transmis en évasion de fréquence, est réalisée au moyen des deux portes NAND du module 56, contrôlée notamment par les deux bascules 65, 66, mémorisant respectivement le bit HORLOGE BLOC aux instants n et n-1, représentatif du fait que le signal courant reçu est ou n'est pas significatif.

Le fonctionnement du circuit est le suivant :

On compare à chaque période bit fournie par HORLOGE BIT le signal retardé 70 à un seuil qui peut prendre 3 valeurs : +S, 0, -S. La valeur de S est choisie à l'initialisation. La comparaison s'effectue au moyen de l'additionneur 57 et le

10

5

15

20

25

35

choix entre les 3 valeurs ci-dessus au moyen du multiplexeur 53.

Le résultat de la comparaison est donné par le bit 71 de poids fort de la sortie de l'additionneur 57 appelé "BIT DECIDE".

5

10

15

20

25

30

Les portes 61, 62, 63 et le multiplexeur 64 servent à contrôler les dépassements dans la comparaison. On vérifie facilement que la commande de sélection du multiplexeur 64 est à 0 lorsqu'il y a dépassement, c'est-à-dire lorsque les deux entrées 70, 71 de l'additionneur 57 ont le même signe et la sortie un signe contraire. Dans ce cas on garde le signe de l'une des deux entrées.

On retarde ensuite la sortie 73 du multiplexeur 64 d'une période bit (au moyen de la bascule D52) ce qui donne le signal "BIT DECIDE RETARDE" 74.

Le signal "BIT DECIDE RETARDE" 74 et le bit 75 de signe du signal d'entrée 50 donnent les valeurs des deux bits adjacents nécessaires pour choisir entre les 3 valeurs possibles du seuil de décision. Il reste seulement à tenir compte de la valeur du signal "HORLOGE BLOC" 55 qui indique si le signal courant appartient à un bloc de données.

Si HORLOGE BLOC est à 0, le signal d'entrée 50 n'a pas de signification (il n'appartient pas au bloc), et donc on doit considérer que son signe est négatif (le modulateur ayant inséré des 0 entre les blocs). C'est donc le rôle de la porte 58 de forcer l'une des entrées de sélection du multiplexeur 53 à 1(valeur du bit de signe d'un signal négatif).

On fait le même raisonnement avec la porte 60 pour le signal "BIT DECIDE RETARDE" 74 qui doit être considéré comme étant égal à 1 lorsque HORLOGE BLOC RETARDEE 76 est nulle.

Ce mode de réalisation trouve une application avantageuse dans le cas d'une modulation de fréquence à phase continue, démodulée par phase différentielle (par exemple une modulation de type M S K).

5

## REVENDICATIONS

1) Procédé de restitution de la valeur d'origine de signaux numériques affectés d'interférence intersymbole, et dont le signal reçu peut être modélisé, à chaque période bit, comme étant une combinaison linéaire du symbole source correspondant et des symboles sources adjacents,

procédé caractérisé en ce qu'il consiste à effectuer la décision de la valeur du symbole reçu à l'aide d'un seuil de décision variable, en fonction de la valeur desdits symboles adjacents.

15

20

10

2) Procédé de restitution de la valeur d'origine de signaux numériques binaires affectés d'interférence intersymbole, et dont le signal reçu peut être modélisé, à chaque période bit, essentiellement comme une combinaison linéaire du bit source correspondant avec les bits sources précédent et suivant dans la séquence numérique source,

procédé caractérisé en ce qu'il consiste à effectuer la décision de la valeur du bit reçu à l'aide d'un seuil de décision, variable en fonction de la valeur desdits bits précédent et suivant.

25

3) Procédé suivant l'une quelconque des revendications 1 et 2 caractérisé en ce que ledit seuil est défini comme étant la moyenne des valeurs des symboles adjacents, bits adjacents respectivement, pondérées par des coefficients représentatifs de la combinaison linéaire de modélisation.

30

4) Procédé selon l'une quelconque des revendications 1 et 2 caractérisé en ce que ladite valeur des symboles adjacents précédents, bit précédent respectivement, est la valeur décidée pour le signal reçu à la période bit précédente.

35

5) Procédé selon l'une quelconque des revendications 1 et 2 caractérisé en ce que ladite valeur des symboles adjacents suivants, bit suivant respectivement, est temporairement prédécidée, à partir du signal reçu à la période bit suivante, avec un seuil de décision nul.

6) Procédé selon la revendication 2, caractérisé en ce que ledit modèle de combinaison linéaire est de la forme :

s(n) = A a(n-1) + B a(n) + 1 a(n+1), dans laquelle:

- s(n) est la valeur du signal reçu ;

- a(n) est la valeur du bit source ;

- a(n-1) est la valeur du bit source précédent,

- a(n+1) est la valeur du bit source suivant ;

- A est un coefficient réel positif, commun aux bits sources précédent et suivant ;

- B est le coefficient réel positif appliqué au bit source courant,

avec B > 0,5 et B + 2 A = 1,

lesdites valeurs du seuil variable de décision étant alors respectivement :

2A, si a(n+1) = a(n-1) = 1,

5

15

20

25

30

35

(-2A), si A(n+1) = a(n-1) = -1,

0 si a(n+1) différent de a(n-1).

7) Dispositif de restitution de signaux numériques binaires affectés d'interférence intersymbole, et dont le signal reçu peut être modélisé, à chaque période bit, essentiellement comme une combinaison linéaire du bit source correspondant avec le bit source précédent et le bit source suivant dans la séquence numérique source,

dispositif caractérisé en ce qu'il comprend :

- des moyens (51) de retardement du bit courant reçu, pendant la durée d'une période bit;

- des moyens (52) de mémorisation de la valeur décidée pour le bit reçu précédent ;

- des moyens (13, 53) de choix du seuil de décision de la valeur du bit courant retardé, en fonction de la valeur reçue du bit suivant et de la valeur mémorisée du bit reçu précédent;

- des moyens (14, 54) de comparaison dudit bit courant reçu retardé avec ledit seuil choisi, lesdits moyens de comparaison (14, 54) fournissant en sortie la valeur décidée pour ledit bit courant reçu.

- 8) Dispositif selon la revendication 7 caractérisé en ce que lesdits moyens (13, 53) de choix du seuil de décision, reçoivent en entrée d'une part la valeur décidée et mémorisée

du bit reçu précédent, et d'autre part, le signe du bit reçu suivant.

9) Dispositif selon la revendication 7, destiné à être utilisé dans un démodulateur de signal transmis en évasion de fréquence, chacun des blocs de données sources étant précédé et suivi d'un motif connu du récepteur,

dispositif caractérisé en ce qu'il comporte :

5

- des moyens (55) de génération d'un signal de bloc indiquant si le bit courant reçu appartient ou non à un bloc de données ;

- des moyens (56) de forçage de la valeur décidée pour le bit courant reçu à une valeur prédéterminée, lorsque ledit signal de bloc indique que le signal courant reçu n'appartient pas à un bloc de données.

ig. 3