### (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2008-33995 (P2008-33995A)

(43) 公開日 平成20年2月14日(2008.2.14)

(51) Int.Cl.

FL

テーマコード (参考)

G11C 29/04

(2006.01)

G 1 1 C 29/00 603B 5L106

#### 審査請求 未請求 請求項の数 12 OL (全 12 頁)

| (21) 出願番号 | 特願2006-203856 (P2006-203856) | (71) 出願人 | 000005821        |

|-----------|------------------------------|----------|------------------|

| (22) 出願日  | 平成18年7月26日 (2006.7.26)       |          | 松下電器産業株式会社       |

|           |                              |          | 大阪府門真市大字門真1006番地 |

|           |                              | (74) 代理人 | 100077931        |

|           |                              |          | 弁理士 前田 弘         |

|           |                              | (74) 代理人 | 100110939        |

|           |                              |          | 弁理士 竹内 宏         |

|           |                              | (74)代理人  |                  |

|           |                              |          | 弁理士 嶋田 高久        |

|           |                              | (74) 代理人 |                  |

|           |                              |          | 弁理士 竹内 祐二        |

|           |                              | (74) 代理人 | ····             |

|           |                              |          | 弁理士 今江 克実        |

|           |                              | (74)代理人  |                  |

|           |                              |          |                  |

|           |                              |          | 弁理士 藤田 篤史<br>    |

|           |                              |          | 最終頁に続く           |

(54) 【発明の名称】 メモリシステム

### (57)【要約】

【課題】アクセス速度の低下をできるだけ抑えながら、 メモリの故障を確実に救済する。

【解決手段】メモリシステムであって、故障を救済する ための冗長領域をそれぞれ有する複数のメモリバンクを 有するメモリを備え、同一のメモリバンクで複数の故障 が発生した場合には、少なくとも1つの故障を、そのメ モリバンクが有する冗長領域を用いて救済し、その他の 少なくとも1つの故障を、他のメモリバンクが有する冗 長領域を用いて救済する。

### 【選択図】図1

#### 【特許請求の範囲】

### 【請求項1】

故障を救済するための冗長領域をそれぞれ有する複数のメモリバンクを有するメモリを 備え、

同一のメモリバンクで複数の故障が発生した場合には、少なくとも 1 つの故障を、そのメモリバンクが有する冗長領域を用いて救済し、その他の少なくとも 1 つの故障を、他のメモリバンクが有する冗長領域を用いて救済する

ことを特徴とするメモリシステム。

ことを特徴とするメモリシステム。

### 【請求項2】

請求項1記載のメモリシステムにおいて、

前記少なくとも 1 つの故障は、前記故障が発生したメモリバンクが有する冗長領域を用いて、ヒューズ方式により救済されるものである

## 【請求項3】

請求項1記載のメモリシステムにおいて、

前記その他の少なくとも1つの故障は、アクセス先のアドレスを前記他のメモリバンクが有する冗長領域のアドレスに変換することにより、救済されるものであることを特徴とするメモリシステム。

#### 【 請 求 項 4 】

請求項3記載のメモリシステムにおいて、

前記複数のメモリバンクのそれぞれと、そのメモリバンクで発生した故障を救済するそのメモリバンク以外のメモリバンクとは、あらかじめ対応付けられており、前記アクセス先のアドレスの変換の際には、そのアドレスのうち、前記複数の故障が発生したメモリバンクに対応するメモリバンクを特定するために必要なビットだけを変換することを特徴とするメモリシステム。

### 【請求項5】

請求項1記載のメモリシステムにおいて、

前記複数のメモリバンクのそれぞれと、そのメモリバンクで発生した故障を救済することが可能であるそのメモリバンク以外のメモリバンクとは、あらかじめ対応付けられており、前記複数の故障が発生したメモリバンクに対応するメモリバンクを活性化させることを特徴とするメモリシステム。

### 【請求項6】

請求項1記載のメモリシステムにおいて、

当該メモリシステムへのアクセスが示す第1のアドレスを、前記アクセスが読み出そうとする領域に故障があった場合にそれを救済する、前記他のメモリバンクが有する冗長領域を示す第2のアドレスに変換するアドレス変換回路と、

前記他のメモリバンクが有する冗長領域によって救済されている領域を示すアドレスを保持し、入力されたバンク選択アドレスが示すメモリバンクに対応するアドレスを出力する故障アドレスレジスタと、

前記故障アドレスレジスタから出力されたアドレスと前記第1のアドレスの所定の部分とが一致した場合に、ヒット信号を有効にして出力するヒット信号生成回路と、

前記ヒット信号が有効である場合には、前記第2のアドレスによって前記メモリから読み出されるデータを選択して出力し、前記ヒット信号が無効である場合には、前記第1のアドレスによって前記メモリから読み出されるデータを選択して出力するセレクタとを更に備える

ことを特徴とするメモリシステム。

### 【請求項7】

請求項6記載のメモリシステムにおいて、

前記アクセスが読み出そうとする領域を有するメモリバンクと、その領域に故障があった場合にそれを救済する前記他のメモリバンクとは、あらかじめ対応付けられているもの

10

20

30

30

40

であり、

前記第1のアドレスを、あらかじめ対応付けられた前記他のメモリバンクを示すように 、 前 記 バン ク 選 択 ア ド レ ス に 変 換 し て 、 前 記 故 障 ア ド レ ス レ ジ ス タ に 出 力 す る バ ン ク 変 換 回路を更に備える

ことを特徴とするメモリシステム。

### 【請求項8】

請求項6記載のメモリシステムにおいて、

故障を救済する単位によって、前記故障アドレスレジスタのエントリ数が決定される ことを特徴とするメモリシステム。

### 【請求項9】

請求項6記載のメモリシステムにおいて、

前記メモリは、

a個(aは自然数)のメモリバンクを備えるものであり、

前記a個のメモリバンクは、

エントリ数がb(bは自然数)である冗長領域をそれぞれ有するものであり、

前記故障アドレスレジスタは、

前記メモリの c 個( c は自然数)のエントリを単位として故障を救済する場合には、 a x b / c 個のエントリを有するものである

ことを特徴とするメモリシステム。

### 【請求項10】

請求項6記載のメモリシステムにおいて、

前記故障アドレスレジスタ及び前記ヒット信号生成回路は、

前記メモリからデータを読み出す処理とは、独立して処理を行うものである

ことを特徴とするメモリシステム。

#### 【請求項11】

請求項6記載のメモリシステムにおいて、

前記メモリは、

前記第1のアドレスに基づいてデータを読み出す処理と、前記第2のアドレスに基づい てデータを読み出す処理とを、それぞれ独立して行うものである

ことを特徴とするメモリシステム。

#### 【請求項12】

請求項6記載のメモリシステムにおいて、

前記アドレス変換回路は、

前記第1のアドレスを変換して、前記第2のアドレスを複数生成するものであり、

前記メモリは、

前記第1のアドレスに基づいてデータを読み出す処理と、前記複数の第2のアドレスに 基づいてそれぞれデータを読み出す処理とを、それぞれ独立して行うものである ことを特徴とするメモリシステム。

【発明の詳細な説明】

### 【技術分野】

[00001]

本発明は、メモリの故障を救済するメモリシステムに関する。

#### 【背景技術】

### [00002]

製 造 さ れ た 半 導 体 メ モ リ を 選 別 す る 検 査 に よ っ て 故 障 と 判 定 さ れ た 領 域 を 救 済 す る 方 法 としては、メモリへのアクセスにおいて、入力されたアドレスがメモリの故障領域を示す か否かを判定し、故障領域を示す場合は、入力されたアドレスをメモリの冗長的な領域を 指し示すように変換するものがある。メモリの冗長救済を効率よく行うために、カラムや ロ ウ 単 位 で は な く ア ド レ ス 単 位 で 救 済 を 行 う メ モ リ の 冗 長 救 済 装 置 が 、 例 え ば 、 下 記 特 許 文献1に開示されている。

10

20

30

50

#### [00003]

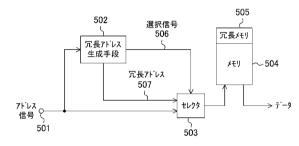

図5は、従来のメモリの冗長救済装置の構成を示すブロック図である。図5のメモリの冗長救済装置は、冗長アドレス生成手段502と、セレクタ503と、メモリ504と、冗長メモリ505とを備える。

### [0004]

冗長アドレス生成手段502は、メモリの故障箇所を示す故障アドレスと、それに対応した冗長メモリの冗長アドレスとを保持する。冗長アドレス生成手段502は、受け取った入力アドレス501が、保持するどの故障アドレスとも一致しない場合は、入力アドレス501を選択してメモリ504に供給するように指示する制御信号506を、セレクタ503に出力する。また、冗長アドレス生成手段502は、受け取った入力アドレス501が、保持する故障アドレスと一致する場合は、故障アドレスに対応する冗長アドレス507と、冗長アドレス507を選択して冗長メモリ505に供給するように指示する制御信号506とを、セレクタ503に出力する。

### [0005]

このような構成を取ることで、メモリの故障をアドレス単位で救済し、冗長メモリの容量を削減して、効率の良い冗長救済を行うことができる。

【特許文献 1 】特開 2 0 0 5 - 1 9 6 8 4 3 号公報

#### 【発明の開示】

【発明が解決しようとする課題】

### [0006]

しかしながら、図5の冗長救済装置においては、例えば、ヒューズ方式を用いてメモリアクセスの速度を低下させずに救済することができる故障についても、全てアドレス変換によって救済することにより、メモリのアクセス速度が低下するという問題があった。

#### [0007]

また、全てのアクセスについて、それぞれのアクセスが示すアドレスがアドレス生成手段が保持する故障箇所のアドレスと一致するか否かの判定を行ってから、メモリアクセスを行うことによっても、メモリのアクセス速度が低下するという問題があった。

#### [00008]

さらに、故障した箇所の数だけ故障アドレスと冗長アドレスとを保持する必要があり、 故障アドレスの数が増えるほど、それを保持する冗長アドレス生成手段の回路の面積が増 大するという問題があった。

### [0009]

本発明は、冗長領域によって故障を救済するメモリシステムにおいて、アクセス速度の低下をできるだけ抑えながら、メモリの故障を確実に救済することを目的とする。 さらに、故障箇所を記憶するレジスタの数を削減することを目的とする。

【課題を解決するための手段】

#### [0010]

前記課題を解決するため、請求項1の発明が講じた手段は、メモリシステムであって、故障を救済するための冗長領域をそれぞれ有する複数のメモリバンクを有するメモリを備え、同一のメモリバンクで複数の故障が発生した場合には、少なくとも1つの故障を、そのメモリバンクが有する冗長領域を用いて救済し、その他の少なくとも1つの故障を、他のメモリバンクが有する冗長領域を用いて救済するものである。

### [0011]

請求項1の発明によると、同一のメモリバンクで発生した複数の故障を、メモリのアクセス速度をできるだけ低下させずに救済することができる。

### [0012]

請求項2の発明は、請求項1記載のメモリシステムにおいて、前記少なくとも1つの故障は、前記故障が発生したメモリバンクが有する冗長領域を用いて、ヒューズ方式により救済されるものである。

### [0013]

10

20

30

請求項3の発明は、請求項1記載のメモリシステムにおいて、前記その他の少なくとも 1つの故障は、アクセス先のアドレスを前記他のメモリバンクが有する冗長領域のアドレスに変換することにより、救済されるものである。

#### [ 0 0 1 4 ]

請求項4の発明は、請求項3記載のメモリシステムにおいて、前記複数のメモリバンクのそれぞれと、そのメモリバンクで発生した故障を救済するそのメモリバンク以外のメモリバンクとは、あらかじめ対応付けられており、前記アクセス先のアドレスの変換の際には、そのアドレスのうち、前記複数の故障が発生したメモリバンクに対応するメモリバンクを特定するために必要なビットだけを変換するものである。

### [0015]

請求項4の発明によると、複数の故障が発生した場合に、少なくともその1つを救済する他のメモリバンクをあらかじめ決定しておくことにより、アドレス変換において変換するビットの数を削減することができる。

### [0016]

請求項5の発明は、請求項1記載のメモリシステムにおいて、前記複数のメモリバンクのそれぞれと、そのメモリバンクで発生した故障を救済することが可能であるそのメモリバンク以外のメモリバンクとは、あらかじめ対応付けられており、前記複数の故障が発生したメモリバンクに対応するメモリバンクを活性化させるものである。

### [ 0 0 1 7 ]

請求項5の発明によると、複数の故障が発生した場合に、少なくともその1つを救済することが可能である他のメモリバンクをあらかじめ決定しておくことにより、活性化するバンクの数を削減することができる。

#### [0018]

請求項6の発明は、請求項1記載のメモリシステムにおいて、当該メモリシステムへのアクセスが示す第1のアドレスを、前記アクセスが読み出そうとする領域に故障があった場合にそれを救済する、前記他のメモリバンクが有する冗長領域を示す第2のアドレスに変換するアドレス変換回路と、前記他のメモリバンクが有する冗長領域によって救済されている領域を示すアドレスを保持し、入力されたバンク選択アドレスが示すメモリバンクに対応するアドレスを出力する故障アドレスレジスタと、前記故障アドレスレジスタと、前記故障アドレスから出力されたアドレスと前記第1のアドレスの所定の部分とが一致した場合に、ヒット信号を有効にして出力するヒット信号生成回路と、前記ヒット信号が有効である場合には、前記第2のアドレスによって前記メモリから読み出されるデータを選択して出力するセレクタとを更に備えるものである。

### [0019]

請求項7の発明は、請求項6記載のメモリシステムにおいて、前記アクセスが読み出そうとする領域を有するメモリバンクと、その領域に故障があった場合にそれを救済する前記他のメモリバンクとは、あらかじめ対応付けられているものであり、前記第1のアドレスを、あらかじめ対応付けられた前記他のメモリバンクを示すように、前記バンク選択アドレスに変換して、前記故障アドレスレジスタに出力するバンク変換回路を更に備えるものである。

#### [0020]

請求項8の発明は、請求項6記載のメモリシステムにおいて、故障を救済する単位によって、前記故障アドレスレジスタのエントリ数が決定されるものである。

#### [0021]

請求項8の発明によると、故障を救済する単位を決定することにより、故障アドレスレジスタのエントリ数を決定することができる。このため、故障アドレスレジスタの回路規模を調整することができる。

#### [0022]

請求項9の発明は、請求項6記載のメモリシステムにおいて、前記メモリは、a個(a

10

20

30

40

は自然数)のメモリバンクを備えるものであり、前記 a 個のメモリバンクは、エントリ数が b ( b は自然数 ) である冗長領域をそれぞれ有するものであり、前記故障アドレスレジスタは、前記メモリの c 個 ( c は自然数 ) のエントリを単位として故障を救済する場合には、 a × b / c 個のエントリを有するものである。

### [0023]

請求項10の発明は、請求項6記載のメモリシステムにおいて、前記故障アドレスレジスタ及び前記ヒット信号生成回路は、前記メモリからデータを読み出す処理とは、独立して処理を行うものである。

# [ 0 0 2 4 ]

請求項10の発明によると、メモリシステムへのアクセスが示すアドレスが故障領域に該当するか否かの判定と、メモリバンクからデータを読み出す処理とをそれぞれ独立して行うことができる。このため、メモリのアクセス速度を向上させることができる。

#### [0025]

請求項11の発明は、請求項6記載のメモリシステムにおいて、前記メモリは、前記第 1のアドレスに基づいてデータを読み出す処理と、前記第2のアドレスに基づいてデータ を読み出す処理とを、それぞれ独立して行うものである。

### [0026]

請求項12の発明は、請求項6記載のメモリシステムにおいて、前記アドレス変換回路は、前記第1のアドレスを変換して、前記第2のアドレスを複数生成するものであり、前記メモリは、前記第1のアドレスに基づいてデータを読み出す処理と、前記複数の第2のアドレスに基づいてそれぞれデータを読み出す処理とを、それぞれ独立して行うものである。

### 【発明の効果】

#### [0027]

本発明によれば、同一メモリバンク内に複数の故障が発生した場合であっても、故障を 救済することができ、メモリのアクセス速度の低下を抑えることができる。また、故障を 救済するための回路の規模を抑えることができる。

【発明を実施するための最良の形態】

### [0028]

以下、本発明の実施の形態について、図面を参照しながら説明する。

#### [0029]

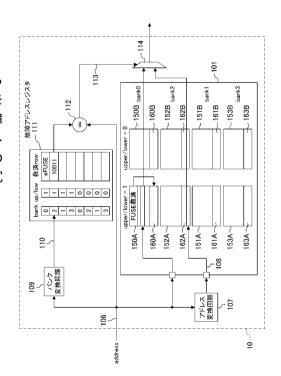

図1は、本発明の実施形態に係るメモリシステム10の構成を示すブロック図である。図1のメモリシステム10は、メモリ101と、アドレス変換回路107と、バンク変換回路109と、故障アドレスレジスタ111と、ヒット信号生成回路112と、セレクタ114とを備えている。メモリシステム10へのアクセスが示す入力アドレス106を受け取り、メモリ101からデータを読み出して出力する。

### [0030]

メモリ101は、メモリバンク150A,150B,151A,151B,152A, 152B,153A,153Bを備える。縦方向にはバンク番号bank0,bank1 ,bank2,bank3、横方向にはupper/lowerを指定することによって 、メモリバンクが選択される。

### [0031]

メモリバンク 1 5 0 A , 1 5 0 B , 1 5 1 A , 1 5 1 B , 1 5 2 A , 1 5 2 B , 1 5 3 A , 1 5 3 B は、冗長領域 1 6 0 A , 1 6 0 B , 1 6 1 A , 1 6 1 B , 1 6 2 A , 1 6 2 B , 1 6 3 A , 1 6 3 B をそれぞれ備える。

### [0032]

アドレス変換回路107は、受け取った入力アドレス106を変換して、冗長領域16 0A~163Bのいずれかを指定する冗長アドレス108を生成して出力する。メモリ1 01は、入力アドレス106と冗長アドレス108とによってアクセスされ、それぞれア クセスされたデータを、互いに独立に読み出すことができる。 10

20

30

40

10

20

30

40

50

[ 0 0 3 3 ]

バンク変換回路109は、入力アドレス106を変換し、故障アドレスレジスタ111にアクセスするバンク選択アドレス110を、生成して出力する。故障アドレスレジスタ1110は、冗長領域160A~163Bがそれぞれ救済する故障箇所を示す故障アドレスを、保持する。ヒット信号生成回路112は、故障アドレスレジスタ111から読み出された故障アドレスと、入力アドレス106が示す内容を比較して一致する場合は、有効を示すヒット信号113を出力する。

[0034]

バンク選択アドレス110の生成から、故障アドレスレジスタ111から故障アドレスが読み出され、ヒット信号113が出力されるまでの処理は、メモリ101からデータが読み出される処理とは、独立して行われる。

[0035]

セレクタ114は、入力アドレス106及び冗長アドレス108により読み出されたデータをそれぞれ受け取り、ヒット信号113が有効であれば冗長アドレス108により読み出されたメモリ101のデータを、ヒット信号113が無効であれば入力アドレス106により読み出されたメモリ101のデータを、それぞれ選択して出力する。

[0036]

メモリシステム10は、メモリ101において故障が発生した場合は、可能な限りヒューズ(FUSE)方式で救済する。ヒューズ方式は、ヒューズ回路内部の信号線を物理的に切断し、アドレス信号の接続を故障の発生している領域から冗長領域に変更するので、メモリへのアクセス速度を低下させない。

[ 0 0 3 7 ]

メモリシステム 1 0 は、故障が発生したメモリバンクが備える冗長領域が、既に他の故障領域をヒューズ方式で救済したことによって使用されている場合には、そのメモリバンクとあらかじめ対応付けられた他のメモリバンクの冗長領域が、さらに他の故障をヒューズ方式で救済したことによって、使用されていないことを前提とする。

[0038]

以上のことを踏まえ、以下で各処理の詳細を説明する。

[ 0 0 3 9 ]

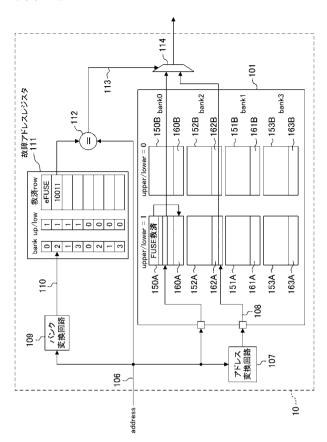

図 2 は、図 1 の入力アドレス 1 0 6 の構成を示す説明図である。入力アドレス 1 0 6 は、フラグビット 2 0 1 と、エントリ選択ビット 2 0 2 と、バンク選択ビット 2 0 3 と、upper / lower選択ビット 2 0 4 とを備える。

[0040]

フラグビット201は、冗長領域160A~163Bのいずれかにアクセスするか否かを示す。フラグビット201に1が設定されている場合は、冗長領域をアクセスすることを示す。フラグビット201は、プログラムなどのソフトウェアで1に設定することはできないものとする。エントリ選択ビット202は、メモリバンクでのエントリを示す。バンク選択ビット203は、データが格納されているメモリバンクのバンクを示す。upper/1ower選択ビット204は、データが格納されているメモリバンクのupper/1owerを示す。

[0041]

メモリ101の、各メモリバンクのエントリ数は128、各冗長領域のエントリ数は4とする。また、本実施形態での救済単位は4エントリ毎とする。また、入力アドレス106は、図2の「0\_1001100\_00\_1」として与えられ、このアドレスでアクセスされる領域は、故障しているものとする。

[0042]

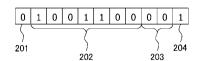

図 3 は、入力アドレス 1 0 6 が図 2 の値を示す場合の、冗長アドレス 1 0 8 の値を示す 説明図である。冗長アドレス 1 0 8 は、フラグビット 3 0 1 と、エントリ選択ビット 3 0 2 と、バンク選択ビット 3 0 3 と、 u p p e r / l o w e r 選択ビット 3 0 4 とを備える [0043]

アドレス変換回路 1 0 7 は、受け取った入力アドレス 1 0 6 のフラグビット 2 0 1 を 1 としてフラグビット 3 0 1 に設定する。アドレス変換回路 1 0 7 は、入力アドレス 1 0 6 が示すメモリバンクの冗長領域が既に使用されている場合に、新たな故障を救済するようにあらかじめ対応付けられている他のメモリバンクを指定するように、バンク選択ビット 2 0 3 及び u p p e r / 1 o w e r 選択ビット 3 0 4 にそれぞれ設定する。アドレス変換回路 1 0 7 は、入力アドレス 1 0 6 を以上のように変換して、冗長アドレス 1 0 8 を生成する

[0044]

本実施形態では、メモリ101でのuppoer/lowerが同じで、隣り合うバンクの冗長領域を使用して故障を救済するものとする。よって、メモリバンク150Aの冗長領域160Aが既に他の故障領域をヒューズ方式で救済したことによって使用されている場合は、メモリバンク152Aの冗長領域162Aを使用して、故障を救済する。これに従って、アドレス変換回路107は、入力アドレス106が図2で示されるように「0\_1001100\_1」で与えられた場合は、冗長アドレス108を、図3のように「1\_1001100\_10\_1」とする。

[0045]

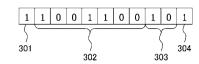

図 4 は、入力アドレス 1 0 6 が図 2 の値を示す場合の、バンク選択アドレス 1 1 0 の値を示す説明図である。バンク選択アドレス 1 1 0 は、バンク選択ビット 4 0 1 と、 u p p e r / 1 o w e r 選択ビット 4 0 2 とを備える。

[0046]

バンク変換回路109は、受け取った入力アドレス106のバンク選択ビット203及びupper/10wer選択ビット204を変換して、アドレス変換回路107と同様に、入力アドレス106が示すメモリバンクの冗長領域が既に使用されている場合に、新たな故障を救済するようにあらかじめ対応付けられている他のメモリバンクを指定するように、バンク選択ビット401及びupper/1ower選択ビット402をそれぞれ設定する。入力アドレス106が図2で示されるように「0\_1001100\_00\_1」で与えられた場合は、バンク変換回路109は、バンク選択アドレス1106を以上のように変換して、バンク選択アドレス110を生成する。

[0047]

本実施形態では、各冗長領域のエントリ数は 4 であり、救済単位は 4 エントリ毎であるので、故障アドレスレジスタ 1 1 1 は、故障が発生したメモリバンクの冗長領域が既に使用されていて、各冗長領域がそれぞれ救済している故障箇所を示す故障アドレスを、バンク及び u p p e r / l o w e r で示された各メモリバンク毎に 1 つずつ保持する。

[0048]

例えば、図1によると、故障アドレスレジスタ111が保持するデータは、bank0の、upper/lowerが1であるメモリバンク150Aで故障が発生し、この故障をヒューズ方式で救済したことによって、冗長領域160Aが使用されていることが示されている。さらに、アドレス「10011」で示されるメモリバンク150Aの領域で新たな故障が発生し、冗長領域160Aは既に使用されているため、メモリバンク150Aとあらかじめ対応付けられたbank2の、upper/lowerが1であるメモリバンク152Aが備える、冗長領域162Aで新たな故障を救済していることが示されている。

[0049]

バンク選択アドレス110が図4で示されるように「10<u></u>1」である場合は、bank2の、upper/lowerが1であるメモリバンクを示し、図1の通り、「100 11」が故障アドレスレジスタ111から読み出される。 10

20

30

40

10

20

30

40

50

#### [0050]

故障アドレスレジスタ111から読み出された故障アドレスが「10011」である場合は、各メモリバンクのエントリ数は128であるので、「10011\_00」~「10011\_11」のエントリで示される領域が救済されている。よって、図1及び図2の通り、入力アドレス106のエントリ選択ビット202が「10011\_00」であり、故障アドレスレジスタ111から読み出された故障アドレスが「10011」である場合は、ヒット信号生成回路112は、有効を示すヒット信号113を出力する。

### [0051]

メモリ101からは、入力アドレス106「0\_1001100\_00\_1」で示されたメモリバンク150A、及び、冗長アドレス108「1\_1001100\_10\_1」で示された冗長領域162Aから、それぞれデータが読み出される。ヒット信号113が有効であるので、入力アドレス106が示す領域は、故障が発生して救済されている領域であり、セレクタ114は、冗長アドレス108により読み出されたデータを選択して出力する。

#### [0052]

上記のように、アドレス変換回路107において、変換するビットをあらかじめ決めておくことにより、変換するビット数を低く抑えることができるので、メモリへのアクセス速度の低下を最小限にし、回路規模を削減することが可能である。

### [0053]

また、特定のメモリバンクで故障が発生した場合に、その故障を救済することが可能である冗長領域を持つメモリバンクを決めておき、活性化させるようにする。これにより、同時に活性化するメモリバンクの数を制御することが可能であり、消費電力を削減することができる。

#### [0054]

本実施形態の場合は、メモリ101は8つのメモリバンクを備え、各冗長領域のエントリ数は4であり、救済単位は4エントリ毎であるため、故障アドレスレジスタ111のエントリ数は8となる。よって、メモリバンクをa個、各冗長領域のエントリ数をbとして、メモリのc個のエントリを単位として故障を救済する場合には、故障アドレスレジスタ107は、a\*b/c個のエントリを有する。

### [0055]

このように救済単位や、故障が発生した領域を救済する冗長領域を備えるメモリバンクをあらかじめ決めておくことによって、故障アドレスレジスタ111のエントリ数が決定される。従って、故障アドレスレジスタ111の回路の面積を削減したり、アドレス変換に要する時間を短縮したりすることも可能である。

### [0056]

また、バンク選択アドレス110の生成から、故障アドレスレジスタ111から故障アドレスが読み出され、ヒット信号113が出力されるまでの処理と、メモリ101からデータが読み出される処理とは、それぞれの処理が独立して行われることにより、アドレス変換や、入力アドレスと故障アドレスとの比較がメモリアクセスの速度に与える影響を、最小限にすることが可能である。

### [ 0 0 5 7 ]

なお、本実施形態では、アドレス変換回路107とバンク変換回路109とをそれぞれ別の回路として構成してあるが、バンク選択アドレス110は、アドレス変換回路107で変換された冗長アドレス108のビットの一部を切り出して使用しても良い。これによって、バンク変換回路109が不要となり、さらに回路規模を削減することが可能である

### [0058]

なお、入力アドレス106が示すメモリバンクの冗長領域が既に使用されている場合に 、新たな故障を救済するようにそのメモリバンクとあらかじめ対応付けられている他のメ モリバンクが、複数であっても良い。この場合、アドレス変換回路107は、受け取った入力アドレス106を変換して、複数の冗長アドレス108を生成して出力する。メモリ101は、入力アドレス106と複数の冗長アドレス108とによってアクセスされて、それぞれデータが読み出される。また、冗長アドレス108が複数であっても、それぞれアクセスされたデータを、互いに独立に読み出すことができるようにしても良い。

### 【産業上の利用可能性】

[0059]

以上説明したように、本発明は、故障アドレスを保持する回路の面積を削減し、メモリアクセスの速度低下を最小限に抑えるので、回路規模の縮小や高速なメモリアクセスが要求されるシステム等について有用である。

10

【図面の簡単な説明】

[0060]

- 【図1】本発明の実施形態に係るメモリシステム10の構成を示すブロック図である。

- 【図2】図1の入力アドレス106の構成を示す説明図である。

- 【図3】入力アドレス106が図2の値を示す場合の、冗長アドレス108の値を示す説明図である。

- 【図4】入力アドレス106が図2の値を示す場合の、バンク選択アドレス110の値を示す説明図である。

- 【図5】従来のメモリの冗長救済装置の構成を示すブロック図である。

### 【符号の説明】

[0061]

- 10 メモリシステム

- 101 メモリ

- 107 アドレス変換回路

- 109 バンク変換回路

- 111 故障アドレスレジスタ

- 112 ヒット信号生成回路

- 114 セレクタ

- 150A,150B,151A,151B,152A,152B,153A,153B メモリバンク

- 1 6 0 A , 1 6 0 B , 1 6 1 A , 1 6 1 B , 1 6 2 A , 1 6 2 B , 1 6 3 A , 1 6 3 B 冗長領域

30

# 【図1】

# 【図2】

# 【図3】

# 【図4】

# 【図5】

### フロントページの続き

(74)代理人 100117581

弁理士 二宮 克也

(74)代理人 100117710

弁理士 原田 智雄

(74)代理人 100121728

弁理士 井関 勝守

(74)代理人 100124671

弁理士 関 啓

(74)代理人 100131060

弁理士 杉浦 靖也

(72)発明者 大八木 睦

大阪府門真市大字門真1006番地 パナソニック半導体システムテクノ株式会社内

(72)発明者 西川 亮太

大阪府門真市大字門真1006番地 松下電器産業株式会社内

Fターム(参考) 5L106 CC01 CC04 CC11 CC21 CC32