#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

## (19) World Intellectual Property Organization

International Bureau

# (10) International Publication Number WO 2014/065301 A1

## (43) International Publication Date 1 May 2014 (01.05.2014)

(21) International Application Number:

PCT/JP2013/078634

(22) International Filing Date:

15 October 2013 (15.10.2013)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

2012-234427

24 October 2012 (24.10.2012)

JP

2012-234510

24 October 2012 (24.10.2012)

JP

2012-244909

6 November 2012 (06.11.2012)

JP

- (71) Applicant: SEMICONDUCTOR ENERGY LABORAT-ORY CO., LTD. [JP/JP]; 398, Hase, Atsugi-shi, Kanagawa, 2430036 (JP).

- (72) Inventor: YAMAZAKI, Shunpei; c/o SEMICONDUCT-OR ENERGY LABORATORY CO., LTD., 398, Hase, Atsugi-shi, Kanagawa, 2430036 (JP).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, KE, KG, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

[Continued on next page]

#### (54) Title: SEMICONDUCTOR DEVICE

(57) Abstract: Oxygen is likely to be released or an oxygen vacancy is likely to occur during a manufacturing process particularly at a side surface of an oxide semiconductor layer. When an oxygen vacancy occurs at the side surface of the oxide semiconductor layer, a problem arises in that the resistance of the side surface is reduced, the apparent threshold voltage of a transistor varies, and variation in the threshold voltage is increased. Further, the variation in the threshold voltage may cause unintentional current to flow between a source and a drain, which might lead to an increase in the offstate current of the transistor and deterioration in the electric characteristics of the transistor. A semiconductor device in which a multilayer film including an oxide semiconductor layer and an oxide layer surrounding the oxide semiconductor layer is used for a channel formation region is provided.

#

### Published:

— with international search report (Art. 21(3))

#### DESCRIPTION

# SEMICONDUCTOR DEVICE

# 5 TECHNICAL FIELD

[0001]

The present invention relates to a semiconductor device and a method for manufacturing the semiconductor device.

[0002]

In this specification, a semiconductor device generally means a device which can function by utilizing semiconductor characteristics, and an electrooptic device, a semiconductor circuit, and electronic equipment are all semiconductor devices.

# **BACKGROUND ART**

15 [0003]

20

25

Attention has been focused on a technique for forming a transistor using a semiconductor thin film (also referred to as a thin film transistor (TFT)). The transistor is applied to a wide range of electronic devices such as an integrated circuit (IC) or an image display device. A silicon-based semiconductor material is widely known as a material for a semiconductor thin film applicable to a transistor. As another example, an oxide semiconductor has been attracting attention.

For example, a transistor using an amorphous oxide containing indium (In), gallium (Ga), and zinc (Zn) for a channel formation region of a transistor is disclosed (see Patent Document 1).

[0005]

Further, it is known that oxygen is released from an oxide semiconductor during a manufacturing process, so that an oxygen vacancy is formed (see Patent Document 2).

30 [Reference]

[Patent Document]

[0006]

[Patent Document 1] Japanese Published Patent Application No. 2006-165528 [Patent Document 2] Japanese Published Patent Application No. 2011-222767

#### DISCLOSURE OF INVENTION

5 [0007]

During a manufacturing process, oxygen is likely to be released or an oxygen vacancy is likely to occur particularly at a side surface of an oxide semiconductor layer. When an oxygen vacancy occurs at the side surface of the oxide semiconductor layer, a problem arises in that the resistance of the side surface is reduced, the apparent threshold voltage of a transistor varies, and variation in the threshold voltage is increased. Further, the variation in the threshold voltage may cause unintentional current to flow between a source and a drain, which might lead to an increase in the off-state current of the transistor and deterioration in the electric characteristics of the transistor.

15 [0008]

10

20

25

30

In view of the above problems, an object of one embodiment of the present invention is to provide a semiconductor device including an oxide semiconductor layer and having little variation in electric characteristics. Another object is to provide a highly reliable semiconductor device including an oxide semiconductor layer and exhibiting stable electric characteristics. Another object is to provide a semiconductor device having stable electric characteristics. Another object is to provide a highly reliable semiconductor device. Another object is to provide a semiconductor device with low power consumption. Another object is to provide a semiconductor device that is less likely to have a defective shape. Another object is to provide a method for manufacturing any of the semiconductor devices. Another object is to provide a method for manufacturing a semiconductor device with high productivity. Another object is to provide a method for manufacturing a semiconductor device with high productivity. Another object is to provide a method for manufacturing a semiconductor device with high yield.

One embodiment of the present invention is a semiconductor device in which a multilayer film including an oxide semiconductor layer and an oxide layer surrounding the oxide semiconductor layer is used for a channel formation region.

[0010]

In the case where a transistor is formed using an oxide semiconductor, a carrier due to an oxygen vacancy might occur. Many oxygen vacancies in an oxide semiconductor layer including a channel formation region of the transistor lead to generation of electrons in the channel formation region, which causes defective electric characteristics of the transistor, for example, a normally-on state, an increase in leakage current, and a shift of the threshold voltage due to stress application. In the oxide semiconductor layer, hydrogen, silicon, nitrogen, carbon, and metal elements which are not the main component are impurities. For example, hydrogen has a donor level in the oxide semiconductor layer, which results in an increase in carrier density. Further, silicon has an impurity level in the oxide semiconductor layer and the impurity level serves as a trap, which might deteriorate the electric characteristics of the transistor.

Thus, to obtain stable electric characteristics of a semiconductor device including an oxide semiconductor layer, some measures need to be taken to reduce oxygen vacancies in the oxide semiconductor layer and decrease the concentration of impurities such as hydrogen and silicon.

[0012]

5

10

15

20

25

30

Thus, in a semiconductor device in one embodiment of the present invention, an oxide layer which contains one or more kinds of elements composing an oxide semiconductor layer and in which an oxygen vacancy occurs less frequently than in the oxide semiconductor layer is provided in contact with the top surface, the bottom surface, and a side surface of the oxide semiconductor layer so as to surround the oxide semiconductor layer in which a channel is formed. Accordingly, oxygen vacancies which may occur in the oxide semiconductor layer in which a channel is formed can be reduced. As a result, variation in the electric characteristics such as the threshold voltage of a transistor can be reduced.

[0013]

The oxide semiconductor layer and the oxide layer contain at least indium. The oxide layer has an energy gap wider than that of the oxide semiconductor layer, and the content ratio of indium in the oxide semiconductor layer is higher than the content ratio of indium in the oxide layer. As a typical example, an oxide containing indium, zinc, and the element M can be used for the oxide semiconductor layer and the oxide

WO 2014/065301 PCT/JP2013/078634

4

layer. In addition, the content ratio of the element M is preferably higher in the oxide layer than in the oxide semiconductor layer.

[0014]

An oxide preferably used for the oxide layer has a high content ratio of the element M such as gallium, aluminum, silicon, titanium, germanium, yttrium, zirconium, tin, lanthanum, cerium, or hafnium. These elements strongly bond with oxygen and need high energy for forming an oxygen vacancy, so that an oxygen vacancy is less likely to occur. For this reason, an oxygen vacancy is less likely to occur in an oxide layer that contains any of these elements with a high proportion, and the oxide layer has stable characteristics. Thus, when a surface of the oxide semiconductor layer is surrounded by the oxide layer, an oxygen vacancy is less likely to be formed at an end portion of the oxide semiconductor layer; as a result, a semiconductor device having stable characteristics can be obtained.

[0015]

5

10

15

20

25

30

Further, in the case where the end portion of a multilayer film has curvature in a cross section, the coverage with a film which is to be formed over the multilayer film can be improved. With such a structure, the film can be formed uniformly over the multilayer film so as to prevent an entry of an impurity element from a region having low film density or a region where the film is not formed into the multilayer film, which causes deterioration in the characteristics of a semiconductor device. Thus, a semiconductor device having stable characteristics can be obtained. Note that it is particularly preferable that the whole end portion, a lower end portion, or the lower end portion and an upper end portion of the multilayer film be curved.

Alternatively, the oxide layer may include a first oxide layer below the oxide semiconductor layer, a second oxide layer over the oxide semiconductor layer, and a third oxide layer which covers the side surface of the oxide semiconductor layer. The space between the surface of the oxide semiconductor layer and a surface of the oxide layer can be wider at a side portion of the multilayer film than at an upper portion thereof. The thickness of the multilayer film may be 1/50 to 50 times the radius of curvature of a curved surface on a side surface. With such a structure, a reduction in reliability of the semiconductor device in which the oxide semiconductor layer is

surrounded by the oxide layer can be suppressed.

[0017]

Further alternatively, a base insulating film may be provided below the multilayer film. The thickness of a region of the base insulating film which overlaps with the multilayer film is larger than the thicknesses of the other regions. The base insulating film includes a first region overlapping with the multilayer film, a second region surrounding the first region, and a third region surrounding the second region. The thickness of the second region is preferably smaller than that of the first region and the thickness of the third region is preferably smaller than that of the second region. The base insulating film having such a shape with a step (also referred to as a step-like shape) allows the step coverage with a film which is to be formed over the base insulating film and the multilayer film to be improved and the defective shapes of the semiconductor device to be reduced.

[0018]

5

10

15

20

25

30

The film can be formed uniformly over the multilayer film so as to prevent an entry of an impurity element from a region having low film density or a region where the film is not formed into the multilayer film, which causes deterioration in the characteristics of a semiconductor device. Thus, a semiconductor device having stable characteristics can be obtained. Note that it is particularly preferable that a lower end portion, or both the lower end portion and an upper end portion of the multilayer film be curved.

[0019]

In the semiconductor device in one embodiment of the present invention, which has the above structure, the oxide semiconductor layer serving as a channel (serving as a main path of a carrier) can be a highly purified intrinsic oxide semiconductor layer. Note that a highly purified intrinsic oxide semiconductor layer in this specification and the like refers to an oxide semiconductor layer having a Fermi level whose difference from the intrinsic Fermi level is  $0.5 \, \text{eV}$  or smaller. In this case, the carrier density of the oxide semiconductor layer is lower than  $1 \times 10^{17} / \text{cm}^3$ , lower than  $1 \times 10^{15} / \text{cm}^3$ , or lower than  $1 \times 10^{13} / \text{cm}^3$ . With a highly purified intrinsic oxide semiconductor layer, the transistor can have stable electric characteristics.

[0020]

Specifically, the following structure can be employed for example.

[0021]

5

One embodiment of the present invention is a semiconductor device including a multilayer film which includes an oxide semiconductor layer and an oxide layer surrounding the oxide semiconductor layer, a gate insulating film over the multilayer film, and a gate electrode overlapping with the multilayer film with the gate insulating film therebetween.

[0022]

One embodiment of the present invention is a semiconductor device including a gate electrode, a gate insulating film over the gate electrode, and a multilayer film overlapping with the gate electrode with the gate insulating film therebetween. The multilayer film includes an oxide semiconductor layer and an oxide layer surrounding the oxide semiconductor layer.

15 [0023]

One embodiment of the present invention is a semiconductor device including a gate electrode, a gate insulating film over the gate electrode, a multilayer film which overlaps with the gate electrode with the gate insulating film therebetween and includes an oxide semiconductor layer and an oxide layer surrounding the oxide semiconductor layer, and a source electrode and a drain electrode electrically connected to the oxide semiconductor layer. The oxide semiconductor layer and the oxide layer each contain indium, zinc, and a metal element other than indium and zinc as constituent elements. The content ratio of the metal element other than indium and zinc is higher in the oxide layer than in the oxide semiconductor layer.

25 [0024]

20

30

One embodiment of the present invention is a semiconductor device including a gate electrode; a gate insulating film over the gate electrode; a multilayer film which overlaps with the gate electrode with the gate insulating film therebetween and includes an oxide semiconductor layer, a first oxide layer in contact with a bottom surface of the oxide semiconductor layer, a second oxide layer in contact with a top surface of the oxide semiconductor layer, and a third oxide layer in contact with a side surface of the oxide semiconductor layer; and a source electrode and a drain electrode electrically

connected to the oxide semiconductor layer. The oxide semiconductor layer, the first oxide layer, the second oxide layer, and the third oxide layer are each an In-M-Zn oxide. The content ratio of an element M in each of the first oxide layer, the second oxide layer, and the third oxide layer is higher than that in the oxide semiconductor layer.

5 [0025]

10

15

20

30

One embodiment of the present invention is a semiconductor device including a gate electrode; a gate insulating film over the gate electrode; a multilayer film which overlaps with the gate electrode with the gate insulating film therebetween and includes an oxide semiconductor layer, a first oxide layer in contact with a bottom surface of the oxide semiconductor layer, a second oxide layer in contact with a top surface of the oxide semiconductor layer, and a third oxide layer in contact with a side surface of the oxide semiconductor layer; a source electrode and a drain electrode electrically connected to the oxide semiconductor layer; and a protective insulating film containing oxygen which is over the source electrode and the drain electrode and in contact with the multilayer film. The oxide semiconductor layer, the first oxide layer, the second oxide layer, and the third oxide layer are each an In-M-Zn oxide. The content ratio of an element M in each of the first oxide layer, the second oxide layer, and the third oxide layer is higher than that in the oxide semiconductor layer.

[0026]

Note that an absorption coefficient of a defect level (density of state (DOS)) in the multilayer film measured by a constant photocurrent method (CPM) is preferably lower than  $1 \times 10^{-3}$  cm<sup>-1</sup>.

[0027]

Further, the multilayer film is preferably surrounded by an insulating film containing excess oxygen.

[0028]

Furthermore, the oxide layer preferably includes a first region in contact with the bottom surface of the oxide semiconductor layer, a second region in contact with the top surface of the oxide semiconductor layer, and a third region in contact with the side surface of the oxide semiconductor layer. The third region preferably contains the same kind of element as that in the first region.

[0029]

With one embodiment of the present invention, variation in the electric characteristics of a semiconductor device including an oxide semiconductor layer can be reduced. Further, a semiconductor device having improved reliability and exhibiting stable electric characteristics can be provided. In addition, the above semiconductor device can be manufactured.

### BRIEF DESCRIPTION OF DRAWINGS

[0030]

5

15

25

30

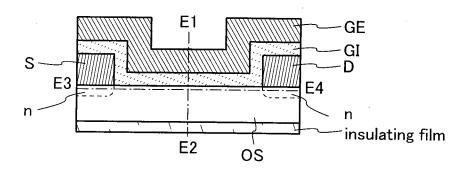

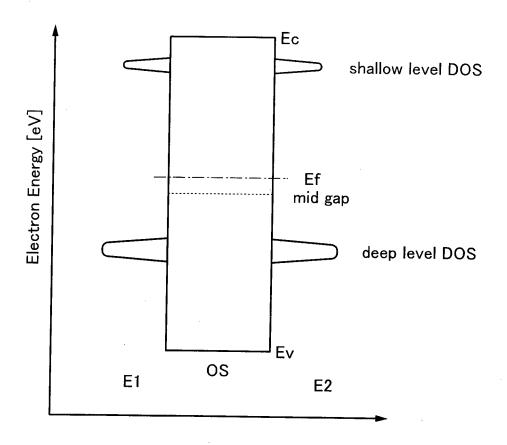

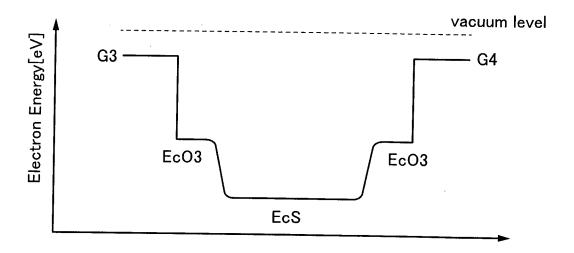

FIG. 1A is a cross-sectional view of a transistor including an oxide semiconductor layer and FIG. 1B shows a band structure thereof.

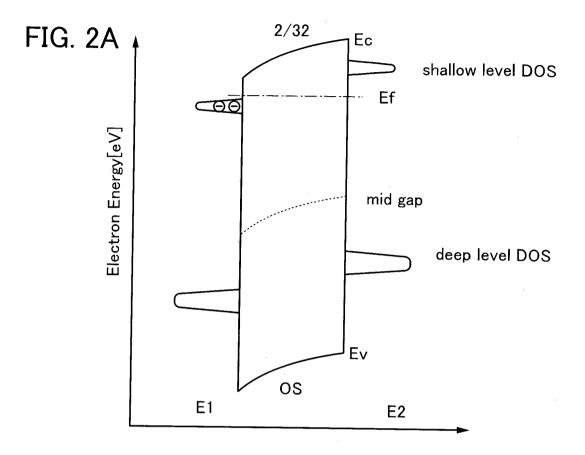

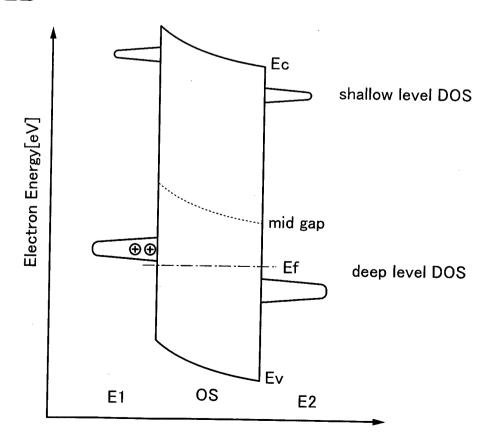

FIGS. 2A and 2B each show a band structure of a transistor including an oxide semiconductor layer.

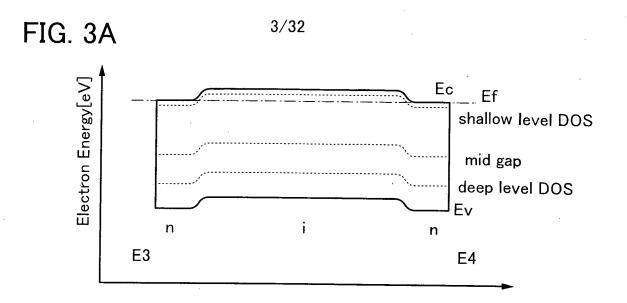

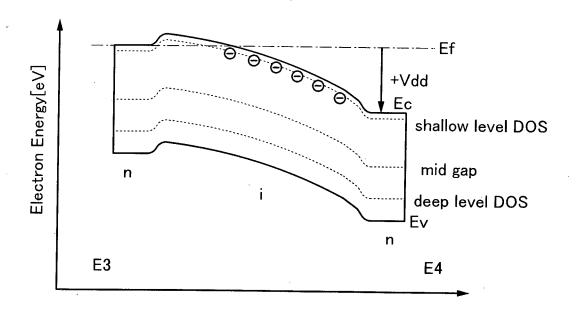

FIGS. 3A and 3B each show a band structure of a transistor including an oxide semiconductor layer.

FIG. 4 illustrates a cross-sectional structure of a calculation model.

FIG. 5 shows band structures of calculation models.

FIGS. 6A and 6B each show a band structure of a transistor including an oxide semiconductor layer.

FIG. 7 shows Vg-Id characteristics of a transistor including an oxide 20 semiconductor layer.

FIG. 8 shows Vg-Id characteristics of a transistor including an oxide semiconductor layer.

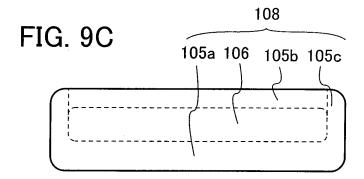

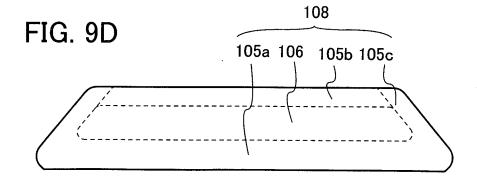

FIGS. 9A to 9D are a cross-sectional views each illustrating a multilayer film in one embodiment of the present invention.

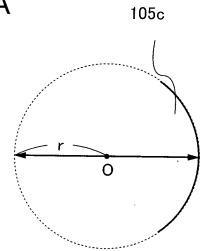

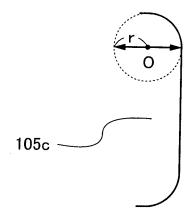

FIGS. 10A to 10C are diagrams illustrating the radius of curvature.

FIGS. 11A to 11C are cross-sectional views illustrating a formation mechanism of a multilayer film in one embodiment of the present invention.

FIGS. 12A to 12C are cross-sectional views illustrating a formation mechanism of a multilayer film in one embodiment of the present invention.

FIGS. 13A and 13B are cross-sectional views illustrating a formation mechanism of a multilayer film in one embodiment of the present invention.

FIGS. 14A to 14C are cross-sectional views illustrating a formation mechanism

15

20

of a multilayer film in one embodiment of the present invention.

- FIGS. 15A to 15C are cross-sectional views illustrating a formation mechanism of a multilayer film in one embodiment of the present invention.

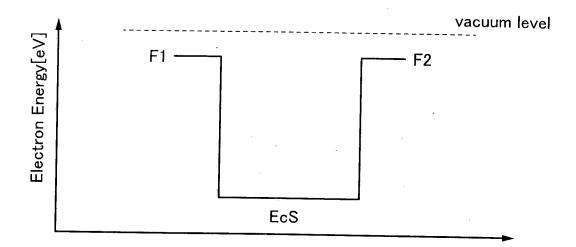

- FIG. 16A is a cross-sectional view of the case where an oxide semiconductor layer is a single layer and FIG. 16B shows a band structure thereof.

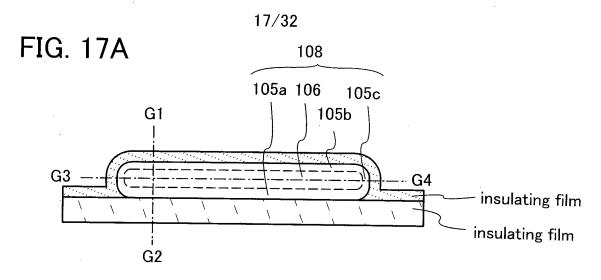

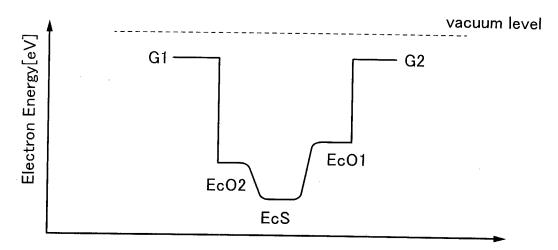

- FIG. 17A is a cross-sectional view of the case of where a multilayer film is used and FIGS. 17B and 17C show band structures thereof.

- FIGS. 18A to 18C each show diffusion of oxygen in a multilayer film in one embodiment of the present invention.

- FIGS. 19A and 19B show results of CPM measurement of a multilayer film in one embodiment of the present invention.

- FIG. 20 shows ToF-SIMS results of a multilayer film in one embodiment of the present invention.

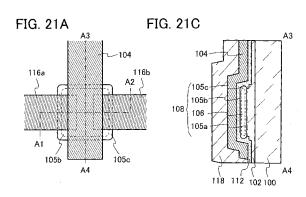

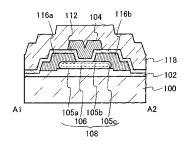

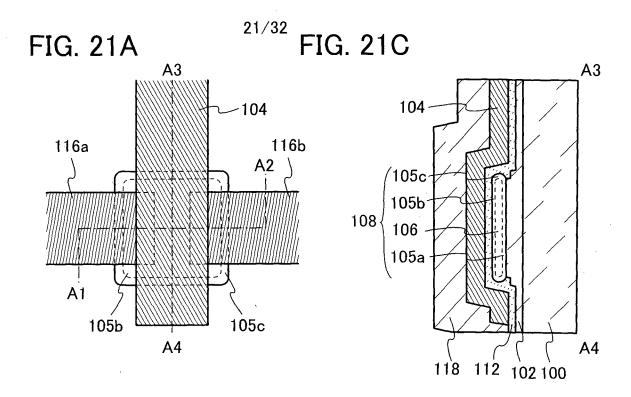

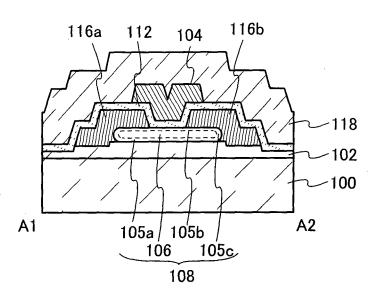

- FIGS. 21A to 21C are a top view and cross-sectional views illustrating a semiconductor device in one embodiment of the present invention.

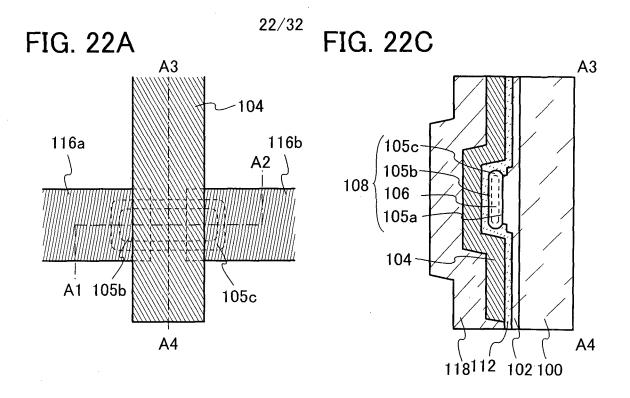

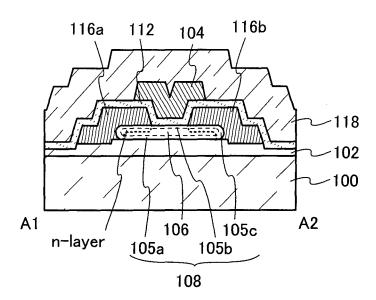

- FIGS. 22A to 22C are a top view and cross-sectional views illustrating a semiconductor device in one embodiment of the present invention.

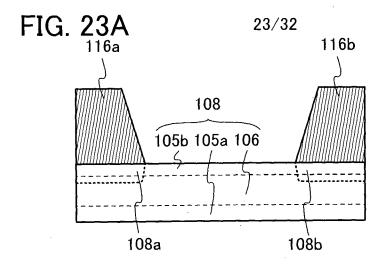

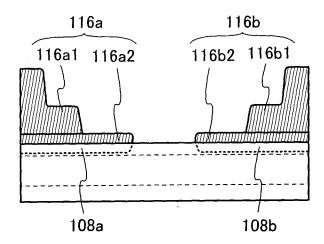

- FIGS. 23A to 23C are cross-sectional views each illustrating shapes of a source electrode and a drain electrode.

- FIGS. 24A to 24C are cross-sectional views illustrating a method for manufacturing a semiconductor device in one embodiment of the present invention.

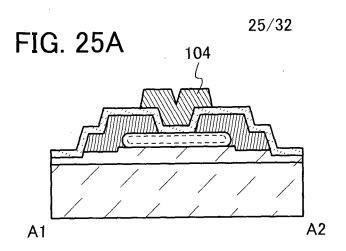

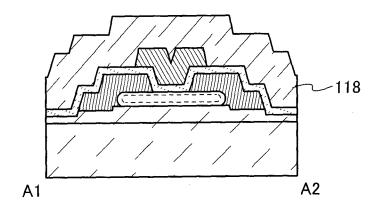

- FIGS. 25A and 25B are cross-sectional views illustrating a method for manufacturing a semiconductor device in one embodiment of the present invention.

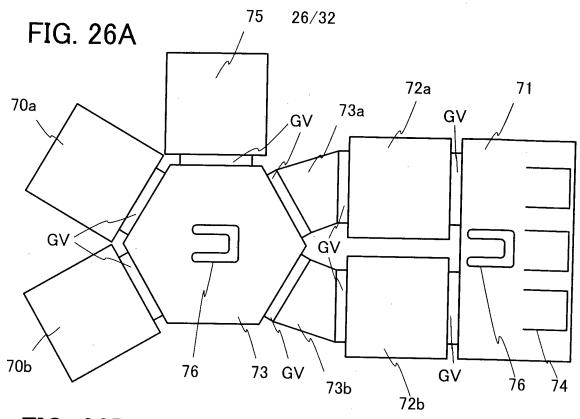

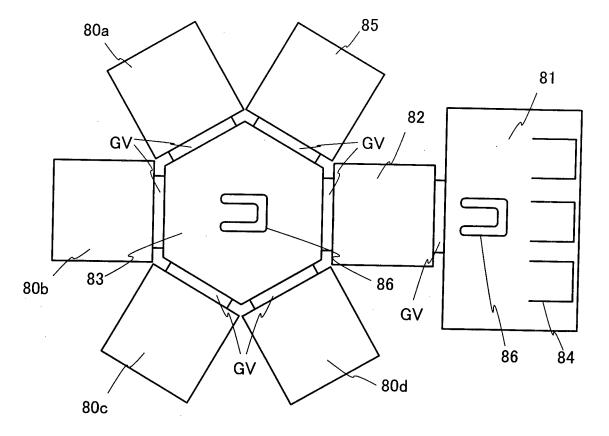

- FIGS. 26A and 26B are top views each illustrating an example of a deposition apparatus.

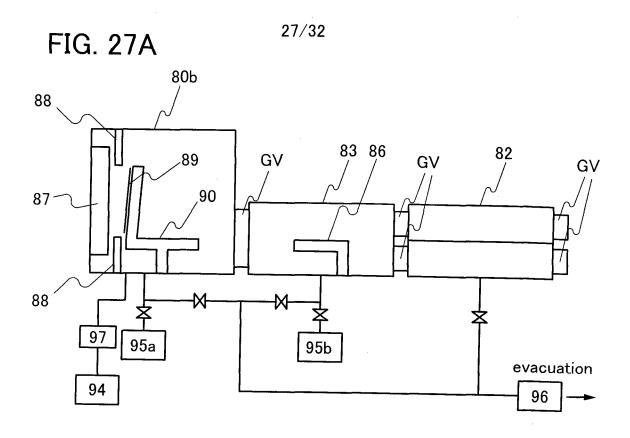

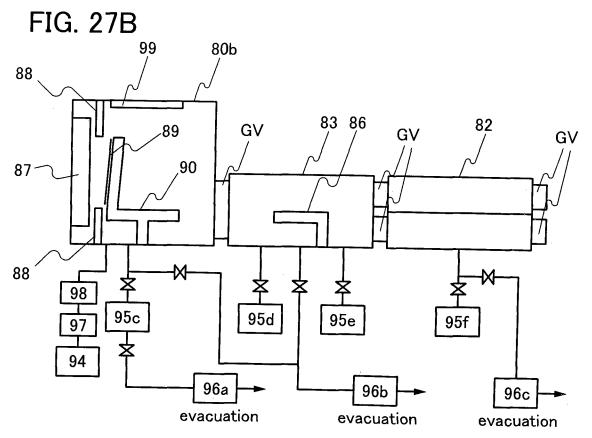

- FIGS. 27A and 27B are cross-sectional views each illustrating an example of a deposition chamber.

- FIG. 28 illustrates an example of a heat treatment chamber.

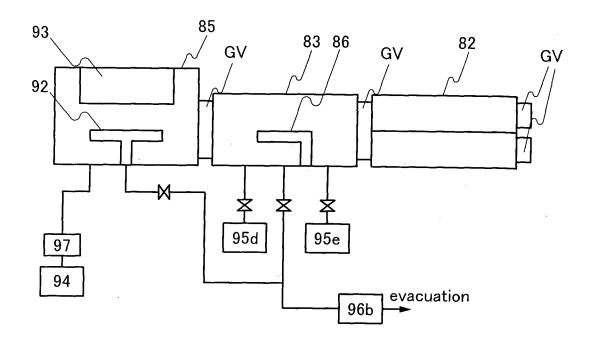

- FIGS. 29A to 29D are a top view and cross-sectional views illustrating a semiconductor device in one embodiment of the present invention.

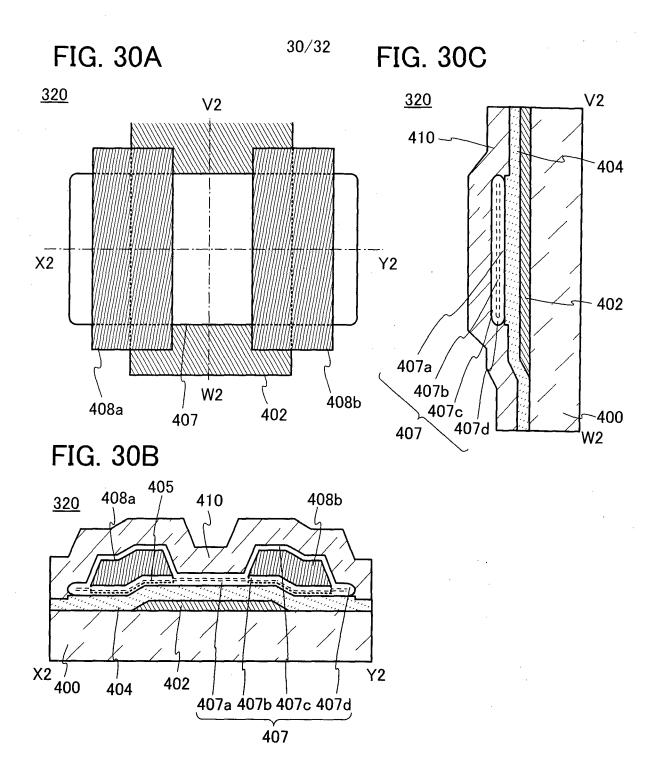

- FIGS. 30A to 30C are a top view and cross-sectional views illustrating a semiconductor device in one embodiment of the present invention.

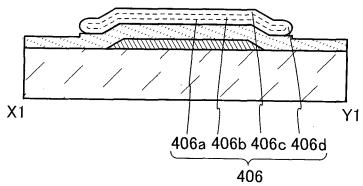

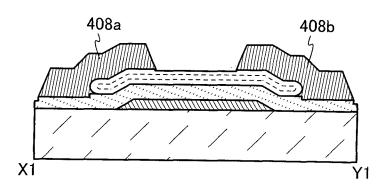

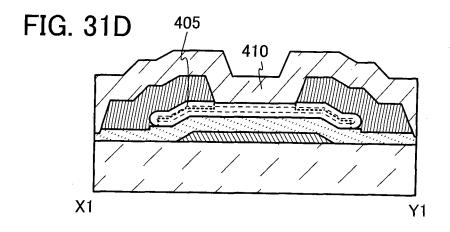

FIGS. 31A to 31D are cross-sectional views illustrating a method for manufacturing a semiconductor device in one embodiment of the present invention.

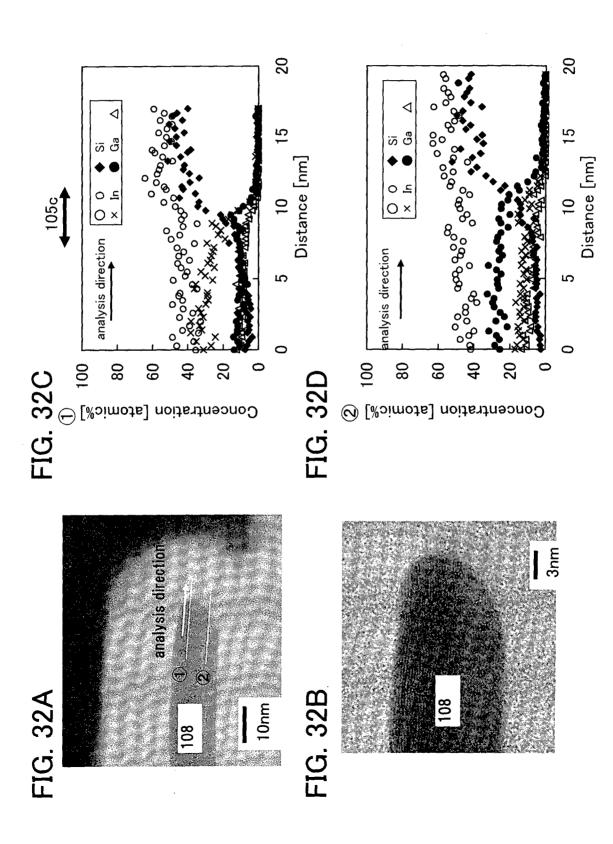

FIGS. 32A to 32D show cross-sectional observation images and composition of a multilayer film.

5

10

15

20

25

30

# BEST MODE FOR CARRYING OUT THE INVENTION [0031]

Embodiments and an example of the present invention are described below in detail with reference to the accompanying drawings. However, the present invention is not limited to the following description and it is easily understood by those skilled in the art that the mode and details can be variously changed. In addition, the present invention should not be construed as being limited to the description in the following embodiments and the example. In describing structures of the present invention with reference to the drawings, the same reference numerals are used in common for the same portions in different drawings. Note that the same hatch pattern is applied to similar parts, and in some cases the similar parts are not especially denoted by reference numerals.

[0032]

Note that in the actual manufacturing process, a resist mask or the like might be unintentionally reduced in size by treatment such as etching, which is not illustrated in some cases for easy understanding.

[0033]

Further, the ordinal numbers such as "first" and "second" in this specification are used for convenience and do not indicate the order of steps or the stacking order of layers. In addition, the ordinal numbers in this specification do not indicate particular names which specify the present invention.

[0034]

Note that in many cases, a voltage refers to a potential difference between a certain potential and a reference potential (e.g., a ground potential (GND) or a source potential). Accordingly, a voltage can also be called a potential.

[0035]

Even when the expression "to be electrically connected" is used, there is a case

in which no physical connection is made and a wiring is just extended in an actual circuit.

[0036]

Further, functions of a source and a drain might be switched when a direction of current flow is changed in circuit operation, for example. Thus, the terms "source" and "drain" can be switched in this specification.

[0037]

The descriptions in this embodiment can be combined with each other as appropriate.

10 [0038]

5

<1. Deterioration Mechanism of Transistor Including Oxide Semiconductor Layer>

First, a deterioration mechanism model of a transistor including an oxide semiconductor layer will be described to show that the removal or reduction of DOS is effective to improve reliability of the transistor including the oxide semiconductor layer.

15 [0039]

20

25

30

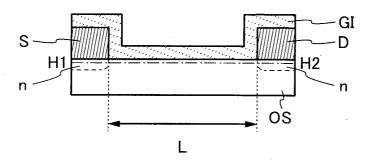

An example of the transistor including the oxide semiconductor layer is illustrated in FIG. 1A. In FIG. 1A, "OS" denotes an oxide semiconductor layer, "S" denotes a source electrode, "D" denotes a drain electrode, "GI" denotes a gate insulating film, and "GE" denotes a gate electrode. Note that an n-layer (denoted by "n" in the drawings) having higher carrier density than the oxide semiconductor layer is included between the oxide semiconductor layer and the source and drain electrodes.

FIG. 1B shows a band structure along dashed-dotted line E1-E2 in FIG. 1A. According to FIG. 1B, there are two kinds of DOS: shallow level DOS and deep level DOS. A common factor causing the shallow level and the deep level is an oxygen vacancy (Vo). In an oxide semiconductor layer containing indium, in particular, an oxygen atom which is adjacent to an indium atom is released, so that an oxygen vacancy is formed. Note that "Ec" denotes the lowest conduction band energy of the oxide semiconductor layer, "Ev" denotes the highest valence band energy of the oxide semiconductor layer, "Ef" denotes the Fermi energy of the oxide semiconductor layer, and "mid gap" denotes the middle of the energy gap of the oxide semiconductor layer (intrinsic level). It is assumed that the oxide semiconductor layer is an intrinsic

WO 2014/065301 PCT/JP2013/078634

12

(i-type) or substantially intrinsic oxide semiconductor layer. In that case, the Fermi energy coincides with "mid gap"; however, they are slightly shifted from each other in the drawings for easy understanding. Note that DOS distributes in the energy axis direction and its height (the direction perpendicular to the electron energy axis) indicates the density of DOS.

[0041]

5

15

20

25

In the case where voltage is not applied to the gate electrode, DOS is neutral and is not positively or negatively charged.

[0042]

When positive voltage is applied to the gate electrode, the band of the oxide semiconductor layer curves as shown in FIG. 2A. Further, in the case where shallow level energy is lower than the Fermi energy because of the electric field from the gate electrode, a negative charge (e.g., electron) is trapped in the shallow level.

[0043]

Similarly, when negative voltage is applied to the gate electrode, the band of the oxide semiconductor layer curves as shown in FIG. 2B. Further, in the case where deep level energy is higher than the Fermi energy because of the electric field from the gate electrode, a positive charge (e.g., hole) is trapped in the deep level.

[0044]

Since a charge trapped in DOS of the oxide semiconductor layer has an extremely long relaxation time  $(\tau)$ , the charge is held for a long time even when the electric field from the gate electrode is stopped. Thus, the charge trapped in DOS behaves like a fixed charge. For example, in the case where a negative charge is trapped in a shallow level, the charge works in a manner similar to that in the case where an electric field is generated by a negative fixed charge and as a result, the threshold voltage of a transistor shifts in the positive direction. On the other hand, in the case where a positive charge is trapped in a deep level, the charge works in a manner similar to that in the case where an electric field is generated by a positive fixed charge and as a result, the threshold voltage of the transistor shifts in the negative direction.

30 [0045]

As described above, the transistor including the oxide semiconductor layer has a deterioration mechanism in which the threshold voltage shifts in the positive direction

or the negative direction depending on DOS in the oxide semiconductor layer. This shows that the removal or reduction of DOS is effective to improve the reliability of the transistor including the oxide semiconductor layer.

[0046]

5

10

15

25

Next, deterioration caused by the application of positive voltage to the drain electrode of the transistor will be described.

[0047]

FIG. 3A shows a band structure along dashed-dotted line E3-E4 in FIG. 1A. Note that an oxide semiconductor layer (OS) is shown as an i-layer (denoted by "i") in FIG. 3A to be distinguished from the n-layer.

[0048]

As shown in FIG. 3A, the Fermi energy of the oxide semiconductor layer is higher than the mid gap. This is because when the distance between the source electrode and the drain electrode is sufficiently short, the lowest conduction band energy (Ec) is lowered by the effect of the source electrode and the drain electrode and thus, the lowest conduction band energy and the Fermi energy come close to each other. This phenomenon is called a conduction band lowering (CBL) effect. The CBL effect is an effect specific to an oxide semiconductor, which is due to an extremely large depletion layer of the oxide semiconductor layer.

20 [0049]

Here, the CBL effect will be described in detail. [0050]

It seems intuitively that in the case where an intrinsic or substantially intrinsic oxide semiconductor layer is used as the oxide semiconductor layer, a barrier that is about half the energy gap of the oxide semiconductor layer is formed between the source and drain electrodes and the oxide semiconductor layer. However, the transistor including the oxide semiconductor layer actually has such Vg-Id characteristics that drain current starts to flow when gate voltage is about 0 V. [0051]

In view of the above, the following structure illustrated in FIG. 4 is assumed: an oxide semiconductor layer (OS) is provided; a source electrode (S) and a drain electrode (D) are provided over the oxide semiconductor layer; and a gate insulating film (GI) is

provided over the oxide semiconductor layer, the source electrode, and the drain electrode. Then, a band structure along dashed-dotted line H1-H2 of the case where the channel length (L) is changed is calculated. In FIG. 4, an n-layer is provided in regions of the oxide semiconductor layer, which are in contact with the source electrode and the drain electrode.

[0052]

5

10

15

20

25

30

From an estimate of the curve width of the band obtained by solving the Poisson's equation, the curve width of the band is found to be characterized by the Debye shielding length  $\lambda_D$  in the following formula. Note that  $k_B$  in the following formula is the Boltzmann constant.

[0053]

[Formula 1]

the curve width of the band -  $\sqrt{\frac{\varepsilon\varepsilon_0 k_B T}{e^2 n i}}$  - the Debye shielding length  $\lambda_D$  [0054]

By substituting  $6.6 \times 10^{-9}$  cm<sup>-3</sup> for the intrinsic carrier density ni of the oxide semiconductor layer, 15 for the relative permittivity  $\varepsilon$  of the oxide semiconductor layer, and 300 K for temperature T in the above formula, the Debye shielding length  $\lambda_D$  is found to be as long as  $5.7 \times 10^{10}$   $\mu m$ . This indicates that when the channel length is greater than  $1.14 \times 10^{11}$   $\mu m$ , which is twice as large as the Debye shielding length  $\lambda_D$ , the height of a barrier between the n-layer and the i-layer is half the energy gap of the oxide semiconductor layer.

[0055]

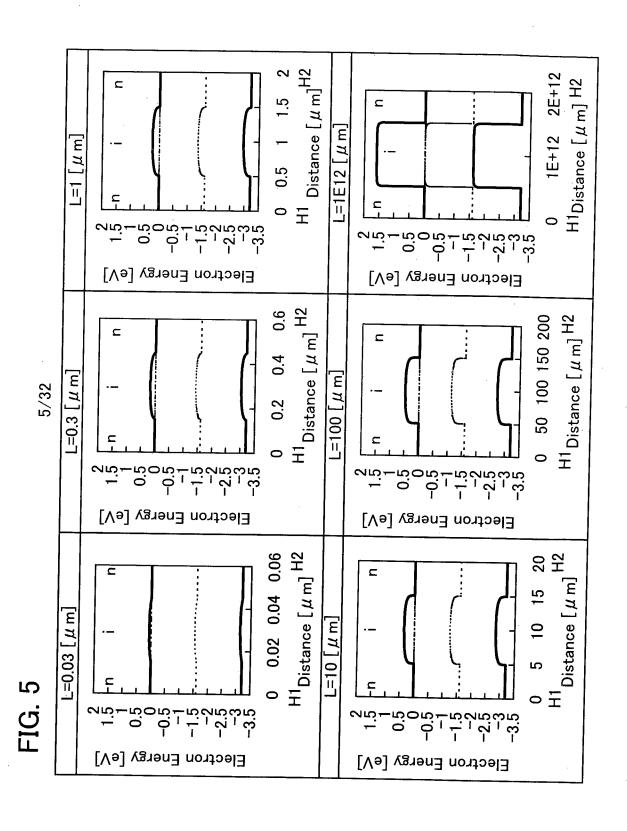

FIG. 5 shows calculation results of band structures with channel lengths of 0.03  $\mu m$ , 0.3  $\mu m$ , 1  $\mu m$ , 10  $\mu m$ , 100  $\mu m$ , and 1  $\times$  10  $^{12}$   $\mu m$ . Note that in FIG. 5, "n" denotes the n-layer and "i" denotes a region of an oxide semiconductor layer (i-layer) which is sandwiched between the n-layers, and a dashed-dotted line represents the Fermi energy of the oxide semiconductor layer and a dashed line indicates the mid gap of the oxide semiconductor layer.

[0056]

According to FIG. 5, in the case where a channel length is as large as  $1 \times 10^{12}$

$\mu$ m, the difference in electron energy between the i-layer and the n-layer is half the energy gap of the oxide semiconductor layer. However, the difference in electron energy between the i-layer and the n-layer gradually becomes smaller as the channel length becomes smaller, and there is almost no barrier when the channel length is 1  $\mu$ m or less. Note that the electron energy of the n-layer is fixed by the source electrode and the drain electrode.

[0057]

As described above, the barrier between the n-layer and the i-layer is sufficiently small when the channel length is small.

10 [0058]

Owing to the CBL effect, the subthreshold value of the transistor including the oxide semiconductor layer is reduced to near the theoretical limit even when there is a barrier between the source and drain electrodes and the oxide semiconductor layer; thus, favorable switching characteristics are obtained.

15 [0059]

When positive voltage Vdd is applied to the drain electrode, the band structure shown in FIG. 3A turns into a band structure shown in FIG. 3B. When positive voltage is applied to the gate electrode at this time, current flows in the forward direction of the transistor. In that case, more negative charges are accumulated in the shallow level with energy that is lower than the Fermi energy. This indicates that the shallow level energy is likely to be much lower than the Fermi energy when positive voltage is applied to the drain electrode. Thus, even when positive voltage or negative voltage is applied to the gate electrode, the threshold voltage might shift in the positive direction depending on voltage applied to the drain electrode.

25 [0060]

20

30

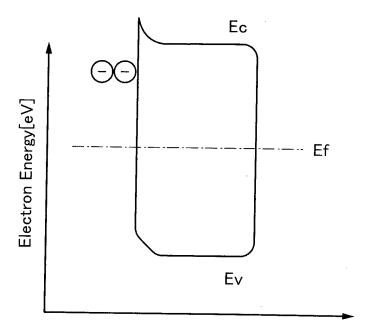

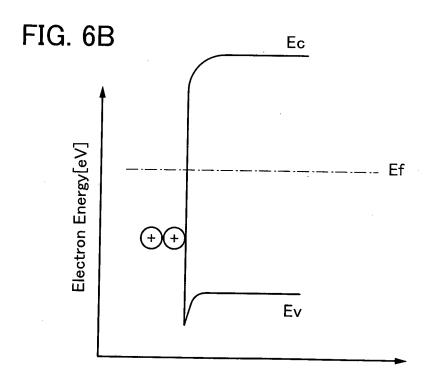

Further, after positive voltage is applied to the gate electrode, a gate potential is set to be equal to a source potential (ground potential (GND)), whereby a band structure shown in FIG. 6A or FIG. 6B is obtained. At this time, the surface band bends towards opposite directions depending on a trapped charge. For example, in the case where a negative charge is trapped as shown in FIG. 6A, the band bends in the normally-off direction and the threshold voltage shifts in the positive direction. Alternatively, in the

case where a positive charge is trapped as shown in FIG. 6B, the band bends in the normally-on direction and the threshold voltage shifts in the negative direction.

[0061]

In a channel having n-type conductivity (n type conductivity), an electron can easily pass from the source to the drain and a path is formed between the source and the drain. As a result, the switching characteristics are hard to be obtained. To avoid this, the channel needs to be completely prevented from having n-type conductivity and needs to be necessarily intrinsic (i-type).

[0062]

5

Here, causes and remedies of DOS will be described. [0063]

Formation of an oxygen vacancy due to silicon is one of the causes of DOS. Specifically, a bond between indium and oxygen is cut by silicon and an oxygen vacancy is formed as shown in the following Chemical Formula (1).

15 [0064]

[Chemical Formula 1]

[0065]

To suppress the formation of an oxygen vacancy due to silicon, it is important that silicon, which is a substance inducing DOS formation, be prevented from being in contact with the oxide semiconductor layer or entering the oxide semiconductor layer. It is particularly important that an oxide semiconductor layer containing indium be separated from a layer containing silicon.

[0066]

Damage by plasma is another cause of DOS. In the case where plasma is used to form the oxide semiconductor layer or a layer which is to be formed over the oxide semiconductor layer, the oxide semiconductor layer might be damaged by the plasma and an In-O-In bond having the weakest bonding might be cut, which causes an oxygen vacancy (see Chemical Formula (2) below). In addition, the released oxygen

bonds with hydrogen to produce water.

[0067]

[Chemical Formula 2]

InVo + O-In + 2H

$$\downarrow \qquad \cdots (2)$$

2InVo +  $H_2O$

5 [0068]

To reduce DOS, it is important to reduce damage of the oxide semiconductor layer by plasma and to supply oxygen to the oxide semiconductor layer by heat treatment for repairing an oxygen vacancy.

[0069]

Then, two kinds of DOS, which might be formed in the oxide semiconductor layer, will be described below.

[0070]

A deep level, which is one kind of DOS, is described in detail. The deep level is DOS in a deep level (deep position in terms of energy as compared with the lowest conduction band energy (Ec)) which is in a band gap (field band) between the highest valence band energy (Ev) and the mid gap. As described above, an oxygen vacancy is formed when an In-O-In bond in the oxide semiconductor layer is cut. This oxygen vacancy becomes a neutral deep level. The deep level becomes a hole trapping center and a positively charge is trapped above the Fermi energy.

20 [0071]

15

Note that the deep level can be quantified by CPM.

[0072]

Next, a shallow level, which is another kind of DOS, is described in detail. The shallow level is said to be in a position in the band gap which is close to the lowest conduction band energy.

[0073]

25

Here, the shallow level is assumed to be In-VoH. That is, a neutral becomes

an electron trapping center and a negatively charge is trapped below the Fermi energy. The neutrals are formed as follows: a large amount of hydrogen contained in the oxide semiconductor layer comes close to oxygen vacancies.

[0074]

5

10

15

20

25

30

To reduce oxygen vacancies, the oxide semiconductor layer in which the channel is formed is surrounded (or wrapped or covered) by an oxide semiconductor layer containing a small amount of In (or containing a large amount of M such as Ga), whereby the channel where current flows can be separated from impurities which might be contained in an insulating film in contact with the oxide semiconductor layer. As the insulating film in contact with the oxide semiconductor layer, a silicon oxide film can be given, for example. Silicon becomes a substance inducing Vo formaiton. [0075]

Since DOS is less likely to be formed in the oxide semiconductor layer containing a small amount of In (or containing a large amount of M such as Ga), DOS is less likely to be formed at an interface between the oxide semiconductor layer which surrounds the channel and a silicon oxide film. The proportion of M (e.g., Ga) atoms in the oxide semiconductor layer surrounding the channel is increased and M (e.g., Ga) is substituted for In in an In-O plane of the oxide semiconductor layer, whereby the number of In-O bonds having weak bonding is reduced and Vo is less likely to be formed. This enables a transistor to have stable electric characteristics (or high reliability).

[0076]

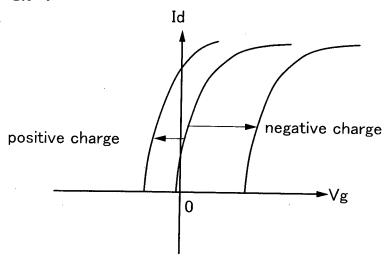

FIG. 7 shows a relation between Vg-Id characteristics and DOS. As shown in FIG. 7, the threshold voltage shifts in the negative direction in the Vg-Id characteristics when a positive charge is trapped in the deep level. On the other hand, the threshold voltage shifts in the positive direction in the Vg-Id characteristics when a negative charge is trapped in the shallow level.

[0077]

When positive voltage is applied to the drain and the shallow level energy is lower than the Fermi energy, DOS is likely to be negatively charged. This means that the threshold voltage likely shifts in the positive direction. To prevent this shift, the number of shallow levels needs to be reduced.

[0078]

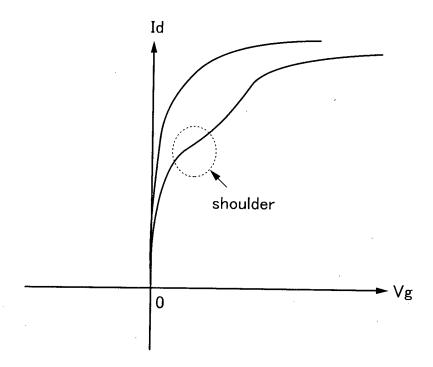

Further, when constant positive voltage is applied to the drain so that the gate voltage can vary, the shallow level energy becomes lower than the Fermi energy and DOS is negatively charged in accordance with the drain voltage and the gate voltage. This negative charge apparently exhibits the same effect as the case where negative voltage is applied to the gate voltage. Thus, the drain current (Id) is decreased, in other words, a shoulder appears, at a position where the gate voltage is low in a graph of the Vg-Id characteristics (see FIG. 8).

[0079]

5

The shoulder shown in FIG. 8 appears when positive voltage is applied to the drain. When DOS at the gate electrode side to which higher electric field is applied (particularly in the shallow level) is reduced, the shoulder shown in FIG. 8 can be probably relieved.

[0080]

The above description shows that the removal or reduction of DOS is effective to improve the reliability of the transistor including the oxide semiconductor layer.

[0081]

<2. Multilayer Film Including Oxide Semiconductor Layer>

A multilayer film having a small number of DOS, with which a transistor including an oxide semiconductor layer and having stable electric characteristics can be fabricated, will be described below.

[0082]

<2-1. Structure of Multilayer Film>

In this section, a structure of the multilayer film is described.

25 [0083]

The multilayer film having low DOS has a structure in which an oxide layer is provided so as to surround an oxide semiconductor layer in which a channel is formed. In the oxide layer, DOS is less likely to be formed than in the oxide semiconductor layer. Note that there are a variety of possible methods for forming the structure in which the oxide semiconductor layer is surrounded by the oxide layer, and one of them is described below.

[0084]

30

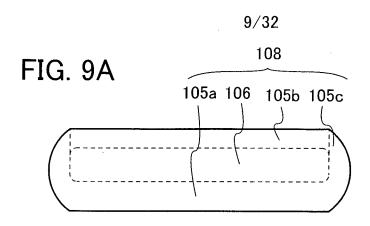

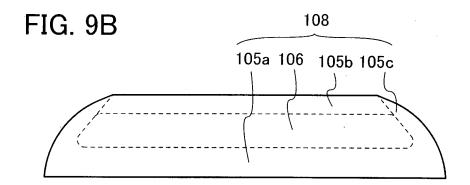

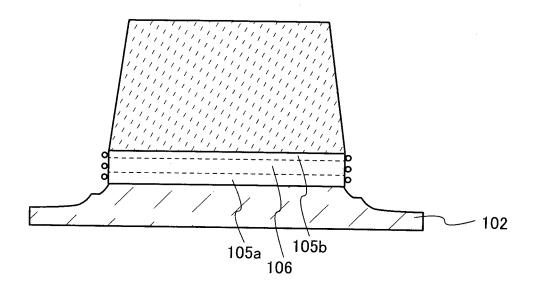

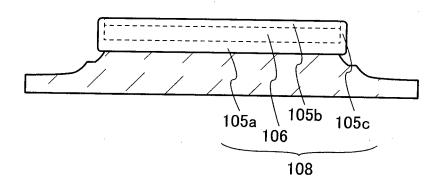

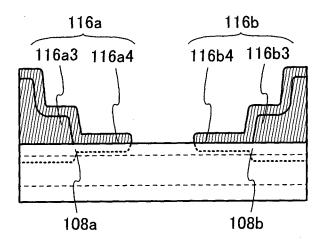

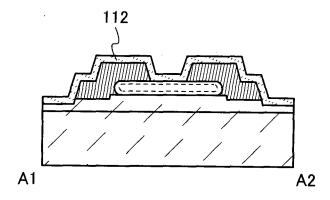

FIG. 9A to FIG. 9D each illustrate a cross-sectional structure of a multilayer film 108. The multilayer film 108 includes an oxide layer 105a, an oxide semiconductor layer 106 provided over the oxide layer 105a, an oxide layer 105b provided over the oxide semiconductor layer 106, and an oxide layer 105c which is in contact with at least a side surface of the oxide semiconductor layer 106. Note that the oxide layer 105c has a curved surface.

[0085]

In one of the side surfaces of a cross section of the multilayer film 108 illustrated in FIG. 9A or FIG. 9B, the oxide layer 105c has curvature (a curved surface) based on one osculating circle (also referred to as a circle of curvature). On the other hand, in one of the side surfaces of a cross section of the multilayer film 108 illustrated in FIG. 9C or FIG. 9D, the oxide layer 105c has curvature based on one osculating circle at each of an upper end portion and a lower end portion.

As in the multilayer film 108 in FIG. 9A or FIG. 9C, side surfaces of the oxide layer 105a, the oxide semiconductor layer 106, and the oxide layer 105b may be substantially perpendicular to the bottom surface of the oxide layer 105a. Alternatively, the multilayer film 108 may have a slope (taper angle) as illustrated in FIG. 9B and FIG. 9D.

20 [0087]

With the above-described oxide layer 105c having a curved side surface, which is part of the multilayer film 108, occurrence of a shape defect of a transistor including the multilayer film 108 can be reduced.

[8800]

25 <2-1-1. Oxide Layer Forming End Portion of Multilayer Film>

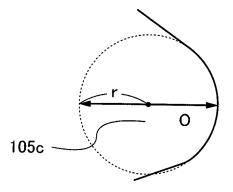

A curved surface included in the oxide layer 105c will be described with reference to FIGS. 10A to 10C.

[0089]

30

FIG. 10A is a cross-sectional view of the oxide layer 105c, which corresponds to each of the side surfaces of the cross sections of the multilayer films 108 in FIG. 9A and FIG. 9B. The oxide layer 105c illustrated in FIG. 10A has curvature based on an osculating circle whose radius of curvature is r. Note that the radius of curvature is

equal to the radius of an osculating circle of a curve. [0090]

FIG. 10B is a cross-sectional view of the oxide layer 105c, which corresponds to each of the side surfaces of the cross sections of the multilayer films 108 in FIG. 9C and FIG. 9D. The oxide layer 105c illustrated in FIG. 10B has curvature based on an osculating circle whose radius of curvature is r at each of the upper end portion and the lower end portion. Note that the curvature of the upper end portion and the curvature of the lower end portion may have different radiuses of curvature. [0091]

The oxide layer 105c illustrated in FIG. 10C has curvature based on an osculating circle whose radius of curvature is r. Note that the oxide layer 105c may have two or three portions with curvatures based on different osculating circles.

[0092]

At this time, the radius of curvature r is 1/50 to 50 times as large as the thickness t of the multilayer film 108 (the total thickness of the oxide layer 105a, the oxide semiconductor layer 106, and the oxide layer 105b), preferably 1/20 to 20 times as large as the thickness t, further preferably 1/10 to 10 times as large as the thickness t, still further preferably 1/5 to 5 times as large as the thickness t. [0093]

20 <2-1-2. Formation Mechanism of Multilayer Film>

A formation mechanism of the multilayer film 108 which includes the oxide layer 105c having a curved surface will be described.

[0094]

<2-1-3. Formation Mechanism (1)>

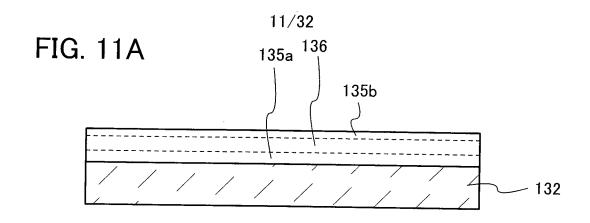

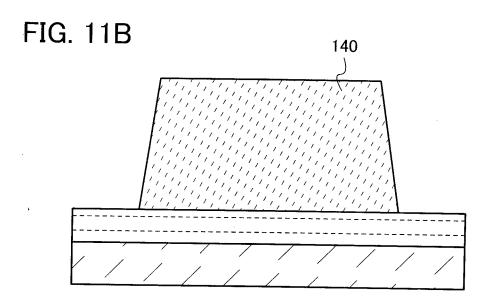

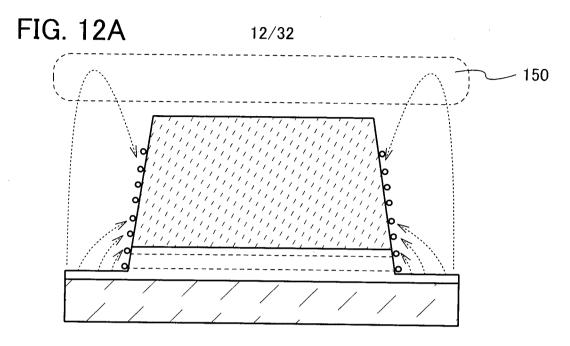

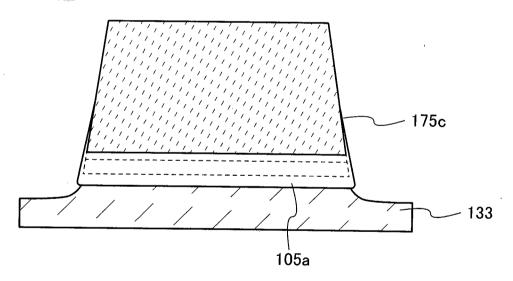

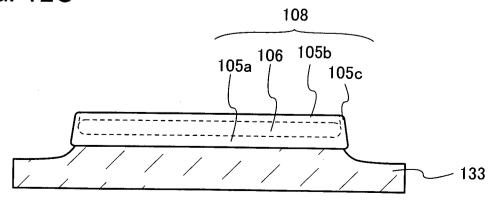

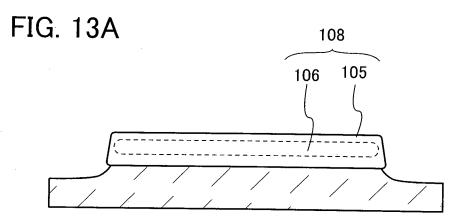

An example of the formation mechanism of the multilayer film 108 which includes the oxide layer 105c having a curved surface is described with reference to FIGS. 11A to 11C, FIGS. 12A to 12C, and FIGS. 13A and 13B.

[0095]

First, a multilayer film including an oxide layer 135a provided over a base insulating film 132, an oxide semiconductor layer 136 provided over the oxide layer 135a, and an oxide layer 135b provided over the oxide semiconductor layer 136 is prepared (see FIG. 11A).

ा अत्राह्म । भारति व मुक्कारीक अस्माक्ष । जा कर

[0096]

Next, a resist mask 140 is formed over part of the oxide layer 135b (see FIG. 11B).

[0097]

5

10

15

20

25

30

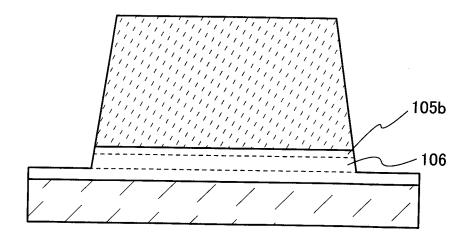

Then, the oxide layer 135b and the oxide semiconductor layer 136 in a region where the resist mask 140 is not provided are etched by a dry etching method, so that the oxide layer 135a is exposed (see FIG. 11C).

[0098]

After that, the oxide layer 135a exposed by the dry etching method is etched (see FIG. 12A). At this time, a reaction product of the oxide layer 135a is attached to at least a side surface of the oxide semiconductor layer 106 in the multilayer film to form an oxide layer serving as a sidewall protective film (also referred to as a rabbit ear). Note that the reaction product of the oxide layer 135a is attached by a sputtering phenomenon or through plasma 150 at the time of the dry etching. The dry etching may be performed under the following conditions, for example: a boron trichloride gas and a chlorine gas are used as etching gases, and inductively coupled plasma (ICP) power and substrate bias power are applied.

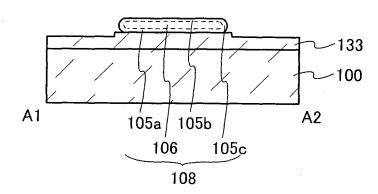

Subsequently, the oxide layer 135a is etched so that the oxide layer 105a and an oxide layer 175c are formed. At this time, the base insulating film 132 is partly etched to be a base insulating film 133 (see FIG. 12B).

[0100]

Note that since the oxide layer 175c is formed using the reaction product of the oxide layer 135a, constituent of the etching gas used at the time of etching (e.g., chlorine and boron) remains therein. When the constituent reacts with moisture or the like in the air, for example, the oxide layer 175c is further etched.

[0101]

Next, the constituent of the etching gas remaining in the etched oxide layer 175c is removed by ashing treatment, whereby an oxide layer to be the oxide layer 105c is formed.

[0102]

After that, the resist mask 140 is removed.

[0103]

5

10

15

Then, heat treatment is performed in an atmosphere containing an oxidizing gas to reduce oxygen vacancies in the oxide layer 105a, the oxide semiconductor layer 106, the oxide layer 105b, and the oxide layer to be the oxide layer 105c. An oxygen vacancy is likely to occur particularly in the oxide layer to be the oxide layer 105c, because the oxide layer is formed using the reaction product at the time of etching. In such a manner, the oxide layer to be the oxide layer 105c becomes the oxide layer 105c with an extremely low carrier density by the above-described ashing treatment and the heat treatment (see FIG. 12C). Note that the oxidizing gas refers to a gas of oxygen, nitrous nitrogen, ozone, or the like. The heat treatment is performed at a temperature higher than or equal to 250 °C and lower than or equal to 650 °C, preferably higher than or equal to 300 °C and lower than or equal to 500 °C. The heat treatment is performed in an atmosphere containing an oxidizing gas at 10 ppm or more, 1 % or more, or 10 % or more. Alternatively, the heat treatment may be performed in such a manner that heat treatment is performed in an inert gas atmosphere, and then another heat treatment is performed in an atmosphere containing an oxidizing gas at 10 ppm or more, 1 % or more, or 10 % or more in order to compensate desorbed oxygen. [0104]

In the above manner, the multilayer film 108 which includes the oxide layer 105c having a curved surface can be formed. This means that a photomask or the like only for forming the oxide layer 105c is unnecessary to form the multilayer film 108 which includes the oxide layer 105c having a curved surface.

[0105]

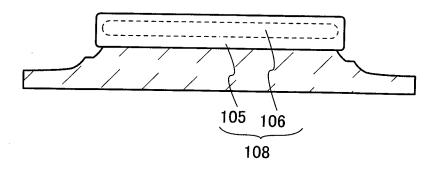

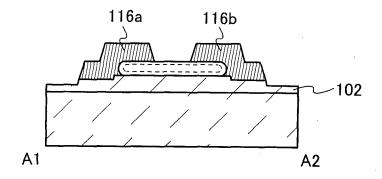

The oxide layer 105a, the oxide layer 105b, and the oxide layer 105c formed in the above manner cannot be clearly distinguished from each other in some cases. Thus, the oxide layer 105a, the oxide layer 105b, and the oxide layer 105c can be collectively called an oxide layer 105. As illustrated in FIG. 13A, the oxide semiconductor layer 106 and the oxide layer 105 which surrounds the oxide semiconductor layer 106 can be collectively called the multilayer film 108.

30 [0106]

25

Next, the base insulating film 133 may be etched so that a base insulating film

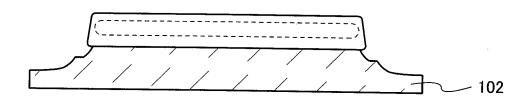

102 having a plurality of steps (two steps here) is formed (see FIG. 13B). When the base insulating film 102 has two steps, the base insulating film 102 has three regions with different thicknesses.

[0107]

5 <2-1-4. Formation Mechanism (2)>

An example of the formation mechanism of the multilayer film 108 which includes the oxide layer 105c having a curved surface is described with reference to FIGS. 14A to 14C and FIGS. 15A to 15C.

[0108]

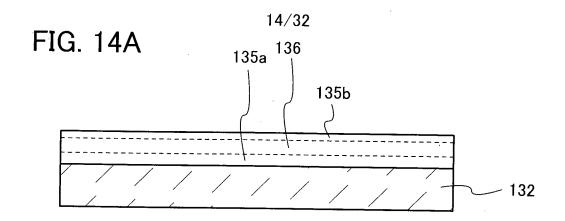

First, a multilayer film including an oxide layer 135a provided over a base insulating film 132, an oxide semiconductor layer 136 provided over the oxide layer 135a, and an oxide layer 135b provided over the oxide semiconductor layer 136 is prepared (see FIG. 14A).

[0109]

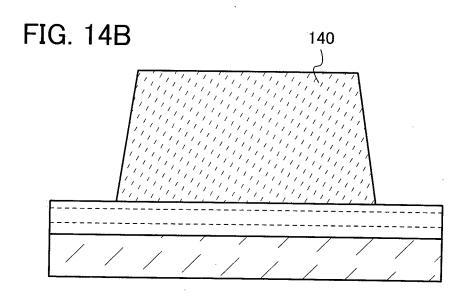

Next, a resist mask 140 is formed over part of the oxide layer 135b (see FIG. 14B).

[0110]

20

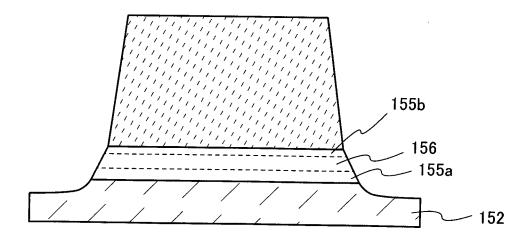

Then, the oxide layer 135b, the oxide semiconductor layer 136, and the oxide layer 135a in a region where the resist mask 140 is not provided are etched by a dry etching method to be an oxide layer 155b, an oxide semiconductor layer 156, and an oxide layer 155a, respectively. At this time, the base insulating film 132 is partly etched to be a base insulating film 152 (see FIG. 14C). Note that the oxide layer 155b, the oxide semiconductor layer 156, and the oxide layer 155a have taper angles.

After that, the oxide layer 155b, the oxide semiconductor layer 156, and the oxide layer 155a are etched by a dry etching method to be the oxide layer 105b, the oxide semiconductor layer 106, and the oxide layer 105a, respectively. At this time, a reaction product of the oxide layer 155a is attached to a side surface of the multilayer film to form an oxide layer to be the oxide layer 105c serving as a sidewall protective film (also referred to as a rabbit ear). Note that the reaction product of the oxide layer 155a is attached by a sputtering phenomenon or through plasma at the time of the dry etching. At this time, the base insulating film 152 is partly etched and becomes the

base insulating film 102 (see FIG. 15A).

[0112]

Note that since the oxide layer to be the oxide layer 105c is formed using the reaction product of the oxide layer 155a, constituent of the etching gas used at the time of etching (e.g., chlorine and boron) remains therein.

[0113]

5

15

20

25

30

Next, the constituent of the etching gas remaining in the oxide layer to be the oxide layer 105c is removed by ashing treatment.

[0114]

After that, the resist mask 140 is removed.

[0115]

Then, heat treatment is preferably performed in an atmosphere containing an oxidizing gas to reduce oxygen vacancies in the oxide layer 105a, the oxide semiconductor layer 106, the oxide layer 105b, and the oxide layer to be the oxide layer 105c. An oxygen vacancy is likely to occur particularly in the oxide layer to be the oxide layer 105c, because the oxide layer is formed using the reaction product at the time of etching. In such a manner, the oxide layer to be the oxide layer 105c becomes the oxide layer 105c with an extremely low carrier density by the above-described ashing treatment and the heat treatment (see FIG. 15B). Note that the oxidizing gas refers to a gas of oxygen, nitrous nitrogen, ozone, or the like.

[0116]

In the above manner, the multilayer film 108 which includes the oxide layer 105c having a curved surface can be formed. This means that a photomask or the like only for forming the oxide layer 105c is unnecessary to form the multilayer film 108 which includes the oxide layer 105c having a curved surface.

[0117]

As described above, the oxide layer 105c is formed using the reaction product of the oxide layer 155a which becomes the oxide layer 105a. Thus, the oxide layer 105c might have composition and physical properties different from those of the oxide layer 105a because of its formation process. Note that the oxide layer 105a and the oxide layer 105c cannot be distinguished from each other by analysis or the like, in some cases. In that case, the oxide layer 105c has physical properties similar to those

5

of the oxide layer 105a and if there is no description of the physical properties of the oxide layer 105c, the description of the oxide layer 105a can be referred to. Further, when the oxide layer 105b has a structure similar to that of the oxide layer 105a, the oxide layer 105b cannot be distinguished from the oxide layer 105c in some cases. Thus, the oxide layer 105a, the oxide layer 105b, and the oxide layer 105c can be collectively called an oxide layer 105. As illustrated in FIG. 15C, the oxide semiconductor layer 106 and the oxide layer 105 which surrounds the oxide semiconductor layer 106 can be collectively called the multilayer film 108.

The multilayer film 108 has a structure in which the oxide semiconductor layer 106 is surrounded (or wrapped or covered) by the oxide layer 105a, the oxide layer 105b, and the oxide layer 105c. Thus, entry of impurities to the oxide semiconductor layer 106 can be reduced. Further, since there is no level between the oxide semiconductor layer 106 and another oxide layer, the carrier mobility (electron mobility) of the oxide semiconductor layer 106 can be increased.

[0119]

<2-2. Physical Properties of Multilayer Film>

In this section, the physical properties of the multilayer film will be described. [0120]

20 <2-2-1. Composition of Multilayer Film>

The compositions of the multilayer film 108, and the oxide layer 105a, the oxide semiconductor layer 106, the oxide layer 105b, and the oxide layer 105c included in the multilayer film 108 will be described below.

[0121]

The oxide semiconductor layer 106 contains at least indium. In addition to indium, an element *M* (aluminum, titanium, silicon, gallium, germanium, yttrium, zirconium, tin, lanthanum, cerium, or hafnium) is preferably contained. It is preferable that the oxide semiconductor layer 106 contain at least indium because carrier mobility (electron mobility) can be increased.

30 [0122]

The oxide layer 105a contains one or more elements which are not oxygen and are contained in the oxide semiconductor layer 106. For that reason, interface

scattering is unlikely to occur at the interface between the oxide semiconductor layer 106 and the oxide layer 105a. Thus, the transistor can have high field-effect mobility because the movement of carriers is not hindered at the interface.

[0123]

5

The oxide layer 105a may contain, for example, aluminum, titanium, silicon, gallium, germanium, yttrium, zirconium, tin, lanthanum, cerium, or hafnium at a higher atomic ratio than indium. Specifically, the amount of any of the above elements in the oxide layer 105a in an atomic ratio is 1.5 times or more, preferably 2 times or more, more preferably 3 times or more as much as that of indium in an atomic ratio. Any of the above elements strongly bonds with oxygen and thus has a function of suppressing generation of an oxygen vacancy in the oxide layer. That is, an oxygen vacancy is less likely to occur in the oxide layer 105a. Further, the oxide layer 105a contains any of the above elements at a higher atomic ratio than the oxide semiconductor layer 106.

15

20

10

The oxide layer 105b contains one or more elements which are not oxygen and are contained in the oxide semiconductor layer 106. Since the oxide layer 105b includes one or more elements other than oxygen included in the oxide semiconductor layer 106, an interface state is unlikely to be formed at the interface between the oxide semiconductor layer 106 and the oxide layer 105b. When the interface has an interface level, in some cases, a second transistor in which the interface serves as a channel and which has a different threshold voltage is formed; accordingly, the apparent threshold voltage of the transistor is changed. Thus, with the oxide layer 105b, fluctuation in the electric characteristics of the transistors, such as a threshold voltage, can be reduced. [0125]

25

30

The oxide layer 105b may contain, for example, aluminum, titanium, silicon, gallium, germanium, yttrium, zirconium, tin, lanthanum, cerium, or hafnium at a higher atomic ratio than indium. Specifically, the amount of any of the above elements in the oxide layer 105b in an atomic ratio is 1.5 times or more, preferably 2 times or more, more preferably 3 times or more as much as that of indium in an atomic ratio. Any of the above elements strongly bonds with oxygen and thus has a function of suppressing generation of an oxygen vacancy in the oxide layer. That is, an oxygen vacancy is less likely to occur in the oxide layer 105b. Further, the oxide layer 105b contains any of

the above elements at a higher atomic ratio than the oxide semiconductor layer 106. [0126]

The description of the oxide layer 105a can be referred to for the oxide layer 105c. The oxide layer 105c is formed as the side surface of the multilayer film 108. When an oxygen vacancy occurs in the oxide layer 105c, a second transistor in which an interface between the oxide layer 105c and the oxide semiconductor layer 106 serves as a channel and which has a different threshold voltage is formed at the interface; accordingly, the apparent threshold voltage of the transistor is changed. Thus, with the oxide layer 105c in which an oxygen vacancy is less likely to occur, fluctuation in the electric characteristics of the transistors, such as a threshold voltage, can be reduced. The variation in the electric characteristics of the second transistor becomes noticeable, as a channel length of a transistor is smaller. This indicates that a smaller transistor has a stronger effect with the oxide layer 105c in which an oxygen vacancy is less likely to occur.

# 15 [0127]

5

10

When indium contained in the oxide layer 105b is diffused outward, the electric characteristics of the transistor might deteriorate; thus, the oxide layer 105b preferably contains indium at a lower atomic ratio than the oxide semiconductor layer 106.

# 20 [0128]

25

30

It is preferable that the oxide layer 105a and the oxide layer 105c be each an oxide layer in which an oxygen vacancy is less likely to occur than in the oxide layer 105b. It is further preferable that the oxide layer 105a and the oxide layer 105c be each an oxide layer having a higher insulating property than the oxide layer 105b. To obtain the oxide layer 105a and the oxide layer 105c in which an oxygen vacancy occurs less frequently than in the oxide layer 105b and the insulating property is higher than that of the oxide layer 105b, the oxide layer 105a and the oxide layer 105c preferably contain an element which reduces occurrence of an oxygen vacancy in the oxide layer or a metal element which strongly bonds with oxygen at a higher concentration than the oxide layer 105b.

[0129]

When an In-M-Zn oxide is used for the oxide layer 105a, the atomic ratio

5

10

15

20

25

30

between In and M is preferably as follows: the atomic percentage of In is less than 50 atomic% and the atomic percentage of M is greater than or equal to 50 atomic%; further preferably, the atomic percentage of In is less than 25 atomic% and the atomic percentage of M is greater than or equal to 75 atomic%. When an In-M-Zn oxide is used for the oxide semiconductor layer 106, the atomic ratio between In and M is preferably as follows: the atomic percentage of In is greater than or equal to 25 atomic% and the atomic percentage of M is less than 75 atomic%; further preferably, the atomic percentage of In is greater than or equal to 34 atomic% and the atomic percentage of Mis less than 66 atomic%. When an In-M-Zn oxide is used for the oxide layer 105b, the atomic ratio between In and M is preferably as follows: the atomic percentage of In is less than 50 atomic% and the atomic percentage of M is greater than or equal to 50 atomic%; further preferably, the atomic percentage of In is less than 25 atomic% and the atomic percentage of M is greater than or equal to 75 atomic%. When an In-M-Zn oxide is used for the oxide layer 105c, the atomic ratio between In and M is preferably as follows: the atomic percentage of In is less than 50 atomic% and the atomic percentage of M is greater than or equal to 50 atomic%; further preferably, the atomic percentage of In is less than 25 atomic% and the atomic percentage of M is greater than or equal to 75 atomic%.

[0130]

The thickness of the oxide layer 105a is greater than or equal to 3 nm and less than or equal to 100 nm, preferably greater than or equal to 3 nm and less than or equal to 50 nm. The thickness of the oxide semiconductor layer 106 is greater than or equal to 3 nm and less than or equal to 200 nm, preferably greater than or equal to 3 nm and less than or equal to 100 nm, more preferably greater than or equal to 3 nm and less than or equal to 50 nm. The thickness of the oxide layer 105b is greater than or equal to 3 nm and less than or equal to 50 nm, preferably greater than or equal to 3 nm and less than or equal to 20 nm. The thicknesses of the oxide layer 105a and the oxide layer 105c are preferably larger than the thickness of the oxide layer 105b. In other words, the thickness of the oxide layer 105b is preferably smaller than the thicknesses of the oxide layer 105a and the oxide layer 105c.

[0131]

In the case where the oxide layer 105a and the oxide layer 105b are formed by a sputtering method, a target containing indium is preferably used in order not to increase the number of particles. Moreover, it is preferable to use an oxide target in which the proportion of gallium is relatively small. Particularly in the case where a target containing indium is used, the conductivity of the target can be increased and DC discharge and AC discharge are facilitated; thus, deposition over a large substrate can be easily performed. Thus, semiconductor devices can be manufactured with improved productivity.

[0132]

5

10 <2-2-2. Band Structure of Multilayer Film>

First of all, a band structure of the multilayer film including the oxide semiconductor layer will be described.

[0133]

15

20

25

30

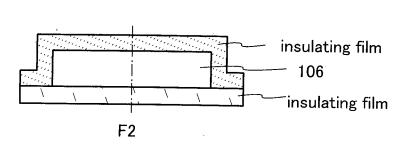

FIG. 16A is a cross-sectional view of the case of using a single layer of the oxide semiconductor layer 106, which is shown as a comparative example. FIG. 16B shows a band structure along dashed-dotted line F1-F2 in FIG. 16A. The lowest conduction band energy of the oxide semiconductor layer 106 is denoted by "EcS". Note that FIGS. 16A and 16B show the case where an insulating film (e.g., a silicon oxide film) which has an energy gap sufficiently wider than that of the oxide semiconductor layer 106 and has the lowest conduction band energy sufficiently higher than that of the oxide semiconductor layer 106 is provided over and below the oxide semiconductor layer 106.

[0134]

According to FIG. 16B, in the case of using a single layer of the oxide semiconductor layer 106, the lowest conduction band energy is probably changed discontinuously (discontinuous connection) between the oxide semiconductor layer 106 and the insulating films. This is because the insulating film has an energy gap sufficiently wider than that of the oxide semiconductor layer 106 and has the lowest conduction band energy sufficiently higher than that of the oxide semiconductor layer 106, that is, the insulating film has physical properties completely different from those of the oxide semiconductor layer 106.

[0135]

This suggests that a number of DOS exist at an interface between the oxide semiconductor layer 106 and the insulating film. The DOS which exists at the interface between the oxide semiconductor layer 106 and the insulating film (corresponding to a gate insulating film or a protective insulating film) in a transistor including a single layer of the oxide semiconductor layer 106 causes deterioration of the transistor in some cases.

[0136]

5

10

15

FIG. 17A is a cross-sectional view of the multilayer film 108. FIG. 17B shows a band structure along dashed-dotted line G1-G2 in FIG. 17A and FIG. 17C shows a band structure along dashed-dotted line G3-G4 in FIG. 17A. The lowest conduction band energy of the oxide layer 105a is denoted by "EcO1", the lowest conduction band energy of the oxide layer 105b is denoted by "EcO2", and the lowest conduction band energy of the oxide layer 105c is "EcO3". Note that FIGS. 17A to 17C show the case of providing insulating films (e.g., silicon oxide films) which surround the multilayer film 108 and each of which has an energy gap sufficiently wider than that of any layer in the multilayer film 108, and has the lowest conduction band energy sufficiently higher than that of any layer in the multilayer film 108.

The oxide layer 105a, the oxide semiconductor layer 106, the oxide layer 105b, and the oxide layer 105c are selected so that the relation expressed by Formula (2) is satisfied when the lowest conduction band energies of the oxide layer 105a, the oxide semiconductor layer 106, the oxide layer 105b, and the oxide layer 105c are EcS1, EcS2, EcS3, and EcS4, respectively.

[0138]

25 [Formula 2]

$EcS1 = EcS4 \ge EcS3 > EcS2$

[0139]

30

According to FIG. 17B, in the multilayer film 108, the lowest conduction band energy is probably changed continuously (continuous connection) between the oxide layers 105a and 105b and the oxide semiconductor layer 106. This is because the oxide layer 105a and the oxide layer 105b have physical properties similar to those of the oxide semiconductor layer 106.

[0140]

This suggests that DOS scarcely exists at interfaces between the oxide semiconductor layer 106 and the oxide layers 105a and 105b. Since the oxide layer 105a and the oxide layer 105b are oxide layers in which an oxygen vacancy is less likely to occur as described above, DOS which is probably due to an oxygen vacancy scarcely exists.

[0141]

5

10

15

20

Note that for each of the oxide layer 105a, the oxide layer 105b, the oxide layer 105c, and the oxide semiconductor layer 106, the difference (also referred to as the electron affinity) between the lowest conduction band energy and the vacuum energy can be obtained by subtracting an energy gap from the difference (also referred to as an ionization potential) between the vacuum energy and the highest valence band energy. [0142]

The energy gaps can be measured using a spectroscopic ellipsometer (UT-300 manufactured by HORIBA JOBIN YVON SAS.). The ionization potential can be measured using an ultraviolet photoelectron spectroscopy (UPS) apparatus (VersaProbe manufactured by Physical Electronics, Inc.).

[0143]

According to FIGS. 17B and 17C, the oxide semiconductor layer 106 of the multilayer film 108 serves as a well and a channel of the transistor including the multilayer film 108 is formed in the oxide semiconductor layer 106. Note that since the lowest conduction band energy of the multilayer film 108 is continuously changed, the oxide semiconductor layer 106 and the oxide layer 105b can be regarded as being continuously connected.

25 [0144]

Then, diffusion of oxygen in the multilayer film 108 through heat treatment at  $300\,^{\circ}\text{C}$  or  $450\,^{\circ}\text{C}$  will be described with reference to FIGS. 18A to 18C. [0145]

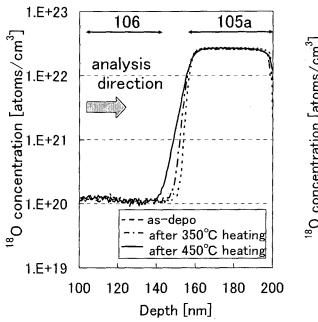

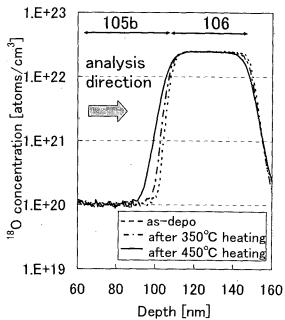

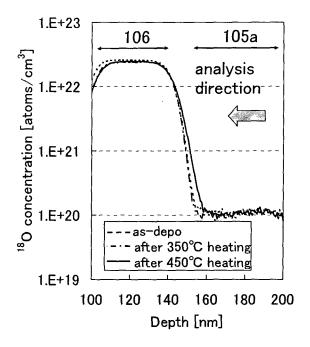

FIGS. 18A to 18C each show SIMS measurement results of concentration distribution of <sup>18</sup>O in a depth direction in samples in which any of the layers of the multilayer film 108 is formed using an <sup>18</sup>O<sub>2</sub> gas.

[0146]

Here, the oxide layer 105a is an oxide layer formed by a sputtering method using an In-Ga-Zn oxide (the atomic ratio of In to Ga and Zn is 1:1:1) target.

[0147]

The oxide semiconductor layer 106 is an oxide semiconductor layer formed by a sputtering method using an In-Ga-Zn oxide (the atomic ratio of In to Ga and Zn is 3:1:2) target.

[0148]

The oxide layer 105b is an oxide layer formed by a sputtering method using an In-Ga-Zn oxide (the atomic ratio of In to Ga and Zn is 1:1:1) target.

10 [0149]

5

Here, FIG. 18A shows <sup>18</sup>O concentration distributions in a depth direction of the oxide layer 105a, the oxide semiconductor layer 106, and the interface therebetween of samples in each of which an <sup>18</sup>O<sub>2</sub> gas is used for forming the oxide layer 105a but an <sup>18</sup>O<sub>2</sub> gas is not used for forming the other layers. The SIMS measurement results show as follows: <sup>18</sup>O is more diffused from the oxide layer 105a to the oxide semiconductor layer 106 in a sample subjected to the heat treatment at 350 °C (shown as "after heat treatment at 350 °C" with a dashed-dotted line) and a sample subjected to the heat treatment at 450 °C (shown as "after heat treatment at 450 °C (shown as "after heat treatment at 450 °C" with a solid line) than in a sample not subjected to heat treatment (shown as "as-depo" with a dotted line).

20 [0150]

25

30

15

FIG. 18B shows <sup>18</sup>O concentration distributions in a depth direction of the oxide semiconductor layer 106, the oxide layer 105b, and the interface therebetween of samples in each of which an <sup>18</sup>O<sub>2</sub> gas is used for forming oxide semiconductor layer 106 but an <sup>18</sup>O<sub>2</sub> gas is not used for forming the other layers. The SIMS measurement results show as follows: <sup>18</sup>O is more diffused from the oxide semiconductor layer 106 to the oxide layer 105b in a sample subjected to the heat treatment at 350 °C (shown as "after heat treatment at 350 °C" with a dashed-dotted line) and a sample subjected to the heat treatment at 450 °C" with a solid line) than in a sample not subjected to heat treatment (shown as "as-depo" with a dotted line).

FIG. 18C shows <sup>18</sup>O concentration distributions in a depth direction of the

oxide layer 105a, the oxide semiconductor layer 106, and the interface therebetween of samples in each of which an <sup>18</sup>O<sub>2</sub> gas is used for forming the oxide semiconductor layer 106 but an <sup>18</sup>O<sub>2</sub> gas is not used for forming the other layers. The SIMS measurement results show as follows: <sup>18</sup>O is more diffused from the oxide semiconductor layer 106 to the oxide layer 105a in a sample subjected to the heat treatment at 350 °C (shown as "after heat treatment at 350 °C" with a dashed-dotted line) than in a sample subjected to the heat treatment at 450 °C" with a solid line) and a sample not subjected to heat treatment (shown as "as-depo" with a dotted line). [0152]

As shown in FIGS. 18A to 18C, in the multilayer film 108, oxygen is diffused from one layer to the other layer. This means that at an interface between any two of the oxide layer 105a, the oxide semiconductor layer 106, the oxide layer 105b, and the oxide layer 105c, a layer in which constituent elements of the two layers are mixed (also referred to as a mixed layer) is formed and the two layers are continuously connected.

Note that the mixed layer has an intermediate property between the table.

Note that the mixed layer has an intermediate property between the two layers.

[0153]

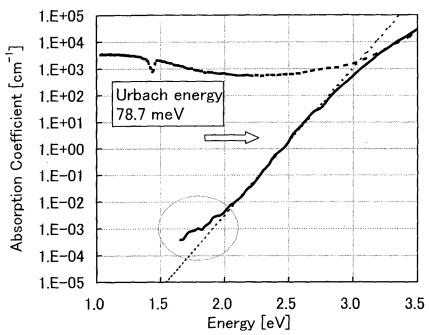

5

Next, DOS in the multilayer film 108 was measured by CPM. [0154]

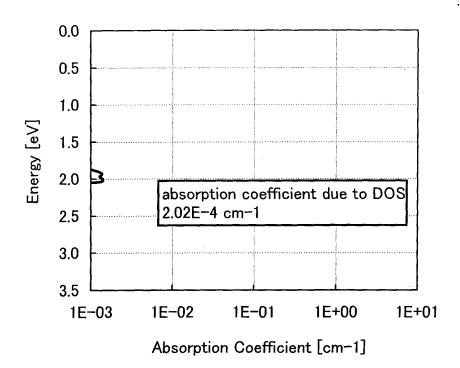

In order that the transistor may have high field-effect mobility and stable electric characteristics, the absorption coefficient due to the localized states of the multilayer film 108 measured by CPM is preferably lower than  $1 \times 10^{-3}$  cm<sup>-1</sup>, more preferably lower than  $3 \times 10^{-4}$  cm<sup>-1</sup>.

[0155]

20

A sample on which CPM measurement was performed will be described below. 25 [0156]

The oxide layer 105a is an oxide layer formed by a sputtering method using an In-Ga-Zn oxide (the atomic ratio of In to Ga and Zn is 1:3:2) target. Note that an argon gas at a flow rate of 30 sccm and an oxygen gas at a flow rate of 15 sccm were used as a deposition gas, the pressure was 0.4 Pa, the substrate temperature was 200 °C, and a DC power of 0.5 kW was applied.

[0157]

30

The oxide semiconductor layer 106 is an oxide semiconductor layer formed by a sputtering method using an In-Ga-Zn oxide (the atomic ratio of In to Ga and Zn is 1:1:1) target. Note that an argon gas at a flow rate of 30 sccm and an oxygen gas at a flow rate of 15 sccm were used as a deposition gas, the pressure was 0.4 Pa, the substrate temperature was 200 °C, and a DC power of 0.5 kW was applied.

[0158]

[0159]

5

10

15

20

25

The oxide layer 105b is an oxide layer formed by a sputtering method using an In-Ga-Zn oxide (the atomic ratio of In to Ga and Zn is 1:3:2) target. Note that an argon gas at a flow rate of 30 sccm and an oxygen gas at a flow rate of 15 sccm were used as a deposition gas, the pressure was 0.4 Pa, the substrate temperature was 200 °C, and a DC power of 0.5 kW was applied.

Here, in order to improve the accuracy of the CPM measurement, the multilayer film 108 needs to have a certain thickness. Specifically, the thicknesses of the oxide layer 105a, the oxide semiconductor layer 106, and the oxide layer 105b which are included in the multilayer film 108 were set at 30 nm, 100 nm, and 30 nm, respectively.

[0160]

In the CPM measurement, the amount of light with which a surface of the sample between terminals is irradiated is adjusted so that a photocurrent value is kept constant in the state where voltage is applied between a first electrode and a second electrode provided in contact with the multilayer film 108 that is the sample, and then an absorption coefficient is derived from the amount of the irradiation light at each wavelength. In the CPM measurement, when the sample has a defect, the absorption coefficient of energy which corresponds to a level at which the defect exists (calculated from a wavelength) is increased. The increase in the absorption coefficient is multiplied by a constant, whereby the defect density of the sample can be obtained.

FIG. 19A shows results of fitting the absorption coefficient (dotted line)

30 measured using a spectrophotometer and the absorption coefficient (solid line)

measured by CPM in the range of energy higher than or equal to the energy gap of each

WO 2014/065301 PCT/JP2013/078634

layer in the multilayer film 108. Note that the Urbach energy obtained based on the absorption coefficient measured by CPM was 78.7 meV. The integral value of the absorption coefficient in the energy range was derived in such a manner that a background (thin dotted line) was subtracted from the absorption coefficient measured by CPM in the energy range shown with a dashed-line circle in FIG. 19A (see FIG. 19B). As a result, the absorption coefficient due to DOS of this sample was found to be  $2.02 \times 10^{-4}$  cm<sup>-1</sup>.

[0162]

5

10

15

20

25

This indicates that an extremely small number of DOS is in the multilayer film 108. That is, the transistor including the multilayer film 108 has high field-effect mobility and stable electric characteristics.

[0163]

<2-2-3. Impurities in Multilayer Film>

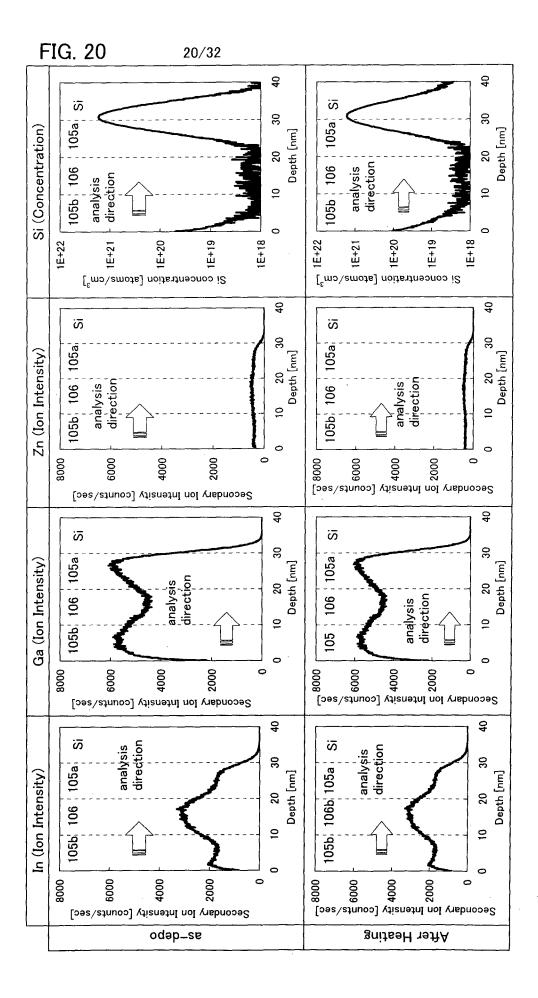

The concentrations of silicon in the layers included in the multilayer film 108 will be described below with reference to FIG. 20.

[0164]