# (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2005-274868 (P2005-274868A)

(43) 公開日 平成17年10月6日(2005.10.6)

| (51) Int.C1. <sup>7</sup> |       | F 1                        |                 |            |      | テーマ   | コード (    |         |

|---------------------------|-------|----------------------------|-----------------|------------|------|-------|----------|---------|

| G09G                      | 3/36  | GO9G                       | 3/36            |            |      | 2H0   | 93       |         |

| G02F                      | 1/133 | GO2F                       | 1/133           | 505        |      | 5 C O | 06       |         |

| GO9G                      | 3/20  | GO2F                       | 1/133           | 550        |      | 5CO8O |          |         |

|                           |       | GO9G                       | 3/20            | 611A       |      |       |          |         |

|                           |       | GO9G                       | 3/20            | 623B       |      |       |          |         |

|                           |       | 審査請求 未                     | 請求 請求           | マ項の数 12    | OL   | (全 12 | 頁) 最     | 終頁に続く   |

| (21) 出願番号                 |       | 特願2004-86728 (P2004-86728) | (71) 出願         | 人 0000014  | 43   |       |          |         |

| (22) 出願日                  |       | 平成16年3月24日 (2004.3.24)     | カシオ計算機株式会社      |            |      |       |          |         |

|                           |       |                            | 東京都渋谷区本町1丁目6番2号 |            |      |       |          |         |

|                           |       |                            | (74)代理          |            |      |       |          |         |

|                           |       |                            |                 | 弁理士        | 荒船   | 博司    |          |         |

|                           |       |                            | (74)代理          |            |      |       |          |         |

|                           |       |                            |                 | 弁理士        |      | 良男    |          |         |

|                           |       |                            | (72) 発明:        |            | -    |       |          |         |

|                           |       |                            |                 |            |      |       |          | 地 5 カ   |

|                           |       |                            |                 |            |      |       |          | ンター内    |

|                           |       |                            | F <i>タ</i> ーム   | (参考) 2H093 |      |       | NC10 NC  |         |

|                           |       |                            |                 |            | NC21 |       | NC35 NC4 |         |

|                           |       |                            |                 |            | NC65 | ND12  | ND48 ND  | 58 ND60 |

|                           |       |                            |                 |            | NH12 |       |          |         |

|                           |       |                            |                 |            |      |       | 最終頁      | に続く     |

(54) 【発明の名称】液晶表示装置及び液晶表示装置の駆動方法

# (57)【要約】

【課題】 液晶表示装置をパワーセーブ状態に設定する際に、表示画面の残像を迅速に消去することができるとともに、残留電圧による焼き付きの発生や液晶の劣化を抑制することができる液晶表示装置及びその駆動方法を提供すること。

【解決手段】 互いに直交する複数の走査ラインと複数の信号ラインとの交点近傍に表示画素を形成するアクティブマトリクス型の液晶表示パネル10を備えた液晶表示装置1において、信号ドライバ80は、パワーセーブ制御信号Psavがローレベルの場合に、反転アンプ50から入力される輝度信号に対応する表示信号電圧を液晶表示パネル10の各信号ラインに供給し、パワーセーブ制御信号Psavがハイレベルの場合には、所定の低信号レベルを有する電圧V1を液晶表示パネル10の各信号ラインに供給する。

【選択図】図1

#### 【特許請求の範囲】

# 【請求項1】

複数の走査ライン及び複数の信号ラインと、前記複数の走査ラインと複数の信号ラインとの各交点近傍にマトリクス状に配列された複数の画素電極と、各画素電極に対向する共通電極と、前記画素電極と前記共通電極間に充填された液晶と、を有する液晶表示パネルを備え、前記複数の信号ラインに所定の映像信号に基づく表示信号電圧を印加し、前記共通電極に所定のコモン電圧を印加して、当該液晶表示パネルを駆動する液晶表示装置であって、

前記液晶表示装置をパワーセーブ状態に設定するためのパワーセーブ制御信号の入力手段と、前記入力手段にパワーセーブ制御信号が入力された場合に、少なくとも、前記信号ラインを介して前記画素電極に所定の低信号レベルを有する第1の信号電圧を固定的に印加するように制御する手段と、を有するパワーセーブ状態制御手段を備えることを特徴とする液晶表示装置。

## 【請求項2】

前記液晶表示装置は、前記複数の信号ラインに前記表示信号電圧を印加する信号駆動手段を備え、

前記パワーセーブ状態制御手段は、少なくとも、前記信号駆動手段における前記表示信号電圧を前記信号ラインに出力するバッファ回路部に設けられ、前記パワーセーブ制御信号及び前記第1の信号電圧が接続され、前記パワーセーブ制御信号が入力されたとき前記第1の信号電圧を前記信号ラインに供給するように切り替えるスイッチ手段からなることを特徴とする請求項1に記載の液晶表示装置。

# 【請求項3】

前記パワーセーブ状態制御手段は、さらに、前記入力手段に前記パワーセーブ制御信号が入力された場合に、前記共通電極に所定の低信号レベルを有する第2の信号電圧を固定的に印加するように制御する制御手段を備えることを特徴とする請求項1または2に記載の液晶表示装置。

# 【請求項4】

前記液晶表示装置は、前記コモン電圧を生成して前記共通電極に印加する共通電極駆動手段と、所定の周期で反転制御される極性反転制御信号に応じて前記共通電極駆動手段により生成される前記コモン電圧の極性を制御する手段と、を備え、

前記パワーセーブ状態制御手段は、前記パワーセーブ制御信号が入力された場合に、前記極性反転制御信号を所定の低信号レベルに固定的に設定し、これにより前記コモン電圧を前記第2の信号電圧に設定する手段を備えることを特徴とする請求項3に記載の液晶表示装置。

# 【請求項5】

前記第1の信号電圧および前記第2の信号電圧は、同一の電位を有することを特徴とする請求項3に記載の液晶表示装置。

## 【請求項6】

前記第1の信号電圧および前記第2の信号電圧は、接地電位を有することを特徴とする請求項3に記載の液晶表示装置。

# 【請求項7】

前記第1の信号電圧および前記第2の信号電圧は、該第1の信号電圧と該第2の信号電圧との電位差が、前記液晶表示パネルの前記液晶の閾値電圧より小さい値となる電圧であることを特徴とする請求項3に記載の液晶表示装置。

#### 【請求項8】

複数の走査ライン及び複数の信号ラインと、前記複数の走査ラインと複数の信号ラインとの各交点近傍にマトリクス状に配列された複数の画素電極と、各画素電極に対向する共通電極と、前記画素電極と前記共通電極間に充填された液晶と、を有する液晶表示パネルを備え、前記複数の信号ラインに所定の映像信号に基づく表示信号電圧を印加し、前記共通電極に所定のコモン電圧を印加して、当該液晶表示パネルを駆動する液晶表示装置の駆

20

10

30

40

動方法であって、

前記液晶表示装置をパワーセーブ状態に設定する際に、パワーセーブ制御信号を該液晶表示装置に入力し、

入力された前記パワーセーブ制御信号に応じて、前記信号ラインを介して前記画素電極に所定の低信号レベルを有する第 1 の信号電圧を固定的に印加することを特徴とする液晶表示装置の駆動方法。

# 【請求項9】

入力された前記パワーセーブ制御信号に応じて、さらに、前記共通電極に所定の信号レベルを有する第 2 の信号電圧を印加することを特徴とする請求項 8 に記載の液晶表示装置の駆動方法。

【請求項10】

前記第1の信号電圧および前記第2の信号電圧は、同一の電位を有することを特徴とする請求項9に記載の液晶表示装置の駆動方法。

【請求項11】

前記第1の信号電圧および前記第2の信号電圧は、接地電位を有することを特徴とする請求項9に記載の液晶表示装置の駆動方法。

【請求項12】

前記第1の信号電圧および前記第2の信号電圧は、該第1の信号電圧と該第2の信号電圧との電位差が、前記液晶表示パネルの前記液晶の閾値電圧より小さい値となる電圧であることを特徴とする請求項9に記載の液晶表示装置の駆動方法。

【発明の詳細な説明】

【技術分野】

[0001]

本発明は、マトリクス状に表示画素が形成された液晶表示パネルを駆動する液晶表示装置及びその駆動方法に関する。

【背景技術】

[0002]

従来から、互いに直交する複数の走査ラインと複数の信号ラインとの交点近傍に表示画素を形成するアクティブマトリクス型の液晶表示パネルを備えた液晶表示装置が知られている。

[0003]

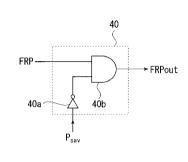

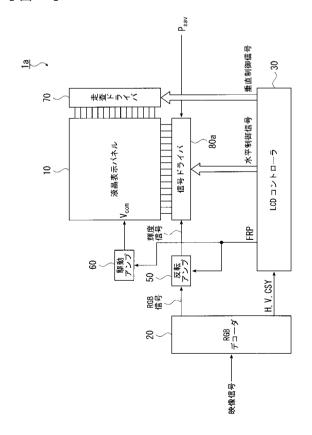

図4は、従来技術における液晶表示装置の概略構成の一例を示すブロック図であり、図5は、従来技術における液晶表示パネルの回路構成の一例を示す図である。図4に示すように、液晶表示装置1aは、液晶表示パネル10と、RGBデコーダ20と、LCDコントローラ30と、反転アンプ50と、駆動アンプ60と、走査ドライバ70と、信号ドライバ80aと、を備えて構成されている。

[0004]

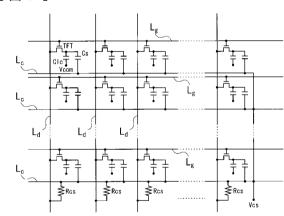

液晶表示パネル10は、図5に示すように、行方向に配設された走査ライン(ゲートライン)Lg及び列方向に配設された信号ライン(ソースライン)Ldと、各走査ラインLgと各信号ラインLdとの交点近傍に配置された画素電極と、各画素電極と対向して配置され、コモン電圧Vcomが印加される共通電極と、画素電極と共通電極との間に充填、保持された液晶からなる液晶容量(画素容量)C1cと、液晶容量C1cに印加された信号電圧を保持するための蓄積容量(補助容量)Csと、走査ラインLgと平行して配設され、所定電圧Vcs(例えば、コモン電圧Vcom)が印加される容量配線Lcと、ゲートが走査ラインLgに、ソースが信号ラインLdに、ドレインが液晶容量C1cに、それぞれ接続された薄膜トランジスタTFTと、及び容量配線Lc(所定電圧Vcs)と各信号ラインLdとの間に接続された静電保護抵抗Rcsと、を備えて構成されている。

[0005]

R G B デコーダ 2 0 は、液晶表示装置 1 a の外部から供給される映像信号(コンポジットビデオ信号)から、水平同期信号 H 、垂直同期信号 V 及びコンポジット同期信号 C S Y

10

20

30

40

20

30

40

50

を抽出してLCDコントローラ30に出力するとともに、映像信号に含まれるRGBの各色信号(RGB信号)を抽出し、反転アンプ50に出力する。

### [0006]

LCDコントローラ30は、RGBデコーダ20から入力される水平同期信号 H、垂直同期信号 V、及びコンポジット同期信号 CSYに基づいて、液晶表示パネル10に映像信号に基づく所定の画像情報を表示させるための制御を行う。具体的には、LCDコントローラ30は、極性反転信号 FRPを生成して反転アンプ50及び駆動アンプ60に出力するとともに、水平制御信号(信号ラインアウトプットイネーブル信号、クリア信号等)及び垂直制御信号(ゲートスタート信号、ゲートクロック、ゲートラインアウトプットイネーブル信号等)を生成し、生成した水平制御信号を信号ドライバ80aに、垂直制御信号を走査ドライバ70に、それぞれ出力する。

#### [0007]

反転アンプ50は、LCDコントローラ30から出力される極性反転信号FRPが入力され、極性反転信号FRPに基づいて、RGBデコーダ20から入力されるRGB信号の極性を例えば水平走査期間毎に周期的に反転させてRGB反転信号(輝度信号)を生成し、信号ドライバ80aに出力する。

駆動アンプ60は、LCDコントローラ30から出力される極性反転信号FRPが入力され、極性反転信号FRPに基づいて、共通電極及び容量配線Lcに印加するコモン電圧Vcomの極性を例えば水平走査期間毎に周期的に反転する。

## [0008]

走査ドライバ70は、シフトレジスタやゲート回路等で構成され、LCDコントローラ30から入力される垂直制御信号に基づいて、各走査ラインLgに走査信号(ゲートパルス)を順次印加する。

信号ドライバ80aは、シフトレジスタや、サンプルホールド回路、バッファ回路等で構成され、LCDコントローラ30から入力される水平制御信号に基づいて、反転アンプ50から入力される輝度信号を順次サンプリングし、対応する表示信号電圧を水平走査期間毎に各信号ラインLdに一斉に印加する。

#### [0009]

そして、液晶表示パネル10の走査ラインLg及び信号ラインLdが、前述の走査ドライバ70及び信号ドライバ80aによって順次選択駆動され、各信号ラインLdに印加された表示信号電圧が、液晶表示パネル10の薄膜トランジスタTFTを介して各画素電極に印加される。この結果、表示信号電圧と共通電極に印加されるコモン電圧Vcomとの電位差(画素電位)による電荷が各表示画素の液晶容量C1cに充電(保持)されて、各表示画素における液晶分子の配向状態が制御され、映像(画像)が液晶表示パネル10に表示される。

# [0010]

ところで、従来の液晶表示装置において、例えば機器の待機状態等において、自動的に、あるいはユーザーの操作に応じて、必要最小限の部分のみを動作状態とするとともに、表示を非表示状態として、消費電力を低減させるパワーセーブ状態に移行させる機能を有するものが知られており、例えば特許文献1等に開示されている。例えば、図4は、従来技術におけるパワーセーブ機能を備える液晶表示装置の構成の一例を示すものであり、パワーセーブ制御信号Psavは、液晶表示装置1aをパワーセーブ状態に設定/解除するための信号であり、信号ドライバ80aに供給され、例えば、ハイレベルで液晶表示装置1aをパワーセーブ状態に設定し、ローレベルでパワーセーブ状態を解除するように構成される。詳細には、信号ドライバ80aを構成するバッファ回路の出力状態がパワーセーブ制御信号Psavの状態に基づいて制御され、液晶表示装置1aのパワーセーブ状態の設定/解除がなされる。

# [0011]

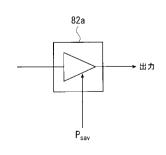

図 6 は、従来技術におけるパワーセーブ機能を備える液晶表示装置の信号ドライバのバッファ回路の要部構成の一例を示す図である。ここで、信号ドライバ 8 0 a におけるバッ

ファ回路82aは、表示信号電圧を、水平走査期間毎に、液晶表示パネル10の各信号ラインLdに一斉に印加する部分である。図6に示すように、信号ドライバ80aにおいて、バッファ回路82aにはパワーセーブ制御信号Psavが印加され、パワーセーブ制御信号Psavがローレベルの場合には、通常の駆動状態に設定されて、バッファ回路82aは、反転アンプ50から入力される輝度信号に対応する表示信号電圧を各信号ラインLdに供給する。また、このバッファ回路82aは、パワーセーブ制御信号Psavがローレベルからハイレベルに切り替えられた場合には、パワーセーブ状態としてハイインピーダンス状態に設定されて、信号ドライバ80aから信号ラインLdへの表示信号電圧の供給が遮断される。

【特許文献1】特開2003-233351号公報

【発明の開示】

【発明が解決しようとする課題】

[ 0 0 1 2 ]

ところで、液晶表示装置1aをパワーセーブ状態に設定する際には、上記したように信号ドライバ80aから信号ラインLdへの表示信号電圧の供給が遮断される。このため、各表示画素の液晶容量C1cは、パワーセーブ状態に移行した時点では、直前の電位を保持した状態となる。そして、この表示画素の液晶容量C1cに保持された電荷(残留電圧)は、静電保護抵抗Rcsや周辺配線(走査ラインLg、信号ラインLd、容量配線Lc等)、トランジスタTFT等を介して発生するリーク電流により徐々に放電され、最終的には電荷が無くなって画素電極の電位がコモン電圧Vcomと同電位となる。

[0013]

ここで、残留電圧がリーク電流によりコモン電圧 V c o m と略同等の電位となるまで(残像期間)には、場合によっては数秒程度の比較的長い時間を要する場合があり、画像が徐々に消えていくといったいわゆる残像が発生し、見苦しい表示画面となってしまうという問題があった。さらに、この間に液晶容量 C 1 c に印加されている残留電圧によって、表示画面の焼き付きの発生や液晶の劣化を招く可能性があるという問題があった。

[0014]

また、液晶表示装置1aをパワーセーブ状態に設定する際には、例えば、共通電極及び容量配線Lcに印加されるコモン電圧Vcomの駆動アンプ60による周期的な反転動作を停止させるように構成されるが、パワーセーブ状態に設定された時点のコモン電圧Vcomの電圧レベルは不定であるため、コモン電圧Vcomがハイレベルとなるタイミングでパワーセーブ状態に設定された場合には、ハイレベルのコモン電圧Vcomから所定の低電圧レベル(例えば、接地電位:0V)まで電荷を放電して安定するまでに時間を比較的長い時間を要し、また、この間に各画素電極に印加される残留電圧によって液晶表の劣化を招く可能性があるという問題があった。

[0015]

そこで本発明は、液晶表示装置をパワーセーブ状態に設定する際に、表示画面の残像を迅速に消去することができるとともに、残留電圧による焼き付きの発生や液晶の劣化を抑制することができる液晶表示装置及びその駆動方法を提供することを目的とする。

【課題を解決するための手段】

[ 0 0 1 6 ]

以上の課題を解決するため、請求項1に記載の発明の液晶表示装置は、複数の走査ライン及び複数の信号ラインと、前記複数の走査ラインと複数の信号ラインとの各交点近傍にマトリクス状に配列された複数の画素電極と、各画素電極に対向する共通電極と、前記複数の信号ラインに所定の映像信号に基づく表示信号電圧を印加し、前記共通電極に所定のコモン電圧を印加して、当該液晶表示パネルを駆動する液晶表示装置であって、前記液晶表示装置をパワーセーブ状態に設定するためのパワーセーブ制御信号の入力手段と、前記行号ラインを介して前記画素電極に所定の低信号レベルを有する第1の信号電圧を固定的に印加するように

10

20

30

40

制御する手段と、を有するパワーセーブ状態制御手段を備えることを特徴としている。

# [0017]

また、請求項8に記載の発明の液晶表示装置の駆動方法は、複数の走査ライン及び複数の信号ラインと、前記複数の走査ラインと複数の信号ラインとの各交点近傍にマトリクス状に配列された複数の画素電極と、各画素電極に対向する共通電極と、前記画素電極と前記共通電極間に充填された液晶と、を有する液晶表示パネルを備え、前記複数の信号ラインに所定の映像信号に基づく表示信号電圧を印加し、前記共通電極に所定のコモン電圧を印加して、当該液晶表示パネルを駆動する液晶表示装置の駆動方法であって、前記液晶表示装置をパワーセーブ状態に設定する際に、パワーセーブ制御信号を該液晶表示装置に入力し、入力された前記パワーセーブ制御信号に応じて、前記信号ラインを介して前記画素電極に所定の低信号レベルを有する第1の信号電圧を固定的に印加することを特徴としている。

#### [0018]

この請求項1又は8に記載の発明によれば、液晶表示装置をパワーセーブ状態に設定するために、液晶表示装置にパワーセーブ制御信号が入力された場合に、信号ラインを介して各画素電極に所定の低信号レベルを有する第1の信号電圧を固定的に印加することができる。これにより、パワーセーブ状態に移行した時点で、各画素電極に印加される電圧が所定の低信号レベルを有する第1の信号電圧に固定されるので、表示画面の残像消去にかかる時間を短縮することができる。これにより、残留電圧による焼き付きの発生や液晶表示パネルの劣化を抑制することができる。

# [0019]

請求項2に記載の液晶表示装置は、請求項1に記載の液晶表示装置において、前記液晶表示装置は、前記複数の信号ラインに前記表示信号電圧を印加する信号駆動手段を備え、前記パワーセーブ状態制御手段は、少なくとも、前記信号駆動手段における前記表示信号電圧を前記信号ラインに出力するバッファ回路部に設けられ、前記パワーセーブ制御信号及び前記第1の信号電圧が接続され、前記パワーセーブ制御信号が入力されたとき前記第1の信号電圧を前記信号ラインに供給するように切り替えるスイッチ手段からなることを特徴としている。

# [0020]

この請求項 2 に記載の発明によれば、液晶表示装置における信号駆動手段のバッファ回路部に、パワーセーブ制御信号が入力されたときに第 1 の信号電圧を信号ラインに供給するように切り替えるスイッチ手段を備えて、パワーセーブ制御信号が入力された場合に信号ラインに第 1 の信号電圧を印加することができる。

# [0021]

請求項3に記載の液晶表示装置は、請求項1または2に記載の液晶表示装置において、前記パワーセーブ状態制御手段は、さらに、前記入力手段に前記パワーセーブ制御信号が入力された場合に、前記共通電極に所定の低信号レベルを有する第2の信号電圧を固定的に印加するように制御する制御手段を備えることを特徴としている。

# [0022]

請求項4に記載の液晶表示装置は、請求項3に記載の液晶表示装置において、前記液晶表示装置は、前記コモン電圧を生成して前記共通電極に印加する共通電極駆動手段と、所定の周期で反転制御される極性反転制御信号に応じて前記共通電極駆動手段により生成される前記コモン電圧の極性を制御する手段と、を備え、前記パワーセーブ状態制御手段は、前記パワーセーブ制御信号が入力された場合に、前記極性反転制御信号を所定の低信号レベルに固定的に設定し、これにより前記コモン電圧を前記第2の信号電圧に設定する手段を備えることを特徴としている。

#### [0023]

この請求項3又は4に記載の発明によれば、パワーセーブ制御信号が入力されたときに 共通電極に第2の信号電圧を固定的に印加する制御手段を備えて、パワーセーブ制御信号 が入力された場合に共通電極の電位を第2の信号電圧に設定することができる。 20

30

50

### [0024]

請求項5に記載の液晶表示装置は、請求項3に記載の液晶表示装置において、前記第1の信号電圧および前記第2の信号電圧は、同一の電位を有することを特徴としている。

#### [0025]

請求項6に記載の液晶表示装置は、請求項3に記載の液晶表示装置において、前記第1の信号電圧および前記第2の信号電圧は、接地電位を有することを特徴としている。

#### [0026]

請求項7に記載の液晶表示装置は、請求項3に記載の液晶表示装置において、前記第1の信号電圧および前記第2の信号電圧は、該第1の信号電圧と該第2の信号電圧との電位差が、前記液晶表示パネルの前記液晶の閾値電圧より小さい値となる電圧であることを特徴としている。

#### [ 0 0 2 7 ]

請求項10に記載の液晶表示装置の駆動方法は、請求項9に記載の液晶表示装置の駆動方法において、前記第1の信号電圧および前記第2の信号電圧は、同一の電位を有することを特徴とする。

# [0028]

請求項11に記載の液晶表示装置の駆動方法は、請求項9に記載の液晶表示装置の駆動方法において、前記第1の信号電圧および前記第2の信号電圧は、接地電位を有することを特徴とする。

## [0029]

請求項12に記載の液晶表示装置の駆動方法は、請求項9に記載の液晶表示装置の駆動方法において、前記第1の信号電圧および前記第2の信号電圧は、該第1の信号電圧と該第2の信号電圧との電位差が、前記液晶表示パネルの前記液晶の閾値電圧より小さい値となる電圧であることを特徴とする。

### [0030]

この請求項5~7又は請求項10~12の何れかに記載の発明によれば、液晶表示装置をパワーセーブ状態に設定する際に信号ラインに印加される第1の信号電圧及び共通電極に印加される第2の信号電圧の値を、同電位あるいは接地電位、又は、両電圧間の電位差が液晶の閾値電圧より小さい値となる電圧として、表示画面の残像消去にかかる時間を短縮し、残留電圧による焼き付きの発生や液晶表示パネルの劣化を抑制することができる。

# 【発明の効果】

# [0031]

請求項1又は4に記載の発明によれば、液晶表示装置をパワーセーブ状態に設定するために、液晶表示装置にパワーセーブ制御信号が入力された場合に、信号ラインを介して各画素電極に所定の低信号レベルを有する第1の信号電圧を固定的に印加することができる。これにより、パワーセーブ状態に移行した時点で、各画素電極に印加される電圧が所定の低信号レベルを有する第1の信号電圧に固定されるので、表示画面の残像消去にかかる時間を短縮することができる。これにより、残留電圧による焼き付きの発生や液晶表示パネルの劣化を抑制することができる。

## [0032]

請求項2に記載の発明によれば、液晶表示装置における信号駆動手段のバッファ回路部に、パワーセーブ制御信号が入力されたときに第1の信号電圧を信号ラインに供給するように切り替えるスイッチ手段を備えて、パワーセーブ制御信号が入力された場合に信号ラインに第1の信号電圧を印加することができる。

請求項3又は4に記載の発明によれば、パワーセーブ制御信号が入力されたときに共通電極に第2の信号電圧を固定的に印加する制御手段を備えて、パワーセーブ制御信号が入力された場合に共通電極の電位を第2の信号電圧に設定することができる。

# [0033]

請求項5~7又は請求項10~12の何れかに記載の発明によれば、液晶表示装置をパワーセーブ状態に設定する際に信号ラインに印加される第1の信号電圧及び共通電極に印

10

20

30

40

10

20

30

40

50

加される第 2 の信号電圧の値を、同電位あるいは接地電位、又は、両電圧間の電位差が液晶の閾値電圧より小さい値となる電圧として、表示画面の残像消去にかかる時間を短縮し、残留電圧による焼き付きの発生や液晶表示パネルの劣化を抑制することができる。

【発明を実施するための最良の形態】

[ 0 0 3 4 ]

以下、図1~図3を参照して、本発明を適用した液晶表示装置の実施形態について詳細に説明する。

[0035]

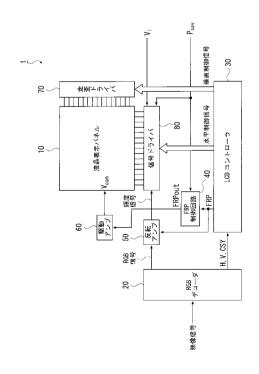

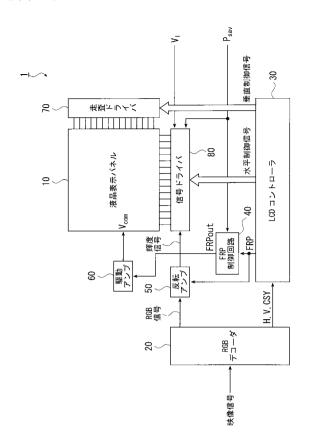

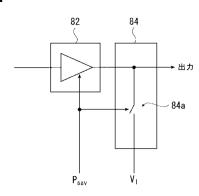

図1は、本発明に係わる表示装置の全体構成の一実施形態を示すプロック図であり、図2は、本実施形態に係わる表示装置に適用される信号ドライバにおけるバッファ回路部の要部構成例を示す図であり、図3は、本実施形態に係わる表示装置に適用されるFRP制御回路の回路構成の一例を示す図である。尚、図1において、従来技術として図4を参照して説明した液晶表示装置1aと同等に機能する構成要素には同一の符号を付し、以下ではその説明を簡略化又は省略する。図1に示すように、本実施形態に係わる液晶表示装置1は、液晶表示パネル10と、RGBデコーダ20と、LCDコントローラ30と、FRP制御回路40と、反転アンプ50と、駆動アンプ60と、走査ドライバ70と、信号ドライバ80とを備えて構成されている。

[0036]

すなわち、本実施形態に係わる液晶表示装置1における信号ドライバ80は、図4に示した従来技術における信号ドライバ80aと同様に、シフトレジスタや、サンプルホールド回路、バッファ回路、制御回路等で構成され、LCDコントローラ30から入力される水平制御信号に基づいて、反転アンプ50から入力される輝度信号を順次サンプリングし、対応する表示信号電圧を一水平走査期間毎に液晶表示パネル10の各信号ラインLdに一斉に印加する構成を備えるとともに、図1に示すように、表示信号電圧を各信号ラインLdに印加するバッファ回路部にパワーセーブ制御信号Psav及び電圧V1が供給されて、バッファ回路の出力状態が、パワーセーブ制御信号Psavの状態に基づいて制御される構成を備えている。ここで、パワーセーブ制御信号Psavは、従来技術と同様に、ねる構成を備えている。ここで、パワーセーブ制御信号Psavは、従来技術と同様に、次晶表示装置1をパワーセーブ状態に設定し、ローレベルでパワーセーブ状態を解除するようになっている。

[0037]

図2は、本実施形態に係わる表示装置に適用される信号ドライバにおけるバッファ回路部の要部構成例を示す図である。すなわち、図2に示すように、本実施形態における信号ドライバ80のバッファ回路部は、パワーセーブ制御信号Psavが供給されるバッファ回路82と、バッファ回路82の出力端に接続されてパワーセーブ制御信号Psavが供給される制御回路84と、を有して構成される。ここで、バッファ回路82は、従来技術と同様に、パワーセーブ制御信号Psavがローレベルの場合には、通常の駆動状態に設定されて、反転アンプ50から入力される輝度信号に対応する表示信号電圧を出力する。また、このバッファ回路82は、パワーセーブ制御信号Psavがハイレベルに設定されて、パワーセーブ状態として出力インピーダンスがハイインピーダンス状態に設定されて、信号ドライバ80から表示信号電圧の出力を遮断する。

[0038]

一方、制御回路84は、パワーセーブ制御信号Psavによってオンオフ制御され、一端がバッファ回路82の出力端に接続されるとともに、他端が所定の低信号レベルを有する電圧V1(第1の信号電圧)に接続されるスイッチ84aを備える。ここで、電圧V1は、例えば、接地電位(0V)を有する一定電位に設定される。そして、この制御回路84は、パワーセーブ制御信号Psavがローレベルの場合には、スイッチ84aがオフ状態に設定されて、バッファ回路82から出力される表示信号電圧を、そのまま出力して、液晶表示パネル10の各信号ラインLdに供給する。また、パワーセーブ制御信号Psa

10

20

30

40

50

vがハイレベルに設定されて、パワーセーブ状態に設定される場合には、スイッチ84aがオン状態に切り替え制御されて電圧 V 1 に接続され、このとき、バッファ回路82はハイインピーダンス状態に設定されていることにより、信号ドライバ80の出力は、所定の低信号レベルを有する電圧 V 1 に固定的に設定される。

#### [ 0 0 3 9 ]

これにより、パワーセーブ制御信号 P s a v がローレベルからハイレベルに切り替えられた場合に、信号ドライバ 8 0 の出力が所定の低信号レベルを有する電圧 V 1 に固定的に設定され、液晶表示パネル 1 0 の各信号ライン L d に供給して、液晶表示パネル 1 0 の各画素電極に、所定の低信号レベルを有する電圧 V 1 (第 1 の信号電圧)に固定的に印加する。

[0040]

また、本実施形態の液晶表示装置1では、図1に示すように、LCDコントローラ30と駆動アンプ60との間にFRP制御回路40が介在され、FRP制御回路40にLCDコントローラ30により生成された極性反転信号FRP及びパワーセーブ制御信号Psavが供給されて、出力極性反転信号FRPoutを出力する構成を備える。また、駆動アンプ60は、FRP制御回路40から出力される出力極性反転信号FRPoutが入力され、この出力極性反転信号FRPoutに基づいて、液晶表示パネル10の共通電極及び容量配線に印加するコモン電圧Vcomの極性を反転制御するように構成される。

[ 0 0 4 1 ]

FRP制御回路40は、図3に示すように、例えば、パワーセーブ制御信号PSavが印加されて、パワーセーブ制御信号PSavを反転した信号を出力するインバータ回路40aと、LCDコントローラ30から出力される極性反転信号FRPとインバータ回路40aから出力されるパワーセーブ制御信号PSavの反転信号が入力されて、出力極性反転信号FRPout)は、パワーセーブ制御信号PSavの状態に基づいて制御される。具体的には、FRP制御回路40は、パワーセーブ制御信号PSavの状態に基づいて制御される。具体的には、FRP制御回路40は、パワーセーブ制御信号PSavがローレベルの場合には、インバータ回路40aから出力されアンド回路40bの一方の入力端に印加される信号レベルがハイレベルとなるため、LCDコントローラ30から出力されて、アンド回路40bの他方の入力端に印加される極性反転信号PRPを出力極性反転信号FRPoutは極性反転信号FRPと同じ信号となり、通常の駆動状態となる。

[0042]

一方、パワーセーブ制御信号 Psavがハイレベルに設定されて、パワーセーブ状態に設定される場合には、インバータ回路 40 aから出力されアンド回路 40 bの一方の入力端に印加される信号レベルがローレベルとなるため、アンド回路 40 bの出力レベルはローレベルに設定され、出力極性反転信号 FRPoutはローレベルに設定されて、ローレベルに設定された出力極性反転信号 FRPoutが駆動アンプ 60 に入力され、これにより、コモン電圧 Vcomが所定の低信号レベルを有する一定電圧(ローレベル:第2の信号電圧)に設定される。ここで、コモン電圧 Vcomに設定される一定電圧は、例えば、接地電位(0V)に設定される。

[ 0 0 4 3 ]

これにより、パワーセーブ制御信号 P s a v がローレベルからハイレベルに切り替えられた場合に、FRP制御回路 4 0 から出力される出力極性反転信号 FRPoutの信号レベルがローレベルに設定され、ローレベルに設定された出力極性反転信号 FRPoutが駆動アンプ 6 0 に入力されることにより、液晶表示パネル 1 0 の共通電極に供給されるコモン電圧 V c o m が、所定の低信号レベルを有する電圧(第 2 の信号電圧)に固定的に設定される。

#### [0044]

以上説明した本実施形態における液晶表示装置1によれば、パワーセーブ制御信号Ps

avをハイレベルに切り替えて液晶表示装置1をパワーセーブ状態に設定する際に、液晶表示パネル10の各画素電極に印加される電圧を所定の低信号レベルを有する電圧V1(第1の信号電圧)に固定的に設定することができ、又、液晶表示パネル10の共通電極に供給されるコモン電圧Vcomを所定の低信号レベルを有する電圧(第2の信号電圧)に固定的に設定される。ここで、第1の信号電圧及び第2の信号電圧は、例えば共に接地電位に設定される。これにより、第1の信号電圧と第2の信号電圧との電位差からなる液晶表示パネル10の各液晶容量に印加される電位差が微小電圧に設定されることになり、表示画面の残像を迅速に消去することができ、また、各画素電極に対する残留電圧の印加を抑制することができて、残留電圧による焼き付きや液晶の劣化を抑制することができる。

#### [0045]

尚、上記した実施形態では、第1の信号電圧及び第2の信号電圧を、共に接地電位(0V)とするものとしたが、本発明はこれに限るものではなく、両者を同電位とするものであればよい。更に、同電位にするものに限らず、第1の信号電圧と第2の信号電圧との電位差が、液晶表示パネル10の液晶の閾値電圧(液晶表示パネル10の透過率が液晶C1cに印加される電圧が0Vの状態から変化し始める電圧:1V程度)より小さい電圧であってもよい。

【図面の簡単な説明】

- [0046]

- 【図1】本発明に係わる表示装置の全体構成の一実施形態を示すブロック図である。

- 【図2】本実施形態に係わる表示装置に適用される信号ドライバにおける、バッファ回路 部の要部構成例を示す図である。

- 【図3】本実施形態に係わる表示装置に適用されるFRP制御回路の回路構成の一例を示す図である。

- 【図4】従来技術における液晶表示装置の概略構成の一例を示すブロック図である。

- 【 図 5 】 従 来 技 術 に お け る 液 晶 表 示 パ ネ ル の 回 路 構 成 の 一 例 を 示 す 図 で あ る 。

- 【図 6 】従来技術における液晶表示装置の信号ドライバにおけるバッファ回路の要部構成の一例を示す図である。

【符号の説明】

- [0047]

- 1 液晶表示装置

- 1 0 液晶表示パネル

- 2 0 R G B デコーダ

- 30 LCDコントローラ

- 4 0 F R P 制御回路

- 5 0 反転アンプ

- 6 0 駆動アンプ

- 70 走査ドライバ

- 80 信号ドライバ

10

30

# 【図1】

# 【図2】

【図3】

# 【図4】

【図5】

【図6】

# フロントページの続き

(51) Int.CI.<sup>7</sup> F I テーマコード (参考)

G 0 9 G 3/20 6 2 4 C G 0 9 G 3/20 6 7 0 K

F ターム(参考) 5C006 AC21 AC25 AF68 BB16 BC11 BF25 BF26 BF42 FA34 5C080 AA10 BB05 DD18 DD26 FF11 JJ02 JJ03