## (19) **日本国特許庁(JP)**

# (12) 特許公報(B2)

(11)特許番号

特許第6123413号 (P6123413)

(45) 発行日 平成29年5月10日(2017.5.10)

(24) 登録日 平成29年4月14日(2017.4.14)

| (51) Int.Cl. | FΙ                            |          |                          |

|--------------|-------------------------------|----------|--------------------------|

| GO9F 9/30    | ( <b>2006.01</b> ) GO9F       | 9/30     | 338                      |

| HO1L 29/786  | <b>(2006.01)</b> GO9F         | 9/30     | 337                      |

| HO1L 21/336  | ( <b>2006.01)</b> HO1L        | 29/78    | 618B                     |

|              | HO1L                          | 29/78    | 618A                     |

|              | HO1L                          | 29/78    | 619A                     |

|              |                               |          | 請求項の数 10 (全 11 頁) 最終頁に続く |

| (21) 出願番号    | 特願2013-66151 (P2013-66151)    | (73) 特許権 | 者 000003193              |

| (22) 出願日     | 平成25年3月27日 (2013.3.27)        |          | 凸版印刷株式会社                 |

| (65) 公開番号    | 特開2014-191169 (P2014-191169A) |          | 東京都台東区台東1丁目5番1号          |

| (43) 公開日     | 平成26年10月6日 (2014.10.6)        | (74) 代理人 | 110001276                |

| 審査請求日        | 平成28年2月19日 (2016.2.19)        |          | 特許業務法人 小笠原特許事務所          |

|              |                               | (72) 発明者 | 宮入 ゆかり                   |

|              |                               |          | 東京都台東区台東1丁目5番1号 凸版印      |

|              |                               |          | 刷株式会社内                   |

|              |                               |          |                          |

|              |                               | 審査官      | 佐野 浩樹                    |

|              |                               |          |                          |

|              |                               |          |                          |

最終頁に続く

## (54) 【発明の名称】薄膜トランジスタアレイおよび画像表示装置

## (57)【特許請求の範囲】

## 【請求項1】

少なくとも、絶縁基板と、ゲート電極と、ゲート絶縁層と、ソース電極と、ドレイン電極と、半導体層と、保護層と、層間絶縁膜と、画素電極とを備えた薄膜トランジスタアレイであって、

前記半導体層及び前記保護層はソース配線に平行なストライプ形状であり、

前記保護層は、前記半導体層よりも幅が広く、幅方向において前記半導体層を覆うよう に形成され、

前記ドレイン電極と前記画素電極との導通を図るために設けられた前記層間絶縁膜のビアホールの中心位置が、互いに隣接するストライプ形状の前記保護層間の中点を通るストライプに平行な直線上に位置することを特徴とする薄膜トランジスタアレイ。

## 【請求項2】

前記ビアホールの中心位置と、前記中点を通るストライプに平行な直線上の位置とのずれが40μm以下であることを特徴とする請求項1に記載の薄膜トランジスタアレイ。

#### 【請求項3】

前記半導体層が有機半導体もしくは酸化物半導体であることを特徴とする請求項 1 に記載の薄膜トランジスタアレイ。

## 【請求項4】

請求項1に記載の薄膜トランジスタアレイの製造方法であって、

半導体層をフレキソ印刷法、インクジェット印刷法、スクリーン印刷法のいずれか1つ

以上により形成することを特徴とする薄膜トランジスタアレイの製造方法。

## 【請求項5】

前記保護層が有機絶縁材料により形成されていることを特徴とする請求項1に記載の薄膜トランジスタアレイ。

## 【請求項6】

請求項1に記載の薄膜トランジスタアレイの製造方法であって、

保護層<u>を</u>フレキソ印刷法、インクジェット印刷法、スクリーン印刷法のいずれか 1 つ以上により形成することを特徴とする薄膜トランジスタアレイの製造方法。

## 【請求項7】

請求項1に記載の薄膜トランジスタアレイの製造方法であって、

層間絶縁膜<u>を</u>スクリーン印刷<u>法に</u>より形成<u>す</u>ることを特徴とす<u>る薄</u>膜トランジスタアレイの製造方法。

#### 【請求項8】

前記絶縁基板がプラスチック基板であることを特徴とする請求項 1 に記載の薄膜トランジスタアレイ。

#### 【請求項9】

請求項1に記載の薄膜トランジスタアレイと画像表示媒体とを備えていることを特徴と する画像表示装置。

## 【請求項10】

前記画像表示媒体が電気泳動方式によるものであることを特徴とする請求項 9 に記載の画像表示装置。

【発明の詳細な説明】

#### 【技術分野】

#### [00001]

本発明は、薄膜トランジスタアレイおよび画像表示装置に関する。

## 【背景技術】

### [0002]

情報技術の目覚しい発展により、現在ではノート型パソコンや携帯情報端末などでの情報の送受信が頻繁に行われている。近い将来、場所を選ばずに情報をやり取りできるユビキタス社会が来るであろうことは周知の事実である。そのような社会においては、より軽量で薄型の情報端末が望まれる。

## [0003]

そのような情報端末に使用する電子部材の中でも、現在薄膜トランジスタ素子に使用されている半導体材料の主流はシリコン系である。シリコン系材料を用いた薄膜トランジスタ素子の形成には高い温度の工程が含まれるため、薄膜トランジスタ素子の基板材料には工程温度に耐え得ることが求められる。このため、一般的には薄膜トランジスタ素子を形成する基板としてガラスが使用されている。

## [0004]

しかしながら、先に述べた情報端末を構成する際にガラスを用いた場合、その情報端末は重く、柔軟性がなく、落下の衝撃で割れる可能性のある製品となってしまう。従ってガラス上に薄膜トランジスタ素子を形成することに起因するこれらの特徴は、ユビキタス社会における情報端末として望ましくないものであるといえる。

## [0005]

そこで近年、薄膜トランジスタの半導体材料として有機半導体が注目されている。有機 半導体材料はシリコン系材料のような高温での熱処理工程を必要としないため可撓性のプ ラスチック基板上に設けられる等の利点を有する。さらに、真空プロセスを用いず印刷プ ロセスで作製できるためコストを下げられる等の利点も有する。

### [0006]

溶液から半導体層を形成するには、スピンコート法やディップ法、インクジェット法などの方法が挙げられる。なかでも、印刷プロセスを適用することにより、効率よく半導体

10

20

30

40

層を形成することができる。例えば特許文献 1 においては、フレキソ印刷により有機半導体溶液のパターニングを行っている。

#### [0007]

さらに、特許文献 2 では、半導体層をストライプ形状とすることで、アライメント精度 を向上させ、生産効率を更に高めることができる。

#### [00008]

保護層の形成においても、ウェットプロセスを適用することで簡便かつ低コストに保護層を形成することができる。例えば特許文献 3 では、フレキソ印刷により保護層を形成し、簡便に薄膜トランジスタアレイを作製している。

【先行技術文献】

10

## 【特許文献】

[0009]

【特許文献 1 】特開 2 0 0 6 - 6 3 3 3 4 号公報

【特許文献2】特開2008-235861号公報

【特許文献3】国際公開第2010/107027号

【発明の概要】

【発明が解決しようとする課題】

### [0010]

しかしながら、印刷法によって薄膜トランジスタアレイを形成する場合、従来のフォトリソグラフィを用いたパターニング法に比べ、アライメント精度が低く、パターン形状のバラツキも大きいため、より多くのアライメントマージンが必要となる。なかでも、印刷法により半導体層と保護層を形成する場合、半導体層と保護層双方のバラツキを考慮してアライメントマージンを取らなければならない。特に、保護層のアライメントマージンが小さく、保護層の絶縁性材料がドレイン電極上にはみ出してしまうと、層間絶縁膜のビアホールを塞いでしまい、ドレイン電極と画素電極とが導通することができなくなってしまう。一方、アライメントマージンが多くなりすぎると、薄膜トランジスタアレイの解像度が低下し、視認性が低下してしまう。

## [0011]

そこで、本発明では、保護層と層間絶縁膜のビアホールとの距離を最大にとることで、 保護層材料がビアホールを塞いでしまうことを抑制でき、歩留まりを向上することができ る薄膜トランジスタアレイ、およびそれを備えた画像表示装置を提供する。

30

20

## 【課題を解決するための手段】

### [0012]

前記課題を解決するための第1の発明は、少なくとも、絶縁基板と、ゲート電極と、ゲート電極と、ゲート絶縁層と、ソース電極と、ドレイン電極と、半導体層と、保護層と、層間絶縁膜と、画素電極とを備えた薄膜トランジスタアレイであって、前記半導体層及び前記保護層はソース配線に平行なストライプ形状であり、前記保護層は、前記半導体層よりも幅が広く、幅方向において前記半導体層を覆うように形成され、前記ドレイン電極と前記画素電極との導通を図るために設けられた前記層間絶縁膜のビアホールの中心位置が、互いに隣接するストライプ形状の前記保護層間の中点を通るストライプに平行な直線上に位置することを特徴とする薄膜トランジスタアレイである。

40

50

#### [0013]

また、第 2 の発明は、前記第 1 の発明において、前記ビアホールの中心位置と、前記中点を通るストライプに平行な直線上の位置とのずれが 4 0  $\mu$  m以下であることを特徴とする薄膜トランジスタアレイである。

## [0014]

また、第3の発明は、前記第1の発明において、前記半導体層が有機半導体もしくは酸化物半導体であることを特徴とする薄膜トランジスタアレイである。

## [0015]

また、第4の発明は、上述の薄膜トランジスタアレイの製造方法であって、半導体層を

フレキソ印刷法、インクジェット印刷法、スクリーン印刷法のいずれか 1 つ以上により形成することを特徴とする薄膜トランジスタアレイの製造方法である。

#### [0016]

また、第5の発明は、前記第1の発明において、前記保護層が有機絶縁材料により形成されていることを特徴とする薄膜トランジスタアレイである。

#### [0017]

また、第6の発明は、<u>上述の薄膜トランジスタアレイの製造方法であって、</u>保護層<u>を</u>フレキソ印刷法、インクジェット印刷法、スクリーン印刷法のいずれか1つ以上により形成することを特徴とする薄膜トランジスタアレイの製造方法である。

#### [0018]

また、第7の発明は、<u>上述の薄膜トランジスタアレイの製造方法であって、</u>層間絶縁膜<u>を</u>スクリーン印刷<u>法に</u>より形成<u>す</u>ることを特徴とする薄膜トランジスタアレイ<u>の製造方法</u>である。

## [0019]

また、第8の発明は、前記第1の発明において、前記絶縁基板がプラスチック基板であることを特徴とする薄膜トランジスタアレイである。

#### [0020]

また、第9の発明は、前記薄膜トランジスタアレイと画像表示媒体とを備えていること を特徴とする画像表示装置である。

## [0021]

また、第10の発明は、前記第9の発明において、前記画像表示媒体が電気泳動方式によるものであることを特徴とする画像表示装置である。

## 【発明の効果】

#### [0022]

本発明の薄膜トランジスタアレイによれば、低コストかつ高品質なフレキシブル薄膜トランジスタを歩留まりよく提供することが可能となる。薄膜トランジスタアレイのドレイン電極と画素電極との導通を図るために設けられた層間絶縁膜のビアホールの中心位置が、半導体層を覆う隣接したストライプ形状の保護層の中点を通るストライプに平行な直線上に位置することで、アライメントマージンを最大にとることができ、線幅のバラツキやアライメントずれに起因する歩留まりの低下を軽減し、フレキシブル薄膜トランジスタのスループットを向上することができる。

## [0023]

少なくとも、絶縁基板と、ゲート電極と、ゲート絶縁層と、ソース電極と、ドレイン電極と、半導体層と、前記半導体層を覆う保護層と、層間絶縁膜と、上部画素電極とを備えた薄膜トランジスタアレイであって、前記保護層は前記ソース配線に平行なストライプ形状であり、ドレイン電極と画素電極との導通を図るために設けられた層間絶縁膜のビアホールの中心位置が、前記ストライプ形状の保護層と、それに隣接するストライプ形状の保護層との中点を通るストライプに平行な直線上に位置することで、薄膜トランジスタアレイの解像度によらず、保護層のアライメントマージンを最大にとることができる。さらに、保護層の形状をストライプとすることで、層間絶縁膜や半導体層とのアライメント精度が向上する。

#### [0024]

前記層間絶縁膜のビアホールの中心位置と、隣接するストライプ形状の保護層の中点を通るストライプに平行な直線上からのずれ量を、最大40μm考慮することで、パターン形状のバラツキや印刷機のアライメント誤差、工程中の加熱によるプラスチック基材の伸縮についても加味したパターン設計を行うことができる。

## [0025]

前記半導体層を有機半導体とすることで、ウェットプロセスを適用することができ、大面積にも短いタクトタイムで薄膜トランジスタアレイを形成することができる。

## [0026]

50

40

10

20

前記半導体層がフレキソ印刷法、インクジェット印刷法、スクリーン印刷法により形成されることで、大面積にも短いタクトタイムで薄膜トランジスタアレイを形成することができる。

## [0027]

前記保護層が有機絶縁材料により形成されていることで、ウェットプロセスを適用することができ、大面積にも短いタクトタイムで薄膜トランジスタアレイを形成することができる。

## [0028]

前記保護層がフレキソ印刷法、インクジェット印刷法、スクリーン印刷法により形成されることで、大面積にも短いタクトタイムで薄膜トランジスタアレイを形成することができる。

## [0029]

前記層間絶縁膜が有機絶縁材料により形成されていることで、ウェットプロセスを適用でき、大面積を有する薄膜トランジスタアレイでも短いタクトタイムで形成することができる。

## [0030]

前記絶縁基板がプラスチック基板であることで、軽量でフレキシブルな薄膜トランジスタアレイを作製することができる。

## 【図面の簡単な説明】

## [0031]

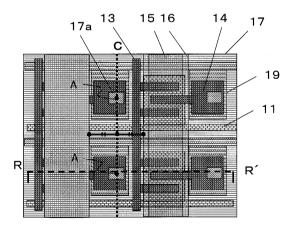

【図1】本発明の実施形態を示すものであり、薄膜トランジスタアレイ全体の概略構成を示すパターンレイアウト平面図である。

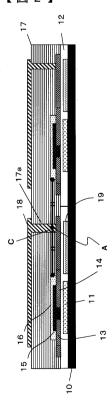

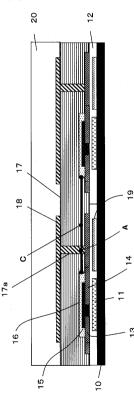

【図2】本トランジスタアレイの隣接した2素子における断面構造である(図1のR-R ・間をスライスしたもの)。

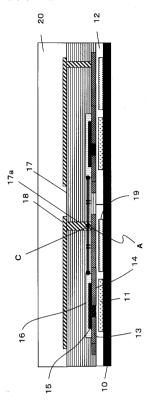

【図3】比較例1の実施形態を示すものであり、本トランジスタアレイの隣接した2素子における断面構造である。

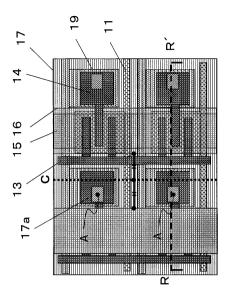

【図4】比較例1における薄膜トランジスタアレイ全体の概略構成を示すパターンレイアウト平面図である。

【図5】比較例1における隣接した2素子における断面構造である(図4のR-R'間をスライスしたもの)。

【発明を実施するための形態】

## [0032]

以下、本発明の実施の形態を、図面を参照しつつ説明する。実施の形態において、同一構成要素には同一符号を付け、実施の形態間において重複する説明は省略する。

## [0033]

図1、図2に、本発明の薄膜トランジスタアレイ1の構成の一例を示す。図1は薄膜トランジスタアレイ1のパターンレイアウト平面図を示す。図2は、図1の薄膜トランジスタアレイ1を、ビアホール17aを通るR-R'線で、保護層16のストライプの延伸方向に垂直に切断した断面図を示す。

## [0034]

プラスチック基板10上にゲート電極11、キャパシタ電極19、ゲート絶縁層12、ソース電極13、ドレイン電極14、半導体層15、保護層16、層間絶縁膜17、および画素電極18を備えた薄膜トランジスタアレイであり、保護層16は有機絶縁材料からなり、ストライプ形状を有していることを特徴とする。さらに、画素電極18とドレイン電極14を導通するために層間絶縁膜17にあけられたビアホール17aの中心位置Aが、図2に示すように、互いに隣接するストライプ形状の保護層16間の中点を通るストライプに平行な直線C上に位置し、ビアホール17aの中心位置Aと直線Cとのずれが40μm以内であることを特徴とする。互いに隣接する2つの保護層16間は、各保護層16をラインとした場合のスペースであり、当該中点は、図2の断面図上では、上記2つの保護層

30

10

20

40

10

20

30

40

50

16間のスペースに面する各保護層16の端部から、等距離にある線分上の点である。上記中心位置Aは、ビアホール17aのアライメント位置の中心であって基板面に平行な平面上での点の位置を意味し、当該平面上での2次元座標で表される位置である。

## [0035]

本発明のプラスチック基板10には、ポリメチレンメタクリレート、ポリアクリレート、ポリカーボネート、ポリスチレン、ポリエチレンサルファイド、ポリエーテルスルホン、ポリオレフィン、ポリエチレンテレフタレート、ポリエチレンナフタレート、シクロオレフィンポリマー、ポリエーテルサルフォン、トリアセチルセルロース、ポリビニルフルオライドフィルム、エチレン・テトラフルオロエチレン、共重合樹脂、耐候性ポリエチレンテレフタレート、耐候性ポリプロピレン、ガラス繊維強化アクリル樹脂フィルム、ガラス繊維強化ポリカーボネート、透明性ポリイミド、フッ素系樹脂、環状ポリオレフィン樹脂等を使用することができるが、本発明はこれらに限定されるものではない。これらは単独でも、二種以上が積層された複合基板としても使用することができる。またガラスやプラスチック基板上にカラーフィルタのような樹脂層を有する基板も使用することができる

### [0036]

本発明のゲート電極11、ソース電極13、ドレイン電極14、画素電極18、キャパ シタ電極19には、Au、Ag、Cu、Cr、Al、Mg、Liなどの低抵抗金属材料や 酸化物材料が好適に用いられる。具体的には、酸化インジウム(In,Oa)、酸化錫( SnO₂)、酸化亜鉛(ZnO)、酸化カドミウム(CdO)、酸化インジウムカドミウ ム(CdIn<sub>2</sub>O<sub>4</sub>)、酸化カドミウム錫(Cd<sub>2</sub>SnO<sub>4</sub>)、酸化亜鉛錫(Zn<sub>2</sub>Sn 〇 ょ)、酸化インジウム亜鉛(InZnO)等が挙げられる。またこの酸化物材料に不純 物をドープしたものも好ましい。一例として酸化インジウムにモリブデンやチタンをドー プしたもの、酸化錫にアンチモンやフッ素をドープしたもの、酸化亜鉛にインジウム、ア ルミニウム、ガリウムをドープしたものなどが挙げられる。なかでも酸化インジウムに錫 をドープした酸化インジウム錫(ITO)がとりわけ低い抵抗率を示す。またPEDOT (ポリエチレンジオキシチオフェン)等の有機導電性材料も好適であり、単体の場合も導 電性酸化物材料との複数積層の場合も好んで用いられる。ゲート電極11、ソース電極1 3 およびドレイン電極 1 4、 画素電極 1 8、 キャパシタ電極 1 9 は、すべて同じ材料から できていても、違う材料からできていてもよい。しかし、工程を減らすためにはソース電 極13とドレイン電極14に同一の材料を使用することが望ましい。これらの電極は、真 空蒸着法、イオンプレーティング法、スパッタ法、レーザーアブレーション法、プラズマ CVD法、光CVD法、ホットワイヤーCVD法等により形成される。また上述の導電性 材料をインキ状、ペースト状にしたものをスクリーン印刷、フレキソ印刷、インクジェッ ト法等により塗布し、焼成することでも形成が可能である。本発明はこれらに限定される ものではない。

## [0037]

本発明のゲート絶縁膜12には、酸化シリコン、窒化シリコン、酸化窒化シリコン、酸化アルミニウム、酸化タンタル、酸化イットリウム、酸化ハフニウム、ハフニウムアルミネート、酸化ジルコニア、酸化チタン等の無機材料、または PMMA(ポリメチルメタクリレート)等のポリアクリレート、PVA(ポリビニルアルコール)、PVP(ポリビニルフェノール)等が挙げられるが、本発明はこれらに限定されるものではない。またゲートリーク電流を抑えるために、絶縁材料の好ましい抵抗率は10<sup>11</sup> cm以上、より好ましくは10<sup>14</sup> cm以上である。

## [0038]

本発明で用いられる半導体層 1 5 として、酸化物半導体や有機半導体が挙げられる。酸化物半導体材料としては、亜鉛、インジウム、錫、タングステン、マグネシウム、ガリウムなどのうち一種類以上の元素を含む酸化物、すなわち酸化亜鉛、酸化インジウム、酸化インジウム亜鉛、酸化錫、酸化タングステン、酸化亜鉛ガリウムインジウム等公知の材料が挙げられる。有機半導体材料としては、ポリチオフェン、ポリアリルアミン、フルオレ

ンビチオフェン共重合体、およびそれらの誘導体のような高分子有機半導体材料、およびペンタセン、テトラセン、銅フタロシアニン、ペリレン、6,13‐ビス(トリイソプロピルシリルエチニル)ペンタセン(TIPS‐ペンタセン)、およびそれらの誘導体のような低分子有機半導体材料や加熱処理などで有機半導体に変換される前駆体を半導体材料インキとして用いることができる。また、カーボンナノチューブあるいはフラーレンなどの炭素化合物や半導体ナノ粒子分散液なども半導体層の材料として用いることができる。半導体材料インキを用いる場合には、溶媒としてトルエンやキシレン、インダン、テトラリン、プロピレングリコールメチルエーテルアセテートなどが挙げられるが、これらに限定されるものではない。上述の導電性材料をインキ状、ペースト状にしたものをスクリーン印刷、フレキソ印刷、インクジェット法等により塗布し、乾燥する方法が好適に用いられる。

[0039]

本発明で用いられる保護層16として用いられる材料はポリビニルフェノール、ポリメタクリル酸メチル、ポリイミド、ポリビニルアルコール、エポキシ樹脂、フッ素樹脂などの高分子溶液、アルミナやシリカゲルなどの粒子を分散させた溶液が好適に用いられる。また、保護層の形成方法はスクリーン印刷やフレキソ印刷、インクジェット法などの湿式法を用いて直接パターンを形成する方法が好適に用いられる。

[0040]

本発明のパターン形成方法を用いて形成される薄膜トランジスタの構造としては、特に限定されるものではなくトップゲート型、ボトムゲート型のいずれの構造であってもよい

ゲート電極の配置以外の構造の違いとして、半導体層の位置が異なるボトムコンタクト型、トップコンタクト型があるが、本発明はこれらに限定されるものではない。

【実施例1】

[0041]

図3に、実施例1に係るボトムゲートボトムコンタクト型のフレキシブル薄膜トランジスタアレイから成る薄膜トランジスタアレイ1の断面構造を示し、製造方法を説明する。本薄膜トランジスタアレイ1は1素子サイズ300μm×300μmであり、この素子が240×320個あるものである。

[0042]

プラスチック基板 1 0 としてポリエチレンナフタレート(PEN)フィルムを用いた。 PENフィルム上にアルミニウムをスパッタ法により 1 0 0 n m成膜後、ポジレジストを 用いてフォトリソグラフィ、エッチングを行い、その後レジストを剥離することによりゲ ート電極 1 1 、キャパシタ電極 1 9 を形成した。

[0043]

続いてゲート絶縁材料としてポリイミドをダイコーターにより塗布し、180 で1時間乾燥させゲート絶縁膜12を得た。次に金を蒸着法により50nm成膜し、ポジレジストを用いてフォトリソグラフィおよびエッチングを行い、その後レジストを剥離することによりソース電極13およびドレイン電極14を形成した。

[0044]

半導体層形成用材料として、テトラリンと6,13・ビス(トリイソプロピルシリルエチニル)ペンタセン(TIPS・ペンタセン)を混合した溶液を用いた。半導体層の形成にはフレキソ印刷法を用いた。フレキソ印刷には感光性樹脂フレキソ版と150線のアニロックスロールを用い、幅100μmのストライプ形状の半導体層を形成した。印刷後、100で60分乾燥させて半導体層15を形成した。

[0045]

続いて保護層16を形成した。保護層形成材料としてフッ素系樹脂を用いた。保護層形成にはフレキソ印刷を用いた。フレキソ版として感光性樹脂フレキソ版を用い、150線アニロックスロールを用いた。ストライプ形状のフレキソ版を用い、半導体層15を覆うように、線幅150μmのストライプ形状の保護層16を印刷した。保護層16の線幅の

10

20

30

40

バラツキは±10μmであった。その後、100 で90分乾燥させて保護層16を形成した。

## [0046]

続いて層間絶縁膜 1 7を形成した。層間絶縁膜形成材料としてエポキシ樹脂を用いた。スクリーン印刷を用いて形成を行い、90 で1時間乾燥させ、層間絶縁膜 1 7とした。層間絶縁膜 1 7 はアレイ全体を覆うように形成され、画素電極 1 8 とドレイン電極 1 4 を導通するための、5 0  $\mu$  m角のビアホール 1 7 a を有する。そのビアホール 1 7 a の中心位置 A は保護層 1 6 のストライプ間の中点を通るストライプに平行な直線 C 上にあったため、保護層 1 6 のストライプ線幅が設計値よりも太くなっている箇所でも、ビアホール部の導通を阻害されることがなかった。

[0047]

[0048]

その後、画素電極18を形成した。画素電極材料として銀ペーストを用いた。画素電極18の形成には、スクリーン印刷を用い、銀ペーストをビアホール17a内に完全に充填させた。パターン形成後、90 で1時間乾燥させることにより、画素電極18とした。

しかる後、対向電極との間に電気泳動媒体 2 0 を挟んで本実施例によるディスプレイを駆動した。保護層 1 6 の線幅バラツキによる線太り(+ 1 0 μm)と、保護層 1 6 のアライメントずれ(左側へ 1 0 μm)および層間絶縁膜 1 7 のアライメントずれ(左側へ 1 0 μm)が発生したが、層間絶縁膜 1 7 のビアホール 1 7 a が保護層 1 6 のストライプ間の中央にあったため、画素電極 1 8 とドレイン電極 1 4 間の導通を図ることができ、点欠陥なく良好な画像表示を行うことができた。

【比較例1】

[0049]

図4、図5に示した形態をとるボトムゲートボトムコンタクト型フレキシブル薄膜トランジスタアレイの製造方法を示す。本トランジスタアレイは1素子サイズ300μm×300μmであり、この素子が240×320個あるものである。

[0050]

プラスチック基板 1 0 としてポリエチレンナフタレート(PEN)フィルムを用い、実施例 1 と同様にゲート電極 1 1、キャパシタ電極 1 9、ゲート絶縁膜 1 2、ソース電極 1 3、ドレイン電極 1 4、半導体層 1 5、保護層 1 6を形成した。

[0051]

層間絶縁膜17の形成には、実施例1と同様の材料および印刷方法を用いた。ただし、画素電極18とドレイン電極14を導通するための50μm角のビアホール17aの中心位置Aは保護層16のストライプ間の中点を通るストライプに平行な直線C上よりも50μm左側にずれた位置となるよう設計されていた。その結果、ビアホール17aの中心が直線C上にあるものに比べ、保護層16と層間絶縁膜17のビアホール17a端部との余白部分は50μm小さくなった。その結果、保護層16の線幅バラツキによる線太りと、保護層16および層間絶縁膜17のアライメントずれによって、保護層16端部と層間絶縁膜17のビアホール17a端部との間隔は一部の保護層16がビアホール部分まではみ出して形成されてしまった。

[0052]

実施例1と同様に、画素電極18を形成し、対向電極との間に電気泳動媒体20を挟んで本実施例によるディスプレイを駆動したところ、保護層16が層間絶縁膜17のビアホール部分まではみ出して形成されてしまった箇所では、画素電極18とドレイン電極14の導通が阻害され、点欠陥が多くなり、良好な表示を行うことができなかった。

【産業上の利用可能性】

[0053]

本発明のフレキシブル薄膜トランジスタは、フレキシブル電子ペーパーや、フレキシブル有機 ELディスプレイ等のスイッチング素子として利用することができる。特に、層間絶縁膜のビアホールの中心位置を、ストライプ形状の保護層間の中点を通る、ストライプ

10

20

30

40

に平行な直線上に形成することにより、製造工程における歩留まりやスループットを向上することができる。アライメントずれ等を考慮すると、ビアホール中心位置とストライプ中点の位置とのずれが40μm以内であれば、ドレイン電極と層間絶縁膜との導通を阻害することなく、保護層を形成することができ、スループットを向上することができる。これによって、フレキシブルディスプレイやICカード、ICタグ等広範囲に応用可能なフレキシブル薄膜トランジスタを低コストかつ高品質に作製することが可能となる。

## 【符号の説明】

## [0054]

10・・・プラスチック基板

11・・・ゲート電極

12・・・ゲート絶縁膜

13・・・ソース電極

14・・・ドレイン電極

15・・・半導体層

16・・・保護層

17・・・層間絶縁膜

17a・・・ビアホール

18・・・画素電極

19・・・キャパシタ電極

20・・・電気泳動媒体

## 【図1】

## 【図2】

10

【図3】

【図4】

【図5】

## フロントページの続き

(51) Int.CI. F I

H 0 1 L 29/78 6 2 6 C H 0 1 L 29/78 6 1 2 C

(56)参考文献 国際公開第2011/122205(WO,A1)

特開2008-270744(JP,A) 特開2010-181785(JP,A) 特開2002-151522(JP,A) 特開2002-268084(JP,A)

国際公開第2013/073495(WO,A1)

特開2012-047776(JP,A)

米国特許出願公開第2009/0026509(US,A1)

(58)調査した分野(Int.CI., DB名)

G 0 9 F 9 / 3 0 - 9 / 4 6 、 H 0 1 L 2 1 / 3 3 6、2 7 / 3 2 、2 9 / 7 8 6