## (19)**日本国特許庁(JP)**

# (12)特許公報(B2)

гт

(11)特許番号 特許第7231340号 (P7231340)

(45)発行日 令和5年3月1日(2023.3.1)

(24)登録日 令和5年2月20日(2023.2.20)

| (51)国際特計分類 | 貝                                | F 1         |          |                      |  |

|------------|----------------------------------|-------------|----------|----------------------|--|

| H 0 1 G    | 4/30 (2006.01)                   | H 0 1 G     | 4/30     | 2 0 1 F              |  |

|            |                                  | H 0 1 G     | 4/30     | 2 0 1 C              |  |

|            |                                  | H 0 1 G     | 4/30     | 3 1 1 D              |  |

|            |                                  | H 0 1 G     | 4/30     | 3 1 1 E              |  |

|            |                                  | H 0 1 G     | 4/30     | 5 1 3                |  |

|            |                                  |             | 請求耳      | 頁の数 19 (全16頁) 最終頁に続く |  |

| (21)出願番号   | 特願2018-107425(P20                | )18-107425) | (73)特許権者 | 000204284            |  |

| (22)出願日    | 平成30年6月5日(2018.6.5)              |             |          | 太陽誘電株式会社             |  |

| (65)公開番号   | )公開番号 特開2019-212746(P2019-212746 |             |          | 東京都中央区京橋二丁目7番19号     |  |

|            | A)                               |             | (74)代理人  | 100087480            |  |

| (43)公開日    | 令和1年12月12日(2019                  | 9.12.12)    |          | 弁理士 片山 修平            |  |

| 審査請求日      | 令和3年2月2日(2021.2.2)               |             | (72)発明者  | 財満 知彦                |  |

|            |                                  |             |          | 東京都中央区京橋二丁目7番19号 太   |  |

|            |                                  |             |          | 陽誘電株式会社内             |  |

|            |                                  |             | (72)発明者  | 笹木 隆                 |  |

|            |                                  |             |          | 東京都中央区京橋二丁目7番19号 太   |  |

|            |                                  |             |          | 陽誘電株式会社内             |  |

|            |                                  |             | (72)発明者  | 松下 邦博                |  |

|            |                                  |             |          | 東京都中央区京橋二丁目7番19号 太   |  |

|            |                                  |             |          | 陽誘電株式会社内             |  |

|            |                                  |             | 審査官      | 鈴木 駿平                |  |

|            |                                  |             |          | 最終頁に続く               |  |

## (54)【発明の名称】 セラミック電子部品およびその製造方法

## (57)【特許請求の範囲】

#### 【請求項1】

セラミックを主成分とする誘電体層が積層され、略直方体形状を有し、対向する2端面と、前記誘電体層の積層方向の上面および下面と、前記2端面、前記上面および前記下面以外の2側面とを有する積層チップと、

前記積層チップの内部に設けられ、前記2側面に引き出された突出部を有する複数の第1内部電極層と、

前記2端面の間において、前記2側面に設けられ、前記突出部と接続された外部電極と、を備え、

前記外部電極は、<u>同一組成の一体物であり、</u>前記2端面を結ぶ方向において、前記突出部に接続されていない領域では薄く形成され、前記突出部に向かって<u>変曲点</u>を有し、前記突出部に接続される領域では厚く形成されていることを特徴とするセラミック電子部品。

## 【請求項2】

前記外部電極において、前記突出部に接続される領域で厚く形成された厚膜部の最大厚みは、6µm以上であることを特徴とする請求項1に記載のセラミック電子部品。

## 【請求項3】

前記外部電極において、前記突出部に接続されていない領域で薄く形成された薄膜部の最大厚みは、3 μ m以下であることを特徴とする請求項1または請求項2に記載のセラミック電子部品。

## 【請求項4】

前記外部電極において、前記<u>変曲点</u>は、前記突出部から第1内部電極層の長手方向の外側に向かって30µmの位置から、前記長手方向の内側に向かって10µmの位置までの範囲に位置していることを特徴とする請求項1から請求項3のいずれか一項に記載のセラミック電子部品。

#### 【請求項5】

セラミックを主成分とする誘電体層が積層され、略直方体形状を有し、対向する2端面と、前記誘電体層の積層方向の上面および下面と、前記2端面、前記上面および前記下面以外の2側面とを有する積層チップと、

前記積層チップの内部に設けられ、前記2端面に引き出された複数の第2内部電極層と、 前記2端面において前記第2内部電極層と接続された外部電極と、を備え、

前記外部電極は、<u>前記2側面を結ぶ方向において、前記第2内部電極層に接続されている全体の領域が、前記第2内部電極層に接続されていない領域よりも厚く形成されている</u>ことを特徴とするセラミック電子部品。

## 【請求項6】

前記外部電極は、前記2側面を結ぶ方向において、前記第2内部電極層に接続されていない領域では前記第2内部電極層に接続される領域より厚さが薄く形成されていることを特徴とする請求項5に記載のセラミック電子部品。

#### 【請求項7】

前記外部電極において、前記第2内部電極層に接続される前記領域である厚膜部と前記第2内部電極層に接続されていない前記領域である薄膜部との間に、<u>変曲点</u>があることを特徴とする<u>請求項5または請求項6に</u>記載のセラミック電子部品。

#### 【請求項8】

前記外部電極において、前記変曲点は、前記第 2 内部電極層の前記 2 側面側の端から前記 2 側面に向かって 3 0 μmの位置から、前記第 2 内部電極層の前記 2 側面側の端から前記 2 側面と反対側に向かって 1 0 μmの位置までの範囲に位置していることを特徴とする請求項 7 に記載のセラミック電子部品。

## 【請求項9】

前記外部電極において、前記第 2 内部電極層に接続される前記領域である厚膜部の厚みが 6  $\mu$  m以上であり、前記第 2 内部電極層に接続されていない前記領域である薄膜部の厚みが 3  $\mu$  m以下であることを特徴とする<u>請求項 5 から請求項 8 のいずれか一項に</u>記載のセラミック電子部品。

### 【請求項10】

前記セラミック電子部品のサイズは、長さが1.0 mmから1.6 mmであり、幅が0.5 mmから0.8 mmであり、高さが0.5 mmから0.7 mmであることを特徴とする<u>請求項5 から請求項9 のいずれか一項に</u>記載のセラミック電子部品。

## 【請求項11】

前記誘電体層は、Ba、Ti、Ca、およびZrを含むことを特徴とする<u>請求項5から</u> <u>請求項10のいずれか一項に</u>記載のセラミック電子部品。

## 【請求項12】

前記積層チップの内部に設けられ、前記2端面に引き出された複数の第2内部電極層と、 前記2端面において前記第2内部電極層と接続された1対の外部電極と、を備え、

前記1対の外部電極は、前記2側面を結ぶ方向において、前記第2内部電極層に接続されていない領域では薄く形成され、前記第2内部電極層に向かって<u>変曲点</u>を有し、前記第2内部電極層に接続される領域では厚く形成されていることを特徴とする<u>請求項1から請求項11のいずれか一項に</u>記載のセラミック電子部品。

## 【請求項13】

<u>前記外部電極は、同一組成の一体物である、請求項5~11のいずれか一項に記載のセラ</u> ミック電子部品。

### 【請求項14】

前記外部電極の上にめっき層が設けられている、請求項1~13のいずれか一項に記載の

10

20

30

- -

40

#### セラミック電子部品。

## 【請求項15】

前記複数の第1内部電極層の少なくとも2つにおいて、前記突出部同士の位置が、前記 2端面を結ぶ方向において互いにずれていることを特徴とする請求項1から請求項4のい ずれか一項に記載のセラミック電子部品。

### 【請求項16】

セラミックを含有し長方形状の誘電体グリーンシート上に前記誘電体グリーンシートの 2長辺の一部に露出するように印刷された内部電極用導電ペーストと、前記内部電極用導 雷ペーストと逆パターンに印刷されたセラミック含有の逆パターンスラリとを備えるパタ ーン形成部が複数積層された略直方体形状のセラミック積層体を用意する工程と、

前記セラミック積層体において、2端面以外であって、前記パターン形成部の積層方向 の上面および下面以外の2側面において、露出した複数の前記内部電極用導電ペーストを 連続して覆うように外部電極用導電ペーストを塗布する工程と、

前記セラミック積層体と前記外部電極用導電ペーストとを焼成する工程と、を含み、

前記焼成する工程前において、前記2側面において、前記逆パターンスラリの積層部に 対する前記外部電極用導電ペーストの濡れ性が、前記内部電極用導電ペーストの積層部に 対する前記外部電極用導電ペーストの濡れ性よりも良いことを特徴とするセラミック電子 部品の製造方法。

#### 【請求項17】

セラミックを含有し長方形状の誘電体グリーンシート上に前記誘電体グリーンシートの 対向する2辺のそれぞれ一部に露出するように印刷された内部電極用導電ペーストと、前 記内部電極用導電ペーストと逆パターンに印刷されたセラミック含有の逆パターンスラリ とを備えるパターン形成部が複数積層された略直方体形状のセラミック積層体を用意する 工程と、

前記セラミック積層体の2端面において、露出した複数の前記内部電極用導電ペースト を連続して覆うように外部電極用導電ペーストを塗布する工程と、

前記セラミック積層体と前記外部電極用導電ペーストとを焼成する工程と、を含み、

前記焼成する工程前において、前記2端面において、前記逆パターンスラリの積層部に 対する前記外部電極用導電ペーストの濡れ性が、前記内部電極用導電ペーストの積層部に 対する前記外部電極用導電ペーストの濡れ性よりも良いことを特徴とするセラミック電子 部品の製造方法。

#### 【請求項18】

前記逆パターンスラリのバインダ含有量が、前記内部電極用導電ペーストのバインダ含 有量よりも多いことを特徴とする<u>請求項16または請求項17に記載の</u>セラミック電子部 品の製造方法。

## 【請求項19】

プラズマ処理によって、前記逆パターンスラリの積層部に対する前記外部電極用導電ペ ーストの濡れ性が、前記内部電極用導電ペーストの積層部に対する前記外部電極用導電ペ ーストの濡れ性よりも良くなるようにすることを特徴とする請求項<u>16または請求項17</u> に記載のセラミック電子部品の製造方法。

【発明の詳細な説明】

#### 【技術分野】

### [00001]

本発明は、セラミック電子部品およびその製造方法に関する。

## 【背景技術】

## [0002]

小型携帯端末などでは、部品の小型化が望まれている。例えば、3端子型積層セラミッ クコンデンサなどのセラミック電子部品は、低ESL特性を有しているため、少ない員数 で所望の性能を実現する。したがって、3端子型積層セラミックコンデンサなどのセラミ ック電子部品(例えば、特許文献1参照)は、省スペース化の要求を満たすことができる。 10

20

30

40

【先行技術文献】

【特許文献】

[0003]

【文献】特開2014-27077号公報

【発明の概要】

【発明が解決しようとする課題】

[0004]

このような3端子型積層セラミックコンデンサなどのセラミック電子部品に対しても、さらなる小型・大容量化が求められている。しかしながら、容量領域の拡大や、積層数の増加は困難となっている。そこで、外部電極を薄くすることで、得られた外形寸法の余裕分を容量領域および積層数の増加に還元することが考えられる。しかしながら、外部電極を薄くしようとすると、耐湿性が低下するおそれがある。

[0005]

本発明は、上記課題に鑑みなされたものであり、耐湿性を維持しつつ外径寸法を抑制することができるセラミック電子部品およびその製造方法を提供することを目的とする。

【課題を解決するための手段】

[0006]

本発明に係るセラミック電子部品は、セラミックを主成分とする誘電体層が積層され、略直方体形状を有し、対向する2端面と、前記誘電体層の積層方向の上面および市面と、前記2端面、前記上面および前記下面以外の2側面とを有する積層チップと、前記電極層と、前記2端面の間において、前記2側面に引き出された突出部を有する複数の第1内部電極層と、前記2端面の間において、前記2側面に設けられ、前記2端面を結ぶ方向において、前記突出部に接続されていない領域では薄く形成され、前記突出部に向かって変曲点を有し、前記突出部に接続される領域では厚く形成されていることを特徴とする。前記外部電極において、前記突出部に接続される領域で厚く形成された厚膜部の最大厚みは、6μm以上であってもよい。前記外部電極において、前記突出部に接続されていない領域で薄く形成された薄膜部の最大厚みは、3μm以下であってもよい。前記外部電極において、前記ののののののののののののののののののののののののののののののののののではあれていののののでは、10000万

[0007]

本発明に係る他のセラミック電子部品は、セラミックを主成分とする誘電体層が積層さ れ、略直方体形状を有し、対向する2端面と、前記誘電体層の積層方向の上面および下面 と、前記2端面、前記上面および前記下面以外の2側面とを有する積層チップと、前記積 層チップの内部に設けられ、前記2端面に引き出された複数の第2内部電極層と、前記2 端面において前記第2内部電極層と接続された外部電極と、を備え、前記外部電極は、前 記2側面を結ぶ方向において、前記第2内部電極層に接続されている全体の領域が、前記 <u>第2内部電極層に接続されていない領域よりも厚く形成されている</u>ことを特徴とする。前\_ <u>記外部電極は、前記2側面を結ぶ方向において、前記第2内部電極層に接続されていない</u> <u>領域では前記第2内部電極層に接続される領域より厚さが薄く形成されていてもよい。</u>前 記外部電極において、前記第2内部電極層に接続される前記領域である厚膜部と前記第2 内部電極層に接続されていない前記領域である薄膜部との間に、変曲点があってもよい。 前記外部電極において、前記変曲点は、前記第2内部電極層の前記<u>2側面</u>側の端から前記 <u>2側面</u>に向かって30μmの位置から、前記第2内部電極層の前記<u>2側面</u>側の端から前記 <u>2側面</u>と反対側に向かって10µmの位置までの範囲に位置していてもよい。前記外部電 極において、前記第2内部電極層に接続される前記領域である厚膜部の厚みが6μm以上 であり、前記第2内部電極層に接続されていない前記領域である薄膜部の厚みが3μm以 下であってもよい。前記セラミック電子部品のサイズは、長さが1.0mmから1.6m mであり、幅が0.5mmから0.8mmであり、高さが0.5mmから0.7mmであ ってもよい。前記誘電体層は、Ba、Ti、Ca、およびZrを含んでいてもよい。上記

10

20

30

40

セラミック電子部品において、前記積層チップの内部に設けられ、前記2端面に引き出された複数の第2内部電極層と、前記2端面において前記第2内部電極層と接続された1対の外部電極と、を備え、前記1対の外部電極は、前記2側面を結ぶ方向において、前記第2内部電極層に接続されていない領域では薄く形成され、前記第2内部電極層に向かって変曲点を有し、前記第2内部電極層に接続される領域では厚く形成されていてもよい。前記外部電極は、同一組成の一体物であってもよい。前記外部電極の上にめっき層が設けられていてもよい。

## [0008]

上記セラミック電子部品において、前記複数の第1内部電極層の少なくとも2つにおいて、突出部同士の位置が、前記2端面を結ぶ方向において互いにずれていてもよい。

[0009]

本発明に係るセラミック電子部品の製造方法は、セラミックを含有し長方形状の誘電体 グリーンシート上に前記誘電体グリーンシートの2長辺の一部に露出するように印刷され た内部電極用導電ペーストと、前記内部電極用導電ペーストと逆パターンに印刷されたセ ラミック含有の逆パターンスラリとを備えるパターン形成部が複数積層された略直方体形 状のセラミック積層体を用意する工程と、前記セラミック積層体において、2端面以外で あって、前記パターン形成部の積層方向の上面および下面以外の2側面において、露出し た複数の前記内部電極用導電ペーストを連続して覆うように外部電極用導電ペーストを塗 布する工程と、前記セラミック積層体と前記外部電極用導電ペーストとを焼成する工程と 、を含み、前記焼成する工程前において、前記2側面において、前記逆パターンスラリに 対する前記外部電極用導電ペーストの濡れ性が、前記内部電極用導電ペーストに対する前 記外部電極用導電ペーストの濡れ性よりも良いことを特徴とする。本発明に係る他のセラ <u>ミック電子部品の製造方法は、セラミックを含有し長方形状の誘電体グリーンシート上に</u> 前記誘電体グリーンシートの対向する2辺のそれぞれ一部に露出するように印刷された内 部電極用導電ペーストと、前記内部電極用導電ペーストと逆パターンに印刷されたセラミ <u>ック含有の逆パターンスラリとを備えるパターン形成部が複数積層された略直方体形状の</u> セラミック積層体を用意する工程と、前記セラミック積層体の2端面において、露出した 複数の前記内部電極用導電ペーストを連続して覆うように外部電極用導電ペーストを塗布 する工程と、前記セラミック積層体と前記外部電極用導電ペーストとを焼成する工程と、 を含み、前記焼成する工程前において、前記2端面において、前記逆パターンスラリの積 層部に対する前記外部電極用導電ペーストの濡れ性が、前記内部電極用導電ペーストの積 <u>層部に対する前記外部電極用導電ペーストの濡れ性よりも良いことを特徴とする。</u>

[0010]

上記セラミック電子部品の製造方法において、前記逆パターンスラリのバインダ含有量を、前記内部電極用導電ペーストのバインダ含有量よりも多くしてもよい。プラズマ処理によって、逆パターンスラリの積層部に対する前記外部電極用導電ペーストの濡れ性が、前記内部電極用導電ペーストの濡れ性より も良くなるようにしてもよい。

## 【発明の効果】

### [0011]

本発明によれば、耐湿性を維持しつつ外径寸法を抑制することができる。

【図面の簡単な説明】

[0012]

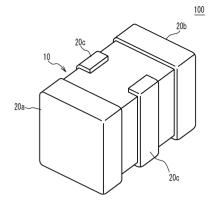

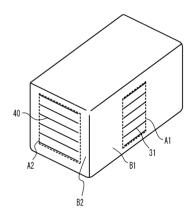

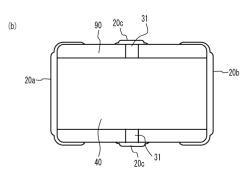

【図1】積層セラミックコンデンサの斜視図である。

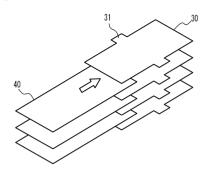

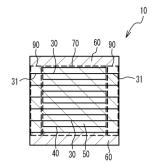

【図2】積層チップの内部における内部電極層の積層構造を例示する図である。

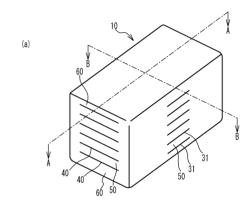

【図3】(a)および(b)は外部電極を透過した状態での積層チップの斜視図である。

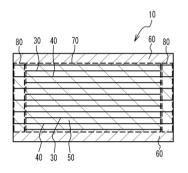

【図4】図3(a)のA-A線断面図である。

【図5】図3(a)のB-B線断面図である。

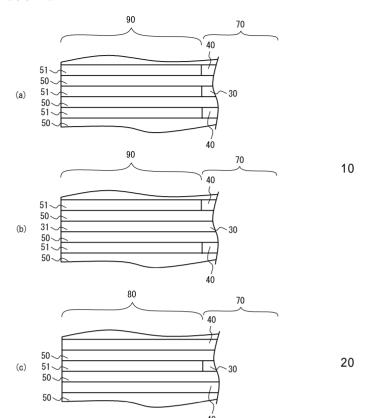

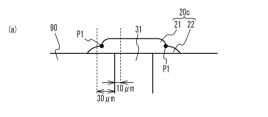

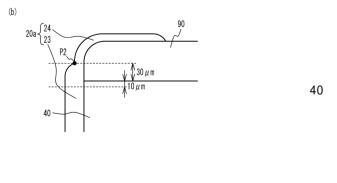

【図 6 】(a)および(b)はサイドマージン領域の断面を拡大したものであり、(c)はエンドマージン領域の断面を拡大したものである。

10

20

30

50

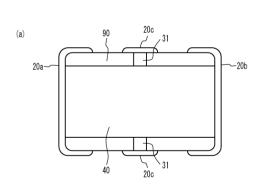

【図7】(a)および(b)は積層セラミックコンデンサを積層方向から透過した図である。

【図8】(a)は外部電極20cを表す図であり、(b)は外部電極20aを表す図である。

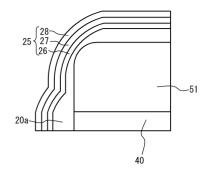

【図9】めっき層を例示する図である。

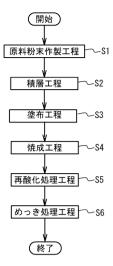

【図10】積層セラミックコンデンサの製造方法のフローを例示する図である。

【図11】(a)は第1パターン形成シート、第2パターン形成シートおよびカバーシートの積層構造を例示する図であり、(b)は突出部の位置ずれについて例示する図である。 【図12】(a)~(f)は外部電極20cに対応する領域に外部電極用導電ペーストを 塗布した場合の図である。

【発明を実施するための形態】

[0013]

以下、図面を参照しつつ、実施形態について説明する。

[0014]

(実施形態)

まず、セラミック電子部品の1例として、積層セラミックコンデンサの概略について説明する。図1は、積層セラミックコンデンサ100の斜視図である。図1で例示するように、積層セラミックコンデンサ100の斜視図である。図1で例示するよる。積層チップ10は、対向する2端面を有する。積層チップ10において、各層の積層方向の上下の面を上面および下面と称する。積層チップ10において、2端面、上面および下面以外の2面を側面と称する。積層チップ10において、2端面、上面およびでででは外部電極20bが設けられている。外部電極20a,20bは、上面、下面および2側面に延在している。ただし、外部電極20a,20bは、下面および2側面にがいて互いに離間している。外部電極20aと外部電極20bとの間において互いに離間して、積層チップ10の下面、小の側面および上面にわたって、外部電極20aおよび外部電極20aおよび外部電極20aおよび外部電極20aおよび外部電極20aおよび外部電極20aおよび外部電極20aおよび外部電極20aおよび外部電極20aおよび外部電極20aおよび外部電極20aおよび外部電極20aおよび外部電極20cが設けられている。これら2つの外部電極20cは、互いに離間している。

[0015]

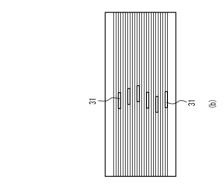

図2は、積層チップ10の内部における内部電極層の積層構造を例示する図である。図2で例示するように、積層チップ10の内部において、第1内部電極層30と第2内部電極層40とが互いに積層されている。第1内部電極層30は、平面視で長方形状を有し、2つの長辺の中央部に突出部31を有する。したがって、第1内部電極層30は、平面視で略十字形状を有している。第2内部電極層40の長辺は、第1内部電極層30の長辺よりも長くなっている。

[0016]

図3(a)は、外部電極20a~20cを透過した状態での積層チップ10の斜視図である。図3(a)で例示するように、積層チップ10の2端面に対して、各第2内部電極層40が露出している。各第2内部電極層40は、外部電極20aおよび外部電極20bの両方に接続されている。積層チップ10の2端面において、第1内部電極層30は露出していない。したがって、第1内部電極層30は、外部電極20a,20bには接続されている。当該2側面において、突出部31は、外部電極20cに接続されている。当該2側面に対して、第2内部電極層40は露出していない。したがって、第2内部電極層40は、外部電極20cには接続されていない。

[0017]

第1内部電極層30と第2内部電極層40との間には、誘電体層50が配置されている。積層チップ10において、積層構造において第1内部電極層30、第2内部電極層40 および誘電体層50の積層方向(以下、積層方向と称する。)の上面および下面は、カバ 10

20

30

40

-層60によって覆われている。

#### [0018]

なお、図3(b)で例示するように、積層チップ10の2側面において、各突出部31が引き出されている領域を覆う領域を第1引出領域A1と称する。当該2側面において、第1引出領域A1の周辺の領域を第1周辺領域B1と称する。積層チップ10の2端面において、各第2内部電極層40が引き出されている領域を覆う領域を第2引出領域A2と称する。当該2端面において、第2引出領域A2の周辺の領域を第2周辺領域B2と称する。

#### [0019]

図4は、図3(a)のA-A線断面図である。図4で例示するように、第1内部電極層30と第2内部電極層40とが対向する領域は、積層セラミックコンデンサ100において電気容量を生じる領域である。そこで、当該領域を、容量領域70と称する。積層チップ10の両端面近傍において第2内部電極層40同士が第1内部電極層30を介さずに対向する領域を、エンドマージン領域80と称する。エンドマージン領域80は、電気容量を生じない領域である。

#### [0020]

図5は、図3(a)のB-B線断面図である。図5で例示するように、積層チップ10において、積層チップ10の2側面から第2内部電極層40に至るまでの領域をサイドマージン領域90と称する。すなわち、サイドマージン領域90は、積層チップ10の2側面側における、第2内部電極層40の端部を覆うように設けられた領域である。サイドマージン領域90においては、第1内部電極層30の突出部31同士が対向しているが、電気容量は生じない。

## [0021]

図6(a)は、サイドマージン領域90の断面を拡大したものである。サイドマージン領域90は、誘電体層50と逆パターン層51とが、積層方向において交互に積層された構造を有する。容量領域70の各誘電体層50とサイドマージン領域90の各誘電体層50とは、互いに連続する層である。この構成によれば、容量領域70とサイドマージン領域90との段差が抑制される。なお、図6(b)で例示するように、第1内部電極層30の突出部31が設けられている領域では、誘電体層50、突出部31、誘電体層50、および逆パターン層51の順に積層が繰り返されている。図6(c)は、エンドマージン領域80の断面(図3(a)のA-A線の方向)を拡大したものである。エンドマージン領域80は、誘電体層50、逆パターン層51、誘電体層50、および第2内部電極層40の順に積層が繰り返されている。この構成によれば、容量領域70とエンドマージン領域80との段差が抑制される。

## [0022]

積層セラミックコンデンサ100のサイズは、例えば、長さ1.0mm、幅0.5mm、高さ0.5mmであり、または長さ1.2mm、幅0.9mm、高さ0.8mmであり、または長さ1.6mm、幅0.8mm、高さ0.7mmであり、または長さ2.0mm、幅1.25mm、高さ1.0mmであり、または長さ3.2mm、幅1.6mm、高さ1.6mmであるが、これらのサイズに限定されるものではない。

## [0023]

10

20

30

40

10

20

30

40

50

)等を用いることができる。逆パターン層 5 1 およびカバー層 6 0 は、セラミック材料を主成分とする。例えば、逆パターン層 5 1 およびカバー層 6 0 の主成分材料は、誘電体層 5 0 の主成分材料と同じである。

## [0024]

図7(a)は、積層セラミックコンデンサ100を、積層方向から透過した図である。積層セラミックコンデンサ100のような3端子型積層セラミックコンデンサは、低ESL特性を有しているため、少ない員数で所望の性能を実現する。したがって、3端子型積層セラミックコンデンサは、省スペース化の要求を満たすことができる。このような3端子型積層セラミックコンデンサに対しても、さらなる小型・大容量化が求められている。しかしながら、容量領域70の拡大や、積層数の増加は困難となっている。そこで、外部電極20a~20cを薄くすることで、得られた外形寸法の余裕分を容量領域70および積層数の増加に還元することが考えられる。しかしながら、外部電極20a~20cを薄くしようとすると、耐湿性が低下するおそれがある。例えば、電圧印加時に、内部電極層と外部電極層との接続界面から、H2が内部に拡散して容量領域70に到達することで耐湿性が低下する。

#### [0025]

そこで、本実施形態においては、図7(b)で例示するように、外部電極20cは、突出部31に接続される領域において厚く形成され、他の領域においては薄く形成されている。すなわち、外部電極20cは、図3(b)で例示した第1引出領域A1において厚く形成され、第1周辺領域B1で薄く形成されている。それにより、積層セラミックコンデンサ100の耐湿性を維持しつつ、外形寸法を抑制することができる。また、外部電極20a,20bは、第2内部電極層40に接続される領域において厚く形成され、他の領域においては薄く形成されていることが好ましい。すなわち、外部電極20a,20bは、図3(b)で例示した第2引出領域A2において厚く形成され、第2周辺領域B2で薄く形成されていることが好ましい。この場合、積層セラミックコンデンサ100の耐湿性をより高く維持しつつ、外形寸法をより抑制することができる。

## [0026]

図8(a)で例示するように、積層方向から見た場合に、積層チップ10の2端面を結ぶ方向において、外部電極20cは、突出部31を覆う厚膜部21と、厚膜部21の周辺の薄膜部22とを備えている。厚膜部21と薄膜部22との境界には、段差(変曲点)P1が設けられている。すなわち、外部電極20cは、突出部31に接続されていない領域では薄く形成されており、変曲点P1から段差を有して厚くなる。例えば、厚膜部21の最大厚みは、6μm以上であることが好ましい。薄膜部22の最大厚みは、3μm以下であることが好ましい。また、変曲点P1は、突出部31から第1内部電極層30の長手方向外側に向かって30μmの位置から、当該長手方向内側に向かって10μmの位置までの範囲に位置していることが好ましい。

## [0027]

図8(b)で例示するように、積層方向から見た場合に、積層チップ10の2側面を結ぶ方向において、外部電極20aは、第2内部電極層40の露出部分を覆う厚膜部23と、厚膜部23の周辺の薄膜部24とを備えていることが好ましい。厚膜部23と薄膜部24との境界には、段差(変曲点)P2が設けられている。すなわち、外部電極20aは、サイドマージン領域90では薄く形成されており、変曲点P2から段差を有して厚くなることが好ましい。例えば、厚膜部23は、6μm以上の厚みを有していることが好ましい。薄膜部24は、3μm以下の厚みを有していることが好ましい。また、変曲点P2は、第2内部電極層40の側面側端から側面に向かって30μmの位置から、第2内部電極層40の側面側端から側面と反対側に向かって10μmの位置までの範囲に位置していることが好ましい。外部電極20bも、外部電極20aと同様の形状を有していることが好ましい。

#### [0028]

外部電極20a~20cは、Cu,Ni,A1(アルミニウム),Zn(亜鉛)などの

金属、またはこれらの2以上の合金(例えば、CuとNiとの合金)を主成分とし、外部電極20a~20cの緻密化のためのガラス成分、外部電極20a~20cの焼結性を制御するための共材、などのセラミックを含んでいる。ガラス成分は、Ba(バリウム),Sr(ストロンチウム),Ca(カルシウム),Zn,Al,Si(ケイ素),B(ホウ素)等の酸化物である。共材は、例えば、誘電体層50の主成分と同じ材料を主成分とするセラミック成分である。

#### [0029]

図9で例示するように、外部電極20aの表面には、めっき層25が設けられていてもよい。めっき層25は、Cu,Ni,Al,Zn,Snなどの金属またはこれらの2以上の合金を主成分とする。めっき層25は、単一金属成分のめっき層でもよく、互いに異なる金属成分の複数のめっき層でもよい。例えば、めっき層25は、外部電極20a側から順に、第1めっき層26、第2めっき層27および第3めっき層28が形成された構造を有する。第1めっき層26は、例えば、Cuめっき層である。第2めっき層27は、例えば、Niめっき層である。第3めっき層28は、例えば、Snめっき層である。外部電極20b,20cにおいても、同様のめっき層が設けられていてもよい。

#### [0030]

本実施形態に係る積層セラミックコンデンサ 1 0 0 においては、外部電極 2 0 c が、突出部 3 1 に接続される領域において厚く形成され、他の領域においては薄く形成されている。それにより、積層セラミックコンデンサ 1 0 0 の耐湿性を維持しつつ、外形寸法を抑制することができる。ところで、複数の突出部 3 1 のうち少なくとも 2 つの位置は、積層チップ 1 0 の 2 端面を結ぶ方向(積層セラミックコンデンサ 1 0 0 の長手方向)において、互いにずれていてもよい。例えば、最大で 1 0 0  $\mu$ m程度、平均的には 5 0  $\mu$ m以内程度のズレが発生することがある。この場合においても、外部電極 2 0 c が、各突出部 3 1 に接続される領域において厚く形成され、他の領域においては薄く形成されていることが好ましい。

## [0031]

続いて、積層セラミックコンデンサ 1 0 0 の製造方法について説明する。図 1 0 は、積層セラミックコンデンサ 1 0 0 の製造方法のフローを例示する図である。

## [0032]

### (原料粉末作製工程)

まず、誘電体層 5 0 の主成分であるセラミック材料の粉末に、目的に応じて所定の添加化合物を添加する。添加化合物としては、Mg(マグネシウム),Mn(マンガン),V(バナジウム),Cr(クロム),希土類元素(Y(イットリウム),Sm(サマリウム),Eu(ユウロピウム),Gd(ガドリニウム),Tb(テルビウム),Dy(ジスプロシウム),Ho(ホロミウム),Er(エルビウム),Tm(ツリウム)およびYb(イッテルビウム))の酸化物、並びに、Co(コバルト),Ni,Li(リチウム),B,Na(ナトリウム),K(カリウム)およびSiの酸化物もしくはガラスが挙げられる。例えば、まず、セラミック材料の粉末に添加化合物を含む化合物を混合して仮焼を行う。続いて、得られたセラミック材料の粒子を添加化合物とともに湿式混合し、乾燥および粉砕してセラミック材料の粉末を調製する。

## [0033]

## (積層工程)

次に、得られたセラミック材料の粉末に、ポリビニルブチラール(PVB)樹脂等のバインダと、エタノール、トルエン等の有機溶剤と、可塑剤とを加えて湿式混合する。得られたスラリを使用して、例えばダイコータ法やドクターブレード法により、基材上に例えば厚み 0 .8 μ m 以下の帯状の誘電体グリーンシートを塗工して乾燥させる。誘電体グリーンシートは、後述する焼成工程によって誘電体層 5 0 となるシートである。

## [0034]

次に、誘電体グリーンシートの表面に、内部電極用導電ペーストをスクリーン印刷、グラビア印刷等により印刷することで、第1内部電極層30に対応する第1パターンおよび

10

20

30

第2内部電極層40に対応する第2パターンを配置する。内部電極用導電ペーストは、第1内部電極層30および第2内部電極層40の主成分金属の粉末と、バインダと、溶剤と、必要に応じてその他助剤とを含んでいる。また、内部電極用導電ペーストには、共材として、誘電体層50の主成分であるセラミック材料を分散させてもよい。次に、原料粉末作製工程で作製されたセラミック材料の粉末に、ポリビニルブチラール(PVB)樹脂等のバインダと、エタノール、トルエン等の有機溶剤と、可塑剤とを加えて湿式混合する。得られたスラリを、誘電体グリーンシート上において、第1パターンおよび第2パターンと逆パターンに、第1逆パターンスラリおよび第2逆パターンスラリとして印刷する。それにより、第1パターンおよび第2パターンを有するシートが形成される。第1逆パターンスラリおよび第2逆パターンスラリおよび第2逆パターンを有するシートが形成される。第1逆パターンスラリおよび第2逆パターンスラリは、後述する焼成工程によって逆パターン層51となる。

## [0035]

次に、第1パターンおよび第2パターンを有するシートを所定の大きさに打ち抜いて、打ち抜かれたシートを、基材を剥離した状態で、所定層数(例えば200~500層)だけ第1パターンと第2パターンとが交互に重なるように積層する。積層したシートの上下にカバー層60となるカバーシートを圧着させ、所定チップ寸法(例えば1.0mm×0.5mm)にカットする。これにより、略直方体形状のセラミック積層体が得られる。なお、カバーシートも、原料粉末作製工程で作製されたセラミック材料の粉末に、ポリビニルブチラール(PVB)樹脂等のバインダと、エタノール、トルエン等の有機溶剤と、可塑剤とを加えて湿式混合し、印刷することで作製することができる。

### [0036]

上述した変曲点 P 1 や段差の角度は、図 3 ( b )で例示した第 1 引出領域 A 1 の濡れ性と第 1 周辺領域 B 1 の濡れ性との差に応じて決まる関数である。上述した変曲点 P 2 や段差の角度は、図 3 ( b )で例示した第 2 引出領域 A 2 の濡れ性と第 2 周辺領域 B 2 の濡れ性との差に応じて決まる関数である。そこで、積層工程で得られるセラミック積層体において、第 1 引出領域 A 1、第 1 周辺領域 B 1、第 2 引出領域 A 2、および第 2 周辺領域 B 2 に対応する箇所におけるバインダ量を調整してもよい。ここでのバインダ量とは、誘電体グリーンシート、第 1 逆パターンスラリ、第 2 逆パターンスラリ、もしくは内部電極用導電ペーストに対する体積%または重量%である。

### [0037]

例えば、バインダの露出量が多い面では、外部電極用導電ペーストの濡れ性が良くなる。したがって、バインダの露出量が多い面では、外部電極用導電ペーストが薄くなる。一方、バインダの露出量が少ない面では、外部電極用導電ペーストの濡れ性が悪くなる。したがって、バインダの露出量が少ない面では、外部電極用導電ペーストが厚くなる。そこで、第1逆パターンスラリのバインダ量を、内部電極用導電ペーストのバインダ量よりも多くしてもよい。接触角の観点からすると、積層工程で得られるセラミック積層体において、第1引出領域A1に対応する領域の接触角が、第1周辺領域B1に対応する領域の接触角+15°を上回ることが好ましい。

### [0038]

# (塗布工程)

次に、セラミック積層体において、外部電極 2 0 a ~ 2 0 c に対応する領域に、共材を含む外部電極用導電ペーストを塗布する。具体的には、セラミック積層体において、第 2 パターンが露出する 2 端面のそれぞれを覆うように外部電極ペーストを塗布する。さらに、セラミック積層体の各側面において、露出した複数の第 1 パターンを連続して覆うように外部電極ペーストを塗布する。外部電極用導電ペーストの厚みは、外部電極用導電ペーストを希釈することで調整することができる。

### [0039]

## ( 焼成工程)

その後、セラミック積層体を、 2 0 0 ~ 3 0 0 の N <sub>2</sub> 雰囲気中で脱バインダした後に、還元雰囲気中で 1 1 0 0 ~ 1 3 0 0 で 1 0 分~ 2 時間焼成することで、各化合物が焼

10

20

30

結する。このようにして、内部に焼結体からなる第1内部電極層30、第2内部電極層4 0、および誘電体層50が積層されてなる積層チップ10と、積層方向上下の最外層とし て形成されるカバー層60とを有する積層セラミックコンデンサ100が得られる。

#### [0040]

(再酸化処理工程)

その後、N<sub>2</sub>ガス雰囲気中で600~1000 で再酸化処理を行ってもよい。

#### [0041]

(めっき処理工程)

その後、電解めっき等の湿式めっきによって、外部電極20a~20c上にめっき層25を形成する。例えば、第1めっき層26、第2めっき層27および第3めっき層28を順に形成する。

### [0042]

本実施形態に係る製造方法によれば、外部電極20cは、第1内部電極層30に接続される領域において厚く形成され、他の領域においては薄く形成される。それにより、積層セラミックコンデンサ100の耐湿性を維持しつつ、外形寸法を抑制することができる。また、外部電極20a,20bにおいても、第2内部電極層40に接続される領域において厚く形成され、他の領域においては薄く形成される。それにより、積層セラミックコンデンサ100の耐湿性を維持しつつ、外形寸法をより抑制することができる。

## [0043]

また、本実施形態に係る製造方法によれば、積層チップ10の2端面を結ぶ方向(積層セラミックコンデンサ100の長手方向)において各突出部31の位置が互いにずれていても、突出部31を覆う外部電極20cを厚くすることができる。以下、その理由について説明する。

#### [0044]

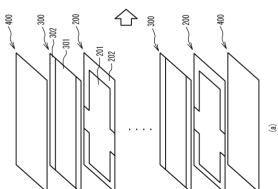

図11(a)は、第1パターン形成部200、第2パターン形成部300およびカバーシート400の積層構造を例示する図である。図11(a)で例示するように、第1パターン形成部200では、第1内部電極層30に対応する第1パターン201と、逆パターン層51に対応する第1逆パターンスラリ202とが形成されている。第2パターン形成部300では、第2内部電極層40に対応する第2パターン301と、逆パターン層51に対応する第2逆パターンスラリ302とが形成されている。なお、図11(a)においては、誘電体グリーンシートについては図示を省略している。

#### [0045]

積層工程において、各シートに位置ずれが生じる場合がある。この場合、図11(b)で例示するように、積層チップ10の2端面を結ぶ方向(積層セラミックコンデンサ10 0の長手方向)において、突出部31の位置にバラツキが生じる。

## [0046]

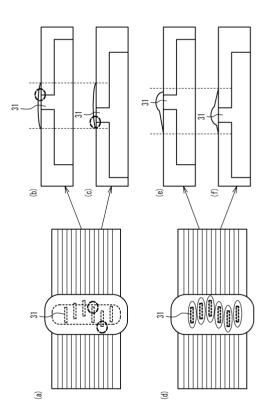

図12(a)は、この場合において、外部電極20cに対応する領域に外部電極用導電ペーストを塗布した場合の図である。図12(b)で例示するように、突出部31の位置がずれていない層では、突出部31が外部電極用導電ペーストの中央部に位置するようになる。この場合、当該突出部31を覆う外部電極用導電ペーストは十分な厚みを有する。一方、図12(c)で例示するように、突出部31の位置が大きくずれた層では、突出部31が外部電極用導電ペーストの端部に位置するようになる。この場合、当該突出部31を覆う外部電極用導電ペーストの厚みが不足する。それにより、突出部31を覆う外部電極20cの厚みが不足し、耐湿性を悪化させる箇所が現れる。

#### [0047]

これに対して、図12(d)で例示するように、本実施形態において外部電極20cに対応する領域に外部電極用導電ペーストを塗布した場合の図である。本実施形態においては、積層工程で得られたセラミック積層体において、外部電極用導電ペーストの内部電極露出部分の濡れ性が周辺領域の濡れ性よりも悪くなっている。それにより、図12(e)および図12(f)で例示するように、突出部31の位置が大きくずれた層でも、突出部

10

20

30

40

3 1 を覆う外部電極用導電ペーストが十分な厚みを有する。それにより、突出部 3 1 を覆う外部電極 2 0 c を十分に厚くすることができる。

#### [0048]

#### (変形例)

上記製造方法においては、内部電極用導電ペーストの露出部に対する外部電極用導電ペーストの濡れ性を調整するために、バインダの露出量を調整したが、それに限られない。例えば、積層工程で得られるセラミック積層体の2側面において露出する内部電極用導電ペーストにプラズマ処理を行うことで、内部電極用導電ペーストの露出部に対する外部電極用導電ペーストの濡れ性が悪くなるように調整してもよい。または、プラズマ処理を行うことで、内部電極用導電ペーストの露出部の周辺に対する外部電極用導電ペーストの濡れ性が良くなるように調整してもよい。

### [0049]

以上、本発明の実施例について詳述したが、本発明は係る特定の実施例に限定されるものではなく、特許請求の範囲に記載された本発明の要旨の範囲内において、種々の変形・変更が可能である。

### 【符号の説明】

### [0050]

- 10 積層チップ

- 20a,20b,20c 外部電極

- 2 1 厚膜部

- 2 2 薄膜部

- 2 3 厚膜部

- 2 4 薄膜部

- 25 めっき層

- 26 第1めっき層

- 27 第2めっき層

- 28 第3めっき層

- 30 第1内部電極層

- 3 1 突出部

- 40 第2内部電極層

- 5 0 誘電体層

- 60 カバー層

- 70 容量領域

- 80 エンドマージン領域

- 90 サイドマージン領域

- 100 積層セラミックコンデンサ

10

20

30

【図面】

【図2】

10

20

【図3】

【図4】

(b)

30

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

40

10

20

## フロントページの続き

(51)国際特許分類

FΙ

H 0 1 G 4/30 5 1 7 H 0 1 G 4/30 5 5 0

(56)参考文献 特開2018-067562(JP,A)

特開平 1 0 - 0 2 2 1 6 4 ( J P , A ) 特開 2 0 1 8 - 1 7 0 3 2 2 ( J P , A ) 特開昭 5 8 - 0 2 1 8 1 3 ( J P , A )

特開2001-126951(JP,A)

(58)調査した分野 (Int.Cl., DB名)

H 0 1 G 4 / 0 0 - 4 / 2 2 4 H 0 1 G 4 / 2 5 5 - 4 / 4 0 H 0 1 G 1 3 / 0 0 - 1 3 / 0 6