(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

FL

(11) 特許番号

特許第4140886号 (P4140886)

(45) 発行日 平成20年8月27日(2008.8.27)

(24) 登録日 平成20年6月20日(2008.6.20)

(51) Int. Cl.

HO1L 27/10 (2006.01)

HO1L 27/10 431 HO1L 27/10 451

請求項の数 9 (全 20 頁)

(21) 出願番号 特願2002-263591 (P2002-263591)

(22) 出願日 平成14年9月10日 (2002. 9.10) (65) 公開番号 特開2003-142654 (P2003-142654A)

(43) 公開日 平成15年5月16日 (2003. 5. 16) 審査請求日 平成16年9月7日 (2004. 9. 7)

(31) 優先権主張番号 09/951,378

(32) 優先日 平成13年9月14日 (2001.9.14)

(33) 優先権主張国 米国(US)

|(73)特許権者 398038580

ヒューレット・パッカード・カンパニー HEWLETT-PACKARD COM

PANY

アメリカ合衆国カリフォルニア州パロアルト ハノーバー・ストリート 3000

||(74) 代理人 | 100081721

弁理士 岡田 次生

(74)代理人 100105393

弁理士 伏見 直哉

|(74)代理人 100111969

弁理士 平野 ゆかり

最終頁に続く

(54) 【発明の名称】 デュアル・トンネル接合メモリ・セルを有するメモリ・デバイス

## (57)【特許請求の範囲】

【請求項1】

第1の電極と、第2の電極と、該第1の電極および該第2の電極の間に形成された誘電体とからなる第1のトンネル接合と、

前記第1のトンネル接合と直列の第2のトンネル接合であって、前記第1の電極と、第 3の電極と、該第1の電極および該第3の電極の間に形成された誘電体とからなる第2の トンネル接合と、を備え、

前記第1のトンネル接合は、<u>前記第2のトンネル接合よりも低い破壊電圧を有し、書き込み電流または書き込み電圧が印加された時に、前記第2のトンネル接合が短絡されない</u>状態のままで、該第1のトンネル接合は、所定の抵抗値を有する第1の抵抗状態から短絡 状態に変化する、

メモリ・セル。

【請求項2】

第1の電極と、第2の電極と、該第1の電極および該第2の電極の間に形成された誘電体とからなる第1のトンネル接合と、

前記第1のトンネル接合と直列の第2のトンネル接合であって、前記第1の電極と、第 3の電極と、該第1の電極および該第3の電極の間に形成された誘電体とからなる第2の トンネル接合と、を備え、

前記第1のトンネル接合は、<u>前記第2のトンネル接合よりも高い抵抗を有し、書き込み</u> 電流が印加された時に、前記第2のトンネル接合が短絡されない状態のままで、該第1の

トンネル接合は、所定の抵抗値を有する第1の抵抗状態から短絡状態に変化する、

メモリ・セル。

## 【請求項3】

前記第1のトンネル接合のトンネリング領域は、前記第2のトンネル接合のトンネリング 領域よりも小さい、

請求項1または2に記載のメモリ・セル。

#### 【 請 求 項 4 】

前記第1のトンネル接合の前記誘電体は、不均一な厚さを有する、

請求項1または2に記載のメモリ・セル。

#### 【請求項5】

10

前記第1のトンネル接合の前記誘電体は、該第1のトンネル接合のトンネリング領域を画 定する特徴形状を含む、

請求項1または2に記載のメモリ・セル。

## 【請求項6】

メモリ・セルのアレイと、

前記メモリ・セルに接続された複数のワード線と、

前記メモリ・セルに接続された複数のビット線と、を備えるメモリ・アレイであって、

前記ワード線は、該メモリ・セルにおいて前記ビット線と交差しており、

前記メモリ・セルのそれぞれは、さらに、

第1の電極と、第2の電極と、該第1の電極および該第2の電極の間に形成された誘電 体とからなる第1のトンネル接合と、

前記第1のトンネル接合に直列の第2のトンネル接合であって、前記第1の電極と、第3の電極と、該第1の電極および該第3の電極の間に形成された誘電体とからなる第2のトンネル接合と、を備え、

前記第1のトンネル接合は、<u>前記第2のトンネル接合よりも低い破壊電圧を有し、書き込み電流または書き込み電圧が印加された時に、前記第2のトンネル接合が短絡されない状態のままで、該第1のトンネル接合は、所定の抵抗値を有する第1の抵抗状態から短絡状態に変化する、</u>

メモリ・アレイ。

## 【請求項7】

30

40

50

20

メモリ・セルのアレイと、

前記メモリ・セルに接続された複数のワード線と、

前記メモリ・セルに接続された複数のビット線と、を備えるメモリ・アレイであって、

前記ワード線は、該メモリ・セルにおいて前記ビット線と交差しており、

前記メモリ・セルのそれぞれは、さらに、

第1の電極と、第2の電極と、該第1の電極および該第2の電極の間に形成された誘電体とからなる第1のトンネル接合と、

前記第1のトンネル接合に直列の第2のトンネル接合であって、前記第1の電極と、第 3の電極と、該第1の電極および該第3の電極の間に形成された誘電体とからなる第2の トンネル接合と、を備え、

前記第1のトンネル接合は、<u>前記第2のトンネル接合よりも高い抵抗を有し、書き込み</u> 電流が印加された時に、前記第2のトンネル接合が短絡されない状態のままで、該第1の トンネル接合は、所定の抵抗値を有する第1の抵抗状態から短絡状態に変化する、

メモリ・アレイ。

#### 【請求項8】

前記第1のトンネル接合のトンネリング領域は、前記第2のトンネル接合のトンネリング 領域よりも小さい、

請求項6または7に記載のメモリ・アレイ。

## 【請求項9】

前記第1のトンネル接合の前記誘電体は、不均一な厚さを有しており、さらに、該第1の

トンネル接合の該誘電体は、該第1のトンネル接合のトンネリング領域を画定する特徴形状を有する、

請求項6または7に記載のメモリ・アレイ。

### 【発明の詳細な説明】

[00001]

## 【発明の属する技術分野】

この発明は、データを記憶するメモリ・デバイスに関し、より具体的には、直列のトンネル接合を備えたメモリ・セルを有するメモリ・デバイスに関する。

#### [00002]

#### 【従来の技術】

民生の電子製品において、該製品によって使用される命令などのデータを記憶するのにメモリ・デバイスが使用される。不揮発性メモリ・デバイスは、データを保持するのに電力を必要としないので望ましい。したがって、不揮発性メモリ・デバイスに記憶されたデータは、電源が消耗しつくされたりメモリ・デバイスから切断されたりしたときでも維持される。また、消費者は、ボリュームが小さくかつ低価格の製品を好み、不揮発性、高密度および低価格の要件は、メモリ・デバイスの設計上の主な決定要因である。また、より小さい電源を使用するほど民生電子製品のサイズを小さくすることができるので、消費電力が少ないことが望ましい。

#### [0003]

不揮発性メモリ・デバイスは、一般に、ワンタイム・プログラム可能(OTP)または再プログラム可能なメモリ・セルを有する。再プログラム可能なメモリ・セルは、2値状態の間で切り替えることができる。OTPメモリ・セルの状態は、一端セルがプログラムされた後は恒久的なものとなる。OTPメモリ・デバイスは、一般に、ヒューズ、アンチヒューズ、電荷蓄積、またはマスク読み取り専用メモリ(マスクROM)として分類されることができる。

## [0004]

ヒューズ・メモリ・セルは、プログラミング中にセルが「飛ばされる」ように、セルの両端に大きな電圧を印加することによってプログラムされる。ヒューズ・メモリ・セルの2値状態は、読み取りプロセス中に測定されるセル両端の抵抗として検出されることができる。ヒューズ・メモリ・デバイスは、ヒューズ・メモリ・セルをプログラムするために大きい電流が必要になるので、あまり普及していない。プログラミング電流が大きいと、大きい駆動トランジスタを有する高圧電源または電荷ポンプ回路が必要とされる。また、ヒューズ・メモリ・セルは、それぞれのヒューズ要素に必要なコンタクト領域のために、基板の大きな領域を占める。セル・サイズが大きいと、アレイ密度が低下し、ヒューズ・メモリ・デバイスのサイズが大きくなる。

### [0005]

ヒューズ・メモリ・セルは、ダイオードやトランジスタなどの分離素子を含むことが多く、これにより、セル・サイズがさらに大きくなる。ヒューズ・メモリ・セル内に使用される分離ダイオードおよびトランジスタは、電流性能が制限されており、メモリ・セルをプログラムするのに必要な大きい書き込み電流によって損傷されることがある。さらに、絶縁ダイオードおよびトランジスタは、一般にシリコン・ベースの能動素子であり、これは、シリコン結晶基板上に最も容易に形成される。この種の分離素子は、多層のヒューズのTPアレイの積み重ねを含まず、よって可能なアレイ密度を低下させる。微結晶および非晶質のダイオードおよびトランジスタなどの他のシリコン・ベースの分離素子は、積み重ね(スタック)を可能にするが、製作の複雑さおよびコストを増やす。最後に、ヒューズ・メモリ・セルは、破壊しきい値分布が広いという特徴がある。破壊しきい値分布が広いということは、セルをプログラムするために書き込み電流の大きな変化を必要とすることを意味する。一般に、広い破壊しきい値分布を考慮するためには、書き込み電流を大きくしなければならない。

#### [0006]

10

20

30

従来のアンチヒューズ・メモリ・セルは、一般に、金属・誘電体・金属のスタックを含む。従来のアンチヒューズ・メモリ・セルは、セルの両端に大きい書き込み電位を印加することによってプログラムされる。この書き込み電位は、アンチヒューズをトリガし、プログラムされたメモリ・セルの両端の抵抗を小さくする。従来のアンチヒューズ・メモリ・セルには、ヒューズ/トランジスタ・セルと同じ多数の欠点がある。例えば、従来のアンチヒューズ・メモリ・セルは、高い書き込み電位を必要とし、シリコン・ベースの能動分離素子を必要とすることがある。

## [0007]

一般の電荷蓄積メモリは、EPROMである。EPROMメモリは、ファウラー=ノルトハイム・トンネル効果(Fowler-Nordheim tunneling)を利用して、基板からメモリ・セル内のフローティング・ゲートに電荷を送る。EPROMメモリは、高い書き込み電圧を必要とし、EPROM素子の書き込み速度は、トンネル電流密度によって制限される。

#### [00008]

マスクROMメモリは、ユーザ・レベル(「フィールド・プログラミング」)でではなく製造時にプログラムされる。したがって、マスクROM素子の各バッチは、アプリケーション(用途)固有である。ほとんどの製造プロセスに見られるように、コストの削減は量を増やすことにより実現される。したがって、マスクROMの生産のコスト効率を高めるためには、アプリケーション固有のメモリに大きな需要がなければならない。大規模な処理を求めるこの要件により、多くのアプリケーションにとってマスクROMは高価になりすぎる。

#### [0009]

## 【発明が解決しようとする課題】

したがって、高密度配列が可能なメモリ・セルを有する低コストのメモリ・デバイスが必要とされている。また、高速処理が可能で過度の処理電力を必要としないメモリ・デバイスが必要とされている。

## [0010]

## 【課題を解決するための手段】

第1の側面によると、メモリ・デバイスは、第1のトンネル接合と、第1のトンネル接合と直列な第2のトンネル接合とを有するデュアル・トンネル接合メモリ・セルを含む。第1のトンネル接合を、第1の抵抗状態から第2の抵抗状態に変化させることができる。メモリ・セルは、メモリ・デバイスのデータ記憶要素であり、この2つの抵抗状態は、メモリ・セルの2値状態を表す。第1と第2のトンネル接合は、異なるアンチヒューズ特性を有し、第2のトンネル接合抵抗が実質的に変化しないままで第1のトンネル接合が短絡されるように、メモリ・セルをプログラムすることができる。

## [0011]

第1の側面によれば、第1のトンネル接合が短絡された場合、第2のトンネル接合は、プログラムされたメモリ・セルの分離機能を提供する。したがって、メモリ・デバイス内のメモリ・セルを分離(絶縁)するために、シリコン・ベースの能動的な分離ダイオードおよび / またはトランジスタが不要となる。したがって、メモリ・デバイスは、スタック型のメモリ要素を含むことができ、アレイ密度を高めることができる。

## [0012]

また、第1の側面によれば、トンネル接合メモリ・セルは、ダイオード / トランジスタの分離素子を有する従来のメモリ・セルよりも小さい。この側面により、さらに、アレイ密度が向上する。また、ダイオード / トランジスタの分離素子が無いので、メモリ・デバイスの製造が単純になる。

## [0013]

第2の側面によれば、メモリ・セルに書き込み電流を印加することによって、選択された メモリ・セルをプログラムすることができる。第1のトンネル接合の抵抗を、第2のトン ネル接合の抵抗よりも高くして、書き込み電流が印加されたときに、第1のトンネル接合 の両端に高い電圧が生成されるようにすることができる。 20

10

30

40

20

30

40

50

#### [0014]

第2の側面によれば、第1のトンネル接合の両端の高い電圧は、第1のトンネル接合の破壊電圧を超えることができ、選択されたセルをプログラムするのに使用されることができる。第1のトンネル接合のトンネリング領域を減少させ、誘電体内にあり得る欠陥領域を有利に減少させることによって、第1のトンネル接合の抵抗を増やすことができる。該あり得る欠陥が減少するので、メモリ・デバイスの電圧/電流プログラミング分布(破壊しきい値分布)が小さくなり、それによりメモリ・デバイスの電力要件が低減する。

## [0015]

本発明の第3の側面によると、第1のトンネル接合の破壊電圧を超える書き込み電圧を印加することによって、デュアル・トンネル接合メモリ・セルをプログラムすることができる。第1のトンネル接合の破壊電圧は、第1のトンネル接合内の誘電体を形成するのに使用される材料とその厚さによって決定されることができる。

#### [0016]

第3の側面によれば、トンネル接合のプログラミング電圧は、誘電層の破壊電圧を低下させることによって低下させることができる。したがって、プログラミング電圧を、従来のアンチヒューズ素子よりも低くすることができる。プログラミング電圧が低いと、メモリ・デバイス内の書き込み回路を小さくし、消費電力を少なくすることができる。

### [0017]

第4の側面によれば、不均一な厚さを有する第1のトンネル接合に誘電体を設けることによって、第1のトンネル接合の破壊しきい値分布を小さくすることができる。この不均一な厚さは、誘電体内に特徴形状を形成することによって確立されることができ、この場合、書き込みプロセス中、トンネル効果は該特徴形状において生じる。

## [0018]

第4の側面によれば、特徴形状は、誘電体の薄い領域に作られることができ、これにより、第1のトンネル接合の破壊電圧を低くすることができる。また、特徴形状は、第1のトンネル接合に比較的小さいトンネリング領域を提供し、これにより、メモリ・デバイスの破壊しきい値分布を小さくする。

#### [0019]

他の側面および利点は、図と関連して行われる以下の詳細な説明から明らかになるであろう。詳細な説明は、同じ番号が同じ要素を示す図面を参照する。

### [0020]

## 【発明の実施の形態】

好ましい実施形態および図面によって、デュアル・トンネル接合メモリ・セルを有するメ モリ・デバイスについて説明する。

## [0021]

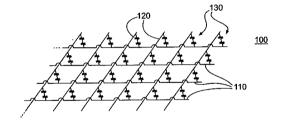

図1は、デュアル・トンネル接合メモリ・セル130を有するメモリ・アレイ100の回路の斜視図である。このメモリ・アレイ100において、ワード線110が横の行に延び、ビット線120が縦の列に延びる。ワード線110は、メモリ・セル130においてビット線120と交差する。各メモリ・セル130は、「1」または「0」の2値状態を記憶することができる。図1において、デュアル・トンネル接合メモリ・セル130は、2つの抵抗型素子として象徴的に示されている。各抵抗型素子は、メモリ・セル130内のトンネル接合に対応する。

## [0022]

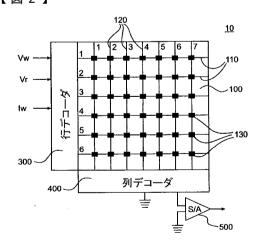

図 2 は、図 1 に示したようなメモリ・アレイ 1 0 0 と、関連する読み書き回路とを含むメモリ・デバイス 1 0 の概略図である。メモリ・デバイス 1 0 は、メモリ・アレイ 1 0 0 、メモリ・アレイ 1 0 0 の行 1 ~ 6 に結合された行デコーダ 3 0 0、メモリ・アレイ 1 0 0 の列 1 ~ 7 に結合された列デコーダ 4 0 0、および読み取りプロセス中にメモリ・セル 1 3 0 の 2 値状態を検出するセンス・アンプ 5 0 0 を含む。図 2 において、説明のために、4 2 個のメモリ・セル 1 3 0 で交差する 6 つの行のワード線 1 1 0 と 7 つの列のビット線 1 2 0 が示されている。実際には、例えば 1 0 2 4 × 1 0 2 4 個以上のメモリ・セルのア

20

30

40

50

レイを使用することができる。

## [0023]

行デコーダ300は、書き込みプロセス中に選択されたメモリ・セル130を含む行に、書き込み電圧Vwまたは書き込み電流Iwを選択的に印加したり、読み取りプロセス中に読み取り電位Vrを印加したりするための複数のスイッチを含む。同様に、列デコーダ400は、書き込みプロセス中に選択されたメモリ・セル130を含む選択された列をアースに接続したり、読み取りプロセス中に選択された列をセンス・アンプ500に接続したりするための複数のスイッチを含むことができる。

## [0024]

選択されたメモリ・セル130をプログラムし、すなわちそれに「書き込む」ために、行デコーダ300は、書き込み電圧Vwまたは書き込み電流Iwと、選択された列のワビット線110との間のスイッチを閉じる。書き込み電圧Vwか書き込み電流Iwかの選択に、メモリ・アレイ100に含まれるデュアル・トンネル接合メモリ・セル130の種類に依存することがある。選択されたメモリ・セル130に印加される書き込み電圧Vwは書き込み電圧Vwは言き込み電圧Vwは言き込み電圧Vwは言き込み電圧Vwは合きにより、選択されたメモリ・セル130の第1のトンネル接合を絶縁すなわち「飛ばす(blow)」のに十分であり、これにより、選択されたメモリ・セル130の両端の抵抗を変化させる。書き込み電圧Vwまたは書き込み電流Iwは、メモリ・セル130の第2のトンネル接合は、実質的に、その書き込み前の抵抗を維持するとができ、プログラムされたメモリ・セル130の分離素子として機能する。メモリ・セル130と書き込みプロセスの実施形態については、後で詳しく説明する。

## [0025]

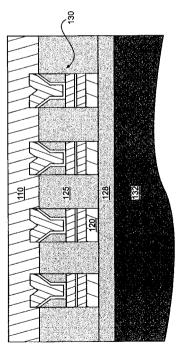

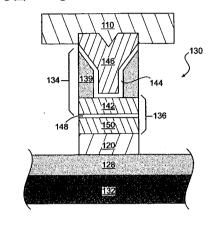

図3 A は、図1 に示したメモリ・アレイ100の実施形態の一部を示す断面図であり、メモリ・セル130の実施形態を含む。図3 B は、メモリ・アレイ100の一部の上面図である。図3 C は、図3 A に示したようなメモリ・セル130の側面図である。

#### [0026]

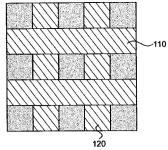

図 3 A および 3 B 参照すると、メモリ・アレイ 1 0 0 の図示される部分は、ワード線 1 1 0 とビット線 1 2 0 の交点に配置された複数のメモリ・セル 1 3 0 を含む。ビット線 1 2 0 は、メモリ・アレイ 1 0 0 の基板 1 3 2 上に配置された絶縁層 1 2 8 上に配置される。絶縁層 1 2 8 は、例えば、SiO $_{\times}$ 、SiО $_{\times}$ 、SiО $_{\times}$ 、N $_{y}$ 、 A 1 O  $_{\times}$ 、 TaO $_{\times}$ 、 TiO $_{\times}$ 、 A 1 N  $_{\times}$ 、 および他の非導電材料であることができる。基板 1 3 2 は、例えば半導体基板である。基板 1 3 2 は電子回路を含むことができ、絶縁層 1 2 8 は、回路とメモリ・セル 1 3 0 の間を絶縁する。代替的に、ビット線 1 2 0 は、基板 1 3 2 のすぐ上に配置されてもよい。絶縁層 1 2 8 上のメモリ・セル 1 3 0 間に、絶縁体 1 2 5 が配置される。絶縁体 1 2 5 は、説明のため図 3 B には示されていない。絶縁体 1 2 5 は、例えば、SiO $_{\times}$ 、SiO $_{\times}$ 、SiO $_{\times}$ 、N $_{y}$ 、 A 1 O  $_{\times}$ 、 TiO $_{\times}$ 、 A I N  $_{\times}$ 、 および他の非導電材料である。

## [0027]

図3Cを参照すると、メモリ・セル130は、第1のトンネル接合134と、該第1のトンネル接合134に直列な第2のトンネル接合136とを含む。第1のトンネル接合134は、第2のトンネル接合136と異なるアンチヒューズ特性を有する。メモリ・セル130は、第1のトンネル接合134を絶縁破壊、すなわち「飛ばす」のに十分な書き込み電流 Iwをメモリ・セル130に印加し、メモリ・セル130の抵抗状態を変化させることによって、プログラムすなわち書き込まれる。その結果である第2の抵抗状態は、第1のトンネル接合134の短絡状態となりうる。第2のトンネル接合136を短絡するのに不十分なように設計される。したがって、第2のトンネル接合136は、第1のトンネル接合134が飛ばされた後、メモリ・セル130における分離機能としてはたらき、これによってシリコン・ベースの能動的な分離素子が不要となる。第1と第2のトンネル接

合134、136の異なるアンチヒューズ特性は、この書き込み方式を可能にし、これについては後で説明する。

## [0028]

第1のトンネル接合134は、第1の電極142、誘電体144、および第2の電極146を含む。第1のトンネル接合134のトンネリング領域は、誘電体144が第1の電極142と接触している部分である。第2の電極146は、誘電体144をワード線110に電気的に結合する。代替的に、第2の電極146を省略することができ、ワード線110を誘電体144に直接結合することができる。誘電体144は、例えばSiO $_{\times}$ 、SiО $_{\times}$ 、N $_{y}$ 、A1О $_{\times}$ 、TiО $_{\times}$ 、A1N $_{\times}$ 、および他の誘電体材料からなることができる。誘電体144は、例えば、0.5nm~50nm程度の厚さを有する。第1と第2の電極142、146は、例えば、アルミニウム、銅、銀、金、および他の導電体などの任意の導電体材料であることができる。また、第1のトンネル接合134は、スペーサ139を含む。スペーサ139は、メモリ・セル130の製造中に、誘電体144の第1の電極142と接触する面積を小さくするのに使用され、これによって第1のトンネル接合134のトンネリング領域が小さくなる。

#### [0029]

## [0030]

第1のトンネル接合134は、書き込み電流 I w が印加されたときに第2のトンネル接合 1 36よりも前に絶縁破壊するように設計されている。トンネル接合の絶縁破損は、電極 材料、誘電体材料、誘電体の製造方法、および誘電体の厚さを含むいくつかの要因に依存 する。一般に、トンネル接合の両端の抵抗は、トンネル接合の面積に反比例する。図3A~図3Cに示した実施形態において、トンネル接合134のトンネル効果が生じる領域は、第2の電極146の底部と第1の電極142の頂部の間の誘電体144の領域である。この領域は、メモリ・アレイ100の製造中、誘電体144を形成する前にスペーサ139を形成することによって、比較的小さくされる。第2のトンネル接合136の領域は、誘電体148の第1と第3の電極142、150と接触している領域であり、第1のトンネル接合134のトンネリング領域よりも大きい。誘電体144、148の厚さと材料が同様のものである場合、第1のトンネル接合134のトンネリング領域の方が小さいため、第1のトンネル接合134は、第2のトンネル接合136の抵抗R<sub>2</sub>よりも大きい抵抗R<sub>1</sub>を有する。

## [0031]

トンネル接合の破壊電圧(breakdown voltage)は、トンネル接合の誘電体障壁層を形成するのに使用される厚さおよび材料に依存する。メモリ・セル130において、第1と第2のトンネル接合134、136の破壊電圧を、ほぼ等しくすることができる。

## [0032]

書き込みプロセスは、書き込み電流 Iwが印加されたときに生成される電圧に関して以下のように説明することができる。

[0033]

## 【数1】

$V_1 = I w \cdot R_1$  $V_2 = I w \cdot R_2$  10

20

30

#### [0034]

ここで、

V」は、第1のトンネル接合134の両端の電圧であり、

Vっは、第2のトンネル接合136の両端の電圧であり、

R」は、第1のトンネル接合134の抵抗であり、

Rっは、第2のトンネル接合136の抵抗である。

#### [0035]

$V_1$  と  $V_2$  の式に示されるように、第 1 のトンネル接合 1 3 4 の抵抗  $R_1$  が、第 2 のトンネル接合 1 3 6 の抵抗  $R_2$  よりも高いので、第 1 のトンネル接合 1 3 4 の両端の電圧  $V_1$  は、  $V_2$  よりも高い。アンチヒューズ素子は、トンネル接合がその破壊電圧よりも高い電位にさらされたとき、金属または他の導電性エレメントが誘電体中に拡散することによって「短絡」する。この拡散は、アンチヒューズの両端の電圧によって引き起こされる。したがって、第 1 のトンネル接合 1 3 4 の電流の流れ I wにより、電圧  $V_1$  は第 1 のトンネル接合 0 破壊電圧を超えるが、電圧  $V_2$  は第 2 のトンネル接合 1 3 6 の破壊電圧を超えない。第 1 のトンネル接合 1 3 4 の絶縁破壊により、第 2 の電極 1 4 6 から誘電体 1 4 4 を 横切るよう導電性エレメントが拡散することとなり、それにより、第 1 の  $V_2$  の  $V_3$  を  $V_4$  が短絡する。また、書き込み電流 I wの方向を逆にして、第 1 の電極 1 4 2 から誘電体 1 4 4 を 横切るよう導電性エレメントを拡散させることもできる。

#### [0036]

図 3 A ~ 図 3 C に示した実施形態において、第 2 のトンネル接合 1 3 6 と第 1 のトンネル接合 1 3 4 の面積比は、約 1 . 5 : 1 であることができる。誘電体 1 4 4 、 1 4 8 を形成するのに使用される材料およびその厚さが同様のものである場合は、抵抗 R  $_1$  と R  $_2$  の比率も約 1 . 5 : 1 である。したがって、 V  $_1$  は、 V  $_2$  の 1 . 5 倍以上であり、書き込みプロセス中に第 2 のトンネル接合 1 3 6 に著しい変化が起こらないよう、 V  $_2$  を十分低くすることができる。トンネル接合 1 3 6 に変化が起こる前に確実に第 1 のトンネル接合 1 3 4 が飛ぶようにすることができる。この面積比はまた、メモリ・セル 1 3 0 が使用される用途によっては、 1 . 5 : 1 よりも小さくすることができる。

## [0037]

## [0038]

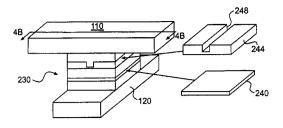

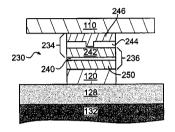

図4Aおよび図4Bは、トンネル接合が直列に配列されたデュアル・トンネル接合メモリ・セル230の代替実施形態を示す。図4Aは、メモリ・セル230の斜視図であり、図4Bは、図4Aにおいて線4B-4Bで切断した断面図である。メモリ・セル230は、図2に示したようなメモリ・アレイ100で使用されることができる。

## [0039]

メモリ・セル 2 3 0 は、ワード線 1 1 0 とビット線 1 2 0 の間に挟まれた第 1 のトンネル接合 2 3 4 と第 2 のトンネル接合 2 3 6 とを含む。第 1 のトンネル接合 2 3 4 は、不均一な厚さの誘電体 2 4 4 (分解形式で示されている)を有し、第 2 のトンネル接合 2 3 6 と 異なるアンチヒューズ特性を有する。第 1 のトンネル接合 2 3 4 は、第 1 の電極 2 4 2、 誘電体 2 4 4、および第 2 の電極 2 4 6 を含む。第 2 のトンネル接合 2 3 6 は、第 1 の電極 2 4 6 を第 1 のトンネル接合 2 3 6 は、第 1 の電極 2 4 6 を第 1 のトンネル接合 2 3 4 と共用し、また誘電体 2 4 0 (分解形式で示されて 10

20

30

40

いる)と第3の電極250を含む。

## [0040]

図4Aおよび図4Bに示されるように、誘電体244は、不均一な厚さを有し、誘電体244内に延びる特徴形状すなわち溝248を含む。第1のトンネル接合234のトンネリング領域は、本質的に、溝248の底の領域に等しい。したがって、溝248によって、第1のトンネル接合234の破壊電圧が低減する。溝248の下の誘電体244の厚さを変化させ、誘電体244の材料を変更することによって、誘電体244の破壊電圧を容易に調整することができる。

## [0041]

メモリ・セル 2 3 0 は、書き込み電流 I wまたは書き込み電圧 V wをメモリ・セル 2 3 0 に印加することによってプログラムされる。溝 2 4 8 の下の誘電体 2 4 4 の比較的薄い領域は、書き込み電流 I wまたは書き込み電圧 V w が印加されたときの第 1 のトンネル接合 2 3 4 の絶縁破壊の場所であり、ここで、電極 2 4 2 、 2 4 4 の一方から金属が、溝 2 4 8 の下の誘電体 2 4 4 に拡散する。溝 2 4 8 の下の比較的小さいトンネリング領域は、局所的な拡散領域を提供し、その結果、メモリ・セル 2 3 0 の破壊しきい値分布が小さくなる。破壊しきい値分布が小さいと、誘電体 2 4 4 の欠陥によって第 1 のトンネル接合 2 3 4 内の破壊電圧に変動がもたらされる可能性が低くなる。したがって、メモリ・セル 2 3 0 をプログラムするために使用される書き込み電流 I wまたは書き込み電圧 V wを小さくすることができる。また、この特徴は、書き込みプロセス中に第 2 のトンネル接合 2 3 6 が不慮に変化する可能性を小さくする。

#### [0042]

第2のトンネル接合236の厚さと材料は、(プログラミング前に)第2のトンネル接合236の抵抗が第1のトンネル接合234の抵抗とほぼ等しくなるように選択することができる。この実施形態において、書き込みプロセスにおいて第1のトンネル接合234が短絡されると、メモリ・セル130の全抵抗を約半分に減少させることができる。

## [0043]

図4Bにおいて、第2および第3の電極246、250は必須ではなく、代わりに、誘電体をワード線とビット線に直接結合してもよい。

## [0044]

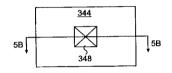

図5A、図5B、図6A、図6B、図7、および図8は、メモリ・セル230に使用するのに適した誘電体の代替実施形態を示す。それぞれの実施形態は、低い破壊電圧と小さいトンネリング領域を提供するのに異なる特徴を有する。

#### [0045]

図 5 A は、底が尖った凹部 3 4 8 を有する誘電体 3 4 4 を示す。図 5 B に示したように、凹部 3 4 8 は、その最も低い場所で厚さが比較的小さく、誘電体 3 4 4 に小さいトンネリング領域を提供する。図 6 A および図 6 B は、V字形の切り欠き形状の凹部 4 4 8 を有する誘電体 4 4 4 を示す。図 7 および図 8 は、円錐形の切り欠き形状の凹部 5 4 8 を有する誘電体 5 4 4 を示す。これらのすべての特徴形状は、低い破壊電圧と、小さい破壊しきい値分布を提供する。図 4 ~ 図 7 に示した特徴形状 2 4 8 、 3 4 8 、 4 4 8 、 5 4 8 は、例えば刻印プロセス(imprinting process)によって誘電体に形成することができる。

## [0046]

低い破壊電圧を得るために、不均一な誘電体を設けたり誘電体の表面積を小さくしなくてもよい。例えば、厚さが薄い誘電体を使用することによって、または低い破壊電界の誘電体材料を使用することによって、または材料と幾何学形状の違いを組み合わせることによっても、低い破壊電圧を得ることができる。メモリ・セルの代替実施形態(図示せず)は、比較的薄い誘電体を有する第1のトンネル接合と、より厚い誘電体を有する第2のトンネル接合とを含むことができる。両方の誘電体は、類似の形状(例えば、平行六面体)を有することができ、類似の材料で作成することができる。第1のトンネル接合234の薄い誘電体は、書き込み電流または書き込み電圧Vwが印加されたときに第1のトンネル接合234が第2のトンネル接合236よりも前に飛ばされることができるように、異なる

10

20

30

40

20

30

40

50

アンチヒューズ特性(この実施形態では、より低い破壊電圧)を提供する。

#### [0047]

上記の実施形態によれば、メモリ・デバイス10は、メモリ・アレイ100内のメモリ・セルを分離するために、ダイオードやトランジスタなどのシリコン・ベースの能動的な分離素子を必要としない。したがって、メモリ・デバイス10は、スタック型のメモリ要素を含むことができ、アレイ密度を高めることができる。トンネル接合を比較的小さくすることができ、それによりアレイ100について可能なアレイ密度をさらに高める。さらに、トンネル接合の破壊電圧は、誘電体の厚さ、材料、および幾何学形状を調整することによって容易に操作される。したがって、所望のトンネル接合特性を選択することによって、書き込み電流Iwまたは書き込み電圧Vwを低減させることができる。

[0048]

上記の実施形態のもう1つの利点は、第1のトンネル接合における誘電体によって提供される小さな破壊しきい値分布である。誘電体の破壊電圧の変動が低減されるので、メモリ・セルをプログラムするのに使用される書き込み電圧Vwまたは書き込み電流Iwの分布(電圧/電流プログラミング分布)を制御することができる。この態様は、メモリ・デバイス10の電力要件を減少させ、メモリ・デバイス10内の選択されていない要素が、書き込みプロセスで不慮に変更される可能性を減少させる。

[0049]

次に、図2および図3A~図3Cに示したメモリ・セルの実施形態と関連して、メモリ・デバイス10の書き込みプロセスを説明する。この実施形態では、メモリ・セル130をプログラムするために書き込み電流 Iwが印加される。

[0050]

図2を参照すると、選択されたメモリ・セル130に書き込むために、選択されたメモリ・セル130と交差するワード線110に書き込み電流Iwが印加される。選択されたワード線110をIwに接続する行デコーダ300内のスイッチを閉じることによって、書き込み電流Iwを印加することができる。選択されていないワード線110に接続された行デコーダ300内のスイッチは、開いている。同時に、列デコーダ400は、選択されたメモリ・セル130と交差するビット線120をアースに接続する。したがって、書き込み電流Iwは、選択されたワード線110と、選択されたメモリ・セル130と、選択されたビット線120とを通ってアースに流れる。選択されていないビット線120へのスイッチは開いている。

[0051]

図3Cを参照すると、書き込み電流Iwは、選択されたメモリ・セル130内の第1のトンネル接合134を飛ばすのに十分な電圧Vュを誘電体144の両端に生成し、第2のトンネル接合136を飛ばすのに不十分な電圧Vュを誘電体148の両端に生成するように選択される。電圧Vュは、第2の電極146から誘電体144への導電性エレメントの拡散を引き起こし、第2の電極146(およびビット線110)を第1の電極142に電気的に接続する。第2の電極146と第1の電極142が繋がると、メモリ・セル130の抵抗が第1の状態から第2の状態に変化し、これは、読み取りプロセスによって検出可能である。第1のトンネル接合134が飛ばされた後、アンチヒューズの働きにより、第1のトンネル接合134の両端の抵抗をほぼゼロに減少させることができる(すなわち、短絡)。したがって、書き込みプロセスの後では、メモリ・セル130の両端の抵抗は、第2のトンネル接合136の両端の抵抗に近いものとなる。

[0052]

図4~図8に示した実施形態の書き込みプロセスは、上記の実施形態と類似している。図4~図8の実施形態は、書き込み電流 I w または書き込み電圧 V w を印加することによってプログラムすることができる。図2は、メモリ・セル130を有するアレイ100を示すが、メモリ・デバイス10に、図4Aおよび図4Bに示されるセルのようなメモリ・セル230を使用することもできる。メモリ・セル230をプログラムする書き込みプロセスを以下に説明する。

20

30

40

50

#### [0053]

図2および図4Bを参照すると、選択されたメモリ・セル230は、選択されたメモリ・セル230と交差するワード線110に書き込み電圧Vwまたは書き込み電流Iwを印加することによってプログラムされる。書き込み電圧Vwまたは書き込み電流Iwは、行デコーダ300内のスイッチを閉じて、選択したワード線110をVwまたはIwに接続することによって印加されることができる。選択していないワード線110に接続された行デコーダ300内のスイッチは開いている。これと同時に、列デコーダ400は、選択されたメモリ・セル230に印加される。残りのビット線120へのスイッチは開いている。

[0054]

図4 Bを参照すると、選択されたメモリ・セルの両端の書き込み電圧 V w は、 V  $_1$  の第 1 のトンネル接合 2 3 4 と V  $_2$  の第 2 のトンネル接合 2 3 6 の間で分配される。ここで、 V w = V  $_1$  + V  $_2$  である。書き込み電圧 V w は、選択されたメモリ・セル 2 3 0 に直接印加されてもよく、または、選択されたメモリ・セル 2 3 0 に印加される書き込み電流 I w から生じたものでもよい。 V  $_1$  は、選択されたメモリ・セル 2 3 0 内の第 1 のトンネル接合 2 3 4 を飛ばすのに十分であるが、 V  $_2$  は、第 2 のトンネル接合 2 3 6 を飛ばすのに不分である。書き込み電圧 V w の印加は、第 1 のトンネル接合 2 3 4 が短絡されたときに制つされてもよい。電圧 V  $_1$  は、第 2 の電極 2 4 6 のよびビット線 1 1 0 )を第 1 のを加てもよい。電圧 V  $_1$  は、第 2 の電極 2 4 6 (およびビット線 1 1 0 )を第 1 の電極 2 4 2 に電気的に接続する。第 2 の電極 2 4 6 と第 1 の電極 2 4 2 とが繋がると、メモリ・セル 2 3 0 の抵抗が変化し、これは、読み取りプロセスによって検出可能である。第 1 のトンネル接合 2 3 4 が飛ばされた後、アンチヒューズの働きにより、第 1 のトンネル接合 2 3 4 の両端の抵抗をほぼゼロに減少させることができる(すなわち短絡)。

[0055]

上記の電圧書き込みプロセスに代えて、行デコーダ300と列デコーダ400は、選択されたメモリ・セルを流れる電流を検知するフィードバック・センサ(図示せず)に応答することができる。フィードバック・センサは、選択されたメモリ・セルの第1のトンネル接合が飛ばされたことを示し、そのとき、書き込みプロセスを中止して第2のトンネル接合が不慮に飛ばされないようにすることができる。

[0056]

次に、図 2 を参照して、メモリ・デバイス 1 0 の読み取りプロセスを説明する。メモリ・デバイス 1 0 は、Tranらに対する米国特許第6,259,644号に開示されているような等電位読み取りプロセス(equipotential read process)を有利に使用することができ、この特許の内容は、参照よりここに組み込まれる。等電位読み取りプロセスについては、後でメモリ・セル 1 3 0 に関して概略的に説明するが、ここで説明するプロセスは、本明細書に記載されている代替メモリ・セルの実施形態を使用するメモリ・デバイス 1 0 に適している。

[0057]

選択されたメモリ・セル130の2値状態を求めるために(すなわち、読み取るために)、読み取り電位Vrが、選択されたメモリ・セル130の行に対応するワード線110に印加され、選択されたメモリ・セル130の列に対応するビット線120が、列デコーダ400を介してセンス・アンプ500に結合される。メモリ・アレイ100内の他のすべてのビット線120に、等しい電位を印加することができる。センス・アンプ500は、選択されたビット線120からの電流を検出して、選択されたメモリ・セル130の2値状態を求める。この2値状態は、センス・アンプ500の出力に結合された処理装置(図示せず)によって検出されることができ、センス・アンプ500の出力は、選択されたメモリ・セル130の抵抗状態を示す。代替的に、センス・アンプ500は、2値状態を求めて該2値状態を処理装置に出力する回路を含むことができる。

20

30

40

50

[0058]

選択されたメモリ・セル 1 3 0 の 2 値状態は、選択されたメモリ・セル 1 3 0 の抵抗の第 1 の高い値から、書き込みプロセス後の第 2 の低い値への変化として求めることができる。例えば、第 1 の高い抵抗状態では、メモリ・セル 1 3 0 内の電流が少なくなり、これは、 2 値状態の「 0 」を表すことができる。第 2 の低い抵抗状態(第 1 のトンネル接合 1 3 4 を飛ばした後)では、メモリ・セル 1 3 0 内の電流が多くなり、 2 値状態の「 1 」を表すことができる。

[0059]

書き込みプロセス後で、メモリ・セル130は、第2のトンネル接合136を非短絡状態に維持する。したがって、選択されたメモリ・セル130をプログラムした後において、メモリ・アレイ100内に短絡はない。この分離機能により、メモリ・アレイ100内の読書きプロセスに悪影響を及ぼすことなく、複数のセル130をプログラムすることができる。

[0060]

上記の実施形態によると、2値状態の「1」または「0」をメモリ・セルに記憶することができる。書き込み前のメモリ・セルの第1の高抵抗状態は、メモリ・セルの2値状態の「0」に対応することができ、第2の低抵抗状態は、2値状態の「1」に対応することができる。しかしながら、この取り決めは任意なものであり、2値状態の「0」の割り当てを、「1」または他の任意の記号値に割り当て直すことができる。

[0061]

次に、図9~図20を参照して、メモリ・アレイ100を作成する方法を説明する。

[0062]

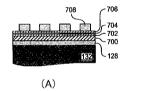

図9~図20において、"(A)"によって示される図は、製作されているメモリ・アレイの行に沿った断面図であり、"(B)"によって示される図は、平面図である。図9~図20は、図3Aおよび図3Bに示されるようなメモリ・セル130を有するメモリ・アレイ100の製作を示す。

[0063]

図9Aおよび図9Bを参照すると、製作プロセスは、最初に基板132を提供する。例えば、基板132は、単結晶シリコン・ウェハのような半導体基板である。

[0064]

基板132の上に絶縁層128が形成される。絶縁層128は、例えば、CVD(化学蒸着法)、プラズマCVD(PECVD)、および他の堆積プロセスによって堆積された二酸化ケイ素である。絶縁層128の他の適切な材料には、SiO $_{ imes}$ 、SiN $_{ imes}$ 、SiО $_{ imes}$ 、SiО $_{ imes}$ 、N $_{ imes}$ 、AIN $_{ imes}$ 、および他の誘電体材料を含むことができる。二酸化ケイ素は、例えば、シリコン層を堆積し、次に該シリコンを酸化させることによって形成されることができる。

[0065]

次に、絶縁層128の上に第1の導電層700が形成される。第1の導電層は、ビット線120を形成する。第1の導電層700は、例えば、銀、金、銅、アルミニウム、および他の金属であることができる。第1の導電層700は、例えばDCまたはRFスパッタ堆積、および他の堆積法で形成することができる。また、第1の導電層700は、例えばドープされた半導体層である。

[0066]

第1の導電層700上に第2の導電層702が形成される。第2の導電層702は、例えば、銀、金、銅、アルミニウム、および他の金属であることができる。第2の導電層702は、例えばDCまたはRFスパッタ堆積法、および他の堆積法で堆積することができる。第2の導電層702は、第2のトンネル接合136をビット線120に結合する第3の電極150となり、したがって必須ではない。

[0067]

第2の導電層702上に誘電層704が形成される。誘電層704は、例えばSiOェ、

$SiN_x$ 、 $SiO_xN_y$ 、 $AIO_x$ 、 $TaO_x$ 、 $TiO_x$ 、 $AIN_x$ 、および他の誘電体材料であることができる。誘電層 704 は、例えば CVD、PECVD、および他の堆積法で堆積させることができ、例えば、約0.5nm~50nmの厚さを有することができる。二酸化ケイ素は、例えば、シリコン層を堆積させ、次に該シリコンを酸化させることによって形成されることができる。

### [0068]

誘電層704の上に第3の導電層706が形成される。第3の導電層706は、例えば銀、金、銅、アルミニウム、および他の導体であることができる。第3の導電層706は、例えばDCまたはRFスパッタ堆積、および他の堆積法で堆積させることができる。層700、702、704、706を堆積させた後で、製作しているメモリ・アレイ上にフォトレジスト・マスク708が置かれる。

[0069]

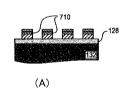

図10Aおよび図10Bを参照すると、層700、702、704、706は、エッチング・プロセスでパターン形成される。エッチング・プロセスにより、行710が得られる。次に、マスク708は、アッシング・プロセス(ashing process)によって除去される

[0070]

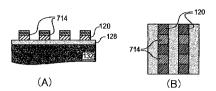

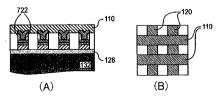

図11Aおよび図11Bを参照すると、上部の2つの導電層および誘電層が、フォトレジスト・マスク712を使用してパターン形成される。行710の一番下の導電層はパターン形成されず、よってビット線120が残る。このパターン形成のステップによって、ビット線120上に配置される導体 / 誘電体 / 導体ポスト(柱)714が得られる。ポスト714は、第2のトンネル接合136に対応する。次に、図12Aおyび図12Bに示されるように、フォトレジスト・マスク712が、アッシング・プロセスによって除去される。

[0071]

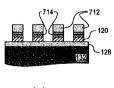

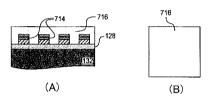

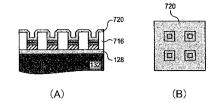

図13Aおよび13Bを参照すると、製作されているメモリ・アレイ上に絶縁体716が形成される。絶縁体716は、例えば、SiO $_{\times}$ 、Si $_{\times}$  N $_{y}$ 、A1О $_{\times}$ 、TaO $_{\times}$ 、TiO $_{\times}$ 、A1N $_{\times}$ 、および他の絶縁体であることができる。絶縁体716は、例えばCVD、PECVD、および他の堆積法で堆積されることができる。次に、絶縁体716の表面が、例えば化学機械研磨(CMP)などの方法を使用して平坦化されることができる。

[0072]

図 1 4 A および図 1 4 B を参照すると、絶縁体 7 1 6 の上にフォトレジスト・マスク 7 1 8 が置かれ、ポスト 7 1 4 上の絶縁体 7 1 6 領域が露出される。その後、ポスト 7 1 4 上の絶縁体 7 1 6 が、エッチングで除去される。

[0073]

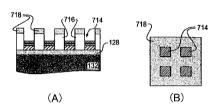

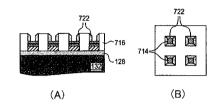

図 1 5 A および図 1 5 B を参照すると、フォトレジスト・マスク 7 1 8 は、アッシング・プロセスによって除去される。次に、アレイ上にスペーサ層 7 2 0 が形成される。スペーサ層 7 2 0 は、例えば窒化シリコンであることができる。スペーサ層 7 2 0 は、例えば C V D、 P E C V D、および他の堆積法によって堆積されることができる。

[0074]

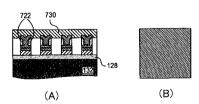

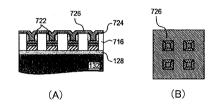

図16Aおよび図16Bを参照すると、スペーサ層720が、スペーサ722に形作られる。スペーサ722は、例えば異方性エッチングによって形成されることができる。スペーサ722は、ポスト714上に、比較的小さい露出した表面積を残す。

[0075]

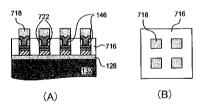

図17Aおよび図17Bを参照すると、アレイの上に誘電層724が形成される。誘電層724は、例えばSiO $_{ imes}$ 、SiО $_{ imes}$ 、N $_{ imes}$ 、AIО $_{ imes}$ 、TaО $_{ imes}$ 、TiО $_{ imes}$ 、 および他の誘電体材料であることができる。誘電層724は、例えばCVD、PECVD、および他の堆積法で堆積させることができる。

[0076]

10

20

30

誘電層724の上に第4の導電層726が形成される。第4の導電層726は、例えば銀、金、銅、アルミニウム、および他の金属であることができる。第4の導電体層726は、例えばDCまたはRFスパッタ堆積、および他の堆積法で堆積されることができる。

## [0077]

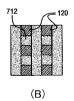

図18Aおよび図18Bを参照すると、フォトリソグラフィ/エッチング・プロセスによって電極146が形成される。フォトレジスト・マスクは、図14Bに示したマスク718でよい。こうして、ポスト714上に第1のトンネル接合が形成される。

## [0078]

図19Aおよび図19Bを参照すると、アッシング・プロセスによってフォトレジスト・マスク718が除去される。次に、アレイ上に第5の導電層730が形成される。第5の導電層730は、例えば、銀、金、銅、アルミニウム、および他の導体であることができる。第5の導電層730は、例えばDCまたはRFスパッタ堆積法、および他の堆積法で形成されることができる。また、第5の導電層730は、例えばドープされた半導体層でもよい。

### [0079]

図 2 0 A および図 2 0 B を参照すると、第 5 の導電層 7 3 0 は、フォトリソグラフィ / エッチング・プロセスを使用してワード線 1 1 0 にパターン形成される。図 2 0 A および図 2 0 B に、完成したメモリ・アレイの一部を示す。図 2 0 A および図 2 0 B において、ビット線 1 2 0 は、絶縁体で覆われてもよい。図 2 0 B では、ビット線 1 2 0 の位置を示すために該絶縁体は省略されている。

#### [0800]

図 9 ~ 図 1 4 と図 2 1 ~ 図 2 2 を参照して、図 4 ~ 図 8 に示した代替のメモリ・セルを有するメモリ・アレイ 1 0 0 を製作する代替の方法を説明する。

## [0081]

一般に、前述のプロセスは、図3A~図3Cに示したようなメモリ・セル130を有するメモリ・アレイ100を作成するよう適合される。図4~図8に示したようなセルを有するメモリ・アレイ100は、異なる製作方法を必要とする。そのようなメモリ・アレイを製作する方法は、一般に、図9~図14に示した方法に対応し、この時点で、異なるものとなる。図14Aと図14Bに示したステップよりも後の代替方法のステップについて、以下に説明する。

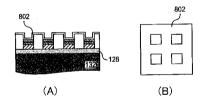

### [0082]

図 2 1 A および図 2 1 B を参照すると、図 1 4 A および図 1 4 B に示したようにポスト 7 1 4 上の絶縁体 7 1 6 の領域を露出させた後、アレイ上に第 2 の誘電層 8 0 2 が形成される。誘電層 8 0 2 は、例えば、S i O  $_{\times}$ 、S i O  $_{\times}$  N  $_{y}$ 、A 1 O  $_{\times}$ 、T a O  $_{\times}$ 、T i O  $_{\times}$ 、A 1 N  $_{\times}$ 、および他の誘電体材料であることができる。二酸化ケイ素は、例えば、シリコン層を堆積し、次に該シリコンを酸化させることによって形成されることができる。次に、各メモリ・セルの個々の誘電体を、図 1 4 B に示したマスク 7 1 8 と同様のマスクを使用するフォトリソグラフィ / エッチング・プロセスを用いて形成されることができる。

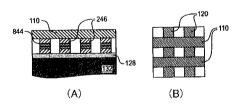

## [0083]

図 2 2 A および図 2 2 B を参照すると、誘電体 8 4 4 は、図 4 ~ 図 8 に示した誘電体 2 4 4、3 4 4、4 4 4 および 5 4 4のいずれかに対応することができる。特徴形状 2 4 8、3 4 8、4 4 8、5 4 8 は、誘電体 2 4 4、3 4 4、4 4 4、5 4 4 に、例えば刻印プロセスなどの方法によって形成されることができる。

## [0084]

誘電体 2 4 4 、 3 4 4 、 4 4 4 および 5 4 4 のうちの選択されたものを形成した後で、導電層(図示せず)がアレイ上に堆積され、誘電体 8 4 4 上に、該導電層から電極 2 4 6 がパターン形成される。次に、ワード線 1 1 0 を、図 1 9 および図 2 0 に示したように、アレイ上に形成することができる。代替的に、誘電体 8 4 4 までのバイア (via) を埋めるよう単一層を堆積し、ワード線 1 1 0 を形成することができる。ビット線 1 2 0 の位置を

20

10

30

40

示すために、図22Bでは絶縁体が省略されている。

## [0085]

上記のプロセスにより、図4Aおよび図4Bに示されるようなメモリ・セル230を有するメモリ・アレイが得られる。メモリ・セル230は、誘電体244、344、444、544のうち任意のものを含むことができる。

#### [0086]

この仕様において、メモリ・アレイに「0」と「1」の状態を書き込む電流についての取り決めは任意であり、メモリ・デバイス10の任意の所望の用途(アプリケーション)に適合するように割り当てなおすことができる。

#### [0087]

上記の実施形態は、メモリ・セルの抵抗を第1の高い状態から第2の低い状態に変化させるために、第1のトンネル接合を短絡するという点から説明されている。メモリ・セルの抵抗はまた、第1のトンネル接合の誘電体に導電性エレメントを部分的に拡散させることによって変化させることができる。これは、「部分的な飛ばし(partial blow)」と呼ばれる。トンネル接合の部分的な飛ばしは、トンネル接合を短絡させることなく、トンネル接合の両端の抵抗を減少させる。誘電体への導電性エレメントの拡散は、メモリ・セルの抵抗をかなり減少させ、この抵抗の変化を、読み取りプロセスで検出することができる。

### [0088]

本明細書において、「行」および「列」という用語は、メモリ・アレイ内の固定された向きを意味するものではない。さらに、「行」と「列」という用語は、必ずしも直角の関係を意味するものではない。

#### [0089]

図 2 に示したセンス・アンプ 5 0 0 は、メモリ・デバイス 1 0 内のメモリ・セルの 2 値状態を検出するための検出デバイスの例である。実際には、例えばトランスインピーダンス・センス・アンプ、電荷注入センス・アンプ、差動センス・アンプ、デジタル差動センス・アンプなどの他の検出デバイスを使用することができる。

#### [0090]

図3に、メモリ・セル230の2値状態を検出する1つのセンス・アンプ500が示されている。実際には、1つのメモリ・アレイに多数の検出デバイスを結合することができる。例えば、メモリ・アレイ内の各ビット線ごとにセンス・アンプを含んでもよく、メモリ・アレイ内の複数のビット線ごとにセンス・アンプを含んでもよい。

## [0091]

メモリ・アレイ100は、様々な用途に使用することができる。1つの用途は、例えば、記憶モジュールを有するコンピューティング装置である。記憶モジュールは、長期記憶のために1つまたは複数のメモリ・アレイ100を含むことがある。記憶モジュールは、ラップトップ・コンピュータ、パーソナル・コンピュータ、およびサーバなどの装置に使用されることができる。

## [0092]

メモリ・デバイス10は、例示的な実施形態に関して説明されたが、当業者には多くの変形が容易に明らかであり、本開示は、それらの変形を含むように意図されている。

## [0093]

本発明は、以下の実施態様を含む。

(1)第1のトンネル接合(134、234)と、

前記第1のトンネル接合(134、234)と直列の第2のトンネル接合(136、23 6)とを備え、

前記第1のトンネル接合(134、234)を第1の抵抗状態から第2の抵抗状態に変化させることができ、該第1のトンネル接合(134、234)が、該第2のトンネル接合(136、236)と異なるアンチヒューズ特性を有するメモリ・セル(130、230)。

(2)前記第2の抵抗状態は、短絡状態である上記(1)に記載のメモリ・セル(130

10

20

30

40

230)。

- (3)前記アンチヒューズ特性は、破壊電圧であり、前記第1のトンネル接合(134、234)は、前記第2のトンネル接合(136、236)より低い破壊電圧を有する上記(1)に記載のメモリ・セル(130、230)。

- (4)前記第1のトンネル接合(134、234)は、誘電体(144、244、344 、444、544)を含み、前記第2のトンネル接合(136、236)は、誘電体(1 48、240)を含む上記(3)に記載のメモリ・セル(130、230)。

- (5)前記第1のトンネル接合(134、234)のトンネリング領域は、前記第2のトンネル接合(136、236)のトンネリング領域よりも小さい上記(4)に記載のメモリ・セル(130、230)。

[0094]

- (6)前記第1のトンネル接合(234)の前記誘電体(244、344、444、54 4)は、不均一な厚さを有する上記(4)に記載のメモリ・セル(230)。

- (7)前記第1のトンネル接合(234)の前記誘電体(244、344、444、544)は、特徴形状(248)を含み、該特徴形状(248)は、該第1のトンネル接合(234)のトンネリング領域を画定する上記(6)に記載のメモリ・セル(230)。

- (8)前記アンチヒューズ特性は、抵抗であり、前記第1のトンネル接合(134)は、書き込みプロセス前に前記第2のトンネル接合(136)よりも高い抵抗を有する上記(1)に記載のメモリ・セル(130)。

- (9)前記第1のトンネル接合(134)は、誘電体(144)を含み、前記第2のトンネル接合(136)は、誘電体(148)を含む上記(8)に記載のメモリ・セル(130)。

- (10)前記第1のトンネル接合(134)のトンネリング領域は、前記第2のトンネル接合(136)のトンネリング領域よりも小さい上記(9)に記載のメモリ・セル(130)。

【図面の簡単な説明】

- 【図1】デュアル・トンネル接合メモリ・セルを有するメモリ・アレイの概略的な斜視図である。

- 【図2】 図1に示したメモリ・アレイとそれに関連した読み書き回路を含むメモリ・デバイスの概略図。

- 【図3A】図1に示したメモリ・アレイの一部の断面図。

- 【図3B】図3Aに示したメモリ・アレイの一部の上面図。

- 【図3C】図3Aに示したようなメモリ・セルの一実施形態の側面図。

- 【図4A】メモリ・セルの代替の実施形態の斜視図。

- 【図4B】図4Aに示したメモリ・セルの線4B-4Bに沿った断面図。

- 【図5A】誘電体の一実施形態の平面図。

- 【図5B】図5Aの線5B-5Bに沿った断面図。

- 【図6A】誘電体のもう他の代替の実施形態の平面図。

- 【図6B】図6Aの線6B-6Bに沿った断面図。

- 【図7】誘電体の他の代替の実施形態の平面図。

- 【図8】図7の線8-8に沿った断面図。

- 【図9】図1に示したメモリ・アレイを作成する方法を示す図。

- 【図10】図1に示したメモリ・アレイを作成する方法を示す図。

- 【図11】図1に示したメモリ・アレイを作成する方法を示す図。

- 【図12】図1に示したメモリ・アレイを作成する方法を示す図。

- 【図13】図1に示したメモリ・アレイを作成する方法を示す図。

- 【図14】図1に示したメモリ・アレイを作成する方法を示す図。

- 【図15】図1に示したメモリ・アレイを作成する方法を示す図。

- 【図16】図1に示したメモリ・アレイを作成する方法を示す図。

- 【図17】図1に示したメモリ・アレイを作成する方法を示す図。

10

20

30

40

【図18】図1に示したメモリ・アレイを作成する方法を示す図。

【図19】図1に示したメモリ・アレイを作成する方法を示す図。

【図20】図1に示したメモリ・アレイを作成する方法を示す図。

【図21】図1に示したメモリ・アレイを作成する代替の方法を示す図。

【図22】図1に示したメモリ・アレイを作成する代替の方法を示す図。

## 【符号の説明】

130、230 メモリ・セル

134、234 第1のトンネル接合

136、236 第2のトンネル接合

144、244、344、444、544 誘電体

2 4 8 特徴形状

## 【図1】

## 【図2】

## 【図3A】

【図3B】

【図3C】

【図4A】

【図4B】

【図5A】

【図5B】

【図6A】

【図6B】

【図7】

【図8】

【図9】

....

【図10】

(B)

【図11】

(A)

# 【図12】

# 【図13】

【図14】

【図18】

【図19】

【図20】

# 【図15】

【図16】

【図17】

【図21】

【図22】

## フロントページの続き

(72)発明者 ラング・ティ・トラン

アメリカ合衆国95070カリフォルニア州サラトガ、ウッドブラ・コート 5085

(72)発明者 ヘオン・リー

アメリカ合衆国 9 4 0 8 7 カリフォルニア州サニーベール、プラームス・ウェイ 4 5 5、アパートメント 2 3 0

## 審査官 河口 雅英

(56)参考文献 特開2001-244352(JP,A)

特開昭59-168665(JP,A)

特開昭60-117660(JP,A)

特開平11-040758(JP,A)

特開2000-164735(JP,A)

(58)調査した分野(Int.CI., DB名)

H01L 27/10