# (19) 国家知识产权局

# (12) 发明专利申请

(10) 申请公布号 CN 117559999 A (43) 申请公布日 2024.02.13

(21)申请号 202311848919.1

(22)申请日 2023.12.29

(71) 申请人 深圳市山海半导体科技有限公司 地址 518000 广东省深圳市南山区粤海街 道高新区社区高新南四道18号创维半 导体设计大厦东座1105

(72) 发明人 范学莲

(74) 专利代理机构 北京祯新珵艺知识产权代理 事务所(特殊普通合伙) 16110

专利代理师 沈超

(51) Int.CI.

HO3M 1/08 (2006.01) HO3M 1/46 (2006.01)

权利要求书2页 说明书11页 附图8页

## (54) 发明名称

一种逐次逼近型模数转换器及模数转换处 理方法

#### (57) 摘要

本申请涉及一种逐次逼近型模数转换器及 模数转换处理方法,属于模数转换技术领域,用 于解决现有模数转换器有效位数受限于量化噪 声的技术问题。逐次逼近型模数转换器包括DAC 电容阵列、噪声整形电路、比较器和SAR逻辑单 元,所述噪声整形电路包括一阶噪声整形电路和 二阶噪声整形电路,在量化阶段结束后的残差存 储阶段,所述一阶噪声整形电路的信号输入端和 二阶噪声整形电路的信号输入端按照存储时序 顺次连接到所述DAC电容阵列的输出端,对量化 阶段结束产生的残差电压分次存储;所述二阶噪 v 声整形电路的信号输出端和所述一阶噪声整形 电路的信号输出端在下一量化阶段分别连接所 述比较器的第一输入端和第二输入端。本申请实 施例提高了有效位数及精度。

1.一种逐次逼近型模数转换器,包括DAC电容阵列、比较器和SAR逻辑单元,所述DAC电容阵列的输入端连接模拟输入信号,所述比较器的输出端连接所述SAR逻辑单元,所述SAR逻辑单元输出控制信号给所述DAC电容阵列;其特征在于,在所述DAC电容阵列与所述比较器之间还包括噪声整形电路,所述噪声整形电路包括一阶噪声整形电路和二阶噪声整形电路,其中,

在量化阶段结束后的残差存储阶段,所述一阶噪声整形电路的信号输入端和二阶噪声整形电路的信号输入端按照存储时序先后顺次连接到所述DAC电容阵列的输出端,对量化阶段结束产生的残差电压分次存储;所述二阶噪声整形电路的信号输出端和所述一阶噪声整形电路的信号输出端在下一量化阶段分别连接所述比较器的第一输入端和第二输入端,使所述比较器在下一量化阶段的逐次比较过程中减去存储的当前量化阶段的残差电压。

- 2.根据权利要求1所述的逐次逼近型模数转换器,其特征在于,所述一阶噪声整形电路包括一阶第一电容;一阶第一电容第一端在残差存储阶段作为信号输入端与所述DAC电容阵列的输出端连接,通过电荷共享存储在所述DAC电容阵列的输出端产生的量化残差电压以实现一阶残差存储;一阶第一电容第一端在下一量化阶段作为信号输出端连接所述比较器的第二输入端。

- 3.根据权利要求2所述的逐次逼近型模数转换器,其特征在于,所述一阶噪声整形电路进一步包括一阶第二电容和动态放大器;所述一阶第一电容和所述一阶第二电容分别在相邻的一阶残差存储阶段接入所述动态放大器;对应地,在所述动态放大器的输入端连接所述一阶第一电容第一端/所述一阶第二电容第一端时,所述动态放大器的输出端对应连接所述一阶第二电容的第一端/所述一阶第一电容的第一端,将所述一阶第一电容/所述一阶第二电容中的残差电压放大后存储在对应的所述一阶第二电容/所述一阶第一电容。

- 4.根据权利要求3所述的逐次逼近型模数转换器,其特征在于,所述一阶第一电容的容量与所述一阶第二电容的容量相同。

- 5.根据权利要求4所述的逐次逼近型模数转换器,其特征在于,所述动态放大器的放大倍数为所述一阶第一电容容量和从所述DAC电容阵列电容容量的总和与所述一阶第一电容容量的比值。

- 6.根据权利要求1所述的逐次逼近型模数转换器,其特征在于,所述二阶噪声整形电路包括二阶第一电容,在残差存储阶段,在所述一阶噪声整形电路完成一阶残差存储后,二阶第一电容第一端作为信号输入端与所述DAC电容阵列的输出端连接,通过电荷共享实现二阶残差存储,二阶第一电容第二端在下一量化阶段作为信号输出端连接所述比较器的第一输入端。

- 7.根据权利要求1-6任一所述的逐次逼近型模数转换器,其特征在于,所述模拟输入信号为差分信号,包括同相模拟输入信号和反相模拟输入信号;DAC电容阵列的输出端包括同相输出端和反相输出端;对应地,所述比较器的输入端包括一对同相输入端和一对反相输入端;所述噪声整形电路包括同相噪声整形电路和反相噪声整形电路;

在量化阶段结束后的残差存储阶段,基于存储时序,同相一阶噪声整形电路的信号输入端和反相一阶噪声整形电路的信号输入端分别连接所述DAC电容阵列的同相输入端和反相输入端,在实现了一阶残差存储后,同相二阶噪声整形电路和反相二阶噪声整形电路并联后的两端分别连接所述DAC电容阵列的同相输入端和反相输入端;

在下一量化阶段,同相一阶噪声整形电路的信号输出端和反相一阶噪声整形电路的信号输出端分别连接所述比较器第二同相输入端和第二反相输入端;在实现了一阶存储后,同相二阶噪声整形电路的信号输入端和反相二阶噪声整形电路的信号输入端分别连接所述DAC电容阵列的同相输入端和反相输入端,同相二阶噪声整形电路的信号输出端和反相二阶噪声整形电路的信号输出端分别连接所述比较器的第一同相输入端和第一反相输入端。

- 8.根据权利要求7所述的逐次逼近型模数转换器,其特征在于,所述同相二阶噪声整形电路包括同相二阶电容,所述反相二阶噪声整形电路包括反相二阶电容,所述同相二阶电容和所述反相二阶电容容量相等;在实现二阶残差存储时,所述同相二阶电容和所述反相二阶电容并联,并联的第一端连接所述DAC电容阵列的同相输出端,并联的第二端连接所述DAC电容阵列的反相输出端。

- 9.根据权利要求7所述的逐次逼近型模数转换器,其特征在于,同相一阶噪声整形电路和反相一阶噪声整形电路共用一个双端输入、双端输出的动态放大器。

- 10.一种基于权利要求1所述逐次逼近型模数转换器的模数转换处理方法,其特征在于,所述逐次逼近型模数转换器在一个处理周期进行的模数转换处理过程包括:

响应于采样时序信号中的有效电平,在采样阶段控制DAC电容阵列的输入端接通模拟输入信号,由所述DAC电容阵列对所述模拟输入信号采样并进行电荷保持;

响应于量化时序信号的有效电平,在量化阶段期间基于数字码控制所述DAC电容阵列产生与数字码对应的电压信号;

在所述电压信号中累加上一量化阶段结束后存储的残差电压信号以得到待比较信号, 经过比较器对所述待比较信号的逐次逼近式地比较,在量化结束时得到对应所述模拟输入 信号的二进制码;以及

在量化阶段结束时,响应于存储时序信号的有效电平,噪声整形电路中的一阶噪声整形电路和二阶噪声整形电路分次先后与所述DAC电容阵列的输出端电压进行电荷共享,以对当前量化阶段结束后产生的残差电压分次存储。

# 一种逐次逼近型模数转换器及模数转换处理方法

#### 技术领域

[0001] 本申请涉及模数转换技术领域,特别地涉及一种逐次逼近型模数转换器及模数转换处理方法。

# 背景技术

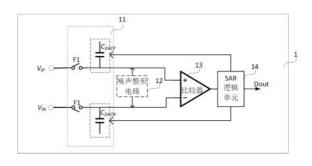

随着模数转换器 (Analog-to-Digital Converter, 简称ADC) 向低功耗、高分辨率 [0002] 的趋势发展,逐次逼近型模拟-数字转换器(Successive Approximation Analog-to-Digital Converter, 简称SAR ADC) 凭借着面积小、功耗低的优点越来越引起人们的注意。 参见图1,图1是现有技术中的差分输入的3位SARADC原理示意图。所述SARADC包括采样保持 电路、DAC电容阵列11、比较器13和逐次逼近(SAR)逻辑单元14,其中,采样保持电路通常由 采样电容构成,采样电容通常由构成所述的DAC电容阵列11的电容阵列实现。DAC电容阵列 11包括一组并联的二进制权重的电容阵列,每个电容的容量分别如图中所示的 $2^2C \cdot 2^1C \cdot$  $2^{0}\mathrm{C} \cdot 2^{0}\mathrm{C}$ 。DAC电容阵列11中的每个电容的第一极板连接到公共端,作为DAC电容阵列11的输 出端,DAC电容阵列11连接有电容切换的开关组,开关组中包括多个开关,DAC电容阵列11中 每个电容的第二极板与一个开关的第一端连接,开关的第二端连接一个差分信号输入端 (如图中的表示同相输入端电压V<sub>IP</sub>和反相输入端电压V<sub>IN</sub>的两端)、开关的第三端连接参考 高电平端(如图中的参考高电压V<sub>REPP</sub>),开关的第四端连接参考低电平端(如图中的参考低 电压V<sub>REEN</sub>),开关的第二端、第三端和第四端根据控制时序分别与第一端接通。DAC电容阵列 11的输出端通过采样控制开关F1连接共模信号端(如图中的共模电压Vol),同时连接到比较 器13的一个输入端。SAR逻辑单元14输出控制时序信号给各个开关。其中,在采样阶段,采样 控制开关F1闭合,DAC电容阵列11中的开关的第一端和第二端接通,将模拟输入信号采样到 DAC电容阵列11上,在采样控制开关F1断开后,模拟输入信号保持在DAC电容阵列11中。

[0003] 在量化阶段,SAR逻辑单元14按照量化时序向开关组发送对应不同数字码的控制信号,开关组中的各个开关根据与数字码对应的控制信号在第三端和第四端之间进行切换,以实现在数字码为"1"时将电容与参考高电压V<sub>REFP</sub>接通,在数字码为"0"时将电容与参考低电压V<sub>REFN</sub>接通,从而使得DAC电容阵列11中的电容阵列中的电荷重新分布而在输出端产生相应的电压,如图中所示,在DAC电容阵列11正相端产生同相输出端电压V<sub>DACP</sub>,在反相端产生反相输出端电压V<sub>DACN</sub>。由于DAC电容阵列11的输出端与比较器13的输入端连接,因而在DAC电容阵列11的输出端产生的电压送到比较器13中,由比较器对两个输入端的信号进行比较,SAR逻辑单元14根据比较结果得到对应的数字码"1"或"0",从而在量化阶段结束时得到对应模拟输入信号的数字码。

[0004] 所以在SAR ADC中,由于SARADC使用非线性过程将连续信号转换为离散电平,因而本身就会产生量化噪声。SARADC输入信号Vin、ADC输出数字码D<sub>OUT</sub>对应的电压量和量化噪声产生的量化误差Q之间满足以下公式(1-1):

$$D_{OUT} = V_{in} + Q \tag{1-1}$$

[0005] 参见图1,DAC电容阵列11的输出端电压V<sub>DAC</sub>、DAC电容阵列11的同相输出端电压

$V_{DACP}$ 、DAC电容阵列11的反相输出端电压 $V_{DACN}$ 、同相输入端电压 $V_{IP}$ 、反相输入端电压 $V_{IN}$ 满足以下公式(1-2):

$$V_{DAC} = V_{DACP} - V_{DACN} = V_{res} = V_{IP} - V_{IN} - D_{out} = V_{in} - D_{out}$$

(1-2)

[0006] 结合公式(1-1)和(1-2)可以得到公式(1-3):

$$V_{\text{res}} = -Q \tag{1-3}$$

[0007] 从而可知,在SAR ADC中,DAC电容阵列11的输出端电压 $V_{DAC}$ 即为残差电压 $V_{TRS}$ 中、数值上与量化误差Q相等。

[0008] 为了降低DAC电容阵列11在量化时的能量消耗,控制 DAC电容阵列11的开关采用 "先判决,再打开"的切换方案,当比较器13判断已经确定最低有效位后,模数转换完成,量 化周期中比较器13最后一次的比较结果不会反馈到DAC电容阵列11上,因而DAC电容阵列11输出端在量化结束后产生的残差电压Vres的大小只能表示前n-1位的量化噪声,而不是n位的量化噪声,如图1中的示例,DAC电容阵列11输出端在量化结束后产生的残差电压Vres的大小只能表示前2位的量化噪声,而不是3位。因而,传统的SAR ADC在量化阶段并不能有效 地消除全部的量化噪声影响。随着对SAR ADC分辨率的需求的提高,SAR ADC本身的量化噪声限制了其自身有效位数的增加。

## 发明内容

[0009] 针对现有技术中存在的技术问题,本申请提出了一种逐次逼近型模数转换器及模数转换处理方法,用以提高逐次逼近型模数转换器的有效位数。

[0010] 为了解决上述技术问题,本申请提供了一种逐次逼近型模数转换器,包括DAC电容阵列、噪声整形电路、比较器和SAR逻辑单元,所述DAC电容阵列的输入端连接模拟输入信号,所述比较器的输出端连接所述SAR逻辑单元,所述SAR逻辑单元输出控制信号给所述DAC电容阵列,在所述DAC电容阵列与所述比较器之间包括所述噪声整形电路,所述噪声整形电路包括一阶噪声整形电路和二阶噪声整形电路,其中,在量化阶段结束后的残差存储阶段,所述一阶噪声整形电路的信号输入端和二阶噪声整形电路的信号输入端按照存储时序顺次连接到所述DAC电容阵列的输出端,对量化阶段结束产生的残差电压分次存储;所述二阶噪声整形电路的信号输出端和所述一阶噪声整形电路的信号输出端和在下一量化阶段分别连接所述比较器的第一输入端和第二输入端,使所述比较器在下一量化阶段的逐次比较过程中减去存储的当前量化阶段的残差。

[0011] 可选地,所述一阶噪声整形电路包括一阶第一电容;一阶第一电容第一端在残差存储阶段作为信号输入端与所述DAC电容阵列的输出端连接,通过电荷共享存储在所述DAC电容阵列的输出端产生的量化残差电压以实现一阶残差存储;一阶第一电容第一端在下一量化阶段作为信号输出端连接所述比较器的第二输入端。

[0012] 可选地,所述一阶噪声整形电路进一步包括一阶第二电容和动态放大器,其中,所述一阶第一电容和所述一阶第二电容分别在相邻的一阶残差存储阶段接入所述动态放大器;对应地,在所述动态放大器的输入端连接所述一阶第一电容第一端/所述一阶第二电容第一端/所述一阶第一电容的第一端/所述一阶第一电容的第一端,将所述一阶第一电容/所述一阶第二电容中的残差电压放大后存储在对应

的所述一阶第二电容/所述一阶第一电容。

[0013] 可选地,所述一阶第一电容的容量与所述一阶第二电容的容量相同。

[0014] 可选地,所述动态放大器的放大倍数为所述一阶第一电容容量和从所述DAC电容阵列接入的电容容量的总和与所述一阶第一电容容量的比值。

[0015] 可选地,所述二阶噪声整形电路包括二阶第一电容,在残差存储阶段,在所述一阶噪声整形电路完成一阶残差存储后,二阶第一电容第一端作为信号输入端与所述DAC电容阵列的输出端连接,通过电荷共享实现二阶残差存储,二阶第一电容第二端在下一量化阶段作为信号输出端连接所述比较器的第一输入端。

[0016] 可选地所述模拟输入信号为差分信号,包括同相模拟输入信号和反相模拟输入信号;DAC电容阵列的输出端包括同相输出端和反相输出端;对应地,所述比较器的输入端包括一对同相输入端和一对反相输入端;所述噪声整形电路包括同相噪声整形电路和反相噪声整形电路;在量化阶段结束后的残差存储阶段,基于存储时序,同相一阶噪声整形电路的信号输入端和反相一阶噪声整形电路的信号输入端分别连接所述DAC电容阵列的同相输入端和反相输入端,在实现了一阶残差存储后,同相二阶噪声整形电路和反相二阶噪声整形电路并联后的两端分别连接所述DAC电容阵列的同相输入端和反相输入端;在下一量化阶段,同相一阶噪声整形电路的信号输出端和反相一阶噪声整形电路的信号输出端分别连接所述比较器第二同相输入端和第二反相输入端;在实现了一阶存储后,同相二阶噪声整形电路的信号输入端和反相二阶噪声整形电路的信号输入端和反相二阶噪声整形电路的信号输入端和反相二阶噪声整形电路的信号输出端和反相二阶噪声整形电路的信号输出端和反相二阶噪声整形电路的信号输出端和反相二阶噪声整形电路的信号输出端和反相二阶噪声整形电路的信号输出端和反相二阶噪声整形电路的信号输出端分别所述比较器的第一同相输入端和第一反相输入端。

[0017] 可选地,所述同相二阶噪声整形电路包括同相二阶电容,所述反相二阶噪声整形电路包括反相二阶电容,所述同相二阶电容和所述反相二阶电容容量相等;在实现二阶残差存储时,所述同相二阶电容和所述反相二阶电容并联,并联的第一端连接所述DAC电容阵列的同相输出端,并联的第二端连接所述DAC电容阵列的反相输出端。

[0018] 可选地同相噪声整形电路中的一阶噪声整形电路和反相噪声整形电路中的一阶噪声整形电路共用一个双端输入、双端输出的动态放大器。

[0019] 根据本申请的另一方面,本申请还提供了一种前述逐次逼近型模数转换器的模数转换处理方法,所述逐次逼近型模数转换器在一个处理周期进行的模数转换处理过程包括以下步骤:

响应于采样时序信号中的有效电平,在采样阶段控制DAC电容阵列的输入端接通模拟输入信号,由所述DAC电容阵列对所述模拟输入信号采样并进行电荷保持;

响应于量化时序信号的有效电平,在量化阶段期间基于数字码控制所述DAC电容阵列产生相应的电压信号;

在所述电压信号中累加上一量化阶段结束后存储的残差电压信号以得到待比较信号,经过比较器对所述待比较信号的逐次逼近式地比较,在量化结束时得到对应所述模拟输入信号的二进制码;以及

在量化阶段结束时,响应于存储时序信号的有效电平,噪声整形电路中的一阶噪声整形电路和二阶噪声整形电路分次先后与所述DAC电容阵列的输出端电压进行电荷共享,以对当前量化阶段结束后产生的残差电压分次存储。

[0020] 本申请提供的逐次逼近型模数转换器通过二阶级联电路在输入信号不发生衰减、 且仅增加一个比较器输入端的条件下实现了二阶前馈噪声整形,将低频噪声整形至高频, 从而减小了带内噪声,提高了SAR ADC的有效位数和精度。

#### 附图说明

[0021] 下面,将结合附图对本申请的优选实施方式进行进一步详细的说明,其中:

图1是现有技术中的差分输入的3位SARADC原理示意图;

图2是根据本申请的一个实施例的一种逐次逼近型模数转换器原理框图;

图3是根据本申请的一个实施例的前馈噪声整形时的逐次逼近型模数转换器的信号流图:

图4是根据本申请的一个实施例的一种逐次逼近型模数转换器的简化电路原理

图5是基于图4所示逐次逼近型模数转换器的简化电路的时序信号图; 图6是图4所示逐次逼近型模数转换器在采样阶段时的电路连接示意图; 图7是图4所示逐次逼近型模数转换器在量化阶段时的电路连接示意图; 图8是图4所示逐次逼近型模数转换器在一阶存储阶段时的电路连接示意图; 图9是图4所示逐次逼近型模数转换器在二阶存储阶段时的电路连接示意图; 图10是根据本申请另一个实施例的一种逐次逼近型模数转换器的简化电路原理

图:

图;

图11是基于图10所示逐次逼近型模数转换器的简化电路的时序信号图;以及 图12是根据本申请的一个实施例的逐次逼近型模数转换器在一个处理周期进行 模数转换处理的方法流程图。

## 具体实施方式

[0022] 为使本申请实施例的目的、技术方案和优点更加清楚,下面将结合本申请实施例中的附图,对本申请实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本申请一部分实施例,而不是全部的实施例。基于本申请中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本申请保护的范围。

[0023] 在以下的详细描述中,可以参看作为本申请一部分用来说明本申请的特定实施例的各个说明书附图。在附图中,相似的附图标记在不同图式中描述大体上类似的组件。本申请的各个特定实施例在以下进行了足够详细的描述,使得具备本领域相关知识和技术的普通技术人员能够实施本申请的技术方案。应当理解,还可以利用其它实施例或者对本申请的实施例进行结构、逻辑或者电性的改变。

[0024] 对于相关领域普通技术人员已知的技术、方法和设备可能不作详细讨论,但在适当情况下,所述技术、方法和设备应当被视为说明书的一部分。对于附图中的各单元之间的连线,仅仅是为了便于说明,其表示至少连线两端的单元是相互通信的,并非旨在限制未连线的单元之间无法通信。另外,两个单元之间线条的数目旨在表示该两个单元之间通信至少所涉及的信号数或至少具备的输出端,并非用于限定该两个单元之间只能如图中所示的信号来进行通信。

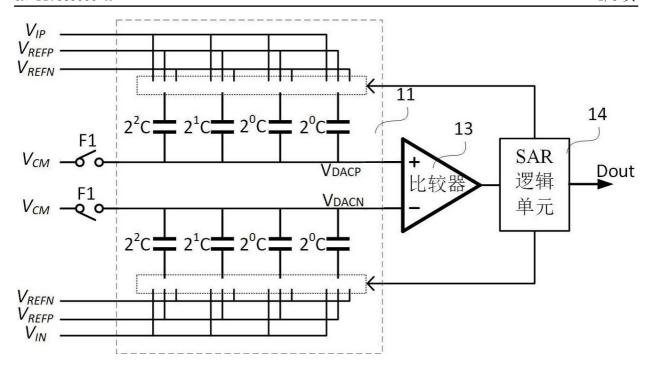

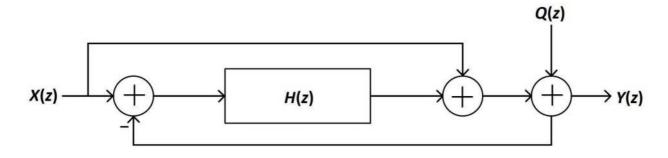

[0025] 图2是根据本申请一个实施例的一种逐次逼近型模数转换器原理框图。在本实施例中,逐次逼近型模数转换器1包括DAC电容阵列11、噪声整形电路12、比较器13和SAR逻辑单元14。其中,所述DAC电容阵列11连接模拟输入信号,比较器13的两个输入端分别与DAC电容阵列11的两个输出端连接,比较器13的输出端连接SAR逻辑单元14,SAR逻辑单元14向所述DAC电容阵列11发送量化时序信号,并输出对应模拟输入信号的数字码Dout。所述DAC电容阵列11、比较器13和SAR逻辑单元14在采样、量化时的工作过程与图1相似,在此不再赘述。本申请通过增加噪声整形电路12对逐次逼近型模数转换器1内的噪声进行整形,并将噪声整形电路12置于前馈路径,噪声整形电路12的输出信号直接输入至比较器13,从而实现前馈噪声整形。前馈噪声整形时的逐次逼近型模数转换器1的信号流图如图3所示。由信号流图得到逐次逼近型模数转换器1输入输出的关系如公式(2-1)所示:

$$[X(z) - Y(z)]H(z) + X(z) + Q(z) = Y(z)$$

(2-1)

[0026] 其中,所述X(z) 为z域的输入信号,Y(z) 为z域的输出信号,Q(z) 为逐次逼近型模数转换器1的量化噪声,H(z) 为噪声整形电路12的传输函数。

[0027] 对公式(2-1)整理得到公式(2-2):

$$Y(z) = X(z) + \frac{1}{1 + H(z)}Q(z)$$

(2-2)

[0028] 从公式(2-2)可以看出,前馈噪声整形容易构造极点,且在量化过程中信号不发生衰减。因而,本申请通过增加噪声整形电路12实现前馈噪声整形,在输入信号不发生衰减的条件下,仅增加一个比较器输入端,将低频噪声整形至高频,从而减小带内噪声,提高SAR ADC的有效精度。

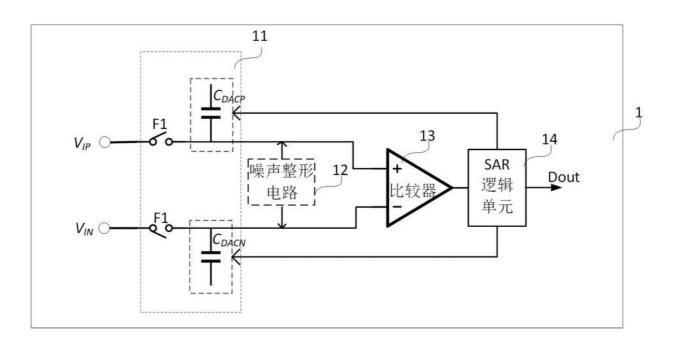

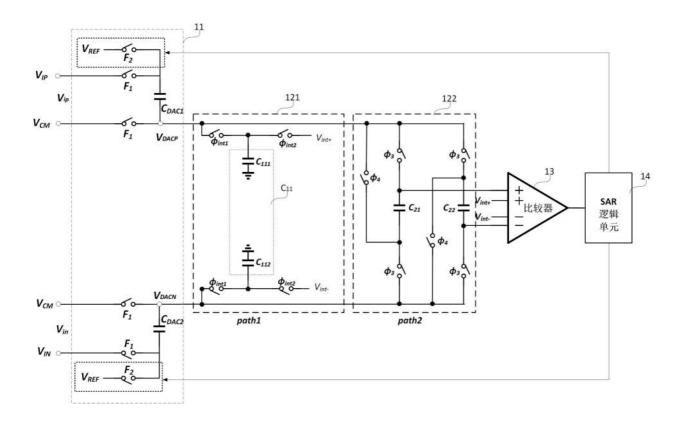

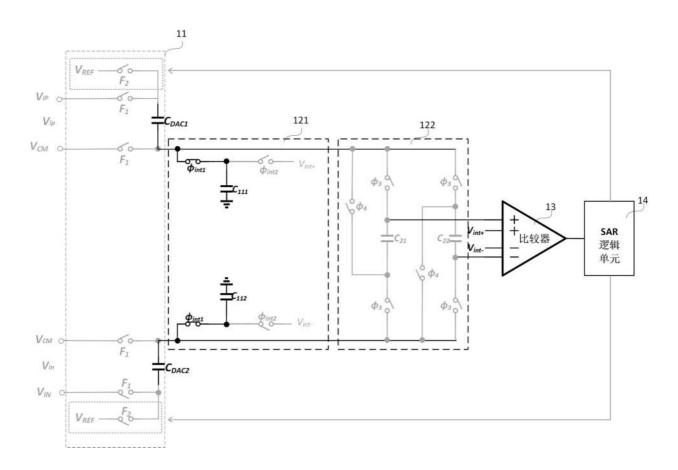

图4是根据本申请一个实施例的一种逐次逼近型模数转换器的简化电路原理图。 在图4中,模拟输入信号为差分信号,模拟输入信号的同相信号端(如图中的同相输入端电  $\mathbb{E}V_{IP}$ )与共模信号端(如图中的共模电压 $V_{CM}$ )构成同相模拟输入信号 $V_{in}$ ,模拟输入信号的反 相信号端(如图中的反相输入端电压V1)与共模信号端(如图中的共模电压V1)构成反相模 拟输入信号V<sub>in</sub>。DAC电容阵列11包括同相电容阵列和反相电容阵列,DAC电容阵列11的输出 端包括同相输出端(如图中的同相输出端电压VDACP)和反相输出端(如图中的反相输出端 电压V<sub>nacy</sub>),对应地,所述噪声整形电路12也分别包括同相噪声整形电路和反相噪声整形电 路,如图4所示,与DAC电容阵列11的同相输出端连接的为同相噪声整形电路,与DAC电容阵 列11的反相输出端连接的为反相噪声整形电路。对应地,所述比较器13的输入端包括一对 同相输入端和一对反相输入端。噪声整形电路12包括一阶噪声整形电路121和二阶噪声整 形电路122。为了简化说明,本申请将DAC电容阵列11中的同相和反相的加权电容阵列分别 简化为一个第一转换电容 $C_{DAC1}$ 和一个第二转换电容 $C_{DAC2}$ 。在介绍一阶噪声整形电路121时, 以同相一阶噪声整形电路为例进行说明。同相一阶噪声整形电路包括一个同相一阶第一电 容C<sub>111</sub>,同相一阶第一电容C<sub>111</sub>第一端通过一个第一残差存储控制开关φ<sub>int1</sub>与所述DAC电容 阵列11的同相输出端连接,同相一阶第一电容C111第一端还通过一个第一量化控制开关 φ<sub>int2</sub>与比较器13的第二同相输入端V<sub>int+</sub>连接。同理,一阶噪声整形电路121中的反相一阶噪 声整形电路结构与同相一阶噪声整形电路结构相同,反相一阶噪声整形电路的反相一阶第 一电容 $C_{11}$ ,的第一端通过一个第一残差存储控制开关 $\varphi_{int}$ 连接所述DAC电容阵列11的反相 输出端,还通过一个第一量化控制开关 $\phi_{int2}$ 与比较器13的第二反相输入端 $V_{int}$ 连接。

[0030] 二阶噪声整形电路122包括两个等容量的二阶第一电容 $C_{21}$ 和二阶第二电容 $C_{22}$ ,二阶第一电容 $C_{21}$ 和二阶第二电容 $C_{22}$ 的各自的两端分别通过一个第二残差存储控制开关  $\phi_3$ 与所述DAC电容阵列11的同相输出端和反相输出端连接,同时,二阶第一电容 $C_{21}$ 的一端通过第二量化控制开关  $\phi_4$ 与所述DAC电容阵列11的同相输出端连接,二阶第一电容 $C_{21}$ 的另一端与比较器13的第一同相输入端连接。二阶第二电容 $C_{22}$ 的一端通过第二量化控制开关  $\phi_4$ 与所述DAC电容阵列11的反相输出端连接,二阶第一电容 $C_{22}$ 的另一端与比较器13的第一反相输入端连接。

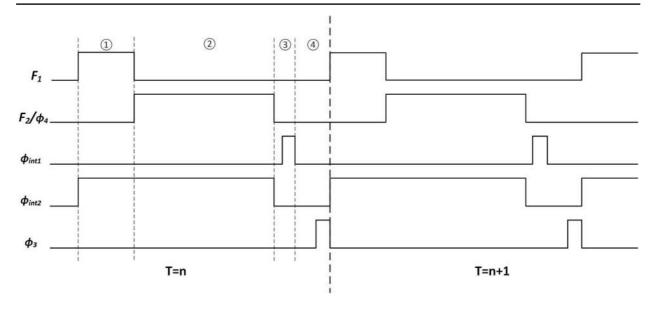

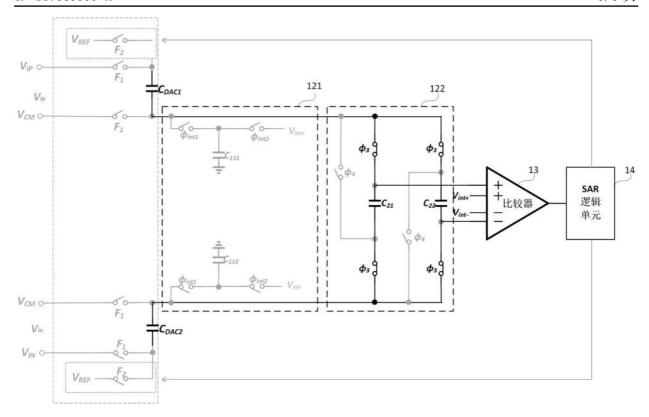

[0031] 图5是基于图4所示逐次逼近型模数转换器的简化电路的时序信号图。其中包括了两个周期的时序信号,其中时序信号中的高电平为有效电平。参考图4和图5,在T=n周期中,首先在采样阶段①,采样控制开关F1在采样时序信号的高电平期间,除了第一量化控制开关  $\phi_{int2}$ 的时序信号为高电平外,其他时序信号为低电平。连接DAC电容阵列11的采样控制开关F1响应于采样时序信号的高电平闭合,连接DAC电容阵列11的量化开关F2响应于量化时序信号的低电平断开,DAC电容阵列11接通模拟输入信号,如图中的同相模拟输入信号Vip和反相模拟输入信号Vin,第一转换电容CDACI和第二转换电容CDACI分别对同相模拟输入信号Vip和反相模拟输入信号Vin采样并进行电荷保持,参见图6,图6是图4所示逐次逼近型模数转换器在采样阶段时的电路连接示意图。从图6至图9,图中的灰色部分表示未工作电路。其中,模拟输入信号可连接到DAC电容阵列11中的电容的顶极板或底极板,本领域的普通技术人员在实际实施时可灵活选择。

[0032] 而后是量化阶段②,参见图7,图7是图4所示逐次逼近型模数转换器在量化阶段时的电路连接示意图。此时控制DAC电容阵列11的量化开关F2的量化时序信号为高电平,同时,控制一阶噪声整形电路121中的第一量化控制开关 $\varphi_{int2}$ 和控制二阶噪声整形电路122中第二量化控制开关 $\varphi_4$ 的量化时序信号为高电平,其余时序信号为低电平。量化开关F2响应于量化时序信号的高电平在有效期内闭合,采样控制开关F1断开,DAC电容阵列11中的电容阵列基于量化阶段与数字码对应的控制信号切换与电容接通的参考电压 $V_{REF}$ 的高电平或低电平,从而使电容阵列中的电荷重新分布,并基于每一个数字码进行重新分布后在DAC电容阵列11的输出端产生电压信号。

[0033] 在量化阶段②,一阶噪声整形电路121中的第一量化控制开关 $\varphi_{int2}$ 和第二量化控制开关 $\varphi_{4}$ 闭合,一阶第一电容中存储的上一量化阶段的残差电压输入给比较器13,二阶第一电容 $C_{21}$ 和二阶第二电容 $C_{22}$  分别在同相端和反相端串入到DAC电容阵列11的输出端和比较器13之间,此时二阶第一电容 $C_{21}$ 和二阶第二电容 $C_{22}$ 在上一量化阶段实现了电压倍增,因而在量化阶段,将倍增的电压累加到DAC电容阵列11的输出端电压中,一起输入到比较器13。

[0034] 在量化阶段②结束后,在所述DAC电容阵列11的输出端产生的电压为全分辨率的 残差电压。而后为残差存储阶段,残差存储阶段分为两个阶段,首先是一阶存储阶段③,参见图8,图8是图4所示逐次逼近型模数转换器在一阶存储阶段时的电路连接示意图。而后是二阶存储阶段④,参见图9,图9是图4所示逐次逼近型模数转换器在二阶存储阶段时的电路 连接示意图。其中,在一阶存储阶段③,首先控制第一残差存储控制开关  $\varphi_{int1}$ 的时序信号为高电平,以同相一阶噪声整形电路为例,所述DAC电容阵列11的同相输出端与同相一阶第一电容 $C_{111}$ 接通,第一转换电容 $C_{DAC1}$ 与同相一阶第一电容 $C_{111}$ 进行电荷共享,从而在同相一

阶第一电容C<sub>111</sub>中存储第一残差电压。

[0035] 而后,控制第二残差存储控制开关  $\varphi_3$ 的时序信号为高电平,二阶噪声整形电路 122中的二阶第一电容 $C_{21}$ 与所述DAC电容阵列11的同相输出端接通,二阶第一电容 $C_{21}$ 继续 与所述DAC电容阵列11中的第一转换电容 $C_{DAC1}$ 进行电荷共享,从而在二阶第一电容 $C_{21}$ 中存储第二残差电压。

[0036] 在本实施例中,在进行二阶残差存储时,二阶噪声整形电路122中的两个电容并联且容量相同,因而可使得每个电容上的电压与不并联时相比成倍增加。当第一转换电容  $C_{DAC1}$ 容量与一阶噪声整形电路121中的电容容量相同时,经过一阶噪声整形电路121的电容共享后,第一转换电容 $C_{DAC1}$ 容量减半,其输出端的残差电压减半,经过二阶残差存储时,可以将二阶噪声整形电路122中每个二阶电容的端电压倍增,提高了在下一量化阶段时累加到采样信号中的电压,降低了量化时产生的残差电压对当前量化的影响,能够有效提高SAR ADC的精度。

[0037] 综合图4至图9可见,本实施例在前馈路径增加的一阶噪声整形电路121和二阶噪声整形电路122构成了两条通路,其中一阶噪声整形电路121构成的通路实现一阶前馈积分,二阶噪声整形电路122构成的通路实现无源电压倍增积分。

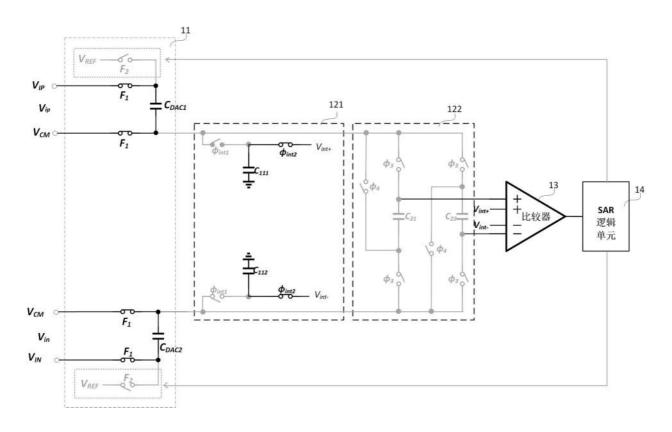

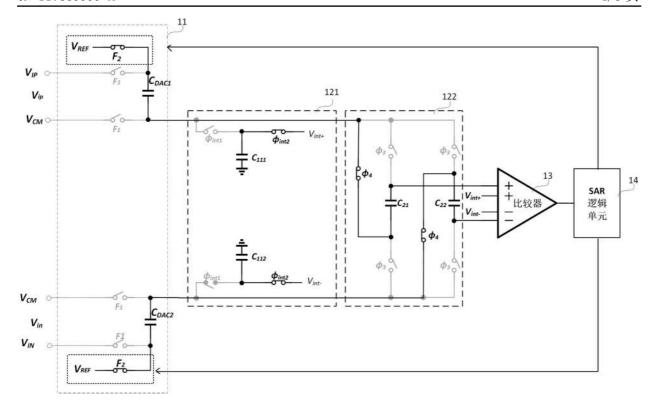

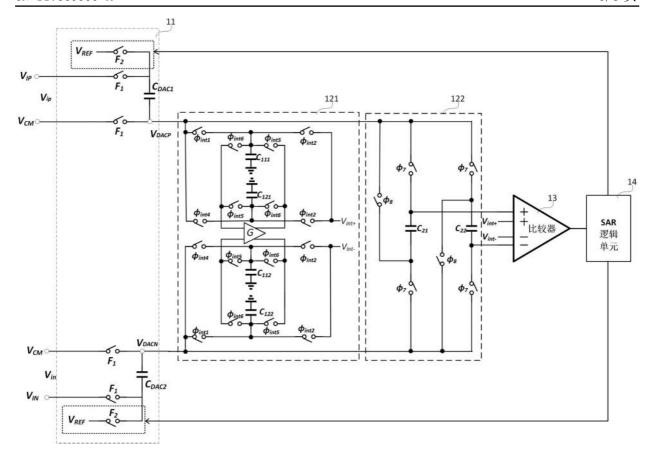

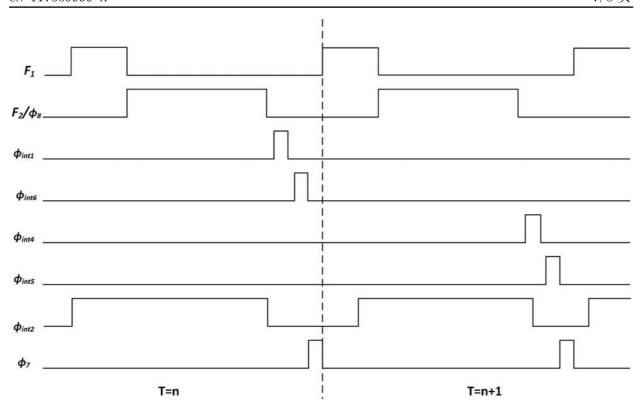

[0038] 图10是根据本申请另一个实施例的一种逐次逼近型模数转换器的简化电路原理图。图11是基于图10所示逐次逼近型模数转换器的简化电路的时序信号图。在本实施例中,一阶噪声整形电路121还包括一阶第二电容和动态放大器G,以同相一阶噪声整形电路为例,同相一阶第一电容 $C_{111}$ 第一端通过一个第一残差存储控制开关 $\phi_{int1}$ 与所述DAC电容阵列11的同相输出端连接,同相一阶第一电容 $C_{111}$ 第一端还通过一个第一量化控制开关 $\phi_{int2}$ 与比较器13的第二同相输入端 $V_{int+}$ 连接。

[0039] 同相一阶第一电容 $C_{111}$ 第一端还通过一个第三残差存储控制开关  $\phi_{int6}$ 与动态放大器G的一个输入端连接,动态放大器G的对应输出端通过一个第三残差存储控制开关  $\phi_{int6}$ 与一阶第二电容 $C_{121}$ 的第一端连接。

[0040] 参考图11,在一阶存储阶段,控制第一残差存储控制开关  $\varphi_{int1}$ 的时序信号首先为高电平,以同相一阶噪声整形电路121为例,所述DAC电容阵列11的同相输出端与同相一阶第一电容 $C_{111}$ 接通,第一转换电容 $C_{DAC1}$ 与同相一阶第一电容 $C_{111}$ 进行电荷共享,从而在同相一阶第一电容 $C_{111}$ 中存储第一残差电压。而后控制第三残差存储控制开关  $\varphi_{int6}$ 的时序信号为高电平,同相一阶第一电容 $C_{111}$ 与动态放大器G的一个输入端接通,同时,动态放大器G的对应输出端与同相一阶第二电容 $C_{121}$ 的第一端接通,动态放大器G对存储在同相一阶第一电容 $C_{111}$ 中的残差电压放大后存储在对应的同相一阶第二电容 $C_{121}$ 中,在量化阶段,同相一阶第二电容 $C_{121}$ 的第一端通过第一量化控制开关  $\varphi_{int2}$ 与比较器13的第二同相输入端 $V_{int+}$ 连接。

[0041] 在本实施例中,通过动态放大器G将存储在同相一阶第一电容C111中的残差电压放大,其放大倍数以使放大后的电压与电荷共享前所述DAC电容阵列11的同相输出端的残差电压相等。也就是说,动态放大器G放大倍数等于所述一阶第一电容容量和从所述DAC电容阵列接入的电容容量的总和与所述一阶第一电容容量的比值。

[0042] 例如,当 $C_{DAC1}$ = $C_{111}$ =C时,N= ( $C_{DAC1}$ + $C_{111}$ )/ $C_{111}$ =2C/C=2其中,N为放大倍数。当 $C_{DAC1}$ =2C, $C_{111}$ =C时,N= ( $C_{DAC1}$ + $C_{111}$ )/ $C_{111}$ =3C/C=3。以此类推。其中,一阶第一电容容量与DAC电容

阵列接入的电容容量相等为优选实施例。

[0043] 在完成量化阶段后,将最后一位数字码传输到电容阵列上,并在电容阵列输出端产生成当前时刻的残差电压 $V_{RES}$  (n),接入比较器13第二输入端的 $V_{int}$  (n-1)是上一周期中动态放大器的输出电压,代表上一周期所有残差电压的总和。当第一转换电容 $C_{DAC1}$ 与同相一阶第一电容 $C_{111}$ 进行电荷共享时,第一转换电容 $C_{DAC1}$ 在上存储的最新的残差电压 $V_{RES}$  (n)和同相一阶第一电容 $V_{111}$ 上存储的上一周期的残差电压 $V_{int+}$  (n-1)各减小一半。在当前周期的量化阶段,即量化时序信号  $\Phi_{int2}$ 期间,对同相一阶第一电容 $V_{111}$ 上积分到的残差电压进行2倍放大并存储在同相一阶第二电容 $V_{121}$ 上,那么由于之前无源积分所造成的电压衰减得到了完全补偿。

[0044] 另外,同相一阶第二电容 $C_{121}$ 第一端通过一个第四残差存储控制开关  $\phi_{int4}$ 与所述 DAC电容阵列11的同相输出端连接,同相一阶第二电容 $C_{121}$ 第一端还通过一个第一量化控制 开关  $\phi_{int2}$ 与比较器13的第二同相输入端 $V_{int+}$ 连接。

[0045] 同相一阶第二电容 $C_{121}$ 第一端还通过一个第五残差存储控制开关  $\phi_{int5}$ 与动态放大器G的另一个输入端连接,动态放大器G的对应输出端通过一个第五残差存储控制开关  $\phi_{int5}$ 与一阶第一电容 $C_{111}$ 的第一端连接。

[0046] 参考图11,在下一个周期的阶存储阶段,控制第四残差存储控制开关  $\varphi_{int4}$ 的时序信号首先为高电平,以同相一阶噪声整形电路为例,所述DAC电容阵列11的同相输出端与同相一阶第二电容 $C_{121}$ 接通,第一转换电容 $C_{DAC1}$ 与同相一阶第二电容 $C_{121}$ 进行电荷共享,从而在同相一阶第二电容 $C_{121}$ 中存储第一残差电压。而后控制第五残差存储控制开关  $\varphi_{int5}$ 的时序信号为高电平,同相一阶第二电容 $C_{121}$ 与动态放大器G的另一个输入端接通,同时,动态放大器G的对应输出端与同相一阶第一电容 $C_{111}$ 的第一电容 $C_{111}$ 的第一电容 $C_{121}$ 中的残差电压放大后存储在对应的同相一阶第一电容 $C_{111}$ 中,在量化阶段,同相一阶第一电容 $C_{111}$ 的第一端通过第一量化控制开关  $\varphi_{int2}$ 与比较器13的第二同相输入端 $V_{int4}$ 连接。

[0047] 通过图10和图11可见,一阶噪声整形电路121中的两个电容轮流交替地作为原始 共享电容和存储电压放大后的电容,从而使得在任一量化阶段在第二输入端输入给比较器 13的残差电压都是无损的残差电压。

[0048] 在本实施例中,同相噪声整形电路中的同相一阶噪声整形电路和反相噪声整形电路中的反相一阶噪声整形电路共用一个双端输入、双端输出的动态放大器G。反相噪声整形电路中的一阶噪声整形电路的结构及工作原理相同,在此不再赘述。当然,本申请中的同相一阶噪声整形电路和反相一阶噪声整形电路也可以使用各自的放大器,本领域的普通技术人员可以根据实际的应用需求采用一个或两个放大器,同理,当前噪声整形电路中的各种电容的数量也可以根据实际需要灵活设置,并不局限于本申请示例中的一个电容。

[0049] 二阶噪声整形电路122与图4中的电路相同,在此不再赘述。

[0050] 本申请中采用两对输入的比较器13,从而能够将前一周期产生的残差电压信号累加到模拟输入信号的采样信号中,并在比较器13的比较时降低了转换器的量化噪声的影响,进而提高了转换器的有效位数。

[0051] 以下通过具体实施例对本申请的SAR DAC的传递函数分析如下:

首先,在一阶噪声整形电路121中,由电荷守恒定律可知:

$$C_{DAC} \times V_{RES}(n) + C_{111} \times V_{int}(n-1) = (C_{DAC} + C_{111}) \times V_{int}(n)$$

(3-1)

$$[0052] \quad \stackrel{\text{def}}{=} C_{DAC} = C_{111} = C_{121} = C \tag{3-2}$$

[0053] 其中, $C_{DAC}$ 为DAC电容阵列11的电容容量, $V_{RES}$  (n) 为当前第n周期DAC电容阵列11输出端产生的残差电压, $V_{int}$  (n-1) 为上一周期在一阶第一电容 $C_{111}$ 上存储的残差电压, $V_{int}$  (n) 为当前第n周期在一阶第一电容 $C_{111}$ 上存储的残差电压。

[0054] 将公式(3-2)带入公式(3-1),并转换到z域可得:

$$V_{\text{int}}(n) = \frac{V_{RES}(n) + V_{\text{int}}(n-1)}{2}$$

(3-3)

[0055] 在经过动态放大器放大后存储到一阶第二电容 $C_{121}$ 上,此时一阶第二电容 $C_{121}$ 上最终的残差电压 $V_{int}$  (n) 为:

$$V'_{int}(n) = 2V_{int}(n) = V_{RES}(n) + V_{int}(n-1)$$

(3-4)

[0056] 整理后可得一阶噪声整形电路121对残差积分的传递函数为:

$$V'_{int}(z) = \frac{1}{1 - z^{-1}} V_{RES}(z)$$

(3-5)

[0057] 而后,在二阶噪声整形电路122中,由于DAC电容阵列11的电容 $C_{DAC}$ 上的残差电压已经经一阶噪声整形电路121的电荷共享,所以此时DAC电容阵列11的电容 $C_{DAC}$ 上所存储的残差电压为当前时刻残差电压的一半,在第二残差存储期间(或称为积分阶段),两个二阶电容与DAC电容阵列11的电容 $C_{DAC}$ 进行无源电荷共享,由于两个二阶第一电容 $C_{21}$ 和二阶第二电容 $C_{22}$ 构成并联关系,所以在二阶第一电容 $C_{21}$ 和二阶第二电容 $C_{22}$ 上得到的残差电压为传统连接方式的2倍。由电荷守恒定律可知:

$$C_{DAC} \times \frac{1}{2} V_{RES}(n) + 2(C_{21} + C_{22}) \times V_{int}(n-1) = (C_{DAC} + 2 \times (C_{21} + C_{22})) \times V_{int}(n)$$

(3-6)

[0058]  $\sharp h$ ,  $C_{DAC} = 2C_{21} = 2C_{22} = C$  (3-7)

[0059] 将(3-7)带入(3-6),并转换到z域可得二阶噪声整形电路122对残差积分的传递函数为公式(3-8):

$$V_{\rm int}(z) = \frac{1}{6 - 4z^{-1}} V_{RES}(z) \tag{3-8}$$

[0060] 根据梅森定律, SAR ADC的传递函数为公式(3-9):

$$D_{OUT}(z) = V_{IN}(z) + (1 - z^{-1})(6 - 4z^{-1})Q(z)$$

(3-9)

[0061] 其中, $D_{OUT}(z)$  为z域的SAR ADC输出的数字码对应的电压量, $V_{IN}(z)$  为z域的SAR ADC输入信号的电压,Q(z) 为z域的SAR ADC的量化噪声对应的量化误差。

[0062] 通过公式(3-9)所示的传递函数可知,本申请有效地抑制了量化噪声对模数转换精度的影响。

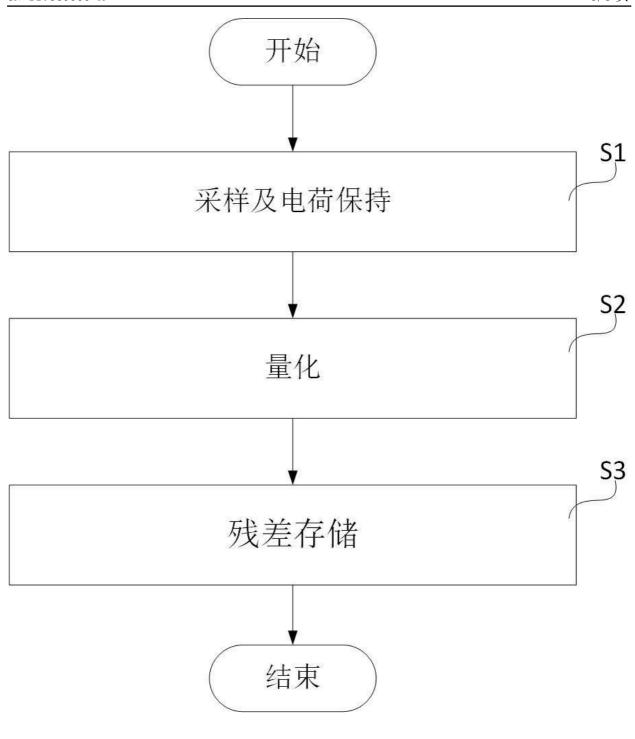

[0063] 图12是根据本申请一个实施例的逐次逼近型模数转换器在一个处理周期进行模数转换处理的方法流程图,包括以下步骤:

步骤S1,采样及电荷保持。其中,基于采样时序信号,在采样阶段控制DAC电容阵列

接通模拟输入信号,由所述DAC电容阵列11对所述模拟输入信号采样并进行电荷保持。

[0064] 步骤S2,量化。基于量化时序信号,所述DAC电容阵列11在量化阶段产生相应的电压信号,在所述电压信号中累加上一量化阶段结束后存储的残差电压信号以得到待比较信号,经过比较器对所述待比较信号的逐次逼近式地比较,在量化结束时得到对应所述模拟输入信号的二进制码。

[0065] 步骤S3,残差存储。在量化阶段结束时,基于存储时序信号,由噪声整形电路中的一阶噪声整形电路和二阶噪声整形电路分次与所述DAC电容阵列进行电荷共享,以对当前量化阶段结束后产生的残差电压分次存储,用于在下一量化阶段时累加到信号中。

[0066] 而后返回步骤S1执行下一个周期的处理流程。

[0067] 具体地,在每个处理周期中,在对当前量化阶段结束后产生的残差电压分次存储时依次包括以下步骤:

在存储时序信号中的一阶存储信号有效期间,通过一阶电容与所述DAC电容阵列进行电荷共享以在一阶电容中存储第一残差电压。

[0068] 在存储时序信号中的二阶存储信号有效期间,通过二阶电容与所述DAC电容阵列进行电荷共享以在二阶电容中存储第二残差电压;其中,二阶存储信号的有效开始时刻在一阶存储信号有效期结束时刻之后。

[0069] 所述在一阶电容包括一阶第一电容和一阶第二电容,在通过一阶电容与所述DAC 电容阵列进行电荷共享时包括:

所述一阶第一电容与所述DAC电容阵列进行电荷共享以在所述一阶第一电容中存储第三残差电压。

[0070] 通过动态放大器对所述第三残差电压进行放大并存储在所述一阶第二电容中,所述一阶第二电容的第一端为下一量化阶段提供当前量化阶段产生的残差电压,其中,存储在所述一阶第二电容中的电压与共享前所述DAC电容阵列的输出电压相等。

[0071] 在下一残差存储阶段,所述一阶第二电容与所述DAC电容阵列进行电荷共享以在所述一阶第二电容中存储第四残差电压。

[0072] 通过动态放大器对所述第四残差电压进行放大并存储在一阶第一电容中,所述一阶第一电容的第一端为接下来的下一量化阶段提供其当前量化阶段产生的残差电压;其中,存储在所述一阶第一电容中的电压与共享前所述DAC电容阵列的输出电压相等。

[0073] 在二阶存储信号有效期间,二阶电容第一端作为信号输入端与所述DAC电容阵列的输出端连接,通过电荷共享实现二阶残差存储;所述二阶电容第二端在下一量化阶段为比较器提供当前量化阶段产生的残差电压。

[0074] 所述二阶电容包括二阶第一电容和二阶第二电容,在二阶存储信号有效期间,二阶第一电容和二阶第二电容并联,并与所述DAC电容阵列中的电容阵列进行电荷共享。

[0075] 本申请提供的逐次逼近型模数转换器通过噪声整形降低了带内噪声,能够有效提高转换器的有效位数,并且不需要使用运算跨导放大器,功耗低;本申请中的逐次逼近型模数转换器采用DAC电容阵列同时实现采样、电荷保持及量化,因而电路的复杂度低,实现难度小、可靠性高。

[0076] 上述实施例仅供说明本申请之用,而并非是对本申请的限制,有关技术领域的普通技术人员,在不脱离本申请范围的情况下,还可以做出各种变化和变型,因此,所有等同

的技术方案也应属于本申请公开的范畴。

图 1

图 2

图 3

图 4

图 5

图 6

图 7

图 8

图 9

图 10

图 11

图 12