#### (19) **日本国特許庁(JP)**

# (12) 特許公報(B2)

(11)特許番号

特許第4480341号 (P4480341)

(45) 発行日 平成22年6月16日(2010.6.16)

(24) 登録日 平成22年3月26日(2010.3.26)

| (45) 発行日 平成225 | ≢6月16日 (2010. 6. 16)  |          |             | (24) 登録日    | 平成22年3月26       | 5日 (2010.3.26) |

|----------------|-----------------------|----------|-------------|-------------|-----------------|----------------|

| (51) Int.Cl.   | F I                   | -        |             |             |                 |                |

| GO9G 3/28      | (2006.01)             | GO9G     | 3/28        | Н           |                 |                |

| GO9G 3/20      | (2006.01)             | G09G     | 3/28        | K           |                 |                |

| HO3K 5/13      | •                     | GO9G     | 3/20        | 611J        |                 |                |

| HO3K 17/00     | •                     | G09G     |             | 612R        |                 |                |

| HO3K 17/693    | (2006.01)             | GO9G     | 3/20        | 622M        |                 |                |

|                |                       |          |             | 請求項の数 1     | (全 26 頁)        | 最終頁に続く         |

| (21) 出願番号      | 特願2003-106839 (P2003- | 106839)  | (73) 特許権    | 者 599132708 |                 |                |

| (22) 出願日       | 平成15年4月10日 (2003.4    |          |             |             | ディスプレイ树         | <b>术式会</b> 社   |

| (65) 公開番号      | 特開2004-309983 (P2004- | 309983A) |             | 宮崎県東諸県      | 郡国富町大字田         | 3月1815番        |

| (43) 公開日       | 平成16年11月4日 (2004.1    | 1.4)     |             | 地 1         |                 |                |

| 審査請求日          | 平成18年2月28日 (2006.2    | . 28)    | (74) 代理人    | 100080001   |                 |                |

|                |                       |          |             | 弁理士 筒井      | 大和              |                |

|                |                       |          | (72) 発明者    |             |                 |                |

|                |                       |          |             |             | 市高津区坂戸3         |                |

|                |                       |          |             |             | <b>プラズマディ</b> ス | スプレイ株式会        |

|                |                       |          | (50) RABE + | 社内          |                 |                |

|                |                       |          | (72) 発明者    |             | *******         | 700#10         |

|                |                       |          |             |             | 市高津区坂戸3         |                |

|                |                       |          |             |             | プラズマディス         | ペプレイ 休式会       |

|                |                       |          |             | 社内          |                 |                |

|                |                       |          |             |             | 昂               | <b>最終頁に続く</b>  |

### (54) 【発明の名称】プラズマディスプレイ装置

### (57)【特許請求の範囲】

## 【請求項1】

複数のX電極と、

該複数のX電極に略平行に配置され、該複数のX電極との間に放電を発生させる複数のY電極と、

前記複数のX電極にサステイン放電電圧を印加するX電極駆動回路と、

前記複数のY電極に<u>サステイン</u>放電電圧を印加するY電極駆動回路と、を有するプラズマディスプレイ装置であって、

前記X電極駆動回路または前記Y電極駆動回路は、

前記第1の入力端子から入力された第1の入力信号のフロントエッジを遅延させる第1 のフロントエッジ遅延回路と、

前記第1のフロントエッジ遅延回路を介して得られた遅延信号から第1のパルス幅を有する第1の駆動制御信号を生成する第1のパルス幅調整回路と、

前記第1の駆動制御信号を増幅する第1の増幅回路と、

前記第1の増幅回路によって増幅された前記第1の駆動制御信号のタイミングで、対応する前記X電極または前記Y電極に高電圧を印加する第1のサステイン出力スイッチ素子と、

第2の入力端子と、

前記第2の入力端子から入力された第2の入力信号のフロントエッジを遅延させる第2 のフロントエッジ遅延回路と、

前記第2のフロントエッジ遅延回路を介して得られた遅延信号から第2のパルス幅を有する第2の駆動制御信号を生成する第2のパルス幅調整回路と、

前記第2の駆動制御信号を増幅する第2の増幅回路と、

前記第2の増幅回路によって増幅された前記第2の駆動制御信号のタイミングで、対応する前記X電極または前記Y電極に低電圧を印加する第2のサステイン出力スイッチ素子とを有し、

<u>前記第1および前記第2のフロントエッジ遅延回路は、クロック信号をカウントする第</u>1および第2のカウンタであり、

前記第1および前記第2のパルス幅調整回路は、前記クロック信号をカウントする第3 および第4のカウンタであり、

前記第1および前記第2のカウンタのカウント値を変化させることにより前記第1および前記第2の入力信号の遅延時間を調整し、前記第3および前記第4のカウンタのカウント値を変化させることにより前記第1および前記第2の駆動制御信号のパルス幅を調整することを特徴とするプラズマディスプレイ装置。

【発明の詳細な説明】

[00001]

【発明の属する技術分野】

本発明は、容量性負荷駆動回路およびプラズマディスプレイ装置に関し、特に、プラズマディスプレイパネル(PDP: Plasma Display Panel)の画素のような容量性負荷を駆動する容量性負荷駆動回路およびプラズマディスプレイ装置に関する。

[0002]

近年、薄型の表示装置としてプラズマディスプレイ装置が実用化されている。プラズマディスプレイパネルの各画素のような容量性負荷を駆動する容量性負荷駆動回路において、遅延回路によって遅延時間を調整すると、サステインパルスのパルス幅がばらつく可能性がある。例えば、サステインパルスのパルス幅が大きくなると、タイムマージンの減少や異常電流の発生等が生じる。一方、サステインパルスのパルス幅が小さくなると、サステイン電圧の立ち上がりおよび立ち下がり波形にノイズが重畳されて、プラズマディスプレイ装置における動作マージンが減少し、また、画面のチラツキが発生する。そこで、遅延回路によって遅延時間を調整した場合等に生じる出力パルス幅変動を低減し、適切な出力電圧を容量性負荷に供給することのできる容量性負荷駆動回路の提供が要望されている。さらに、タイムマージンの減少や、異常電流およびノイズ等の問題がない駆動電圧をプラズマディスプレイパネルへ供給することのできるプラズマディスプレイ装置の提供も要望されている。

[0003]

【従来の技術】

近年、プラズマディスプレイパネルは、自己発光型であるため視認性がよく、薄型で大画面表示および高速表示が可能であることから、CRTに替わる表示パネルとして実用化されている。

[0004]

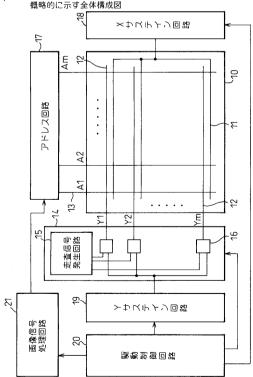

図1は本発明が適用されるプラズマディスプレイ装置の一例を概略的に示す全体構成図であり、一般的な三電極面放電交流駆動型のプラズマディスプレイ装置を示すものである。 図1において、参照符号10はPDP、11は第1の電極(X電極)、12は第2の電極 (Y電極)、13はアドレス電極、そして、14はスキャンドライバを示している。

[0005]

図 1 に示されるように、一般的な P D P 1 0 は、 n 本の X 電極 1 1 と Y 電極 1 2 ( Y 1 ~ Y n )とを隣接して交互に配置して、 n 組の X 電極 1 1 と Y 電極 1 2 の組を形成し、各組の X 電極 1 1 と Y 電極 1 2 の間で表示のための発光を行う。 Y 電極と X 電極は表示電極と呼ばれるが、維持電極またはサステイン電極とも呼ばれることもある。 m 本のアドレス電極 1 3 ( A 1 ~ A m )は、表示電極と垂直な方向に設けら、各アドレス電極 1 3 と X 電極 1 1 および Y 電極 1 2 の各組との交点部分にそれぞれ表示セルが形成される。

10

20

30

40

#### [00006]

Y電極12は、スキャンドライバ14に接続されている。スキャンドライバ14にはY電極の本数分のスイッチ16が設けられており、アドレス期間には走査信号発生回路15からのスキャンパルスが順に印加されるように切り換えられ、維持放電期間には、Yサステイン回路19からのサステインパルスが同時に印加されるように切り換えられる。X電極11はXサステイン回路18に共通に接続され、また、アドレス電極13はアドレスドライバ17に接続される。画像信号処理回路21は、画像信号をプラズマディスプレイ装置内部での動作に適した形式に変換した後、アドレス回路17に供給する。駆動制御回路20は、プラズマディスプレイ装置の各部を制御する信号を発生して供給する。

[0007]

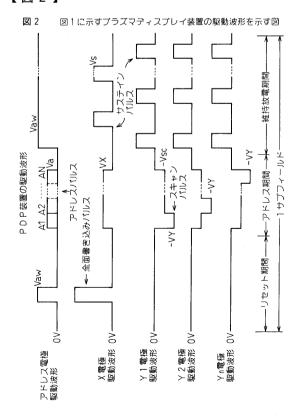

図2は図1に示すプラズマディスプレイ装置の駆動波形を示す図である。

[00008]

プラズマディスプレイ装置は、1つの表示画面を所定の周期毎に書き換えながら表示しており、1表示周期を1フィールドと称する。階調表示を行う場合には、1フィールドをさらに複数のサブフィールドに分割し、表示セル毎に発光するサブフィールドを組み合わせて表示を行う。各サブフィールドは、全表示セルを初期化するリセット期間と、全表示セルを表示する画像に対応した状態に設定するアドレス期間と、設定された状態に応じて各表示セルを発光させる維持放電(サステイン)期間とで構成される。維持放電期間には、X電極とY電極に交互に維持(サステイン)パルスが印加され、アドレス期間に発光するように設定された表示セルで維持放電が行なわれ、これが表示のための発光になる。

[0009]

プラズマディスプレイ装置では、維持放電期間に、電極間に最大で200V程度の電圧を高周波数のパルスとして印加する必要があり、特に、サブフィールド表示で階調表示を行うものではパルス幅は数μsである。このような高電圧で且つ高周波の信号で駆動するため、一般にプラズマディスプレイ装置の消費電力は大きく、省電力化が要望されている。

[0010]

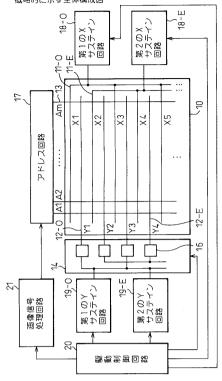

図 3 は本発明が適用されるプラズマディスプレイ装置の他の例を概略的に示す全体構成図であり、ALIS方式(Alternate Lighting of surface method)のプラズマディスプレイ装置を示すものである。

[0011]

図3に示されるように、ALIS方式のPDPでは、n本のY電極(第2の電極)12‐〇および12‐Eとn+1本のX電極(第1の電極)11‐〇および11‐Eを隣接して交互に配置し、全ての表示電極(Y電極とX電極)の間で表示発光を行う。従って、2n+1本の表示電極で、2n本の表示ラインが形成される。つまり、ALIS方式は、図1の構成と同等の表示電極数で2倍の精細度が実現できる。また、放電空間を無駄なく使用でき、さらに、電極などによる遮光が小さいため高い開口率が得られ、高輝度が実現できるという特徴を有する。なお、ALIS方式では、全ての表示電極間を表示のための放電に利用するが、それらの放電を同時に発生することはできない。そこで、表示を奇数ラインと偶数ラインで時間的に分割する、いわゆるインターレース走査を行う。奇数フィールドでは奇数番目の表示ラインで表示を行い、偶数フィールドでは偶数番目の表示ラインで表示を行って、全体として奇数フィールドと偶数フィールドの表示を合わせた表示を得るようになっている。

[0012]

Y電極はスキャンドライバ14に接続されている。スキャンドライバ14にはスイッチ16が設けられており、アドレス期間には順にスキャンパルスが印加されるように切り換えられ、維持放電期間には、奇数のY電極12-0は第1のYサステイン回路19-0に、偶数のY電極12-Eは第2のYサステイン回路19-Eに接続されるように切り換えられる。このとき、奇数のX電極11-Oは第1のXサステイン回路18-0に、偶数のX電極11-Eは第2のXサステイン回路18-Eに接続される。また、アドレス電極13は、アドレスドライバ17に接続される。画像信号処理回路21と駆動制御回路20は、

10

20

30

40

10

20

30

40

50

図1で説明したのと同様の動作を行う。

### [0013]

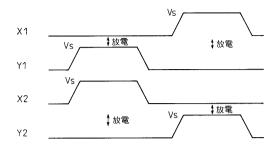

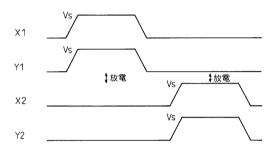

図4は図3に示すプラズマディスプレイ装置における維持放電期間の駆動波形を示す図であり、図4(a)は奇数フィールドの波形を示し、また、図4(b)は偶数フィールドの波形を示す。奇数フィールドでは、電極Y1とX2に電圧Vsを印加し、電極X1とY2をグランドレベルとし、電極X1とY1間および電極X2とY2間で、すなわち、奇数表示ラインで放電を行なわせる。このとき、偶数表示ラインの電極Y1とX2の間の電位差はゼロであり、放電は発生しない。同様に、偶数フィールドでは、電極X1とY2に電圧Vsを印加し、電極Y1とX2をグランドレベルとし、電極Y1とX2間および電極Y2とX1間で、すなわち、偶数表示ラインで放電を発生させる。リセット期間やアドレス期間の駆動波形についての説明は省略する。

[0014]

ところで、従来、サステインパルスの立ち上がり・立ち下がりタイミングのずれや形状のずれのないサステイン回路を有し、低消費電力で誤動作しないプラズマディスプレイ装置が提案されている(例えば、特許文献 1 参照)。

[0015]

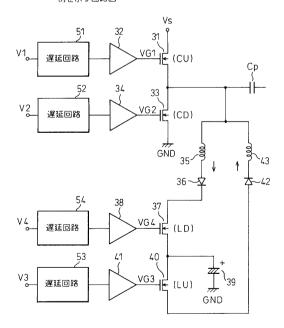

図 5 は従来のプラズマディスプレイ装置におけるサステイン回路(容量性負荷駆動回路)の一例を示す回路図であり、電力を回収する回収経路と蓄積した電力を印加する印加経路を分離した電力回収回路を有するサステイン回路を示すものである。なお、信号 V 1 ~ V 4 を発生する回路も設けられているが、ここでは省略してある。参照符号 C p は P D P ( 1 0 )の X 電極と Y 電極で形成される表示セルの駆動容量を示す。図 5 では、一方の電極のサステイン回路を示したが、他方の電極にも同様のサステイン回路が設けられている。

[0016]

まず、電力回収回路のないサステイン回路は、スイッチ素子(サステイン出力素子: nチャネル型MOSトランジスタ)31および33、増幅回路(ドライブ回路)32および34、並びに、遅延回路(フロントエッジ遅延回路)51および52を備えて構成され、また、電力回収回路は、スイッチ素子37および40、増幅回路38および41、並びに、遅延回路(フロントエッジ遅延回路)54および53を備えて構成される。

[0017]

入力信号 V 1 および V 2 は、それぞれ遅延回路 5 1 および 5 2 を介して増幅回路 3 2 および 3 4 に入力され、これら増幅回路 3 2 および 3 4 から出力される信号 V G 1 および V G 2 がスイッチ素子 3 1 および 3 3 のゲートに供給される。ここで、入力信号 V 1 が高レベル『H』の時にはスイッチ素子 3 1 がオンし、高レベル『H』の信号が電極(X 電極または Y 電極)に印加される。このとき、入力信号 V 2 は低レベル『L』となってスイッチ素子 3 3 はオフする。さらに、入力信号 V 1 が低レベル『L』になってスイッチ素子 3 1 がオフすると、同時に入力信号 V 2 が高レベル『H』になってスイッチ素子 3 3 がオンし、電極にはグランドレベルの電位が印加される。

[0018]

一方、電力回収回路を有するサステイン回路において、サステインパルスを印加する時には、入力信号 V 1 が高レベル『H』になる前に、入力信号 V 2 が低レベル『L』になりスイッチ素子 3 3 がオフした後、入力信号 V 3 が高レベル『H』になってスイッチ素子 4 0 がオンして容量 3 9、ダイオード 4 2、インダクタンス 4 3 および容量 C p で共振回路が形成され、容量 3 9に蓄積された電力が電極に供給されて電極の電位が上昇する。この電位の上昇が終了する直前に入力信号 V 3 が低レベル『L』になってスイッチ素子 4 0 がオフし、さらに、入力信号 V 1 が高レベル『H』になってスイッチ素子 3 1 がオンして、電極の電位を V s に固定する。

[0019]

また、サステインパルスの印加を終了する時には、まず、入力信号 V 1 が低レベル『L』になりスイッチ素子 3 1 がオフした後、入力信号 V 4 が高レベル『H』になってスイッチ素子 3 7 がオンし、容量 3 9 、ダイオード 3 6 、インダクタンス 3 5 および容量 C p で共

振回路が形成され、容量Cpに蓄積された電荷が容量39に供給されて容量39の電圧が上昇する。これにより、電極に印加されたサステインパルスにより容量Cpに蓄積された電力が容量39に回収される。この電極の電位の低下が終了する直前に入力信号V4が低レベル『L』になってスイッチ素子37がオフし、さらに、入力信号V2が高レベル『H』になってスイッチ素子33がオンし、電極の電位がグランドに固定される。維持放電期間の間は、サステインパルス数だけ上記の動作を繰り返す。以上の構成により、維持放電に伴う消費電力を低減することが可能になる。

#### [0020]

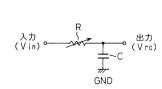

図6は図5に示すサステイン回路における遅延回路の一例を示す回路図である。

#### [0021]

図6に示されるように、遅延回路51(52~54)は、入力端子から入力される入力信号V1(V2~V4)のフロントエッジを遅延させる回路であり、可変抵抗(可変抵抗素子)Rおよび容量(容量素子)Cを備え、可変抵抗Rの抵抗値を可変することにより各入力信号の遅延時間を制御するようになっている。すなわち、遅延回路51,52,53,54により、後段に接続されている増幅回路32,34,41,38の遅延時間のバラツキを補正して、スイッチ素子31,33,40,37を適切なタイミングで駆動できるように、各スイッチ素子に供給するドライブパルスの位相を調整するようになっている。

#### [0022]

これにより、プラズマディスプレイパネルへ適切なタイミングのサステインパルスを供給すると共に、増幅回路の遅延時間のバラツキによって生じる電力増加を抑えることが可能 になる。

#### [0023]

また、従来、交流駆動型 P D P の駆動装置において、電力回収回路が正常に動作しなかった場合、駆動装置における出力ロスが大きくなって該駆動装置を構成する各素子の発熱量が増加するが、駆動装置の各素子を耐圧の大きい部品等で構成することなく、また、電力回収回路が正常に動作しなかった場合でも素子破壊等の発生を防止することができるプラズマディスプレイ装置が提案されている(例えば、特許文献2参照)。

#### [0024]

#### 【特許文献1】

特開 2 0 0 1 - 2 8 2 1 8 1 号公報

#### 【特許文献2】

特開2002-215087号公報

#### [0025]

### 【発明が解決しようとする課題】

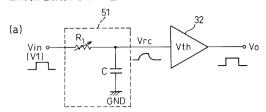

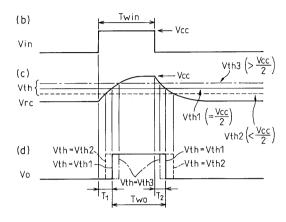

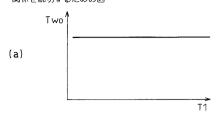

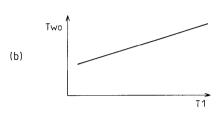

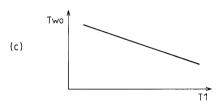

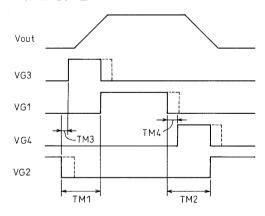

図7は従来のサステイン回路における増幅回路の閾値電圧と出力パルス幅との関係を説明するための図であり、上述した図5に示すサステイン回路における課題を説明するための図である。また、図8は従来のサステイン回路における遅延時間と出力パルス幅との関係を説明するための図であり、そして、図9は従来のサステイン回路における出力パルス幅が大きい場合の動作波形を示す図である。

#### [0026]

図7(a)は、前述した図5に示すサステイン回路において、遅延回路(51)として図6の回路を適用し、1つのスイッチ素子(31)を駆動する要部回路(遅延回路51および増幅回路32)を示している。ここで、図7(a)の回路において、入力信号をVin(V1)、遅延回路51における可変抵抗Rおよび容量Cの接続ノードの電圧をVrc、増幅回路32の閾値電圧をVth、そして、増幅回路の出力電圧をVoとする。このとき、各電圧Vin,Vrc,VthおよびVoの波形は図7(b)~図7(d)のようになる。なお、説明を簡潔にするために増幅回路32での遅延時間を零とする。また、他の遅延回路(52,53,54)および増幅回路(34,41,38)で構成される要部回路も同様である

。 【 0 0 2 7 】 10

20

30

10

20

30

40

50

まず、入力信号 Vinの高レベル『H』の電圧を Vccとすると、増幅回路 3 2 の閾値電圧 Vthが、 Vth = Vth 1 = Vcc / 2 の時、可変抵抗 R および容量 C によるフロントエッジ(立ち上がりエッジ)の遅延時間 T 1 は、バックエッジ(立ち下がりエッジ)の遅延時間 T 2 と等しくなる。従って、入力信号のパルス幅 Twinと増幅回路 3 2 の出力信号 Voのパルス幅 Twoは等しくなる。なお、遅延回路 5 1 における可変抵抗 R の抵抗値を大きくして遅延時間 T 1 を増加させた場合でも、パルス幅 Twoは一定である(図 8 ( a ) を参照)。

#### [0028]

次に、閾値電圧 V thが、 V th = V th 2 < V cc / 2 の時は、図 7 ( d ) の破線で示すような出力波形となり、T 1 < T 2、従って、T win < T woとなる。このとき、T 1 と T woの関係は、図 8 ( b ) に示されるように、遅延時間 T 1 が大きくなるほど出力信号 V oのパルス幅 T woも大きくなる。そして、図 5 に示すサステイン回路における各部の波形は、図 9 の破線に示したようになる。なお、図 9 において、実線は、T win = T woの時の波形を示している。

### [0029]

その結果、図9に示されるように、信号VG2が立ち下ってから信号VG1が立ち上がるまでのタイムマージンTM1、および、信号VG1が立ち下ってから信号VG2が立ち上がるまでのタイムマージンTM2が減少する。このタイムマージンTM1およびTM2は、スイッチ素子31(スイッチ素子CU)および33(CD)が同時にオンになって貫通電流が流れることがないようにするためのタイムマージンである。このようなタイムマージンの減少は、回路の信頼性低下につながることになる。

#### [0030]

また、図9に示されるように、信号 V G 2 が立ち下ってから信号 V G 3 が立ち上がるまでの時間 T M 3、および、信号 V G 1 が立ち下ってから信号 V G 4 が立ち上がるまでの時間 T M 4 も減少するため、場合によってはスイッチ素子 3 3 ( C D ) および 4 0 ( L U ) が同時にオンしたり、スイッチ素子 3 1 ( C U ) および 3 7 ( L D ) が同時にオンすることにより、これらのスイッチ素子に異常電流が流れる危険がある。

#### [0031]

### [0032]

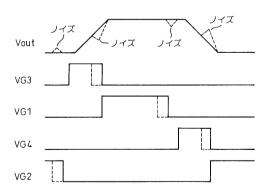

図 1 0 は従来のサステイン回路における出力パルス幅が小さい場合の動作波形を示す図である。

## [0033]

図10に示されるように、信号VG1およびVG2のパルス幅が小さくなると、スイッチ素子31および33がオンしている期間が短くなる。その結果、本来、サステイン電源電圧Vsまたは接地電圧GNDにクランプしていなければならない期間においても、ハイインピーダンス状態となる。この結果、サステイン電圧(サステイン回路の出力信号)Voutの高レベル『H』期間や低レベル『L』期間において、ノイズが重畳される恐れがある

## [0034]

また、信号 V G 3 および V G 4 のパルス幅が小さくなった場合、スイッチ素子 3 7 および 4 0 に電流が流れている途中で信号 V G 3 および V G 4 が立ち下がると、上述したスイッチ素子 3 7 および 4 0 を強制的にオフ状態にする可能性がある。このように、スイッチ素子 3 7 および 4 0 を強制的にオフ状態にすると、スイッチ素子 3 7 および 4 0 の電力損失が増加したり、図 1 0 に示すサステイン電圧 Voutの立ち上がり波形および立ち下がり波形にノイズが重畳されることにもなる。

#### [0035]

このようなハイインピーダンス状態でのノイズや、サステイン電圧の立ち上がり波形および立ち下がり波形におけるノイズが重畳されると、プラズマディスプレイ装置における動作マージンが減少し、画面のチラツキが発生することになる。

#### [0036]

さらに、以上の説明では増幅回路における遅延時間を零としたが、実際には、増幅回路においても遅延時間が存在し、さらに、増幅回路内の部品バラツキ等により遅延時間にもバラツキが生じている。図5に示す4つの遅延回路(51,52,53,54)は、対応する各増幅回路(32,34,41,38)における遅延時間のバラツキを吸収するために、フロントエッジの遅延時間T1をそれぞれ独立に調整するようになっており、そのため、出力信号Voのパルス幅(出力パルス幅)Twoも増幅回路毎に異なる特性となっている。従って、出力パルス幅が大きくなった場合に生じるタイムマージンの減少および異常電流の発生等の問題、或いは、出力パルス幅が小さくなった場合に生じるサステイン電圧Voutに重畳されるノイズの問題等が、より一層発生し易いといった解決すべき課題がある

### [0037]

本発明の目的は、遅延回路によって遅延時間を調整した場合等に生じる出力信号のパルス幅の変動を低減し、適切な出力電圧を容量性負荷に供給することのできる容量性負荷駆動回路を提供することにある。さらに、本発明の他の目的は、タイムマージンの減少、異常電流の発生、および、ノイズ等の問題がない駆動電圧をプラズマディスプレイパネルへ供給することのできるプラズマディスプレイ装置を提供することにある。

#### [0038]

#### 【課題を解決するための手段】

本発明の第1の形態によれば、入力端子と、該入力端子から入力された入力信号のフロントエッジを遅延させるフロントエッジ遅延回路と、前記入力信号のバックエッジを遅延させるバックエッジ遅延回路と、前記フロントエッジ遅延回路および前記バックエッジ遅延回路を介して得られる駆動制御信号を増幅する増幅回路と、該増幅回路によって駆動される出力スイッチ素子と、を備えることを特徴とする容量性負荷駆動回路が提供される。

#### [0039]

本発明の第2の形態によれば、入力端子と、該入力端子から入力された入力信号のフロントエッジを遅延させるフロントエッジ遅延回路と、該フロントエッジ遅延回路を介して得られた遅延信号から所定のパルス幅を有する駆動制御信号を生成するパルス幅調整回路と、前記駆動制御信号を増幅する増幅回路と、該増幅回路によって駆動される出力スイッチ素子と、を備えることを特徴とする容量性負荷駆動回路が提供される。

## [0040]

本発明の第3の形態によれば、複数のX電極と、該複数のX電極に略平行に配置され、該複数のX電極との間に放電を発生させる複数のY電極と、前記複数のX電極に放電電圧を印加するX電極駆動回路と、前記複数のY電極に放電電圧を印加するY電極駆動回路と、を有するプラズマディスプレイ装置であって、前記X電極駆動回路または前記Y電極駆動回路は、入力端子と、該入力端子から入力された入力信号のフロントエッジを遅延させるフロントエッジ遅延回路と、前記入力信号のバックエッジを遅延させるバックエッジ遅延回路と、前記フロントエッジ遅延回路および前記バックエッジ遅延回路を介して得られる駆動制御信号を増幅する増幅回路と、該増幅回路によって駆動される出力スイッチ素子と、を備える容量性負荷駆動回路であることを特徴とするプラズマディスプレイ装置が提供される。

## [0041]

本発明の第4の形態によれば、複数のX電極と、該複数のX電極に略平行に配置され、該複数のX電極との間に放電を発生させる複数のY電極と、前記複数のX電極に放電電圧を印加するX電極駆動回路と、前記複数のY電極に放電電圧を印加するY電極駆動回路と、を有するプラズマディスプレイ装置であって、前記X電極駆動回路または前記Y電極駆動

10

20

30

40

回路は、入力端子と、該入力端子から入力された入力信号のフロントエッジを遅延させるフロントエッジ遅延回路と、該フロントエッジ遅延回路を介して得られた遅延信号から所定のパルス幅を有する駆動制御信号を生成するパルス幅調整回路と、前記駆動制御信号を増幅する増幅回路と、該増幅回路によって駆動される出力スイッチ素子と、を備える容量性負荷駆動回路であることを特徴とするプラズマディスプレイ装置が提供される。

#### [0042]

本発明に係る第1の形態の容量性負荷駆動回路によれば、入力信号のフロントエッジの遅延時間とバックエッジの遅延時間を適切に設定することができる。また、本発明に係る第2の形態の容量性負荷駆動回路によれば、入力信号のフロントエッジの遅延時間と出力パルスのパルス幅を適切に設定することができる。これにより、出力パルス幅変動を低減することが可能になる。

[0043]

さらに、本発明に係る第3の形態のプラズマディスプレイ装置によれば、X電極駆動回路またはY電極駆動回路は、入力信号のフロントエッジの遅延時間と出力パルスのパルス幅を適切に設定することができる。また、本発明に係る第4の形態のプラズマディスプレイ装置によれば、X電極駆動回路またはY電極駆動回路は、入力信号のフロントエッジの遅延時間と出力パルスのパルス幅を適切に設定することができる。これにより、プラズマディスプレイ装置のサステイン回路における遅延時間を調整した際に生じる可能性のあるタイムマージンを減少すると共に、異常電流およびノイズ等の問題を解決することが可能になる。

[0044]

#### 【発明の実施の形態】

以下、本発明に係る容量性負荷駆動回路およびプラズマディスプレイ装置の実施例を、図面を参照して詳述する。なお、本発明に係る表示装置およびその駆動方法は、例えば、ALIS方式のプラズマディスプレイ装置に限定されるものでなく、様々な方式のプラズマディスプレイ装置に対して幅広く適用することができる。

[0045]

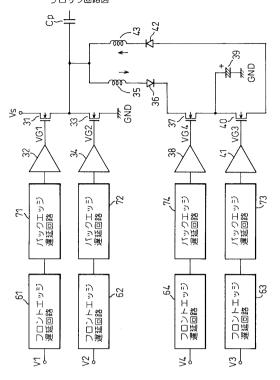

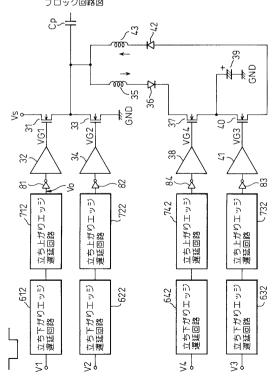

図11は本発明に係る容量性負荷駆動回路の第1実施例を示すブロック回路図である。

[0046]

図11と図5との比較から明らかなように、本第1実施例の容量性負荷駆動回路は、図5に示す従来のサステイン回路(容量性負荷駆動回路)における遅延回路51~54を、それぞれフロントエッジ遅延回路61~64およびバックエッジ遅延回路71~74で構成したものに相当する。従って、スイッチ素子(サステイン出力素子:nチャネル型MOSトランジスタ)31,33および増幅回路(ドライブ回路)32,34による駆動容量Cpの駆動動作、並びに、スイッチ素子37,40、増幅回路38,41、ダイオード36,42、インダクタンス35,43および容量39(Cp)による電力回収回路の動作等は、図5を参照して詳述したのと同様であり、その説明は省略する。

[0047]

すなわち、図11に示されるように、本第1実施例の容量性負荷駆動回路は、入力信号V1およびV2のフロントエッジを遅延させるフロントエッジ遅延回路61および62と、入力信号V1およびV2のバックエッジを遅延させるバックエッジ遅延回路71および72と、フロントエッジ遅延回路61および62並びにバックエッジ遅延回路71および72を介して得られる駆動制御信号を増幅する増幅回路32および34と、増幅回路32および34によって駆動されるスイッチ素子31および33と、を備える。

[0048]

さらに、本第1実施例の容量性負荷駆動回路は、入力信号 V 3 および V 4 のフロントエッジを遅延させるフロントエッジ遅延回路 6 3 および 6 4 と、入力信号 V 3 および V 4 のバックエッジを遅延させるバックエッジ遅延回路 7 3 および 7 4 と、フロントエッジ遅延回路 6 3 および 6 4 並びにバックエッジ遅延回路 7 3 および 7 4 を介して得られる駆動制御信号を増幅する増幅回路 4 1 および 3 8 と、図 5 を参照して説明した増幅回路 4 1 および

10

30

20

40

3 8 によって駆動されるスイッチ素子 4 0 および 3 7 、ダイオード 3 6 , 4 2 、インダクタンス 3 5 , 4 3 、並びに、容量 3 9 を有する電力回収回路と、を備える。

[0049]

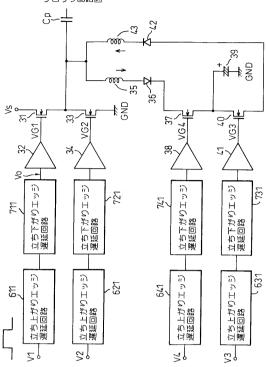

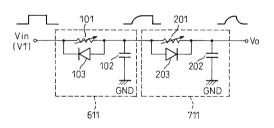

図12は本発明に係る容量性負荷駆動回路の第2実施例を示すブロック回路図である。

[0050]

図12と図11との比較から明らかなように、本第2実施例の容量性負荷駆動回路は、図11に示す第1実施例の容量性負荷駆動回路におけるフロントエッジ遅延回路61~64 およびバックエッジ遅延回路71~74を、それぞれ入力信号 V1~V4の立ち上がりエッジを遅延させる立ち上がりエッジ遅延回路611~641および入力信号 V1~V4の立ち下がりエッジを遅延させる立ち下がりエッジ遅延回路711~741で構成したものである。ここで、入力信号 V1~V4は、高レベル『H』で駆動する正極性パルス信号(ハイイネーブル信号)である。

[0051]

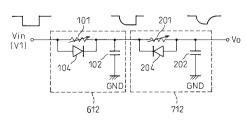

図13は本発明に係る容量性負荷駆動回路の第3実施例を示すプロック回路図である。

[0052]

図13と図11との比較から明らかなように、本第3実施例の容量性負荷駆動回路は、図11に示す第1実施例の容量性負荷駆動回路におけるフロントエッジ遅延回路61~64およびバックエッジ遅延回路71~74を、それぞれ入力信号V1~V4の立ち下がりエッジを遅延させる立ち下がりエッジ遅延回路612~642および入力信号V1~V4の立ち上がりエッジを遅延させる立ち上がりエッジ遅延回路712~742で構成したものである。ここで、入力信号V1~V4は、低レベル『L』で駆動する負極性パルス信号(ロウイネーブル信号)である。また、立ち上がりエッジ遅延回路712~742の出力信号は、インバータ81~84を介して対応する各スイッチ素子(31,33,40,37)に供給される。

[0053]

図14は本発明に係る容量性負荷駆動回路の第4実施例を示す要部回路図であり、上述した図12に示す第2実施例の容量性負荷駆動回路における立ち上がりエッジ遅延回路61 1(621~641)および立ち下がりエッジ遅延回路711(721~741)の具体的な一回路構成を示すものである。

[0054]

図14に示されるように、立ち上がリエッジ遅延回路611は、可変抵抗(可変抵抗素子)101、容量(容量素子)102およびダイオード103を備え、また、立ち下がリエッジ遅延回路711は、可変抵抗201、容量202およびダイオード203を備えている。ここで、立ち上がリエッジ遅延回路611において、可変抵抗101は、入力信号Vin(V1)に対して逆方向のダイオード103と並列に接続され、可変抵抗101およびダイオード103の出力側の接続ノードには、一端が接地GNDに接続された容量102の他端が接続されている。また、立ち下がリエッジ遅延回路711において、可変抵抗201は、入力信号Vinに対して順方向のダイオード203と並列に接続され、可変抵抗201およびダイオード203の出力側の接続ノードには、一端が接地GNDに接続された容量202の他端が接続されている。なお、入力信号Vinとしては、正極性パルス信号が使用される。

[0055]

この図14に示す第4実施例の容量性負荷駆動回路は、立ち上がりエッジ遅延回路611において、まず、可変抵抗101および容量102で構成される積分回路により、入力信号 Vinの立ち上がりエッジを遅延する。ここで、入力信号 Vinの立ち下がり時には、ダイオード103を介して容量102に蓄積された電荷を放電するようになっており、入力信号 Vinの立ち下がりエッジは、可変抵抗101の影響を受けずに次段の立ち下がりエッジ遅延回路711に伝えられる。このように、立ち上がりエッジ遅延回路611は、入力信号 Vinの立ち上がりエッジを遅延させるものであり、可変抵抗101の抵抗値を変化させることによって、立ち上がりエッジの遅延時間のみを独立に調整することができる。

10

20

30

40

#### [0056]

さらに、立ち上がリエッジ遅延回路 6 1 1 の出力信号は、立ち下がリエッジ遅延回路 7 1 1 に供給され、この立ち下がリエッジ遅延回路 7 1 1 において、可変抵抗 2 0 1 および容量 2 0 2 で構成される積分回路により、立ち上がリエッジ遅延回路 6 1 1 の出力信号 (入力信号 V 1 : V in)の立ち下がりが遅延される。ここで、立ち上がリエッジ遅延回路 6 1 1 の出力信号の立ち上がリ時には、ダイオード 2 0 3 を介して容量 2 0 2 を充電する。このように、立ち下がリエッジ遅延回路 7 1 1 は、立ち上がリエッジ遅延回路 6 1 1 の出力信号の立ち下がリエッジを遅延させるものであり、可変抵抗 2 0 1 の抵抗値を変化させることによって、立ち下がリエッジの遅延時間のみを独立に調整することができる。なお、立ち下がリエッジ遅延回路 7 1 1 の出力信号は、スイッチ素子 3 1 を駆動する増幅回路 3 2 に供給される。

10

#### [0057]

上述したように、本第4実施例の容量性負荷駆動回路によれば、入力信号 Vin(V1~V4)の立ち上がリエッジおよび立ち下がリエッジをそれぞれ独立に調整することができ、出力信号のパルス幅の変動を低減して適切な出力電圧を容量性負荷に供給することが可能になる。

#### [0058]

図15は本発明に係る容量性負荷駆動回路の第5実施例を示す要部回路図であり、上述した図13に示す第3実施例の容量性負荷駆動回路における立ち下がリエッジ遅延回路61 2(622~642)および立ち上がリエッジ遅延回路712(722~742)の具体的な一回路構成を示すものである。

20

#### [0059]

図15と図14との比較から明らかなように、本第5実施例の容量性負荷駆動回路は、図14に示す第4実施例のダイオード103および203を、その極性を逆にしたダイオード104および204に置き換えて、第4実施例における立ち上がりエッジ遅延回路611および立ち下がりエッジ遅延回路711を立ち下がりエッジ遅延回路612および立ち上がりエッジ遅延回路712として構成したものである。なお、入力信号Vin(V1)としては、負極性パルス信号が使用される。また、立ち上がりエッジ遅延回路712の出力信号は、インバータ(81)を介してスイッチ素子31を駆動する増幅回路32に供給される。

30

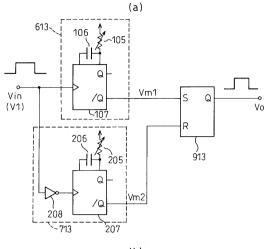

#### [0060]

図16は本発明に係る容量性負荷駆動回路の第6実施例を示す図であり、図16(a)は要部回路図を示し、図16(b)は図16(a)の回路における各波形図を示している。図16(a)において、参照符号613はフロントエッジ遅延回路(立ち上がりエッジ遅延回路)、713はバックエッジ遅延回路(立ち下がりエッジ遅延回路)、107および207は第1および第2のモノマルチバイブレータ、また、913はSRフリップフロップを示している。なお、入力信号Vinとしては、正極性パルス信号が使用される。

40

#### [0061]

図16(a)に示されるように、フロントエッジ遅延回路613は、可変抵抗105、容量106および第1のモノマルチバイブレータ107を備え、また、バックエッジ遅延回路713は、可変抵抗205、容量206、第2のモノマルチバイブレータ207およびインバータ208を備える。入力信号Vin(V1)は、第1のモノマルチバイブレータ107に供給されると共に、インバータ208を介して第2のモノマルチバイブレータ207に供給される。第1のモノマルチバイブレータ107には、可変抵抗105および容量106が設けられ、可変抵抗105の抵抗値を調整することにより時定数を変化させて、入力信号Vinの立ち上がりエッジを遅延するようになっている。また、第2のモノマルチバイブレータ207には、可変抵抗205および容量206が設けられ、可変抵抗205の抵抗値を調整することにより時定数を変化させて、インバータ208で反転された入力信号(/Vin)の立ち上がりエッジ、すなわち、入力信号Vinの立ち下がりエッジを遅延するようになっている。

#### [0062]

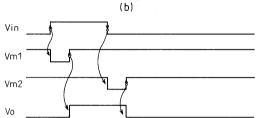

第1のモノマルチバイブレータ107の出力信号(/Q出力)Vm1および第2のモノマ ルチバイブレータ207の出力信号(/Q出力)Vm2は、それぞれSRフリップフロッ プ913のセット端子Sおよびリセット端子Rに供給され、SRフリップフロップ913 から図16(b)に示されるような出力信号Voが出力される。すなわち、第1のモノマ ルチバイブレータ107の出力信号Vm1は、入力信号Vinの立ち上がりエッジで立ち下 がり、可変抵抗105および容量106の時定数により設定された所定時間後に立ち上が る。また、第2のモノマルチバイブレータ207の出力信号Vm2は、入力信号Vinの立 ち下がりエッジで立ち下がり、可変抵抗205および容量206の時定数により設定され た所定時間後に立ち上がる。なお、第1および第2のモノマルチバイブレータ107,2 0 7 およびインバータ 2 0 8 における遅延時間は無視できるものとする。

10

20

30

#### [0063]

さらに、図16(a)および図16(b)に示されるように、SRフリップフロップ91 3は、信号 V m 1 の立ち上がりエッジでセットされ、信号 V m 2 の立ち上がりエッジでリ セットされため、出力信号Voは、信号Vm1の立ち上がりエッジで立ち上がり、信号V m2の立ち上がりエッジで立ち下がるパルス電圧となる。

#### [0064]

このように、本第6実施例の容量性負荷駆動回路において、出力信号Voの立ち上がりエ ッジは、入力信号Vinの立ち上がリエッジを遅延させることによって形成され、また、出 力信号Voの立ち下がりエッジは、入力信号のVinの立ち下がりエッジを遅延させること によって形成される。そして、立ち上がりエッジの遅延時間は、可変抵抗105の抵抗値 を変化させることによって調整することができ、また、立ち下がりエッジの遅延時間は、 可変抵抗205の抵抗値を変化させることによって調整することができる。なお、可変抵 抗105および205の抵抗値を変化させる代わりに、或いは、可変抵抗105および2 05の抵抗値の変化に加えて、容量106および206を可変容量とし、それらの容量値 を変化させることで遅延時間の調整を行うように構成してもよい。

以上のように、本発明に係る容量性負荷駆動回路の第1~第6実施例によれば、入力信号 のフロントエッジ(立ち上がりエッジまたは立ち下がりエッジ)の遅延時間とバックエッ ジ(立ち下がりエッジまたは立ち上がりエッジ)の遅延時間を各々独立に設定することが でき、これにより、従来のフロントエッジの遅延時間を変化させた場合に生じる出力パル ス幅の変動(スイッチ素子へ供給するドライブパルスのパルス幅変動)を低減することが できる。その結果、適切な出力電圧を容量性負荷に供給することができ、容量性負荷駆動 回路をプラズマディスプレイ装置に適用した場合には、タイムマージンの減少、異常電流 の発生、および、ノイズ等の問題がない駆動電圧をプラズマディスプレイパネルへ供給す ることが可能になる。

[0066]

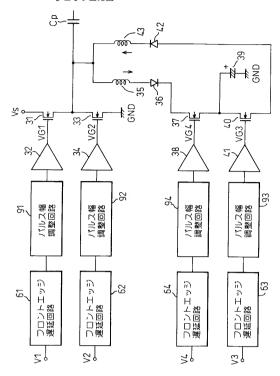

図17は本発明に係る容量性負荷駆動回路の第7実施例を示すブロック回路図である。

図17に示されるように、本第7実施例の容量性負荷駆動回路は、フロントエッジ遅延回 路61~64およびパルス幅調整回路91~94を備えている。すなわち、本第7実施例 の容量性負荷駆動回路は、図11を参照して説明した第1実施例の容量性負荷駆動回路に おいて、バックエッジ遅延回路71~74の代わりにパルス幅調整回路91~94を適用 するようになっている。

40

# [0068]

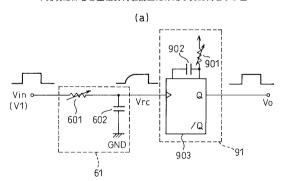

図18は本発明に係る容量性負荷駆動回路の第8実施例を示す図であり、図18(a)は 要部回路図を示し、図18(b)は図18(a)の回路における各波形図を示している。 ここで、図18(a)に示す回路は、上述した図17に示す第7実施例の容量性負荷駆動 回路におけるフロントエッジ遅延回路 6 1 ( 6 2 ~ 6 4 ) およびパルス幅調整回路 9 1 ( 92~94)の一例としての具体的な回路構成を示すものである。

#### [0069]

図18(a)に示されるように、フロントエッジ遅延回路61は、可変抵抗601および容量602を備え、また、パルス幅調整回路91は、可変抵抗901、容量902およびモノマルチバイブレータ903を備える。すなわち、図18(b)に示されるように、本第8実施例の容量性負荷駆動回路において、入力信号Vinは、図7(a)を参照して説明した従来のサステイン回路の遅延回路51と同様の構成を有するフロントエッジ遅延回路61によりフロントエッジが遅延され(遅延時間T1)、そして、モノマルチバイブレータ903により可変抵抗901および容量902により規定される時定数に応じたパルス幅Twoを有する出力信号Voを得るようになっている。すなわち、本第8実施例の容量性負荷駆動回路は、フロントエッジ遅延回路61における可変抵抗601抵抗値を変化させることにより入力信号Vinのフロントエッジの遅延時間T1を調整し、且つ、パルス幅調整回路91における可変抵抗901の抵抗値を変化させることにより出力信号Voのパルス幅Twoを調整することで、フロントエッジの遅延時間と出力信号のパルス幅を独立に設定することができるようになっている。

#### [0070]

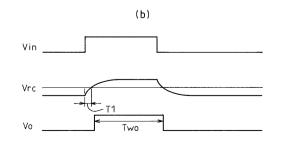

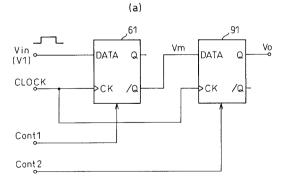

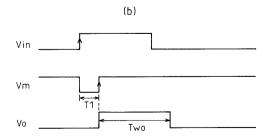

図19は本発明に係る容量性負荷駆動回路の第9実施例を示す図であり、図19(a)は要部回路図を示し、図19(b)は図19(a)の回路における各波形図を示している。ここで、図19(a)に示す回路は、上述した図18(a)に示す第8実施例の容量性負荷駆動回路におけるフロントエッジ遅延回路61(62~64)およびパルス幅調整回路91(92~94)の他の例としての具体的な回路構成を示すものである。

#### [0071]

図19(a)に示されるように、本第9実施例の容量性負荷駆動回路において、フロントエッジ遅延回路61およびパルス幅調整回路91は、クロック信号CLOCKのパルス数を数えるカウンタとして構成され、カウンタ61に設定するカウント数(Cont1)を変化させることにより入力信号Vinのフロントエッジの遅延時間T1を調整し、さらに、カウンタ91に設定するカウント数(Cont2)を変化させることにより出力信号Voのパルス幅Twoを調整するようになっている。本第9実施例の容量性負荷駆動回路は、フロントエッジの遅延時間および出力信号のパルス幅を、カウンタ61および91に供給する信号Cont1およびCont2により独立に且つ容易に調整できるようになっている

#### [0072]

以上のように、本発明に係る容量性負荷駆動回路の第7~第9実施例によれば、入力信号のフロントエッジ(立ち上がりエッジまたは立ち下がりエッジ)の遅延時間と出力信号のパルス幅を各々独立に設定することができ、これにより、従来のフロントエッジの遅延時間を変化させた場合に生じる出力パルス幅の変動を低減することができる。その結果、適切な出力電圧を容量性負荷に供給することができ、容量性負荷駆動回路をプラズマディスプレイ装置に適用した場合には、タイムマージンの減少、異常電流の発生、および、ノイズ等の問題がない駆動電圧をプラズマディスプレイパネルへ供給することが可能になる。

#### [0073]

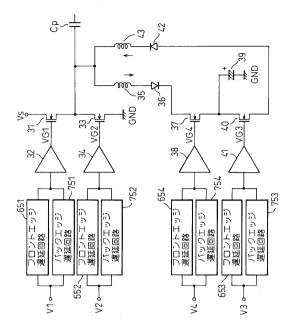

図 2 0 は本発明に係る容量性負荷駆動回路の第 1 0 実施例を示すブロック回路図である。 【 0 0 7 4 】

図20と図11との比較から明らかなように、本第10実施例の容量性負荷駆動回路においては、図11に示す第1実施例における入力端子(例えば、V1)と増幅回路(例えば、32)との間に直列に設けられたフロントエッジ遅延回路(61)およびバックエッジ遅延回路(71)が並列に設けられるようになっている。

## [0075]

すなわち、図20に示されるように、各入力信号V1~V4は、それぞれフロントエッジ 遅延回路651~654およびバックエッジ遅延回路751~754に供給されると共に 、フロントエッジ遅延回路651,652,653,654およびバックエッジ遅延回路 751,752,753,754の出力が増幅回路32,34,41,38に供給される 10

20

30

40

10

20

30

40

50

ようになっている。

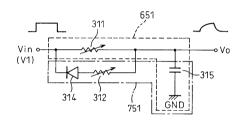

#### [0076]

図21は本発明に係る容量性負荷駆動回路の第11実施例を示す要部回路図であり、上述した図20に示す第10実施例の容量性負荷駆動回路におけるフロントエッジ遅延回路651(652~654)およびバックエッジ遅延回路751(752~754)の具体的な一回路構成を示すものである。

#### [0077]

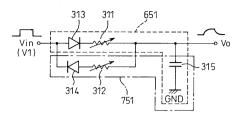

図21に示されるように、本第11実施例の容量性負荷駆動回路において、フロントエッジ遅延回路(立ち上がりエッジ遅延回路)651は、可変抵抗311、ダイオード313および容量315を備えて構成され、また、バックエッジ遅延回路(立ち下がりエッジ遅延回路)751は、可変抵抗312、ダイオード314および容量315を備えて構成される。すなわち、本第11実施例の容量性負荷駆動回路は、容量315をフロントエッジ遅延回路651およびバックエッジ遅延回路751で共用するようになっている。ここで、入力信号Vinのフロントエッジ(立ち上がりエッジ)の遅延時間は、可変抵抗311の抵抗値を変化させることによって調整される。

#### [0078]

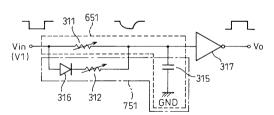

図22は本発明に係る容量性負荷駆動回路の第12実施例を示す要部回路図であり、前述した図20に示す第10実施例の容量性負荷駆動回路におけるフロントエッジ遅延回路651(652~654)およびバックエッジ遅延回路751(752~754)の他の具体的な回路構成を示すものである。ここで、図22に示す第12実施例の容量性負荷駆動回路では、入力信号Vinとして正極性パルス信号が使用され、フロントエッジ遅延回路651は入力信号Vinの立ち上がりエッジを遅延し、また、バックエッジ遅延回路751は立ち下がりエッジを遅延する。

#### [0079]

図22と図21との比較から明らかなように、本第12実施例の容量性負荷駆動回路におけるフロントエッジ遅延回路(立ち上がりエッジ遅延回路)651は、上述した第11実施例の容量性負荷駆動回路におけるフロントエッジ遅延回路からダイオード313を取り除いたものに相当する。入力信号Vinの立ち上がり時は、可変抵抗311を介して容量315に電荷が充電され、また、入力信号Vinの立ち下がり時には、可変抵抗311およびダイオード314と直列に接続された可変抵抗312を介して容量315の電荷を放電する。すなわち、出力電圧Voの立ち上がりエッジの遅延時間は、可変抵抗311の抵抗値によって変化し、また、出力電圧Voの立ち下がりエッジの遅延時間は、可変抵抗311がよび312の抵抗値によって変化する。

#### [0800]

従って、本第12実施例の容量性負荷駆動回路においては、まず、フロントエッジ遅延回路651における可変抵抗311の抵抗値を変化させて立ち上がリエッジの遅延時間を調整し、その後、バックエッジ遅延回路751における可変抵抗312の抵抗値を変化させて立ち下がリエッジの遅延時間を調整することで、立ち上がリエッジおよび立ち下がリエッジの遅延時間を適切に調整することができる。

## [0081]

図23は本発明に係る容量性負荷駆動回路の第13実施例を示す要部回路図である。ここで、図23に示す第13実施例の容量性負荷駆動回路では、入力信号Vinとして負極性パルス信号が使用され、フロントエッジ遅延回路651は入力信号Vinの立ち下がリエッジを遅延し、また、バックエッジ遅延回路751は立ち上がリエッジを遅延する。なお、本第13実施例において、入力信号Vinのフロントおよびバックエッジの遅延時間の調整が行われた信号は、インバータ317で反転および波形整形されて出力信号Voとして次段の増幅回路32に供給されるようになっている。

#### [0082]

図23と図22との比較から明らかなように、本第13実施例の容量性負荷駆動回路にお

けるバックエッジ遅延回路(立ち上がりエッジ遅延回路)751は、上述した第12実施例の容量性負荷駆動回路におけるバックエッジ遅延回路(立ち下がりエッジ遅延回路)におけるダイオードの向きを逆方向にしたものに相当する。入力信号 Vinの立ち下がり時は、可変抵抗311を介して容量315の電荷を放電し、また、入力信号 Vinの立ち上がり時には、可変抵抗311およびダイオード316と直列に接続された可変抵抗312を介して容量315に電荷が充電される。すなわち、出力電圧 Voの立ち下がりエッジの遅延時間は、可変抵抗311の抵抗値によって変化し、また、出力電圧 Voの立ち上がりエッジの遅延時間は、可変抵抗311および312の抵抗値によって変化する。

## [0083]

従って、本第13実施例の容量性負荷駆動回路においては、まず、フロントエッジ遅延回路651における可変抵抗311の抵抗値を変化させて立ち下がりエッジの遅延時間を調整し、その後、バックエッジ遅延回路751における可変抵抗312の抵抗値を変化させて立ち上がりエッジの遅延時間を調整することで、立ち下がりエッジおよび立ち上がりエッジの遅延時間を適切に調整することができる。

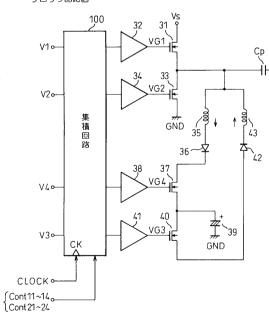

#### [0084]

図 2 4 は本発明に係る容量性負荷駆動回路の第 1 4 実施例を示すブロック回路図であり、集積回路 1 0 0 を、前述した図 1 9 に示す第 9 実施例のフロントエッジ遅延回路( 6 1 ~ 6 4 )およびパルス幅調整回路( 9 1 ~ 9 4 )により構成した例を示すものである。

#### [0085]

図24に示されるように、集積回路100は、例えば、入力信号V1~V4およびクロック信号CLOCKを受け取り、クロック信号CLOCKを制御信号(Cont11~Cont14およびCont21~Cont24)に応じた数だけカウントすることによって、フロントエッジ遅延回路で入力信号のフロントエッジの遅延時間を調整すると共に、パルス幅調整回路でパルス幅を調整する。そして、これらのフロントエッジの遅延時間およびパルス幅が調整された信号が、それぞれ対応する増幅回路32,34,41,38に供給され、図5を参照して説明したのと同様のスイッチ素子(サステイン出力素子)の駆動および電力の回収を行うようになっている。

#### [0086]

すなわち、各フロントエッジ遅延回路(カウンタ:61~64)には、それぞれ入力信号(V1~V4)のフロントエッジの遅延時間(T1)を調整するための制御信号(カウント数)Cont11~Cont14が供給され、また、各パルス幅調整回路(カウンタ:91~94)には、それぞれ出力信号のパルス幅(Two)を調整するための制御信号(カウント数)Cont21~Cont24が供給されている。すなわち、本第14実施例によれば、フロントエッジの遅延時間および出力信号のパルス幅を、カウンタ(61~64 および 91~94)に供給する信号(Cont11~Cont14 およびCont21~Cont24)により独立に且つ容易に調整できるようになっている。

## [0087]

なお、上述した各実施例は、フロントエッジ遅延回路、バックエッジ遅延回路およびパルス幅調整回路等の例を示すだけのものであり、これらの回路は様々に変形し得るのはいうまでもない。

## [0088]

以上、詳述した容量性負荷駆動回路の各実施例は、図1~図4を参照して説明したような プラズマディスプレイ装置におけるサステイン回路として適用することにより、サステイン回路における遅延時間を調整した際に生じる可能性のあるタイムマージンを減少すると 共に、異常電流およびノイズ等の課題を解決することができる。

## [0089]

(付記1) 入力端子と、

該入力端子から入力された入力信号のフロントエッジを遅延させるフロントエッジ遅延回 路と、

前記入力信号のバックエッジを遅延させるバックエッジ遅延回路と、

10

20

30

前記フロントエッジ遅延回路および前記バックエッジ遅延回路を介して得られる駆動制御 信号を増幅する増幅回路と、

該増幅回路によって駆動される出力スイッチ素子と、を備えることを特徴とする容量性負 荷駆動回路。

#### [0090]

(付記2) 付記1に記載の容量性負荷駆動回路において、

前記フロントエッジ遅延回路は、前記入力信号の立ち上がりエッジを遅延させる立ち上が リエッジ遅延回路であり、且つ、

前記バックエッジ遅延回路は、前記入力信号の立ち下がりエッジを遅延させる立ち下がり エッジ遅延回路であることを特徴とする容量性負荷駆動回路。

### [0091]

(付記3) 付記2に記載の容量性負荷駆動回路において、前記入力信号は、正極性パル ス信号であることを特徴とする容量性負荷駆動回路。

### [0092]

(付記4) 付記1に記載の容量性負荷駆動回路において、

前記フロントエッジ遅延回路は、前記入力信号の立ち下がりエッジを遅延させる立ち下が リエッジ遅延回路であり、且つ、

前記バックエッジ遅延回路は、前記入力信号の立ち上がりエッジを遅延させる立ち上がり エッジ遅延回路であることを特徴とする容量性負荷駆動回路。

#### [0093]

付記4に記載の容量性負荷駆動回路において、前記入力信号は、負極性パル ス信号であることを特徴とする容量性負荷駆動回路。

#### [0094]

(付記6) 付記2~5のいずれか1項に記載の容量性負荷駆動回路において、前記立ち 上がりエッジ遅延回路は、抵抗素子およびスイッチ素子の並列回路と容量素子とを備え、 前記入力信号が立ち上がる時は前記抵抗素子を介して前記容量素子に電荷を充電し、且つ 、前記入力信号が立ち下がる時は前記スイッチ素子を介して前記容量素子に充電された電 荷を放電することを特徴とする容量性負荷駆動回路。

#### [0095]

(付記7) 付記6に記載の容量性負荷駆動回路において、前記立ち上がりエッジ遅延回 路におけるスイッチ素子は、ダイオードであることを特徴とする容量性負荷駆動回路。

## [0096]

(付記8) 付記6に記載の容量性負荷駆動回路において、前記立ち上がりエッジ遅延回 路の遅延時間を、前記抵抗素子の抵抗値を変化させることによって調整することを特徴と する容量性負荷駆動回路。

#### [0097]

(付記9) 付記6に記載の容量性負荷駆動回路において、前記立ち上がりエッジ遅延回 路の遅延時間を、前記容量素子の容量値を変化させることによって調整することを特徴と する容量性負荷駆動回路。

#### [0098]

付記2~5のいずれか1項に記載の容量性負荷駆動回路において、前記立 ち下がりエッジ遅延回路は、抵抗素子およびスイッチ素子の並列回路と容量素子とを備え 、前記入力信号が立ち下がる時は前記抵抗素子を介して前記容量素子に電荷を充電し、且 つ、前記入力信号が立ち上がる時は前記スイッチ素子を介して前記容量素子に充電された 電荷を放電することを特徴とする容量性負荷駆動回路。

### [0099]

(付記11) 付記10に記載の容量性負荷駆動回路において、前記立ち下がりエッジ遅 延回路におけるスイッチ素子は、ダイオードであることを特徴とする容量性負荷駆動回路

[0100]

30

10

20

(付記12) 付記10に記載の容量性負荷駆動回路において、前記立ち下がリエッジ遅延回路の遅延時間を、前記抵抗素子の抵抗値を変化させることによって調整することを特徴とする容量性負荷駆動回路。

#### [0101]

(付記13) 付記10に記載の容量性負荷駆動回路において、前記立ち下がリエッジ遅延回路の遅延時間を、前記容量素子の容量値を変化させることによって調整することを特徴とする容量性負荷駆動回路。

#### [0102]

(付記14) 付記1に記載の容量性負荷駆動回路において、

前記フロントエッジ遅延回路は、前記入力信号のフロントエッジをトリガとする第 1 のモ ノマルチバイブレータであり、且つ、

前記バックエッジ遅延回路は、前記入力信号のバックエッジをトリガとする第2のモノマルチバイブレータであり、前記第1のモノマルチバイブレータの出力信号と前記第2のモノマルチバイブレータの出力とを合成することにより、前記駆動制御信号を生成することを特徴とする容量性負荷駆動回路。

#### [0103]

(付記15) 付記1に記載の容量性負荷駆動回路において、

前記フロントエッジ遅延回路は、第1の抵抗素子および第1のスイッチ素子を有する第1 の直列回路と、第1の容量素子とを備え、

前記バックエッジ遅延回路は、第2の抵抗素子および第2のスイッチ素子を有する第2の 直列回路と、第2の容量素子とを備え、前記第1の直列回路および前記第2の直列回路が 並列に接続されていることを特徴とする容量性負荷駆動回路。

#### [0104]

(付記16) 付記15に記載の容量性負荷駆動回路において、前記第1の容量素子および前記第2の容量素子を同一の容量素子により共用したことを特徴とする容量性負荷駆動回路。

### [0105]

(付記17) 付記15または16に記載の容量性負荷駆動回路において、前記第1の抵抗素子の抵抗値を変化させることによって前記入力信号のフロントエッジの遅延時間を調整し、且つ、前記第2の抵抗素子の抵抗値を変化させることによって前記入力信号のバックエッジの遅延時間を調整することを特徴とする容量性負荷駆動回路。

## [0106]

(付記18) 付記15または16に記載の容量性負荷駆動回路において、前記第1のスイッチ素子および前記第2のスイッチ素子は、ダイオードであることを特徴とする容量性負荷駆動回路。

#### [0107]

(付記19) 付記1に記載の容量性負荷駆動回路において、

前記フロントエッジ遅延回路は、第1の抵抗素子および第1の容量素子を備え、

前記バックエッジ遅延回路は、第2の抵抗素子およびスイッチ素子を有する直列回路と、第2の容量素子とを備え、前記第1の抵抗素子と前記直列回路が並列に接続されていることを特徴とする容量性負荷駆動回路。

## [ 0 1 0 8 ]

(付記20) 付記19に記載の容量性負荷駆動回路において、前記第1の容量素子および前記第2の容量素子を同一の容量素子により共用したことを特徴とする容量性負荷駆動回路。

## [0109]

(付記21) 付記19または20に記載の容量性負荷駆動回路において、前記第1の抵抗素子の抵抗値を変化させることによって前記入力信号のフロントエッジの遅延時間を調整し、且つ、前記第2の抵抗素子の抵抗値を変化させることによって前記入力信号のバックエッジの遅延時間を調整することを特徴とする容量性負荷駆動回路。

20

10

30

40

#### [0110]

(付記22) 付記19または20に記載の容量性負荷駆動回路において、最初に前記第1の抵抗素子の抵抗値を変化させて前記入力信号のフロントエッジの遅延時間を調整し、次に前記第2の抵抗素子の抵抗値を変化させて前記入力信号のバックエッジの遅延時間を調整することを特徴とする容量性負荷駆動回路。

#### [0111]

(付記23) 付記19に記載の容量性負荷駆動回路において、前記スイッチ素子は、ダイオードであることを特徴とする容量性負荷駆動回路。

## [0112]

(付記24) 付記1に記載の容量性負荷駆動回路において、

前記フロントエッジ遅延回路は、前記入力信号のフロントエッジからクロック信号のカウントを開始する第 1 のカウンタを備え、且つ、

前記バックエッジ遅延回路は、前記入力信号のバックエッジからクロック信号のカウントを開始する第2のカウンタを備え、前記第1のカウンタのカウント値を変化させて前記フロントエッジの遅延時間を調整し、且つ、前記第2のカウンタのカウント値を変化させて前記バックエッジの遅延時間を調整することを特徴とする容量性負荷駆動回路。

#### [0113]

(付記25) 付記24に記載の容量性負荷駆動回路において、前記第1のカウンタおよび前記第2のカウンタを、同一の半導体集積回路上に形成したことを特徴とする容量性負荷駆動回路。

#### [0114]

(付記26) 入力端子と、

該入力端子から入力された入力信号のフロントエッジを遅延させるフロントエッジ遅延回路と、

該フロントエッジ遅延回路を介して得られた遅延信号から所定のパルス幅を有する駆動制御信号を生成するパルス幅調整回路と、

前記駆動制御信号を増幅する増幅回路と、

該増幅回路によって駆動される出力スイッチ素子と、を備えることを特徴とする容量性負荷駆動回路。

## [0115]

(付記27) 付記26に記載の容量性負荷駆動回路において、

前記フロントエッジ遅延回路は、抵抗素子および容量素子を備え、且つ、

前記パルス幅調整回路は、モノマルチバイブレータであることを特徴とする容量性負荷駆動回路。

### [0116]

(付記28) 付記27に記載の容量性負荷駆動回路において、

前記入力信号の遅延時間を、前記フロントエッジ遅延回路における前記抵抗素子の抵抗値 を変化させることによって調整することを特徴とする容量性負荷駆動回路。

### [0117]

(付記29) 付記27に記載の容量性負荷駆動回路において、

前記入力信号の遅延時間を、前記フロントエッジ遅延回路における前記容量素子の容量値を変化させることによって調整することを特徴とする容量性負荷駆動回路。

#### [0118]

(付記30) 付記27~29のいずれか1項に記載の容量性負荷駆動回路において、前記駆動制御信号のパルス幅を、前記モノマルチバイブレータの時定数等を変化させることによって調整することを特徴とする容量性負荷駆動回路。

#### [0119]

(付記31) 付記26に記載の容量性負荷駆動回路において、

前記フロントエッジ遅延回路は、クロック信号をカウントする第 1 のカウンタであり、且つ、

10

20

30

40

前記パルス幅調整回路は、前記クロック信号をカウントする第2のカウンタであり、前記第1のカウンタのカウント値を変化させることによって前記入力信号の遅延時間を調整し、前記第2のカウンタのカウント値を変化させることによって前記駆動制御信号のパルス幅を調整することを特徴とする容量性負荷駆動回路。

#### [0120]

(付記32) 付記26に記載の容量性負荷駆動回路において、

前記フロントエッジ遅延回路は、前記入力信号の立ち上がりエッジを遅延させる立ち上が リエッジ遅延回路であり、且つ、

前記パルス幅調整回路は、モノマルチバイブレータであることを特徴とする容量性負荷駆動回路。

#### [0121]

(付記33) 付記32に記載の容量性負荷駆動回路において、前記入力信号は、正極性 パルス信号であることを特徴とする容量性負荷駆動回路。

### [0122]

(付記34) 付記26に記載の容量性負荷駆動回路において、

前記フロントエッジ遅延回路は、前記入力信号の立ち下がりエッジを遅延させる立ち下が リエッジ遅延回路であり、且つ、

前記パルス幅調整回路は、モノマルチバイブレータであることを特徴とする容量性負荷駆動回路。

## [0123]

(付記35) 付記34に記載の容量性負荷駆動回路において、前記入力信号は、負極性 パルス信号であることを特徴とする容量性負荷駆動回路。

#### [0124]

(付記36) 付記1~35のいずれか1項に記載の容量性負荷駆動回路において、

該容量性負荷駆動回路は、第1および第2の容量性負荷駆動回路を備え、

前記第1の容量性負荷駆動回路における第1の出力スイッチ素子は、電源線と容量性負荷との間に接続され、

前記第2の容量性負荷駆動回路における第2の出力スイッチ素子は、前記容量性負荷と基準電圧との間に接続されることを特徴とする容量性負荷駆動回路。

### [0125]

(付記37) 付記36に記載の容量性負荷駆動回路において、

該容量性負荷駆動回路は、さらに、第3および第4の容量性負荷駆動回路を備え、

前記第3の容量性負荷駆動回路における第3の出力スイッチ素子は、第1のコイルを介して前記容量性負荷に接続され、

前記第4の容量性負荷駆動回路における第4の出力スイッチ素子は、第2のコイルを介して前記容量性負荷に接続されることを特徴とする容量性負荷駆動回路。

## [0126]

(付記38) 付記36または37に記載の容量性負荷駆動回路において、前記電源線は、プラズマディスプレイ装置のサステイン電源線であることを特徴とする容量性負荷駆動回路。

## [0127]

(付記39) 複数のX電極と、

該複数のX電極に略平行に配置され、該複数のX電極との間に放電を発生させる複数のY電極と、

前記複数のX電極に放電電圧を印加するX電極駆動回路と、

前記複数のY電極に放電電圧を印加するY電極駆動回路と、を有するプラズマディスプレイ装置であって、

前記X電極駆動回路または前記Y電極駆動回路は、付記1~38のいずれか1項に記載の容量性負荷駆動回路を用いて構成したことを特徴とするプラズマディスプレイ装置。

#### [0128]

20

10

30

40

#### 【発明の効果】

以上、詳述したように、本発明によれば、遅延回路によって遅延時間を調整した場合等に生じる出力信号のパルス幅の変動を低減し、適切な出力電圧を容量性負荷に供給するようにした容量性負荷駆動回路を提供することができる。また、本発明によれば、タイムマージンの減少、異常電流の発生、および、ノイズ等の問題がない駆動電圧をプラズマディスプレイパネルへ供給することのできるプラズマディスプレイ装置を適用することができる

#### 【図面の簡単な説明】

- 【図1】本発明が適用されるプラズマディスプレイ装置の一例を概略的に示す全体構成図である。

- 【図2】図1に示すプラズマディスプレイ装置の駆動波形を示す図である。

- 【図3】本発明が適用されるプラズマディスプレイ装置の他の例を概略的に示す全体構成図である。

- 【図4】図3に示すプラズマディスプレイ装置における維持放電期間の駆動波形を示す図 である。

- 【図 5 】従来のプラズマディスプレイ装置におけるサステイン回路の一例を示す回路図である。

- 【図6】図5に示すサステイン回路における遅延回路の一例を示す回路図である。

- 【図7】従来のサステイン回路における増幅回路の閾値電圧と出力パルス幅との関係を説明するための図である。

- 【図8】従来のサステイン回路における遅延時間と出力パルス幅との関係を説明するための図である。

- 【図9】従来のサステイン回路における出力パルス幅が大きい場合の動作波形を示す図である。

- 【図10】従来のサステイン回路における出力パルス幅が小さい場合の動作波形を示す図 である。

- 【図11】本発明に係る容量性負荷駆動回路の第1実施例を示すプロック回路図である。

- 【図12】本発明に係る容量性負荷駆動回路の第2実施例を示すブロック回路図である。

- 【図13】本発明に係る容量性負荷駆動回路の第3実施例を示すブロック回路図である。

- 【図14】本発明に係る容量性負荷駆動回路の第4実施例を示す要部回路図である。

- 【図15】本発明に係る容量性負荷駆動回路の第5実施例を示す要部回路図である。

- 【図16】本発明に係る容量性負荷駆動回路の第6実施例を示す図である。

- 【図17】本発明に係る容量性負荷駆動回路の第7実施例を示すブロック回路図である。

- 【図18】本発明に係る容量性負荷駆動回路の第8実施例を示す図である。

- 【図19】本発明に係る容量性負荷駆動回路の第9実施例を示す図である。

- 【図20】本発明に係る容量性負荷駆動回路の第10実施例を示すブロック回路図である

- 【図21】本発明に係る容量性負荷駆動回路の第11実施例を示す要部回路図である。

- 【図22】本発明に係る容量性負荷駆動回路の第12実施例を示す要部回路図である。

- 【図23】本発明に係る容量性負荷駆動回路の第13実施例を示す要部回路図である。

- 【図24】本発明に係る容量性負荷駆動回路の第14実施例を示すブロック回路図である

#### 【符号の説明】

- 1 0 ... P D P

- 11…第1の電極(X電極)

- 1 1 O ... 奇数 X 電極

- 1 1 E ... 偶数 X 電極

- 1 2 ... 第 2 の電極 ( Y 電極 )

- 1 2 O ... 奇数 Y 電極

- 1 2 E ... 偶数 Y 電極

10

20

30

40

- 13...アドレス電極

- 18 O... 第1 X サステインパルス発生回路

- 18-E…第2Xサステインパルス発生回路

- 19-0...第1Yサステインパルス発生回路

- 19-E…第2Yサステインパルス発生回路

- 3 1 , 3 3 , 3 7 , 4 0 ... スイッチ素子(サステイン出力素子: n チャネル型 M O S トランジスタ)

- 3 2 , 3 4 , 3 8 , 4 1 ... 増幅回路 (ドライブ回路)

- 35,43...インダクタンス

- 36,42,103,104,203,204...ダイオード

- 3 9 , 1 0 2 , 1 0 6 , 2 0 2 , 2 0 6 ... 容量(容量素子)

- 5 1 ~ 5 4 ... 遅延回路

- 61~64,613,651~654...フロントエッジ遅延回路

- 71~74,713,751~754...バックエッジ遅延回路

- 81,208...インバータ

- 9 1 ~ 9 4 ... パルス幅調整回路

- 100 ... 集積回路

- 101,105,201,205...可变抵抗(可变抵抗素子)

- 107,207...モノマルチバイブレータ

- 6 1 1 ~ 6 4 1 , 7 1 2 ~ 7 4 2 ... 立ち上がりエッジ遅延回路

- 6 1 2 ~ 6 4 2 , 7 1 1 ~ 7 4 1 ... 立ち下がりエッジ遅延回路

- 9 1 3 ... S R フリップフロップ

- Cp...PDPのX電極とY電極で形成される表示セルの駆動容量

## 【図1】

図1 本発明が適用されるプラズマティスプレイ装置の一例を 概略的に示す全体構成図

## 【図2】

20

## 【図3】

図3 本発明が適用されるブラズマディスプレイ装置の他の例を 概略的に示す全体構成図

## 【図4】

図 4

34 図3に示すプラズマティスプレイ装置における維持放電期間の 駆動波形を示す図

(a) 奇数フィールド

(b) 偶数フィールド

## 【図5】

図 5 従来のブラズマティスブレイ装置におけるサスティン回路の 一例を示す回路図

## 【図6】

図 6

図 5 に示すサステイン回路における遅延回路の一例を示す回路図

51 (52~53)

## 【図7】

#### 図 7

⊶・ 従来のサステイン回路における増幅回路の閾値電圧と出力バルス幅 との関係を説明するための図

## 【図8】

図 8 従来のサステイン回路における遅延時間と出力バルス幅との 関係を説明するための図

# 【図9】

### 図 9

従来のサステイン回路における出力パルス幅が大きい場合の 動作波形を示す図

## 【図10】

## 図10

従来のサステイン回路における出力バルス幅が小さい場合の 動作波形を示す図

### 【図11】

図 11 本発明に係る容量性負荷駆動回路の第1実施例を示す ブロック回路図

#### 【図12】

図 12 本発明に係る容量性負荷駆動回路の第2実施例を示す ブロック回路図

## 【図13】

図 13 本発明に係る容量性負荷駆動回路の第3実施例を示す ブロック回路図

## 【図14】

#### 図14

本発明に係る容量性負荷駆動回路の第4実施例を示す要部回路図

## 【図15】

#### 図15

本発明に係る容量性負荷駆動回路の第5実施例を示す要部回路図

## 【図16】

図 16 本発明に係る容量性負荷駆動回路の第6実施例を示す図

## 【図17】

図 17 本発明に係る容量性負荷駆動回路の第7実施例を示す ブロック回路図

# 【図18】

図 18 本発明に係る容量性負荷駆動回路の第8実施例を示す図

## 【図19】

図 19

本発明に係る容量性負荷駆動回路の第9実施例を示す図

## 【図20】

### 図 20

-本発明に係る容量性負荷駆動回路の第10実施例を示す ブロック回路図

## 【図21】

#### 図 21

本発明に係る容量性負荷駆動回路の第11実施例を示す要部回路図

## 【図22】

#### 図 22

本発明に係る容量性負荷駆動回路の第12実施例を示す要部回路図

## 【図23】

#### 図 23

本発明に係る容量性負荷駆動回路の第13実施例を示す要部回路図

## 【図24】

#### 図24

本発明に係る容量性負荷駆動回路の第14実施例を示す ブロック回路図

## フロントページの続き

(51) Int.CI. F I

G 0 9 G 3/20 6 2 4 M G 0 9 G 3/20 6 2 4 P H 0 3 K 5/13 H 0 3 K 17/00 M

H 0 3 K 17/693 C

## (72)発明者 小泉 治男

神奈川県川崎市高津区坂戸3丁目2番1号 富士通日立プラズマディスプレイ株式会社内

審査官 堀部 修平

(56)参考文献 特開平11-015436 (JP,A)

特開2001-282181(JP,A)

特開2001-267897(JP,A)

特開平06-292040(JP,A)

特開2001-157443(JP,A)

特開平11-195980(JP,A)

国際公開第00/065651(WO,A1)

特開平05-315908(JP,A)

特開2004-045705(JP,A)

(58)調査した分野(Int.CI., DB名)

G09G 3/00 - 3/38