## (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2006-86272 (P2006-86272A)

(43) 公開日 平成18年3月30日 (2006.3.30)

| (51) Int.Cl.  HO1 L 29/78  HO1 L 21/283  HO1 L 29/423  HO1 L 29/49  HO1 L 21/336 | (2006.01) HOLL<br>(2006.01) HOLL<br>(2006.01) HOLL     | 21/283 C<br>29/58 G<br>29/78 3 O 1 P                                | テーマコード (参考)<br>4M1 O4<br>5 F O 4 8<br>5 F 1 4 O<br>(全 10 頁) 最終頁に続く |

|----------------------------------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------------------|--------------------------------------------------------------------|

| (21) 出願番号<br>(22) 出願日                                                            | 特願2004-268273 (P2004-268273)<br>平成16年9月15日 (2004.9.15) | 1号<br>(74)代理人 100092978<br>弁理士 真田<br>(72)発明者 青山 敬幸                  | 可中原区上小田中4丁目1番<br>有<br>可中原区上小田中4丁目1番                                |

|                                                                                  |                                                        | F ターム (参考) 4M104 BB13<br>CC05<br>EE16<br>5F048 AC03<br>BB11<br>DA23 | DD03 EE03 EE12 EE14<br>EE17 GG08 GG10 HH20                         |

### (54) 【発明の名称】半導体装置

## (57)【要約】

【課題】 高誘電率ゲート絶縁膜やメタルゲート電極を採用する場合に、仕事関数の変動を抑えて閾値電圧の変動量を低く抑えることができるようにし、ゲートリーク電流の増大を抑えて、信頼性の低下を招かないようにする。

【解決手段】 半導体装置を、ゲート電極1がメタルゲート電極であるか、又は、ゲート絶縁膜4が高誘電率ゲート絶縁膜である場合に、ゲート電極1とゲート絶縁膜4との間に、ゲート電極1側から順に、シリコン酸化膜2、シリコン窒化膜3を備えるものとする。

【選択図】 図1

#### 【特許請求の範囲】

### 【請求項1】

ゲート電極と、

ゲート絶縁膜とを備え、

前記ゲート電極がメタルゲート電極であるか、又は、前記ゲート絶縁膜が高誘電率ゲート絶縁膜である場合に、前記ゲート電極と前記ゲート絶縁膜との間に、前記ゲート電極側から順に、シリコン酸化膜、シリコン窒化膜を備えることを特徴とする、半導体装置。

#### 【請求項2】

ゲート電極と、

ゲート絶縁膜とを備え、

前記ゲート電極がメタルゲート電極であるか、又は、前記ゲート絶縁膜が高誘電率ゲート絶縁膜である場合に、前記ゲート電極と前記ゲート絶縁膜との間に、シリコン酸化膜を備えることを特徴とする、半導体装置。

## 【請求項3】

前記メタルゲート電極が、Mo,W,Ta,Ti,Hf,Zr,V,Cr,Nbを含む 金属群から選ばれるいずれか1種の金属を含むものとして構成されることを特徴とする、 請求項1又は2記載の半導体装置。

#### 【請求項4】

前記高誘電率ゲート絶縁膜が、酸化ハフニウム,酸化ジルコニウム,酸化アルミニウム ,酸化イットリウム,ランタン族酸化物、又は前記各酸化物のシリケート、又は前記各酸 化物若しくは前記各シリケートを含む混合物により構成されることを特徴とする、請求項 1~3のいずれか1項に記載の半導体装置。

#### 【請求項5】

Mo,W,Ta,Ti,Hf,Zr,V,Cr,Nbを含む金属群から選ばれるいずれか1種の金属を含む金属膜と、

高誘電率膜とを備え、

前記金属膜と前記高誘電率膜との間に、前記金属膜側から順に、シリコン酸化膜、シリコン窒化膜を備えることを特徴とする、半導体装置。

## 【発明の詳細な説明】

### 【技術分野】

[0001]

本発明は、例えばMOS (Metal Oxide Semiconductor)デバイスのゲートスタック構造に用いて好適の半導体装置に関する。

## 【背景技術】

## [0002]

従来、MOSデバイスでは、ゲート絶縁膜としてSiO2ゲート絶縁膜が広く用いられてきた。しかし、SiO2ゲート絶縁膜の薄膜化が進み、その厚さが原子数個分にまで薄くなると、ゲートリーク電流が増大してしまい、消費電力や発熱量の増大という問題が深刻になり、その抑制が重要な課題となってきた。

そこで、近年、ゲート絶縁膜として、SiO $_2$ ゲート絶縁膜よりも誘電率の高い絶縁膜 (高誘電率ゲート絶縁膜, High-kゲート絶縁膜)を用いることが提案されている。

#### [00003]

一方、ゲート電極としては、従来、ポリシリコンゲート電極が広く用いられてきた。しかし、ゲート絶縁膜の薄膜化が進むにつれて、ゲート空乏化によってトランジスタのオン電流が低下してしまうという問題が深刻になり、その抑制が重要な課題となってきた。

また、ポリシリコンゲート電極は、高誘電率ゲート絶縁膜と組み合わせて使った場合に、ゲート絶縁膜とゲート電極との界面で欠陥が生じやすく、動作電圧(閾値電圧)が上昇してしまう傾向がある。さらにフォノン振動が発生して、トランジスタのチャネル内での電子の移動を阻害するという問題も発生する。

#### [0004]

50

10

20

30

そこで、近年、ゲート電極として、メタルゲート電極を用いることが提案されている。 なお、従来、半導体デバイスにおいて、誘電率の高い膜(高誘電率膜,強誘電率膜)を 設ける場合には、この膜からの酸素の拡散が問題の一つとされており、この問題を解決す るために種々の提案がなされている(例えば特許文献 1 ~ 3 参照)。また、リーク電流を 抑制するために、高誘電率絶縁膜を設ける技術もある(例えば特許文献 4 参照)。

【特許文献1】特開平5-243562号公報

【特許文献2】特開2000-208720号公報

【特許文献3】特開2002-359370号公報

【特許文献4】特開2003-188356号公報

【発明の開示】

【発明が解決しようとする課題】

[0005]

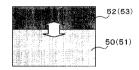

ところで、高誘電率 (High-k) ゲート絶縁膜やメタルゲート電極を採用する場合、例えば図 4 に示すように、高誘電率 (High-k) ゲート絶縁膜 5 0 又は S i O  $_2$  ゲート絶縁膜 5 1 上に直接メタルゲート電極 5 2 を設けることが考えられる。

しかしながら、高誘電率 (High-k)ゲート絶縁膜 5 0 又はS i  $O_2$ ゲート絶縁膜 5 1 上に直接メタルゲート電極 5 2 を設けると、高誘電率ゲート絶縁膜 5 0 又はS i  $O_2$ ゲート絶縁膜 5 1 とメタルゲート電極 5 2 とが激しく反応してしまうという問題がある。特に、高誘電率ゲート絶縁膜 5 0 とメタルゲート電極 5 2 との反応は、低い温度(例えば 5 0 0 程度)でも進行することが多いため、問題が大きい。このように、ゲート絶縁膜 5 0 , 5 1 とゲート電極 5 2 とが反応してしまうと、ゲートリーク電流の増大(極度の場合には絶縁性の喪失)を招き、信頼性の低下につながることになる。

[0006]

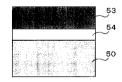

また、高誘電率ゲート絶縁膜 5 0 上にポリシリコン ( Poly-Si ) ゲート電極 5 3 を設けることも考えられる。

しかしながら、この場合にも、上記の組み合わせの場合と同様に、高誘電率ゲート絶縁膜 5 0 とポリシリコンゲート電極 5 3 とが反応してしまうという問題がある。

このような高誘電率ゲート絶縁膜50とポリシリコンゲート電極53との反応を抑えるために、図5に示すように、高誘電率ゲート絶縁膜50とポリシリコンゲート電極53との間にシリコン窒化膜(SiN膜)54を挟むことが提案されている(例えば上記特許文献3など)。

[0007]

しかしながら、高誘電率ゲート絶縁膜50とポリシリコンゲート電極53との間にSiN膜54を挟むと、SiN膜54に含まれる窒素Nがゲート電極53を構成するポリシリコンと反応してしまい、仕事関数が変動してしまう場合がある。そして、仕事関数が変動してしまうと、閾値電圧(Vth)が変動(例えば0.1V以上)してしまうため、目標とする閾値電圧に調整することが難しくなる。

[0008]

なお、上記特許文献 1 ~ 3 には、誘電率の高い膜からの酸素の拡散を抑制するための技術が開示されているに過ぎず、上記の問題については何ら考慮されていない。

また、上記特許文献 4 は、浮遊電極及び強誘電体層を備えるMFMIS型トランジスタにおいて、上部電極金属と強誘電体層との間や強誘電体層と浮遊電極金属層との間に、絶縁体層として、 $SiO_2$ ,  $Si_3N_4$ , SiON のうちのひとつあるいは複数と、高誘電率絶縁膜とを積層させる技術が開示されている。また、 $Si基板と浮遊電極(白金,ポリシリコン,シリサイドなど)との間に、ゲート絶縁膜(<math>SiO_2$ 膜, $Si_3N_4$ 膜,SiON 膜)と、高誘電率絶縁膜とを設けることも記載されている(例えば段落番号 0 0 4 9 ,図 5 参照)。しかしながら、この文献には、 $Si基板と浮遊電極との間に、絶縁体層として、ゲート絶縁膜(<math>SiO_2$ 膜, $Si_3N_4$ 膜,SiON膜)と、高誘電率絶縁膜とを設けることが記載されているに過ぎず、浮遊電極と高誘電率絶縁膜とが反応してしまうという上記の問題については何ら考慮されていない。

10

20

30

#### [0009]

本発明は、このような課題に鑑み創案されたもので、高誘電率ゲート絶縁膜やメタルゲート電極を採用する場合に、仕事関数の変動を抑えて閾値電圧の変動量を低く抑えることができるようにした、半導体装置を提供することを目的とする。

また、高誘電率ゲート絶縁膜やメタルゲート電極を採用する場合に、ゲートリーク電流の増大を抑えて、信頼性の低下を招かないようにすることも目的とする。

【課題を解決するための手段】

#### [0010]

このため、本発明の半導体装置は、ゲート電極と、高誘電率ゲート絶縁膜とを備え、ゲート電極がメタルゲート電極であるか、又は、ゲート絶縁膜が高誘電率ゲート絶縁膜である場合に、ゲート電極と高誘電率ゲート絶縁膜との間に、ゲート電極側から順に、シリコン酸化膜、シリコン窒化膜を備えることを特徴としている(請求項1)。

また、本発明の半導体装置は、ゲート電極と、高誘電率ゲート絶縁膜とを備え、ゲート電極がメタルゲート電極であるか、又は、ゲート絶縁膜が高誘電率ゲート絶縁膜である場合に、ゲート電極と高誘電率ゲート絶縁膜との間に、シリコン酸化膜を備えることを特徴としている(請求項 2 )。

#### [0011]

特に、ゲート電極をメタルゲート電極とする場合に適用するのが好ましい。この場合、メタルゲート電極は、Mo,W,Ta,Ti,Hf,Zr,V,Cr,Nbを含む金属群から選ばれるいずれか1種の金属を含むものとして構成するのが好ましい(請求項3)。また、高誘電率ゲート絶縁膜は、酸化ハフニウム,酸化ジルコニウム,酸化アルミニウム,酸化イットリウム,ランタン族酸化物、又は前記各酸化物のシリケート、又は前記各酸化物若しくは前記各シリケートを含む混合物により構成するのが好ましい(請求項4)。

#### [ 0 0 1 2 ]

さらに、本発明の半導体装置は、Mo,W,Ta,Ti,Hf,Zr,V,Cr,Nb を含む金属群から選ばれるいずれか1種の金属を含む金属膜と、高誘電率膜とを備え、金 属膜と高誘電率膜との間に、金属膜側から順に、シリコン酸化膜、シリコン窒化膜を備え ることを特徴としている(請求項5)。

## 【発明の効果】

### [0013]

したがって、本発明によれば、ゲート電極と高誘電率ゲート絶縁膜との間にシリコン酸化膜が設けられているため、仕事関数の変動を抑えることができ、これにより、閾値電圧の変動量を低く抑えることができるという利点がある。

また、本発明によれば、ゲート電極と高誘電率ゲート絶縁膜との間にシリコン窒化膜が設けられているため、ゲートリーク電流の増大を抑えることができ、ひいては信頼性を確保できるようになるという利点がある。

【発明を実施するための最良の形態】

#### [0014]

以下、図面により、本発明の実施の形態にかかる半導体装置について説明する。

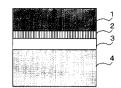

本実施形態にかかる半導体装置 [例えば C M O S (Complementary Metal Oxide Semicond uctor) デバイスなどの M O S デバイス (例えば M O S トランジスタを含む) ]は、図 1 に示すように、ゲート電極 1 と、シリコン酸化膜 2 と、シリコン窒化膜 3 と、ゲート絶縁膜4 とを備えるものとして構成される。

## [0015]

つまり、本半導体装置は、ゲート電極1がメタルゲート電極であるか、又は、ゲート絶縁膜4が高誘電率ゲート絶縁膜である場合に、ゲート電極1とゲート絶縁膜4との間に、ゲート電極1側から順に、シリコン酸化膜2、シリコン窒化膜3を備えるものとする。

ここで、ゲート電極1は、メタルゲート電極とするのが好ましい。特に、製造工程において活性化のために1000 以上の高温にする熱処理(アニール処理)を行なうことを考慮すると、熱処理工程における上限温度よりも高い融点を有する高融点金属により構成

20

10

30

40

するのが好ましい。例えば、Mo,W,Ta,Ti,Hf,Zr,V,Cr,Nbを含む金属群から選ばれるいずれか1種の金属を含む金属膜とするのが好ましい。つまり、Mo,W,Ta,Ti,Hf,Zr,V,Cr,Nbを含む金属群から選ばれるいずれか1種の金属、又はこれらの金属の化合物、又はこれらの金属や化合物を含む混合物により構成される金属膜とするのが好ましい。

#### [0016]

なお、ゲート絶縁膜を高誘電率ゲート絶縁膜とする場合には、ゲート電極はポリシリコンなどの一般に用いられている材料によって構成しても良い。

ゲート絶縁膜 4 は、高誘電率ゲート絶縁膜(High-kゲート絶縁膜,高誘電率膜)とするのが好ましい。例えば、酸化ハフニウム(HfO2),酸化ジルコニウム(ZrO2),酸化アルミニウム(Al2O3),酸化イットリウム(Y2O3),ランタン族酸化物(例えばLa2O3)、又はこれらの酸化物のシリケート(例えば、HfO2の場合、Hf SixOy;Hfシリケート)[Nを含んだシリケート(例えば、HfO2の場合、Hf SixOyNz;Hfシリケート)でも良い]、又はこれらの酸化物やそのシリケートを含む混合物(例えばHfAlOx)などにより構成するのが好ましい。

#### [0017]

なお、ゲート電極をメタルゲート電極とする場合には、ゲート絶縁膜はSiO₂などの一般に用いられている材料によって構成しても良い。

シリコン窒化膜 3 は、ゲートリーク電流の増大を抑えるために、ゲート電極 1 とゲート 絶縁膜 4 との間に設けられる。ここでは、シリコン窒化膜を S i N (窒化ケイ素)により 形成している。

#### [0018]

シリコン酸化膜 2 は、仕事関数の変動を抑えて閾値電圧の変動量を低く抑えるために、シリコン窒化膜 3 とゲート電極 1 との間に設けられる。ここでは、シリコン酸化膜を S i O。(酸化シリコン)により形成している。

上述のように、ゲートリーク電流の増大を抑えるために、シリコン窒化膜3を設けると、ゲート電極1とシリコン窒化膜3とが接することになる。一方、高融点金属に窒素が導入されると仕事関数が変化してしまう。例えば、モリブデンMoに窒素が導入されると仕事関数が変化してしまうことについては、例えば、IEEE Electron Device Letters, vol. 23, no.1, Page: 49-51に記載されている。このため、特に、ゲート電極1を高融点金属により構成する場合に、高融点金属からなるメタルゲート電極1にシリコン窒化膜3から窒素が導入され、仕事関数が変化してしまう可能性が高い。したがって、特に、ゲート電極1を高融点金属により構成する場合に、シリコン窒化膜3とゲート電極1との間にシリコン酸化膜2を設けることが重要になる。

### [0019]

ここでは、ゲート電極 1 とゲート絶縁膜 4 との間に、シリコン酸化膜 2 と、シリコン窒化膜 3 とを設け、ゲート絶縁膜 4 との間に、シリコン酸化膜 4 がート電極(例えば High-k 4 Si N 4 Si O 4 がート電極)の積層構造にし、その厚さ(膜厚)を、その後の熱処理やゲート電極 4 の材料の種類(例えばメタルの種類)によって調整するようにしている。このように構成することで、例えばゲート絶縁膜 4 シリコン酸化膜 4 が 4 で 4 で 4 の 4 の 4 で 4 の 4 で 4 の 4 で 4 の 4 で 4 の 4 で 4 の 4 で 4 の 4 で 4 の 4 で 4 の 4 で 4 の 4 で 4 の 4 で 4 の 4 で 4 の 4 で 4 の 4 で 4 の 4 で 4 の 4 で 4 の 4 で 4 の 4 で 4 の 4 で 4 の 4 で 4 の 4 で 4 の 4 で 4 の 4 で 4 の 4 で 4 の 4 で 4 の 4 で 4 の 4 で 4 の 4 で 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4 の 4

#### [0020]

逆に言うと、全体の厚さを薄くする点をそれほど考慮しなくてもよい場合には、上述の構成において、シリコン窒化膜3を設けずに、ゲート絶縁膜/シリコン酸化膜/ゲート電極(例えばHigh-k/SiO<sub>2</sub>/ゲート電極)という積層構造にすることもできる。

次に、本実施形態にかかる半導体装置の製造方法について説明する。ここでは、2つの代表的な例について説明するが、これに限られるものではない。以下、説明を分かり易くするため、本発明に関わる部分を中心に説明する。

## (第1の製造方法)

20

30

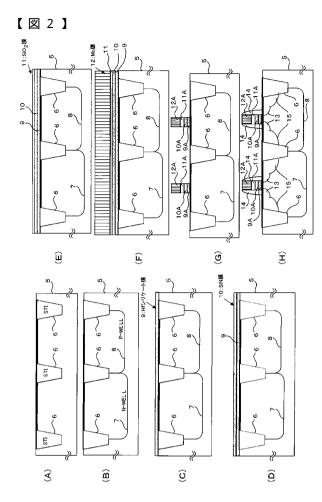

まず、第1の製造方法について、図2を参照しながら説明する。

### [0021]

第1の製造方法は、基本的に、MOSデバイスを製造する際の一般的な製造方法である。この方法によれば、従来の製造装置をそのまま使えることになる。

まず、図 2 ( A ) に示すように、 S T I ( Shallow Trench Isolation ) 技術を用いて、 S i 基板 5 に浅い溝を形成し、絶縁物で埋めて素子分離領域 6 を形成する。

次に、図 2 ( B )に示すように、 N ウエル( N - W E L L ) 7 及び P ウェル( P - W E L L ) 8 を形成し、チャネル注入を行なう。

#### [0022]

次いで、図 2 ( C )に示すように、例えば H f シリケートを M O C V D (Metal Organic Chemical Vapor Deposition)法により堆積させて、例えば 1 . 5 n m の H f シリケート膜(高誘電率膜) 9 [これがゲート絶縁膜(高誘電率ゲート絶縁膜)となる]を形成する。なお、 H f シリケート膜 9 の下側に他の膜を形成しておいても良い。

次に、図 2 ( D )に示すように、例えばLPCVD(Low Pressure Chemical Vapor Deposition)法によりSiH $_2$ С  $1_2$ ( D С S ;ジクロロシラン) - NH $_3$ (アンモニア)のガス系で、例えば 6 8 0 程度の所定の温度条件として、SiNを堆積させて、例えば 0 .2 n m のSiN膜(シリコン窒化膜)10を形成する。

#### [0023]

なお、例えばLPCVD法によりSiH $_4$ (モノシラン) - NH $_3$ (アンモニア)のガス系で、例えば600 程度の所定の温度条件として、SiNを堆積させて、SiN膜(シリコン窒化膜)10を形成しても良い。

次いで、図 2 (E)に示すように、CVD(Chemical Vapor Deposition)法により堆積させたSiN膜(CVD-SiN)の表面を、オゾン中で、かつ常温で酸化して、SiO<sub>2</sub>膜(シリコン酸化膜) 1 1 を形成する。

#### [0024]

なお、 C V D 法により堆積させた S i N 膜( C V D - S i N )の表面を、酸素中で、例えば 6 0 0 程度の所定の温度条件で酸化して、 S i O 2 膜(シリコン酸化膜) 1 1 を形成しても良い。

その後、図 2 ( F )に示すように、 M O C V D 法によりモリブデン M o を堆積させて M o 膜(モリブデン膜,金属膜) 1 2 [これがゲート電極(メタルゲート電極)となる]を 形成する。

## [0025]

そして、図 2 ( G )に示すように、ゲート加工を行なう。この結果、ゲート電極(メタルゲート電極,モリブデンゲート電極) 1 2 A / S i O 2 膜(シリコン酸化膜) 1 1 A / S i N 膜(シリコン窒化膜) 1 0 A / ゲート絶縁膜(高誘電率ゲート絶縁膜,H f シリケートゲート絶縁膜) 9 A の積層構造が形成される。

以降、通常のプロセスにしたがって、図2(H)に示すように、不純物を注入してエクステンション・ソースドレイン13を形成する。また、サイドウォール14も形成する。さらに、不純物を注入してコンタクト・ソースドレイン15も形成する。そして、熱処理(アニール処理)を行なって不純物を活性化させる。その後、メタル配線、層間絶縁膜の形成工程へ進む。

#### (第2の製造方法)

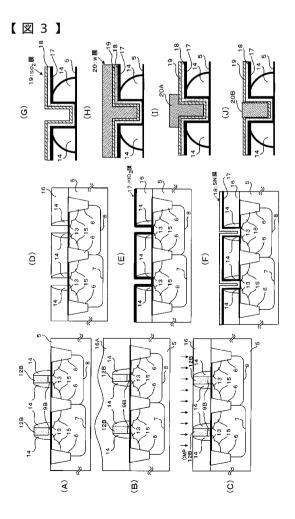

次に、第2の製造方法について、図3を参照しながら説明する。

## [0026]

第2の製造方法は、ダマシン法による製造方法である。ダマシン法は、例えば、Conference: Proceedings of IEEE International Electron Devices Meeting, 1992, Page: 301-4 やInternational Electron Devices Meeting 1998. Technical Digest Page: 785-8に詳しい。この方法によれば、工程は多くなるものの、膜厚を薄くできるという利点がある。

## [0027]

20

まず、上述したような通常の製造プロセス(図 2 参照)にしたがって、チャネル、ソース・ドレインを形成する。つまり、図 3 ( A )に示すように、後で除去しやすい材料 [ 通常、ポリシリコン(poly‐Si),シリコン窒化物(SiN)等 ] でダミー・ゲート絶縁膜9 B 及びダミー・ゲート1 2 B を形成し、これを用いてチャネル及びソース・ドレイン領域のプロファイルを形成する。なお、上述の第 1 の製造方法(図 2 参照)と同じものには同じ符号を付している。

#### [0028]

次に、図3(B)に示すように、層間絶縁膜を形成するための材料(例えば低誘電率材料)16Aを堆積させた後、図3(C)に示すように、ダミー・ゲート12Bの上部表面が出るまでCMP(Chemical Mechanical Polishing)法により研磨・除去して、層間絶縁膜16を形成する。

次いで、図3(D)に示すように、選択性のある溶液でダミー・ゲート12B及びダミー・ゲート絶縁膜9Bを除去する。

## [0029]

次に、図3(E)に示すように、例えばHfO $_2$ をALCVD(Atomic Layer Chemical Vapor Deposition)法により堆積させて、例えば3nmのHfO $_2$ 膜(高誘電率膜)17[これがゲート絶縁膜(高誘電率ゲート絶縁膜)となる]を形成する。

次いで、図3(F)に示すように、例えばLPCVD法によりSiH $_4$ -NH $_3$ のガス系で、例えば600 程度の所定の温度条件として、SiNを堆積させて、例えば0.3nmのSiN膜(シリコン窒化膜)18を形成する。

#### [0030]

なお、例えばLPCVD法によりDCS(SiH $_2$ С  $1_2$ ) - NH $_3$ のガス系で、例えば 6 8 0 程度の所定の温度条件として、SiNを堆積させて、SiN膜(シリコン窒化膜)18を形成しても良い。

以下、図3(G)~図3(J)では、説明を分かり易くするために、一方のゲート部分のみを拡大して示すこととする。

### [0031]

次に、図3(G)に示すように、CVD法により堆積させたSiN膜(CVD-SiN)18の表面を、酸素中で、例えば600 程度の所定の温度条件で酸化して、SiO<sub>2</sub>膜(シリコン酸化膜)19を形成する。

なお、С V D 法により堆積させた S i N 膜(C V D - S i N ) 1 8 の表面を、オゾン中で、かつ常温で酸化して、S i O 2 膜(シリコン酸化膜) 1 9 を形成しても良い。

#### [0032]

次いで、図 3 ( H )に示すように、 M O C V D 法によりタングステンW を堆積させてW 膜(タングステン膜,金属膜) 2 0 [これがゲート電極(メタルゲート電極)となる]を 形成する。

その後、図3(I)に示すように、反応性イオンエッチング (RIE; Reactive Ion Et ching)によりゲート加工を行なう。なお、図3(J)に示すように、СMP法によって削り落とすことでゲート加工を行なっても良い。この結果、ゲート電極(メタルゲート電極,タングステンゲート電極)20A(20B)/SiO $_2$ 膜(シリコン酸化膜)19/SiN膜(シリコン窒化膜)18/ゲート絶縁膜(高誘電率ゲート絶縁膜,HfO $_2$ ゲート絶縁膜)17の積層構造が形成される。以降、メタル配線、層間絶縁膜の形成工程へ進む

## [0033]

したがって、本実施形態にかかる半導体装置によれば、ゲート電極とゲート絶縁膜との間にシリコン酸化膜が設けられているため、仕事関数の変動を抑えることができ、これにより、閾値電圧の変動量を低く抑えることができるという利点がある。例えば、閾値電圧 V,bの変動量を5mV以下に抑えることができる。

また、ゲート電極とゲート絶縁膜との間にシリコン窒化膜が設けられているため、ゲートリーク電流の増大を抑えることができ、ひいては信頼性を確保できるようになるという

20

10

30

40

利点もある。例えば、寿命を2倍以上(多くの場合、数桁)長くすることができる。

#### [0034]

なお、本発明は、上述した実施形態に限定されず、上記以外にも、本発明の趣旨を逸脱 しない範囲で種々変形して実施することができる。

例えば、上述の実施形態では、MOSデバイスを例に説明したが、本発明はその他の構造の半導体装置(半導体デバイス)に適用することもできる。この場合、半導体装置は、Mo,W,Ta,Ti,Hf,Zr,V,Cr,Nbを含む金属群から選ばれるいずれか1種の金属を含む金属膜と、高誘電率膜とを備え、金属膜と高誘電率膜との間に、金属膜側から順に、シリコン酸化膜、シリコン窒化膜を備えるものとして構成される。

【図面の簡単な説明】

10

- [0035]

- 【図1】本発明の一実施形態にかかる半導体装置の構成を示す模式図である。

- 【図2】(A)~(H)は、本発明の一実施形態にかかる半導体装置の製造方法(第1の製造方法)を説明するための模式図である。

- 【図3】(A)~(J)は、本発明の一実施形態にかかる半導体装置の製造方法(第2の製造方法)を説明するための模式図である。

- 【図4】本発明の課題を説明するための模式図である。

- 【図5】本発明の課題を説明するための模式図である。

- 【符号の説明】

- [0036]

- 1 ゲート電極 ( メタルゲート電極 , 金属膜 )

- 2 , 1 1 , 1 1 A , 1 9 S i O <sub>2</sub> 膜 ( シリコン酸化膜 )

- 3 , 1 0 , 1 0 A , 1 8 S i N 膜 (シリコン窒化膜)

- 4 ゲート絶縁膜(高誘電率ゲート絶縁膜,高誘電率膜)

- 5 S i 基 板

- 6 シャロー・トレンチ

- 7 Nウェル

- 8 Pウェル

- 9 Hfシリケート膜

- 9 A H f シリケートゲート絶縁膜

- 12 モリブデン膜

- 12A モリブデンゲート電極

- 13 エクステンション・ソースドレイン

- 14 サイドウォール

- 15 コンタクト・ソースドレイン

- 16層間絶縁膜

- 1 6 A 層間絶縁膜材料

- 1 7 H f O<sub>2</sub>ゲート絶縁膜

- 20 タングステン膜

- 20 A , 20 B タングステンゲート電極

20

30

【図1】

【図4】

【図5】

## フロントページの続き

(51) Int.CI. F I テーマコード (参考)

H 0 1 L 27/092 (2006.01) H 0 1 L 21/8238 (2006.01)

F ターム(参考) 5F140 AA06 AA19 AB03 BD01 BD02 BD04 BD05 BD07 BD11 BD13 BE03 BE07 BE10 BF01 BF04 BF07 BF10 BG03 BG04 BG08

BG27 BG28 BG36 BG38 BG40 BH14 BK05 CB04 CB08 CE07

CE20