(19) **日本国特許庁(JP)**

# (12) 特許公報(B2)

(11)特許番号

特許第5522561号 (P5522561)

(45) 発行日 平成26年6月18日(2014.6.18)

(24) 登録日 平成26年4月18日(2014.4.18)

(51) Int. Cl. FL

HO1L 25/065 (2006, 01) HO1L 25/08 HO1L 25/07 (2006, 01) HO1L 25/12 HO1L 25/18 (2006.01)

HO1L 25/10

(2006, 01)

請求項の数 37 (全 12 頁)

(21) 出願番号 特願2008-528182 (P2008-528182)

(86) (22) 出願日 平成18年8月25日 (2006.8.25) (65) 公表番号 特表2009-506553 (P2009-506553A)

(43) 公表日 平成21年2月12日(2009.2.12)

(86) 国際出願番号 PCT/US2006/033219 (87) 国際公開番号 W02007/025127

(87) 国際公開日 平成19年3月1日(2007.3.1) 平成20年4月23日 (2008.4.23) 審査請求日

審判番号 不服2012-14864 (P2012-14864/J1) 審判請求日 平成24年8月2日(2012.8.2)

(31) 優先権主張番号 11/218,028

(32) 優先日 平成17年8月31日 (2005.8.31)

(33) 優先権主張国 米国(US) (73)特許権者 595168543

$\mathbf{Z}$

$\mathbf{Z}$

マイクロン テクノロジー、 インク. アメリカ合衆国、アイダホ州 83716 -9632. ボイズ、 サウス フェデ

ラル ウェイ 8000

(74)代理人 100106851

弁理士 野村 泰久

(74)代理人 100074099

弁理士 大菅 義之

||(72)発明者 イエ セン キム ダルソン

シンガポール共和国、シンガポール 54 3311, アンカーバレー レーン, #0

5-32, ブロック 311C

最終頁に続く

(54) 【発明の名称】マイクロ電子デバイスパッケージ、積重ね型マイクロ電子デバイスパッケージ、およびマイクロ 電子デバイスを製造する方法

## (57)【特許請求の範囲】

# 【請求項1】

第1の面に設けられた第1の外部コンタクトと、前記第1の面とは反対側の第2の面に 設けられた第1のワイヤボンドコンタクトと、を有する第1の基板と、

前記第1の基板と近接する第1のマイクロ電子ダイと、

前記第1の基板を背にする方に向いた第3の面に設けられた第2の外部コンタクトおよ び第2のワイヤボンドコンタクト、を有する第2の基板と、

前記第2の基板と近接する第2のマイクロ電子ダイであって、前記第1および第2のマ イクロ電子ダイが、個々に、裏面と、該裏面とは反対側の活性面に設けられた複数の活性 端子とを含み、前記第1のマイクロ電子ダイの前記裏面が前記第2のマイクロ電子ダイの 前記裏面に取り付けられている、第2のマイクロ電子ダイと、

前記第1のワイヤボンドコンタクトと前記第2のワイヤボンドコンタクトとを接続する ワイヤと、

モールドコンパウンドであって、前記モールドコンパウンドは、前記ワイヤと前記第1 および第2のマイクロ電子ダイとに接触し、前記ワイヤと前記第1および第2のマイクロ 電子ダイとを完全に封止し、かつ、前記第1の外部コンタクトも前記第2の外部コンタク トも覆うことなく前記第1および第2の基板を少なくとも部分的に封止する、モールドコ ンパウンドと、

を含むマイクロ電子パッケージ。

【請求項2】

20

前記第1の基板が、前記第2の基板よりも大きい、請求項1に記載のマイクロ電子パッケージ。

## 【請求項3】

前記第1の基板が、前記第2の基板にワイヤボンディングによって電気的に接続されている、請求項2に記載のマイクロ電子パッケージ。

## 【請求項4】

前記第1のマイクロ電子ダイが、ボードオンチップパッケージ構造を含む、請求項1に 記載のマイクロ電子パッケージ。

#### 【請求項5】

前記第2のマイクロ電子ダイが、ボードオンチップパッケージ構造を含む、請求項1に 記載のマイクロ電子パッケージ。

#### 【請求項6】

2 つ以上のマイクロ電子パッケージからなる積重ねアセンブリを可能にするために、前記第 2 の基板が、露出した電気コンタクトのグリッドアレイを有する、請求項 1 に記載のマイクロ電子パッケージ。

#### 【請求項7】

前記第1のマイクロ電子ダイが前記第1の基板に隣接し、前記第2のマイクロ電子ダイが前記第2の基板に隣接し、前記第1のマイクロ電子ダイが前記第2のマイクロ電子ダイに隣接する、請求項1に記載のマイクロ電子パッケージ。

# 【請求項8】

第1の面に設けられた第1の外部コンタクトと、前記第1の面とは反対側の第2の面に 設けられた第1のワイヤボンドコンタクトと、を有する第1の基板と、

前記第1の基板と近接する第1のマイクロ電子ダイと、

前記第1の基板を背にする方に向いた第3の面に設けられた第2の外部コンタクトおよび第2のワイヤボンドコンタクト、を有する第2の基板と、

前記第2の基板と近接する第2のマイクロ電子ダイと、

前記第 1 のワイヤボンドコンタクトと前記第 2 のワイヤボンドコンタクトとを接続するワイヤと、

モールドコンパウンドであって、前記モールドコンパウンドは、前記ワイヤと前記第1 および第2のマイクロ電子ダイとに接触し、前記ワイヤと前記第1および第2のマイクロ 電子ダイとを完全に封止し、かつ、前記第1の外部コンタクトも前記第2の外部コンタクトも覆うことなく前記第1および第2の基<u>板を</u>少なくとも部分的に封止する、モールドコンパウンドと、

を含む第1のマイクロ電子パッケージ、ならびに、

第3の基板と、

前記第3の基板と電気的に接続する第3のマイクロ電子ダイと、

前記第2および第3の基板の間の複数の電気接続部と、

を含む第2のマイクロ電子パッケージ、

を含む積重ね型マイクロ電子パッケージアセンブリ。

# 【請求項9】

前記第1および第2のマイクロ電子パッケージの間の前記複数の電気接続部が、前記第2および第3の基板の間のはんだボールを含む、請求項8に記載の積重ね型マイクロ電子パッケージアセンブリ。

# 【請求項10】

前記第1の基板が、前記第2の基板よりも大きい、請求項8に記載の積重ね型マイクロ電子パッケージアセンブリ。

#### 【請求項11】

第1の面に設けられた第1の外部コンタクトと、前記第1の面とは反対側の第2の面に 設けられた第1のワイヤボンドコンタクトと、を有する第1の基板と、

前記第1の基板の前記第2の面に取り付けられた第1のマイクロ電子ダイと、

20

10

30

•

40

前記第1の基板を背にする方に向いた第3の面に設けられた第2の外部コンタクトおよび第2のワイヤボンドコンタクト、を有する第2の基板と、

前記第2の基板に取り付けられた第2のマイクロ電子ダイと、

前記第1および第2のマイクロ電子ダイの間のスペーサと、

前記第1のマイクロ電子ダイを前記第1の基板の前記第1のワイヤボンドコンタクトに接続する第1の組のワイヤと、

前記第2の基板の前記第2のワイヤボンドコンタクトを前記第1の基板の前記第1のワイヤボンドコンタクトに接続する第2の組のワイヤと、

モールドコンパウンドであって、前記モールドコンパウンドは、前記第2の組のワイヤと前記第1および第2のマイクロ電子ダイとに接触し、前記第2の組のワイヤと前記第1 および第2のマイクロ電子ダイとを完全に封止し、かつ、前記第1の外部コンタクトも前記第2の外部コンタクトも覆うことなく前記第1および第2の基板を少なくとも部分的に封止する、モールドコンパウンドと、

を含む積み重ね可能なマルチ電子ダイパッケージ。

# 【請求項12】

前記第2のマイクロ電子ダイを、前記第2の基板内の開口を通って前記第2の基板に接続する第3の組のワイヤをさらに備える、請求項11に記載の積み重ね可能なマルチ電子ダイパッケージ。

#### 【請求項13】

前記第1のマイクロ電子ダイおよび前記第1の基板が、チップオンボードパッケージ構造を含み、前記第2のマイクロ電子ダイおよび前記第2の基板が、ボードオンチップパッケージ構造を含む、請求項11に記載の積み重ね可能なマルチ電子ダイパッケージ。

# 【請求項14】

前記第1の基板が、前記第2の基板よりも大きい、請求項11に記載の積み重ね可能なマルチ電子ダイパッケージ。

## 【請求項15】

第1の面に設けられた第1の外部コンタクトと、前記第1の面とは反対側の第2の面に 設けられた第1のワイヤボンドコンタクトと、を有する第1の基板と、

前記第1の基板と電気的に接続する、前記第1の基板上の第1のマイクロ電子ダイと、前記第1のマイクロ電子ダイの上に取り付けられた第2のマイクロ電子ダイと、

前記第2のマイクロ電子ダイ上の第2の基板であって、該第2の基板は、前記第1の基板を背にする方に向いた第3の面に設けられた第2の外部コンタクトおよび第2のワイヤボンドコンタクトを有する、第2の基板と、

前記第1の基板に設けられた前記第1のワイヤボンドコンタクトを、前記第2の基板に 設けられた前記第2のワイヤボンドコンタクトに接続する第1の組のワイヤと、

モールドコンパウンドであって、前記モールドコンパウンドは、前記第1の組のワイヤと前記第1および第2のマイクロ電子ダイとに接触し、前記第1の組のワイヤと前記第1 および第2のマイクロ電子ダイとを完全に封止し、かつ、前記第1の外部コンタクトも前記第2の外部コンタクトも覆うことなく前記第1および第2の基板を少なくとも部分的に封止する、モールドコンパウンドと、

前記第2の基板を前記第2のマイクロ電子ダイに接続する第2の組のワイヤと、 を含む積み重ね可能なマルチ電子ダイパッケージ。

# 【請求項16】

前記第1の基板の上に積み重ねられるダイパッケージの基板と電気的に接続するように構成された、前記第1の基板の第1の面上の第1のコンタクト配列をさらに含む、請求項15に記載の積み重ね可能なマルチ電子ダイパッケージ。

#### 【請求項17】

前記第1の基板が、前記第2の基板よりも大きい、請求項15に記載の積み重ね可能なマルチ電子ダイパッケージ。

# 【請求項18】

20

10

30

前記第1および第2の基板の少なくとも一部を覆うケーシングをさらに含む、請求項1 5に記載の積み重ね可能なマルチ電子ダイパッケージ。

# 【請求項19】

前記ケーシングが、他のパッケージの基板と接続するように構成された電気コンタクト を有する前記第2の基板の領域を露出させる開口を有する、請求項18に記載の積み重ね 可能なマルチ電子ダイパッケージ。

#### 【請求項20】

前記第1および第2の組のワイヤが、ワイヤボンドを含む、請求項15に記載の積み重 ね可能なマルチ電子ダイパッケージ。

# 【請求項21】

マイクロ電子パッケージを製造する方法であって、

第1のマイクロ電子ダイを第1の基板に取り付けるステップであって、該第1の基板は 、第1の面に設けられた第1の外部コンタクトと、前記第1の面とは反対側の第2の面に 設けられた第1のワイヤボンドコンタクトとを有する、ステップと、

第2のマイクロ電子ダイを前記第1のマイクロ電子ダイに取り付けるステップであって 、前記第1のマイクロ電子ダイの裏面が前記第2のマイクロ電子ダイの裏面と対向してい る、ステップと、

第2の基板を前記第2のマイクロ電子ダイに取り付けるステップであって、前記第2の 基板が、前記第1の基板を背にする方に向いた第3の面に設けられた第2の外部コンタク トおよび第2のワイヤボンドコンタクトを有する、ステップと、

前記第1の基板に設けられた前記第1のワイヤボンドコンタクトと、前記第2の基板に 設けられた前記第2のワイヤボンドコンタクトとの間の第1の組の電気的接続を作成する ステップと、

前記第1のマイクロ電子ダイと前記第1の基板との間の第2の組の電気的接続を作成す るステップと、

前記第2のマイクロ電子ダイと前記第2の基板との間の第3の組の電気的接続を作成す るステップと、

モールドコンパウンドで、前記第1の組の電気的接続と前記第1および第2のマイクロ 電子ダイとを完全に封止するステップであって、前記モールドコンパウンドは前記第1の 組の電気的接続と前記第1および第2のマイクロ電子ダイとに接触する、ステップと、

前記モールドコンパウンドで、前記第1の外部コンタクトも前記第2の外部コンタクト も覆うことなく、前記第1および第2の基板を少なくとも部分的に封止するステップと、 を含む方法。

# 【請求項22】

前記第2の組の電気的接続が、前記第1の基板内の開口を通って延びるワイヤによって 作成される、請求項21に記載の方法。

# 【請求項23】

前記第3の組の電気的接続が、前記第2の基板内の開口を通って延びるワイヤによって 作成される、請求項22に記載の方法。

# 【請求項24】

前記第1、第2および第3の組の電気的接続をモールドコンパウンド内に封入するステ ップをさらに含む、請求項21に記載の方法。

# 【請求項25】

前記第1の基板が、前記第2の基板よりも大きい、請求項21に記載の方法。

#### 【請求項26】

前記第1のマイクロ電子ダイが、ボードオンチップパッケージ構造を含む、請求項21 に記載の方法。

# 【請求項27】

前記第2のマイクロ電子ダイが、ボードオンチップパッケージ構造を含む、請求項21 に記載の方法。

10

20

30

40

10

20

30

50

# 【請求項28】

前記第1のマイクロ電子ダイの裏面を接着剤によって前記第2のダイの裏面に取り付けるステップをさらに含む、請求項21に記載の方法。

#### 【請求項29】

積重ね型マイクロ電子パッケージアセンブリを製造する方法であって、

第1の面に設けられた第1の外部コンタクトと、前記第1の面とは反対側の第2の面に設けられた第1のワイヤボンドコンタクトと、を有する第1の基板に、第1のマイクロ電子ダイを取り付けるステップと、

第2のマイクロ電子ダイを前記第1のマイクロ電子ダイに取り付けるステップであって、前記第1のマイクロ電子ダイの裏面が前記第2のマイクロ電子ダイの裏面と対向している、ステップと、

第2の基板を前記第2のマイクロ電子ダイに取り付けるステップであって、前記第2の 基板が、前記第1の基板を背にする方に向いた第3の面に設けられた第2の外部コンタク トおよび第2のワイヤボンドコンタクトを有する、ステップと、

前記第1の基板に設けられた前記第1のワイヤボンドコンタクトと、前記第2の基板に 設けられた前記第2のワイヤボンドコンタクトとの間の第1の組の電気的接続を作成する ステップと、

前記第1のマイクロ電子ダイと前記第1の基板との間の第2の組の電気的接続を作成するステップと、

前記第2のマイクロ電子ダイと前記第2の基板との間の第3の組の電気的接続を作成するステップと、

によって第1のマイクロ電子パッケージを製作するステップ、

モールドコンパウンドで、前記第1の組の電気的接続と前記第1および第2のマイクロ 電子ダイとを完全に封止するステップであって、前記モールドコンパウンドは前記第1の 組の電気的接続と前記第1および第2のマイクロ電子ダイとに接触する、ステップ、

前記モールドコンパウンドで、前記第1の外部コンタクトも前記第2の外部コンタクトも覆うことなく、前記第1および第2の基<u>板を</u>少なくとも部分的に封止するステップ、ならびに、

第2のマイクロ電子パッケージを前記第1のマイクロ電子パッケージに取り付けるステップ

を含む方法。

# 【請求項30】

前記第2のマイクロ電子パッケージのコンタクトを前記第1の基板上のコンタクトに接続することによって、前記第1および第2のマイクロ電子パッケージの間の電気的接続を 作成するステップをさらに含む、請求項29に記載の方法。

#### 【請求項31】

前記第1および第2のマイクロ電子パッケージの間の電気的接続をはんだ要素によって 作成するステップをさらに含む、請求項30に記載の方法。

#### 【請求頃32】

前記第2の組の電気的接続が、前記第1の基板内の開口を通って延びるワイヤボンドに 40 よって作成される、請求項29に記載の方法。

#### 【請求項33】

前記第3の組の電気的接続が、前記第2の基板内の開口を通って延びるワイヤボンドによって作成される、請求項29に記載の方法。

#### 【請求項34】

前記第1の基板が前記第2の基板よりも大きく、前記第1の組の電気的接続を、前記第 1の基板の第2の面のコンタクトを前記第2の基板の第2の面上のコンタクトにワイヤボ ンディングすることによって作成するステップをさらに含む、請求項29に記載の方法。

## 【請求項35】

第 3 のマイクロ電子パッケージを前記第 1 のマイクロ電子パッケージに取り付けるステ

ップと、前記第3のマイクロ電子パッケージのコンタクトを前記第2の基板上のコンタクトに接続することによって、前記第1および第3のマイクロ電子パッケージの間の電気的接続を作成するステップとをさらに含む、請求項30に記載の方法。

# 【請求項36】

前記第1の基板上の前記コンタクトが、前記第1の基板の縁部から離れて配置される、 請求項30に記載の方法。

#### 【請求項37】

前記第2のマイクロ電子パッケージが、前記第1のマイクロ電子パッケージと同じである、請求項29に記載の方法。

## 【発明の詳細な説明】

# 【技術分野】

#### [0001]

本発明は、マイクロ電子デバイスパッケージ(microelectronic de vice package)、積重ね型マイクロ電子デバイスパッケージ(stacked microelectronic de vice package)、およびマイクロ電子デバイスを製造する方法に関する。

# 【背景技術】

# [0002]

マイクロ電子デバイスは一般に、高密度の微小構成要素を有する集積回路を含むダイ(すなわちチップ)を有する。典型的なプロセスでは、多数のダイが、様々な段階(例えば、注入、ドーピング、フォトリソグラフィ、化学気相成長、プラズマ気相成長、めっき、平坦化、エッチングなど)で繰り返すことができる様々なプロセスを用いて、単一ウェハ上に製造される。ダイは一般に、集積回路に電気的に結合される微小ボンドパッドの配列を含む。ボンドパッドは、供給電圧、信号などが、それを通って集積回路に往復伝送される、ダイ上の外部電気コンタクトである。次に、ダイは、ウェハをダイシングし個々のダイを裏面研削することによって、互いに分離される(すなわち個片化される)。ダイは一般に、個片化された後、ボンドパッドを、様々な電源線、信号線、および接地線により容易に結合されうるより大きな配列の電気端子に結合させるために、「パッケージ化」される。

## [0003]

個々のダイは、ダイ上のボンドパッドをピン、ボールパッドまたは他のタイプの電気端子の配列に電気的に結合し、次いでダイをモールドコンパウンド内に封止して、ダイを環境因子(例えば、湿気、粒子、静電気、および物理的衝撃)から保護し、ならびにマイクロ電子デバイスパッケージを形成することによって、パッケージ化されうる。 1 つの応用例では、ボンドパッドは、ボールパッド配列を有するインタポーザ基板上のコンタクトに電気的に接続される。

# 【発明の開示】

【発明が解決しようとする課題】

#### [0004]

電子製品は、非常に限られた空間に極めて高密度の構成要素を有するために、パッケージ化したマイクロ電子デバイスを必要とする。例えば、記憶装置、プロセッサ、表示装置、および他のマイクロ電子構成要素のために使用可能な空間は、携帯電話、PDA、携帯用コンピュータ、および他の多くの製品内で極めて限定される。したがって、プリント路板上のマイクロ電子デバイスの表面積すなわち「フットプリント」を縮小するために、強力な動因がある。マイクロ電子デバイスのサイズを縮小するのは、困難となりうる。というのは、高性能のマイクロ電子デバイスは一般に、より多くのボンドパッドを有し、とれによってボールグリッドアレイが大きくなり、したがってフットプリントが大きるからである。所与のフットプリント内のマイクロ電子デバイスの密度を増大させるために用いられる1つの技法は、1つのマイクロ電子デバイスパッケージを他のパッケージの上に積み重ねることである。しかし、こうした既存の積重ね設計にはいくつかの欠点があり

10

20

30

40

うる。例えば、それらは、相互接続のために基板上に余分な空間を必要としたり、デバイスの個別の品質管理試験を妨げたり、あるいは他の欠点を有する可能性がある。

## 【課題を解決するための手段】

# [0005]

マイクロ電子パッケージは、単一パッケージ内に2つのチップまたはダイを有利に含む。これは、場所を取らない設計を可能にする。ある設計では、より薄いパッケージを実現することもできる。パッケージは、ダイが積重ねアセンブリに配置される前に個別に試験されうるように、設計することができる。ダイは、共平面性の欠点をよりうまく回避するために、任意で背中合わせに配置することもできる。一実施形態では、マイクロ電子パッケージは、第1の基板と電気的に接続する第1のマイクロ電子ダイと、第1の基板と電気的に接続する第2のマイクロ電子ダイとを有する。電気的接続がワイヤボンディングによって行われる設計では、一方の基板が他方の基板よりも大きいことが有利である。

# [0006]

マイクロ電子パッケージは、積重ねアセンブリを形成するために、他のすなわち第2のマイクロ電子パッケージに積み重ねる、または取り付けることができる。一方のマイクロ電子パッケージの第1の基板上のコンタクトを、他方のマイクロ電子パッケージの第2の基板上のコンタクトに電気的に接続または連接することにより、2つのマイクロ電子パッケージアセンブリを電気的に接続することができる。積み重ねられるパッケージは、回路板に取り付けられ、どちらか一方のパッケージの別の基板上のコンタクトを介して回路板に電気的に接続されうる。

## [0007]

本発明のいくつかの実施形態の多くの具体的な詳細について、複数のマイクロ電子デバイスを単一アセンブリに一体に形成することに関して以下に説明するが、他の実施形態では、各デバイスを別々に形成することができる。本発明によるいくつかの実施形態は、図面に記載されている。しかし、図面は、説明だけのために提供される。それらは、本発明の範囲を限定して示すものではない。以下の文章は、本発明の特定の実施形態を十分理解できるように提供される。しかし、当業者なら、本発明が追加の実施形態を有しうること、あるいは、本発明が、図面に記載されている、または示される詳細のうちのいくつかがなくても実施されうることを理解する。

## 【発明を実施するための最良の形態】

# [0008]

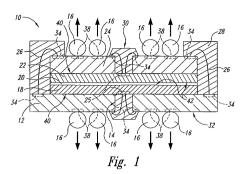

ここで図1を参照すると、積み重ね可能なマイクロ電子パッケージ(stackablemicroelectronic package)10が、開口または溝14を有する第1の基板12を有する。開口14は、基板12のほぼ中心に有利に位置することができる。第1のマイクロ電子ダイまたはチップ18は、活性面40および裏面42を有する。活性面40は、第1の基板12に取り付けられるか、または隣接している。ダイ18の活性面40は、基板12の第2の面(ここでは上面として示される)上のコンタクトと電気的に接続する端子(例えばボンドパッド)を有する。端子およびコンタクトは、典型的にはアレイ状に配置される。基板12上のコンタクトは一般に、基板12の第1の面(ここでは底面として示される)上の他のコンタクトに電気的に接続されて、アセンブリ10を回路板または他の上位アセンブリと電気的に接続できるようにする。

# [0009]

第2のマイクロ電子ダイまたはチップ22は、第1のダイ18の裏面に、好ましくは接着剤20で取り付けられる裏面42を有する。この取付け(ならびに本明細書で記載される他の取付け)は、直接でも間接でもよく、すなわち、それらの間に1つ以上の中間要素があってもなくてもよい。各ダイ18および22は一般に、25に破線で概略的に示される1つ以上の集積回路を有する。第2の基板24は、第2のダイ22の活性面40に取り付けられる。

# [0010]

50

40

10

20

10

20

30

40

50

第1の基板12は、第2の基板24よりも大きく(すなわち、幅が広くおよび / または長さが長い)、これは、図1に示されるように、第1の基板12が第2の基板24から外に広がることを意味する。第1の基板12の上面すなわち第2の面上のパッドまたはコンタクト34を、第2の基板24の上面すなわち第2の面上のパッドまたはコンタクト34に接続することによって、第1の基板と第2の基板との間で電気的接続が行われる。これらの接続は、ワイヤボンド26によって行うことができる。第1の基板上のコンタクト34は、第2の基板24から外に広がる第1の基板12の領域上に位置するので、それらの間のボンド接続は、既存の技法を用いて行うことができる。パッドまたはコンタクト34および38は、説明のために、図1に破線で拡大して不釣り合いに示される。

#### [0011]

第2の基板24の上のコンタクトと第2のダイ22の活性面上の端子との間で、電気的接続が行われる。図1に示されるように、第2の基板24は、貫通する開口または溝14を有する。したがって、ワイヤボンド26または他の接続要素が開口14を通って延びて、第2の基板24と第2のダイ22の間の接続を行うことができる。第2のダイ22に対するワイヤボンド手順は、第1のダイ18に対するワイヤボンド手順と比べると逆であり、したがって、ピンアサインは、ボールピン配列に相当する。

## [0012]

第1の基板12と第1のダイ18上の端子との間の電気的接続も、同じ方法で行うことができる。図1に示されるパッケージ10は、左右対称とすることができる。ダイ18および22は、同じ幅または長さを有するものとして示されるが、ダイは、同じでもよく、あるいは電気的および / または機械的に互いに異なってもよい。基板12および24は、ダイを保持し、かつ電気的相互接続を可能にするために、プリント回路板または他のタイプの基板とすることができる。基板上のパッド134は一般に、同等のまたは対応する配列の電気的結合部(例えば、はんだボールまたは他のはんだ要素)を受けるように、アレイ状に配置される。第1のダイ18および第1の基板12は、ボードオンチップ構造を形成する。同様に、第2のダイ22および第2の基板22もまた、ボードオンチップ構造を形成する。

#### [0013]

ワイヤボンド接続26が行われた後、モールドコンパウンド28が、図1に示される各領域内のワイヤボンド26を覆うように塗布される。ワイヤボンド26と、基板の内端または外端に隣接するコンタクト34と、それらが接続する対象であるダイ上の端子とが、モールドコンパウンド28で覆われる。ダイ18および22のすべての面を、基板およびモールドコンパウンドで完全に密封する、または覆うことができる。第1の基板12の下側は、開口14でのワイヤボンドを除いて、モールドコンパウンド28で覆われていないことが有利である。第2の基板24上のワイヤボンドコンタクト34間に位置する露出コンタクト38は、モールドコンパウンドで覆われない。これにより、パッケージ10上に積み重ねられる他のパッケージとの電気的接続を行う際に使用するために、第1の基板の下面上の露出コンタクト38を覆われないままにしておく。

# [0014]

次いで、すべてのコンタクトおよび端子は、依然として試験装置によってアクセス可能であるので、パッケージ10を試験することができる。これにより、パッケージの積重ねアセンブリへの最終組立ての前に、欠陥パッケージを検出し除去することが可能になる。したがって、積重ねアセンブリは、既知の良好なアセンブリパッケージで製作することができる。これは、製造時の歩留りを改善する。

## [0015]

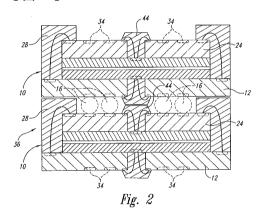

パッケージ10が回路板または他の上位アセンブリに取り付けられる用途では、パッケージ10は、図1の向きに、すなわち第1の基板12が回路板上にある状態で、取り付けることができる。次いで、露出コンタクト38が回路板上のコンタクト、パッドまたは端子に連接することにより、パッケージ10と回路板との間で電気的接続を行うことができる。これらの接続を行うために、リフローはんだボール16を使用することができる。パ

ッケージ上10に追加のパッケージが積み重ねられない場合、回路板への接続は、代替的または付加的に、第2の基板24上の露出コンタクト38を介して行うことができる。図2に示されるように、1つ以上の追加のパッケージがパッケージ10上に積み重ねられる場合、回路板への接続は、代替的または付加的に、スタックの最上部のパッケージ上の露出コンタクトがあればそれを介して行うことができる。

## [0016]

図2は、第1のパッケージ10の上に積み重ねられる第2のパッケージ10を示す。2つの積み重ねられるパッケージの間の電気的接続を行うために、はんだボールまたは要素16をランドグリッドアレイ上で使用することができる。さらに、上部パッケージの第1の基板12と下部パッケージ上のモールドコンパウンド28との間、および/または積重ねアセンブリ36の中心に示される隣接するモールドコンパウンド突出部44相互間で、パッケージ10の機械的取付けを接着剤で行うことができる。第2のパッケージは、相互間で必要な電気的接続を行うことができるのであれば、第1のパッケージと電気的かつ機械的に同じでも異なっていてもよい。図2は、2つのパッケージ10を有する積重ねアセンブリ36を示すが、もちろん、積重ねアセンブリ36は、例えば3つ、4つ、5つまたはそれ以上のパッケージを有することもできる。

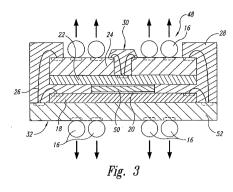

## [0017]

図3は、他の実施形態48を示し、第1の基板52上の第1のダイ18が、チップオンボード構造を形成する。図1に示される第1の基板12とは異なり、図3内の第1の基板52は、開口または溝を有さない。スペーサまたはエポキシパッド50が、第1のダイ18上に設けられる。第2のダイ22が、スペーサ50上に設けられる。これらのダイは、接着剤20によってスペーサに取り付けることができる。第2のダイ22に第2の基板24が取り付けられて、図1内の第2のダイおよび第2の基板に類似のボードオンチップ構造を形成する。スペーサ50は、第1のダイ18の活性面の上に空間をもたらして、第1のダイ18と第1の基板52との間でワイヤボンディングまたは同様の接続を行うことが可能になる。

## [0018]

第2のダイ22が第1のダイ18よりも小さい場合、スペーサ50は、ワイヤボンディングのために必要ないので、省略することができる。この場合、第2のダイ22は、図1と同様に、第1のダイ18に直接取り付けることができる。第1および第2のダイの間の接続は、第2の基板のボンドフィンガから第1の基板のボンドフィンガまでの周辺ワイヤボンディングによって行うことができる。第2の基板24と第2のダイ22との間、および第2の基板24と第1の基板との間のワイヤボンディングまたは他の電気的接続、ならびにモールドコンパウンド28は、上述したように、図1と同じように行う、または使用することができる。図3に示されるパッケージ48は、追加の他のマイクロ電子パッケージ(パッケージ48と同じでも異なっていてもよい)の上に積み重ねられて、図2に示される概念と同様の積重ねアセンブリ36を形成することができる。

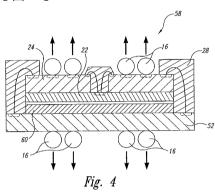

## [0019]

図4は、図3に示す設計とほぼ同様であるが、第1のダイ60がフリップチップパッケージ構造である、他の実施形態58を示す。第1のダイ60は、活性面を下にして第1の基板52に取り付けられる。第1のダイ60と第1の基板52との間の電気的接続は、下向きの活性面上の導電性バンプまたは電気的結合部を介して行われる。バンプは、第1の基板52上の目標パッドまたはコンタクトと一致しかつ接触する。第2のダイ22の裏面は、第1のダイ60の裏面に取り付けられる。第2の基板24は、第2のダイ22の活性面の上に取り付けられて、ボードオンチップ構造を形成する。第2のダイ22と第2の基板24との間、および第1の基板52と第2の基板24との間の電気的接続、ならびにモールドコンパウンド28は、図1または3を参照して上述したのと同じように行うことができる。パッケージ58は、図1~3に関連して上述したように、積み重ねられて、複数パッケージの積重ねアセンブリ36を形成することができる。

# [0020]

10

20

30

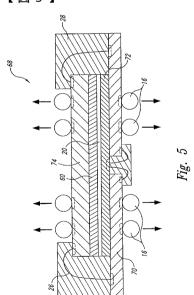

図5は、図4に示す設計とほぼ同様であるが、フリップチップを小さい方の基板74に取り付けられる第2のダイ60として用いた、他の実施形態68を示す。第1のダイ72が、ボードオンチップ構造の形で第1の基板70に取り付けられる。第2のダイ60は、接着剤20を用いて、第1のダイ72の上に背中合わせに取り付けることができる。第2の基板74は、第2のダイ60に取り付けられる。第2のダイ60はフリップチップであるので、図4内の第1のダイ60を参照して上述したように、電気的接続が、第2のダイと第2の基板との間で第2のダイ上のバンプを介して行われる。第2のダイ60に取り付けられる第2の基板74は、第1の基板70よりも小さい。第1および第2の基板の間、および第1のダイ72と第1の基板70との間の電気的接続は、ワイヤボンド26を介して行うことができる。

[0021]

上述の設計は、同一平面性の問題を(ダイが背中合わせになっているため)回避すること、既存の設備を用いてアセンブリが可能であること、第1および第2の基板が、業界標準(JEDEC)に適合するボールピン配列のアサインを有することができること、構成要素を、最終アセンブリの前に個別に試験することができること、より薄いパッケージ高さを達成できること、などの利点を提供することができる。もちろん、様々な実施形態を用いて様々な方法で本発明を実施して、これらの利点それぞれを実現する場合もあり、そうでない場合もある。本発明は、それぞれの利点をかならずしも達成することなく使用することもできる。

[0022]

パッド、コンタクト、端子、バンプ、電気的結合部などの用語は、電気的な接続を行うために用いられる特徴を制限なしに表現するためのものであり、特定の排他的な意味を有するものではない。本明細書で用いられているような、取り付けられる(attached)という用語は、直接間接を問わず、接合される、接着される、連接される、ボンディングされる、あるいはその他の方法で支持されることを意味する。基板という用語は、ここではダイが取り付けられる要素または基部を意味し、基板は、典型的には回路板を含むが、それに限らない。間(between)という用語は、周辺ワイヤボンディングと同様に、第1の要素と第2の要素との間の直接接続を意味するが、他のタイプの直接的または間接的電気的接続も含む。

[0023]

したがって、いくつかの実施形態、およびそれらを製作する方法について示し、説明してきた。本発明の精神および範囲から逸脱することなく、様々な変更および置換を行うことができる。したがって、本発明は、特許請求の範囲とその同等物による以外は限定されるべきでない。

【図面の簡単な説明】

[0024]

【図1】積み重ね可能なマイクロ電子マルチダイパッケージの概略断面図である。

【図2】図1に示される2つのパッケージが、積重ねアセンブリを形成するように互いに取り付けられるものの概略断面図である。

【図3】他の積み重ね可能なマルチダイパッケージの概略断面図である。

【図4】他の積み重ね可能なマルチダイパッケージの概略断面図である。

【図5】さらに他の積み重ね可能なマルチダイパッケージの概略断面図である。

10

20

30

【図1】

【図2】

【図3】

【図4】

【図5】

# フロントページの続き

# (72)発明者 チョン,チン ホイ

シンガポール共和国,シンガポール 579727,ブラッデルヒル,ブラッデル ヴュー,#07-29,ブロック 10H

## 合議体

審判長 丸山 英行

審判官 小関 峰夫

審判官 平田 信勝

# (56)参考文献 特開平2-5553(JP,A)

特開平3-159146(JP,A)

特開2000-228468(JP,A)

特開2005-26680(JP,A)

特開2005-150719(JP,A)

実開平2-89852(JP,U)

米国特許第6472736(US,B1)

米国特許出願公開第2005/0023657(US,A1)

米国特許出願公開第2005/0046006(US,A1)

国際公開第2005/059967(WO,A2)

# (58)調査した分野(Int.CI., DB名)

H01L 25/08

H01L 25/12