### (19) **日本国特許庁(JP)**

# (12) 特許公報(**B2)**

(11)特許番号

特許第4731718号 (P4731718)

(45) 発行日 平成23年7月27日(2011.7.27)

(24) 登録日 平成23年4月28日 (2011.4.28)

| (10) / 514   | , ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | F. 7, 22. Ed (20             | ,             |                     |     | (-1)           | 1 /94=0   1/4=0 | уд (2011. 1.20) |

|--------------|-----------------------------------------|------------------------------|---------------|---------------------|-----|----------------|-----------------|-----------------|

| (51) Int.Cl. |                                         |                              | FI            |                     |     |                |                 |                 |

| G09F         | 9/00                                    | (2006.01)                    | GO9F          | 9/00                | 3 4 | 48C            |                 |                 |

| G02F         | 1/133                                   | (2006.01)                    | GO2F          | 1/133               | 5 5 | 50             |                 |                 |

| G09F         | 9/30                                    | (2006.01)                    | GO9F          | 9/30                | 33  | 38             |                 |                 |

| HO1L         | 27/32                                   | (2006.01)                    | GO9F          | 9/30                | 3 6 | 6 5 Z          |                 |                 |

| G09G         | 3/20                                    | (2006.01)                    | GO9G          | 3/20                | 6   | 1 1 A          |                 |                 |

|              |                                         |                              |               |                     | 1   | 請求項の数 7        | (全 49 頁)        | 最終頁に続く          |

| (21) 出願番号    |                                         | 特願2001-133727 (P2001-133727) |               | (73) 特許権者 000153878 |     |                |                 |                 |

| (22) 出願日     |                                         | 平成13年4月27日 (2001.4.27)       |               |                     | ,   | 株式会社半導         | 体エネルギー研         | F究所             |

| (65) 公開番号    |                                         | 特開2002-328617 (P2            | 2002-328617A) |                     |     | 神奈川県厚木市長谷398番地 |                 |                 |

| (43) 公開日     |                                         | 平成14年11月15日(2                | 2002.11.15)   | (72) 発明者 山          |     | 山崎 舜平          |                 |                 |

| 審查請求日        |                                         | 平成20年4月21日 (20               | 008. 4. 21)   |                     | 1   | 神奈川県厚木         | 市長谷398種         | 地 株式会社          |

|              |                                         |                              |               |                     | 3   | 半導体エネル         | ギー研究所内          |                 |

|              |                                         |                              |               | (72) 発明す            | 首 / | 小山 潤           |                 |                 |

|              |                                         |                              |               |                     | 1   | 神奈川県厚木         | 市長谷398番         | 地 株式会社          |

|              |                                         |                              |               |                     | 3   | 半導体エネル         | ギー研究所内          |                 |

|              |                                         |                              |               | <br>   審査1          |     | 渡邊 吉喜          |                 |                 |

|              |                                         |                              |               |                     | י ו |                |                 |                 |

|              |                                         |                              |               |                     |     |                |                 |                 |

|              |                                         |                              |               |                     |     |                |                 |                 |

|              |                                         |                              |               |                     |     |                |                 |                 |

|              |                                         |                              |               | 最終頁に続く              |     |                |                 |                 |

## (54) 【発明の名称】表示装置

## (57)【特許請求の範囲】

## 【請求項1】

画素部、駆動回路、メモリ、及びコントロール回路が同一基板に形成された表示装置であって、

前記駆動回路と、前記メモリと、前記コントロール回路とは、第1の形状のTFTを<u>有</u>し、

前記画素部は、第2の形状のTFTを有し、

前記第1の形状のTFT及び前記第2の形状のTFTは、

第1の電極と、

前記第1の電極上に設けられた、表面が平坦化された第1の絶縁膜と、

前記第1の絶縁膜上に設けられた、第1のチャネル形成領域を有する第1の半導体膜と

前記第1の半導体膜上に設けられた、第2の絶縁膜と、

前記第2の絶縁膜上に設けられた、第2の電極と、を有し、

前記第1の電極と前記第2の電極は、前記<u>第1の</u>チャネル形成領域を間に挟んで重なり合い、

前記第1の形状のTFT<u>が有する</u>前記第1の電極と前記第2の電極とは電気的に接続され、

前記第2の形状のTFT<u>が有する</u>前記第1の電極には、一定の電圧が印加されていることを特徴とする表示装置。

#### 【請求項2】

<u>画素部、駆動回路、メモリ、及びコントロール回路が同一基板に形成された表示装置で</u>あって、

前記駆動回路と、前記メモリと、前記コントロール回路とは、第1の形状のTFTを有し、

前記画素部は、第2の形状のTFTを有し、

前記第1の形状のTFTは、

第1の電極と、

前記第1の電極上に設けられた、表面が平坦化された第1の絶縁膜と、

前記第1の絶縁膜上に設けられた、第1のチャネル形成領域を有する第1の半導体膜と

10

`

前記第1の半導体膜上に設けられた、第2の絶縁膜と、

前記第2の絶縁膜上に設けられた、第2の電極と、を有し、

前記第1の電極と前記第2の電極は、前記第1のチャネル形成領域を間に挟んで重なり 合い、

前記第1の電極と前記第2の電極とは電気的に接続され、

前記第2の形状のTFTは、

第3の電極と、

前記第3の電極上に設けられた、表面が平坦化された第3の絶縁膜と、

前記第3の絶縁膜上に設けられた、第2の半導体膜と、

前記第2の半導体膜上に設けられた、第4の絶縁膜と、

前記第4の絶縁膜上に設けられた、第4の電極及び第5の電極と、を有し、

前記第2の半導体膜は、第2のチャネル形成領域と、第3のチャネル形成領域と、第1 の不純物領域と、第2の不純物領域と、第3の不純物領域と、第4の不純物領域と、第5 の不純物領域と、第6の不純物領域と、第7の不純物領域と、を有し、

前記第2のチャネル形成領域は、前記第1の不純物領域と前記第2の不純物領域との間に設けられ、

<u>前記第3の不純物領域は、前記第2のチャネル形成領域と前記第1の不純物領域との間</u>に設けられ、

前記第4の不純物領域は、前記第2のチャネル形成領域と前記第2の不純物領域との間に設けられ、

前記第3のチャネル形成領域は、前記第1の不純物領域と前記第5の不純物領域との間 に設けられ、

前記第6の不純物領域は、前記第3のチャネル形成領域と前記第1の不純物領域との間 こ設けられ、

前記第7の不純物領域は、前記第3のチャネル形成領域と前記第5の不純物領域との間 に設けられ、

前記第1の不純物領域、前記第2の不純物領域及び前記第5の不純物領域の不純物濃度 は、前記第3の不純物領域、前記第4の不純物領域、前記第6の不純物領域及び前記第7 の不純物領域の不純物濃度よりも高く、

前記第4の電極と前記第5の電極とは電気的に接続され、

<u>前記第3の電極と前記第4の電極は、前記第2のチャネル形成領域を間に挟んで重なり</u> 合い、

前記第3の電極と前記第5の電極は、前記第3のチャネル形成領域を間に挟んで重なり合い、

前記第3の電極には、一定の電圧が印加されていることを特徴とする表示装置。

#### 【請求項3】

請求項1又は2において、

前記画素部は、前記第2の形状のTFTを有することを特徴とする表示装置。

【請求項4】

20

30

請求項1乃至3のいずれか一項において、

前記第1の形状のTFTが有する前記第1の電極の両端部は、テーパー形状であり、

前記第1の形状のTFTが有する前記第1の半導体膜は、第8の不純物領域と、第9の 不純物領域と、第10の不純物領域と、第11の不純物領域とを有し、

前記第1の形状のTFTが有する前記第1のチャネル形成領域は、前記第8の不純物領域と前記第9の不純物領域との間に設けられ、

前記第10の不純物領域は、前記第1の形状のTFTが有する前記第1のチャネル形成 領域と前記第8の不純物領域との間に設けられ、

前記第11の不純物領域は、前記第1の形状のTFTが有する前記第1のチャネル形成 領域と前記第9の不純物領域との間に設けられ、

前記第8の不純物領域及び前記第9の不純物領域の不純物濃度は、前記第10の不純物領域及び前記第11の不純物領域の不純物濃度よりも高く、

前記第1の電極の両端部はそれぞれ、前記第10の不純物領域及び前記第11の不純物領域と重なっていることを特徴とする表示装置。

### 【請求項5】

請求項1乃至4のいずれか一項において、

前記第2の形状のTFTはnチャネル型TFTであり、

前記一定の電<u>圧は</u>、前記 n チャネル型 T F T の閾値の電圧よりも低いことを特徴とする表示装置。

## 【請求項6】

請求項1乃至4のいずれか一項において、

前記第2の形状のTFTはpチャネル型TFTであり、

前記一定の電<u>圧は</u>、前記 p チャネル型 T F T の閾値の電圧よりも高いことを特徴とする表示装置。

#### 【請求項7】

請求項1乃至6のいずれか一項に記載の表示装置を用いることを特徴とする携帯情報端末、パーソナルコンピュータ、画像再生装置、テレビ、ヘッドマウントディスプレイ、又はビデオカメラ。

【発明の詳細な説明】

### [0001]

【発明の属する技術分野】

本発明は、デジタルビデオ信号を入力して、画像の表示を行う表示装置に関する。また、 表示装置を用いた電子機器に関する。

### [0002]

### 【従来の技術】

発光素子を画素毎に配置し、それらの発光素子の発光を制御することによって、画像の表示を行う表示装置について以下に説明する。

### [0003]

ここで本明細書中では、発光素子は、電界が生じると発光する有機化合物層を、陽極及び 陰極で挟んだ構造を有する素子(OLED素子)を示すものとして説明を行う。

## [0004]

また、本明細書中において、発光素子とは、一重項励起子から基底状態に遷移する際の発 光(蛍光)を利用するものと、三重項励起子から基底状態に遷移する際の発光(燐光)を 利用するものの両方を示す。

### [00005]

有機化合物層としては、正孔注入層、正孔輸送層、発光層、電子輸送層、電子注入層等が 挙げられる。発光素子は、基本的に、陽極/発光層/陰極の順に積み重ねた構造で示され るが、この他に、陽極/正孔注入層/発光層/電子注入層/陰極の順に積み重ねた構造や 、陽極/正孔注入層/正孔輸送層/発光層/電子輸送層/電子注入層/陰極の順に積み重 ねた構造などがある。 10

20

30

40

[00006]

表示装置は、ディスプレイと、ディスプレイに信号を入力する周辺回路によって構成されている。

[0007]

ディスプレイは、ソース信号線駆動回路と、ゲート信号線駆動回路と、画素部とによって 構成されている。画素部は、マトリクス状に画素が配置された構成なっている。

[0008]

各画素に、薄膜トランジスタ(以下、Thin Film Transistor: TFTと表記する)を配置し、これらのTFTによって各画素の発光素子の発光を制御して表示を行う表示装置(アクティブマトリクス型表示装置)について説明する。ここでは、画素毎に2つのTFTを配置し、各画素の発光素子の発光を制御する手法について説明する。

10

[0009]

図21(A)に、表示装置の画素部の構成を示す。

[0010]

画素部 700 には、ソース信号線  $S1\sim Su$ 、ゲート信号線  $G1\sim Gv$ 、電源供給線  $V1\sim Vu$  が配置され、u(uは自然数) 列 v(vは自然数) 行の画素が配置されている。各画素 800は、スイッチング用 TFT801と、駆動用 TFT802と、保持容量 803と、発光素子 804をそれぞれ有している。

[0011]

図 2 1 ( B ) に、図 2 1 ( A ) で示した画素部の 1 つの画素を拡大して示す。

20

[0012]

画素は、ソース信号線S1~Suのうちの1本Sと、ゲート信号線G1~Gvのうちの1本Gと、電源供給線V1~Vuのうちの1本Vと、スイッチング用TFT801と、駆動用TFT802と、保持容量803と、発光素子804とによって構成されている。

[0013]

スイッチング用TFT801のゲート電極は、ゲート信号線Gに接続され、スイッチング用TFT801のソース領域とドレイン領域は、一方はソース信号線Sに接続され、もう一方は、駆動用TFT802のゲート電極もしくは、保持容量803の一方の電極に接続されている。駆動用TFT802のソース領域とドレイン領域は、一方は、電源供給線Vに接続され、もう一方は、発光素子804の陽極もしくは陰極に接続されている。保持容量803の2つの電極のうち、駆動用TFT802及びスイッチング用TFT801に接続されていない側は、電源供給線Vに接続されている。

30

[0014]

ここで本明細書中では、駆動用TFT802のソース領域もしくはドレイン領域が、発光素子804の陽極と接続されている場合、発光素子804の陽極を画素電極と呼び、陰極を対向電極と呼ぶ。一方、駆動用TFT802のソース領域もしくはドレイン領域が、発光素子804の陰極と接続されている場合、発光素子804の陰極を画素電極と呼び、陽極を対向電極と呼ぶ。

[0015]

また、電源供給線 V に与えられる電位を電源電位といい、対向電極に与えられる電位を対 40 向電位と呼ぶことにする。

[0016]

スイッチング用TFT801及び駆動用TFT802は、pチャネル型TFTでもnチャネル型TFTでも構わないが、発光素子804の画素電極が陽極の場合、駆動用TFT802は、pチャネル型TFTが望ましく、スイッチング用TFT801は、nチャネル型TFTが望ましい。一方、画素電極が、陰極の場合、駆動用TFT802は、nチャネル型TFTが望ましく、スイッチング用TFT801は、pチャネル型TFTが望ましい。

[0017]

なお、保持容量803は、必ずしも設ける必要はない。

[0018]

例えば、駆動用TFT802として用いるnチャネル型TFTが、ゲート絶縁膜を介してゲート電極に重なるように設けられたLDD領域を有している場合、この重なり合った領域には一般的にゲート容量と呼ばれる寄生容量が形成されるが、この寄生容量を、駆動用TFT802のゲート電極にかかる電圧を保持するための保持容量として積極的に用いることも可能である。

#### [0019]

上記構成の画素において、画像を表示する際の動作を以下に説明する。

#### [0020]

ゲート信号線 G に信号が入力されて、スイッチング用TFT801のゲート電極の電位が変化し、ゲート電圧が変化する。こうして導通状態となったスイッチング用TFT801のソース・ドレイン間を介して、ソース信号線 S より駆動用TFT802のゲート電極に信号が入力される。また、保持容量803に信号が保持される。駆動用TFT802のゲート電極に入力された信号によって、駆動用TFT802のゲート電圧が変化し、ソース・ドレイン間が導通状態となる。電源供給線 V の電位が、駆動用TFT802を介して、発光素子804の画素電極に与えられる。こうして、発光素子804は発光する。

#### [0021]

このような構成の画素において、階調を表現する手法について説明する。

#### [0022]

階調の表現の方法には、大きくわけて、アナログ方式とデジタル方式とがある。アナログ方式と比べて、デジタル方式は、多階調化に向くなどの利点がある。

#### [0023]

ここでは、デジタル方式の階調表現方法に注目する。

#### [0024]

デジタル方式の階調表現方法として、時間階調方式が挙げられる。

#### [0025]

時間階調方式の駆動方式について、以下に詳しく説明する。

#### [0026]

この方式の駆動方法では、表示装置の各画素が発光する期間を制御することによって、階調を表現する手法である。

### [0027]

1 画像を表示する期間を 1 フレーム期間とすると、 1 フレーム期間は、複数のサブフレーム期間に分割される。

#### [0028]

サブフレーム期間毎に、点灯もしくは非点灯とし、つまり、各画素の発光素子を発光させるかさせないして、1フレーム期間あたりに発光素子が発光する期間を制御し、各画素の階調が表現される。

### [0029]

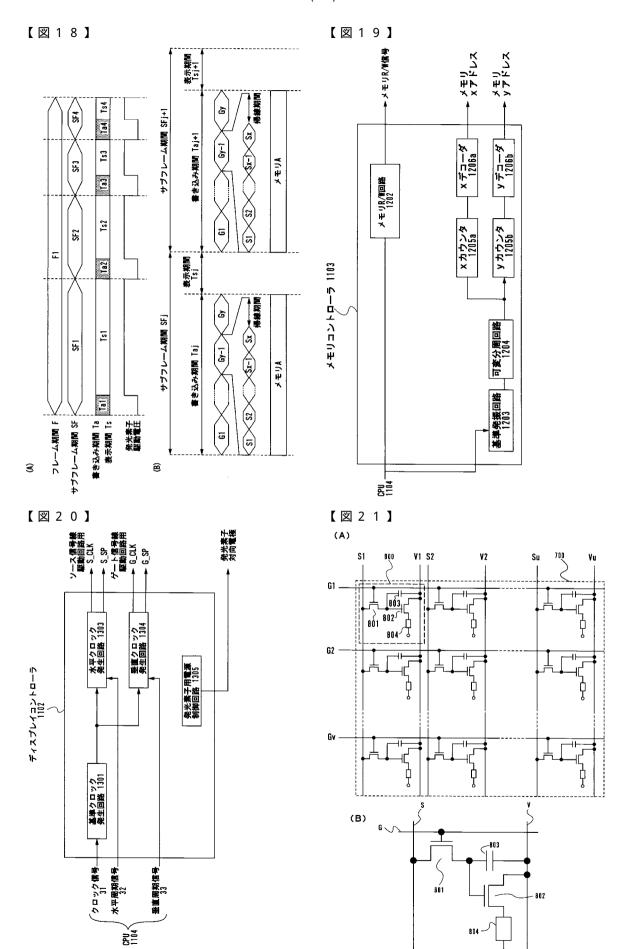

この時間階調方式の駆動方法について、図18のタイミングチャートを用いて詳しく説明 する。

### [0030]

なお、図18においては、4ビットのデジタル映像信号を用いて階調を表現する場合の例を示す。

### [0031]

なお、画素及び画素部の構成としては、図 2 1 (A)及び図 2 1 (B)に示したものを参照する。

## [0032]

ここで、対向電位は、外部電源(図示せず)によって、電源供給線 V 1 ~ V u の電位(電源電位)と同じ程度の電位か、電源供給線 V 1 ~ V u の電位との間に、発光素子 8 0 4 が発光する程度の電位差を有するように切り換えることができる。

## [0033]

50

10

20

30

1フレーム期間Fは、複数のサブフレーム期間SF1~SF4に分割される。

### [0034]

第1のサブフレーム期間SF1において、はじめにゲート信号線G1が選択され、ゲート信号線G1にゲート電極が接続されたスイッチング用TFT801を有する画素においてそれぞれ、ソース信号線S1~Suからデジタル映像信号が入力される。この入力されたデジタル映像信号によって、各画素の駆動用TFT802は、オンの状態もしくはオフの状態となる。

### [0035]

ここで本明細書中では、TFTがオンの状態とは、そのゲート電圧によって、ソース・ドレイン間が導通状態であることを示すとする。また、TFTがオフの状態とは、そのゲート電圧によって、ソース・ドレイン間が、非道通状態であることを示すとする。

10

#### [0036]

このとき、発光素子804の対向電位は、電源供給線V1~Vuの電位(電源電位)とほぼ等しく設定されているので、駆動用TFT802がオンの状態となった画素においても発光素子804は発光しない。

#### [0037]

全てのゲート信号線 G 1 ~ G v について以上の動作を繰り返し、書き込み期間 T a 1 が終了する。

### [0038]

なお、第1のサブフレーム期間SF1の書き込み期間をTa1と呼ぶ。一般に第 j ( j は 自然数 ) のサブフレーム期間の書き込み期間をTa j と呼ぶことにする。

20

#### [ 0 0 3 9 ]

書き込み期間Ta1が終了すると対向電位が、電源電位との間に発光素子804が発光する程度の電位差を有するように変化する。こうして表示期間Ts1が始まる。

#### [0040]

なお、第1のサブフレーム期間 S F 1 の表示期間を T s 1 と呼ぶ。一般に第 j ( j は自然数 ) のサブフレーム期間の表示期間を T s j と呼ぶことにする。

#### [0041]

表示期間 T s 1 において、各画素の発光素子 8 0 4 は、入力された信号に応じて、発光もしくは非発光の状態となる。

30

## [0042]

上記動作を全てのサブフレーム期間 SF1~SF4について繰り返し、1フレーム期間 F1が終了する。

#### [0043]

ここで、サブフレーム期間SF1~SF4の表示期間Ts1~Ts4の長さを適宜設定し、1フレーム期間Fあたりで、発光素子804が発光したサブフレーム期間の表示期間の累計によって階調を表現する。つまり、1フレーム期間中の点灯時間の総和をもって階調を表現する。

### [0044]

一般に、nビットのデジタルビデオ信号を入力して、2 <sup>n</sup>階調を表現する手法について説明する。

[0045]

#### [0046]

1フレーム期間中に発光素子804において、発光状態が選択された表示期間Tsの総和を求めることによって、そのフレーム期間におけるその画素の階調が決まる。例えば、n=8のとき、全部の表示期間で画素が発光した場合の輝度を100%とすると、Ts8と

50

Ts 7 において画素が発光した場合には 1 %の輝度が表現でき、Ts 6 とTs 4 とTs 1 を選択した場合には 6 0 %の輝度が表現できる。

#### [0047]

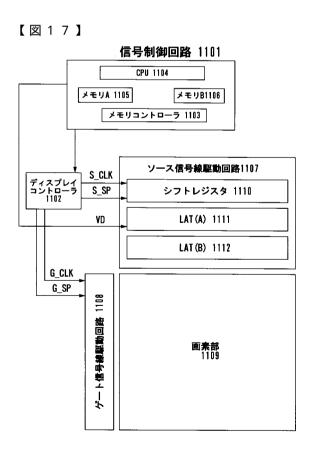

上記の時間階調方式の駆動方法を行うための信号を、ディスプレイのソース信号線駆動回路及びゲート信号線駆動回路に入力する回路について、図17を用いて説明する。

#### [0048]

本明細書中では、表示装置に入力される信号を、デジタルビデオ信号と呼ぶことにする。 なおここでは、 n ビットのデジタルビデオ信号を入力して、画像を表示する表示装置を例 に説明する。

#### [0049]

信号制御回路1101にデジタルビデオ信号が読み込まれ、ディスプレイ1100にデジタル映像信号(VD)を出力する。

#### [0050]

また、本明細書中では、信号制御回路においてデジタルビデオ信号(第1の映像信号)を編集し、ディスプレイに入力する信号に変換したものを、デジタル映像信号(第2の映像信号)と呼ぶ。

### [0051]

ディスプレイ1100の、ソース信号線駆動回路1107及びゲート信号線駆動回路11 08を駆動するための信号は、ディスプレイコントローラ1102によって入力されている。

#### [0052]

信号制御回路1101及びディスプレイコントローラ1102の構成について説明する。

#### [0053]

なお、ディスプレイ1100のソース信号線駆動回路1107は、シフトレジスタ111 0、LAT(A)1111、LAT(B)1112によって構成される。他に、図示して いないが、レベルシフタやバッファ等を設けてもよい。

#### [0054]

信号制御回路 1 1 0 1 は、C P U 1 1 0 4、メモリ A 1 1 0 5、メモリ B 1 1 1 2 及びメ モリコントローラ 1 1 0 3 によって構成されている。

### [0055]

信号制御回路1101に入力されたデジタルビデオ信号は、CPU1104を介してメモリA1105に入力される。ここで、メモリA1105は、ディスプレイ1100の画素部1109の全画素分のnビットのデジタルビデオ信号を、記憶可能な容量を有する。メモリA1105に1フレーム期間分の信号が記憶されると、メモリコントローラ1103によって、各ビットの信号が順に読み出され、デジタル映像信号VDとして、ソース信号線駆動回路に入力される。

## [0056]

メモリA1105に記憶された信号の読み出しが始まると、今度は、メモリB1106に СРU1104を介して次のフレーム期間に対応するデジタルビデオ信号が入力され、記憶され始める。メモリB1106もメモリA1105と同様に、表示装置の全画素分の n ビットのデジタルビデオ信号を記憶可能な容量を有するとする。

#### [0057]

このように、信号制御回路1101は、それぞれ1フレーム期間分ずつの n ビットのデジタルビデオ信号を記憶することができるメモリA1105及びメモリB1106を有し、このメモリA1105とメモリB1106とを交互に用いて、デジタルビデオ信号をサンプリングする。

### [0058]

ここでは、2つのメモリA1105及びメモリB1106を、交互に用いて信号を記憶する信号制御回路1101について示したが、一般に、複数フレーム分の情報を記憶することができるメモリを有し、これらのメモリを交互に用いることができる。

10

20

30

40

#### [0059]

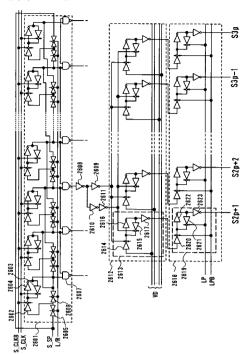

信号制御回路 1 1 0 1 のメモリ A 1 1 0 5 及びメモリ B 1 1 0 6 において、デジタルビデオ信号の入力及び出力を制御するメモリコントローラ 1 1 0 3 の構成について、図 1 9 を用いて説明する。

[0060]

図19において、メモリコントローラ1103は、メモリ読み書きコントロール(以下、メモリR/Wと表記)回路1202、基準発振回路1203、可変分周回路1204、×カウンタ1205a、yカウンタ1205b、xデコーダ1206a及びyデコーダ1206bによって構成されている。

[0061]

以下、上述した信号制御回路が有するメモリA及びメモリBのメモリの両方をまとめて、 メモリと表記する。また、メモリはマトリクス状に配置された複数の記憶素子によって構 成され、それらの記憶素子は、(×、y)のアドレスによって選択されるものとする。

[0062]

CPU11104からの信号は、基準発振回路1203に入力される。基準発振回路1203からの信号は、可変分周回路1204に入力され、適当な周波数の信号に変換される。可変分周回路1204からの信号は、メカウンタ1205a及びメデコーダ1206aを介してメモリの×アドレスを選択する。同様に、可変分周回路1204からの信号は、メカウンタ1205b及びソデコーダ1206bに入力され、メモリソアドレスを選択する。こうしてメモリのアドレス(x、y)が選択される。また、CPU1104からの信号が、メモリR/w回路1202に入力され、メモリに信号を書き込む操作、もしくはメモリから信号を読み出す操作を選択するメモリR/w信号が出力される。

[0063]

こうして、メモリ×アドレス及びメモリッアドレスによって、デジタルビデオ信号を書き込みや読み出しをする際のメモリのアドレスを選択し、このアドレスによって選択された記憶素子において、メモリR/W信号によって、デジタルビデオ信号の書き込みや読み出しの操作が行われる。

[0064]

また、ディスプレイコントローラ1102の構成について、以下に説明する。

[0065]

デスプレイコントローラ 1 1 0 2 は、ソース信号線駆動回路及びゲート信号線駆動回路に、スタートパルスやクロックパルス等の信号を出力している。

[0066]

ディスプレイコントローラ1102の構成について、図20を用いて説明する。

[0067]

ディスプレイコントローラ 1 1 0 2 は、基準クロック発生回路 1 3 0 1、水平クロック発生回路 1 3 0 3、垂直クロック発生回路 1 3 0 4 及び発光素子用電源制御回路 1 3 0 5 によって構成されている。

[0068]

CPU1104から入力されるクロック信号31は、基準クロック発生回路1301に入力され、基準クロックを発生する。この基準クロックは、水平クロック発生回路1303 及び垂直クロック発生回路1304に入力される。また、水平クロック発生回路1303 には、CPU1104から水平周期を定める水平周期信号32が入力され、ソース信号線 駆動回路用のクロックパルスS\_CLK及びスタートパルスS\_SPを出力する。同様に、垂直クロック発生回路1304には、CPUから垂直周期を定める垂直周期信号33が入力され、ゲート信号線駆動回路用のクロックパルスG\_CLK及びスタートパルスG\_SPを出力する。

[0069]

再び図17を参照する。

[0070]

10

20

30

40

ディスプレイコントローラ 1 1 0 2 から出力されたソース信号線駆動回路用スタートパルス S \_ S P 及びクロックパルス S \_ C L K は、ディスプレイのソース信号線駆動回路のシフトレジスタに入力され、ゲート信号線駆動回路用スタートパルス G \_ S P、クロックパルス G \_ C L K は、ディスプレイのゲート信号線駆動回路に入力される。

### [0071]

ここで、ディスプレイコントローラ 1 1 0 2 において、発光素子用電源制御回路 1 3 0 5 は、ディスプレイの各画素の発光素子の対向電極の電位が、書き込み期間中は、電源電位と同じ電位に保たれ、また表示期間においては、電源電位との間に、発光素子が発光する程度の電位差を有するように変化するよう制御している。

### [0072]

ここで、ディスプレイを構成する各駆動回路(ソース信号線駆動回路及びゲート信号線駆動回路)は、IC基板等の別基板上に形成され、画素が形成された基板(画素基板)上に貼り付けられて、表示装置に組み込まれるこたが一般的であった。貼り付けの手法としては、TAB(Tape automated bonding)等がある。

#### [0073]

しかし上記の用に、駆動回路を表示装置に組み込む場合、その接続部分の配線抵抗や、接 続不良の問題、及び画素部の周辺部分の領域(額縁領域)の増加等が問題となっていた。

#### [0074]

そこで、これらの駆動回路を、画素基板上にTFTを用いて形成する手法が提案された。

### [0075]

一般に、アクティブマトリクス型表示装置の画素を構成するTFTとして非晶質半導体薄膜を用いたTFT(以下、a.TFTと表記する)が用いられてきた。ここで、a.TFTでは、その電界効果移動度が小さいなどの問題がある。そのため、a.TFTを用いた駆動回路では、その周波数特性を良くすることができないといった問題がある。

#### [0076]

そこで、画素部及び駆動回路を構成するTFTを、多結晶半導体薄膜を用いたTFT(以下、p-TFTと表記する)とする構成の表示装置が提案された。p-TFTでは、a-TFTと比較して、電界効果移動度が大きい。こうして、画素部及び各駆動回路を同一基板(以下、ディスプレイ基板と表記する)上に形成した表示装置が提案されている。

## [0077]

### 【発明が解決しようとする課題】

表示装置を構成する、メモリと、メモリコントローラ及びディスプレイコントローラ等(以下、コントロール回路と表記する)は、IC基板等の別基板上に形成され、画素や駆動回路が形成されたディスプレイ基板上に接続されていた。

## [0078]

しかし、これらのメモリ及びコントロール回路をディスプレイ基板上に接続する際、その接続部分の配線容量が問題となる。デジスプレイ基板上に形成された各駆動回路及び画素部と、外付けされたメモリ及びコントロール回路の接続部分の配線容量が大きくなるため、表示装置全体の消費電力を小さくすることができない。

### [0079]

## 【課題を解決するための手段】

画素部及び各駆動回路が形成されたディスプレイ基板と同一の基板上に、メモリ及びコントロール回路を形成する。

## [0800]

これによって、メモリ及びコントロール回路と、ディスプレイの各駆動回路との間の配線 容量を低減することができる。また、表示装置を小型化することができる。

#### [0081]

以下に、本発明の構成について記載する。

### [0082]

本発明によって、

20

10

30

40

ディスプレイと、映像信号を前記ディスプレイに出力する信号制御回路とを有する表示装 置において、

前記信号制御回路は、TFTを用いて、前記ディスプレイと一体形成されることを特徴と する表示装置が提供される。

[0083]

本発明によって、

ディスプレイと、前記ディスプレイに出力する映像信号を記憶するメモリとを有する表示 装置において、

前記メモリは、TFTを用いて、前記ディスプレイと一体形成されることを特徴とする表 示装置が提供される。

10

[0084]

本発明によって、

ディスプレイと、前記ディスプレイに映像信号を出力する信号制御回路とを有し、

前記ディスプレイは、複数の画素と、前記複数の画素を駆動する駆動回路とを有する表示 装置において、

前記駆動回路と、前記信号制御回路とは、TFTを用いて、一体形成されることを特徴と する表示装置が提供される。

[0085]

本発明によって、

ディスプレイと、前記ディスプレイに出力する映像信号を記憶するメモリと、前記メモリ への前記映像信号の書き込み及び読み出しを制御するメモリコントローラとを有する表示

20

前記ディスプレイと、前記メモリ、前記メモリコントローラとは、TFTを用いて、一体 形成されることを特徴とする表示装置が提供される。

[0086]

本発明によって、

ディスプレイと、前記ディスプレイに出力する映像信号を記憶するメモリと、前記メモリ への前記映像信号の書き込み及び読み出しを制御するメモリコントローラとを有する表示 装置において、

前記ディスプレイと、前記メモリコントローラとは、TFTを用いて、一体形成されるこ とを特徴とする表示装置が提供される。

30

[0087]

本発明によって、

ディスプレイと、ディスプレイコントローラとを有し、

前記ディスプレイは、複数の画素と、前記複数の画素を駆動する駆動回路とを有し、

前記ディスプレイコントローラからの信号を、前記駆動回路に入力する表示装置において

前記駆動回路と、前記ディスプレイコントローラとは、TFTを用いて一体形成されるこ とを特徴とする表示装置が提供される。

[0088]

40

前記TFTは、第1の電極と、第1の絶縁膜と、半導体膜と、第2の絶縁膜と、第2の電

前記半導体膜は、チャネル形成領域を有し、

前記第1の絶縁膜は、前記第1の電極に接して形成され、

前記半導体膜は、前記第1の絶縁膜に接して形成され、

前記第2の絶縁膜は、前記半導体膜に接して形成され、

前記第2の電極は、前記第2の絶縁膜に接して形成され、

前記第1の電極と前記第2の電極は、前記チャネル形成領域を間に挟んで重なり合ってい ることを特徴とする表示装置であってもよい。

[0089]

#### 本発明によって、

ディスプレイと、前記ディスプレイに映像信号を出力する信号制御回路とを有し、

前記ディスプレイは、複数の画素と、前記複数の画素を駆動する駆動回路とを有する表示 装置において、

前記駆動回路と、前記信号制御回路とは、第1の形状のTFTを用いて形成され、

前記複数の画素は、第2の形状のTFTを用いて形成され、

前記第1の形状のTFT及び第2の形状のTFTは、第1の電極と、第1の絶縁膜と、半導体膜と、第2の絶縁膜と、第2の電極とを有し、

前記半導体膜は、チャネル形成領域を有し、

前記第1の絶縁膜は、前記第1の電極に接して形成され、

前記半導体膜は、前記第1の絶縁膜に接して形成され、

前記第2の絶縁膜は、前記半導体膜に接して形成され、

前記第2の電極は、前記第2の絶縁膜に接して形成され、

前記第1の電極と前記第2の電極は、前記チャネル形成領域を間に挟んで重なり合い、

前記第1の形状のTFTの、前記第1の電極と前記第2の電極とは接続され、

前記第2の形状のTFTの、前記第1の電極には、一定の電圧が印加されていることを特徴とする表示装置が提供される。

#### [0090]

本発明によって、

ディスプレイと、前記ディスプレイに出力する映像信号を記憶するメモリとを有し、 前記ディスプレイは、複数の画素と、前記複数の画素を駆動する駆動回路とを有する表示 装置において、

前記駆動回路と、前記メモリとは、第1の形状のTFTを用いて形成され、

前記複数の画素は、第2の形状のTFTを用いて形成され、

前記第1の形状のTFT及び第2の形状のTFTは、第1の電極と、第1の絶縁膜と、半導体膜と、第2の絶縁膜と、第2の電極とを有し、

前記半導体膜は、チャネル形成領域を有し、

前記第1の絶縁膜は、前記第1の電極に接して形成され、

前記半導体膜は、前記第1の絶縁膜に接して形成され、

前記第2の絶縁膜は、前記半導体膜に接して形成され、

前記第2の電極は、前記第2の絶縁膜に接して形成され、

前記第1の電極と前記第2の電極は、前記チャネル形成領域を間に挟んで重なり合い、

前記第1の形状のTFTの、前記第1の電極と前記第2の電極とは接続され、

前記第2の形状のTFTの、前記第1の電極には、一定の電圧が印加されていることを特徴とする表示装置が提供される。

### [0091]

本発明によって、

ディスプレイと、前記ディスプレイに映像信号を出力する信号制御回路とを有し、

前記ディスプレイは、複数の画素と、前記複数の画素を駆動する駆動回路とを有する表示 装置において、

前記駆動回路と、前記信号制御回路とは、第1の形状のTFTを用いて形成され、

前記複数の画素は、第1の形状のTFTと、第2の形状のTFTとを用いて形成され、

前記第1の形状のTFT及び第2の形状のTFTは、第1の電極と、第1の絶縁膜と、半 導体膜と、第2の絶縁膜と、第2の電極とを有し、

前記半導体膜は、チャネル形成領域を有し、

前記第1の絶縁膜は、前記第1の電極に接して形成され、

前記半導体膜は、前記第1の絶縁膜に接して形成され、

前記第2の絶縁膜は、前記半導体膜に接して形成され、

前記第2の電極は、前記第2の絶縁膜に接して形成され、

前記第1の電極と前記第2の電極は、前記チャネル形成領域を間に挟んで重なり合い、

10

20

30

40

前記第1の形状のTFTの、前記第1の電極と前記第2の電極とは接続され、

前記第2の形状のTFTの、前記第1の電極には、一定の電圧が印加されていることを特徴とする表示装置が提供される。

### [0092]

本発明によって、

ディスプレイと、前記ディスプレイに出力する映像信号を記憶するメモリとを有し、

前記ディスプレイは、複数の画素と、前記複数の画素を駆動する駆動回路とを有する表示 装置において、

前記駆動回路と、前記メモリとは、第1の形状のTFTを用いて形成され、

前記複数の画素は、第1の形状のTFTと、第2の形状のTFTとを用いて形成され、

前記第1の形状のTFT及び第2の形状のTFTは、第1の電極と、第1の絶縁膜と、半 導体膜と、第2の絶縁膜と、第2の電極とを有し、

前記半導体膜は、チャネル形成領域を有し、

前記第1の絶縁膜は、前記第1の電極に接して形成され、

前記半導体膜は、前記第1の絶縁膜に接して形成され、

前記第2の絶縁膜は、前記半導体膜に接して形成され、

前記第2の電極は、前記第2の絶縁膜に接して形成され、

前記第1の電極と前記第2の電極は、前記チャネル形成領域を間に挟んで重なり合い、

前記第1の形状のTFTの、前記第1の電極と前記第2の電極とは接続され、

前記第2の形状のTFTの、前記第1の電極には、一定の電圧が印加されていることを特徴とする表示装置が提供される。

#### [0093]

前記半導体膜は、前記チャネル形成領域を間に挟んで形成された不純物領域を有していることを特徴とする表示装置であってもよい。

#### [0094]

本発明によって、

画素を有する表示装置において、

前記画素は、TFTを有し、

前記TFTは、第1の電極と、第1の絶縁膜と、半導体膜と、第2の絶縁膜と、第2の電極と、第3の電極とを有し、

前記第1の絶縁膜は、前記第1の電極に接して形成され、

前記半導体膜は、前記第1の絶縁膜に接して形成され、

前記第2の絶縁膜は、前記半導体膜に接して形成され、

前記第2の電極及び第3の電極は、前記第2の絶縁膜に接して形成され、

前記半導体膜は、第1のチャネル形成領域と第2のチャネル形成領域と、前記第1のチャネル形成領域と前記第2のチャネル形成領域に挟まれる不純物領域を有し、

前記第2の電極と前記第3の電極とは、前記半導体膜の外側において接続され、

前記第1の電極と前記第2の電極は、前記第1のチャネル領域を間に挟んで重なり合い、

前記第1の電極と前記第3の電極は、前記第2のチャネル領域を間に挟んで重なり合い、

前記第1の電極には、一定の電圧が印加され、

前記不純物領域と、前記第1の電極とは、前記第1の絶縁膜を間に挟んで重なっていることを特徴とする表示装置が提供される。

#### [0095]

前記第2の形状のTFTがnチャネル型TFTのとき、前記一定の電圧とは、前記nチャネル型TFTの閾値の電圧よりも低いことを特徴とする表示装置であってもよい。

## [0096]

前記第2の形状のTFTがpチャネル型TFTのとき、前記一定の電圧とは、前記nチャネル型TFTの閾値の電圧よりも高いことを特徴とする表示装置であってもよい。

### [0097]

前記表示装置を用いることを特徴とするビデオカメラ、DVD再生装置、テレビ受像機、

10

20

30

00

40

ヘッドマウントディスプレイ、携帯情報端末、パーソナルコンピュータであってもよい。

### [0098]

#### 【発明の実施の形態】

本発明の実施の形態について説明する。

### [0099]

画素部が形成された基板と同じ基板上に形成する場合、メモリ及びコントロール回路は、TFTを用いて形成する必要がある。ここで、p-TFTはa-TFTより電気的特性がよいといっても、単結晶シリコン基板上に形成されるMOSトランジスタの特性には劣るといった問題がある。たとえば、電界効果移動度は、単結晶シリコンを用いたMOSトランジスタの1/2以下である。また、p-TFTでは、結晶粒界の欠陥に起因してオフ電流が高くなってしまう。

10

### [ 0 1 0 0 ]

TFTのオフ電流を低減する構成として、低濃度ドレイン(LDD:Light Doped Drain)構造が知られている。この構造は、チャネル形成領域と、高濃度に不純物を添加して形成するソース領域或いはドレイン領域との間に、低濃度に不純物とドープした領域(LDD領域)を設けた構造である。また、ホットキャリアによるオン電流の劣化を防ぐ構成として、LDD領域の一部がゲート電極と重なった構造(以下、Gate-drain Overlapped LDD:GOLDと呼ぶ)が知られている。

### [0101]

上記構造を採用し、回路を構成するTFTを、その動作に応じて作り分ける。それによって、信頼性の高い動作を行う表示装置が提供される。しかし、この際、TFTを作製するプロセスが複雑になり、工程において用いるフォトマスクの枚数が多くなってしまうといった問題点がある。

20

#### [0102]

そこで、表示装置を構成する各回路を同一基板上に形成する際、画素部、駆動回路、メモリ及びコントロール回路それぞれの駆動条件に最適な構造のTFTを、その作製プロセスに用いるフォトマスクの枚数を抑えて、作製した表示装置について以下に説明する。

#### [0103]

本発明の表示装置が有するTFTは、半導体膜と、第1の電極と、半導体膜と第1の電極の間に挟まれた第1の絶縁膜とを有しており、さらに、第2の電極と、半導体膜と第2の電極の間に挟まれた第2の絶縁膜とを有している。そして、第1の電極と第2の電極は、半導体膜が有するチャネル形成領域を間に挟んで重なっている。

30

#### [0104]

そして、本発明では、オン電流の増加よりもオフ電流の低減が重要視されるTFT、例えば表示装置の画素部にスイッチング素子として形成されたスイッチング用TFTの場合、第1の電極に常に一定の電圧(コモン電圧)を印加する。なお、この一定の電圧は、nチャネル型TFTの場合は閾値よりも小さく、pチャネル型TFTの場合は閾値よりも大きくする。

### [0105]

第1の電極にコモン電圧を印加することで、電極が1つの場合に比べて閾値のばらつきを 抑えることができ、なおかつオフ電流を抑えることができる。

[0106]

また、本発明では、オフ電流の低減よりもオン電流の増加が重要視されるTFT、例えば表示装置のメモリ部分を構成するTFTや、各駆動回路やコントロール回路のバッファ等が有するTFTの場合、第1の電極と第2の電極に同じ電圧を印加する。

## [0107]

第 1 の電極と第 2 の電極に同じ電圧を印加することで、実質的に半導体膜の膜厚を薄くしたのと同じように空乏層が早く広がるので、サブスレッショルド係数( S 値)を小さくすることができ、さらに電界効果移動度を向上させることができる。したがって、電極が 1 つの場合に比べてオン電流を大きくすることができる。よって、この構造のTFTを駆動

50

回路に使用することにより、駆動電圧を低下させることができる。また、オン電流を大きくすることができるので、TFTのサイズ(特にチャネル幅)を小さくすることができる。そのため集積密度を向上させることができる。

#### [0108]

図15を用いて、本発明のTFTの回路図について説明する。ここでは代表的に、pチャネル型TFTのみ示す。nチャネル型TFTの場合は、矢印の方向が、pチャネル型TFTの場合と逆になる。図15(A)は、電極301が1つのみの一般的なTFTの回路図である。図15(B)は、半導体膜を間に挟んだ2つの電極(第1の電極302aと第2の電極302b)を有し、なおかつ一方の電極に一定の電圧(ここではグラウンドの電圧)が印加されている、本発明のTFT(第2の形状のTFT)の回路図である。図15(C)は、半導体膜を間に挟んだ2つの電極(第1の電極304aと第2の電極304b)を有し、なおかつ2つの電極が互いに電気的に接続されている、本発明のTFT(第1の形状のTFT)の回路図である。以下、本発明の説明において、図15に示した回路図を用いる。

#### [0109]

本発明の表示装置では、ディスプレイを構成する画素部を図15(B)で示した構成のTFTによって形成し、各駆動回路、メモリ、メモリコントローラ及びディスプレイコントローラを図15(C)に示した構成のTFTによって形成する。

#### [0110]

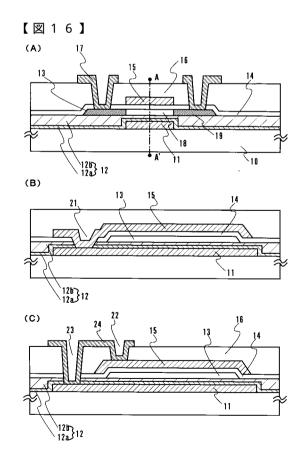

これらの構成のTFTを実際に作製した例について図16を参照して説明する。

#### [0111]

図16(A)において絶縁表面を有する基板10上に第1の電極11が形成されている。第1の電極11は導電性を有する物質で形成されていれば良い。代表的には、アルミニウム(Al)、タングステン(W)、モリブデン(Mo)、タンタル(Ta)、チタン(Ti)から選ばれた一種または複数種からなる合金又は化合物で形成することができる。また何層かの導電性の膜を積層したものを、第1の電極として用いても良い。第1の電極11は、150~400mmの厚さを有している。

#### [0112]

この第1の電極11を覆って、第1の絶縁膜12を形成する。なお本実施の形態では、2層の絶縁膜(第1の絶縁膜A 12a、第1の絶縁膜B 12b)を積層したものを、第1の絶縁膜12として用いている。図16では、第1の絶縁膜A 12aとして、酸化窒化シリコン膜又は窒化シリコン膜で10~50nmの厚さで形成する。第1の絶縁膜B 12bは酸化窒化シリコン膜又は酸化シリコン膜を用い、0.5~1μmの厚さで形成する。酸化窒化シリコン膜を用いる場合にはプラズマCVD法でSiH $_4$ 、NH $_3$ 、N $_2$ Оの混合ガスから作製され、膜中に窒素が20~40原子%含まれる膜を適用する。この酸化窒化シリコン膜、窒化シリコン膜等の窒素含有の絶縁膜を用いることにより、基板10側からアルカリ金属などの不純物の拡散を防止することが出来る。

### [0113]

第1の絶縁膜12の表面は、先に形成した第1の電極11に起因する凹凸を有していることがある。この凹凸は表面を研磨することにより平坦化する。平坦化の手法としては化学的機械研磨(Chemical -Mechanical Polishing:以下、CMPと表記する)が挙げられる。第1の絶縁膜12に対するCMPの研磨剤(スラリー)には、例えば、塩化シリコンガスを熱分解して得られるフュームドシリカ粒子をKOH添加水溶液に分散したものを用いると良い。CMPにより第1の絶縁膜を0.1~0.5μm程度除去して、表面を平坦化する。なお、第1の絶縁膜の表面は必ずしも研磨する必要はない。前記平坦化された第1の絶縁膜は、表面における凹凸の高低差が5nm以下であることが好ましく、より望ましくは、1nm以下であるのが良い。平坦性が向上したことによって、後に形成されるゲート絶縁膜として用いる第1の絶縁膜を薄くすることが可能となり、TFTの移動度を向上させることができる。また、平坦性が向上したことによって、TFTを作製した場合、オフ電流を低減することができる。

10

20

30

40

#### [0114]

表面が平坦化された第1の絶縁膜12上に半導体膜13が形成されている。半導体膜13は、チャネル形成領域18と、チャネル形成領域18を挟んでいる不純物領域19とを有している。そして、半導体膜13上には第2の絶縁膜14が形成され、さらに第2の絶縁膜14を間に挟んで、半導体膜13上に第2の電極15が形成されている。

#### [0115]

第1の電極11と第2の電極15とは、チャネル形成領域18を間に挟んで、互いに重なり合っている。

### [0116]

その他、第3の絶縁膜16、配線17は必要に応じて設ける。

[0117]

第1の電極11と第2の電極15とは、電気的に接続されていても良いし、どちらか一方の電極にコモン電圧を印加していても良い。

[0118]

図 1 6 ( A ) において、第 1 の電極 1 1 と第 2 の電極 1 5 とが直接接続されている場合の、A - A ' の断面図を図 1 6 ( B ) に示す。

[0119]

図16(B)に示すように、第1の電極11と第2の電極15は半導体膜13の外側で、 第1の絶縁膜12及び第2の絶縁膜14に形成されたコンタクトホール21において接続 されている。

[0120]

図16(A)において第1の電極11と第2の電極15とが、配線17と同じ導電膜から 形成された配線24によって接続されている場合の、A-A'の断面図を図16(C)に 示す。

[0121]

図16(C)に示すように、第1の電極11と配線24とが、第1の絶縁膜12、第2の 絶縁膜14及び第3の絶縁膜16に形成されたコンタクトホール23において接続されて いる。また、第2の電極15と配線24とが、第3の絶縁膜16に形成されたコンタクト ホール22において接続されている。

[0122]

なお、第1の電極11と第2の電極15の電気的な接続の仕方は、図16(B)、図16 (C)に示した構成に限定されない。

[0123]

CMPにより除去する膜厚は、第1の絶縁膜12の厚さやその誘電率及び第2の絶縁膜14の厚さを考慮して決める。ここに残存する膜は、実質的にゲート絶縁膜として機能する。従って、第1の絶縁膜を複数の絶縁膜を積層して形成している場合、第1の電極11上において最上層の絶縁膜のみ研磨するようにしても良いし、下層の絶縁膜が露出するように研磨しても良い。

[0124]

例えば、第1の絶縁膜A 12a及び第1の絶縁膜B 12bが酸化窒化シリコン膜で形成され誘電率が7.5であり、第2の絶縁膜14が酸化シリコン膜で形成する場合は誘電率が3.9となり両者に差異が生じる。その場合、CMP後の仕上がり寸法は、第1の絶縁膜12の膜厚を150mとし、第2の絶縁膜14の膜厚を110mとすると良い。

[0125]

第 1 の電極にコモン電圧を印加することで、電極が 1 つの場合に比べて閾値のばらつきを 抑えることができ、なおかつオフ電流を抑えることができる。

[0126]

TFTは半導体膜とゲート絶縁膜とゲート電極との配置により、トップゲート型(プレーナー型)とボトムゲート型(逆スタガ型)などに分類される。いずれにしても、サブスレッショルド係数を小さくするには半導体膜の膜厚を薄くする必要がある。非晶質半導体膜

10

20

30

40

10

20

30

40

50

を結晶化した半導体膜を適用する場合、その半導体膜が薄くなると共に結晶性が悪くなり、純粋に膜厚を薄くした効果を得ることができない。しかし、第1の電極と第2の電極を電気的に接続し、図16において示すように半導体膜の上下に該2つの電極を重ねることにより、実質的に半導体膜の厚さを薄くしたのと同様、電圧の印加と共に早く空乏化し、電界効果移動度を大きくし、サブスレッショルド係数を小さくして、オン電流を大きくすることができる。

#### [0127]

なお、第1の電極11と第2の電極15とが電気的に接続されている場合、第1の絶縁膜12と第2の絶縁膜14の誘電率が近ければ近いほど、電界効果移動度を大きくし、サブスレッショルド係数を小さくして、オン電流を大きくすることができる。

[0128]

また、第1の電極11とチャネル形成領域とが重なっている部分において、第1の絶縁膜12膜の厚さが均一であるときのその膜厚と、第2の電極15とチャネル形成領域とが重なっている部分において、第2の絶縁膜14の厚さが均一であるときのその膜厚は、近ければ近いほど、電界効果移動度を大きくし、やサブスレッショルド係数を小さくして、オン電流を大きくすることができる。第1の電極11と重なる部分における第1の絶縁膜の膜厚をd1、第2の電極15と重なる部分における第2の絶縁膜の膜厚をd2とすると、| d1.d2 | / d1.d2 | / d2 0.1を満たすのが望ましい。より好ましくは、 | d1.d2 | / d1 0.05であり、なおかつ、 | d1.d2 | / d2 0.05を満たすのが良い。

[0129]

最も好ましいのは、第1の電極11と第2の電極15とが電気的に接続されていない状態で、第1の電極11にグラウンドの電圧を印加したときの閾値と、第2の電極15にグラウンドの電圧を印加したときの閾値とがほぼ同じになるようにしたうえで、第1の電極11と第2の電極15とを電気的に接続することである。そうすることで、電界効果移動度を大きくし、サブスレッショルド係数をより小さくして、オン電流をより大きくすることができる。

[0130]

この様な構成とすることによって、半導体膜の上下にチャネル(デュアルチャネル)を形成でき、TFTの特性を向上させることができる。

[0131]

また、第1の電極11と同時に各種信号線や電源線を形成することができる。また、CMPによる平坦化処理と組み合わせると、その上層に形成する半導体膜などに何ら影響を与えることはない。また、多層配線により配線の高密度化を実現できる。

[0132]

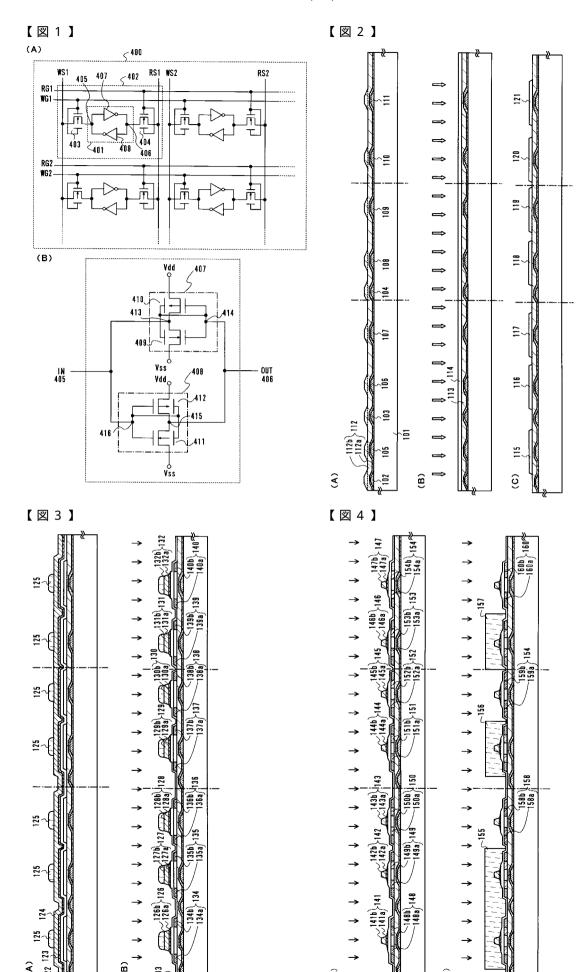

メモリをディスプレイ基板上に作製する場合において、TFTで作製した例を図1の回路図で示す。図1において、メモリは、フリップフロップ回路を用いたSRAM(Static RAM)を用いて構成した例を示す。

[0133]

図1(A)において、メモリ400は、それぞれ1ビットづつの信号を記憶可能な記憶素子401が、s行t列のマトリクス状に配置されたセル402(以下、記憶セルと表記する)に1つずつ配置された構造を有する。記憶セル402は、スイッチング素子として書き込み用TFT403及び読み出し用TFT404を有する。

[0134]

書き込み用TFT403の第1の電極及び第2の電極は、接続されている。また、これらの電極は、書き込み用選択線WG1~WGsのうちの1本に接続されている。書き込み用TFT403のソース領域もしくはドレイン領域の一方は、書き込み用信号線WS1~WStのうちの1本に接続され、もう一方は、記憶素子401の入力端子405に接続されている。読み出し用TFT404の第1の電極と第2の電極とは接続されている。これらの電極は、読み出し用選択線RG1~RGsのうちの1本に接続されている。読み出し用

TFT404のソース領域もしくはドレイン領域は、一方は、記憶素子401の出力端子 406に接続され、もう一方は、読み出し用信号線RS1~RStのうちの1本に接続されている。

### [0135]

図1(B)に、記憶素子401の詳細な構造を示す。記憶素子401は、第1のインバータ407と第2のインバータ408とによって構成される。第1のインバータ407は、 n チャネル型 T F T 4 0 9 と p チャネル型 T F T 4 1 0 によって構成されている。第2のインバータ408は、 n チャネル型 T F T 4 1 1 と p チャネル型 T F T 4 1 2 によって構成されている。

### [0136]

第1のインバータ407において、nチャネル型TFT409の第1の電極と第2の電極とは、接続されている。また、pチャネル型TFT410の第1の電極と第2の電極とは接続されている。nチャネル型TFT409のゲート電極(第1の電極及び第2の電極)とpチャネル型TFT410のゲート電極(第1の電極及び第2の電極)は接続され、第1のインバータ407の入力端子413となる。一方、pチャネル型TFT410のソース領域は、第1の電圧Vddが入力され、ドレイン領域は、nチャネル型TFT409のドレイン領域と接続されている。nチャネル型TFT409のソース領域は、第2の電圧Vssが入力されている。また、nチャネル型TFT409とpチャネル型TFT410それぞれのドレイン領域は、第1のインバータ407の出力端子414となる。

## [0137]

同様に、第2のインバータ408において、nチャネル型TFT411の第1の電極と第2の電極とは、接続されている。また、pチャネル型TFT412の第1の電極と第2の電極とは接続されている。nチャネル型TFT411のゲート電極(第1の電極及び第2の電極)とpチャネル型TFT412のゲート電極(第1の電極及び第2の電極)は接続され、第2のインバータ408の入力端子415となる。一方、pチャネル型TFT412のソース領域は、第1の電圧Vddが入力され、ドレイン領域は、nチャネル型TFT411のドレイン領域と接続されている。nチャネル型TFT411のソース領域は、第2の電圧Vssが入力されている。また、nチャネル型TFT411とpチャネル型TFT412それぞれのドレイン領域は、第2のインバータ408の出力端子416となる。

### [0138]

ここで、第1の電圧Vddは、第2の電圧Vssより大きいとする。

## [0139]

第1のインバータの入力端子413と第2のインバータの出力端子416は、接続され、記憶素子の入力端子405となっている。また、第1のインバータの出力端子414と第2のインバータの入力端子415は、接続され、記憶素子の出力端子406となっている

## [0140]

メモリコントローラによって、書き込み用選択線WG1~WGsのうちの1本が選択され、書き込み用信号線WS1~WStより信号が入力されて、指定された行及び列(従来例において、(x、y)と表記)の記憶セル402において、書き込み用TFT403がオンとなって、記憶素子401に信号が書き込まれる。同様に、または、読み出し用選択線RG1~RGsのうちの1本が選択され、読み出し用信号線RS1~RStより信号が入力されて、指定された行及び列(従来例において、(x、y)と表記)の記憶セル402において、読み出し用TFT404がオンとなって、記憶素子から信号が読み出される。

#### [0141]

上記構成のメモリは、前述した手法によってこれらを構成するTFTを作製し、ディスプレイ基板上に形成することができる。

### [0142]

なお、メモリコントローラやディスプレイコントローラ等のコントロール回路についても 、同様に形成することができる。メモリコントローラ及びディスプレイコントローラを構 10

20

30

40

10

20

30

40

50

成するTFTの構造としては、これらの回路の駆動電圧と小さくするために、オン電流が大きい特徴を有する、第1の電極と第2の電極が接続された構造のTFTを用いるのが望ましい。

#### [0143]

ここで、メモリの構成として、上記構成のSRAMを用いた例を示したが、本発明の表示 装置の有するメモリは、この構成に限定されない。公知の構成の記憶素子を用いて実施す ることが可能である。

### [0144]

なお、本発明の表示装置が有するディスプレイコントローラ、メモリコントローラ、ソース信号線駆動回路及びゲート信号線駆動回路については、公知の構成の回路を自由に用いることができる。

[0145]

こうして、画素部、各駆動回路、メモリ及びコントロール回路を同一基板上に形成した表示装置が提供される。

#### [0146]

ここで、本発明の表示装置のディスプレイが有する画素部の構成としては、従来例において、図21(B)で示した構成の画素を用いることができる。また、それ以外の公知の構成の画素も、自由に用いることができる。

### [0147]

また、本発明は、発光素子として、OLED素子を用いた表示装置だけでなく、画素毎に液晶素子を配置し、この液晶素子の透過率を制御することによって画像の表示をおこなう液晶表示装置についても適用が可能である。

### [0148]

### 【実施例】

以下に、本発明の実施例について説明する。

### [0149]

### (実施例1)

本発明の表示装置の作製工程について説明する。ここでは、同一基板上に画素部のTFT(スイッチング用TFTと、駆動用TFTを代表で示す)と、各駆動回路(ソース信号線駆動回路及びゲート信号線駆動回路)のTFT(nチャネル型TFT及びpチャネル型TFTを代表で示す)及びメモリを構成するTFT(書き込み用TFTと、第1のインバータを構成するnチャネル型TFTとpチャネル型TFTを代表で示す)を同時に作製する方法について詳細に説明する。

### [0150]

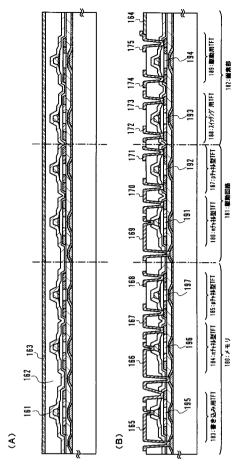

なお、本実施例では、画素部を構成するTFTは、全て第1電極にコモン電圧が印加されており、各駆動回路及びメモリを構成するTFTは第1電極と第2電極とが接続されている例を示している。本実施例において用いる図2~図6は、その作製工程を説明する断面図である。

### [0151]

図 2 (A)において、基板 1 0 1 は絶縁表面を有し、後の工程の処理温度に耐えうるものであれば、どのような材料の基板でも用いることが可能である。代表的には、ガラス基板、石英基板、セラミック基板などを用いることができる。また、シリコン基板、金属基板またはステンレス基板の表面に絶縁膜を形成したものを用いても良い。また、本実施例の処理温度に耐えうる耐熱性を有するプラスチック基板を用いてもよい。

#### [0152]

この基板101の絶縁表面上に第1の配線102、第2の配線103、第3の配線104と第1の電極105~111を形成する。第1~第3の配線及び第1の電極はA1、W、Mo、Ti、Taから選ばれた一種又は複数種からなる導電性の材料で形成する。本実施例ではWを用いたが、TaNの上にWを積層したものを第1~第3の配線及び第1の電極として用いても良い。

#### [0153]

ここで、第1の電極110、111は、コモン配線の一部である。

#### [0154]

第1の配線102、第2の配線103、第3の配線104と第1の電極105~111を形成した後、第1の絶縁膜112を形成する。本実施例では、第1の絶縁膜112は、2つの絶縁膜(第1の絶縁膜A 112a、第1の絶縁膜B 112b)を積層することで形成されている。第1の絶縁膜A 112aは酸窒化シリコン膜を用い、10~50nmの厚さで形成する。第1の絶縁膜B 112bは酸化シリコン膜又は酸窒化シリコン膜を用い、0.5~1 $\mu$ mの厚さで形成する。

### [0155]

第1の絶縁膜112の表面は、先に形成した第1~第3の配線及び第1の電極に起因する凹凸を有している。好ましくは、この凹凸を平坦化することが望ましい。平坦化の手法としてはСMPを用いる。第1の絶縁膜112に対するСMPの研磨剤(スラリー)には、例えば、塩化シリコンガスを熱分解して得られるフュームドシリカ粒子をKOH添加水溶液に分散したものを用いると良い。СMPにより第1の絶縁膜112を0.1~0.5 $\mu$ m程度除去して、表面を平坦化する。

### [0156]

こうして、図 2 ( B )に示すように平坦化された第 1 の絶縁膜 1 1 3 が形成され、その上に半導体層を形成する。半導体層 1 1 4 は結晶構造を有する半導体で形成する。これは、第 1 の絶縁膜 1 1 3 上に形成した非晶質半導体層を結晶化して得る。非晶質半導体層は堆積した後、加熱処理やレーザー光の照射により結晶化させる。非晶質半導体層の材料に限定はないが、好ましくはシリコン又はシリコンゲルマニウム(  $Si_xGe_{1-x}$ ; 0 < x < 1 、代表的には、 x=0 . 0 0 1 ~ 0 . 0 5 )合金などで形成する。

#### [0157]

その後、半導体層114をエッチングにより島状に分割し、図2(C)に示すように半導体膜115~121を形成する。

#### [0158]

第1の電極105は半導体膜115と第1の絶縁膜113を間に介して重なっている。第1の電極106は半導体膜116と第1の絶縁膜113を間に介して重なっている。第1の電極107は半導体膜117と第1の絶縁膜113を間に介して重なっている。第1の電極108は半導体膜118と第1の絶縁膜113を間に介して重なっている。第1の電極109は半導体膜119と第1の絶縁膜113を間に介して重なっている。第1の電極110は半導体膜120と第1の絶縁膜113を間に介して重なっている。また、第1の電極111は半導体膜121と第1の絶縁膜113を間に介して重なっている。

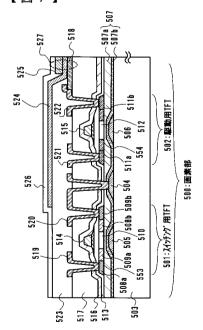

## [0159]

次いで、図 3 ( A ) に示すように、半導体膜 1 1 5 ~ 1 2 1 を覆う第 2 の絶縁膜 1 2 2 を形成する。第 2 の絶縁膜 1 2 2 は、プラズマ C V D 法やスパッタ法でシリコンを含む絶縁物で形成する。その厚さは 4 0 ~ 1 5 0 nmとする。

### [0160]

第2の絶縁膜122上には第2の電極や第2の配線を形成するために導電膜を形成する。本発明において第2の電極は2層又はそれ以上の導電膜を積層して形成する。第2の絶縁膜122上に形成する第1の導電膜123はモリブデン、タングステンなどの高融点金属の窒化物で形成し、その上に形成する第2の導電膜124は高融点金属又はアルミニウムや銅などの低抵抗金属、或いはポリシリコンなどで形成する。具体的には、第1の導電膜としてW、Mo、Ta、Tiから選ばれ一種又は複数種の窒化物を選択し、第2の導電膜としてW、Mo、Ta、Ti、Al、Cuから選ばれ一種又は複数種の合金、或いはn型多結晶シリコンを用いる。例えば、第1の導電膜123をTaNで形成し、第2の導電膜124をWで形成しても良い。また第2の電極や第2の配線を3層の導電膜で形成する場合、1層目をMo、2層目をAl、3層目をTiNとしても良い。配線を多層にすることで、配線自体の厚さが増

10

20

30

40

すので配線抵抗を抑えることができる。

#### [0161]

この第1の導電膜123及び第2の導電膜124を、マスク125を用いてエッチングし、第2の配線及び第2の電極を形成する。

### [0162]

図3(B)に示すように、第1のエッチング処理により、端部にテーパーを有する第1形状の電極126~132を形成する(第1の導電膜126a~132aと第2の導電膜126b~132bで成る)。第2の絶縁膜133は、第1の形状の電極126~132で覆われない部分において、表面が20~50m程度エッチングされ薄くなった状態になっている。

### [0163]

第 1 のドーピング処理は、イオン注入法または質量分離をしないでイオンを注入するイオンドープ法により行う。ドーピングは第 1 形状の電極 1 2 1 ~ 1 2 5 をマスクとして用い、半導体膜 1 1 5 ~ 1 2 1 に第 1 濃度の一導電型不純物領域 1 3 4 ~ 1 4 0 を形成する。第 1 濃度は 1 × 1 0  $^{20}$  ~ 1 . 5 × 1 0  $^{21}$ /cm³とする。

#### [0164]

次に、レジストからなるマスクを除去せずに図4(A)に示すように第2のエッチング処理を行う。このエッチング処理では、第2の導電膜を異方性エッチングして第2の形状の電極141~147を形成する(第1の導電膜141a~147aと第2の導電膜141 b~147bで成る)。第2の形状の電極141~147はこのエッチング処理により幅を縮小させ、その端部が第1濃度の一導電型不純物領域134~140(第2の不純物領域)の内側に位置するように形成する。次の工程で示すように、この後退幅によりLDDの長さを決める。第2の形状の電極141~147は第2の電極として機能する。

#### [ 0 1 6 5 ]

第2形状の電極146は、ゲート配線の一部である。第2の形状の電極141と、第1の電極105は、半導体膜115と第1の絶縁膜113を間に介して重なっている。第2の形状の電極142と、第1の電極106は、半導体膜116と第1の絶縁膜113を間に介して重なっている。第2の形状の電極143と、第1の電極107は、半導体膜117と第1の絶縁膜113を間に介して重なっている。第2の形状の電極144と、第1の電極108は、半導体膜113を間に介して重なっている。第2の形状の電極145と、第1の電極109は、半導体膜119と第1の絶縁膜113を間に介して重なっている。第2の形状の電極145と、第1の電極110は、半導体膜120と第1の絶縁膜113を間に介して重なっている。第2の形状の電極147と、第1の電極111は、半導体膜121と第1の絶縁膜113を間に介して重なっている。

### [0166]

そして、この状態で一導電型の不純物を第2のドーピング処理を行い一導電型の不純物を半導体膜115~121に添加する。このドーピング処理で形成される第2濃度の一導電型不純物領域(第1の不純物領域148~154は、第2形状の電極141~147を構成する第1の導電膜141a~147を構成する第1の導電膜141a~147aを通過させて添加するため、半導体膜に達するイオンの数は減少し、必然的に低濃度となる。その濃度は $1\times10^{17}$ ~ $1\times10^{19}$ /cm³となる。

### [0167]

次いで、図 4 ( B )で示すように、レジストからなるマスク 1 5 5 ~ 1 5 7 を形成し第 3 のドーピング処理を行う。この第 3 のドーピング処理により、半導体膜 1 1 7 、 1 1 9 、 1 2 1 に第 3 濃度の一導電型とは反対の導電型の不純物領域 1 5 8 ~ 1 6 0 を形成する。第 3 濃度の一導電型とは反対の導電型の不純物領域は第 2 形状の電極 1 4 3 、 1 4 5 、 1 4 7 と重なる領域に形成されるものであり、 1 . 5 × 1 0  $^{20}$  ~ 5 × 1 0  $^{21}$ /cm³の濃度範囲で当該不純物元素が添加される。

### [0168]

10

20

30

以上までの工程でそれぞれの半導体膜に価電子制御を目的とした不純物を添加した領域が 形成される。第1の電極105~111と、第2の形状の電極141~147は半導体膜 と交差する位置においてゲート電極として機能する。

#### [0169]

その後、それぞれの半導体膜に添加された不純物元素を活性化処理する工程を行う。この活性化はガス加熱型の瞬間熱アニール法を用いて行う。加熱処理の温度は窒素雰囲気中で400~700 、代表的には450~500 で行う。この他に、YAGレーザーの第2高調波(532nm)を用いたレーザーアニール法を適用することもできる。レーザー光の照射により活性化を行うには、YAGレーザーの第2高調波(532nm)を用いこの光を半導体膜に照射する。勿論、レーザー光に限らずランプ光源を用いるRTA法でも同様であり、基板の両面又は片面からランプ光源の輻射により半導体膜を加熱する。

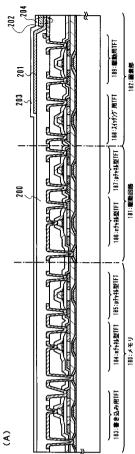

[0170]

その後、図 5 ( A )に示すように、プラズマ C V D 法で窒化シリコンから成るパッシベーション膜 1 6 1 を 5 0 ~ 1 0 0 nmの厚さに形成し、クリーンオーブンを用いて 4 1 0 の 熱処理を行い、窒化シリコン膜から放出される水素で半導体膜の水素化を行う。

[0171]

次いで、パッシベーション膜161上に有機絶縁物材料から成る第3の絶縁膜162を形成する。有機絶縁物材料を用いる理由は第3の絶縁膜162の表面を平坦化するためのものである。より完全な平坦面を得るためには、この表面をCMP法により平坦化処理することが望ましい。CMP法を併用する場合には、第3の絶縁膜をプラズマCVD法で形成される酸化シリコン膜、塗布法で形成されるSOG(Spin on Glass)やPSGなどを用いることもできる。なお、パッシベーション膜161は第3の絶縁膜162の一部とみなしても良い。

[0172]

こうして平坦化された第3の絶縁膜162の表面に酸化インジウム・スズを主成分とする透明導電膜163を60~120nmの厚さで形成する。この表面にも微細な凹凸が形成されるため、酸化アルミニウムを研磨剤として用いたCMP法により研磨して平坦化しておくことが望ましい。

[0173]

その後、透明導電膜163をエッチング処理して画素電極(第3の電極)164を形成する。そして、第2の絶縁膜122、パッシベーション膜161、第3の絶縁膜162にコンタクトホールを形成し、配線165~175を形成する。この配線はチタン膜とアルミニウム膜を積層して形成する。

[0174]

配線165は、第1の配線102と、第2の形状の電極141とに接続されている。また、第1の配線102と第1の電極105は電気的に接続されている。配線166は、第2の配線103と、第2の形状の電極142と不純物領域134bとに接続されている。配線167は、不純物領域135bと、不純物領域158aとに接続されている。配線168は、不純物領域158bに接続されている。なお、図示しないが、第2の形状の電極142と第2の形状の電極143は、電気的に接続されている。

[0175]

配線169は、第3の配線104と、第2の形状の電極144とに接続されている。配線170は、不純物領域137bと、不純物領域159aとに接続されている。配線171は、不純物領域159bに接続されている。

[0176]

配線172は、不純物領域139aに接続されており、ソース配線として機能する。配線173は、不純物領域139bに接続されている。配線174は、不純物領域160aに接続されている。配線175は、不純物領域160bと、画素電極164に接続されている。配線174は、電源供給線として機能する。また、配線173及び配線174は、保持容量(図示せず)の2つの電極にそれぞれ接続される。

10

20

30

40

10

20

30

40

50

#### [0177]

以上までの工程において、一導電型不純物領域を n 型、一導電型とは反対の不純物領域を p 型とすると、同一基板上に、書き込み用TFTとして機能する n チャネル型TFT183、第1のインバータを構成する n チャネル型TFT184と p チャネル型TFT185を有するメモリ180と、 n チャネル型TFT186、 p チャネル型TFT187を有する駆動回路181と、スイッチング素子として機能する n チャネル型TFT188と、駆動用TFTとして機能する p チャネル型TFT189を有する画素部182とが形成される。

### [0178]

メモリ180において、書き込み用TFT183の一対のゲート電極141、105はチャネル形成領域195を間に挟んで重なっている。第2濃度の一導電型の不純物領域148はLDDとして、第1濃度の一導電型の不純物領域134はソース又はドレイン領域として機能する。nチャネル型TFT184の一対のゲート電極142、106はチャネル形成領域196を間に挟んで重なっている。第2濃度の一導電型の不純物領域149はLDDとして、第1濃度の一導電型の不純物領域135はソース又はドレイン領域として機能する。pチャネル型TFT185の一対のゲート電極143、107はチャネル形成領域197を間に挟んで重なっている。第3濃度の一導電型とは反対の不純物領域158はソース又はドレイン領域として機能する。

#### [0179]

駆動回路181において、nチャネル型TFT186の一対のゲート電極144、108はチャネル形成領域191を間に挟んで重なっている。第2濃度の一導電型の不純物領域151はLDDとして、第1濃度の一導電型の不純物領域137はソース又はドレイン領域として機能する。 p チャネル型TFT187の一対のゲート電極145、109はチャネル形成領域192を間に挟んで重なっている。第3濃度の一導電型とは反対の不純物領域159はソース又はドレイン領域として機能する。

### [0180]

LDDのチャネル長方向の長さは $0.5 \sim 2.5 \mu m$ 、好ましくは $1.5 \mu m$ で形成する。このようなLDDの構成は、主にホットキャリア効果によるTFTの劣化を防ぐことを目的としている。これらn チャネル型TFT及びp チャネル型TFTによりシフトレジスタ回路、バッファ回路、レベルシフタ回路、ラッチ回路などを形成することができる。特に、駆動電圧が高いバッファ回路には、ホットキャリア効果による劣化を防ぐ目的から、LDDを有するTFTの構造が適している。

### [0181]

画素部182において、スイッチング用TFT188の一対のゲート電極146、110は、チャネル形成領域193を間に挟んで重なっている。第2濃度の一導電型の不純物領域153はLDDとして、第1濃度の一導電型の不純物領域139はソース又はドレイン領域として機能する。駆動用TFT189において一対のゲート電極147、111は、チャネル形成領域194を間に挟んで重なっている。第3濃度の一導電型とは反対の不純物領域160はソース又はドレイン領域として機能する。

#### [0182]

本実施例では、コモン配線に常に一定の電圧(コモン電圧)を印加することで、第1の電極にコモン電圧を印加する。なお、この一定の電圧は、nチャネル型TFTの場合は閾値よりも小さく、pチャネル型TFTの場合は閾値よりも大きくする。第1の電極にコモン電圧を印加することで、電極が1つの場合に比べて閾値のばらつきを抑えることができ、なおかつオフ電流を抑えることができる。特に、画素部にスイッチング素子として形成されたTFT(スイッチング用TFT)は、オン電流の増加よりもオフ電流の低減が重要視されるので、上記構成は有用である

#### [0183]

また、本実施例では、駆動回路が有するTFTにおいて、半導体膜を挿んで電気的に接続された一対のゲート電極を形成することにより、実質的に半導体膜の厚さが半分となり、

ゲート電圧の印加に伴って空乏化が早く進んで電界効果移動度を増加させ、サブスレッショルド係数を低下させることが可能となる。その結果、この構造のTFTを駆動回路に使用することにより、駆動電圧を低下させることができる。また、電流駆動能力が向上し、TFTのサイズ(特にチャネル幅)を小さくすることができる。そのため集積密度を向上させることができる。

## [0184]

図6(A)に、第3の絶縁膜162上に発光素子を形成した状態を示す。第3の絶縁膜162上には、TFT183~189を覆う隔壁層200が形成される。有機化合物層や陰極はウエット処理(薬液によるエッチングや水洗などの処理)を行うことができないので、画素電極164に合わせて、第4の絶縁膜上に感光性樹脂材料で形成される隔壁層200を設ける。隔壁層200はポリイミド、ポリアミド、ポリイミドアミド、アクリルなど有機樹脂材料を用いて形成する。この隔壁層200は画素電極の端部を覆うように形成する。また、隔壁層200の端部は45~60度のテーパー角が付くように形成する。

### [0185]

発光素子204は陽極と陰極とその間に形成された有機化合物層とから成る。有機化合物層は、正孔移動度が相対的に高い正孔輸送性材料、その逆の電子輸送性材料、発光性材料などを組み合わせて形成する。それらは層状に形成しても良いし、混合して形成しても良い。

## [0186]

画素電極164上に、有機化合物層201を形成する。その後、対向電極202を形成する。

#### [0187]

有機化合物材料は合計しても100nm程度の薄膜層として形成される。そのため、陽極として形成するITOの表面は平坦性を高めておく必要がある。平坦性が悪い場合は、最悪、有機化合物層の上に形成する陰極とショートしてしまう。それを防ぐための他の手段として、1~5nmの絶縁膜を形成する方法を採用することもできる。絶縁膜としては、ポリイミド、ポリイミドアミド、ポリアミド、アクリルなどを用いることができる。対向電極(第4の電極)202はMgAgやLiFなどのアルカリ金属またはアルカリ土類金属などの材料を用いて形成することにより陰極とすることができる。

### [0188]

対向電極 2 0 2 は、仕事関数の小さいマグネシウム(Mg)、リチウム(Li)若しくはカルシウム(Ca)を含む材料を用いる。好ましくはMgAg(MgとAgをMg:Ag = 10:1で混合した材料)でなる電極を用いれば良い。他にもMgAgAl電極、LiAl電極、また、LiFAl電極が挙げられる。さらにその上層には、窒化シリコンまたは、DLC膜で成る絶縁膜 2 0 3 を 2 ~ 30 nm、好ましくは 5 ~ 10 nmの厚さで形成する。DLC膜はプラズマCVD法で形成可能であり、100 以下の温度で形成しても、被覆性良く隔壁層 2 0 0 の端部を覆って形成することができる。DLC膜の内部応力は、アルゴンを微量に混入させることで緩和することが可能であり、保護膜として用いることが可能である。そして、DLC膜は酸素をはじめCO、CO2、H2Oなどのガスバリア性が高いので、バリア膜として用いる絶縁膜 2 0 3 として適している。

## [0189]

なお本実施例では、第1の電極と第2の電極とを、ソース配線と同時に形成された配線で接続しているが、第1の電極と第2の電極とを直接接続するようにしても良い。ただし、本実施例のように、第1の電極と第2の電極とを、ソース配線と同時に形成された配線で接続する場合、工程数を増やす必要がなく、マスク数を抑えることができる。

## [0190]

パッケージング等の処理により気密性を高めたら、基板上に形成された素子又は回路から引き回された端子と外部信号端子とを接続するためのコネクター(フレキシブルプリントサーキット:FPC)を取り付けて製品として完成する。

## [0191]

20

10

30

#### (実施例2)

本実施例では、実施例1とは異なる構成の表示装置を作製した例について説明する。

#### [0192]

本実施例の表示装置の画素の断面図を図7に示す。

### [0193]

5 0 1 はスイッチング用TFTとして機能する、 n チャネル型TFTであり、 5 0 2 は駆動用TFTとして機能する、 p チャネル型TFTである。スイッチング用TFT 5 0 1 は、半導体膜 5 5 3 と、第 1 の絶縁膜 5 0 7 ( 5 0 7 a 及び 5 0 7 b ) と、第 1 の電極 5 0 5 と、第 2 の絶縁膜 5 1 3 と、第 2 の電極 5 1 4 とを有している。そして、半導体膜 5 5 3 は、第 1 濃度の一導電型不純物領域 5 0 8 ( 5 0 8 a 及び 5 0 8 b ) と、第 2 濃度の一導電型不純物領域 5 0 9 ( 5 0 9 a 及び 5 0 9 b ) と、チャネル形成領域 5 1 0 を有している。

#### [0194]

第1の電極505とチャネル形成領域510とは、第1の絶縁膜507を間に挟んで重なっている。また、第2の電極514と、チャネル形成領域510とは、第2の絶縁膜51 3を間に挟んで重なっている。

### [0195]

p チャネル型 T F T 5 0 2 は、半導体膜 5 5 4 と、第 1 の絶縁膜 5 0 7 と、第 1 の電極 5 0 6 と、第 2 の絶縁膜 5 1 3 と、第 2 の電極 5 1 5 とを有している。そして、半導体膜 5 5 4 は、第 3 濃度の一導電型不純物領域 5 1 1 (5 1 1 a 及び 5 1 1 b)と、チャネル形成領域 5 1 2 を有している。

#### [0196]

第1の電極506とチャネル形成領域512とは、第1の絶縁膜507を間に挟んで重なっている。第2の電極515とチャネル形成領域512とは、第2の絶縁膜513を間に挟んで重なっている。

### [0197]

そして、第1の電極506と第2の電極515とは、配線504を介して電気的に接続されている。

### [0198]

本実施例では、同じ画素内のTFTでも、スイッチング素子として用いるスイッチング用 TFT501(本実施例の場合 n チャネル型TFT)は、第1の電極505にコモン電圧 を印加している。第1の電極505にコモン電圧を印加することで、電極が1つの場合に 比べて閾値のばらつきを抑えることができ、なおかつオフ電流を抑えることができる。

#### [0199]

また、スイッチング素子として用いるTFTよりも大きな電流を流す駆動用TFT502(本実施例の場合pチャネル型TFT)は、第1の電極と第2の電極とを電気的に接続している。第1の電極と第2の電極に同じ電圧を印加することで、実質的に半導体膜の膜厚を薄くしたのと同じように空乏層が早く広がるので、サブスレッショルド係数を小さくすることができ、さらに電界効果移動度を向上させることができる。したがって、電極が1つの場合に比べてオン電流を大きくすることができる。よって、この構造のTFTを用いることによって、駆動電圧を低下させることができる。また、オン電流を大きくすることができるので、TFTのサイズ(特にチャネル幅)を小さくすることができる。そのため集積密度を向上させることができる。

## [0200]

本実施例は、実施例1と自由に組み合わせて実施することが可能である。

## [0201]

#### (実施例3)

本実施例では、駆動回路のシフトレジスタに用いられるフリップフロップ回路を、第1の電極と第2の電極を電気的に接続したTFTを用いて形成する例について説明する。

### [0202]

50

10

20

30

10

20

30

40

50

図8に本実施例のフリップフロップ回路の回路図を示す。なお本発明の表示装置が有するフリップフロップ回路は図8に示した構成に限定されない。また、フリップフロップ回路は、駆動回路が有する回路のほんの一例として挙げたまでであり、本発明の表示装置が必ずしもフリップフロップ回路を有している必要はない。

### [0203]

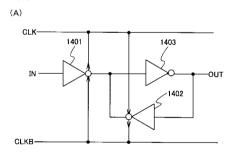

図 8 ( A ) に示したフリップフロップ回路は、クロックドインバーター 1 4 0 1 、 1 4 0 2 と、インバーター 1 4 0 3 を有している。図 8 ( A ) に示したフリップフロップ回路の、各回路素子をより具体的に示した回路図を、図 8 ( B ) に示す。

### [0204]

本実施例のクロックドインバーター (1401及び1402)は、pチャネル型TFTと nチャネル型TFTを2つづつ有している。

### [0205]

クロックドインバータ 1 4 0 1 において、第1の p チャネル型 T F T 1 4 4 4 のソース領域は第1の電圧(Vdd)が印加され、ドレイン領域は第2の p チャネル型 T F T 1 4 4 5 のドレイン領域は第2の p チャネル型 T F T 1 4 4 5 のドレイン領域は、第2の n チャネル型 T F T 1 4 4 6 のドレイン領域に接続されている。第2の n チャネル型 T F T 1 4 4 6 のソース領域は第1の n チャネル型 T F T 1 4 4 7 のドレイン領域に接続されており、第1の n チャネル型 T F T 1 4 4 7 のソース領域は第2の電圧(VSS)が印加されている。なお第1の電圧は第2の電圧よりも高い。

### [0206]

第1の p チャネル型 T F T 1 4 4 4 のゲート電極には、クロック信号(C L K )が入力されており、第1の n チャネル型 T F T 1 4 4 7 のゲート電極にはクロック信号(C L K B )が入力されている。

#### [0207]

クロックドインバータは、クロック信号(CLK)及び反転クロック信号(CLKB)に同期して、第2のpチャネル型TFT1405と第2のnチャネル型TFT1406のゲート電極に入力される信号(IN)の極性を反転させた出力信号(OUT)を出力する。

#### [0208]

クロックドインバータ 1 4 0 2 も同様に、第 1 の p チャネル型 T F T 1 4 4 8 、第 2 の p チャネル型 T F T 1 4 4 9 、第 1 の n チャネル型 T F T 1 4 5 1 、第 2 の n チャネル型 T F T 1 4 5 2 を有する。

## [0209]

本実施例では、図8(B)に示したクロックドインバータが有する全てのTFTは、電気的に接続された第1の電極と第2の電極を有している。

### [0210]

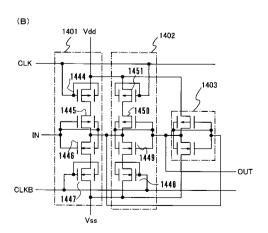

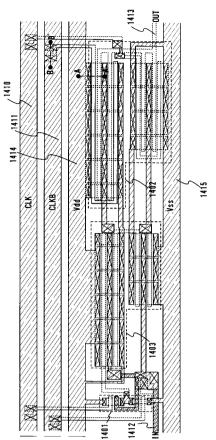

図9に、図8(B)に示したクロックドインバータの上面図を示す。 1401、 1402はクロックドインバーター、 1403はインバーターである。クロック信号(CLK)、反転クロック信号(CLKB)、入力信号(IN)は、それぞれ配線 1410、 1411、 1412に入力されている。出力信号(OUT)は配線 1413 から出力されている。また第1の電圧(Vdd)と第2の電圧(Vss)は、それぞれ配線 1414、 1415 に印加されている。

## [0211]

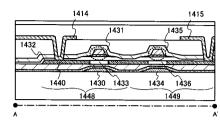

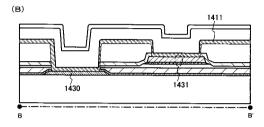

図 9 の A - A 'における断面図を図 1 0 (A)に、B - B 'における断面図を図 1 0 (B)に示す。

#### [0212]

図 1 0 ( A ) において、クロックドインバーター 1 4 0 2 が有する第 1 の p チャネル型 T F T 1 4 4 8 と、クロックドインバーター 1 4 0 2 が有する第 2 の p チャネル型 T F T 1 4 4 9 の断面を示す。

### [0213]

第1のpチャネル型TFT1448は、第1の電極1430と第2の電極1431を有し

ている。第1の電極1430と第2の電極1431は、半導体膜1432が有するチャネル形成領域1433を間に挟んで重なっている。

#### [0214]

第2のpチャネル型TFT1449は、第1の電極1434と第2の電極1435を有している。第1の電極1434と第2の電極1435は、半導体膜1432が有するチャネル形成領域1436を間に挟んで重なっている。

#### [0215]

そして、第1のpチャネル型TFT1448の半導体膜1432が有するソース領域1440は配線1414に接続されている。また、第2のpチャネル型TFT1449の半導体膜1432が有するドレイン領域1441は、配線1415に接続されている。

### [0216]

第1のpチャネル型TFT1448の、第1の電極1430と第2の電極1431は、反転クロック信号(CLKB)が入力されている配線1411に接続されている。よって、第1の電極1430と第2の電極1431は電気的に接続されている。また図示しないが、第1の電極1434と第2の電極1435も電気的に接続されている。

#### [0217]

なお本実施例では、第1の電極と第2の電極とを、他の配線によって電気的に接続しているが、第1の電極と第2の電極とを直接接続しても良い。ただし、第1の電極と第2の電極とを、配線によって電気的に接続する場合、該配線を他の配線と同時に形成することが可能であるので、マスク数を抑えることができる。

#### [0218]

なお、配線1410、1411、1414及び1415を、複数の導電膜を積層して形成することができる。多層配線にして抵抗を下げることで、駆動回路をより高集積化することができる。

#### [0219]

また、本実施例で示したように、各TFTの第1の電極と第2の電極の接続は、各TFTごとに行なう必要はなく、回路が有する複数のTFTにおいて、その第1の電極と第2の電極のいずれか一方が互いに接続されている場合、いずれか1つのTFTにおいて第1の電極と第2の電極が接続されていれば良い。

### [0220]

本実施例は、実施例1または実施例2と自由に組み合わせて実施することが可能である。 (実施例4)

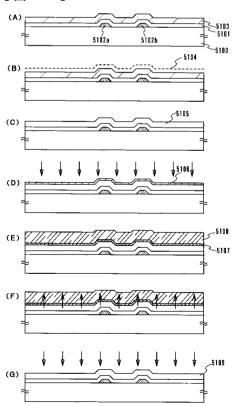

本実施例では、半導体膜の作製方法の例について説明する。

#### [0221]

図11(A)において、5100は絶縁表面を有する基板である。図11(A)において、基板5100はガラス基板、石英基板、セラミック基板などを用いることができる。また、シリコン基板、金属基板またはステンレス基板の表面に絶縁膜を形成したものを用いても良い。また、本工程の処理温度に耐えうる耐熱性を有するプラスチック基板を用いてもよい。

## [0222]

まず、図11(A)に示すように、基板5100上に、第1の電極5102a、5102 bが形成されている。第1の電極5102a、5102 b は導電性を有する物質で形成されていれば良い。代表的には、アルミニウム(A 1)、タングステン(W)、モリブデン(M o )、タンタル(T a )、チタン(T i )から選ばれた一種または複数種からなる合金又は化合物で形成することができる。また何層かの導電性の膜を積層したものを、第1の電極として用いても良い。

### [0223]

そして、第1の電極 5 1 0 2 a 、 5 1 0 2 b を覆って、絶縁表面上に第1の絶縁膜 5 1 0 1 が形成されている。第1の絶縁膜 5 1 0 1 は、酸化シリコン膜、窒化シリコン膜または酸化窒化シリコン膜(SiO $_{\rm x}$  N  $_{\rm v}$ )等で形成する。代表的な一例は第1の絶縁膜 5 1 0 1

10

20

30

40

として、 $SiH_4$ 、 $NH_3$ 、及び $N_2$ Oを反応ガスとして成膜される第 1 酸化窒化シリコン膜を 5 0 ~ 1 0 0 n m、 $SiH_4$ 、及び $N_2$ Oを反応ガスとして成膜される第 2 酸化窒化シリコン膜を 1 0 0 ~ 1 5 0 n mの厚さに積層形成する、 2 層構造が採用される。また、第 1 の絶縁膜 5 1 0 1 の一層として膜厚 1 0 n m以下の窒化シリコン膜(SiN膜)、或いは第 2 酸化窒化シリコン膜( $SiN_xO_y$ 膜(X Y))を用いることが好ましい。ゲッタリングの際、ニッケルは酸素濃度の高い領域に移動しやすい傾向があるため、半導体膜と接する第 1 の絶縁膜を窒化シリコン膜とすることは極めて有効である。また、第 1 酸化窒化シリコン膜、第 2 酸化窒化シリコン膜、窒化シリコン膜とを順次積層した 3 層構造を用いてもよい。

### [0224]

次いで、第1の絶縁膜上に非晶質構造を有する第1の半導体層5103を形成する。第1の半導体層5103は、シリコンを主成分とする半導体材料を用いる。代表的には、非晶質シリコン膜又は非晶質シリコンゲルマニウム膜などが適用され、プラズマCVD法や減圧CVD法、或いはスパッタ法で10~100nmの厚さに形成する。後の結晶化で良質な結晶構造を有する半導体層を得るためには、非晶質構造を有する第1の半導体層5103の膜中に含まれる酸素、窒素などの不純物濃度を5×10<sup>18</sup>/cm³(二次イオン質量分析法(SIMS)にて測定した原子濃度)以下に低減させておくと良い。これらの不純物は後の結晶化を妨害する要因となり、また、結晶化後においても捕獲中心や再結合中心の密度を増加させる要因となる。そのために、高純度の材料ガスを用いることはもとより、反応室内の鏡面処理(電界研磨処理)やオイルフリーの真空排気系を備えた超高真空対応のCVD装置を用いることが望ましい。

## [0225]

次いで、非晶質構造を有する第1の半導体層5103を結晶化させる技術としてここでは特開平8 78329号公報記載の技術を用いて結晶化させる。同公報記載の技術は、非晶質シリコン膜(アモルファスシリコン膜とも呼ばれる)に対して結晶化を助長する金属元素を選択的に添加し、加熱処理を行うことで添加領域を起点として広がる結晶構造を有する半導体層を形成するものである。まず、非晶質構造を有する第1の半導体層5103の表面に、結晶化を促進する触媒作用のある金属元素(ここでは、ニッケル)を重量換算で1~100ppm含む酢酸ニッケル塩溶液をスピナーで塗布してニッケル含有層5104を形成する。(図11(B))塗布によるニッケル含有層5104の形成方法以外の他の手段として、スパッタ法、蒸着法、またはプラズマ処理により、極薄い膜を形成する手段を用いてもよい。また、ここでは、全面に塗布する例を示したが、マスクを形成して選択的にニッケル含有層を形成してもよい。

### [0226]

次いで、加熱処理を行い、結晶化を行う。この場合、結晶化は半導体の結晶化を助長する金属元素が接した半導体層の部分でシリサイドが形成され、それを核として結晶化が進行する。こうして、図11(C)に示す結晶構造を有する第1の半導体層5105が形成される。なお、結晶化後での第1の半導体層5105に含まれる酸素濃度は、5×10<sup>18</sup> / cm³以下とすることが望ましい。ここでは、脱水素化のための熱処理(450 、1時間)の後、結晶化のための熱処理(550 ~650 で4~24時間)を行う。また、強光の照射により結晶化を行う場合は、赤外光、可視光、または紫外光のいずれかーよたはそれらの組み合わせを用いることが可能であるが、代表的には、ハロゲンランプ、ホーボンアークランプ、高圧ナトリウムランプ、または高圧水銀ランプから射出された光を用いる。ランプ光源は、1~60秒、メランプ、または高圧水銀ランプから射出された光を用いる。ランプ光源は、1~60秒、分子ましくは30~60秒点灯させ、それを1回~10回繰り返し、半導体層が瞬間的に600~1000 程度にまで加熱すればよい。なお、必要であれば、強光を照射する前にままに、熱処理と強光の照射とを同時に行って結晶化を行ってもよい。生産性を考慮すると、結晶化は強光の照射により結晶化を行うことが望ましい。

### [0227]

10

20

30

10

20

30

40

50

このようにして得られる第1の半導体層5105には、金属元素(ここではニッケル)が残存している。それは膜中において一様に分布していないにしろ、平均的な濃度とすれば、1×10 $^{19}$ /cm $^3$ を越える濃度で残存している。勿論、このような状態でもTFTをはじめ各種半導体素子を形成することが可能であるが、以降に示す方法で当該元素を除去する

### [0228]

次いで、結晶化率(膜の全体積における結晶成分の割合)を高め、結晶粒内に残される欠陥を補修するために、結晶構造を有する第1の半導体層5105に対してレーザー光(第1のレーザー光)を大気または酸素雰囲気で照射する。レーザー光(第1のレーザー光)を照射した場合、表面に凹凸が形成されるとともに薄い酸化膜5106が形成される。(図11(D))このレーザー光(第1のレーザー光)には波長400m以下のエキシマレーザー光や、YAGレーザーの第2高調波、第3高調波を用いる。また、エキシマレーザー光に代えて紫外光ランプから発する光を用いてもよい。

## [0229]

さらに、オゾン含有水溶液(代表的にはオゾン水)で酸化膜(ケミカルオキサイドと呼ば れる)を形成して合計1~10nmの酸化膜からなるバリア層5107を形成し、このバ リア層5107上に希ガス元素を含む第2の半導体層5108を形成する(図11(E) )。なお、ここでは、結晶構造を有する第1の半導体層5105に対してレーザー光を照 射した場合に形成される酸化膜5106もバリア層の一部と見なしている。このバリア層 5 1 0 7 は、後の工程で第 2 の半導体層 5 1 0 8 のみを選択的に除去する際にエッチング ストッパーとして機能する。また、オゾン含有水溶液に代えて、硫酸、塩酸、硝酸などと 過酸化水素水を混合させた水溶液で処理しても同様にケミカルオキサイドを形成すること ができる。また、他のバリア層5107の形成方法としては、酸素雰囲気下の紫外線の照 射でオゾンを発生させて前記結晶構造を有する半導体層の表面を酸化して形成してもよい 。また、他のバリア層5107の形成方法としては、プラズマCVD法やスパッタ法や蒸 着法などで1~10nm程度の酸化膜を堆積してバリア層としても良い。また、他のバリ ア層5107の形成方法としては、クリーンオーブンを用い、200~350 熱して薄い酸化膜を形成しても良い。なお、バリア層5107は、上記方法のいずれか一 の方法、またはそれらの方法を組み合わせて形成されたものであれば特に限定されないが 、後のゲッタリングで第1の半導体層中のニッケルが第2の半導体層に移動可能な膜質ま たは膜厚とすることが必要である。

## [0230]

ここでは、希ガス元素を含む第2の半導体層5108をスパッタ法にて形成し、ゲッタリングサイトを形成する。(図11(E))なお、第1の半導体層には希ガス元素が添加されないようにスパッタ条件を適宜調節することが望ましい。希ガス元素としてはヘリウム(He)、ネオン(Ne)、アルゴン(Ar)、クリプトン(Kr)、キセノン(Xe)から選ばれた一種または複数種を用いる。中でも安価なガスであるアルゴン(Ar)が好ましい。ここでは希ガス元素を含む雰囲気でシリコンからなるターゲットを用い、第2の半導体層を形成する。膜中に不活性気体である希ガス元素イオンを含有させる意味は二つある。一つはダングリングボンドを形成し半導体層に歪みを与えることであり、他の一つは半導体層の格子間に歪みを与えることである。半導体層の格子間に歪みを与えるにはアルゴン(Ar)、クリプトン(Kr)、キセノン(Xe)などシリコンより原子半径の大きな元素を用いた時に顕著に得られる。また、膜中に希ガス元素を含有させることにより、格子歪だけでなく、不対結合手も形成させてゲッタリング作用に寄与する。

#### [0231]

また、一導電型の不純物元素であるリンを含むターゲットを用いて第 2 の半導体層を形成した場合、希ガス元素によるゲッタリングに加え、リンのクーロン力を利用してゲッタリングを行うことができる。

### [0232]

また、ゲッタリングの際、ニッケルは酸素濃度の高い領域に移動しやすい傾向があるため

、第2の半導体層5108に含まれる酸素濃度は、第1の半導体層に含まれる酸素濃度より高い濃度、例えば $5 \times 10^{18}$  / c m<sup>3</sup>以上とすることが望ましい。

#### [0233]

次いで、加熱処理を行い、第1の半導体層中における金属元素(ニッケル)の濃度を低減、あるいは除去するゲッタリングを行う。(図11(F))ゲッタリングを行う加熱処理としては、強光を照射する処理または熱処理を行えばよい。このゲッタリングにより、図11(F)中の矢印の方向(即ち、基板側から第2の半導体層 5 105に含まれる金属元素が移動し、バリア層 5 107で覆われた第1の半導体層 5 105に含まれる金属元素の除去、または金属元素の濃度の低減が行われる。金属元素がゲッタリングの際に移動する距離は、少なくとも第1の半導体層の厚さ程度の距離であればよく、比較的短時間でゲッタリングを完遂することができる。ここでは、ニッケルが第1の半導体層 5 105に偏析しないよう全て第2の半導体層 5 108に移動させ、第1の半導体層 5 105に含まれるニッケルがほとんど存在しない、即ち膜中のニッケル濃度が1×10 $^{18}$ / c m  $^{3}$ 以下になるように十分ゲッタリングする。

#### [0234]

また、このゲッタリングの加熱処理の条件によっては、ゲッタリングと同時に第 1 の半導体層の結晶化率を高め、結晶粒内に残される欠陥を補修する、即ち結晶性の改善を行うことができる。

### [0235]

本明細書において、ゲッタリングとは、被ゲッタリング領域(ここでは第1の半導体層)にある金属元素が熱エネルギーにより放出され、拡散によりゲッタリングサイトに移動することを指している。従って、ゲッタリングは処理温度に依存し、より高温であるほど短時間でゲッタリングが進むことになる。

#### [0236]

また、このゲッタリングの加熱処理として強光を照射する処理を用いる場合は、加熱用のランプ光源を1~60秒、好ましくは30~60秒点灯させ、それを1~10回、好ましくは2~6回繰り返す。ランプ光源の発光強度は任意なものとするが、瞬間的には600~1000、好ましくは700~750 程度に半導体層が加熱されるようにする。

### [0237]

また、熱処理で行う場合は、窒素雰囲気中で450~800 、1~24時間、例えば550 にて14時間の熱処理を行えばよい。また、熱処理に加えて強光を照射してもよい

#### [0238]

次いで、バリア層 5 1 0 7 をエッチングストッパーとして、 5 1 0 6 で示した第 2 の半導体層のみを選択的に除去した後、酸化膜からなるバリア層 5 1 0 7 を除去する。第 2 の半導体層のみを選択的にエッチングする方法としては、 C 1 F 3 によるプラズマを用いないドライエッチング、或いはヒドラジンや、テトラエチルアンモニウムハイドロオキサイド(化学式 (C H 3 ) 4 N O H )を含む水溶液などアルカリ溶液によるウエットエッチングで行うことができる。また、第 2 の半導体層を除去した後、バリア層の表面を T X R F でニッケル濃度を測定したところ、ニッケルが高濃度で検出されるため、バリア層は除去することが望ましく、フッ酸を含むエッチャントにより除去すれば良い。

#### [0239]

次いで、結晶構造を有する第1の半導体層に対してレーザー光(第2のレーザー光)を窒素雰囲気または真空で照射する。レーザー光(第2のレーザー光)を照射した場合、第1のレーザー光の照射により形成された凹凸の高低差(P V値:Peak to Valley、高さの最大値と最小値の差分)が低減、即ち、平坦化される。(図11(G))ここで、凹凸のP V値は、AFM(原子間力顕微鏡)により観察すればよい。具体的には、第1のレーザー光の照射により形成された凹凸のP V値が10nm~30nm程度であった表面は、第2のレーザー光の照射により表面における凸凹のP V値を5nm以下とすることができ、条件によっては1.5nm以下にすることができる。このレーザー光(第2のレー

10

20

30

40

ザー光)には波長400nm以下のエキシマレーザー光や、YAGレーザーの第2高調波、第3高調波を用いる。また、エキシマレーザー光に代えて紫外光ランプから発する光を用いてもよい。

#### [0240]

第2のレーザー光のエネルギー密度は、第1のレーザー光のエネルギー密度より大きくし、好ましくは30~60 m J / c m  $^2$ 大きくする。ただし、第2のレーザー光のエネルギー密度が第1のレーザー光のエネルギー密度よりも90 m J / c m  $^2$ 以上大きいエネルギー密度だと、表面の粗さが増大し、さらに結晶性の低下、或いは微結晶化してしまい、特性が悪化する傾向が見られる。

### [0241]

なお、第2のレーザー光の照射は、第1のレーザー光のエネルギー密度よりも高いが、照射前後で結晶性はほとんど変化しない。また、粒径などの結晶状態もほとんど変化しない。即ち、この第2のレーザー光の照射では平坦化のみが行われていると思われる。

## [0242]

結晶構造を有する半導体層が第2のレーザー光の照射により平坦化されたメリットは非常に大きい。例えば、平坦性が向上したことによって、後に形成されるゲート絶縁膜として用いる第2の絶縁膜を薄くすることが可能となり、TFTの移動度を向上させることができる。また、平坦性が向上したことによって、TFTを作製した場合、オフ電流を低減することができる。

## [0243]

また、第2のレーザー光を照射することによって、ゲッタリングサイトを形成する際に第1の半導体層にも添加されてしまった場合、結晶構造を有する半導体層中の希ガス元素を除去または低減する効果も得られる。

#### [0244]

次いで、平坦化された第1の半導体層5109を公知のパターニング技術を用いて所望の 形状の半導体膜を形成する。

#### [0245]

本実施例は、実施例1~実施例3と自由に組み合わせて実施することが可能である。

### [0246]

## (実施例5)

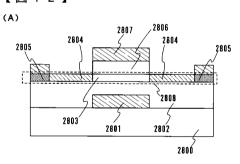

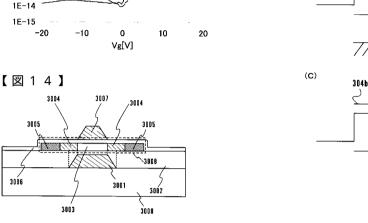

本実施例では、本発明の表示装置が有するTFTの一実施例について、図14を用いて説明する。

#### [0247]

図14に本実施例のTFTの断面図を示す。図14に示したTFTは、絶縁表面を有する基板3000上に、第1の電極3001と、第1の電極3001に接する第1の絶縁膜3002と、第1の絶縁膜3002に接する半導体膜3008と、半導体膜3008に接する第2の絶縁膜3008は、チャネル形成領域3003と、チャネル形成領域3003に接する第1の不純物領域3004と、第1の不純物領域3004に接する第2の不純物領域3005を有している。

## [0248]

第1の不純物領域3004に添加されている一導電型の不純物の濃度は、第2の不純物領域3005に添加されている一導電型の不純物の濃度よりも低い。

## [0249]

第1の電極3001と第2の電極3007は、チャネル形成領域3003を間に挟んで重なり合っている。そして、第1の電極3001と第2の電極3007には同じ電圧が印加されている。

#### [0250]

本実施例のTFTは、第1の電極3001のテーパーになっている部分が、第1の不純物領域3004と重なっている。そして第1の電極3001は、チャネル形成領域3003

10

20

30

40

10

20

30

40

50

と重なっている部分においてほぼ平坦になっている。上記構成により、第1の電極とチャネル形成領域とが、ほぼ一定の間隔をもって重なり合うことになる。この状態において、第1の電極とチャネル形成領域とが重なっている部分における第1の絶縁膜の膜厚と、第2の電極とチャネル形成領域とが重なっている部分における第2の絶縁膜の膜厚とをほぼ同じにすると、S値をより小さくすることができる。

#### [ 0 2 5 1 ]

本実施例は、実施例1~4と自由に組み合わせて実施することが可能である。

### [0252]

(実施例6)

本実施例では、本発明の表示装置のソース信号線駆動回路の構成例について説明する。

#### [0253]

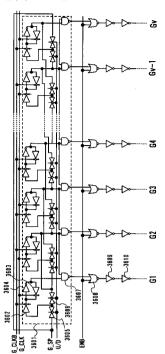

ソース信号線駆動回路の構成例を図22に示す。

### [0254]

ソース信号線駆動回路は、シフトレジスタと、走査方向切り換え回路、LAT(A)及びLAT(B)によって構成されている。なお、図22では、シフトレジスタからの出力の1つに対応する、LAT(A)の一部2612とLAT(B)の一部2618のみを図示するが、シフトレジスタからの全ての出力に対して、同様の構成のLAT(A)及びLAT(B)が対応する。

## [ 0 2 5 5 ]

シフトレジスタ2601は、クロックドインバータ2602と2603、インバータ2604、NAND2607によって構成されている。シフトレジスタ2601には、ソース信号線駆動回路用スタートパルスS\_SPが入力され、ソース信号線駆動回路用クロックパルスS\_CLKとその極性が反転した信号であるソース信号線駆動回路用反転クロックパルスS\_CLKBによって、クロックドインバータ2602及び2603が導通状態、非導通状態と変化することによって、NAND2607から順に、LAT(A)にサンプリングパルスを出力する。

#### [0256]

また、走査方向切り換え回路は、スイッチ2605及びスイッチ2606によって構成され、シフトレジスタの操作方向を、図面向かって左右に切り換える働きをする。図22では、左右切り換え信号L/RがLoの信号に対応する場合、シフトレジスタは、図面向かって左から右に順にサンプリングパルスを出力する。一方、左右切り換え信号L/RがHiの信号に対応する場合、図面向かって右から左に順にサンプリングパルスを出力する。

#### [0257]

各ステージのLAT(A)2613は、クロックドインバータ2614、2615と、インバータ2616、2617によって構成されている。

#### [0258]

ここで、各ステージのLAT(A)とは、1本のソース信号線に入力する映像信号を取り込むLAT(A)を示すものとする。

### [0259]

ソース信号線駆動回路が形成されたディスプレイ基板と同一基板上に形成されたメモリより、読み出されたデジタル映像信号はVDは、p分割(pは自然数)されて入力される。つまり、p本のソース信号線への出力に対応する信号が並列に入力される。サンプリングパルスが、バッファ2608~2611を介して、p個のステージのLAT(A)2612のクロックドインバータ2614、2615に同時に入力されると、p分割された入力信号はp個のステージのLAT(A)2612において、それぞれ同時にサンプリングされる。

#### [0260]

ここでは、 v 本のソース信号線に信号電流を出力するソース信号線駆動回路 2 6 0 0 を例に説明するので、 1 水平期間あたり、 v / p 個のサンプリングパルスが順にシフトレジスタより出力される。各サンプリングパルスに応じて、 p 個のステージの L A T ( A ) 2 6

1 3 は、同時に p 本のソース信号線への出力に対応するデジタル映像信号をサンプリングする。

### [0261]

本明細書中では、このようにソース信号線駆動回路に入力するデジタル映像信号を、 p 相の並列信号に分割し、 p 個のデジタル映像信号を 1 つのサンプリングパルスによって同時に取り込む手法を、 p 分割駆動と呼ぶことにする。

#### [0262]

上記分割駆動を行うことによって、ソース信号線駆動回路のシフトレジスタのサンプリングにマージンを持たせることができる。こうして表示装置の信頼性を向上させることができる。

[0263]

各ステージのLAT(A)2613に1水平期間の信号がすべて入力されると、ラッチパルスLS及びその極性が反転した、反転ラッチパルスLSBが入力されて、各ステージのLAT(A)2613に入力された信号を各ステージのLAT(B)2619へ一斉に出力する。

[0264]

なお、ここで各ステージのLAT(B)とは、各ステージのLAT(A)からの信号をそれぞれ入力する、LAT(B)回路のことを示すとする。

[0265]

LAT(B)の各ステージ2619は、クロックドインバータ2620、2621及び、インバータ2622、2623によって構成されている。LAT(A)の各ステージ2613より出力された信号は、LAT(B)に保持されると同時に、各ソース信号線S1~S×に出力される。

[0266]

なお、ここでは図示しなかったが、レベルシフタやバッファ等を適宜設けても良い。

[0267]

シフタレジスタ及びLAT(A)、LAT(B)に入力されるスタートパルスS\_SP、クロックパルスS\_CLK等は、上記構成のソース信号線駆動回路が形成された基板と同一基板上に形成されたディスプレイコントローラから入力されている。

[0268]

なお、本発明の表示装置は、本実施例のソース信号線駆動回路の構成に限らず、公知の構成のソース信号線駆動回路を自由に用いることができる。

[0269]

本実施例は、実施例1~実施例5と自由に組み合わせて実施することが可能である。

[0270]

(実施例7)

本実施例では、本発明の表示装置のゲート信号線駆動回路の構成例について説明する。

[0271]

ゲート信号線駆動回路は、シフトレジスタ、走査方向切り換え回路等によって構成されて いる。なお、ここでは図示しなかったが、レベルシフタやバッファ等を適宜設けても良い

[0272]

シフトレジスタには、スタートパルス G \_\_ S P 、クロックパルス G \_\_ C L K 等が入力されて、ゲート信号線選択信号を出力している。

[0273]

ゲート信号線駆動回路の構成について、図23を用いて説明する。

[0274]

シフトレジスタ3601は、クロックドインバータ3602と3603、インバータ36 04、NAND3607によって構成されている。シフトレジスタ2601には、スター トパルスG\_SPが入力され、クロックパルスG\_CLKとその極性が反転した信号であ 10

20

30

40

る反転クロックパルス G \_ C L K B によって、クロックドインバータ 3 6 0 2 及び 3 6 0 3 が導通状態、非導通状態と変化することによって、N A N D 3 6 0 7 から順に、サンプリングパルスを出力する。

#### [0275]

また、走査方向切り換え回路は、スイッチ3605及びスイッチ3606によって構成され、シフトレジスタの操作方向を、図面向かって左右に切り換える働きをする。図23では、走査方向切り換え信号U/DがLoの信号に対応する場合、シフトレジスタは、図面向かって左から右に順に、サンプリングパルスを出力する。一方、走査方向切り換え信号U/DがHiの信号に対応する場合、図面向かって右から左に順にサンプリングパルスを出力する。

[0276]

シフトレジスタから出力されたサンプリングパルスは、NOR3608に入力され、イネーブル信号ENBと演算される。この演算は、サンプリングパルスのなまりによって、となり合うゲート信号線が同時に選択される状況を防ぐために行われる。NOR3608から出力された信号は、バッファ3609、3610を介して、ゲート信号線G1~Gyに出力される。

[0277]

なお、ここでは図示しなかったが、レベルシフタやバッファ等を適宜設けても良い。

[0278]

シフタレジスタに入力されるスタートパルスG\_SP、クロックパルスG\_CLK等は、 ゲート信号線駆動回路が形成された基板と同じ基板上に形成されたディスプレイコントローラから入力されている。

[0279]

なお、本発明の表示装置は、本実施例のゲート信号線駆動回路の構成に限らず、公知の構成のゲート信号線駆動回路を自由に用いることができる。

[0280]

本実施例は、実施例1~実施例6と自由に組み合わせて実施することが可能である。 (実施例8)

本実施例では、表示装置の画素が有するスイッチング用TFTを作製した例について説明する。

[0281]

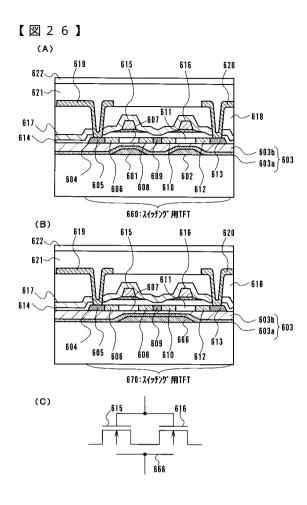

本実施例の表示装置の画素のスイッチング用TFTの断面図を図26に示す。

[0282]

図26(A)において、660はスイッチング用TFTとして機能する、nチャネル型TFTである。スイッチング用TFT660は、半導体膜604と、第1の絶縁膜603(603a及び603b)と、第1の電極601、第2の絶縁膜614と、第2の電極615とを有するTFTと、半導体膜604と、第1の絶縁膜603(603a及び603b)と、第1の電極602、第2の絶縁膜614と、第2の電極616とを有するTFTとが直列に接続されたダブルゲート構造のTFTである。そして、半導体膜604は、第1濃度の一導電型不純物領域605、608、610、612と、チャネル形成領域607、611を有している。

[0283]

第1の電極601とチャネル形成領域607とは、第1の絶縁膜603を間に挟んで重なっている。また、第2の電極615と、チャネル形成領域607とは、第2の絶縁膜614を間に挟んで重なっている。第1の電極602とチャネル形成領域611とは、第1の絶縁膜603を間に挟んで重なっている。また、第2の電極616と、チャネル形成領域611とは、第2の絶縁膜614を間に挟んで重なっている。

[0284]

第1の電極601と602とは、電気的に接続されている。

[0285]

10

20

30

第2の電極615と616とは、半導体膜604の外側にて電気的に接続されている。

[0286]

スイッチング用TFT660(本実施例の場合 n チャネル型TFT)は、第1の電極60 1、602にコモン電圧を印加している。第1の電極601、602にコモン電圧を印加 することで、第2の電極のみの場合に比べて閾値のばらつきを抑えることができ、なおか つオフ電流を抑えることができる。

[0287]

ここで、さらにオフ電流を抑えた構造のTFTの構成を図26(B)に示す。

[0288]

図 2 6 ( A ) における第 1 の電極 6 0 1 及び 6 0 2 の代わりに、図 2 6 ( B ) では、第 1 の電極 6 6 6 を用いている。また、第 2 の電極 6 1 5 と、第 3 の電極 6 1 6 を有する。

[0289]

第1の電極666とチャネル形成領域607、第1濃度の一導電型不純物領域609と、第2濃度の一導電型不純物領域608、610及びチャネル形成領域611とは、第1の 絶縁膜603を間に挟んで重なっている。また、第2の電極615と、チャネル形成領域 607とは、第2の絶縁膜614を間に挟んで重なっている。また、第3の電極616と 、チャネル形成領域611とは、第2の絶縁膜614を間に挟んで重なっている。

[0290]

ここで、第1の電極666と、第1濃度の一導電型不純物領域605及び613と第2濃度の一導電型不純物領域606及び612とは、第1の絶縁膜603を間に挟んで重ならないようにする。

[0291]

そして、第2の電極615と、第3の電極616とは、半導体膜の外側で、電気的に接続されている。

[0292]

ここで、第3の電極616は、第2の電極615と同時に作製することができる。

[0293]

スイッチング用TFT670(本実施例の場合 n チャネル型TFT)は、第1の電極666にコモン電圧を印加している。第1の電極666にコモン電圧を印加することで、第2の電極のみの場合に比べて閾値のばらつきを抑えることができ、なおかつオフ電流を抑えることができる。

[0294]

なお、図26(C)に、図26(B)で示した構造のTFTを模式的に示した図である。

[0295]

ここでは、 n チャネル型TFTを例に示したが、 p チャネル型TFTに応用することができる。

[0296]

本実施例は、実施例1~実施例7と自由に組み合わせて実施することが可能である。

[0297]

(実施例9)

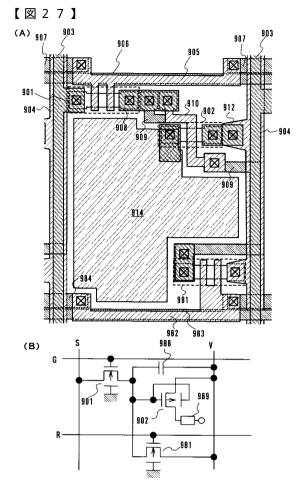

本実施例では、特願2000-359032にあるような、1つの画素に、3つのTFTを配置した構成の画素を、本発明の表示装置に用いた例について説明する。

[0298]

図 2 7 ( B ) に示すように、1つの画素に、スイッチング用 T F T 9 0 1 と、駆動用 T F T 9 0 2 と、リセット用 T F T 9 8 1 の 3 つの T F T を配置する。

[0299]

スイッチング用TFT901のゲート電極は、ゲート信号線Gに接続されている。スイッチング用TFT901のソース領域もしくはドレイン領域は、一方は、ソース信号線Sに接続されている。もう一方は、駆動用TFT902のゲート電極、保持容量988の第1の電極及びリセット用TFT981のソース領域もしくはドレイン領域に接続されている

10

20

30

40

。リセット用TFT981のソース領域もしくはドレイン領域で、スイッチング用TFT901と接続されていない側は、電源供給線Vに接続されている。リセット用TFT981のゲート電極は、リセット用信号線Rに接続されている。駆動用TFT902のソース領域もしくはドレイン領域は、一方は、電源供給線Vに接続され、もう一方は、発光素子989に接続されている。

#### [0300]

この構成の画素の駆動動作について説明する。

#### [0301]

ゲート信号線 G が選択され、スイッチング用TFT901のゲート電極に信号が入力されて、スイッチング用TFT901がオンの状態となった画素において、ソース信号線 S から信号が入力される。入力された信号により、駆動用TFT902のゲート電圧が変化し、駆動用TFT902を介して、電源供給線 V から電流が供給され、発光素子989は発光する。このとき、駆動用TFT902のゲート電圧は、保持容量988に保持されている。

#### [0302]

ここで、保持容量 9 8 8 に保持された電圧を放電するため、リセット用TFT 9 8 1 が設けられている。リセット用信号線 R に入力された信号によって、リセット用TFT 9 8 1 をオンの状態とすることで、保持容量 9 8 8 に保持された電圧を放電することができる。

### [0303]

図27(B)で示した構成の画素を実際に作製した例について、図27(A)にその上面図を示す。

#### [0304]

9 0 1 及び 9 8 1 は n チャネル型TFTであり、 9 0 2 は p チャネル型TFTである。また、 9 0 3 はソース配線、 9 0 4 は電源線、 9 8 2 及び 9 0 5 はゲート配線、 9 0 6 及び 9 8 3 はコモン配線である。

### [0305]

本実施例では電源線904と、ゲート配線905及び982とが、同じ導電膜から同時に形成されている。言いかえると、電源線904と、ゲート配線905とが同じ層に形成されている。そして隣り合う画素が有するゲート配線905どうしは、コモン配線906と同じ層に形成された接続配線907を介して接続されている。また隣り合う画素が有するゲート配線982どうしは、コモン配線983と同じ層に形成された接続配線984を介して接続されている。

### [0306]

ゲート配線905の一部は、nチャネル型TFT901の第2の電極として機能している。また、コモン配線906の一部は、nチャネル型TFT901の第1の電極として機能している。またnチャネル型TFT901のソース領域とドレイン領域は、一方はソース配線903に、もう一方はソース配線903と同じ層に形成された接続配線908を介してpチャネル型TFT902の第1の電極909及び第2の電極910に接続されている

#### [0307]

p チャネル型 T F T 9 0 2 のソース領域とドレイン領域は、一方はソース配線 9 0 3 と同じ層に形成された接続配線 9 1 2 を介して電源線 9 0 4 に、もう一方は、ソース配線 9 0 3 と同じ層に形成された接続配線 9 1 3 を間に介して、画素電極 9 1 4 に接続されている

# [0308]

ゲート配線982の一部は、nチャネル型TFT981の第2の電極として機能している。また、コモン配線983の一部は、nチャネル型TFT981の第1の電極として機能している。

#### [0309]

本実施例では、ソース配線と電源線を異なる層に形成したことで、重ね合わせることがで

10

20

30

40

10

20

30

40

50

き、その結果開口率を上げることができる。なお、本発明はこの構成に限定されず、電源線をソース配線よりも上の層で形成しても良い。また、ソース配線または電源線のいずれか一方を、コモン配線と同じ層に形成しても良い。

#### [0310]

本実施例では、同じ画素内のTFTでも、スイッチング素子として用いるTFT(本実施例の場合nチャネル型TFT901及び981)は、第1の電極にコモン電圧を印加している。第1の電極にコモン電圧を印加することで、電極が1つの場合に比べて閾値のばらつきを抑えることができ、なおかつオフ電流を抑えることができる。

### [0311]

また、スイッチング素子として用いるTFTよりも大きな電流を流すTFT(本実施例の場合 p チャネル型TFT902)は、第1の電極と第2の電極とを電気的に接続している。第1の電極と第2の電極に同じ電圧を印加することで、実質的に半導体膜の膜厚を薄くしたのと同じように空乏層が早く広がるので、サブスレッショルド係数を小さくすることができ、さらに電界効果移動度を向上させることができる。したがって、電極が1つの場合に比べてオン電流を大きくすることができる。よって、この構造のTFTを駆動回路に使用することにより、駆動電圧を低下させることができる。また、オン電流を大きくすることができるので、TFTのサイズ(特にチャネル幅)を小さくすることができる。そのため集積密度を向上させることができる。

## [0312]

本実施例は、実施例1~実施例8と自由に組み合わせて実施することが可能である。

#### [0313]

(実施例10)

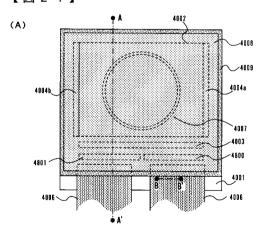

本実施例では、発光素子としてOLED素子を用いた場合の表示装置の封止の方法について、図24を用いて説明する。

#### [0314]

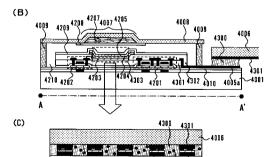

図 2 4 ( A ) は、表示装置の上面図であり、図 2 4 ( B ) は、図 2 4 ( A ) の A - A 'における断面図、図 2 4 ( C ) は図 2 4 ( A ) の B - B 'における断面図である。

#### [0315]

基板 4 0 0 1 上に設けられた画素部 4 0 0 2 と、ソース信号線駆動回路 4 0 0 3 と、第 1 及び第 2 のゲート信号線駆動回路 4 0 0 4 a、 4 0 0 4 bと、メモリ 4 8 0 0 と、メモリコントローラ 4 8 0 1 とを囲むようにして、シール材 4 0 0 9 が設けられている。また画素部 4 0 0 2 と、ソース信号線駆動回路 4 0 0 3 と、第 1 及び第 2 のゲート信号線駆動回路 4 0 0 4 a、 4 0 0 4 bと、メモリ 4 8 0 0 と、メモリコントローラ 4 8 0 1 との上にシーリング材 4 0 0 8 が設けられている。よって画素部 4 0 0 2 と、ソース信号線駆動回路 4 0 0 3 と、第 1 及び第 2 のゲート信号線駆動回路 4 0 0 4 a、 4 0 0 4 bと、メモリ 4 8 0 0 と、メモリコントローラ 4 8 0 1 とは、基板 4 0 0 1 とシール材 4 0 0 9 とシーリング材 4 0 0 8 とによって、充填材 4 2 1 0 で密封されている。

### [0316]

また基板4001上に設けられた画素部4002と、ソース信号線駆動回路4003と、第1及び第2のゲート信号線駆動回路4004a、4004bと、メモリ4800と、メモリコントローラ4801とは、複数のTFTを有している。図24(B)では代表的に、下地膜4010上に形成された、ソース信号線駆動回路4003に含まれる駆動TFT(但し、ここではnチャネル型TFTとpチャネル型TFTを図示する)4201及び画素部4002に含まれる駆動用TFT4202を図示した。

#### [0317]

本実施例では、駆動 T F T 4 2 0 1 には公知の方法で作製された p チャネル型 T F T または n チャネル型 T F T が用いられ、駆動用 T F T 4 2 0 2 には公知の方法で作製された p チャネル型 T F T が用いられる。また、画素部 4 0 0 2 には駆動用 T F T 4 2 0 2 のゲートに接続された保持容量(図示せず)が設けられる。

## [0318]

駆動TFT4201及び駆動用TFT4202上には層間絶縁膜(平坦化膜)4301が 形成され、その上に駆動用TFT4202のドレインと電気的に接続する画素電極(陽極 )4203が形成される。画素電極4203としては仕事関数の大きい透明導電膜が用い られる。透明導電膜としては、酸化インジウムと酸化スズとの化合物、酸化インジウムと 酸化亜鉛との化合物、酸化亜鉛、酸化スズまたは酸化インジウムを用いることができる。 また、前記透明導電膜にガリウムを添加したものを用いても良い。

#### [0319]

そして、画素電極 4 2 0 3 の上には絶縁膜 4 3 0 2 が形成され、絶縁膜 4 3 0 2 は画素電極 4 2 0 3 の上に開口部が形成されている。この開口部において、画素電極 4 2 0 3 の上には有機化合物層 4 2 0 4 が形成される。有機化合物層 4 2 0 4 は公知の有機材料または無機材料を用いることができる。また、有機材料には低分子系(モノマー系)材料と、高分子系(ポリマー系)材料があるがどちらを用いても良い。

#### [0320]

有機化合物層4204の形成方法は公知の蒸着技術もしくは塗布法技術を用いれば良い。 また、有機化合物層の構造は正孔注入層、正孔輸送層、発光層、電子輸送層または電子注 入層を自由に組み合わせて積層構造または単層構造とすれば良い。

## [0321]

有機化合物層4204の上には遮光性を有する導電膜(代表的にはアルミニウム、銅もしくは銀を主成分とする導電膜またはそれらと他の導電膜との積層膜)からなる陰極4205が形成される。また、陰極4205と有機化合物層4204の界面に存在する水分や酸素は極力排除しておくことが望ましい。従って、有機化合物層4204を窒素または希ガス雰囲気で形成し、酸素や水分に触れさせないまま陰極4205を形成するといった工夫が必要である。本実施例ではマルチチャンバー方式(クラスターツール方式)の成膜装置を用いることで上述のような成膜を可能とする。そして陰極4205は所定の電圧が与えられている。

## [0322]

以上のようにして、画素電極(陽極)4203、有機化合物層4204及び陰極4205からなる発光素子4303が形成される。そして発光素子4303を覆うように、絶縁膜4302上に保護膜4303が形成されている。保護膜4303は、発光素子4303に酸素や水分等が入り込むのを防ぐのに効果的である。

### [0323]

4 0 0 5 a は電源供給線に接続された引き回し配線であり、駆動用TFT4202のソース領域に電気的に接続されている。引き回し配線4005 a はシール材4009と基板4001 との間を通り、異方導電性フィルム4300を介してFPC4006が有するFPC用配線4301に電気的に接続される。

#### [0324]

シーリング材4008としては、ガラス材、金属材(代表的にはステンレス材)、セラミックス材、プラスチック材(プラスチックフィルムも含む)を用いることができる。プラスチック材としては、FRP(Fiberglass-Reinforced Plastics)板、PVF(ポリビニルフルオライド)フィルム、マイラーフィルム、ポリエステルフィルムまたはアクリル樹脂フィルムを用いることができる。また、アルミニウムホイルをPVFフィルムやマイラーフィルムで挟んだ構造のシートを用いることもできる

## [0325]

但し、発光素子からの光の放射方向がカバー材側に向かう場合にはカバー材は透明でなければならない。その場合には、ガラス板、プラスチック板、ポリエステルフィルムまたはアクリルフィルムのような透明物質を用いる。

### [0326]

また、充填材4103としては窒素やアルゴンなどの不活性な気体の他に、紫外線硬化樹脂または熱硬化樹脂を用いることができ、PVC(ポリビニルクロライド)、アクリル、

10

20

30

40

ポリイミド、エポキシ樹脂、シリコーン樹脂、 PVB(ポリビニルブチラル)または EVA(エチレンビニルアセテート)を用いることができる。本実施例では充填材として窒素を用いた。

## [0327]

また充填材4103を吸湿性物質(好ましくは酸化バリウム)もしくは酸素を吸着しうる物質にさらしておくために、シーリング材4008の基板4001側の面に凹部4007を設けて吸湿性物質または酸素を吸着しうる物質4207を配置する。そして、吸湿性物質または酸素を吸着しうる物質4207は凹部4007に保持されている。なお凹部カバー材4208は目の細かいメッシュ状になっており、空気や水分は通し、吸湿性物質または酸素を吸着しうる物質4207は通さない構成になっている。吸湿性物質または酸素を吸着しうる物質4207は通さない構成になっている。吸湿性物質または酸素を吸着しうる物質4207を設けることで、発光素子4303の劣化を抑制できる。

[0328]

図 2 4 ( C ) に示すように、画素電極 4 2 0 3 が形成されると同時に、引き回し配線 4 0 0 5 a 上に接するように導電性膜 4 2 0 3 a が形成される。

[0329]

また、異方導電性フィルム 4 3 0 0 は導電性フィラー 4 3 0 0 a を有している。基板 4 0 0 1 と F P C 4 0 0 6 とを熱圧着することで、基板 4 0 0 1 上の導電性膜 4 2 0 3 a と F P C 4 0 0 6 上の F P C 用配線 4 3 0 1 とが、導電性フィラー 4 3 0 0 a によって電気的に接続される。

[0330]

本実施例は、実施例1~実施例9と自由に組み合わせて実施することが可能である。

[ 0 3 3 1 ]

(実施例11)

本発明では、液晶表示装置の画素構造の構成の一例を説明する。

[0332]

図28に、画素の上面図を示す。

[0333]

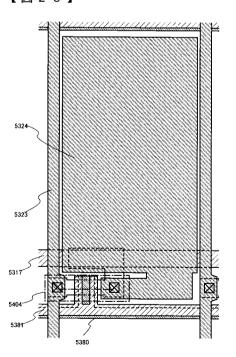

図28において、5317及び5381は、ゲート配線である。ゲート配線5281の一部は、nチャネル型TFT5404の第2のゲート電極を形成している。5380は、コモン配線である。コモン配線5380は、nチャネル型TFT5404の第1のゲート電極を形成している。5323は、ソース配線である。ソース配線5323は、nチャネル型TFT5404のソースもしくはドレイン領域に接続されている。5324は画素電極である。

[0334]

本実施例では、スイッチング素子として用いるTFT(本実施例の場合 n チャネル型TFT5404)は、第1の電極にコモン電圧を印加している。第1の電極にコモン電圧を印加することで、電極が1つの場合に比べて閾値のばらつきを抑えることができ、なおかつオフ電流を抑えることができる。

[0335]

ここで、スイッチング素子として用いるTFT(本実施例の場合 n チャネル型TFT5404)は、ダブルゲート型のTFTで構成されている。ダブルゲート型のTFTとして、 実施例 8 において、図26(B)で示した構造のTFTを用いている。

[0336]

本実施例では、液晶素子の画素電極に印加される電圧を制御するスイッチング素子として、nチャネル型TFTを示したが、pチャネル型TFTでも良い。

[0337]

(実施例12)

本実施例では、第1の電極と第2の電極とを電気的に接続した場合の、TFTの特性につ

10

20

30

40

10

20

30

40

50

いて説明する。

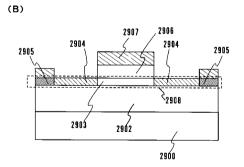

## [0338]

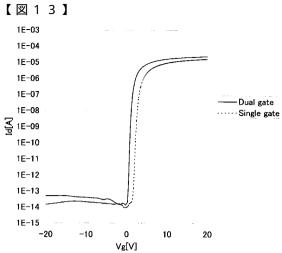

図12(A)に、本発明の第1の電極と第2の電極とを電気的に接続したTFTの断面図を示す。また比較のため、電極を1つだけ有するTFTの断面図を図12(B)に示す。また、図12(A)、図12(B)に示したTFTにおける、シミュレーションによって求めたゲート電圧とドレイン電流の関係を図13に示す。

#### [0339]

図12(A)に示したTFTは、絶縁表面を有する基板2800上に、第1の電極2801と、第1の電極2801に接する第1の絶縁膜2802と、第1の絶縁膜2802に接する半導体膜2808と、半導体膜2808に接する第2の絶縁膜2806と、第2の絶縁膜に接する第2の電極2807を有している。半導体膜2808は、チャネル形成領域2803に接する第1の不純物領域2804と、第1の不純物領域2804に接する第2の不純物領域2805を有している。

## [0340]

第1の電極2801と第2の電極2807は、チャネル形成領域2803を間に挟んで重なり合っている。そして、第1の電極2801と第2の電極2807には同じ電圧が印加されている。

### [0341]

第1の絶縁膜2802及び第2の絶縁膜2806は酸化珪素で形成されている。また第1の電極、第2の電極はA1で形成されている。チャネル長は7 $\mu$ m、チャネル幅は4 $\mu$ m、第1のゲート電極とチャネル形成領域が重なっている部分における第1の絶縁膜の厚さは110 $\mu$ m、第2のゲート電極とチャネル形成領域が重なっている部分における第2の絶縁膜の厚さは110 $\mu$ mである。またチャネル形成領域の厚さは50 $\mu$ mであり、チャネル長方向における第1の不純物領域の長さは1.5 $\mu$ mである。

#### [0342]

そして、チャネル形成領域 2 8 0 3 には 1  $\times$  1 0  $^{17}$  /  $^{17}$  /  $^{17}$  c  $^{17}$  の  $^{17}$  P 型を付与する不純物がドープされており、第 1 の不純物領域には 3  $\times$  1 0  $^{17}$  /  $^{17}$  /  $^{17}$  C  $^{17}$

## [0343]

図12(B)に示したTFTは、絶縁表面を有する基板2900上に、第1の絶縁膜2902と、第1の絶縁膜2902に接する第2の絶縁膜2906と、第2の絶縁膜に接する第2の電極2907を有している。半導体膜2908は、チャネル形成領域2903と、チャネル形成領域2903に接する第1の不純物領域2904と、第1の不純物領域2904に接する第2の不純物領域2905を有している。

#### [0344]

第2の電極2907は、チャネル形成領域2903と重なっている。

## [0345]

第1の絶縁膜2902及び第2の絶縁膜2906は酸化珪素で形成されている。また第2の電極はA1で形成されている。チャネル長は7 $\mu$ m、チャネル幅は4 $\mu$ m、第2のゲート電極とチャネル形成領域が重なっている部分における第2の絶縁膜の厚さは110 $\mu$ mである。またチャネル形成領域の厚さは50 $\mu$ mであり、チャネル長方向における第1の不純物領域の長さは1.5 $\mu$ mである。

## [0346]

そして、チャネル形成領域 2 9 0 3 には 1  $\times$  1 0  $^{17}$  / c m  $^3$  の p 型を付与する不純物がドープされており、第 1 の不純物領域には 3  $\times$  1 0  $^{17}$  / c m  $^3$  の n 型を付与する不純物がドープされており、第 2 の不純物領域には 5  $\times$  1 0  $^{19}$  / c m  $^3$  の n 型を付与する不純物がドープされている。

## [0347]

図13は、横軸がゲート電圧を意味しており、縦軸がドレイン電流を意味している。図1

2 ( A ) の T F T のゲート電圧に対するドレイン電流の値を実線で示し、図 1 2 ( B ) の T F T のゲート電圧に対するドレイン電流の値を破線で示した。

#### [0348]

図 1 3 から、図 1 2 ( A ) においてTFTの移動度 1 3 9 c m  $^2$  / V・s、S値 0 . 1 1 8 V / d e c が得られた。また、図 1 2 ( B ) においてTFTの移動度 8 6 . 3 c m  $^2$  / V・s、S値 0 . 1 6 0 V / d e c が得られた。このことから、第 1 の電極と第 2 の電極を設け、第 2 つの電極を電気的に接続した場合、電極を 1 つしか設けない場合に比べて移動度が高くなり、S値が小さくなる。

[0349]

(実施例13)

10

本実施例では、本発明の表示装置を利用した電子機器について図25を用いて説明する。

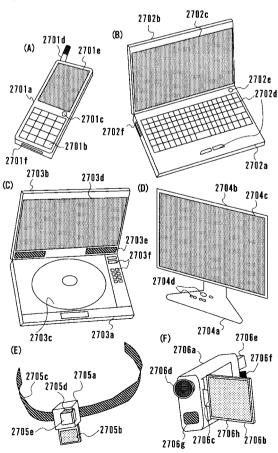

### [0350]

図25(A)に本発明の表示装置を用いた携帯情報端末の模式図を示す。携帯情報端末は、本体2701a、操作スイッチ2701b、電源スイッチ2701c、アンテナ2701d、表示部2701e、外部入力ポート2701fによって構成されている。本発明の表示装置は、表示部2701eに用いることができる。

## [0351]

図25(B)に本発明の表示装置を用いたパーソナルコンピュータの模式図を示す。パーソナルコンピュータは、本体2702a、筐体2702b、表示部2702c、操作スイッチ2702d、電源スイッチ2702e、外部入力ポート2702fによって構成されている。本発明の表示装置は、表示部2702cに用いることができる。

20

#### [0352]

図25(C)に本発明の表示装置を用いた画像再生装置の模式図を示す。画像再生装置は、本体2703a、筐体2703b、記録媒体2703c、表示部2703d、音声出力部2703e、操作スイッチ2703fによって構成されている。本発明の表示装置は、表示部2703dに用いることができる。

### [0353]

図 2 5 ( D ) に本発明の表示装置を用いたテレビの模式図を示す。テレビは、本体 2 7 0 4 a、筐体 2 7 0 4 b、表示部 2 7 0 4 c、操作スイッチ 2 7 0 4 dによって構成されている。本発明の表示装置は、表示部 2 7 0 4 cに用いることができる。

30

### [0354]

図25(E)に本発明の表示装置を用いたヘッドマウントディスプレイの模式図を示す。 ヘッドマウントディスプレイは、本体2705a、モニター部2705b、頭部固定バンド2705c、表示部2705d、光学系2705eによって構成されている。本発明の表示装置は、表示部2705dに用いることができる。

#### [0355]

図 2 5 (F)に本発明の表示装置を用いたビデオカメラの模式図を示す。ビデオカメラは、本体 2 7 0 6 a、筐体 2 7 0 6 b、接続部 2 7 0 6 c、受像部 2 0 0 6 d、接眼部 2 7 0 6 e、バッテリー 2 7 0 6 f、音声入力部 2 7 0 6 g、表示部 2 7 0 6 hによって構成されている。本発明の表示装置は、表示部 2 7 0 6 hに用いることができる。

40

## [0356]

本発明は、上記応用電子機器に限定されず、様々な電子機器に応用することができる。

#### [0357]

本実施例は、実施例1~実施例11と自由に組み合わせて実施することが可能である。

#### [0358]

## 【発明の効果】

本発明は、メモリ、メモリコントローラ及びディスプレイコントローラ等を画素や駆動回路が形成されたディスプレイ基板と同じ基板上に形成する。これによって、メモリ、メモリコントローラ及びディスプレイコントローラと、ディスプレイの駆動回路等との接続部分の配線容量を大幅に低減することができ、表示装置の消費電力を抑えることができる。

#### [0359]

この際、各回路を構成するTFTの構造を、その駆動動作に応じて選択し形成することに よって、信頼性の高い表示装置が得られる。

#### [0360]

## 【図面の簡単な説明】

- 【図1】 本発明の表示装置のメモリの構成を示す回路図。

- 【図2】 本発明の表示装置の作製工程を示す図。

- 【図3】 本発明の表示装置の作製工程を示す図。

- 【図4】 本発明の表示装置の作製工程を示す図。

- 【図5】 本発明の表示装置の作製工程を示す図。

- 【図6】

- 本発明の表示装置の作製工程を示す図。

- 【図7】 表示装置の構成を示す断面図。

- 【図8】 フリップフロップ回路の構成を示す図。

- 【図9】 フリップフロップ回路の構成を示す上面図。

- 【図10】 フリップフロップ回路の構成を示す断面図。

- 【図11】 本発明の表示装置の半導体層の結晶化工程を示す図。

- 【図12】 シュミレーションに用いたTFTの構成を示す図。

- 【図13】 シュミレーションにより得られたTFTの特性を示す図。

- 【図14】 本発明の表示装置のTFTの構造を示す図。

- 【図15】 一般的なTFTの回路図と、本発明のTFTの回路図を示す図。

- 【図16】 本発明の表示装置のTFTの構造を示す図。

- 【図17】 表示装置の構成を示すブロック図。

- 【図18】 表示装置の駆動方法を示すタイミングチャートを示す図。

- 【図19】 メモリコントローラの構成を示すブロック図。

- 【図20】 ディスプレイコントローラの構成を示すブロック図。

- 【図21】 従来の表示装置の画素部の構成を示す回路図。

- 【図22】 表示装置のソース信号線駆動回路の構成を示す回路図。

- 【図23】 表示装置のゲート信号線駆動回路の構成を示す回路図。

- 【図24】 本発明の表示装置の外観を示す図。

- 【図25】 本発明の表示装置を用いた電子機器を示す図。

- 【図26】 本発明の表示装置のスイッチング用TFTの構造を示す図。

- 【図27】 本発明の表示装置の画素の構造を示す図。

- 【図28】 本発明の表示装置の画素の構造を示す図。

10

20

【図7】

【図6】

【図8】

【図9】

【図10】

(A)

【図11】

【図12】

(A)

(B)

【図15】

301

304b

₹304a

304a

【図22】

【図23】

【図24】

【図25】

【図28】

## フロントページの続き

| (51) Int.CI. |         |           | FΙ      |       |         |

|--------------|---------|-----------|---------|-------|---------|

| G 0 9 G      | 3/30    | (2006.01) | G 0 9 G | 3/20  | 6 2 1 M |

| H 0 1 L      | 29/786  | (2006.01) | G 0 9 G | 3/20  | 680B    |

| H 0 1 L      | 27/08   | (2006.01) | G 0 9 G | 3/20  | 680G    |

| H 0 1 L      | 27/10   | (2006.01) | G 0 9 G | 3/20  | 680T    |

| H 0 1 L      | 27/092  | (2006.01) | G 0 9 G | 3/20  | 6 8 0 V |

| H 0 1 L      | 21/8238 | (2006.01) | G 0 9 G | 3/30  | J       |

| H 0 1 L      | 27/11   | (2006.01) | H 0 1 L | 29/78 | 6 1 2 B |

| H 0 1 L      | 21/8244 | (2006.01) | H 0 1 L | 29/78 | 6 1 3 B |

| H 0 5 B      | 33/08   | (2006.01) | H 0 1 L | 27/08 | 3 3 1 E |

| H 0 1 L      | 51/50   | (2006.01) | H 0 1 L | 29/78 | 6 1 7 N |

|              |         |           | H 0 1 L | 27/10 | 4 6 1   |

|              |         |           | H 0 1 L | 27/08 | 3 2 1 C |

|              |         |           | H 0 1 L | 27/10 | 3 8 1   |

|              |         |           | H 0 5 B | 33/08 |         |

|              |         |           | H 0 5 B | 33/14 | Α       |

# (56)参考文献 特開平11-074540(JP,A)

特開2000-235355(JP,A)

特開2001-051292(JP,A)

特開2001-013893(JP,A)

特開平6-338611(JP,A)

特開2000-150906(JP,A)

## (58)調査した分野(Int.CI., DB名)

G02F 1/1343- 1/1345、

1/135- 1/1368、

G09F 9/00- 9/46、

G09G 3/00- 3/08、 3/12、 3/16- 3/26、

3/30、 3/34- 3/38、

H01L 27/32