## (19) 대한민국특허청(KR) (12) 공개특허공보(A)

(11) 공개번호 10-2017-0013343(43) 공개일자 2017년02월06일

(51) 국제특허분류(Int. Cl.)

H01L

23/498

(2006.01)

H01L

21/48

(2006.01)

H01L

21/56

(2006.01)

H01L

23/00

(2006.01)

H01L

23/10

(2006.01)

H01L

25/16

(2006.01)

H01L

25/16

(2006.01)

(52) CPC특허분류

HO1L 23/49827 (2013.01) HO1L 21/486 (2013.01)

(21) 출원번호 10-2016-7036858

(22) 출원일자(국제) **2015년06월02일** 심사청구일자 **없음**

(85) 번역문제출일자 2016년12월29일

(86) 국제출원번호 PCT/US2015/033786

(87) 국제공개번호 **WO 2015/187694** 국제공개일자 **2015년12월10일**

(30) 우선권주장

62/007,758 2014년06월04일 미국(US) 14/586,580 2014년12월30일 미국(US) (71) 출원인

#### 인벤사스 코포레이션

미국 캘리포니아 산 호세 오처드 파크웨이 3025 (우편번호 95134)

(72) 발명자

#### 선 홍

미국 캘리포니아 95134 새너제이 오처드 파크웨이 3025 인벤사스 코포레이션

#### 워이칙 찰스 지.

미국 캘리포니아 95134 새너제이 오처드 파크웨이 3025 인벤사스 코포레이션

(뒷면에 계속)

(74) 대리인

리앤목특허법인

전체 청구항 수 : 총 24 항

### (54) 발명의 명칭 2D 및 3D IC 패키징을 위한 통합된 인터포저 솔루션

#### (57) 요 약

집적 회로(IC) 패키지가 배면 표면 및 공동이 그 내부에 배치되는 상부 표면을 갖는 제1 기판을 포함한다. 공동은 전면 표면을 한정하는 바닥을 갖는다. 복수의 제1 전기전도성 접점이 전면 표면 상에 배치되고, 복수의 제2 전기전도성 접점이 배면 표면 상에 배치된다. 복수의 제1 전기전도성 요소가 제1 기판을 관통하고, 제1 및 제2 전기전도성 접점들 중 선택된 접점을 서로 결합시킨다. IC를 포함하는 제1 다이가 제1 전기전도성 접점들 중 대응하는 접점에 전기전도성으로 결합된다. 제2 기판이 제1 기판의 상부 표면에 밀봉식으로 부착되는 저부 표면을 갖고, 제1 다이를 봉지하도록 공동 내에 유전체 재료가 배치된다.

#### 대 표 도 - 도18

### (52) CPC특허분류

**H01L 21/56** (2013.01)

**H01L 23/10** (2013.01)

**H01L 23/3121** (2013.01)

**H01L 23/49838** (2013.01)

**H01L 24/97** (2013.01)

**H01L 25/0652** (2013.01)

**H01L 25/162** (2013.01)

H01L 2224/16235 (2013.01)

H01L 2224/73204 (2013.01)

(72) 발명자

## 시타람 아르칼굿 알.

미국 캘리포니아 95134 새너제이 오처드 파크웨이

3025 인벤사스 코포레이션

## 가오 구이리안

미국 캘리포니아 95134 새너제이 오처드 파크웨이 3025 인벤사스 코포레이션

### 명세서

### 청구범위

### 청구항 1

집적 회로(integrated circuit, IC) 패키지(package)로서,

배면 표면 및 공동(cavity)이 그 내부에 배치되는 상부 표면을 갖는 제1 기판(substrate)으로서, 상기 공동은 전면 표면을 한정하는 바닥(floor)을 갖는, 상기 제1 기판;

상기 전면 표면 상에 배치되는 복수의 제1 전기전도성 접점(electroconductive contact)들;

상기 배면 표면 상에 배치되는 복수의 제2 전기전도성 접점들;

상기 제1 기판을 관통하고 상기 제1 및 제2 전기전도성 접점들 중 선택된 접점들을 서로 결합시키는 복수의 제1 전기전도성 요소들;

상기 제1 전기전도성 접점들 중 대응하는 접점들에 전기전도성으로 결합되는 IC를 포함하는 제1 다이(die);

상기 제1 기판의 상기 상부 표면에 밀봉식으로 부착되는 저부 표면을 갖는 제2 기판; 및

상기 공동 내에 배치되어 상기 제1 다이를 봉지(encapsulating)하는 유전체 재료(dielectric material)를 포함하는, IC 패키지.

#### 청구항 2

제1항에 있어서,

상기 제1 다이의 상부 표면 상에 배치되는 복수의 제3 전기전도성 접점들;

상기 제2 기판의 상부 표면 상에 배치되는 복수의 제4 전기전도성 접점들;

상기 제2 기판을 관통하고 상기 제3 및 제4 전기전도성 접점들 중 선택된 접점들을 서로 결합시키는 복수의 제2 전기전도성 요소들;

상기 제4 전기전도성 접점들 중 대응하는 접점들에 전기전도성으로 결합되는 IC를 포함하는 제2 다이; 및

상기 제2 기판의 상기 상부 표면에 밀봉식으로 부착되어 상기 제2 다이를 둘러싸는 저부 표면을 갖는 커버 (cover)

를 추가로 포함하는, IC 패키지.

## 청구항 3

제2항에 있어서, 상기 커버는 상기 제2 기판의 상기 상부 표면 위에 성형되어 상기 제2 다이를 봉지하는 중합체를 포함하는, IC 패키지.

#### 청구항 4

제2항에 있어서, 상기 커버는

공동이 그 내부에 배치되는 저부 표면을 갖는 제3 기판으로서, 상기 저부 표면은 상기 제2 다이가 상기 공동 내에 배치되도록 상기 제2 기판의 상기 상부 표면에 밀봉식으로 부착되는, 상기 제3 기판; 및

상기 공동 내에 배치되어 상기 제2 다이를 봉지하는 유전체 재료

를 포함하는, IC 패키지.

## 청구항 5

제4항에 있어서, 상기 유전체 재료는 무기 재료(inorganic material)를 포함하는, IC 패키지.

### 청구항 6

제4항에 있어서, 상기 제1, 제2 및/또는 제3 기판들 중 적어도 하나는 반도체(semiconductor)를 포함하는, IC 패키지.

### 청구항 7

제2항에 있어서, 상기 제1 기판의 상기 전면 표면, 상기 제1 기판의 상기 배면 표면 및/또는 상기 제2 기판의 상기 상부 표면 중 적어도 하나 상에 배치되어 그 상에 각각 배치되는 상기 전기전도성 접점들 중 선택된 접점들을 서로 결합시키는 전기전도성 재배선 층(redistribution layer, RDL)을 추가로 포함하는, IC 패키지.

## 청구항 8

제2항에 있어서, 상기 제1 및 제2 기판들을 관통하는 상기 전기전도성 요소들 중 적어도 하나는 규소-관통 비아 (through-silicon via, TSV)를 포함하는, IC 패키지.

#### 청구항 9

제2항에 있어서, 상기 제1 및 제2 다이들 중 적어도 하나는 솔더 범프(solder bump)들에 의해 상기 전기전도성 접점들 중 대응하는 접점들에 전기전도성으로 결합되는, IC 패키지.

### 청구항 10

제2항에 있어서, 상기 제1 다이, 상기 제2 다이, 또는 상기 제1 및 상기 제2 다이 둘 모두는 복수의 다이들을 포함하는, IC 패키지.

#### 청구항 11

집적 회로(IC) 패키지를 제조하기 위한 방법으로서,

배면 표면, 상부 표면 및 상기 상부 표면 내에 배치되는 공동을 갖는 제1 기판을 제공하는 단계로서, 상기 공동은 전면 표면을 한정하는 바닥을 갖는, 상기 제1 기판을 제공하는 단계;

상기 전면 및 배면 표면들의 각각의 표면들 상에 전기전도성 접점들을 형성하는 단계;

상기 제1 기판을 관통하고 상기 전면 및 배면 표면들 상에 각각 배치되는 상기 전기전도성 접점들 중 선택된 접점들을 서로 상호접속시키는 복수의 전기전도성 요소들을 형성하는 단계;

상기 공동 내에 IC를 포함하는 제1 다이를 배치하고 상기 제1 다이를 상기 전면 표면 상에 배치되는 상기 전기 전도성 접점들 중 대응하는 접점들에 전기전도성으로 결합시키는 단계;

제2 기판의 저부 표면을 상기 제1 기판의 상기 상부 표면에 밀봉식으로 부착하는 단계; 및

상기 제1 다이를 봉지하도록 상기 공동 내에 유전체 재료를 주입하는 단계

를 포함하는, 방법.

### 청구항 12

제11항에 있어서, 상기 IC 패키지의 최종 두께를 감소시키기 위해 상기 제1 다이의 상부 표면 및 상기 제1 기판의 상기 상부 표면을 에칭(etching)하는 단계를 추가로 포함하는, 방법.

#### 청구항 13

제11항에 있어서.

상기 제1 기판의 상기 배면 표면을 웨이퍼 척(wafer chuck)에 결합시키는 단계; 및

상기 유전체 재료, 상기 다이 및 상기 제1 기판의 상부 표면들을 서로 동일 평면 상에 있게 하고 상기 IC 패키지의 최종 두께를 감소시키기 위해, 상기 유전체 재료, 상기 다이 및 상기 제1 기판의 상부 표면들을 그라인딩 (grinding)하는 단계

를 추가로 포함하는, 방법.

### 청구항 14

제11항에 있어서,

상기 제2 기판의 상부 표면을 웨이퍼 척에 결합시키는 단계; 및

상기 IC 패키지의 최종 두께를 감소시키기 위해 상기 제1 기판의 상기 배면 표면을 그라인당하는 단계를 추가로 포함하는, 방법.

#### 청구항 15

제11항에 있어서, 상기 전기전도성 요소들을 형성하는 상기 단계는 반응성 이온 에칭(reactive ion etching, RIE)을 포함하는, 방법.

#### 청구항 16

집적 회로(IC) 패키지로서,

배면 표면 및 전면 표면을 갖는 제1 기판;

상기 제1 기판을 관통하고 상기 전면 표면 및 상기 배면 표면 상에 각각 배치되는 전기전도성 접점들 중 선택된 접점들을 서로 결합시키는 복수의 전기전도성 요소들;

상기 전면 표면 상에 배치되는 상기 전기전도성 요소들 중 대응하는 요소들에 전기전도성으로 결합되는 IC를 포함하는 적어도 하나의 제1 다이;

상기 제1 기판의 상기 전면 표면에 밀봉식으로 부착되는 저부 표면 및 상기 제1 다이를 둘러싸는 관통-개구 (through-opening)를 갖는 제2 기판;

상기 제2 기판의 상부 표면에 밀봉식으로 부착되는 저부 표면을 갖는 제3 기판으로서, 상기 저부 표면 및 상기 관통-개구는 상기 제1 다이를 둘러싸는 제1 공동을 한정하는, 상기 제3 기판; 및

상기 제1 공동 내에 배치되어 상기 적어도 하나의 제1 다이를 봉지하는 유전체 재료

를 포함하는, IC 패키지.

#### 청구항 17

제16항에 있어서,

상기 제3 기판을 관통하고 상기 적어도 하나의 제1 다이의 상부 표면 및 상기 제3 기판의 상부 표면 상에 각각 배치되는 전기전도성 접점들 중 선택된 접점들을 서로 결합시키는 복수의 전기전도성 요소들;

상기 제3 기판의 상기 상부 표면 상에 배치되는 상기 전기전도성 접점들 중 대응하는 접점들에 전기전도성으로 결합되는 IC를 포함하는 적어도 하나의 제2 다이; 및

상기 적어도 하나의 제2 다이를 봉지하는 유전체 재료

를 추가로 포함하는, IC 패키지.

#### 청구항 18

제17항에 있어서,

상기 제3 기판은 상기 제3 기판의 상기 저부 표면 내에 제2 공동을 포함하고,

상기 적어도 하나의 제2 다이 및 상기 유전체 재료는 상기 제2 공동 내에 배치되는, IC 패키지.

## 청구항 19

제18항에 있어서, 상기 유전체 재료는 무기 재료를 포함하는, IC 패키지.

#### 청구항 20

제17항에 있어서, 상기 제1 기판의 상기 전면 표면, 상기 제1 기판의 상기 배면 표면 및/또는 상기 제3 기판의 상기 상부 표면 중 적어도 하나 상에 배치되어 그 상에 각각 배치되는 상기 전기전도성 접점들 중 선택된 접점들을 서로 결합시키는 전기전도성 재배선 층(RDL)을 추가로 포함하는, IC 패키지.

#### 청구항 21

제17항에 있어서, 상기 적어도 하나의 제1 다이 및 상기 적어도 하나의 제2 다이 중 적어도 하나는 솔더 범프들에 의해 상기 전기전도성 접점들 중 대응하는 접점들에 전기전도성으로 결합되는, IC 패키지.

#### 청구항 22

집적 회로(IC) 패키지로서,

배면 표면 및 전면 표면을 갖는 제1 기판으로서, 상기 배면 및 전면 표면들 각각은 그 상에 각각 배치되는 관련된 복수의 전기전도성 접점들을 갖는, 상기 제1 기판;

상기 제1 기판을 관통하고 상기 전면 표면 및 상기 배면 표면 상에 각각 배치되는 상기 관련된 전기전도성 접점들 중 선택된 접점들을 서로 결합시키는 복수의 전기전도성 요소들;

상기 전면 표면 상에 배치되는 상기 전기전도성 접점들 중 대응하는 접점들에 전기전도성으로 결합되는 IC를 포함하는 제1 다이;

공동이 그의 저부 표면 내에 배치되는 제2 기판으로서, 상기 저부 표면은 상기 공동이 상기 제1 다이를 둘러싸도록 상기 제1 기판의 상기 전면 표면에 밀봉식으로 부착되는, 상기 제2 기판; 및

상기 공동 내에 배치되어 상기 제1 다이를 봉지하는 유전체 재료

를 포함하는, IC 패키지.

#### 청구항 23

제22항에 있어서, 상기 제1 기판의 상기 전면 표면 상에 배치되어 그 상에 배치되는 상기 전기전도성 접점들 중 선택된 접점들을 서로 결합시키는 전기전도성 재배선 충(RDL)을 추가로 포함하는, IC 패키지.

## 청구항 24

제22항에 있어서, 상기 유전체 재료는 무기 재료를 포함하는, IC 패키지.

#### 발명의 설명

#### 기술분야

#### [0001] 관련 출원

[0002] 본 출원은 그 전체 개시 내용이 본 명세서에 참고로 포함되는, 2014년 6월 4일자로 출원된 미국 가출원 제 62/007,758호의 이익을 주장한다.

### [0003] <u>기술분야</u>

[0004] 본 출원은 일반적으로 집적 회로(integrated circuit, IC) 패키지(package) 및 이를 제조하기 위한 웨이퍼 스케일(wafer scale) 방법에, 그리고 특히 통합된 인터포저(integrated interposer)(ITP)를 사용하여 2차원(2D) 및 3차원(3D) IC 패키지를 제조하는 것에 관한 것이다.

#### 배경기술

[0005] 최근에, 다수의 성능 목표, 예컨대 특히 보다 높은 신호 전파, 보다 낮은 전력 소비, 보다 낮은 제조 비용, 감소된 폼 팩터(form factor)를 달성하기 위해 반도체 칩(semiconductor chip)의 크기가 극적으로 축소되었다. 반도체 산업이 점점 더 작은 공간에 보다 많은 기능성을 채우기 위해 노력하면서, 몇몇은, 처리와 조립에 있어서 새로운 획기적인 기술 없이는, 잘 알려진 "무어의 법칙(Moore's law)", 즉 조밀한 집적 회로 내의 트랜지스터(transistor)의 수가 컴퓨팅 하드웨어의 역사에 걸쳐 대략 2년마다 두 배로 되는 것이 들어맞는 것이 중단될수 있음을 제안하였다. 수직 통합, 즉, 3차원 집적 회로("3D IC" 또는 "3D") 패키징이 상기 목표를 달성하기

위한 보다 유망한 기술 중 하나로 부상했다.

- [0006] 그러나, 3D IC 패키징은 설계자와 제조자에게 다수의 난제를 제기한다. 예를 들어, 3D IC 조립의 현재 추세는 얇은 인터포저(ITP) 상으로 마이크로범프형 다이(microbumped die)를 조립하는 것이다. 그러나, 비교적 얇은 ITP의 제조 및 조립은 다수의 문제를 야기할 수 있다. 그 중 하나는 ITP를 원하는 두께로 얇게 만들기 위해, ITP 웨이퍼는 전형적으로 박화(thinning) 및 후속 처리 동안, 임시 접착제, 전형적으로 저-용융-온도 중합체로 "캐리어(carrier)" 상에 실장된다는 것이다. 접착제의 비교적 낮은 용융 온도는 소위 "배면" 처리에서 사용될 수 있는 전체 최대 온도를 제한한다. 또한 분리 공정 및 관련 웨이퍼 취급 동안 웨이퍼 파손이 증가된다. 다른 문제는 조립 동안 발생할 수 있는 힘(warpage) 문제인데, 그 이유는 휘어진 ITP 다이에 마이크로범프를 접속시키는 것은 매우 어려울 뿐 아니라, 힘은 솔더 범프(solder bump) 및 기능성 다이에 응력을 부과하여 장기 신뢰성 문제를 일으키기 때문이다.

- [0007] 따라서, 종래 기술의 전술한 그리고 다른 문제를 극복하는 2D 및 3D IC 설계 및 제조 방법에 대한 오랫동안 느껴왔지만 아직 충족되지 않은 필요성이 존재한다.

#### 발명의 내용

- [0008] 본 개시 내용의 실시예에 따르면, 통합된 ITP들을 사용하는 신규한 2D 및 3D IC 패키지들이 이들을 제조하는 방법과 함께 제공된다.

- [0009] 예시적인 일 실시예에서, 2D IC 패키지는 배면 표면 및 공동(cavity)이 그 내부에 배치되는 상부 표면을 갖는 제1 기판(substrate)을 포함한다. 공동은 전면 표면을 한정하는 바닥(floor)을 갖는다. 복수의 제1 전기전도 성 접점(electroconductive contact)들이 전면 표면 상에 배치되고, 복수의 제2 전기전도성 접점들이 배면 표면 상에 배치된다. 복수의 제1 전기전도성 요소들이 제1 기판을 관통하고, 제1 및 제2 전기전도성 접점들 중 선택된 접점들을 서로 결합시킨다. IC를 포함하는 제1 다이가 제1 전기전도성 접점들 중 대응하는 접점들에 전기전도성으로 결합된다. 제2 기판이 제1 기판의 상부 표면에 밀봉식으로 부착되는 저부 표면을 갖고, 제1 다이를 봉지(encapsulate)하도록 공동 내에 유전체 재료(dielectric material)가 배치된다. 유전체 재료는 무기 재료 (inorganic material)를 포함할 수 있다.

- [0010] 다른 예시적인 실시예에서, 전술한 2D IC 패키지는, 제1 다이의 상부 표면 상에 배치되는 복수의 제3 전기전도 성 접점들, 제2 기판의 상부 표면 상에 배치되는 복수의 제4 전기전도성 접점들, 및 제2 기판을 관통하고 제3 및 제4 전기전도성 접점들 중 선택된 접점들을 서로 결합시키는 복수의 제2 전기전도성 요소들을 포함하는 3D IC 패키지를 제조하기 위한 기초로서 사용될 수 있다. IC를 포함하는 제2 다이가 제4 전기전도성 접점들 중 대응하는 접점들에 전기전도성으로 결합되고, 저부 표면을 갖는 커버(cover)가 제2 다이를 둘러싸도록 제2 기판의 상부 표면에 밀봉식으로 부착된다.

- [0011] 본 발명의 범주는 본 섹션에 참고로 포함되는, 이하에 첨부된 청구범위에 의해 한정된다. 통합된 ITP를 사용하여 신규한 2D 및 3D IC 패키지를 제조하기 위한 신규한 방법의 특징 및 이점의 더욱 완전한 이해가 아래에 제시되는 그의 일부 예시적인 실시예의 상세한 설명의 고려에 의해, 특히 그러한 고려가 유사한 도면 부호가 그의 도면들 중 하나 이상에 예시되는 유사한 요소를 식별하기 위해 사용되는, 아래에 간략히 기술되는 첨부 도면들의 도면과 함께 이루어지면, 당업자에게 제공될 것이다.

#### 도면의 간단한 설명

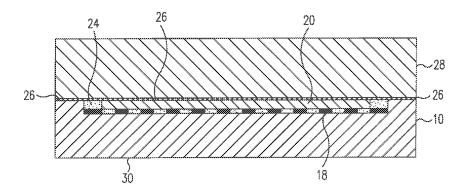

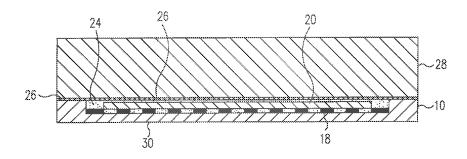

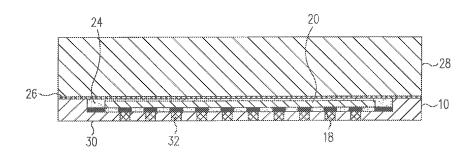

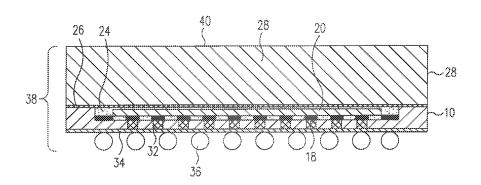

- [0012] 도 1 내지 도 30은 본 발명에 따른 2D 및 3D IC 패키지의 예시적인 실시예를 제조하기 위한 웨이퍼 스케일 방법 의 예시적인 실시예에 수반되는 순차적인 단계를 예시하는, 하나 이상의 웨이퍼의 부분들의 부분 단면도로서,

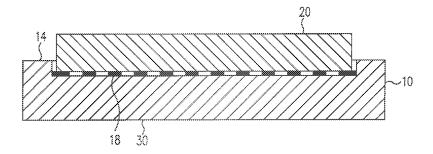

- 도 1은 제1 기판을 한정하는 웨이퍼의 일부분의 단면도.

- 도 2는 그의 상부 표면 내에 배치되는 공동을 도시하는, 도 1의 기판의 단면도.

- 도 3은 공동의 바닥 상에 배치되는 복수의 전기전도성 접점을 도시하는, 도 2의 기판의 단면도.

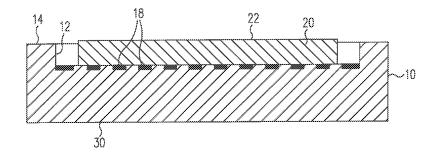

- 도 4는 전기전도성 접점들 중 대응하는 접점에 전기전도성으로 결합되는 IC를 포함하는 제1 다이를 도시하는, 도 3의 기판의 단면도.

- 도 5는 IC 패키지 두께를 감소시키기 위해 기판 및 다이의 상부 표면에 박화 공정이 적용된 후에 도시된, 도 4의 기판 및 다이의 단면도.

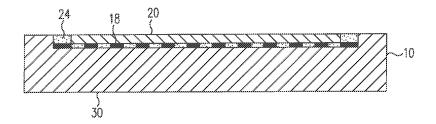

도 6은 기판, 공동 내에 배치되는 다이 및 유전체 재료의 상부 표면을 서로 동일 평면 상에 있게 하기 위한, 그리고 IC 패키지 두께를 감소시키기 위한 평탄화 공정 후에 도시된, 도 5의 기판 및 다이의 단면도.

도 7은 그의 평탄화된 상부 표면 상에 침착되는 접합 재료의 층을 도시하는, 도 6의 기판, 다이 및 유전체 재료의 단면도.

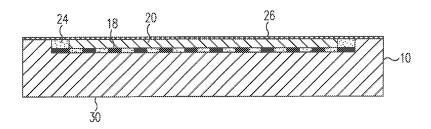

도 8은 제1 기판의 적어도 상부 표면에 밀봉식으로 부착되는 저부 표면을 갖는 제2 기판을 도시하는, 도 7의 기판, 다이 및 접합 재료의 단면도.

도 9는 IC 패키지 두께를 감소시키기 위해 제1 기판의 배면 표면에 박화 공정을 적용한 후에 도시된, 도 8의 기판 및 다이의 단면도.

도 10은 제1 기판을 관통하고 공동의 바닥 상의 전기전도성 접점들 중 선택된 접점에 결합되는 상부 단부를 갖는 복수의 전기전도성 요소를 도시하는, 도 9의 기판 및 다이의 단면도.

도 11은 제1 기판의 배면 표면 상에 배치되는 전기전도성 재배선 층(redistribution layer, RDL) 및 RDL에 의해 전기전도성 요소들 중 선택된 요소의 하부 단부에 각각 결합되는 복수의 전기전도성 솔더 범프를 도시하는, 도 10의 기판 및 다이의 단면도.

도 12는 IC 패키지 두께를 감소시키기 위해 제2 기판의 상부 표면에 박화 공정을 적용한 후에 도시된, 도 11의 기판 및 다이의 단면도.

도 13은 공동의 바닥 상의 전기전도성 접점들 중 대응하는 접점에 전기전도성으로 결합되는 복수의 제1 다이를 도시하는 것을 제외하고는, 도 11과 유사한 단면도.

도 14는 공동의 바닥 상에 배치되고 그 상에 배치되는 전기전도성 접점들 중 선택된 접점을 서로 결합시키는 전기전도성 재배선 층(RDL)을 도시하는 것을 제외하고는, 도 3과 유사한 단면도.

도 15는 그 내부에 배치되는 도 14의 RDL을 도시하는 것을 제외하고는, 도 12와 유사한 단면도.

도 16은 솔러 범프가 없는 것을 제외하고는, 도 12와 유사한 단면도.

도 17은 제2 기판을 관통하고 제1 다이의 상부 표면 상에 배치되는 복수의 전기전도성 접점들 중 선택된 접점에 각각 결합되는 하부 단부를 갖는 복수의 제2 전기전도성 요소를 도시하는, 도 16의 기판의 단면도.

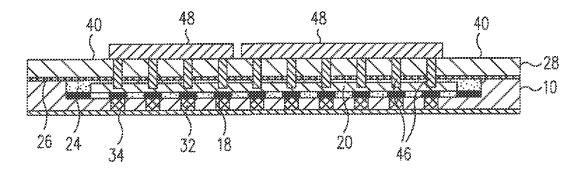

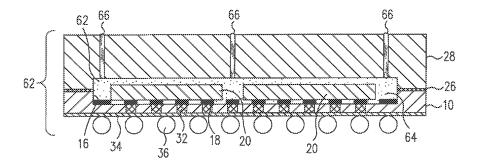

도 18은 제2 전기전도성 요소들 중 대응하는 요소의 상부 단부에 전기전도성으로 각각 결합되는 복수의 제2 IC 다이를 도시하는, 도 17의 기판 및 다이의 단면도.

도 19a는 공동이 그 내부에 배치되는 저부 표면을 갖는 제3 기판을 도시하는, 도 18의 기판 및 다이의 단면도로서, 저부 표면은 제2 기판의 상부 표면에 밀봉식으로 부착되어, 제2 다이가 공동 내에 배치되고 공동 내에 배치되는 유전체 재료가 제2 다이를 봉지하는 도면.

도 19b는 제2 기판이 공동이 그 내부에 배치되는 저부 표면을 갖는 것을 제외하고는, 도 13과 유사한 단면도로 서, 저부 표면은 제1 기판의 상부 표면에 밀봉식으로 부착되어, 기판의 각각의 공동이 조합되어 보다 큰 공동을 형성하고, 보다 큰 공동 내에 복수의 제1 다이가 배치되고, 보다 큰 공동 내에 배치되는 유전체 재료가 제1 다이를 봉지하는 도면.

도 20은 그의 전면 표면 상에 배치되는 복수의 전기전도성 접점을 도시하는, 본 발명에 따른 제1 기판의 대안적 인 실시예를 한정하는 웨이퍼의 일부분의 단면도.

도 21은 그것을 통해 연장되는 개구를 갖는 제2 기판의 대안적인 실시예를 한정하는 웨이퍼의 일부분의 단면도.

도 22는 제2 기판의 저부 표면이 공동을 한정하도록 제1 기판의 상부 표면에 접합된 후에 도시된, 도 20 및 도 21의 제1 및 제2 기판의 단면도.

도 23은 공동 내에 배치되는 IC를 포함하고 제1 기판의 전면 표면 상의 전기전도성 접점들 중 대응하는 접점에 전기전도성으로 결합되는 제1 다이를 도시하는, 도 22의 기판의 단면도.

도 24는 IC 패키지 두께를 감소시키기 위해 제2 기판 및 다이의 상부 표면에 박화 공정이 적용된 후에 도시된, 도 23의 기판 및 다이의 단면도.

도 25는 기판, 공동 내에 배치되는 다이 및 유전체 재료의 상부 표면을 서로 동일 평면 상에 있게 하기 위한,

그리고 IC 패키지 두께를 감소시키기 위한 평탄화 공정 후에 도시된, 도 24의 기판 및 다이의 단면도.

도 26은 그의 평탄화된 상부 표면 상에 침착되는 접합 재료의 층을 도시하는, 도 25의 기판, 다이 및 유전체 재료의 단면도.

도 27은 제2 기판의 적어도 상부 표면에 밀봉식으로 부착되는 저부 표면을 갖는 제3 기판을 도시하는, 도 26의 기판 및 다이의 단면도.

도 28은 IC 패키지 두께를 감소시키기 위해 제1 기판의 배면 표면에 박화 공정을 적용한 후에 도시된, 도 27의 기판 및 다이의 단면도.

도 29는 제1 기판을 관통하고 공동의 바닥 상의 전기전도성 접점들 중 선택된 접점에 결합되는 상부 단부를 갖는 복수의 전기전도성 요소를 도시하는, 도 28의 기판 및 다이의 단면도.

도 30은 제1 기판의 배면 표면 상에 배치되는 전기전도성 재배선 층(RDL) 및 전기전도성 요소들 중 선택된 요소의 하부 단부에 각각 결합되는 복수의 전기전도성 솔더 범프를 도시하는, 도 29의 기판 및 다이의 단면도.

### 발명을 실시하기 위한 구체적인 내용

- [0013] 본 개시 내용에 따르면, 2D 및 3D 집적 회로 패키지의 예시적인 실시예가, 그들을 통합된 ITP를 사용하여 제조하기 위한 방법과 함께 제공된다.

- [0014] 집적 회로(IC) 패키지의 "웨이퍼 레벨(wafer level)" 또는 "웨이퍼 스케일" 제조가 생성되는 패키지의 크기와 비용의 수반되는 감소와 함께, 주로 그러한 제조 기술이 제공하는 규모의 경제(economy of scale)로 인해, 최근에 확산되었다. 그러한 IC 패키지 및 그들을 제조하기 위한 방법의 예가 예컨대, 그 전체 개시 내용이 본 명세서에 참고로 포함되는, 2014년 3월 14일자로 출원된, 발명의 명칭이 "공동을 가진 기판에 의해 보호되는 집적회로 및 제조 방법(Integrated Circuits Protected by Substrates with Cavities, and Methods of Manufacture)"인, 에이치. 센(H. Shen) 등에 의한 공동 소유의 미국 특허 출원 제14/214,365호에서 확인될 수있다.

- [0015] 많은 가능한 실시예들 중 단지 하나에서, 그러한 패키지는 다수의 유사한 패키지를 포함하는 웨이퍼 또는 2개이상의 정렬된 웨이퍼의 샌드위치(sandwich)로부터 커팅되거나 "개별화(singulated)"될 수 있고, 각각 하나 이상의 집적 회로(IC)를 포함하는 하나 이상의 반도체 다이, 칩 또는 적충된 다이(패키징되거나 패키징되지 않을 수 있음)가 그 상에 실장되는 상부 표면을 갖는, 때때로 "인터포저"(ITP) 웨이퍼로 지칭되는 적어도 하나의 배선 기판 웨이퍼(wiring substrate wafer)의 일부분을 포함할 수 있다. ITP는 그의 상부 표면, 그의 하부 표면, 및/또는 그의 상부 표면과 하부 표면의 중간 상에, 예컨대 "재배선 층"(RDL)의 형태로, 전기전도성 트레이스(trace)의 패턴을 포함할 수 있으며, 그것에 IC가 다양하게 서로 그리고/또는 다른 구성요소에 전기전도성으로 접속된다. ITP는 또한 예컨대, 그 각각의 전체 개시 내용이 본 명세서에 참고로 포함되는, 공동 소유의 미국 특허 출원들인, 2014년 5월 2일자로 출원된 엘. 왕(L. Wang) 등에 의한 제14/268,899호 및 2014년 6월 13일자로 출원된 엘. 왕 등에 의한 제14/304,535호에 기술된 바와 같이, 그의 표면 상에 또는 그의 두께 내에 배치되는 저항기(resistor), 커패시터(capacitor), 인덕터(inductor) 등과 같은 개별 수동 전기 구성요소를 실장하고/하거나 포함할 수 있다.

- [0016] 규소-관통 "비아"(through-silicon "via", TSV)를 사용하는 규소 ITP는 다이가 적충되고 수직으로 전기전도성으로 접속되어 단일 디바이스로서 기능하는 3D IC 기술 발전의 핵심 구성요소가 될 수 있다. 전형적인 TSV 제조 공정은 규소 웨이퍼 내의 관통-구멍(through-hole) 또는 "비아"의 깊은 반응성 이온 에칭(deep reactive ion etching), 비아 내측의 장벽 및 시드 층(seed layer)의 화학적 증착(chemical vapor deposition, CVD) 또는 물리적 증착(physical vapor deposition, PVD), 및 전기전도성 재료로 비아를 충전하기 위한, 예컨대 구리(Cu), 텅스텐(W) 또는 다결정 규소(폴리실리콘(polysilicon))의 전기화학적 침착(electrochemical deposition, ECD)을 수반할 수 있다.

- [0017] 패키징된 디바이스의 속도를 증가시키기 위해서는, 신호 전송 라인이 매우 짧게 만들어져야 한다. 3D IC 조립의 현재 추세는, 예를 들어 두께가 25 내지 100 미크론 또는 마이크로미터(μm)(1 μm = 1×10 미터) 범위 내의 얇은 ITP 상으로 마이크로범프형 다이를 조립하는 것이다. 그러나, 그러한 얇은 ITP의 제조 및 조립은 몇가지 문제를 야기할 수 있다. 그 중 하나는 ITP를 원하는 두께로 얇게 만들기 위해, ITP 웨이퍼는 전형적으로 박화 및 후속 처리 동안, 임시 접착제, 전형적으로 저-용융-온도 중합체로 캐리어 상에 실장된다는 것이다. 접

착제의 낮은 용융 온도는 배면 처리에서 사용될 수 있는 전체 온도를 불리하게 제한한다. 또한 분리 공정 및 후속 웨이퍼 취급 동안 웨이퍼 파손의 가능성이 증가된다. 얇은 ITP로 인해 발생할 수 있는 다른 문제는 조립 동안의 휨 문제인데, 그 이유는 휘어진 ITP 다이 상에 마이크로범프를 접속시키는 것은 매우 어려울 뿐 아니라, 휨은 사용 동안 솔더 범프 및 기능성 다이에 응력을 부과하여 장기 신뢰성 문제를 일으키기 때문이다.

- [0018] 연구 및 개발을 통해, 상기 얇은-웨이퍼 취급 및 휨 문제는, 통상적인 공정에서 사용되는 임시 캐리어와 달리, 캐리어 웨이퍼(또는 그의 관련된 부분)가 최종 IC 패키지의 기계적 구조의 통합된 부분이 되는 그러한 캐리어 웨이퍼의 이용에 의해 성공적으로 해결될 수 있는 것으로 밝혀졌다. 따라서 기능성 다이는 전체-두께(full-thickness) ITP 웨이퍼에 부착된다. 웨이퍼 대 웨이퍼 접합을 사용하여, 캐리어 웨이퍼 또는 그의 관련된 부분은 기능성 다이를 완전히 둘러싸도록 영구적으로 ITP에 부착된다. 캐리어 웨이퍼는 ITP 웨이퍼의 후속 박화 공정 동안 필요한 지지 및 구조를 제공하여, 웨이퍼를 저-용융-온도 접착제를 사용하여 캐리어 웨이퍼에 실장할 필요가 없다. 캐리어 웨이퍼 및 ITP 웨이퍼는, 통상적인 다이 부착 및 성형 공정과 대조적으로, 처리 후에, 캐리어 및 ITP 웨이퍼의 각각의 열 팽창 계수(coefficient of thermal expansion, CTE)의 부정합으로 인한 응력이 거의 없거나 전혀 없도록 열적으로 정합된다.

- [0019] 전술한 바에 따르면, 도 1 내지 도 19a는 본 개시 내용에 따른 2D, 2.5D 및/또는 3D IC 패키지를 제조하기 위한 웨이퍼 레벨 방법의 제1 예시적인 실시예에 관련된 순차적인 단계를, 그에 의해 생성되는 IC 패키지의, 그것이 웨이퍼 샌드위치로부터 개별화된 후의 예시적인 실시예와 함께 예시하는, 하나 이상의 웨이퍼의 부분들의 부분 단면도이다.

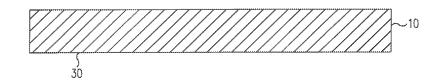

- [0020] 도 1은 제1 기판(10)을 한정하는 전체-두께 웨이퍼의 일부분의 단면도이다. 도 1 및 후속 도면에서는 웨이퍼의 단지 일부분, 예컨대 단일 최종 IC 패키지와 관련된, 즉 개별화 후의 제1 기판(10)을 한정하는 부분만이 도시되고 그에 적용되는 공정과 관련하여 기술되지만, 웨이퍼 레벨 제조에서, 그들 공정은 웨이퍼 샌드위치로부터 개별 패키지의 개별화 전에, 동시에 또는 순차적으로, 전체 웨이퍼의 다른 인접한 부분에 또한 적용된다는 것이 이해되어야 한다.

- [0021] 웨이퍼는 잘 알려진 포토리소그래피(photolithography) 제조 기술을 따르고, 예컨대 그에 부착되는 하나 이상의 규소 IC 다이의 것과 정합되는 CTE를 갖는 반도체 재료, 예컨대 단결정 규소를 포함하는 매우 다양한 적합한 재료를 포함할 수 있다. 대안적으로 또는 추가적으로, 유리, 금속 또는 다른 적합한 재료와 같은 다른 재료가 이용되거나 포함될 수 있다.

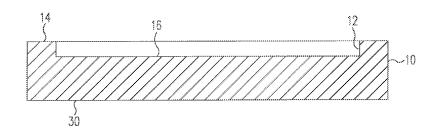

- [0022] 도 2에 예시된 바와 같이, 2D 또는 3D IC 패키지를 제조하기 위한 제1 예시적인 방법의 제1 단계는 기판(10)의 상부 표면(14) 내에 공동(12)을 형성하는 것을 포함할 수 있다. 공동(12)은 전면 표면(16)을 한정하는 바닥을 갖는다. 많은 가능한 실시예들 중 단지 하나에서, 공동(12)은 예컨대 50 내지 500 μm의 깊이를 가질 수 있고, 하나 이상의 알려진 에칭 기술, 예컨대 반응성 이온 에칭(RIE)을 사용하여 형성될 수 있다.

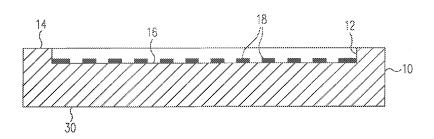

- [0023] 도 3은 제1 방법의 다음 단계인, 기판(10)의 전면 표면(16) 상에 배치되는 복수의 전기전도성 접점(18)의 형성을 도시하는, 도 2의 기판의 단면도이다. 이는 전면 표면(16) 상에 절연체, 예컨대 이산화규소(SiO<sub>2</sub>)의 얇은 층을 침착 및 패턴화하고, 이어서 절연체 층 상에, 예를 들어 Cu 증발 기술, 또는 무전해 니켈(Ni) 침지 금 (Au)(ENIG) 도금 기술을 사용하여 금속, 예컨대 구리(Cu)를 침착 및 패턴화함으로써 달성될 수 있다.

- [0024] 도 4에 예시된 바와 같이, 전기전도성 접점(18)이 상면 표면(16) 상에 한정된 후에, 적어도 하나의 IC를 포함하는 제1 다이(20)가 공동(12) 내에 배치되고 접점들(18) 중 대응하는 접점에 전기전도성으로 결합된다. 예를 들어, 일 실시예에서, 다이(20)의 저부 면 상에 배치되는 전기전도성 접점(예시되지 않음)이 리플로우 솔더링 기술(reflow soldering)을 사용하여 접점들(18) 중 대향하는 접점에 결합될 수 있으며, 이 리플로우 솔더링 기술에서는 기판(10)과 다이(20) 상의 대향하는 접점들 사이에 배치되는 솔더 범프가 예컨대 오븐 내에서 먼저 용융되어 대향하는 접점들 둘 모두를 솔더로 습윤시키고 이어서 고형화되어 전기전도성 결합부가 되게 한다.

- [0025] 도 5에 예시된 바와 같이, 다이(20)가 기판(10)에 결합된 후, 기판(10)과 다이(20)의 상부 표면(14, 22)에 대해 동시에 박화 공정, 예컨대 추가 에칭 공정, 화학적 및/또는 기계적 폴리싱(polishing) 등이 수행되어 최종 IC 패키지의 두께를 감소시킬 수 있다. 도 6에 예시된 바와 같이, 기판(10)과 다이(20)가 원하는 두께로 얇게 된후에, 공동(12)이 예컨대 유전체 접합 재료(24), 예컨대 에폭시 수지로 충전되어 다이(20)를 공동(12) 내에 매립시킬 수 있는데, 즉 다이를 공동(12)의 내부 표면과 밀접하게 언더필링(underfill), 경화 및 결합시킬 수 있다. 추가적으로 또는 대안적으로, 공동의 적어도 일부분이, 그 전체 개시 내용이 본 명세서에 참고로 포함되는, 2014년 12월 4일자로 출원된 공동 소유의 가출원 제62/087,361호에 논의된 바와 같이, 산화물 또는

질화물과 같은, 열 전도성 재료 또는 무기 층으로 충전될 수 있다. 그러한 재료는 개선된 열 특성, CTE 정합 또는 둘 모두를 제공할 수 있다.

- [0026] 도 6에 예시된 바와 같이, 기판(10), 다이(20) 및 접합 재료(24)의 각각의 상부 표면이 이어서 예컨대 화학적 기계적 폴리싱(CMP) 기술을 사용하여 평탄화될 수 있어서, 기판(10), 공동(24) 내에 배치되는 다이(20) 및 접합 재료(24)의 상부 표면이 서로 동일 평면 상에 있게 된다. 이 단계에 이어서, 도 7에 예시된 바와 같이, 평탄화된 상부 표면 상으로 접합 재료의 층(26)이 침착될 수 있다. 당면하는 특정 응용에 따라, 접합 재료는, 예를들어 산화물, 예컨대 SiO<sub>2</sub>, 질화물, 금속, 벤조사이클로부텐(BCB), 열 계면 재료(thermal interface material, TIM), 접착제, 유리 프릿(glass frit) 등을 포함할 수 있다.

- [0027] 도 8에 예시된 바와 같이, 예컨대 규소를 포함하는, 예컨대 제2 또는 "커버" 웨이퍼의 일부분을 포함하는 제2 기판(28)의 저부 표면이 이어서 접합 재료의 층(26)을 사용하여 적어도 제1 기판(10) 및 일부 실시예에서 다이 (20) 및 접합 재료(24)의 평탄화된 상부 표면에 밀봉식으로 부착, 즉 접합된다. 상기한 바와 같이, 당면하는 응용에 따라, 수행되는 접합은 예를 들어 표면 접합, 예컨대 양극(anodic) 또는 융합(fusion) 접합, 금속 층간 접합, 예컨대 공융(eutectic), 열압착(thermocompression) 또는 솔더 접합, 또는 절연 층간 접합, 예컨대 유리 프릿 또는 접착제 접합을 포함할 수 있다. 또한, 제2 기판(28) 웨이퍼는 유리 패널 또는 다른 적합한 재료를 포함할 수 있다.

- [0028] 당업자가 이해할 바와 같이, 제2 기판(28)은 반드시 제2 웨이퍼의 일부분을 포함할 필요는 없다. 따라서, 대안적인 실시예에서, 접합 재료의 층(26)은 생략될 수 있고, 제2 기판(28)은 대신에 제1 기판(10), 다이(20) 및 접합 재료(24)의 평탄화된 상부 표면 위에 성형되는 중합체, 예컨대 에폭시 수지의 층을 포함할 수 있거나, 또 다른 실시예에서, TIM 층 또는 금속 층을 포함할 수 있다.

- [0029] 도 9에 예시된 바와 같이, 박화 공정, 예컨대 CMP 공정이 이어서 최종 IC 패키지 두께의 추가 감소를 위해 제1 기판(10)의 배면 표면(30)에 적용될 수 있다. 당업자가 알 수 있는 바와 같이, 이는 부분적으로는 제2 기판(28)의 상부 표면을 통상적인 진공 또는 정전기 웨이퍼 척(wafer chuck)에 클램핑(clamping)함으로써 달성될 수 있다. 배면 박화 공정 후에, 복수의 제1 전기전도성 요소(32)가 배면 표면(30) 내에 형성될 수 있다. 도 10에 예시된 바와 같이, 제1 전기전도성 요소(32)는, 예를 들어 제1 기판(30)을 관통하고 제1 기판(10)의 전면 표면(16) 상에 배치되는 전기전도성 접점들(18) 중 선택된 접점에 결합되는 상부 단부를 갖는 비아-라스트(vialast)-공정 TSV를 포함할 수 있다. 대안적으로, 다이(20)를 부착하기 전에 부분적인 TSV가 제공되고 도 9와 관련하여 상기 논의된 박화 공정에 의해 노출될 수 있는, 비아-퍼스트(via-first) 또는 비아-미들(via-middle) 공정이 채용될 수 있음을 알아야 한다.

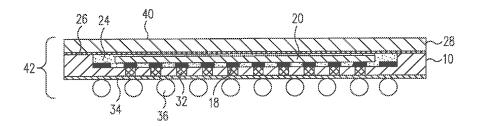

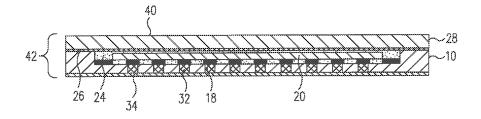

- [0030] 다른 박화 공정이 적용되지 않는다면, 도 11에 예시된 바와 같이, 방법은 제1 기판(10)의 배면 표면(30) 상에 언더-범프 금속화(under-bump metallization, UBM)의 형성을 계속할 수 있으며, 이는 그 상의 패턴화된 전기전도성 재배선 층(RDL)(34)의 형성과, 이어서 UMB들 중 대응하는 것 및/또는 RDL(34)에 각각 결합되는 복수의 전기전도성 솔더 범프(36)의 형성을 포함할 수 있다. UMB 및/또는 RDL(34)은 전기전도성 요소(18)의 하부 단부, UMB 및/또는 RDL(34)을 통상적인 인쇄 회로 보드(printed circuit board, PCB)의 전도성 트레이스와 같이 서로선택적으로 상호접속시키고, 예컨대 절연체, 예컨대 이산화규소(SiO2)의 얇은 층을 제1 기판(10)의 배면 표면(30) 상에 침착 및 패턴화하고(그 단계가 전기전도성 상호접속부(32)의 형성 동안 이미 구현되지 않았다면), 이어서 예컨대 Cu 증발 또는 ENIG 도금을 사용하여 표면 상에 금속, 예컨대 Cu를 침착 및 패턴화함으로써 달성될수 있다. 도 11은 웨이퍼 샌드위치로부터의 그의 개별화 후에 생성되는 2D IC 패키지(38)의 예시적인 실시예를예시한다.

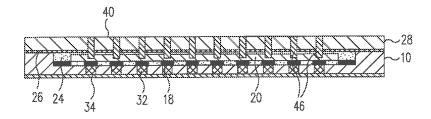

- [0031] 그러나, 최종 IC 패키지(38)를 추가로 얇게 하는 것이 바람직하다면, 전술한 "배면" 공정들 및 대응하는 특징부들 중 하나 이상은, 제2 기판(28)의 상부 표면(40)에 적용되는 것을 제외하고는, 도 9와 관련하여 전술된 제1 기판(10)의 배면 표면(30)에 적용되는 것과 유사한 상면 박화 작업을 위해 지연될 수 있으며, 그 동안에 제1 기판(10)의 배면 표면(30)은, 지연되는 특징부 없이, 통상적인 웨이퍼 척에 클램핑될 수 있다. 상기 지연된 특징부가 그에 부가되고 그것이 웨이퍼 샌드위치로부터 개별화된 후에 생성되는 실질적으로 보다 얇은 2D IC 패키지(42)가 도 12의 단면도에 예시되어 있다.

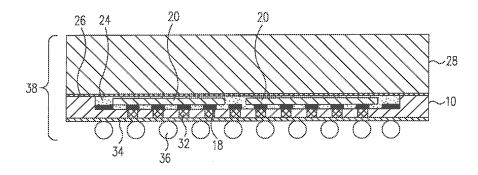

- [0032] 도 13에 예시된 바와 같이, 일부 실시예에서, 제1 다이(20)는 유리하게는 단일 다이(20)가 아니라, 제1 기판 (10)의 상면 표면(16) 상에 배치되는 전기전도성 접점들(18) 중 대응하는 접점에 전기전도성으로 결합되는 복수의 제1 다이(20)를 포함할 수 있다. 또한, 예시된 예시적인 실시예에서는 단일 다이(20)만이 도시되어 있지만, 도시된 단일 다이(20)는 수직으로 상호접속된 다이의 스택(stack), 즉 "다이 스택"을 나타낼 수 있음을 이해해

야 한다.

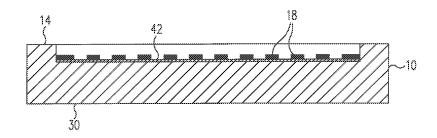

- [0033] 도 14는 RDL(42)이 또한 제1 기판(10)의 전면 표면(18) 상에 형성되고 그 상에 배치되는 전기전도성 접점들(18) 중 선택된 접점을 서로 결합시키는 데 사용될 수 있는 것을 제외하고는, 도 3과 유사한 단면도이다. 이 RDL(42)은 전기전도성 접점(18)이 형성된 직후, 전술된 제1 기판(10)의 배면 표면(30) 상의 RDL(34)에 대안적으로 또는 추가적으로, RDL(34)을 형성하는 데 사용된 동일한 재료 및 공정을 사용하여 형성될 수 있다. 상기 논의된 바와 같이, 비아-퍼스트 공정 또는 비아-미들 공정을 구현하는 경우, TSV는 TDL(42)의 형성 전에 제1 기판(10) 내에 부분적으로 형성될 수 있다.

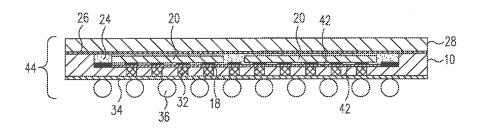

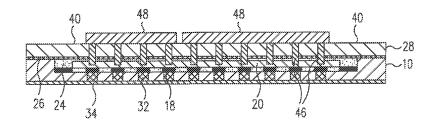

- [0034] 도 15는 그것이 도 13과 관련하여 상기 논의된 바와 같은 복수의 제1 다이(20) 및 도 14와 관련하여 상기 논의된 바와 같은 제2 RDL(42)을 포함한다는 것을 제외하고는, 도 12에 예시된 것과 유사한 소위 "2.5D" IC 패키지 (44)의 예시적인 실시예의 단면도이다.

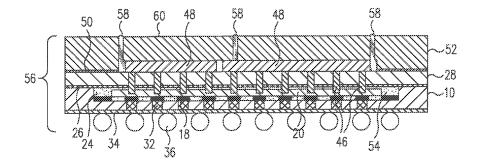

- [0035] 도 16은 도 12의 것과 유사하지만, 그의 배면 표면 상에 솔더 범프(36)가 형성되기 전에 도시된, IC 패키지(42)의 단면도이다. 도 17 내지 도 19a와 관련하여 아래에 논의되는 바와 같이, 이 초기 2D 패키지(42)는 3D IC 패키지(56)를 제조하기 위한 기초로서 사용될 수 있다. 따라서, 도 17에 예시된 바와 같이, 제1 예시적인 방법은 도 16에 예시된 단계로부터 계속해서, 도 10과 관련하여 상기 논의된 제1 전기전도성 요소(32)와 유사한 방식으로, 제2 기판(28)을 관통하고 제1 다이(20)의 상부 표면 상에 배치되는 복수의 전기전도성 접점들 중 선택된 접점에 각각 결합되는 하부 단부를 갖는 복수의 제2 전기전도성 요소(46), 예컨대 TSV를 형성할 수 있다.

- [0036] 도 18에 예시된 바와 같이, 그의 각각의 하부 표면 상에 배치되는 전기전도성 접점(예시되지 않음)을 각각 갖는 하나 이상의 제2 다이(48)(또는 다이 스택)가 도 4와 관련하여 상기 논의된 제1 다이(들)(20)를 접속시키는 데 사용되는 것과 유사한 솔더링 기술을 사용하여 제2 전기전도성 요소들(46) 중 대응하는 요소의 대향하는 상부 단부에 결합될 수 있다.

- [0037] 이 단계 후에, 도 7과 관련하여 상기 논의된 것과 유사한 방식으로, 제2 기판(28)의 상부 표면(40) 상으로 접합 재료의 층(50), 예컨대 산화물, 예컨대 SiO<sub>2</sub>, 금속, BCB, TIM, 접착제, 유리 프릿 등의 층이 침착될 수 있다. 도 19a에 예시된 바와 같이, 예컨대 규소로 제조된, 예컨대 제3 웨이퍼의 일부분을 포함하는 제3 기판(52)이 제 공된다. 제3 기판(52)은 공동(54)이 그 내부에 배치되는 저부 표면을 가질 수 있다. 이어서, 제3 기판(52)의 저부 표면은 제2 다이(48)가 공동(54) 내에 배치되도록 제2 기판(28)의 상부 표면(40)에 접합될 수 있다. 도 8 및 제1 기판(10)에 대한 제2 기판(28)의 접합과 관련하여 상기 논의된 바와 같이, 접합은 다양한 웨이퍼 접합 기술을 사용하여 달성될 수 있다.

- [0038] 도 19a에 예시된 특정한 예시적인 3D IC 패키지(56)에서, 제2 다이(48)는 유리하게는 IC 패키지(56) 내의 제2 다이(48)의 실장을 보강하고/하거나 패키지(10)를 둘러싸는 주변으로 다이들(48) 사이의 향상된 열 전달 경로를 제공하기 위해, 공동(54) 내에 배치되는 에폭시 또는 TIM과 같은 충전재(filler)로 봉지된다. 도 19a에 예시된 바와 같이, 가능한 일 실시예에서, 이는 공동(54)과 제3 기판(52)의 상부 표면(60) 사이에서 연장되는 하나 이 상의 채널(58)을 제3 기판(52) 내에 형성함으로써 달성될 수 있다. 충전재가 제3 기판(52)이 부착되기 전에 또는 부착된 후에 도입되는지에 따라, 충전재는 채널(58)을 통해 공동(54) 내로 주입되고/되거나 그로부터 빠져나 갈 수 있어, 공극(void)을 제한하고 가스 방출(outgassing) 등을 가능하게 한다. 상기 논의된 바와 같이, 산화물 충 또는 다른 무기 재료가 제3 기판(52) 내의 공동을 적어도 부분적으로 충전하기 위해 충전재를 첨가하기전에 다이(20) 상에 형성될 수 있다. 이는 필요한 충전재의 양을 감소시키고, 이는 충전된 공동의 유효 CTE를 낮출 수 있다.

- [0039] 도 8 및 제2 기판(28)과 관련하여 상기 논의된 바와 같이, 제3 기판(52)은 반드시 제2 웨이퍼의 일부분을 포함할 필요는 없다. 따라서, 대안적인 실시예에서, 접합 재료의 층(50)은 생략될 수 있고, 제3 기판(52)은 대신에 제2 기판(28) 및 제2 다이(48)의 상부 표면 위에 성형되는 중합체, 예컨대 에폭시 수지의 층을 포함할 수 있다.

- [0040] 도 19b는 그것이 제1 및 제2 접합된 기판(10, 28)과 복수의 제1 다이(20)를 포함한다는 점에서, 도 13의 2D 패키지(38)와 유사한 2D IC 패키지(62)의 단면도이다. 그러나, 도 19b에 예시된 바와 같이, IC 패키지(62)는 제1 기판(10)과 마찬가지로 제2 기판(20)이 또한 그의 저부 표면 내에 배치되는 공동(62)을 갖는다는 점에서 IC 패키지(38)와 상이하다. 제2 기판(28)의 저부 표면은, 2개의 기판(10, 28)의 각각의 공동(16, 62)이 조합되어 제1 다이(20)가 그 내부에 배치되는 단일의 보다 큰 공동(64)을 형성하도록 제1 기판(10)의 상부 표면에 접합된다. 또한, 도 19b의 실시예와 관련하여 상기 논의된 바와 같이, 제1 다이(20)는 유리하게는 제2 기판(28) 내에 형성되는 채널(66)을 통해 그리고 확대된 공동(64) 내로 재료를 주입함으로써 에폭시 또는 열 계면

재료와 같은 충전재로 봉지될 수 있다. 또한 상기 논의된 바와 같이, 공동은 또한 적어도 부분적으로 산화물 충과 같은 무기 재료로 충전될 수 있다. 따라서, 전술된 제1 예시적인 방법에 의해 생성되는 도 18b의 IC 패키지(62)는 보다 두꺼운 다이 또는 다이 스택을 위한, 또는 SOC(System On Chip) 디바이스를 위한 다중-공동 솔루션(multi-cavity solution)을 제공할 수 있다.

- [0041] 도 20 내지 도 30은 본 발명에 따른 2D, 2.5D 및/또는 3D IC 패키지를 제조하기 위한 웨이퍼 레벨 방법의 제2 예시적인 실시예에 관련된 순차적인 단계를, 그에 의해 생성되는 패키지의 예시적인 실시예와 함께 예시하는, 하나 이상의 웨이퍼의 부분들의 부분 단면도이다.

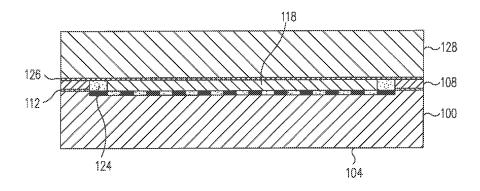

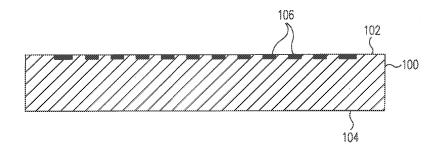

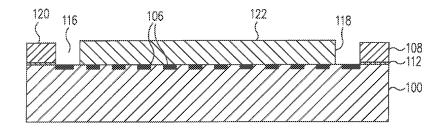

- [0042] 도 20은 복수의 전기전도성 접점(106)이 그 상에 형성되는 전면 표면(102), 및 배면 표면(104)을 갖는 제1 기판 (100)을 한정하는 전체-두께 웨이퍼의 일부분의 단면도이다. 따라서 도 20에 예시된 제1 기판(100)은, 이 예시 적인 실시예에서 기판(100)이 그의 상부 표면 내에 공동이 없다는 것을 제외하고는, 도 3과 관련하여 상기 논의된 제1 기판(10)과 유사하다. 이러한 차이를 제외하고, 기판(100)은 도 1 내지 도 3 및 기판(10)과 관련하여 상기 논의된 바와 동일한 재료 및 처리 단계를 사용하여 제조될 수 있다.

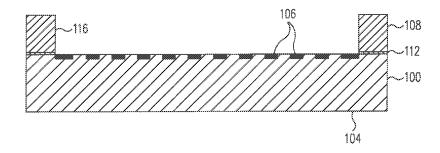

- [0043] 도 21은 윈도우 프레임(window frame)의 방식으로 그것을 통해 연장되는 개구(110)를 갖는 제2 기판(108)의 대 안적인 실시예를 한정하는 웨이퍼의 일부분의 단면도이다. 도 22에 예시된 바와 같이, 전기전도성 접점(106)을 둘러싸는 제1 기판(100)의 전면 표면(102)의 가장자리 영역 상에 접합 재료의 층(112)이 배치될 수 있고, 도 8, 도 19a 및 도 19b와 관련하여 상기 논의된 것과 유사한 방법을 사용하여 제1 공동(116)을 한정하기 위해 제1 기판(100)의 전면 표면(102)에 제2 기판(108)의 저부 표면(114)이 접합될 수 있다.

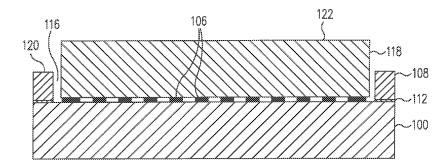

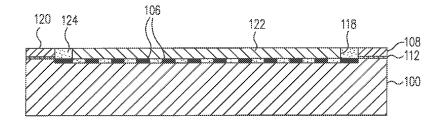

- [0044] 당업자가 인식할 바와 같이, 도 22의 실시예는 제1 실시예 및 도 3과 관련하여 상기 논의된 실시예의 것과 실질적으로 유사하고, 후속 처리는 제1 실시예와 관련하여 상기 논의된 것과 실질적으로 유사한 경로를 따를 수 있다. 따라서, 도 23에 예시된 바와 같이, IC를 포함하는 제1 다이(118)가 제1 공동(116) 내에 배치될 수 있고, 예를 들어 리플로우된 솔더 범프를 사용하여 제1 기판(100)의 상면 표면(102) 상에 배치되는 접점들(106) 중 대응하는 접점에 전기전도성으로 결합될 수 있다.

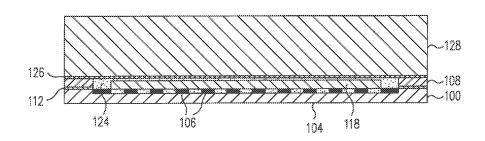

- [0045] 도 24에 예시된 바와 같이, 제1 다이(118)가 제1 기판(100)에 부착된 후, 제2 기판(108)과 다이(118)의 상부 표면(120, 122)에 대해 동시에 에칭 공정이 수행되어 최종 IC 패키지의 두께를 감소시킬 수 있다. 도 25에 예시된 바와 같이, 제2 기판(108)과 다이(118)가 원하는 두께로 얇게 된 후에, 제1 공동(116)이 유전체 접합 재료(124), 예컨대 에폭시 수지로 충전되어 다이(118)를 제1 공동(116) 내에서 강건한 방식으로 지지하고 보호할 수 있다. 상기 논의된 바와 같이, 공동(116)은 또한 산화물 층과 같은 무기 재료로 적어도 부분적으로 충전되어, 충전된 공동의 유효 CTE를 다이(118) 및 기판(100, 108)의 유효 CTE와 보다 잘 정합시킬 수 있다.

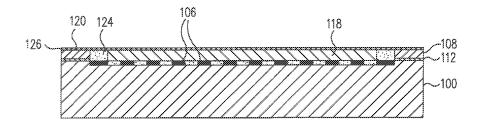

- [0046] 도 25에 예시된 바와 같이, 제2 기판(108), 다이(118) 및 접합 재료(124)의 각각의 상부 표면이 이어서 예컨대 CMP 공정을 사용하여 평탄화될 수 있어서, 제2 기판(108), 제1 공동(116) 내에 배치되는 제1 다이(118) 및 접합 재료(124)의 상부 표면이 서로 동일 평면 상에 배치된다. 이 단계에 이어서, 도 26에 예시된 바와 같이, 평탄 화된 표면 상으로 접합 재료의 층(126)이 침착될 수 있다. 상기한 바와 같이, 접합 재료는, 예를 들어 산화물, 예컨대 SiO2, 금속, 벤조사이클로부텐(BCB), 열 계면 재료(TIM), 접착제, 유리 프릿(glass frit) 등의 층을 포함할 수 있다.

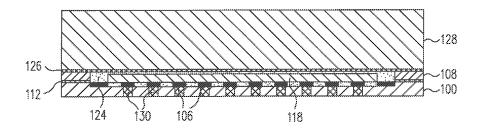

- [0047] 도 27에 예시된 바와 같이, 예컨대 규소를 포함하는, 예컨대 제3 또는 "커버" 웨이퍼의 일부분을 포함하는 제3 기판(128)의 저부 표면이 이어서 접합 재료의 층(26)을 사용하여 적어도 제2 기판(108) 및 일부 실시예에서 제1 다이(118) 및 접합 재료(124)의 평탄화된 상부 표면에 접합될 수 있다. 상기한 바와 같이, 당면하는 응용에 따라, 사용되는 접합 방법은 광범위한 알려진 웨이퍼 접합 기술을 포함할 수 있다.

- [0048] 그리고 상기한 바와 같이, 제3 기판(128)은 반드시 제3 웨이퍼의 일부분을 포함할 필요는 없다. 따라서, 대안 적인 실시예에서, 접합 재료의 층(126)은 생략될 수 있고, 제2 기판(128)은 대신에 제2 기판(108), 제1 다이 (20) 및 접합 재료(124)의 평탄화된 상부 표면 위에 성형되거나 형성되거나 접합되는 유리, 중합체, 예컨대 에 폭시 수지, 또는 금속의 층을 포함할 수 있다.

- [0049] 도 28에 예시된 바와 같이, 박화 공정, 예컨대 CMP 공정이 이어서 최종 IC 패키지 두께의 추가 감소를 위해 제1 기판(100)의 배면 표면(104)에 적용될 수 있다. 상기한 바와 같이, 이는 부분적으로는 제3 기판(128)의 상부 표면을 통상적인 진공 또는 정전기 웨이퍼 척에 클램핑함으로써 달성될 수 있다. 배면 박화 공정 후에, 복수의 제1 전기전도성 요소(130)가 배면 표면(104) 내에 형성될 수 있다. 도 30에 예시된 바와 같이, 제1 전기전도성 요소(32)는, 예컨대 제1 기판(100)을 관통하고 제1 다이(100)의 전면 표면(102) 상에 배치되는 전기전도성 접점

들(118) 중 선택된 접점에 결합되는 상부 단부를 갖는 비아-라스트-공정 TSV를 포함할 수 있다.

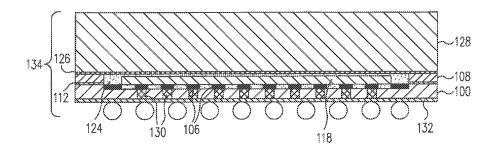

[0050] 다른 박화 공정이 적용되지 않는다면, 도 30에 예시된 바와 같이, 방법은 제1 기판(100)의 배면 표면(104) 상에 언더-범프 금속화(UBM)의 형성을 계속할 수 있으며, 이는 그 상의 패턴화된 전기전도성 재배선 층(RDL)(132)의 형성과, 이어서 UMB들 중 대응하는 것 및/또는 RDL(132)에 각각 결합되는 복수의 전기전도성 솔더 범프(36)의 형성을 포함할 수 있다. UMB 및/또는 RDL(132)은 전기전도성 요소(106)의 하부 단부, UMB 및/또는 RDL(132)을 서로 선택적으로 상호접속시키고, 도 15와 관련하여 상기 논의된 제1 실시예의 배면 표면 RDL(34)을 형성하는 데 사용되는 동일한 재료 및 공정을 사용하여 달성될 수 있다. 도 30은 웨이퍼 샌드위치로부터의 그의 개별화후에 생성되는 2D IC 패키지(134)의 예시적인 실시예를 예시한다.

[0051] 당업자가 인식할 바와 같이, 제1 공동(116)을 한정하는 데 사용되는 "윈도우 프레임" 제2 웨이퍼(108)를 제외하고, 도 30의 2D IC 패키지(134)는 도 11과 관련하여 상기 논의된 2D IC 패키지(38)와 실질적으로 유사하다. 따라서, 최종 IC 패키지 두께를 감소시키고, 대안적인 또는 추가적인 RDL을 형성하고/하거나 도 12 내지 도 19b와 관련하여 상기 논의된 단일 및/또는 복수의 제1 및 제2 다이를 사용하여 3D IC 패키지를 조립하는 데 사용되는 모든 동일한 재료 및 공정이 도 30의 실시예와 관련하여 동일하게 사용될 수 있으며, 따라서, 이들 대안적인 실시예에 대한 추가의 상세한 설명은 간결함을 위해 생략된다.

[0052] 전술한 상세한 설명을 고려하여, 본 개시 내용의 통합된 ITP를 가진 IC 패키지의 방법 및 재료에서 그리고 그에 대해 많은 변경, 대체 및 변형이 이루어질 수 있으며, 따라서 본 명세서에 예시되고 기술된 특정 실시예가 단지 그의 일부 예에 불과하기 때문에 본 개시 내용의 범주가 그러한 특정 실시예의 범주로 제한되지 않아야 하고 오히려 이하에 첨부된 청구범위와 그들의 기능적 등가물의 범주에 완전히 상응하여야 하는 것이 당업자에게 명백할 것이다.

#### 도면

### 도면1

### 도면2

## 도면5

# 도면6

# 도면9

# 도면10

# *도면13*

## 도면14

## 도면15

# 도면18

# 도면19a

# *도면19b*

## 도면21

# *도면22*

# 도면25

## 도면26

## 도면27