## UK Patent Application (19)GB (11)2571218

21.08.2019

(21) Application No: 1907335.2

(22) Date of Filing: 25.10.2017

Date Lodged: 24.05.2019

(30) Priority Data:

(31) 15346841 (32) 09.11.2016 (33) **US**

(86) International Application Data: PCT/IB2017/056618 En 25.10.2017

(87) International Publication Data: WO2018/087617 En 17.05.2018

(71) Applicant(s):

**International Business Machines Corporation** New Orchard Road, Armonk 10504, New York, **United States of America**

(72) Inventor(s):

Takeo Yasuda Kohji Hosokawa Masatoshi Ishii

(74) Agent and/or Address for Service:

**IBM United Kingdom Limited** Intellectual Property Law, Hursley Park, WINCHESTER, Hampshire, SO21 2JN, **United Kingdom**

(51) INT CL:

**G11C 11/54** (2006.01) G06N 3/063 (2006.01) G11C 11/24 (2006.01) G11C 11/56 (2006.01) G11C 13/00 (2006.01)

(56) Documents Cited:

US 5790461 A US 20150039547 A1 US 20140310220 A1

(58) Field of Search:

INT CL G06N, G11C Other: DWPI, USTXT, CNABS, CNTXT, CNKI, **EPODOC, WPI**

(54) Title of the Invention: Memory cell structure Abstract Title: Memory cell structure

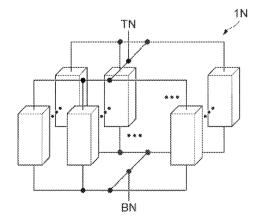

(57) A memory cell structure includes a synapse memory cell including plural cell components, each of the plural cell components including a unit cell, plural write lines arranged for writing a synapse state to the synapse memory cell, each of the plural write lines being used for writing one of a first set of a predetermined number of states to a corresponding cell component by writing one of a second set of the predetermined number of states to the unit cell included in the corresponding cell component, the first set depending on the second set and a number of the unit cell included in the corresponding cell component, and a read line arranged for reading the synapse state from the synapse memory cell, the read line being used for reading one of the first set of the predetermined number of states from all of the plural cell components simultaneously.