(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11) 特許番号

特許第6299760号 (P6299760)

(45) 発行日 平成30年3月28日(2018.3.28)

(24) 登録日 平成30年3月9日(2018.3.9)

(51) Int.Cl. F.1

**G11C** 13/00 (2006.01) G11C 13/00 464

G 1 1 C 13/00 2 3 O

請求項の数 9 (全 18 頁)

(21) 出願番号 特願2015-523854 (P2015-523854)

(86) (22) 出願日 平成26年6月17日 (2014.6.17)

(86) 国際出願番号 PCT/JP2014/003246

(87) 国際公開番号 W02014/208049 (87) 国際公開日 平成26年12月31日 (2014.12.31)

審査請求日 平成29年5月15日 (2017.5.15) (31) 優先権主張番号 特願2013-131263 (P2013-131263)

(32) 優先日 平成25年6月24日 (2013.6.24)

(33) 優先権主張国 日本国(JP)

(出願人による申告) 国等の委託研究の成果に係る特許 出願(平成23年度、独立行政法人新エネルギー・産業 技術総合開発機構委託研究「低炭素社会を実現する超低 電圧デバイスプロジェクト」、産業技術力強化法第19

条の適用を受ける特許出願)

||(73)特許権者 000004237

日本電気株式会社

東京都港区芝五丁目7番1号

|(74)代理人 100109313

弁理士 机 昌彦

(74)代理人 100124154

弁理士 下坂 直樹

||(72)発明者 多田 宗弘

東京都港区芝五丁目7番1号 日本電気株

式会社内

審査官 後藤 彰

最終頁に続く

## (54) 【発明の名称】スイッチング素子のプログラム方法

## (57)【特許請求の範囲】

## 【請求項1】

第1電極と、第2電極と、前記第1電極と前記第2電極との間に設けられ、前記第1電極と前記第2電極との間の電位差に応じて抵抗値Rが増減する抵抗変化膜と、を有するスイッチング素子のプログラム方法において、

第1のパルス電圧を前記第1電極あるいは前記第2電極に与えることで前記抵抗変化膜の抵抗値Rを増減させるプログラムをし、

前記抵抗値Rを測定し、前記測定された前記抵抗値Rが所望の値であるか否かを判定するベリファイをし、

前記抵抗値 R が所望の値でない場合に、前記抵抗値 R に基づいて前記第 1 のパルス電圧と同じ極性の第 2 のパルス電圧を、前記第 1 のパルス電圧と同じ電極に与える再プログラムを <u>し、</u>

前記再プログラムは、前記第 2 のパルス電圧のパルス幅と、前記第 2 のパルス電圧を与えたときの電流とを、予め得られた A 、 m 、 n から、抵抗値 R = A ・ I m ・ t n ( I は電流、 t はパルス幅)の式に基づいて決定する、

スイッチング素子のプログラム方法。

## 【請求項2】

前記抵抗変化膜は金属架橋型抵抗変化膜である、請求項 1 記載のスイッチング素子のプログラム方法。

【請求項3】

20

前記抵抗値 R は前記抵抗変化膜内の伝導物質の量に対応し、前記 R = A・I <sup>m</sup>・t <sup>n</sup>の式に基づいて決定される前記第 2 のパルス電圧は、前記抵抗変化膜内の、前記伝導物質の不足分を供給する、あるいは前記伝導物質の残留分を回収する、請求項 1 または 2 記載のスイッチング素子のプログラム方法。

## 【請求項4】

<u>前記第2のパルス電圧は前記第1のパルス電圧と同じである、請求項1または2記載のス</u>イッチング素子のプログラム方法。

## 【請求項5】

<u>前記再プログラムの後に、再度、前記ベリファイを行う、請求項1から4の内の1項記載</u>のスイッチング素子のプログラム方法。

【請求項6】

前記ベリファイは、前記第1のパルス電圧と同じ極性の電圧で前記抵抗値 R を測定する、 請求項1から5の内の1項記載のスイッチング素子のプログラム方法。

## 【請求項7】

前記抵抗変化膜は固体電解質を有する、請求項1から6の内の1項記載のスイッチング素 子のプログラム方法。

## 【請求項8】

<u>前記第1電極は銅を有する、請求項1から7の内の1項記載のスイッチング素子のプログ</u>ラム方法。

## 【請求項9】

<u>前記第2電極はルテニウムを有する、請求項1から8の内の1項記載のスイッチング素子</u>のプログラム方法。

【発明の詳細な説明】

【技術分野】

[0001]

本発明は、多層配線層の内部に不揮発な抵抗変化素子を有するスイッチング素子のプログラム方法に関する。

【背景技術】

[0002]

半導体デバイス、特に、シリコンデバイスは、Mooreの法則と呼ばれるスケーリング則に沿った微細化により、3年間で4倍という速度で集積化や低電力化が進められてきた。しかしながら、近年、MOSFET (Metal Oxide Semiconductor Field Effect Transistor)のゲート長は20nm以下となり、リソグラフィプロセスの高騰、すなわち、リソグラフィ装置価格とマスクセット価格の高騰が著しい。さらに、デバイス寸法の物理的な限界、すなわち、動作限界やばらつき限界により、これまでの速度でのスケーリングが不可能となってきた。そこで、スケーリング則とは異なる別のアプローチでのデバイス性能の改善が求められている。

[0003]

近年、ゲートアレイとスタンダードセルとの中間的な位置づけとしてFPGA(Field-Programmable Gate Array)と呼ばれる再書き換え可能なプログラマブルロジックデバイスが開発されている。FPGAは、顧客自身がチップの製造後に任意の回路構成を行うことを可能とする。すなわち、FPGAは、多層配線層の内部に抵抗変化素子を有し、顧客自身が任意に配線の電気的接続をできるようにしたものである。このようなFPGAを搭載した半導体装置を用いることで、回路の自由度を向上させることができるようになる。

## [0004]

抵抗変化素子としては、MRAM(Magnetoresistive Random Access Memory)、PRAM(Phase-change Random Access Memory)、ReRAM(Resistance Random Access Memory)、CBRAM(Conductive Bridge R

10

20

30

40

10

20

30

40

50

andom Access Memory)などに使用される抵抗変化素子が挙げられる

## [00005]

これらの中でReRAMに使用される抵抗変化素子は、2つの電極と、これらに挟まれた金属酸化物からなる抵抗変化膜とを有し、2つの電極間に電界を印加することで抵抗値が変化する性質を利用する。すなわち、2つの電極間に電界を印加することによって、抵抗変化膜の内部にフィラメントが生成されることで、2つの電極間には導電性パスが形成されて低抵抗化する。この状態をON状態とする。他方、前記の逆方向の電界を印加することで、フィラメントが消失することで、2つの電極間に形成されていた導電性パスが消失して高抵抗化する。この状態をOFF状態とする。印加する電界の方向を反転させることで、2つの電極間の抵抗値が大きく変化し、ON状態とOFF状態との間のスイッチングがなされる。

#### [0006]

R e R A M では、前記 O N 状態と O F F 状態との抵抗値の違いに応じて、抵抗変化素子を流れる電流が変化することを利用して、データを記憶する。データ書き込み時は、記憶したいデータに従って、 O F F 状態から O N 状態への遷移、あるいは、 O N 状態から O F F 状態への遷移を生じさせる電圧値と電流値とパルス幅を選択し、フィラメントの生成と消失、すなわち、導電性パスの形成と消失を行う。

## [0007]

R e R A M に使用される抵抗変化素子の一種は、イオン伝導体中における金属イオン移動と、電気化学反応による、金属イオンの還元による金属の析出と、金属の酸化による金属イオンの生成とを利用する。これにより、抵抗変化膜を挟む電極間の抵抗値を可逆的に変化させる不揮発性スイッチング素子が、非特許文献1に開示されている。この不揮発性スイッチング素子を用いたR A M は C B R A M と呼ばれている。

#### [00008]

非特許文献1に開示される不揮発性スイッチング素子は、イオン伝導体からなる固体電解質と、この固体電解質の2つの面のそれぞれに接して設けられた第1電極および第2電極とで構成される。第1電極を構成する第1の金属と、第2電極を構成する第2の金属とは、金属が酸化されて金属イオンを生成する過程の標準生成ギブズエネルギー Gが異なる。非特許文献1の第1電極を構成する第1の金属と、第2電極を構成する第2の金属とは、それぞれ、下記のように選択される。

## [0009]

まず、OFF状態からON状態へ遷移させる電圧を第1電極と第2電極との間に印加した場合、第1電極と固体電解質との界面で、印加された電圧で誘起される電気化学反応によって、第1電極を構成する第1の金属が酸化されて金属イオンを生成する。このとき、固体電解質内に金属イオンとして供給されることのできる金属が、第1電極として選択される。

## [0010]

一方、ON状態からOFF状態へ遷移させる電圧を第1電極と第2電極との間に印加した場合、第2電極の表面に第1の金属が析出している場合に、第1の金属は、印加された電圧で誘起される電気化学反応によって、酸化されて金属イオンを生成する。このとき、第1の金属は、固体電解質内に金属イオンとして溶解する。一方で、第2電極を構成する第2の金属は、印加された電圧によっては、酸化されて金属イオンを生成することのない金属が、第2電極として選択される。

## [0011]

以下に、上記の第1電極を構成する第1の金属が第2電極に析出することで第1電極と第2電極とを架橋する金属架橋構造の形成と、この金属架橋構造の溶解とによって、ON 状態とOFF状態を形成する金属架橋型の抵抗変化素子のスイッチング動作を説明する。

## [0012]

OFF状態からON状態への遷移過程(セット過程と呼ぶ)では、第2電極を接地して

第1電極に正電圧を印加すると、第1電極と固体電解質の界面では、第1電極の金属が酸化され金属イオンになって固体電解質に溶解する。一方、第2電極側では、第2電極から供給される電子により、固体電解質中の金属イオンが金属になって析出する。析出した金属により、固体電解質中に金属架橋構造が形成されることで、第1電極と第2電極とが電気的に接続され、スイッチはON状態になる。

#### [0013]

一方、ON状態からOFF状態への遷移過程(リセット過程と呼ぶ)では、第2電極を接地して第1電極に負電圧を印加すると、金属架橋を構成している金属が金属イオンになって固体電解質に溶解する。溶解が進行すると、金属架橋の一部が切れることで、第1電極と第2電極との電気的接続が切れ、スイッチはOFF状態になる。

## [0014]

なお、金属架橋の溶解が進行している途中では、架橋が細くなることによって、電極間の抵抗が増大する変化が生じる。また、固体電解質中に含まれる金属イオン濃度が変化することで固体電解質の比誘電率が変化し、電極間の容量が変化する。これらの中間的な変化を経て、最終的には電気的接続が切断される。

#### [0015]

また、OFF状態へと遷移させた金属架橋型抵抗変化素子に、再び、第2電極を接地して第1電極に正電圧を印加すると、OFF状態からON状態への遷移過程(セット過程)が進行する。すなわち、金属架橋型抵抗変化素子では、OFF状態からON状態への遷移過程(セット過程)と、ON状態からOFF状態への遷移過程(リセット過程)とを、可逆的に行うことが可能である。

### 【先行技術文献】

## 【特許文献】

## [0016]

【特許文献 1 】特開 2 0 1 0 - 1 5 3 5 9 1 号公報

## 【非特許文献】

#### [0017]

【非特許文献 1】M. Tada, K. Okamoto, T. Sakamoto, M. Miyamura, N. Banno, and H. Hada, "Polymer Solid-Electrolyte (PSE) Switch Embedded on CMOS for Nonvolatile Crossbar Switch", IEEETRANSACTION ON ELECTRON DEVICES, Vol. 58, No. 12, pp. 4398-4405, (2011).

## 【発明の概要】

【発明が解決しようとする課題】

#### [0018]

前述の金属架橋型抵抗変化素子を半導体装置内に形成したスイッチング素子をプログラムする場合、各素子の電極にパルス電圧を印加することで、素子の抵抗状態を低抵抗から高抵抗へ、あるいは高抵抗から抵抵抗へ変化させる。この際、大規模に集積化された素子を一度にプログラムすると、プログラムに失敗する素子が生じる場合がある。このプログラムに失敗した素子を検出するために、前記パルス電圧の印加後に素子が所望の抵抗状態になっているかを検証するベリファイが用いられる。

## [0019]

ベリファイによって検出された書き込みに失敗した素子に対しては、書き込みプログラムを再度実施することが有効であると一般的には考えられている。しかしながら、金属架橋型抵抗変化を用いたスイッチング素子のプログラム方法においては、ベリファイとそれに伴う再プログラムの好適な方法がないという問題を有していた。

#### [0020]

本発明は、上記の問題に鑑みてなされたものである。その目的は、金属架橋型抵抗変化 を用いたスイッチング素子をプログラムする際のベリファイとそれに基づく再プログラム 10

20

30

40

の方法を提供することで、スイッチング素子の高信頼化と高密度化を実現することである

## 【課題を解決するための手段】

## [0021]

本発明のスイッチング素子のプログラム方法は、第1電極と、第2電極と、前記第1電極と前記第2電極との間に設けられ、前記第1電極と前記第2電極との間の電位差に応じて抵抗値Rが増減する抵抗変化膜と、を有するスイッチング素子のプログラム方法において、第1のパルス電圧を前記第1電極あるいは前記第2電極に与えることで前記抵抗変化膜の抵抗値Rを増減させるプログラムをし、前記抵抗値Rを測定し、前記測定された前記抵抗値Rが所望の値であるか否かを判定するベリファイをし、前記抵抗値Rが所望の値でない場合に、前記抵抗値Rに基づいて前記第1のパルス電圧と同じ極性の第2のパルス電圧を、前記第1のパルス電圧と同じ電極に与える再プログラムをする。

#### 【発明の効果】

## [0022]

本発明によれば、金属架橋型抵抗変化を用いたスイッチング素子をプログラムする際のベリファイとそれに基づく再プログラムの方法が提供され、スイッチング素子の高信頼化と高密度化を実現することが可能となる。

## 【図面の簡単な説明】

#### [0023]

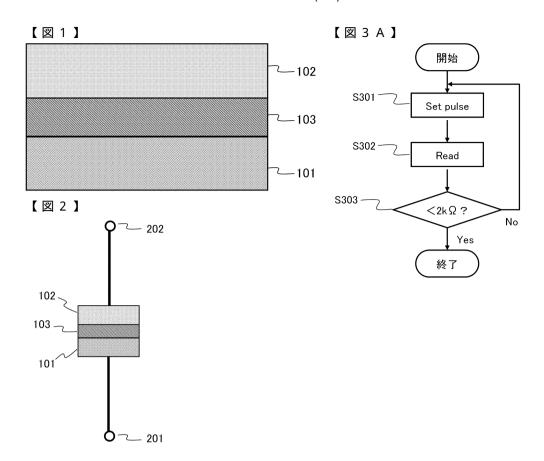

【図1】本発明の第1の実施形態のスイッチング素子の構成を示す図である。

【図2】本発明の第2の実施形態のスイッチング素子の構成を示す図である。

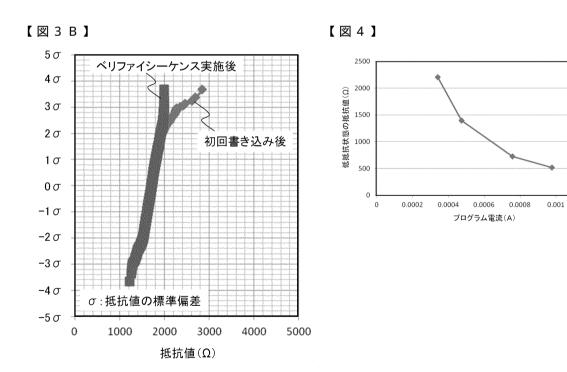

【図3A】本発明の第2の実施形態のスイッチング素子にプログラム(書き込み)する場合のベリファイを含むシーケンスを示す図である。

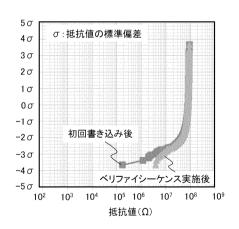

【図3B】本発明の第2の実施形態のシーケンスの実施前後でのスイッチング素子の抵抗値分布を示す図である。

【図4】本発明の第2の実施形態のスイッチング素子の低抵抗状態の抵抗値のプログラム 電流依存性を示す図である。

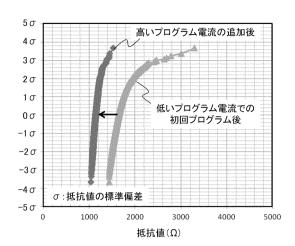

【図5】本発明の第2の実施形態のスイッチング素子の、低いプログラム電流での初回プログラム後と、高いプログラム電流の追加後の抵抗値分布を示す図である。

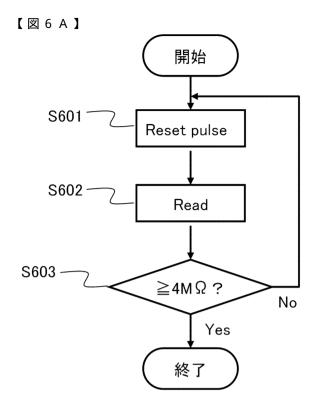

【図6A】本発明の第3の実施形態スイッチング素子にプログラム(消去)する場合のベリファイを含むシーケンスを示す図である。

【図6B】本発明の第3の実施形態のシーケンスの実施前後でのスイッチング素子の抵抗値分布を示す図である。

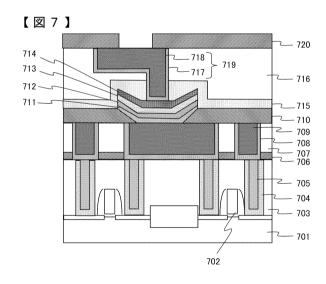

【図7】本発明の第4の実施形態のスイッチング素子を有する半導体装置の構成を示す断面図である。

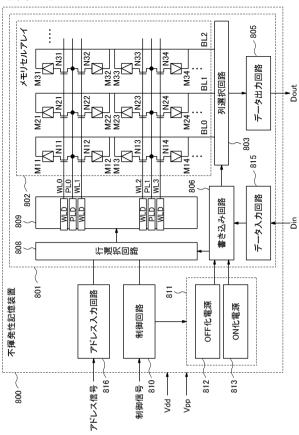

【図8】本発明の第4の実施形態のスイッチング素子を有する不揮発性記憶装置の構成を示す図である。

## 【発明を実施するための形態】

## [0024]

以下、図を参照しながら、本発明の実施形態を詳細に説明する。但し、以下に述べる実施形態には、本発明を実施するために技術的に好ましい限定がされているが、発明の範囲を以下に限定するものではない。

## (第1の実施形態)

図1は、本発明の第1の実施形態のプログラムを行うスイッチング素子の構成を示す。本実施形態のスイッチング素子は、第1電極101と、第2電極102と、前記第1電極101と前記第2電極102との間に設けられ、前記第1電極101と前記第2電極102との間の電位差に応じて抵抗値Rが増減する抵抗変化膜103とを有する。このスイッチング素子のプログラム方法は、第1のパルス電圧を前記第1電極101あるいは前記第2電極102に与えることで前記抵抗変化膜103の抵抗値Rを増減させるプログラムをする。さらに、前記抵抗値Rを測定し、前記測定された前記抵抗値Rが所望の値であるか

10

20

30

40

否かを判定するベリファイをする。さらに、前記抵抗値Rが所望の値でない場合に、前記抵抗値Rに基づいて前記第1のパルス電圧と同じ極性の第2のパルス電圧を、前記第1のパルス電圧と同じ電極に与える再プログラムをする。

#### [0025]

本実施形態によれば、金属架橋型抵抗変化を用いたスイッチング素子をプログラムする際のベリファイとそれに基づく再プログラムの方法が提供され、スイッチング素子の高信頼化と高密度化を実現することが可能となる。

## (第2の実施形態)

図1を用いて、第1の実施形態をより具体的にした本発明の第2の実施形態を説明する。本実施形態のスイッチング素子は、金属架橋型の抵抗変化膜103と、第1電極101 と、第2電極102とを備える。第1電極101は活性電極であって、たとえば銅を有する。また、第2電極102は不活性電極であって、たとえばルテニウムを有する。

#### [0026]

抵抗変化膜103は固体電解質材料であって、酸化物や硫化物や有機物などを用いることができる。あるいは酸化欠損タイプの抵抗変化素子でも良い。例えば、A1、Ti、Ta、Si、Hf、Zrなどを含む酸化物や、Ge、As、TeSなどを含むカルコゲナイド化合物や、炭素と酸素とシリコンを含む有機ポリマー膜などを用いることができる。あるいはそれらの積層構造であっても良い。

#### [0027]

第1電極101は銅を主成分とし、T i、A l、M n、W、M g などを添加物として含んでいても良い。第2電極102はR u、あるいはP tを主成分とし、T a、T i、W などを含んでいても良い。

## [0028]

本実施形態のスイッチング素子は、抵抗変化膜103である固体電解質層と、固体電解質層に一側とその反対側の各面に当接して対向配置された第1電極101及び第2電極102とを有する。このうち、第1電極101は、固体電解質層に金属イオンを供給する役割を果たしている。第2電極102からは、金属イオンは供給されない。第1電極101を活性電極、第2電極102を不活性電極と呼ぶ。

## [0029]

以下では、このスイッチング素子の動作について説明する。

### [0030]

第1電極101を接地して第2電極102に負電圧を印加すると、第1電極の金属が金属イオンになって固体電解質層に溶解する。そして、固体電解質層中の金属イオンが固体電解質層中に金属となって析出する。固体電解質層中に析出した金属により、第1電極101と第2電極102とを接続する金属架橋が形成される。金属架橋により第1電極101と第2電極102とが電気的に接続することで、スイッチング素子はON状態になる。

## [0031]

上記のスイッチング素子がON状態になる動作は、第2電極102を接地して第1電極101に正電圧を印加することによっても可能である。第1電極と第2電極との電位差は、第1電極101を接地して第2電極102に負電圧を印加する場合と、第2電極102を接地して第1電極101に正電圧を印加する場合とで、同じためである。

## [0032]

一方、上記ON状態で、第1電極101を接地して第2電極102に正電圧を印加すると、金属架橋の一部が切れる。これにより、第1電極101と第2電極102との電気的接続が切れ、スイッチング素子はOFF状態になる。なお、電気的接続が完全に切れる前の段階から、第1電極101及び第2電極102の間の抵抗が大きくなったり、電極間容量が変化したりするなど、電気特性が変化し、最終的に電気的接続が切れる。

### [0033]

上記のスイッチング素子をOFF状態とする動作は、第2電極102を接地して第1電極101に負電圧を印加することによっても可能である。第1電極と第2電極との電位差

10

20

30

40

は、第1電極101を接地して第2電極102に正電圧を印加する場合と、第2電極10 2を接地して第1電極101に負電圧を印加する場合とで、同じなためである。

#### [0034]

また、上記OFF状態からON状態にするには、再び、第1電極101を接地して第2電極102に負電圧を印加する、あるいは、第2電極102を接地して第1電極101に 正電圧を印加すればよい。

#### [0035]

図2は、本実施形態のスイッチング素子の構成を示す。本実施形態のスイッチング素子は、金属架橋型の抵抗変化膜103と、第1電極101と、第2電極102と、第1電極101に接続した第1端子201と、第2電極に接続した第2端子202を有する。高抵抗状態から低抵抗状態にプログラム(書き込み)する際には、第2電極102を接地し、第1電極101に正電圧を印加する。一方、低抵抗状態から高抵抗状態にプログラム(消去)する際には、第1電極101を接地し、第2電極102に正電圧を印加する。

## [0036]

発明者らが鋭意検討を行った結果、スイッチング素子の抵抗値は、電圧パルスの幅 t と、プログラム電流 I の関数で示されることがわかった。これは固体電解質中へ電気分解した銅の供給量(伝導物質量)Jが、ファラデーの第一法則に近いモデルで説明できることを意味する。

$J = K \cdot I \cdot t = K \cdot Q \qquad 式(1)$

ここで、Jは供給量(伝導物質量)、Kは定数、Iはプログラム電流、tは電圧パルス幅、Qは電荷量である。銅の供給量(伝導物質量)JとON状態での抵抗R $_{ON}$ とは相関があり、

1/J R<sub>ON</sub> 式(2)

しかしながら、固体電界質は電解質イオンを含まないかわりに、薄膜の絶縁体(厚さ 5 n m程度)である固体電解質を介した電子伝導が生じる。そのため、通常の電気分解とは異なり、全ての電荷の移動が銅イオンの輸送によるものではないため、電流 I とパルス幅 t に、それぞれ感度指数 m と n を導入したところ、 t < 1 m s e c . の範囲において実験値を良く説明できることがわかった。

$R_{ON} = A \cdot I^m \cdot t^n$  式(3)

Jは固体電解質中に供給される伝導物質量であり、本実施形態では主に銅であり、Jが大きいほど抵抗値は低くなる。m値、n値はプロセスおよび材料に依存し、予めプログラム電流と電圧パルス幅の異なる条件でテストすることにより抽出することができる。所望の抵抗値を得るためには、式(4)を元にI値、t値を設定してプログラムを行うことが可能である。

## [0037]

例えば、本実施形態で抽出された上記式(4)のA値、m値、n値は、A1とTiを添加物として含む銅電極上に、TiA1の複合酸化物を1nm、その上にSiOを30%含む低密度有機ポリマー膜を4nm、不活性電極としてRuTa合金を用いた場合の例である。

[0038]

ここで抵抗状態を高抵抗から低抵抗にプログラム(書き込み)した場合の、書き込み不良、すなわち、ON抵抗が所望の値よりも高い不良が発生する場合がある。発明者は、この時、不良の原因は、A値が素子によってばらつくため、偶発的に高い値を有する素子が存在するためであることを明らかにした。すなわち、A値が高いと銅の供給量」が小さいため、ON抵抗が大きくなってしまうことがわかった。これを解決するためには、再プログラムにより、不足分の銅イオンを固体電解質内へ供給すればよい。そのため、例えば同じプログラム条件、すなわち同じ電流値であっても、追加のパルス電圧を印加することで高抵抗の不良を解消することができる。

## [0039]

50

10

20

30

あるいは、式(3)に基づいて、所望の抵抗値を得るために不足している銅の量を自動的に算出するシーケンスを設定し、電流一定のままパルス電圧の印加時間のみを変更した Set pulseを印加することで、ベリファイに基づいた再プログラムを行うこともできる。

## [0040]

例えば、所望の $R_{ON}$ が2k であって、不良bitの抵抗値が4k である場合に、式(3)によれば2倍の銅供給量が必要であることが分かる。そのため、パルス電圧印加時間による銅供給量を2倍にすることで不足分の銅を固体電解質内に供給することによって、所望の抵抗値が得られるようになる。

#### [0041]

読み出した当該スイッチング素子の抵抗値に基づいて、予め設定した固体電解質内の銅の量を算出して不足分の銅の供給を実施するアルゴリズムは、次の通りである。すなわち、式(3)に基づいて、予めm値とn値とを算出しておき、書き込みされたbitのA値に基づいて再プログラムの電圧パルス幅や電流値を設定する作業を行う。

### [0042]

本実施形態では、高抵抗状態から低抵抗状態にプログラム(書き込み)する場合に着目する。低抵抗状態は10k より小さく、好ましくは2k 以下とする。高抵抗状態とは、10k 以上と規定し、プログラムには電圧パルスを用いる場合について説明する。

## [0043]

図3Aは、高抵抗状態から低抵抗状態にプログラム(書き込み)する場合のベリファイを含むシーケンスを示す。まずSet pulseとして、高抵抗状態のスイッチング素子に第1の電圧パルスを印加する(S301)。このときの電圧パルスの振幅と幅は、例えば3.3Vで1μsとする。続いて、スイッチング素子の抵抗値の読み出しを行うReadを行う(S302)。抵抗値の読み出しは、プログラムの際の電圧パルスと同じ極性の電圧で測定を行うことができる。次に、抵抗値の判定を行う(S303)。スイッチング素子の抵抗値が2k 未満の場合は、シーケンスを終了する。

### [0044]

一方、スイッチング素子の抵抗値が2k 以上の場合は、抵抗値に基づいて第2の電圧パルスを印加する(S301)。第2の電圧パルスは、再プログラム用のパルスである。ここで、第2の電圧パルスの振幅と幅は、第1の電圧パルスと同一とすることもできる。また、式(3)に基づいて決めることもできる。その後、再び抵抗値の読み出しを行い(S302)、スイッチング素子の抵抗値が2k 未満の場合は、シーケンスを終了する。一方、2k 以上の場合には、再々度、Set pulse(S301)に戻る。

## [0045]

図3 B は、図3 A に示す本実施形態のシーケンスの実施前後でのスイッチング素子アレイの抵抗値分布を示す。図3 A のベリファイを含むシーケンスを実施する前、すなわち、初回書き込み後の場合には、抵抗値のばらつきが大きく、2 k 以上の抵抗変化素子が複数存在する。これに対して、図3 A のシーケンスを実施した後には、抵抗値の分布のばらつきが減少し、全て2 k 未満となっていることがわかる。

## [0046]

これは初回のSet pulseによってやや高抵抗(図3Bから2~3k 程度)となりプログラムを失敗した素子に対して、例えば、初回と同一のパルス電圧を再度、あるいは再々度と印加する。これにより、不足分の銅が供給され所望の抵抗値となる。図3Aは、ベリファイに伴う再プログラムが可能であることを示している。

#### [0047]

以下、一度書き込みを行った素子に対して、図3Aによるベリファイに伴う再プログラムが可能である別の実験結果について説明する。

#### [0048]

スイッチング素子を高抵抗状態から低抵抗状態へ遷移させる場合、式(3)に基づいて、プログラム電流によって低抵抗状態の抵抗値が制御できる。例えば、図4では、第1の

10

20

30

40

電極 1 0 1 は銅を主成分とする。さらに、スイッチング素子 1 0 3 は固体電解質材料であって、炭素と酸素とシリコンを含む有機ポリマー膜とする。さらに、第 2 の電極 1 0 2 は R u を主成分とし、 T a 、あるいは T i を含んでいる。図 4 は、以上の場合のプログラム電流を変えたときの低抵抗状態の抵抗値を示す図である。プログラム電流のパルス幅は 1 0 0 µ s e c で一定とした。プログラム電流を下げると低抵抗状態の抵抗値が大きくなることがわかる。

#### [0049]

## [0050]

本実施形態のスイッチング素子のプログラム方法によれば、金属架橋型抵抗変化を用いたスイッチング素子をプログラムする際の、好適なベリファイとそれに基づく再プログラムの方法が提供される。これにより、スイッチング素子のON状態とOFF状態の切り替えが高信頼化される。さらに、一つ一つのスイッチング素子の切り替えが高信頼化されることによって、より多くのスイッチング素子を扱うことが可能となる。すなわち、スイッチング素子の高密度化が可能となる。

## [0051]

以上のように本実施形態によれば、金属架橋型抵抗変化を用いたスイッチング素子をプログラムする際のベリファイとそれに基づく再プログラムの方法が提供され、スイッチング素子の高信頼化と高密度化を実現することが可能となる。

## (第3の実施形態)

図1を用いて、第1の実施形態をより具体的にした本発明の第3の実施形態を説明する。本実施形態のスイッチング素子は、金属架橋型の抵抗変化膜103と、第1電極101と、第2電極102とを備える。第1電極101は活性電極であって、たとえば銅を有する。また、第2電極102は不活性電極であって、たとえばルテニウムを有する。本実施形態のスイッチング素子を構成する材料は、第2の実施形態と同様であるので、詳細な説明は省略する。

## [0052]

図2は、第2の実施形態と同様の本実施形態のスイッチング素子の構成を示す。本実施形態のスイッチング素子は、金属架橋型の抵抗変化膜103と、第1電極101と、第2電極102と、第1電極101に接続した第1端子201と、第2電極に接続した第2端子202とを有する。低抵抗状態から高抵抗状態にプログラム(消去)する際には、第1電極101を接地し、第2電極102に正電圧を印加する。

## [0053]

発明者らが鋭意検討を行った結果、高抵抗状態でのスイッチング素子の抵抗値のばらつきは、抵抗変化膜である固体電解質内に残留した伝導物質の残留物に影響されていることがわかった。これは書き込み時に固体電解質内に析出した銅が、消去の際に完全に回収されずに残留したためである。

## [0054]

本実施形態の場合、固体電界質は電解質イオンを含まないかわりに、固体電解質を6 nm以下の薄い膜厚としている。これにより電極間には高い電位差が生じ、第 2 の実施形態と同じく、消去時間を長くすることで銅の回収を促進することができることを見出した。

## [0055]

50

40

10

20

本実施形態は、低抵抗状態から高抵抗状態にプログラム(消去)する場合を対象とする。低抵抗状態は10k より小さく、好ましくは2k 以下とする。高抵抗状態とは、10k 以上と規定し、プログラムにはパルス電圧を用いる場合について説明する。

#### [0056]

図6Aは、低抵抗状態から高抵抗状態にプログラム(消去)する場合の、ベリファイを含むシーケンスを示す。まず、Reset pulseとして、低抵抗状態のスイッチング素子に第1の電圧パルスを印加する(S601)。例えば2.5 Vで10  $\mu$ sの電圧パルスを印加する。続いて、スイッチング素子の抵抗値の読出しを行うReadを実施し(S602)、抵抗値の判定を行う(S603)。抵抗値の読み出しは、プログラムの際の電圧パルスと同じ極性の電圧で測定を行うことができる。素子の抵抗値が4M以上の場合は、シーケンスを終了する。ここで4Mとは、高抵抗状態を10k以上と規定した場合の一例である。

#### [0057]

一方、素子の抵抗値が4M 未満の場合は、S601に戻って第2の電圧パルスを印加する(S601)。第2の電圧パルスは、ベリファイに伴う再プログラム用のパルスである。ここで、第2の電圧パルスの振幅と幅は、第1の電圧パルスと同一とすることもできる。また、第2の実施形態と同様に式(3)に基づいて決めることもできる。

### [0058]

次に、再び抵抗値の読み出しを行う(S602)。スイッチング素子の抵抗値が4M以上の場合は、シーケンスを終了する。一方、4M 未満の場合には、再々度、S601に戻る。

#### [0059]

図6Bは、本実施形態のシーケンスの実施前後でのスイッチング素子の抵抗値分布を示す図である。図6Aのベリファイを含むシーケンスを実施する前、すなわち、初回書き込み後の場合には、抵抗値のばらつきが大きく、4M 未満の抵抗変化素子が複数存在する。これに対して、図6Aのシーケンスを実施した後には、抵抗値の分布のばらつきが減少し、全て4M 以上となっていることがわかる。

#### [0060]

この結果は、初回のReset pulseによるプログラムで所望の抵抗値よりも低抵抗となりプログラムを失敗した素子に対して、パルス電圧を再度、あるいは再々度と印加することで、ベリファイとそれに伴う再プログラムが可能であることを示している。

## [0061]

また、高抵抗状態に遷移させる場合には、電圧印加時に流れる電流が低いため、多数の 素子に対して同時にパルス電圧を印加するベリファイプログラムとすることも可能である

#### [0062]

本実施形態のスイッチング素子のプログラム方法によれば、金属架橋型抵抗変化を用いたスイッチング素子をプログラムする際の、好適なベリファイとそれに基づく再プログラムの方法が提供される。これにより、スイッチング素子のON状態とOFF状態の切り替えが高信頼化される。さらに、一つ一つのスイッチング素子の切り替えが高信頼化されることによって、より多くのスイッチング素子を扱うことが可能となる。すなわち、スイッチング素子の高密度化が可能となる。

## [0063]

以上のように本実施形態によれば、金属架橋型抵抗変化を用いたスイッチング素子をプログラムする際のベリファイとそれに基づく再プログラムの方法が提供され、スイッチング素子の高信頼化と高密度化を実現することが可能となる。

#### (第4の実施形態)

本発明の第4の実施形態として、図7に示す、半導体基板上にMOSFETを形成し、 さらに、銅配線の内部にスイッチング素子を形成した半導体装置について説明する。

## [0064]

50

10

20

30

10

20

30

40

50

図7に示す半導体装置は、まず、シリコン基板701に形成されたMOSFET702、シリコン酸化膜からなる層間絶縁膜703、TiN膜からなるバリアメタル層704とタングステンビア705によるタングステンプラグを有する。さらに、SiCN膜からなるバリア絶縁膜706、比誘電率3以下のSiOCH膜による層間絶縁膜707、Ta膜とTaN膜の積層膜によるバリアメタル層708と銅層709とからなる銅配線を有する

#### [0065]

SiN膜からなるバリア絶縁膜710は、銅配線の銅層709上で開口する。開口部には、第1イオン伝導層711と第2イオン伝導層712を有する抵抗変化層、第1上部電極713、第2上部電極714が積層される。銅層709は抵抗変化層の一方の電極を兼ねている。

#### [0066]

抵抗変化層は固体電解質であり、第1イオン伝導層711は、酸化チタン、酸化アルミニウム、あるいは酸化チタンと酸化アルミニウムとの積層構成を有する。第2イオン伝導層712は、シリコンと酸素と炭素とを有する比誘電率が2.1以上3.0以下のポリマー膜を有する。第1上部電極713は、Ru、RuTa、あるいはRuTi合金膜を有する。第2上部電極714は、Ta膜、Ti膜、あるいはそれらの窒化膜を有する。バリア絶縁膜715はSiN膜を有する。

## [0067]

さらに、SiOCH膜による層間絶縁膜716内に形成されたTa膜とTaN膜の積層膜によるバリアメタル層717と銅層718とからなる銅配線719は、第2上部電極714に接続する。銅配線719の上には、SiCN膜などによるバリア絶縁膜720を介して、さらに上層の配線層などが形成される。

#### [0068]

以上の構造とすることで、最先端のULSI(Ultra-Large Scale Integration)ロジックなどの半導体装置の内部に、抵抗変化層を有するスイッチング素子を搭載することができるようになる。このような積層構造は、FPGA用のスイッチング素子としてだけでなく、大規模なメモリ量を実現するメモリ素子構造としても、有効である。

## [0069]

図8は、図7のスイッチング素子を内蔵した不揮発性記憶装置800の構成を示すブロック図である。

#### [0070]

図8に示すように、不揮発性記憶装置800は、CMOS(Complementary Metal-Oxide Semiconductor)半導体基板上に、メモリ本体部801を備える。メモリ本体部801は、メモリセルアレイ802、行選択回路808、ワード線ドライバWLDとプレート線ドライバPLDとを有する行ドライバ809、列選択回路803、データの書き込みを行うための書き込み回路806を備える。さらに、端子Dinを介して入力データの入力処理を行うデータ入力回路815、端子Doutを介して出力データの出力処理を行うデータ出力回路805、を備える。

## [0071]

さらに、書き込み用電源 8 1 1 として、低抵抗(LR)化用電源(OFF化電源 8 1 2)と、高抵抗(HR)化用電源(ON化電源 8 1 3)とを備える。OFF化電源 8 1 2 の出力、およびON化電源 8 1 3 の出力は、書き込み回路 8 0 6 に供給される。

#### [0072]

さらに、外部から入力されるアドレス信号を受け取るアドレス入力回路816と、外部から入力されるコントロール信号に基づいて、メモリ本体部801の動作及び書き込み用電源811の動作を制御する制御回路810とを備えている。

## [0073]

メモリセルアレイ802は、半導体基板の上に形成され、互いに交差するように配列さ

10

20

30

40

50

れた複数のワード線WL0、WL1、WL2、・・・、および複数のビット線BL0、BL1、BL2、・・・を有する。さらに、これらの交点に設けられた複数のNMOSトランジスタN11、N12、N13、N21、N22、N23、N31、N32、N33、・・・(以下、「トランジスタN11、N12、・・・」と表す)を有する。さらに、トランジスタN11、N12、・・・と1対1に直列接続された複数の抵抗変化素子M11、M12、M13、M21、M22、M23、M31、M32、M33、・・・(以下、「抵抗変化素子M11、M12、・・・」と表す)を有する。

## [0074]

図 8 に示すように、トランジスタN 1 1、N 2 1、N 3 1、・・・のゲートはワード線W L 0 に接続する。トランジスタN 1 2、N 2 2、N 3 2、・・・のゲートはワード線W L 1 に接続する。トランジスタN 1 3、N 2 3、N 3 3、・・・のゲートはワード線W L 2 に接続する。トランジスタN 1 4、N 2 4、N 3 4、・・・のゲートはワード線W L 3 に接続する。

## [0075]

また、抵抗変化素子M 1 1、M 1 2、M 1 3、M 1 4・・・はビット線 B L 0 に接続する。抵抗変化素子M 2 1、M 2 2、M 2 3、M 2 4・・・はビット線 B L 1 に接続する。抵抗変化素子M 3 1、M 3 2、M 3 3、M 3 4・・・はビット線 B L 2 に接続する。

## [0076]

アドレス入力回路816は、外部回路(図示せず)からアドレス信号を受け取り、このアドレス信号に基づいて、行アドレス信号を行選択回路808へ出力し、列アドレス信号を列選択回路803へ出力する(図示せず)。ここで、アドレス信号は、複数のメモリセルM11、M12、・・・のうちの選択される特定のメモリセルのアドレスを示す信号である。

#### [0077]

制御回路810は、データの書き込みサイクルでは、後述する選択部で選択されたメモリセルの有する抵抗変化素子に対してデータが書き込まれるように書き込み用電源811と書き込み回路806とを制御する。ここでは、書き込み時のパルス電圧の電圧レベルを指示する電圧設定信号を書き込み用電源811へ出力し、データ入力回路815に入力された入力データDinに応じて、書き込み用電圧の印加を指示する書き込み信号を書き込み回路806へ出力する。他方、データの読み出しサイクルでは、制御回路810は、読み出し動作を指示する読み出し信号を出力する。

## [0078]

行選択回路 8 0 8 は、アドレス入力回路 8 1 6 から出力された行アドレス信号を受け取る。この行アドレス信号に応じて、行ドライバ 8 0 9 より、複数のワード線W L 0、W L 1、W L 2、・・・のうちの何れかに対応するワード線ドライバ回路W L D より、その選択されたワード線に対して、所定の電圧を印加する。

## [0079]

また、列選択回路 8 0 3 は、アドレス入力回路 8 1 6 から出力された列アドレス信号を受け取る。この列アドレス信号に応じて、複数のビット線 B L 0 、 B L 1 、 B L 2 、・・・のうちの何れかを選択し、その選択されたビット線に対して書き込み用電圧または読み出し用電圧を、非選択ビット線に対しては非選択電圧を印加する。

#### [0800]

なお、行選択回路 8 0 8 及び列選択回路 8 0 3 によって、メモリセルアレイ 8 0 2 の中から少なくとも 1 つメモリセルを選択する選択部が構成されている。

#### [0081]

書き込み回路806は、制御回路810の制御の下で、選択部で選択されたメモリセルに含まれる抵抗変化素子に対して、書き込み用電源811から供給される電源に基づく電圧パルスが印加されるように制御する回路である。ここでは、制御回路810から出力された書き込み信号を受け取った場合、列選択回路803による選択されたビット線に対して、書き込み用電圧の印加を指示する信号を受けて、書き込みモードによって設定された

電圧に従った書き込みパルスを出力する。

## [0082]

図示していないが、抵抗変化素子の抵抗値のOFF/ON比が低い場合には、センスアンプを設けることができる。これにより、データの読み出しサイクルで、読み出し対象となる選択ビット線に流れる電流量を複数の検知レベルから目的に合わせた1つの検知レベルに従って検出する。そして、ビット線に流れる電流量が検知レベル以上か以下かを、データ「0(低抵抗状態)」か「1(高抵抗状態)」の論理結果として出力し、記憶されているデータの状態を判定する。その結果得られた出力データDoutは、データ出力回路805を介して、回路外部へ出力される。

#### [0083]

書き込み用電源811は、低抵抗(LM)化書き込み(単に書き込みともいう)時のパルス電圧を発生するための電源を供給するOFF化電源812を有する。さらに、高抵抗(HM)化書き込み(単に消去ともいう)時のパルス電圧を発生するための電源を供給するON化電源813を有する。OFF化電源812とON化電源813は、ともに書き込み回路806へ入力されている。

#### [0084]

抵抗変化素子の第1電極は、BL側に接続されており、第2電極はPL側に接続されている。例えば、抵抗状態を高抵抗から低抵抗に変化させる(セット動作する)場合は、PLを接地し、BLに電圧を印加することで、プログラムを行う。プログラム電流はトランジスタの飽和電流によって制御することができる。一方、抵抗状態を低抵抗から高抵抗へ変化させる(リセット動作する)場合には、BLを接地し、PLに消去電圧を印加する。このような回路構成において第2および第3の実施形態に基づいて、書き込み回路にベリファイとそれに基づく再プログラムの機能を備えることで、誤書き込みを防ぐことが可能となる。

#### [0085]

本実施形態のスイッチング素子のプログラム方法によれば、金属架橋型抵抗変化を用いたスイッチング素子をプログラムする際の、好適なベリファイとそれに基づく再プログラムの方法が提供される。これにより、スイッチング素子のON状態とOFF状態の切り替えが高信頼化される。さらに、一つ一つのスイッチング素子の切り替えが高信頼化されることによって、より多くのスイッチング素子を扱うことが可能となる。すなわち、スイッチング素子の高密度化が可能となる。

## [0086]

以上のように本実施形態によれば、金属架橋型抵抗変化を用いたスイッチング素子をプログラムする際のベリファイとそれに基づく再プログラムの方法が提供され、スイッチング素子の高信頼化と高密度化を実現することが可能となる。

#### [0087]

以上の本発明の実施形態では、CMOS回路を有する半導体装置に関し、半導体基板上の銅多層配線内部に抵抗変化素子を形成する例について説明した。本発明はこれに限定されるものではなく、バイポーラトランジスタ等のようなメモリ回路を有する半導体装置、マイクロプロセッサなどの論理回路を有する半導体装置、あるいはそれらを同時に搭載したボードやパッケージの銅配線上へも適用することができる。

#### [0088]

また、本発明は半導体装置に、電子回路装置、光回路装置、量子回路装置、マイクロマシン、MEMS(Micro Electro Mechanical Systems)などを接合する際にも適用することができる。また、本発明ではスイッチ機能の例を中心に説明したが、不揮発性と抵抗変化特性の双方を利用したメモリ素子にも用いることができる。

### [0089]

本発明は上記の実施形態に限定されることなく、請求の範囲に記載した発明の範囲内で、種々の変形が可能であり、それらも本発明の範囲内に含まれるものである。

10

20

30

40

## [0090]

この出願は、2013年6月24日に出願された日本出願特願2013-131263 を基礎とする優先権を主張し、その開示の全てをここに取り込む。

## 【産業上の利用可能性】

## [0091]

本発明は、半導体装置であるFPGAなどのスイッチング素子やメモリ素子への利用が 可能である。

## 【符号の説明】

## [0092]

8 1 6

アドレス入力回路

| 0 | 0 | 9 | 2 ] |             |    |

|---|---|---|-----|-------------|----|

| 1 | 0 | 1 |     | 第1電極        | 10 |

| 1 | 0 | 2 |     | 第2電極        |    |

| 1 | 0 | 3 |     | 抵抗变化膜       |    |

| 2 | 0 | 1 |     | 第1端子        |    |

| 2 | 0 | 2 |     | 第 2 端子      |    |

| 7 | 0 | 1 |     | シリコン基板      |    |

| 7 | 0 | 2 |     | MOSFET      |    |

| 7 | 0 | 3 |     | 層間絶縁膜       |    |

| 7 | 0 | 4 |     | バリアメタル層     |    |

| 7 | 0 | 5 |     | タングステンビア    |    |

| 7 | 0 | 6 |     | バリア絶縁膜      | 20 |

| 7 | 0 | 7 |     | 層間絶縁膜       |    |

| 7 | 0 | 8 |     | バリアメタル層     |    |

| 7 | 0 | 9 |     | 銅層          |    |

| 7 | 1 | 0 |     | バリア絶縁膜      |    |

| 7 | 1 | 1 |     | 第1イオン伝導層    |    |

| 7 | 1 | 2 |     | 第2イオン伝導層    |    |

| 7 | 1 | 3 |     | 第1上部電極      |    |

| 7 | 1 | 4 |     | 第 2 上部電極    |    |

| 7 | 1 | 5 |     | バリア絶縁膜      |    |

| 7 | 1 | 6 |     | 層間絶縁膜       | 30 |

| 7 | 1 | 7 |     | バリアメタル層     |    |

| 7 | 1 | 8 |     | 銅層          |    |

| 7 | 1 | 9 |     | 銅配線         |    |

| 7 | 2 | 0 |     | バリア絶縁膜      |    |

| 8 | 0 | 0 |     | 不揮発性記憶装置    |    |

| 8 | 0 | 1 |     | メモリ本体部      |    |

| 8 | 0 | 2 |     | メモリセルアレイ    |    |

| 8 | 0 | 3 |     | 列選択回路       |    |

| 8 | 0 | 5 |     | データ出力回路     |    |

| 8 | 0 | 6 |     | 書き込み回路      | 40 |

| 8 | 0 | 8 |     | 行選択回路       |    |

| 8 | 0 | 9 |     | 行ドライバ       |    |

| 8 | 1 | 0 |     | 制御回路        |    |

| 8 | 1 | 1 |     | 書き込み用電源     |    |

| 8 | 1 | 2 |     | OFF化電源      |    |

| 8 | 1 | 3 |     | ON化電源       |    |

| 8 | 1 | 5 |     | データ入力回路     |    |

| _ |   |   |     | <del></del> |    |

0.0012

【図5】

【図 6 B】

# 【図8】

# フロントページの続き

(56)参考文献 特開2012-064286(JP,A)

特開2013-084324(JP,A)

国際公開第2012/128017(WO,A1)

特表2013-520761(JP,A)

特開2005-123575(JP,A)

特開2012-069221(JP,A)

(58)調査した分野(Int.CI., DB名)

G11C 13/00