(19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2006-80237 (P2006-80237A)

(43) 公開日 平成18年3月23日(2006.3.23)

(51) Int.C1.

FI

テーマコード (参考)

HO 1 L 27/12 (2006.01) HO 1 L 21/02 (2006.01) HO1L 27/12

В

審査請求 未請求 請求項の数 15 OL (全 20 頁)

(21) 出願番号

特願2004-261567 (P2004-261567)

(22) 出願日

平成16年9月8日 (2004.9.8)

(71) 出願人 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74)代理人 100076428

弁理士 大塚 康徳

(74)代理人 100112508

弁理士 高柳 司郎

(74)代理人 100115071

弁理士 大塚 康弘

(74)代理人 100116894

弁理士 木村 秀二

(72)発明者 佐藤 信彦

東京都大田区下丸子3丁目30番2号 キ

ヤノン株式会社内

最終頁に続く

(54) 【発明の名称】半導体装置及びその製造方法

# (57)【要約】

【課題】 デバイス形成工程での剥離を抑えること。

【解決手段】 半導体装置の製造方法であって、分離領域103と分離領域103の全体を覆う半導体領域102とを有する半導体基板101を準備し、半導体領域102に1又は複数の回路素子109を形成し、半導体基板101を分離領域103で分離する。

【選択図】 図1

#### 【特許請求の範囲】

#### 【請求項1】

分離領域と該分離領域の全体を覆う半導体領域とを有する半導体基板を準備する工程と

前記半導体領域に1又は複数の回路素子を形成する工程と、

前記半導体基板を前記分離領域で分離する工程と、

を含むことを特徴とする半導体装置の製造方法。

#### 【請求項2】

半導体領域を有する半導体基板を準備する工程と、

前記半導体領域に1又は複数の回路素子を形成する工程と、

前記半導体基板に前記半導体領域によって全体が覆われた分離領域を形成する工程と、

前記半導体基板を前記分離領域で分離する工程と、

を含むことを特徴とする半導体装置の製造方法。

### 【請求項3】

前記分離領域は、多孔質層であることを特徴とする請求項1に記載の半導体装置の製造方法。

### 【請求項4】

前記半導体基板は、複数の多孔質層を有し、

前記分離領域は、前記複数の多孔質層のうち前記半導体基板の表面に最も近い多孔質層を除いた層であることを特徴とする請求項3に記載の半導体装置の製造方法。

#### 【請求項5】

前記分離領域は、イオン注入により形成されることを特徴とする請求項1又は請求項2 に記載の半導体装置の製造方法。

#### 【請求項6】

前記半導体基板は、格子定数が異なる複数の単結晶層を有し、

前記分離領域は、前記格子定数が異なる単結晶層の界面であることを特徴とする請求項1に記載の半導体装置の製造方法。

#### 【請求項7】

前記分離工程の前に、前記半導体基板の周辺部の前記半導体領域を除去して前記分離領域を露出させる工程を含むことを特徴とする請求項1乃至請求項6のいずれか1項に記載の半導体装置の製造方法。

# 【請求項8】

前記分離領域は、少なくとも前記1又は複数の回路素子が形成される領域の下方に形成されることを特徴とする請求項1乃至請求項7のいずれか1項に記載の半導体装置の製造方法。

### 【請求項9】

前記分離工程の前に、前記半導体基板を他の部材と結合させる工程を含むことを特徴とする請求項1乃至請求項8のいずれか1項に記載の半導体装置の製造方法。

#### 【請求頃10】

前記結合工程では、前記分離領域が形成される領域内において、前記半導体基板の表面と前記他の部材とを結合させることを特徴とする請求項9に記載の半導体装置の製造方法

# 【請求項11】

前記分離領域は、1又は複数の回路素子を形成できない前記半導体基板の周辺部の領域よりも内側に形成されることを特徴とする請求項1乃至請求項10のいずれか1項に記載の半導体装置の製造方法。

#### 【請求項12】

前記分離工程の前に、前記半導体領域をチップ化する工程を含むことを特徴とする請求項1乃至請求項11のいずれか1項に記載の半導体装置の製造方法。

# 【請求項13】

50

40

10

20

前記1又は複数の回路素子が形成される領域は、複数のチップ領域を含み、

前記分離領域は、前記複数のチップ領域の各々の下方に形成され、

前記チップ化する工程では、前記半導体領域のうち前記分離層が形成されていない領域 を ダ イ シ ン グ し て 前 記 分 離 領 域 を 露 出 さ せ る こ と を 特 徴 と す る 請 求 項 1 2 に 記 載 の 半 導 体 装置の製造方法。

#### 【 請 求 項 1 4 】

分離領域と、

前記分離領域の全体を覆う半導体領域と、

前記半導体領域に形成された1又は複数の回路素子と、

前記分離領域は、少なくとも前記1又は複数の回路素子が形成される領域の下方に形成 されることを特徴とする半導体装置。

# 【請求項15】

前記分離領域は、前記1又は複数の回路素子が形成される領域の外接円と当該半導体装 置 の 主 面 端 と に 囲 ま れ た 領 域 に 形 成 さ れ る こ と を 特 徴 と す る 請 求 項 1 4 に 記 載 の 半 導 体 装

【発明の詳細な説明】

#### 【技術分野】

# [0001]

本発明は、半導体装置及びその製造方法に関する。

【背景技術】

#### [00002]

LSIチップを薄層化するため、シリコン基板に集積回路等を形成した後、基板裏面側か らグラインダーにより薄層化する技術が知られている。しかしながら、集積回路等が形成 さ れ る 部 分 は シ リ コ ン 基 板 の 表 面 の み で あ り 、 大 部 分 の 領 域 が 研 削 さ れ て 捨 て ら れ て しま う。これでは資源を有効活用することができない。

# [00003]

一 方 、 半 導 体 装 置 の 微 細 化 ・ 高 集 積 化 に 伴 い 、 チ ッ プ の 発 熱 量 が 飛 躍 的 に 大 き く な る こ とが懸念され、LSIチップを薄層化する技術の確立が求められている。また、通常の半導 体 チップ は、 柔 軟 性 が な い た め 、 ICカ ー ド 等 の 薄 型 デ バ イ ス に 搭 載 す る 際 に は 、 曲 げ 強 度 を高める必要がある。ICカードのように携帯して使用される場合には、収容時に曲げ応力 が加わる場合があるからである。従って、薄型デバイスに搭載されるLSIチップ等にも、 放 熱 性 及 び 柔 軟 性 の 点 か ら 薄 層 化 が 求 め ら れ て い る 。 半 導 体 装 置 を 薄 膜 化 す る 技 術 と し て は、以下のものが開示されている。

#### [0004]

特 許 文 献 1 は 、 多 孔 質 層 の 表 面 に 形 成 さ れ た 半 導 体 層 上 に デ バ イ ス を 形 成 し 、 デ バ イ ス が 形 成 さ れ た 半 導 体 層 を 多 孔 質 層 で 分 離 す る こ と に よ っ て 、 薄 膜 半 導 体 装 置 又 は I C カ ー ドを形成する薄膜形成技術を開示している。

特許文献2は、多孔質層表面に形成された半導体層の周辺部を除去することによって、 半導体基板を多孔質層で分離する際にひび割れが起こりにくくする薄膜形成技術を開示し ている。

### [0006]

特許文献3は、半導体基板上に多孔質層を形成しない領域を設けることによって、多孔 質の表面に形成された半導体層を支持部材側に移設する前に半導体層が分離することを防 止する薄膜形成技術を開示している。ここで、半導体基板の周辺部に多孔質層が露出して いる場合には、露出した多孔質層を除去する。

特許文献4は、半導体基板表面の周辺部以外の領域に第1の電流密度で第1の多孔質層 を形成した後に、半導体基板表面全体に第2の電流密度で第2の多孔質層を形成し、その 10

20

30

40

後、半導体基板表面の周辺部以外の領域に結晶薄膜を形成する薄膜形成技術を開示している。

【 特 許 文 献 1 】 特 開 平 9 - 3 1 2 3 4 9 号 公 報 ( 第 2 図 - 第 4 図 )

【特許文献2】特開2000-349066号公報(第1図)

【 特 許 文 献 3 】 特 開 2 0 0 1 - 2 8 4 6 2 2 号 公 報 ( 第 3 図 及 び 第 4 図 )

【 特 許 文 献 4 】 特 開 2 0 0 2 - 1 4 1 3 2 7 号 公 報 ( 第 1 図 - 第 3 図 )

【発明の開示】

【発明が解決しようとする課題】

[00008]

しかし、従来の薄膜形成技術では、分離領域としての多孔質層が露出した状態で半導体基板に1又は複数の回路素子を形成するので、その工程(以下「デバイス形成工程」という。)において、半導体基板が剥離されやすいという問題があった。

[0009]

例えば、特許文献1に記載の発明では、半導体層上にデバイスを形成する工程において、多孔質層の周辺部が露出しているため、基板を装置に配置する際や基板を搬送する時等に、基板の周辺部が装置や搬送部材と接触し、基板周辺部に形成された多孔質層から半導体層の剥離が生じうる。

[0010]

また、特許文献 2 に記載の発明では、多孔質層を形成してから多孔質層で半導体層を分離するまで、多孔質層の周辺部が露出した状態にあるため、特許文献 1 と同様に、露出した多孔質層から半導体層の剥離が生じうる。

[0011]

また、特許文献3に記載の発明では、多孔質を形成しない領域を設けることによって、 半導体層の分離が生じにくくなっているものの、多孔質層を形成してから多孔質層で半導 体層を分離するまで、多孔質層の周辺部が露出した状態にあるため、特許文献1、2と同様に、露出した多孔質層から半導体層の剥離が生じうる。

[ 0 0 1 2 ]

また、特許文献4に記載の発明では、第2の多孔質層を形成してから第1の多孔質層で 半導体層を分離するまで、第2の多孔質層が露出しており、特許文献1~3と同様に、基 板周辺部に形成された第2の多孔質層から結晶薄膜の剥離が生じうる。

[0013]

このように、従来の技術では、多孔質層が露出しているため、基板を装置に配置する際や基板を搬送する時等に、基板の周辺部が装置や搬送部材と接触し、基板周辺部に形成された多孔質層から予期せぬ剥離が生じるという問題点があった。デバイス形成工程で半導体基板が剥離されると、剥離片が他の半導体基板上に落下して、落下部のデバイスに動作不良を起こし、結果として、チップの歩留まりが低下しうる。また、半導体基板が剥離されると、剥離片を完全に除去するために、製造装置を停止して装置内の部品を洗浄する必要があり、デバイス形成工程の稼働率の低下、メンテナンス工数の発生等、デバイス形成に悪影響を及ぼす。

[0014]

本発明は上記の問題点に鑑みてなされたものであり、デバイス形成工程での剥離を抑えることを目的とする。

【課題を解決するための手段】

[0015]

本発明の第1の側面は、半導体装置の製造方法に係り、分離領域と該分離領域の全体を 覆う半導体領域とを有する半導体基板を準備する工程と、前記半導体領域に1又は複数の 回路素子を形成する工程と、前記半導体基板を前記分離領域で分離する工程と、を含むこ とを特徴とする。

[0016]

本発明の第2の側面は、半導体装置の製造方法に係り、半導体領域を有する半導体基板

10

20

30

を準備する工程と、前記半導体領域に1又は複数の回路素子を形成する工程と、前記半導体基板に前記半導体領域によって全体が覆われた分離領域を形成する工程と、前記半導体基板を前記分離領域で分離する工程と、を含むことを特徴とする。

#### [0017]

本発明の第3の側面は、半導体装置に係り、分離領域と、前記分離領域の全体を覆う半導体領域と、前記半導体領域に形成された1又は複数の回路素子と、を含み、前記分離領域は、少なくとも前記1又は複数の回路素子が形成される領域の下方に形成されることを特徴とする。

#### 【発明の効果】

#### [0018]

本発明によれば、デバイス形成工程での剥離を抑えることができる。

【発明を実施するための最良の形態】

#### [0019]

本発明は、デバイス形成工程においては分離領域を露出させないことを特徴とする半導体基板及びその製造方法によって、デバイス形成工程では剥離又は分離が生じにくく、半導体基板の分離工程では容易に分離可能である半導体基板及びその製造方法を提供するものである。

# [0020]

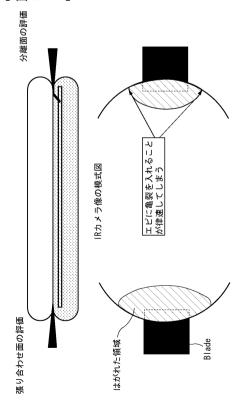

Maszaraらは、ウェーハの貼り合わせに際する接着強度の測定方法(以下「Maszara, J. Appl. Phys. 64 (1988) p.4943.を参照)。具体的には、貼り合わせたウェーハの周辺部からブレードを挿入し、ブレード端から剥離した領域の最大距離を測定することによって、貼り合わせ面の接着強度指標としての表面エネルギーを測定する方法である。

# [ 0 0 2 1 ]

本発明者らは、上記のMaszara法を用いて、半導体膜/分離領域/基板構造の一例として、シリコン単結晶膜/第1多孔質層/第2多孔質層(分離領域)/シリコン単結晶基板の構造を持つウェーハにおいて、剥離に要する強度を測定した。上記のウェーハは、表面を洗浄した後に、シリコンウェーハと重ね合わせて、1000 で2時間の熱処理を施すことによって、強固な結合強度が得られた。なお、貼り合わせ面よりも分離領域において半導体層が優先して剥離されることは予め確認されている。

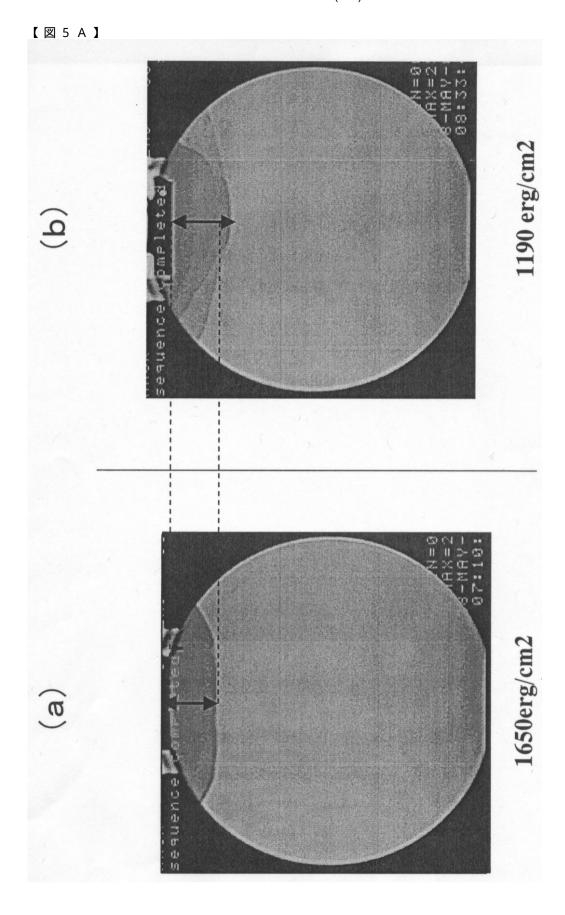

#### [0022]

図 5 A ( a ) は、貼り合わせウェーハにブレードを挿入し、赤外線カメラで剥離領域を 観 察 し た 像 を 示 す 図 で あ る 。 図 中 の 色 の 濃 い 領 域 は 、 剥 離 さ れ た 領 域 を 示 す 。 こ の 場 合 、 分離領域中に形成された剥離面の表面エネルギーは、Maszara法の計算式によって 、 1 6 5 0 e r g / c m <sup>2</sup> という値が得られた。一方、ブレード挿入時にウェーハ外周部 の位置において、剥離領域と未剥離領域の境界となるであろう部位付近に予めブレードを 軽 く 挿 入 し て 、 ウ ェ ー ハ 周 辺 部 の み で 半 導 体 層 を 剥 離 し た 後 に ブ レ ー ド を 挿 入 し た の が 図 5 A ( b ) である。この方式で剥離強度を測定したところ、分離領域に形成された剥離面 の表面エネルギーは1190erg/cm<sup>2</sup> であった。この差を解析したところ、図5A ( a ) の場合には、ウェーハ周辺部を剥離する際に、図 5 B に示すように剥離面が半導体 膜及び第1の多孔質層を破って分離領域に到達しなければならず、半導体膜及び第1の多 孔質層を破らなければならないため、図 5 A ( a ) においてウェーハ周辺部での剥離領域 が狭くなっており、表面エネルギー値が高く測定されたことが分かった。一方、図5A( b)では、予めプレードを挿入することによって、図 5 B に示すように半導体膜及び第 1 の多孔質層を破ってあるので、上記の測定で得られる表面エネルギーは分離領域に形成さ れ た 剥 離 面 の も の で あ る 。 こ の 実 験 結 果 は 、 デ バ イ ス 形 成 工 程 で 基 板 の 周 辺 部 が 他 の 部 材 等に接触して分離領域が露出すると、分離領域中に形成された場合には、半導体膜及び第 1の多孔質層を破る必要がないため、上述の場合と比べれば剥離され易く、本来の剥離面 の表面エネルギーが測定されている。

### [0023]

40

10

20

本発明は上記の知見に基づくものであり、デバイス形成工程において分離領域を露出させないことが可能な半導体基板及びその製造方法を提供するものである。本発明の好適な実施の形態に係る半導体基板は、半導体領域と、半導体領域の内部に形成された分離領域と、半導体領域の表面に形成された1又は複数の回路素子と、を備える。半導体基板は、少なくとも1又は複数の回路素子を形成することができる程度に十分に平坦な主面を有する。半導体膜及び分離領域は、半導体基板の主面上に膜を堆積することによって形成されてもよいし、半導体基板の主面の下方にイオン注入等の方法によって分離領域を形成し、その表層を半導体基板の主面の下方にイオン注入等の方法によって分離領域を形成し、その表層を半導体とすることによって形成されてもよい。半導体基板の形状は、板状であることが好ましく、円板状であることが更に好ましい。なお、半導体基板が円板状である場合には、ウェーハと呼ばれる。

[0024]

半導体膜は、1又は複数の回路素子の形成に適した材料を用いることが望ましい。このような材料としては、例えば、Si、SiGe、Ge等のIV族半導体、GaAs、InP、GaN等の化合物半導体、InGaAs、HgCdTe等の混昌半導体等の半導体等を用いることができる。また、これらの半導体は、単結晶の半導体であることが望ましい。

[0025]

半導体膜の形成方法としては、例えば、以下の(1)、(2)が挙げられる。

(1)分離領域の形成領域に分離領域を形成した後に、堆積法によって分離領域を覆う半 導体膜を形成する方法

( 2 ) 半導体基板の表面層を半導体層として、半導体基板の内部に分離領域を形成する方法

(2)の場合には、付加的に半導体膜を形成してもよい。半導体膜を形成する方法は特に限定されないが、例えば、CVD(熱CVD,プラズマCVD、光CVD等)、MBE法等を用いることができる。陽極化成によって多孔質層を形成した場合には、多孔質層上へ半導体膜を成長させる前に、多孔質の孔の内壁に窒化膜又は酸化膜等の保護膜を設ける保護膜形成工程や水素を含む雰囲気中で熱処理をする熱処理工程を行うことが好ましい。また、上記の保護膜形成工程の後に、熱処理工程を行ってもよい。その後、CVD法等により多孔質層上に半導体膜を形成し、通常の半導体製造プロセスを経て、半導体膜に1又は複数の回路素子を形成する。以下、本発明の好適な実施の形態について述べる。

(第1の実施形態)

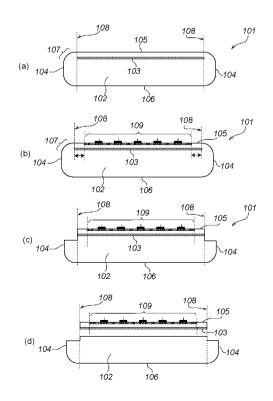

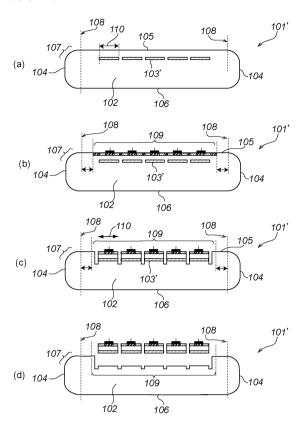

図1は、本発明の好適な第1の実施形態に係る半導体基板の製造工程を示す図である。 【0026】

[分離領域の形成]

まず、図1(a)に示す工程では、半導体基板101の内部に分離領域103を形成する。半導体基板101は、1又は複数の回路素子が形成される主面105と、その裏側に位置する裏面106と、主面105の主面端108の外側に位置する周辺部104は、略平坦な面を有する主面105の輪郭線にある主面端108の外側に位置する。周辺部104には、面取り加工が施された面取り部107が形成られる。面取り加工の方法としては、R加工やC加工等が挙げられるが、本発明はこれらの方法には限定されない。分離領域103は、その全体が半導体領域102で覆われ、外形のにこまには限定されない。分離領域103は、半導体基板101の声面105の下方近傍に形形がある。分離領域103は、半導体基板101にデバイスを形成した後の分離工程においるの方の方に、分離領域103は、半導体基板101にデバイスを形成した後の分離工程において、外力又はエネルギー等を外部から印加した際に、半導体領域102が優先的においるの方の方に、分離工程の前に半導体領域102とは構造、組成、欠陥密度等が異なる高欠陥密度層、(3)歪み蓄積層及び(4)物理特性の異なる層が挙げられる。これらの作別を度層、(3)歪み蓄積層及び(4)物理特性の異なる層が挙げられる。これらの作別に、構造、組成等は、特に限定されないが、例えば、以下の(1)~(4)が例示される

20

30

40

50

#### (1)多孔質層

多孔質層は、半導体基板中にスポンジ状に微小な空洞が形成された層である。多孔質層を多層構造にして、この中の特定の層を分離領域としてもよい。多孔質層の形成方法としては、例えば、陽極化成法、ステインエッチ法、希ガス(水素、ヘリウム等)のイオン注入、熱処理によるマイクロキャビティの形成等が挙げられる。ここでは、多孔質層の形成方法の一例として、シリコン基板を多孔質化して多孔質シリコンを形成する方法について述べる。多孔質シリコンの形成方法は特に限定されないが、例えば、陽極化成法が好適に用いられる。陽極化成法を用いてシリコン基板の主面を多孔質化する場合は、概略以下の方法による。

# [0027]

### (2)高欠陥密度層

高欠陥密度層は、ミスフィット転位、刃状転位等の結晶欠陥が他の領域と比べて高密度に導入された層である。結晶欠陥部分には、半導体基板のダングボンドが存在するので、外力等を加えたときに優先的に分離される。高欠陥密度層の作製方法としては、例えば、ヘテロエピタキシャル成長によって、ヘテロエピタキシャル層と基板との界る方法が挙げられることができ事人する方法が挙げられる。これで、マロエピタキシャル成長による場合には、例えば、以下の方法を用いることができずなわち、Si基板上にSiGe層(Ge濃度が例えば20%)を50nm形成した後に、半導体を形成する。この分離領域が形成されなり除去して分離領域が形成されない部分は、半導体基板の周辺部にマスクを被で大態で半導体基板をエッチングすることによって形成されてもよい。次にエッチング接置で半導体基板の周辺部のみにエッチング液を供給して半導体をエッチングすることによって形成されてもよい。次にで、半導体基板全面にSi層をエッチングする。

#### [0028]

また、半導体基板にイオン注入を行って、注入されたイオンの投影飛程近傍に結晶欠陥を導入してもよい。イオン注入による分離領域の形成は、半導体膜の形成前に行うことが 好適であるが、半導体膜形成後に行ってもよい。

#### 【 0 0 2 9 】

デバイス形成前にイオン注入する場合には、半導体基板の表面から所定の深さにイオン注入層を形成する。注入されるイオン種としては、水素又はヘリウムが好適である。イオン注入量が多い場合には、デバイス形成工程で熱処理により剥離現象が生じることがあるので、デバイス形成工程中に剥離が生じないように注入量を少なく設定することが望ましい。また、イオン注入の前に、チャネリングを防止するために、半導体基板の表面に熱酸化シリコン膜等のアモルファス膜を形成することが望ましい。また、イオン注入装置において、半導体基板を保持する冶具の形状を、半導体基板の周辺部にイオン注入されないように設計することによって本方法が実現される。また、イオン注入におけるイオンビーム

10

20

30

40

のスキャン領域を制御することによって、半導体基板の周辺部にはイオン注入されないようにしてもよいし、半導体基板の周辺部に予めイオン注入の投影飛程よりも厚い膜を形成 した後にイオン注入を行ってもよい。

#### [0030]

デバイス形成後にイオン注入する場合には、シリコン基板(又はエピタキシャル半導体基板)表面に形成された1又は複数の回路素子の表面上に、必要に応じて保護膜を形成した後に、所望の深さに水素等のイオンを注入して、分離領域として機能するイオン注入層を形成する。このように、デバイス形成後にイオン注入して、分離領域を形成することもできる。

# (3) 歪み蓄積層

歪み蓄積層は、格子定数の異なる層の界面、又は、半導体基板と格子定数の異なる層である。上記の高欠陥密度層のように、ミスフィット転位等の欠陥が導入されれば歪みが開放されるが、欠陥が導入されない程度に層が薄ければ、格子定数差に起因する歪みが層に蓄積される。このような歪みは、分離面に引き剥がし力を与えたときに、歪みが蓄積されている分だけ優先的に分離される。歪み蓄積層の作製方法としては、例えば、ヘテロエピタキシャル成長が挙げられる。この場合には、ミスフィット転位が導入される臨界膜厚以下に膜厚を設定する。また、多孔質シリコンは表面積が大きく、表面張力、孔の内壁に形成された酸化膜又は孔壁に吸収された水素によって、格子定数がシリコンと比べて10~3~4 程度異なるので、半導体基板がシリコンである場合に歪み蓄積層として好適である

#### (4)物理特性の異なる層

物理特性の異なる層は、例えば、熱膨張係数、熱伝導係数、光吸収率、比熱等が異なる層である。物理特性が異なる層の作製方法としては、例えば、Siに対してSiGe、サファイア基板に対してGaN膜等を堆積する方法が挙げられる。前者は熱伝導率が、後者は光吸収率がそれぞれ異なる。分離領域での分離は、このような物理特性の差を利用したものである。例えば、光吸収係数が異なれば、光照射による温度上昇速度が異なるので、基板と分離領域との間に熱膨張量の差が生じる。すなわち、基板と分離領域との界面近傍に内部応力が集中して優先的に分離される。

# [0031]

#### [分離領域の形成領域]

次に、分離領域の形成領域について述べる。本発明の好適な実施の形態では、半導体基板の端部で分離領域が露出しないように、分離領域の形成領域を規定する。デバイス形成工程での予期せぬ剥離の主原因は、デバイス形成工程において、半導体基板を装置に設置する際や搬送時に、半導体基板の端部が装置や搬送部材と接触することによって、半導体基板の端部に露出した分離領域から剥離が生じることである。半導体基板の端部で分離領域が露出しなければ、分離領域より上部の層が剥離防止被膜として機能する。

# [0032]

本実施形態では、装置や搬送部材と接触しうる半導体基板の端部に分離領域を設けず、本来分離すべき半導体基板の主面の1又は複数の回路素子が形成される領域(以下「素子形成領域」という。)の下部に分離領域を設置する。したがって、半導体基板の主面のうち、半導体基板の外周端から通常1~3mm程度の領域にはデバイスを形成しない。これは、デバイス形成工程で半導体基板を保持するときに、半導体基板の周辺部に冶具が接したり、半導体基板の周辺部の平坦度が良好でなかったり等の理由により、デバイス形成に適さない領域だからである。

#### [0033]

上述のように、分離領域の作製方法としては、半導体基板の表層を改質させてもよいし、半導体基板内に結晶欠陥を導入してもよいし、半導体基板の表面からイオンを注入してもよいし、半導体基板内に歪みを蓄積させてもよいし、半導体基板に物理特性の異なる膜を堆積してもよい。分離領域の形成領域を規定する方法としては、例えば、以下の(1)~(3)の方法が挙げられる。

20

10

30

50

20

30

40

50

- (1)多孔質層の非形成領域では、化成液が接しないようにし、多孔質層の形成領域では、化成液が接するようにする。このような方法としては、例えば、以下の(a)、(b)の方法が考えられる。

- (a) 多孔質層の非形成領域を化成装置内の構成部品で被覆し、多孔質層の形成領域を化成液に露出する。この場合、弗化水素耐性のある樹脂(フッ素系樹脂)又はフッ素ゴム等で非形成領域を被覆してもよいし、化成液に溶解しない材料で非形成領域を被覆してもよいし、気圧によって化成領域と非形成領域とを限定してもよい。

- (b)多孔質層の非形成領域に化成防止膜を形成し、多孔質層の形成領域を化成液に露出する。例えば、熱CVD法でSiN膜を形成し,基板裏面と主面の化成層を形成すべき領域のみSiN膜を除去する。化成防止膜としては、SiN膜、レジスト、SiO2膜等の他、導電型、比抵抗の異なるシリコン表層であってもよい。この場合には、化成領域と非化成領域の組み合わせとしては、以下に示す化成されやすさに基づき、化成領域に対して非化成領域が化成されにくい材料で構成されるように設定すればよい。

#### [0034]

化成されやすさ p + > p - > n + > n - (左に行くほど化成され易い)、ただし、 + 、 - は 導電率の大小を示す。

- (2)多孔質層を形成した後に、多孔質層の非形成領域における多孔質層を除去し、多孔質層の形成領域における多孔質層を残す。この方法は、多孔質のみならず、他の方式で形成する分離領域についても、同様に適用可能である。

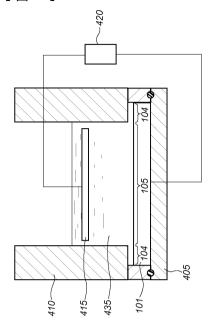

- (3)多孔質層が複数形成される場合は、複数の多孔質層のうち半導体層の形成に適した 半導体基板の表面に最も近い多孔質層を除いた層が分離領域となるため、例えば、多孔質 層が、第1多孔質層と第1多孔質層の下に位置する分離に好適な第2多孔質層との少なく とも2層で構成される場合には、第2の多孔質層が分離領域となり、第2多孔質層が形成 されない領域が分離領域が形成されない領域となる。すなわち、半導体基板の周辺部の分 離領域が形成されない領域に第1多孔質層が形成されていてもよい。このような構造は、 例えば、分離領域が形成されない領域での化成時の電流密度を分離領域が形成される領域 に比べて小さくすることによって形成されうる。例えば、図4は、このような陽極化成装 置の概略構成を示す図である。陽極化成装置の化成槽405は、電解質溶液435に対し て耐性を有する材料(例えば、四弗化エチレン樹脂)等によって構成されうる。化成槽4 0 5 内には、処理対象の基板 1 0 1 が配置される。基板 1 0 1 の表面は、分離領域が形成 される領域(主面)105と、分離領域が形成されない領域(周辺部)104と、に分け られる。電極415は、分離領域が形成される領域105に対向して配置され、絶縁部材 410は、分離領域が形成されない領域104に対向して配置される。より好ましくは、 絶 縁 部 材 4 1 0 と 分 離 領 域 が 形 成 さ れ な い 領 域 1 0 4 と の 間 の 距 離 を 、 電 極 4 1 5 と 分 離 領域が形成される領域105との間の距離より小さく配置する。

### [0035]

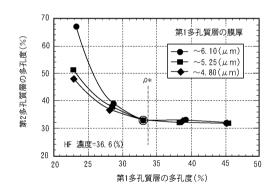

Pits and Pores II:Formation PropertiesandSignificance for Advanced Materials, P. Schumki, D. J. Lockwood, Y. H. Ogata, H.S. Isaacs, PV 2000-25, Phoenix, Arizona, Fall 2000 に掲載されている坂口らの報告(p.318-)(表題「Mechanismof Pore-Enlarg ement in Double Porous Si Layers」)によれば、図6に示すように、第1多孔質層の厚みが厚くなるにつれて第2多孔質層の多孔度(Porosity)が大きくなることが示されている。電流密度を小さくすると多孔質層の厚みは薄くなるので、上記設定によれば、分離領域が形成されない領域においては、第1多孔質層の膜厚は薄くなる。分離領域による分離性は、概ね多孔質層の多孔度が高い方が高いことが知られている。すなわち、上記したように電流密度分布を設定すれば、分離領域が形成されない領域には分離領域が形成される領域よりも低い多孔度(Porosity)の第2多孔質層が形成されるため、電流密度分布、弗化水素濃度等を適切に設定することによって、分離領域が形成されない領域には実質的に分離領域となる第2多孔質層が形成されない。

#### [0036]

半導体基板101の材料は、特に限定されないが、半導体素子形成工程での熱処理等に

20

30

40

50

(10)

耐えうるものが望ましい。このような材料としては、例えば、(1)Si、SiGe、Ge等のIV族半導体、GaAs、InP、GaN等の化合物半導体、InGaAs、HgCdTe等の混昌半導体等の半導体、(2)シリカ、石英、ガラス、サファイア等の絶縁体、(3)ステンレス等の金属が挙げられる。また、これらの半導体としては、CZ法、MCZ法、FZ法等で作製された単結晶の半導体だけでなく、表面が水素アニール処理された半導体、エピタキシャル成長法により形成された半導体等を用いることができる。

#### [0037]

# [回路素子の形成]

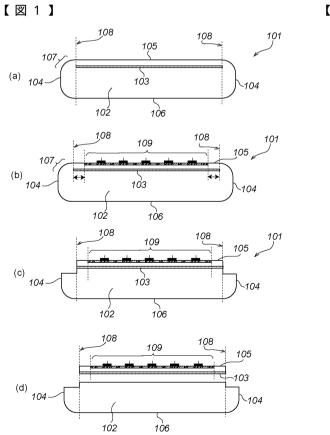

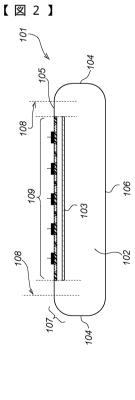

次いで、図1(b)に示す工程では、半導体基板101の半導体領域102に1又は複数の回路素子を形成する。1又は複数の回路素子は、半導体基板101の露光領域(素子領域)109に形成される。図3(a)は、露光領域109と半導体基板101の主面端108の内側には、露光装置の露光領域109が存在し、露光領域109に1又は複数の回路素子が形成される。露光領域109の外接円は、図1に示した分離領域103の上方に位置する。分離領域103は、半導体基板101の主面の全面に必ずしも形成される必要はなく、例えば、露光領域109よりも外側でかつ主面端108の内側の領域に形成されてもよいし、露光領域109の下方に形成されてもよい。好適には、分離領域103は、図2に示すように露光領域109の直下に形成される。

#### [0038]

上記の露光領域109には、ステッパー又はスキャナーと呼ばれる縮小投影型露光装置又は等倍投影型露光装置等によって、1又は複数の回路素子のパターンが焼き付けられる。例えば、ステッパーの場合、1回の最大露光領域は、例えば、26×33mm²である。この露光領域を1つの露光マスクで露光する。この際、露光領域109に形成される集積回路、デバイスチップは1つに限定されず、複数個含まれる。例えば、11×11mm²のチップの場合には、図3(a)に示すように2×3=6個のチップが一括で露光され、露光領域は22×33に設定される。また、図3(b)に示すように1個のチップを一つづつ露光してもよい。このように、半導体基板上の露光領域109を順次移動させることによって、半導体基板全面に露光領域109が形成される。

# [0039]

また、半導体基板の主面端の近傍は、半導体基板上の主面であっても、例えば、以下の(1)~(3)の理由から、素子又は集積回路が形成できない領域(周辺除外領域)が存在しうる。

(1)製造装置内で半導体基板を保持するときに、半導体基板の裏面又は周辺部では保持 しきれないため、半導体基板の表面にも半導体基板を保持するための冶具が接する。

(2)半導体基板の主面は、半導体基板の周辺部近傍では平坦度が低く、被露光面を露光装置の焦点深度内に収まるように制御できないため、パターンの加工精度が低い。

(3)半導体基板の主面は、半導体基板の周辺部では、成膜、エッチング、イオン注入等の均一性を確保することが難しい。

# [0040]

その結果、半導体基板の外周端から概ね2~5mmの領域が周辺除外領域となる。周辺除外領域は、半導体基板端を含む主面内の領域であって、半導体基板端から10mm以内、より好ましくは5mm以内、さらに好ましくは3mm以内の領域である。周辺除外領域は、より好ましくは、素子又は集積回路形成領域の外接円と主面端とで囲まれた領域と定義される。より好ましくは、分離領域は、主面内において素子形成に用いるステッパー等の縮小投影型露光装置の露光領域に形成され、かつ、周辺部には形成されない。なお、素子又は集積回路が形成できない領域(周辺除外領域)とは、素子又は集積回路を形成しても、出荷時の使用を満たし実質的に動作可能な素子又は集積回路が形成されない領域をいう。

#### [0041]

図3(b)に示すように、11x11mmチップを配置した場合には、周辺除外領域を

2 .5 mmとすることが好適である。さらに、最近では、上記したような課題を排して、周辺除外領域を縮小する傾向にある。いずれにしても、半導体基板主面の周辺部近傍に周辺除外領域が存在する。

#### [0042]

### [分離領域の露出]

次いで、図1(c)に示す工程では、半導体基板101の周辺部104を除去して分離領域103の一部を露出させる。すなわち、図1(b)に示すデバイス形成工程の後に、分離領域103が形成されていない領域にある半導体基板101の周辺部104を予め除去し、分離領域103の一部を露出させる。デバイス形成層等の分離領域103よりも上部の層は、分離防止被膜として作用して剥離を抑制するが、図1(c)に示す工程で分離領域103を意図的に露出させることによって、分離領域103が本来有する分離性を発揮することができる。このような露出領域は、半導体基板102の周辺部104全体である必要はなく、分離開始点のみを露出させることによっても、所望の目的を達することができる。図1(c)に示す工程は、図1(b)に示すデバイス形成工程より後であり、かつ、図1(d)に示す分離工程より前に行われる。

#### 【 0 0 4 3 】

このように、分離領域の周辺部の一部を露出させることにより、上記のような半導体膜等の分離領域上の膜を破る必要がなくなるため、分離工程において容易に分離できるようになる。分離領域の端面の露出工程は、特に限定されないが、例えば、以下の(1)~(3)の方法が選択されうる。

(1)研削、研磨等の機械的除去方法によって、半導体基板外周部を研削し、分離領域を 露出させる。

(2)エッチング等の化学的除去方法、特に、第2の部材と貼り合わせた後に分離する方法において、貼り合わせ後にエッチングを施して、半導体基板の周辺部を選択的にエッチングする。

(3) その他の方法としては、レーザー照射等を用いることができる。

# [0044]

#### [半導体基板の分離]

次いで、図1(d)に示す工程では、半導体基板101を分離領域103で分離する。分離領域103での分離方法は特に限定されないが、例えば、固体のクサビを半導体基板の周辺部から挿入して剥離する方法や半導体基板の周辺部の分離領域103の露出部に流体により圧力を印加する方法等が挙げられる。圧力を印加する方法としては、例えば、液体又は気体からなる流体を高圧のジェットとして分離領域103の側面に噴きつけたり、分離領域103に静圧を印加したり、流体のクサビを半導体基板周辺部から分離領域103に挿入したりする方法がある。また、半導体基板の両面を冶具等で固定して、両面から引っ張り力を印加して引き剥がす方法を用いてもよい。また、超音波等の振動エネルギーを分離面に印加して分離したり、加熱又は冷却によってデバイス形成層と半導体基板との間の熱膨張係数差による内部応力を利用して引き剥がしたりしてもよい。

### [0045]

流体で分離する場合には、水、エッチング液、アルコール等の液体、又は、空気、窒素ガス、アルゴンガス等の気体を用いることができる。静圧下(実質的に静止した流体による圧力下)で分離するには、例えば、次のような圧力印加機構を用いることができる。即ち、部材の周辺部の少なくとも一部を取り囲んで密閉空間を構成するための密閉空間構成部材、及び、前記密閉空間内に外部の空間よりも高い圧力が印加できる圧力印加機構である。

# [0046]

分離領域103を水素、窒素、ヘリウム、希ガス等のイオン注入により作製した場合には、400~600 程度の熱処理を施すことによって、イオン注入により形成される微小気泡層(マイクロバブル層、マイクロキャビティ層)が凝集するので、流体による圧力に加えて斯かる現象を利用して分離することもできる。また、CO<sub>2</sub> レーザー等により加熱し

20

30

40

てもよい。

# [0047]

分離に際し、半導体基板101に支持部材を接着層を介して貼り合わせておいてもよい。勿論、支持部材に貼り合わせる工程は省略してもよい。接着層としては、エポキシ系接着剤や他の接着剤を用いることができる。この際、接着する領域は、分離領域103を形成していない領域を含まないことが好ましい。また、予め分離領域103を露出させた場合には、露出領域が接着剤で覆われないようにすることが好ましい。

#### [0048]

分離後には、1又は複数の回路素子が形成された半導体基板を砥石又はレーザーによりダイシングして、1又は複数の回路素子毎に所望のサイズにチップ化することによって、単数或いは複数の薄膜半導体装置が得られる。なお、ダイシングによる切り込み溝の先端は、必ずしも接着層まで達しなくてもよい。このチップ化の際に切り込み溝を支持部材まで到達させておけば、支持部材に貼り合せたまま薄膜半導体装置をパッケージ台に載せ、その後、支持部材を取り除くことも可能である。薄膜半導体装置に残留した分離領域は、必要に応じて除去してもよい。

#### [0049]

チップ化後には、他の回路との接続或いはパッケージングを行うことができる。即ち、支持基体上に薄膜半導体装置を載置したり、プラスチックカード上に移設することもできる。また、残留した分離領域は、ゲッタリングサイトになり得るので、プロセス中の金属汚染耐性が増す。なお、デバイス層をパッケージ台に対して上面に配置してもよいし、デバイス層側を貼り合わせ面にしてもよい。

#### [0050]

分離領域側から行うチップ化は、通常用いられるダイシング装置を用いることができる他、エッチングやレーザーアブレーション、超音波カッター、高圧ジェット(例えば、ウォータージェット)等も用いることができる。エッチングにより行う場合は、HF+H2〇2、HF+HNO3、アルカリ溶液等のエッチング液を用いることができる。レーザーとしては、YAGレーザー、CO2レーザー、エキシマレーザー等を用いることができる

### [0051]

チップ化工程は、分離工程前に実施してもよいし、分離工程後に実施してもよい。また、それぞれのチップ間にLOCOSを形成したりメサエッチングしたりして、チップ間に 半導体膜が存在しないようにしてもよい。このようにして、部材は分離領域103で分離 される。

# [0052]

なお、分離、チップ化の工程としては、特開平 5 - 2 1 8 3 6 5 号公報、特開 2 0 0 2 - 2 3 1 9 1 2 号公報及び特開 2 0 0 2 - 2 3 1 9 0 9 号公報等に開示された方法等を適用できるが、本発明は特にこれらに限定されない。

#### [0053]

以上のように、図1(a)~(d)に示す工程によって、本発明の好適な実施の形態に係る半導体基板を作製することができる。本発明によれば、デバイスが形成されない半導体基板周辺部における分離領域の露出を排除し、分離領域より上部の層が剥離防止被膜として機能することによって、デバイス形成工程において、基板を装置に設置する際や搬送時に半導体基板周辺部が装置や搬送部材と接触することによって、半導体基板周辺部に不用意に露出した分離領域から予期せぬ剥離が生じることを抑えることができる。

#### [0054]

また、デバイス形成後に、分離工程の前に予め分離領域が形成されていない半導体基板周辺部の一部を除去し、分離領域の一部を意図的に露出させることによって、デバイス形成層等の分離領域より上部の層が分離防止被膜として機能することによる剥離の抑制を低減し、本来分離領域が有する分離性を発揮することが可能となる。さらに、予期せぬ分離を抑制することで、分離領域の分離性をより高めておくことが可能となる。

10

20

30

40

#### (第2の実施形態)

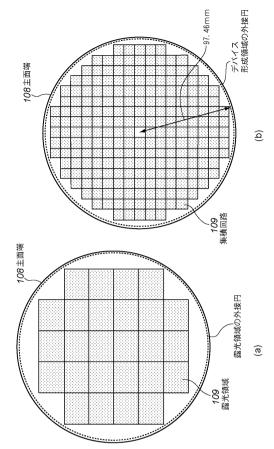

次に、本発明の好適な第2の実施形態について説明する。図7(a)~(d)は、本発明の好適な第2の実施形態に係る半導体基板の製造工程を示す図である。図7(a)~(d)は、本発明の好適な第2の実施形態に係る半導体基板の製造工程を示す図である。図7(a)の形態と同分離領域103′を形成する。第1の実施形態図7(c)に示す工程でダイシングを行う部分に分離領域103′を形成しない点で、第1のの形態とは相違する。すなわち、分離領域103′を形成しない点で、第1のの形態とは相違する。すなわち、分離領域103′は、1又は複数の回路素子が形成ったのののでである。図7(c)に示す工程では、半導体領域102に1又は複数の回路素を形成する。必要に応じてでは、半導体領域102のうち分離領域103′が形成されていない領域をダイシングによる。半導体領域102のうち分離領域103′が形成されていない領域をダイシングにより込み溝を入れ、分離領域103′を露出させるチップ化を行う。切り込み溝の大には切り込み溝を入れ、分離領域103′を露出させるチップ化された微小半導体領域と支持部材の界面付近又は接着層付近まで到達していることが望ましい。そ分離領域103′で分離する。

#### [0055]

このようして薄膜半導体装置が製造される。分離化工程でチップ化した後は、シリコン半導体基板に比べて分離面積が非常に小さくなっているので、引っ張り、圧縮、剪断等の外力を用いてもよいが、好ましくは上述の流体を用いて分離することが望ましい。また、分離領域に熱を加えることによって分離してもよい。特に、分離領域が水素等のイオン注入層により形成されている場合には、レーザー等により局所的な加熱を行ってもよい。なお、分離領域、半導体膜、半導体基板、1又は複数の回路素子に関しては、上記の第1の実施形態で説明したことをそのまま適用することができる。

#### [0056]

本実施形態においても、分離領域を半導体基板の周辺部に形成しないことによって、デバイス形成工程中での剥離を防止することができる。また、分離工程での分離性については、切り込み溝を入れて分離領域を露出させることにより高く維持することができる。

以下に本発明を実施例に基づき説明するが、本発明はこれらの実施例に限定されない。

# 【実施例1】

## [ 0 0 5 7 ]

比抵抗0.01 ・cm、P型の200mm 単結晶Si半導体基板を用意した、次いで、弗化水素溶液中において基板表面の陽極化成を行い、多孔質層を形成した。陽極化成条件は表1の通りであった。このとき、半導体基板周辺部に多孔質層が形成されないように、半径98mmの位置でフッ素樹脂(例えば、PTFE材)を接触させ、半導体基板の表面側の化成液と裏面側の化成液とが混ざらないように仕切りをした。これによって、半導体基板表面側の化成液と接触する面のみに多孔質層を形成することができる。なお、半導体基板の裏面側の化成液は、導電性であれば化成液でなくともよく、弗化水素を含むと酸化物を除去できるのでより好適である。

# [0058]

# 【表 1 】

| 陽極化成溶液                           |                                               |

|----------------------------------|-----------------------------------------------|

| ΗF                               | 42%                                           |

| C <sub>z</sub> H <sub>z</sub> OH | 9%                                            |

|                                  | 陽極化<br>HF<br>C <sub>2</sub> H <sub>2</sub> OH |

|     | 多孔質シリコン第1層 |                           |

|-----|------------|---------------------------|

|     | 電流密度       | 16 (mA·cm <sup>-2</sup> ) |

| (b) | 時間         | 2.5 (min)                 |

|     | 多孔質Si層の厚み  | β (μm)                    |

|     | 多孔質シリコン第2層 |                           |

|-----|------------|---------------------------|

|     | 電流密度       | 30 (mA·cm <sup>-2</sup> ) |

| (c) | 時間         | 0.5 (min)                 |

|     | 多孔質Si層の厚み  | 2 (µm)                    |

#### [0059]

形成された多孔質層を断面SEMで観察したところ、半径98mmの位置を境に、半導

20

30

40

体基板の中心に近い側には多孔質層が形成され、それより外側、周辺部及び半導体基板裏面には、多孔質層は形成されなかった。また、多孔質層を斜め研磨したのち、SEMで観察し、孔面積を計測して多孔度を求めたところ、第1層は多孔度20%、第2層は多孔度40%であった。次いで、この単結晶Si基板を400 の酸素雰囲気中で1時間酸化した。これによって、多孔質Siの孔の内壁は熱酸化膜で覆われた。その後、この多孔質Si層の表面をフッ酸に浸漬し、孔の内壁の酸化膜を残して、多孔質Si層の表面の酸化膜のみ除去した。次に多孔質Si層上にCVD(ChemicalVaporDeposition)法により単結晶Si層を3μmエピタキシャル成長した。成長条件は表2の通りである。

#### [0060]

#### 【表2】

| ソースガス | SiH <sub>2</sub> Cl <sub>2</sub> /H <sub>2</sub> |

|-------|--------------------------------------------------|

| ガス流量  | 0.3/40 l/min                                     |

| ガス圧力  | 80Torr                                           |

| 温度    | 900℃                                             |

#### [0061]

エピタキシャル成長に先立って、水素含有雰囲気中の熱処理を行った。これは、表面孔を封止するためである。この熱処理に加えて、微小なSi原子を原料ガス等により添加し、その表面孔封止用の原子を補ってもよい。こうして得られる部材は、通常用いられているエピ半導体基板と同一の半導体基板として扱うことが出来る。異なるのは、エピタキシャル層の下に多孔質Si層が形成されていることである。このエピタキシャル層に、マイクロプロセッサー、ロジックIC、メモリ等の回路を作製した。LSIの作製は、通常の工程を適用することにより、従来と同一の性能を持つLSIを作製できた。こうして出来たLSIを通常は裏面研削およびダイシングによるチップ化を行う。分離に先立ち、半導体基板の表面側の周辺部半径97.5mmより外側に砥石をあて、研削を行い、第2多孔質層を露出させた。この後、ここでは、前もって作製してあった第2多孔質層で半導体基板全面を、基板側とLSI側に分離する。分離は流体の圧力を利用した。具体的には、多孔質Si層側面に高圧のウォータージェットを噴きつけて分離を行った。

なお、流体としては以下のものを用いることができる。気体、液体、或いは、それらに固体の粒体・粉体を含有したものがある。この実施例では、ウォータージェット(以下「WJ」と記述する)用いたが、エアージェット、窒素ガスジェット、その他気体ジェット、水以外の液体ジェット、氷やプラスチック片、研磨材の混ざった流体ジェット、或いはこれらの静圧をかけることも可能である。流体は非常に微小な隙間へも流入し内部の圧力を上げることが可能で、外圧を分散して印加できることが特徴である。また、一部に極端に圧力がかからないことから、もっとも分離しやすい個所を選択的に分離させるという特徴がある。本発明のように、半導体デバイスがすでに作製されている薄層全面を分離するには、最適の手段である。なお、分離の際には表面側を他の支持部材で支えた方が好ましい

### [0062]

たとえば、フレキシブルなシート、ガラス基板、プラスチック基板、金属基板、他の半導体基板がある。これらの支持部材を接着剤でデバイス形成した基板の表面側と貼りあわせる。支持部材で支えた第1の基板のエッジ付近に流体を印加し、多孔質Si層を全面で分離する。流体を印加する際には、第1の基板エッジに多孔質Siを表出させておいた方が好ましい。さらには、多孔質Si部が凹状になるように表出させておくと、より流体の圧力を多孔質Si層に効率よく印加することができる。デバイス層側に残留した多孔質Siは、除去してもしなくてもよい。その後、デバイス層側をダイシングによってチップサイズに切り、それぞれのチップのパッケージングを行った。分離面をパッケージ台に乗せて、表面側からワイアーボンディングしてもよいし、表面を伏せてパッケージしてもよい。プラスチックカードに直接設置することで、ICカードを作製できる。

### 【実施例2】

10

20

30

#### [0063]

比抵抗 0 . 0 1 ・ c m、 P 型 の 2 0 0 m m 単結晶 S i 半導体基板を用意し、弗化水素溶液中において基板表面の陽極化成を行い、多孔質層を形成した。陽極化成条件は表 1 に示す実施例 1 と同じ条件であった。この際 , 半導体基板周辺部に半径 9 8 m m の位置より外側で、半導体基板から 0 . 1 m m 離れた位置にフッ素樹脂(例えば P T F E 材)からなる部材を設置した。また、表面側の化成液と半導体基板裏面側の化成液が混ざらないように、半導体基板を裏面側の外周でフッ素ゴムからなるハ゜ット゛で保持した。かかるハ゜ット゛には同心円状の溝があり、この溝内を真空引きすることでハ゜ット゛と半導体基板を密着させている。

### [0064]

形成された多孔質層を断面SEMで観察したところ、半径98mmの位置を境に半導体基板の中心に近い側には上記した第1多孔質層と第2層が形成されていた。多孔度について、多孔質層を斜め研磨したのち、SEMで観察し、孔面積を計測したところ、第1層は多孔度20%、第2層は多孔度40%であった。

#### [0065]

しかし、それより外側、ならびに周辺部には、第1多孔質層とほぼ同様な構造の多孔質層がおおよそ0.2μmの厚みで形成されているのみで第2多孔質層に相当する多孔度の層は形成されていなかった。これは半導体基板外周部において、半導体基板表面に近接する位置に部材を配置することで、該当部における電流密度を実質的に低下させたため、第1多孔質層の厚みが薄くなった。この結果、第2多孔質層を形成する際にも、第1多孔質層が薄いために第2多孔質層の多孔度があがらなかったためである。なお、半導体基板裏面には多孔質層は形成されていなかった。

#### [0066]

以後、実施例 1 と同様の方法でエピタキシャル成長層を形成し、デバイスを作製した。この後、第 2 の支持部材と接着材で張り合わせた。支持部材としては石英半導体基板を用いた。引き続いて、かかる貼り合わせ組をフッ硝酸の薬液に漬け、半導体基板外周部のおいて、デバイス形成層、エピタキシャルシリコン層等を除去し、第 2 多孔質層を露出させた。以後の工程は実施例 1 と同様とした。

# 【実施例3】

# [0067]

抵抗率14 ・cm、P型の単結晶Si基板を用意した。面方位は<100>であった。回路を形成する主面側から、所定の深さ(本実施例では、表面側から3μmの深さ)に水素イオンを注入してイオン注入層を形成した。注入量は、1×10 $^{1}$ 6~1×10 $^{1}$ 7/cm $^{2}$ 7であった。注入に際して、最表面にCVD法によりSiO $_{2}$ 保護膜を形成しておいてもよい。この際、半導体基板外周部半径99mmより外側はイオンが照射されないように冶具で保護した。この単結晶Si基板表面に、マイクロプロセッサー、ロジックIC、メモリ等の回路形成層を作製した。次に、半導体基板の外周部に常圧プラズマを照射し、デバイス形成層、ならびに、単結晶Si層をエッチングした。デバイス形成層と支持部材としてのプラスチック基板(或いはガラス基板、Si基板、フレキシブルフィルム、接着テープでもよい。)を接着剤で貼り合わせた。その後、窒素ガスをイオン注入層側面に噴きつけて分離工程を行った。そして、実施例1と同様にチップ化工程を行いICカードを作製した。

#### 【図面の簡単な説明】

# [0068]

- 【図1】本発明の好適な第1の実施形態に係る半導体基板の製造工程を示す図である。

- 【図2】本発明の好適な第1の実施形態に係る他の半導体基板を示す図である。

- 【図3】露光領域と半導体基板の主面端との関係を示す図である。

- 【図4】陽極化成装置の概略構成を示す図である。

- 【 図 5 A 】貼り合わせウェーハにブレードを挿入し、赤外線カメラで剥離領域を観察した 像を示す図である。

- 【図5B】図5Aの像を模式的に示す図である。

10

20

30

【図 6 】第 1 多孔質層の膜厚をパラメータとして第 1 多孔質層と第 2 多孔質層の間の多孔度の関係を示す図である。

【図7】本発明の好適な第2の実施形態に係る半導体基板の製造工程を示す図である。

【図3】

【図4】

【図5B】

【図6】

# 【図7】

# フロントページの続き

(72)発明者 木戸 滋

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 桃井 一隆

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内