# (19) 国家知识产权局

# (12) 发明专利

(10) 授权公告号 CN 114548169 B (45) 授权公告日 2023. 04. 21

(21)申请号 202210156761.0

(22)申请日 2022.02.21

(65) 同一申请的已公布的文献号 申请公布号 CN 114548169 A

(43) 申请公布日 2022.05.27

(73) **专利权人** 电子科技大学 **地址** 611731 四川省成都市高新区(西区) 西源大道2006号

(72) **发明人** 赵文浩 刘科 刘航麟 郭广坤 付在明 肖寅东 张朋 侯东 田书林

(74) 专利代理机构 成都行之智信知识产权代理 有限公司 51256

专利代理师 温利平

(51) Int.CI.

G06F 18/00 (2023.01) G06F 18/10 (2023.01)

(56) 对比文件

CN 102868650 A,2013.01.09

CN 111835434 A, 2020.10.27

US 6400415 B1,2002.06.04

武长春.任意波形发生器幅频校正方法研究及模块设计.中国优秀硕士学位论文全文数据库(工程科技Ⅱ辑).2011,C042-484.

Yindong Xiao 等.An Algorithm for Selecting Sampling Rate in Arbitrary Waveform Generator.2018 IEEE AUTOTESTCON.2018,全文.

审查员 杏运

权利要求书2页 说明书6页 附图5页

#### (54) 发明名称

一种任意波形发生器输出幅频响应校正方 法

#### (57) 摘要

本发明公开了一种任意波形发生器输出幅频响应校正方法,首先通过扫频法获取带宽内N个等间隔频点的幅度值,并且通过调整DAC参考电流/或者电压保证幅度值最低的频点仍能满足合成系统输出幅度的最大值,以便后续通过滤波器进行幅度校正;在调整后,再次测量这N个频点输出的幅度值,并根据测量值计算出合成系统的幅频响应,并推算出校正滤波器的幅频响应;最后,利用最大最小化设计方法,获得校正滤波器系数,实现全频带幅频校正,降低输出宽带信号的幅度失真。

- 1.一种任意波形发生器输出幅频响应校正方法,其特征在于,包括以下步骤:

- (1)、记任意波形发生器的输出幅度最大设置值 $Amp_{max}$ ,输出有效带宽为 $f_{band}$ ,内部DAC的参考电压调节范围为 $V_{min}\sim V_{max}$ ,内部DAC的参考电压初始默认值为: $\frac{V_{max}+V_{min}}{2}$  ;

- (2)、采用扫频法获取任意波形发生器输出的幅频特性;

- (2.1)、将任意波形发生器的有效输出带宽为f<sub>band</sub>等间隔均分为N个频率值,记为:

$$f_0, f_1, \dots, f_{N-1} = \frac{f_{band}}{N}, \frac{2f_{band}}{N}, \dots, f_{band};$$

- (2.2)、设置任意波形发生器的输出幅度值为 $Amp_{max}$ 、偏移为0、输出频率依次为 $f_0$ , $f_1$ ,…, $f_{N-1}$ ;利用测量仪器分别测量任意波形发生器输出的N个正弦信号的幅度值,记为: $Amp_0$ , $Amp_1$ ,…, $Amp_{N-1}$ ;

- (2.3)、在N个正弦信号的幅度值中找到幅度值最小对应的频点,记为 $f_i$ ,其幅度值记为  $Amp_i$ ;

- (2.4)、设置任意波形发生器的输出幅度值为 $Amp_{max}$ 、偏移为0、输出频率为 $f_i$ ;利用测量仪器测量任意波形发生器输出的正弦信号的幅度值 $Amp_i$ ,若输出的幅度值 $Amp_i$ 等于最大幅度值 $Amp_{max}$ ,则保持任意波形发生器当前状态不变;否则,调节DAC的参考电流或参考电压让输出幅度发生改变 $Amp_{adjust}$ ,使得 $Amp_{max} = Amp_i \pm Amp_{adjust}$ ;

- (2.5)、保持任意波形发生器当前状态不变,将输出频率分别调整为输出频率依次为 $f_0$ ,  $f_1$ ,…, $f_{N-1}$ ,再次按照步骤 (2.2) 测试各频点的输出幅度,记为:

$$\mathrm{Amp_0}'$$

,  $\mathrm{Amp_1}'$  ,  $\cdots$  ,  $\mathrm{Amp_i}' \cdots$  ,  $\mathrm{Amp_{N-1}}'$  ;

- (3)、设计用于幅频校正的数字滤波器:

- (3.1)、根据步骤(2.5)调整后的输出幅度值计算任意波形发生器的通带幅频响应为:

$$|G(e^{jw_k})| = \frac{Amp_k'}{Amp_i'}, w_k = 2\pi \cdot f_k, k = 0, 1, 2, ..., N-1;$$

(3.2)、校正滤波器的幅频响应在通带内应与系统的幅频响应互补,即  $|G(e^{jw_k})||G_{comp}(e^{jw_i})|=1$ ;在阻带内幅频响应为0,同时为了防止过渡带下降过快导致通带内幅频响应纹波较大,过渡带的幅频响应应平滑下降,则校正滤波器的幅频响应满足:

$$\left|G_{comp}\left(e^{jw_{i}}\right)\right| = \begin{cases} \frac{Amp_{i}^{'}}{Amp_{k}^{'}} & w_{i} \in [0, w_{pass}], \quad w_{pass} = 2\pi \cdot f_{band} \\ \frac{Amp_{i}^{'}}{Amp_{k}^{'}} (1 - \frac{i - N}{N_{trans-zone}}) & w_{i} \in \left(w_{pass}, w_{stop}\right) \\ 0 & w_{i} \in \left(w_{stop}, \pi\right) \end{cases}$$

其中,w<sub>stop</sub>为滤波器截止带,N<sub>trans-zone</sub>为过渡带频点数;

- (3.3)、利用最大最小化设计方法计算出幅频特性满足步骤(3.2)的m阶有限冲击响应滤波器系数,记为:h(0),h(1),…,h(m-1);

- (4)、将步骤(3)获得的幅频校正滤波器添加到任意波形发生器中;

在任意波形发生器的FPGA与DAC之间添加幅频校正滤波器,利用幅频校正滤波器对任意波形发生器输出幅频响应进行校正;

$$x'(n) = \sum_{i=0}^{m} x(n-i) \cdot h(i)$$

其中,x(n)为校正前的数据,x'(n)为校正后的数据。

# 一种任意波形发生器输出幅频响应校正方法

#### 技术领域

[0001] 本发明属于波形发生器技术领域,更为具体地讲,涉及一种任意波形发生器输出幅频响应校正方法。

## 背景技术

[0002] 任意波形发生器是一种广泛应用于电子装备、设备研制、生产和维护保障的信号源,可解决真实信号场景难以复现或风险代价极高等问题。如雷达的整机调试和性能鉴定,全部采用真实目标(如飞机)给雷达提供测试信号,不仅花费大量的人力和物力,影响研制进度,甚至在某些情况下(如恶劣天气)无法实现,宽带任意波形发生器是解决这一难题的理想工具。随着现代通信、航空航天探测、人工智能、雷达侦查等相关电子信息领域的高速发展,电子系统变得越来越庞大,电子信号的复杂程度也越来越高,尤其是信号的频率范围不断拓宽。然而,模拟器件难以保证宽带信号幅频响应的平坦性,导致输出的宽带信号幅度失真,因此对于作为关键测试设备的任意波形发生器实现宽带信号的幅频校正尤为重要。

[0003] 在以往的校准方法中,通常通过扫频方法获取频带内单音信号的幅度值,然后通过调节输出幅度设置值使得实际输出幅度值接近理想值,并记录该频点的幅度调节系数,最终将所有调节系数存入波形合成系统中,在输出不同频率值时调用对应调节系数的方法实现任意波形发生器的校准,该方法针对单频点输出信号是切实有效的。但在输出宽带信号时,由于不同频点的调节系数不一致,因此无法通过该方法实现幅度校准。因此,本发明针对传统任意波形发生器无法实现宽带信号幅度校准的问题,提出了一种基于数字滤波器的宽带任意波形合成系统幅频校正方法。

#### 发明内容

[0004] 本发明的目的在于克服现有技术的不足,提供一种任意波形发生器输出幅频响应校正方法,采用数字滤波器调整每个频点的幅频响应,这样有利于同时校正多个频点实现宽带信号的幅频校正。

[0005] 为实现上述发明目的,本发明提出一种任意波形发生器输出幅频响应校正方法, 其特征在于,包括以下步骤:

[0006] (1)、记任意波形发生器的输出幅度最大设置值 $\mathrm{Amp}_{\mathrm{max}}$ ,输出有效带宽为 $\mathrm{f}_{\mathrm{band}}$ ,内部 DAC的参考电压调节范围为 $\mathrm{V}_{\mathrm{min}}$ ~ $\mathrm{V}_{\mathrm{max}}$ ,内部DAC的参考电压初始默认值为: $\frac{V_{\mathrm{max}}+V_{\mathrm{min}}}{2}$  ;

[0007] (2)、采用扫频法获取任意波形发生器输出的幅频特性;

[0008] (2.1)、将任意波形发生器的有效输出带宽为f<sub>hand</sub>等间隔均分为N个频率值,记为:

$$f_0, f_1, \dots, f_{N-1} = \frac{f_{band}}{N}, \frac{2f_{band}}{N}, \dots, f_{band};$$

[0009] (2.2)、设置任意波形发生器的输出幅度值为 $Amp_{max}$ 、偏移为0、输出频率依次为 $f_0$ ,  $f_1, \cdots, f_{N-1}$ ;利用测量仪器分别测量任意波形发生器输出的N个正弦信号的幅度值,记为:

$Amp_0$ ,  $Amp_1$ ,  $\cdots$ ,  $Amp_{N-1}$ ;

[0010] (2.3)、在N个正弦信号的幅度值中找到幅度值最小对应的频点,记为 $f_i$ ,其幅度值记为 $f_i$ ,

[0011] (2.4)、设置任意波形发生器的输出幅度值为 $Amp_{max}$ 、偏移为0、输出频率为 $f_i$ ;利用测量仪器测量任意波形发生器输出的正弦信号的幅度值 $Amp_i$ ,若输出的幅度值 $Amp_i$ 等于最大幅度值 $Amp_{max}$ ,则保持任意波形发生器当前状态不变;否则,调节DAC的参考电流或参考电压让输出幅度发生改变 $Amp_{adjust}$ ,使得 $Amp_{max} = Amp_i \pm Amp_{adjust}$ ;

[0012] (2.5)、保持任意波形发生器当前状态不变,将输出频率分别调整为输出频率依次为 $f_0$ , $f_1$ ,…, $f_{N-1}$ ,再次按照步骤 (2.2) 测试各频点的输出幅度,记为:

[0013]  $Amp_0', Amp_1', \dots, Amp_i' \dots, Amp_{N-1}';$

[0014] (3)、设计用于幅频校正的数字滤波器;

[0015] (3.1)、根据步骤(2.5)调整后的输出幅度值计算任意波形发生器的通带幅频响应为:

[0016]

$$\left| G\left(e^{jw_k}\right) \right| = \frac{Amp_k'}{Amp_i'}, w_k = 2\pi \cdot f_k, k = 0, 1, 2, ..., N-1;$$

[0017] (3.2)、校正滤波器的幅频响应在通带内应与系统的幅频响应互补,即  $|G(e^{jw_k})||G_{comp}(e^{jw_i})|=1$ ;在阻带内幅频响应为0,同时为了防止过渡带下降过快导致通带内幅频响应纹波较大,过渡带的幅频响应应平滑下降,则校正滤波器的幅频响应满足:

$$\left| G_{comp} \left( e^{jw_i} \right) \right| = \begin{cases} \frac{Amp_i'}{Amp_k'} & w_i \in [0, w_{pass}], \quad w_{pass} = 2\pi \cdot f_{band} \\ \frac{Amp_i'}{Amp_k'} \left( 1 - \frac{i - N}{N_{trans-zone}} \right) & w_i \in \left( w_{pass}, w_{stop} \right) \\ 0 & w_i \in \left( w_{stop}, \pi \right) \end{cases}$$

[0019] 其中, $w_{\text{stop}}$ 为滤波器截止带, $N_{\text{trans-zone}}$ 为过渡带频点数;

[0020] (3.3)、利用最大最小化设计方法计算出幅频特性满足步骤 (3.2) 的m阶有限冲击响应滤波器系数,记为:h(0),h(1),…,h(m-1);

[0021] (4)、将步骤(3)获得的幅频校正滤波器添加到任意波形发生器中;

[0022] 在任意波形发生器的FPGA与DAC之间添加幅频校正滤波器,利用幅频校正滤波器对任意波形发生器输出幅频响应进行校正;

[0023]

$$x'(n) = \sum_{i=0}^{m} x(n-i) \cdot h(i)$$

[0024] 其中,x(n)为校正前的数据,x'(n)为校正后的数据。

[0025] 本发明的发明目的是这样实现的:

[0026] 本发明一种任意波形发生器输出幅频响应校正方法,首先通过扫频法获取带宽内N个等间隔频点的幅度值,并且通过调整DAC参考电流/或者电压保证幅度值最低的频点仍能满足合成系统输出幅度的最大值,以便后续通过滤波器进行幅度校正;在调整后,再次测量这N个频点输出的幅度值,并根据测量值计算出合成系统的幅频响应,并推算出校正滤波器的幅频响应;最后,利用最大最小化设计方法,获得校正滤波器系数,实现全频带幅频校正,降低输出宽带信号的幅度失真。

[0027] 同时,本发明一种任意波形发生器输出幅频响应校正方法还具有以下有益效果:

[0028] (1)、本发明利用数字滤波器实现不同频点的幅频校正,改变输出波形频率时无需通过调整幅度设置系数来校正幅度,避免了波形频率信息和幅度信息存在耦合关系;

[0029] (2)、本发明利用数字滤波器可同时对多个频点幅度值进行校正,实现宽带信号的幅频校正:

[0030] (3)、本发明采用高性能FPGA,在实现高速数据合成和发送的同时,可直接利用其丰富的逻辑资源完成基于数字滤波器的幅频校正,另外FPGA作为可编程逻辑器件,还具有便于设计任意做调试、用户二次开发和定制自身所需功能的优点。

### 附图说明

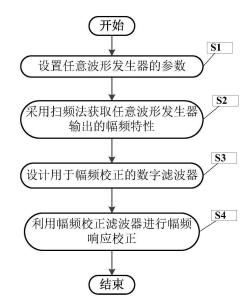

[0031] 图1是本发明一种任意波形发生器输出幅频响应校正方法流程图:

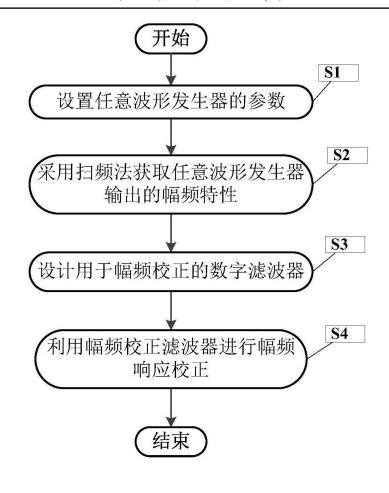

[0032] 图2是任意波形发生器的输出幅频响应图;

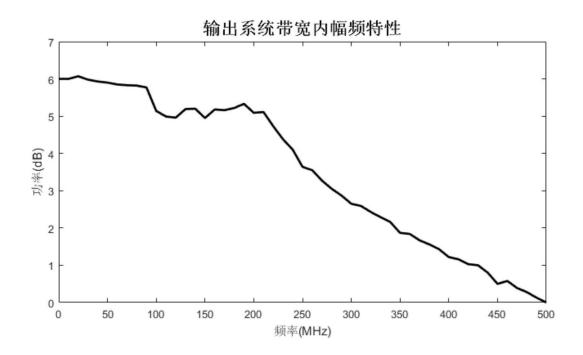

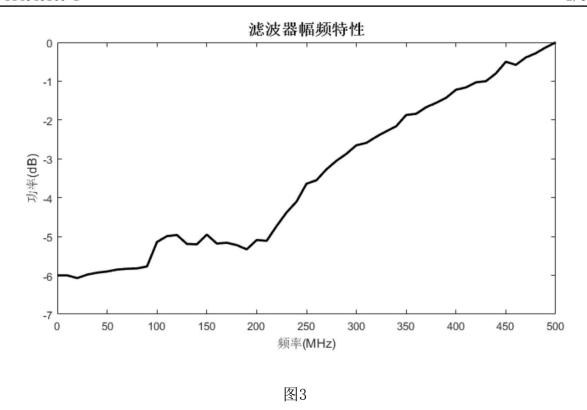

[0033] 图3是幅频校正滤波器的幅频响应与任意波形发生器的输出幅频响应的互补示意图:

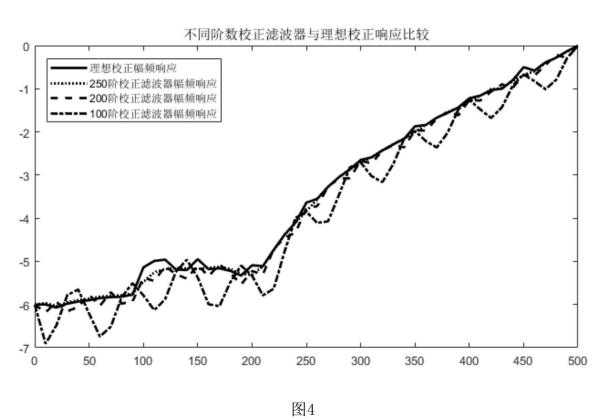

[0034] 图4是幅频校正滤波器的幅频响应与理想校正响应的对比图;

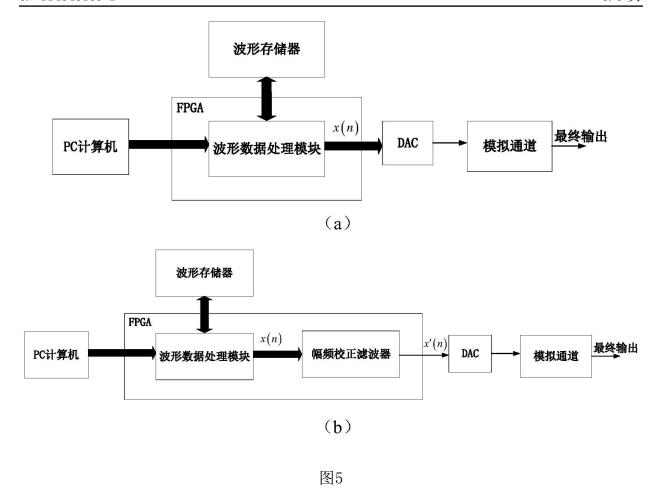

[0035] 图5是任意波形发生器添加幅频校正滤波器的对比图;

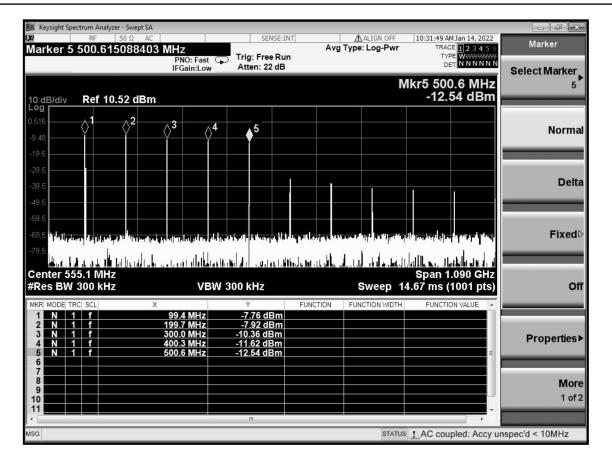

[0036] 图6是添加幅频校正滤波器前任意波形发生器的输出幅频响应;

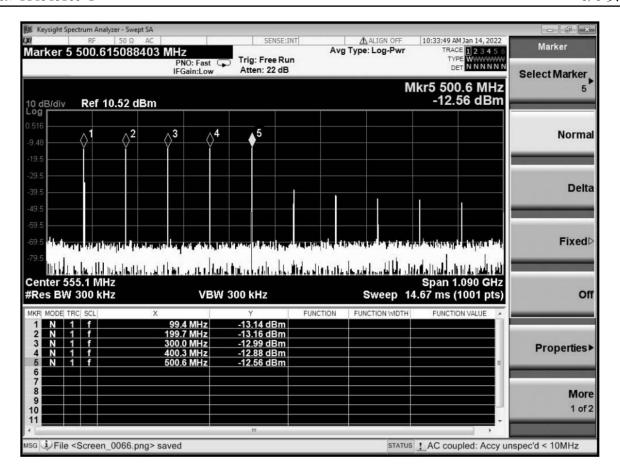

[0037] 图7是添加幅频校正滤波器后任意波形发生器的输出幅频响应。

## 具体实施方式

[0038] 下面结合附图对本发明的具体实施方式进行描述,以便本领域的技术人员更好地理解本发明。需要特别提醒注意的是,在以下的描述中,当已知功能和设计的详细描述也许会淡化本发明的主要内容时,这些描述在这里将被忽略。

[0039] 实施例

[0040] 在本实施例中,如图1所示,本发明一种任意波形发生器输出幅频响应校正方法,包括以下步骤:

[0041] S1、记任意波形发生器的输出幅度最大设置值Amp<sub>max</sub>,输出有效带宽为 $f_{band}$ ,内部DAC的参考电压调节范围为 $V_{min}\sim V_{max}$ ,内部DAC的参考电压初始默认值为: $\frac{V_{max}+V_{min}}{2}$  ;

[0042] 在本实施例中,将DAC的参考电流或参考电压设置为中间值的目的是为了保证后续步骤中,可以将幅频特性的最低点的输出幅度值调节至设置幅度值一致。

[0043] S2、采用扫频法获取任意波形合成系统输出的幅频特性;

[0044] 在本实施例中,任意波形发生器的有效输出带宽为500MHz,我们以10MHz为起始,

以10MHz为间隔对任意波形发生器的输出带宽进行扫频测试,设置输出幅度为0.75Vpp (1.48dBm),偏移为0V,测得输出幅度与频点的对应关系如表1所示。

[0045] 表1是各频点及对应输出幅度;

| 频率     | 测试幅度     | 频率     | 测试幅度     | 频率     | 测试幅度     |

|--------|----------|--------|----------|--------|----------|

| 10MHz  | 0.16dBm  | 180MHz | -0.62dBm | 350MHz | -3.84dBm |

| 20MHz  | 0.23dBm  | 190MHz | -0.51dBm | 360MHz | -4.00dBm |

| 30MHz  | 0.14dBm  | 200MHz | -0.5dBm  | 370MHz | -4.17dBm |

| 40MHz  | 0.09dBm  | 210MHz | -0.73dBm | 380MHz | -4.29dBm |

| 50MHz  | 0.06dBm  | 220MHz | -1.11dBm | 390MHz | -4.41dBm |

| 60MHz  | 0.01dBm  | 230MHz | -1.46dBm | 400MHz | -4.55dBm |

| 70MHz  | -0.01dBm | 240MHz | -1.74dBm | 410MHz | -4.68dBm |

| 80MHz  | -0.02dBm | 250MHz | -2.01dBm | 420MHz | -4.81dBm |

| 90MHz  | -0.07dBm | 260MHz | -2.29dBm | 430MHz | -4.94dBm |

| 100MHz | -0.35dBm | 270MHz | -2.57dBm | 440MHz | -5.04dBm |

| 110MHz | -0.56dBm | 280MHz | -2.79dBm | 450MHz | -5.14dBm |

| 120MHz | -0.63dBm | 290MHz | -2.97dBm | 460MHz | -5.26dBm |

|        |          |        |          |        |          |

[0047]

[0046]

| 130MHz | -0.65dBm | 300MHz | -3.11dBm | 470MHz | -5.45dBm |

|--------|----------|--------|----------|--------|----------|

| 140MHz | -0.64dBm | 310MHz | -3.25dBm | 480MHz | -5.56dBm |

| 150MHz | -0.63dBm | 320MHz | -3.41dBm | 490MHz | -5.71dBm |

| 160MHz | -0.66dBm | 330MHz | -3.55dBm | 500MHz | -5.84dBm |

| 170MHz | -0.68dBm | 340MHz | -3.68dBm |        |          |

[0048] 由上表可知,在500MHz处输出幅度最低为-5.84dBm与设置值相差7.32dBm。因此,可通过调节放大器放大倍数以及DAC电流调节,使得500MHz处输出幅度达到设置值需求,那么,调整后各频点的输出幅度如表2所示;

[0049] 表2调整后各频点及对应输出幅度;

[0050]

| 频率     | 测试幅度    | 频率     | 测试幅度    | 频率     | 测试幅度    |

|--------|---------|--------|---------|--------|---------|

| 10MHz  | 7.48dBm | 180MHz | 6.70dBm | 350MHz | 3.35dBm |

| 20MHz  | 7.55dBm | 190MHz | 6.81dBm | 360MHz | 3.32dBm |

| 30MHz  | 7.43dBm | 200MHz | 6.57dBm | 370MHz | 3.15dBm |

| 40MHz  | 7.36dBm | 210MHz | 6.59dBm | 380MHz | 3.04dBm |

| 50MHz  | 7.34dBm | 220MHz | 6.21dBm | 390MHz | 2.91dBm |

| 60MHz  | 7.34dBm | 230MHz | 5.86dBm | 400MHz | 2.70dBm |

| 70MHz  | 7.31dBm | 240MHz | 5.58dBm | 410MHz | 2.64dBm |

| 80MHz  | 7.29dBm | 250MHz | 5.12dBm | 420MHz | 2.51dBm |

| 90MHz  | 7.13dBm | 260MHz | 5.03dBm | 430MHz | 2.48dBm |

| 100MHz | 6.62dBm | 270MHz | 4.75dBm | 440MHz | 2.28dBm |

| 110MHz | 6.47dBm | 280MHz | 4.53dBm | 450MHz | 1.98dBm |

| 120MHz | 6.44dBm | 290MHz | 4.35dBm | 460MHz | 2.18dBm |

| 130MHz | 6.42dBm | 300MHz | 4.13dBm | 470MHz | 2.06dBm |

| 140MHz | 6.67dBm | 310MHz | 4.07dBm | 480MHz | 1.87dBm |

| 150MHz | 6.43dBm | 320MHz | 3.91dBm | 490MHz | 1.61dBm |

|--------|---------|--------|---------|--------|---------|

| 160MHz | 6.62dBm | 330MHz | 3.77dBm | 500MHz | 1.48dBm |

| 170MHz | 6.64dBm | 340MHz | 3.64dBm |        |         |

[0051] S3、设计用于幅频校正的数字滤波器;

[0052] 根据S2获得的测试值以及公式

[0053]

$$\left| G\left(e^{jw_k}\right) \right| = \frac{Amp_k'}{Amp_i'}, w_k = 2\pi \cdot f_k, k = 0, 1, 2, ..., N-1$$

[0054] 可以获得校正前任意波形发生器在通带内的输出幅频响应,如图2所示。幅频校正的目的是为了输出信号在通带内幅度保持一致,即

[0055]

$$\left|G\left(e^{jw_k}\right)\right|\left|G_{comp}\left(e^{jw_i}\right)\right|=1$$

[0056] 同时,为了防止过渡带下降过快导致通带内幅频响应纹波较大,过渡带的幅频响 应应平滑下降,则校正滤波器的幅频响应满足:

$$\left| G_{comp} \left( e^{jw_i} \right) \right| = \begin{cases} \frac{Amp_i'}{Amp_k'} & w_i \in [0, w_{pass}], \quad w_{pass} = 2\pi \cdot f_{band} \\ \frac{Amp_i'}{Amp_k'} \left( 1 - \frac{i - N}{N_{trans-zone}} \right) & w_i \in \left( w_{pass}, w_{stop} \right) \\ 0 & w_i \in \left( w_{stop}, \pi \right) \end{cases}$$

[0058] 因此,校正滤波器的幅频响应与任意波形发生器的输出幅频响应互补如图3所示。以500MHz输出幅度为基础,可计算出频点的幅度校正系数如表3所示;

[0059] 表3是幅频校正系数表;

[0060]

| 频率     | 幅频响应   | 频率     | 幅频响应   | 频率     | 幅频响应   |

|--------|--------|--------|--------|--------|--------|

| 10MHz  | 0.5012 | 180MHz | 0.5483 | 350MHz | 0.8063 |

| 20MHz  | 0.4972 | 190MHz | 0.5414 | 360MHz | 0.8091 |

| 30MHz  | 0.5023 | 200MHz | 0.5565 | 370MHz | 0.8251 |

| 40MHz  | 0.5052 | 210MHz | 0.5553 | 380MHz | 0.8356 |

| 50MHz  | 0.5070 | 220MHz | 0.5801 | 390MHz | 0.8482 |

| 60MHz  | 0.5099 | 230MHz | 0.6039 | 400MHz | 0.8690 |

| 70MHz  | 0.5111 | 240MHz | 0.6237 | 410MHz | 0.8750 |

| 80MHz  | 0.5117 | 250MHz | 0.6577 | 420MHz | 0.8882 |

| 90MHz  | 0.5146 | 260MHz | 0.6645 | 430MHz | 0.8913 |

| 100MHz | 0.5534 | 270MHz | 0.6863 | 440MHz | 0.9120 |

| 110MHz | 0.5630 | 280MHz | 0.7039 | 450MHz | 0.9441 |

| 120MHz | 0.5649 | 290MHz | 0.7186 | 460MHz | 0.9354 |

| 130MHz | 0.5502 | 300MHz | 0.7371 | 470MHz | 0.9561 |

|--------|--------|--------|--------|--------|--------|

| 140MHz | 0.5495 | 310MHz | 0.7422 | 480MHz | 0.9683 |

| 150MHz | 0.5656 | 320MHz | 0.7560 | 490MHz | 0.9851 |

| 160MHz | 0.5508 | 330MHz | 0.7682 | 500MHz | 1      |

| 170MHz | 0.5521 | 340MHz | 0.7798 |        |        |

[0061] 设幅频响应校正滤波器的阶数为m,则滤波器的频响为

[0062]

$$\left| G_{comp} \left( e^{jw} \right) \right| = \sum_{i=0}^{m-1} h_{comp}(i) \cdot e^{-jwi}$$

[0063] 利用最大最小化设计方法,可根据表3的数据和上式计算出幅频校正滤波器的系数h<sub>comp</sub>。校正滤波器的幅频响应随着滤波器阶数的提升而更加逼近所需的校正效果,如图4 所示。100阶滤波器的幅频响应与理想的校正幅频响应仍存在±1dB的误差,而当滤波器阶数达到250时,滤波器的幅频响应已基本趋于理想的校正幅频响应。然而,滤波器阶数越大意味着将在FPGA中消耗更多的硬件资源。因此,在实际应用中,需根据实际需求选择合适的滤波器阶数,以通过最少的硬件资源实现所需的幅频校正效果。

[0064] S4、将步骤S3获得的幅频校正滤波器添加到任意波形发生器中;

[0065] 在任意波形发生器的FPGA与DAC之间添加幅频校正滤波器,利用幅频校正滤波器对任意波形发生器输出幅频响应进行校正,如图5所示,其中,图5中的(a)是未包含幅频校正滤波器的任意波形发生器的结构框图,图5中的(b)是添加了幅频校正滤波器的任意波形发生器的结构框图。

[0066] 本实施例中,设置任意波形发生器输出由100MHz,200MHz,300MHz,400MHz,500MHz 正弦信号组成的多音信号,输出幅度为0.75V(1.48dBm),各个频点的幅度一致。因此每个频点的输出幅度应为0.15V(-12.42dBm)。通过频谱仪测得各频点输出幅度分别为-7.76dBm,-7.92dBm,-10.36dBm,-11.62dBm,-12.54dBm,如图6所示,符合表1测试的幅频响应规律。然后利用本发明设计了100阶的幅频校正滤波器,并再次测量输出信号得到各个频点输出幅度分别为-13.14dBm,-13.16dBm,-12.99dBm,-12.88dBm,-12.56dBm,如图7所示,校正误差在生1dBm,在100阶幅频校正滤波器的误差范围内。因此,证明本专利方法可有效实现宽带任意波形发生器的幅频校正。

图1

图2

图6

图7