(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第4660316号 (P4660316)

(45) 発行日 平成23年3月30日(2011.3.30)

(24) 登録日 平成23年1月7日(2011.1.7)

|       |           | FΙ   |                                      |                                      |

|-------|-----------|------|--------------------------------------|--------------------------------------|

| 16/02 | (2006.01) | G11C | 17/00                                | 613                                  |

| 16/06 | (2006.01) | G11C | 17/00                                | 634A                                 |

|       |           | G11C | 17/00                                | 601E                                 |

|       |           | G11C | 17/00                                | 633A                                 |

|       |           | G11C | 17/00                                | 634G                                 |

|       |           | • •  | 16/06 (2006.01) G11C<br>G11C<br>G11C | <b>16/02</b> (2006.01) G 1 1 C 17/00 |

請求項の数 12 (全 30 頁)

(21) 出願番号 特願2005-231494 (P2005-231494) (22) 出願日 平成17年8月10日 (2005.8.10) (65) 公開番号 特開2006-99940 (P2006-99940A) 平成18年4月13日 (2006.4.13) 審査請求日 平成20年2月5日 (2008.2.5) (31) 優先権主張番号 特願2004-257278 (P2004-257278)

(32) 優先日 平成16年9月3日 (2004-23727)

(33) 優先権主張国 日本国(JP)

||(73)特許権者 000005821

パナソニック株式会社

大阪府門真市大字門真1006番地

||(74)代理人 110000202

新樹グローバル・アイピー特許業務法人

||(74)代理人 100094145

弁理士 小野 由己男

|(74)代理人 100106367

弁理士 稲積 朋子

(74)代理人 100121120

弁理士 渡辺 尚

(74)代理人 100130340

弁理士 木村 健二

最終頁に続く

## (54) 【発明の名称】不揮発性メモリ装置

## (57)【特許請求の範囲】

## 【請求項1】

データの読み出し単位であり、複数の不揮発性メモリセルから構成されるページを複数 個含む不揮発性メモリアレイを有する不揮発性メモリ装置であって、

前記ページそれぞれは、データを記憶する第1領域と、前記第1領域のデータに付随する制御情報を記憶する第2領域とを有し、

前記ページからデータを読み出す読出手段と、

前記読出手段によりページから読み出されたデータを一時記憶するデータバッファと<u>、</u>前記不揮発性メモリアレイの行方向に配置され、前記ページ毎に前記第1領域の不揮発性メモリセルに共通に接続される複数の第1ワード線と、

前記行方向に配置され、前記ページ毎に前記第2領域の不揮発性メモリセルに共通に接続される複数の第2ワード線と、

前記制御情報の読み出し時以外(以下、通常時という)は、前記ページ毎に前記第1及び第2ワード線を活性化し、前記制御情報の読み出し時は、複数ページに亘って前記複数の第2ワード線のみを活性化するワード線選択手段と、

前記不揮発性メモリアレイの列方向に配置され、複数ページの前記第1及び第2領域の 不揮発性メモリセルに共通に接続され、前記読出手段と前記不揮発性メモリセルとの間を 接続する複数のビット線と、

## を含み、

前記制御情報の読み出し時において、前記読出手段は、前記ビット線を介して前記第2

領域を複数ページに亘って一度に読み出すことを特徴とする<u>、</u> 不揮発性メモリ装置。

### 【請求項2】

前記読出手段により複数ページに亘って一度に読み出された<u>前記</u>第2領域の制御情報に基づいて、前記不揮発性メモリ装置を制御するシステムから入力される論理アドレスと<u>前</u>記不揮発性メモリアレイの物理アドレスとの対応付けを行うアドレス変換テーブルを作成するメモリ制御部をさらに含むことを特徴とする請求項1に記載の不揮発性メモリ装置。

## 【請求項3】

前記メモリ制御部は、前記不揮発性メモリ装置へのアクセスのために入力される論理アドレスを、前記アドレス変換テーブルに基づき物理アドレスに変換することを特徴とする請求項2に記載の不揮発性メモリ装置。

#### 【請求項4】

前記複数のビット線は、前記列方向に配置され前記第1及び第2領域の前記不揮発性メ モリセルに共通に接続される第1ビット線と、前記列方向に配置され前記第2領域の前記 不揮発性メモリセルに接続される第2ビット線と、を含み、

前記読出手段は、

前記通常時は、複数の<u>前記</u>第1ビット線を選択し、<u>前記複数の第1ビット線を介して前</u> 記ページ毎に前記第1領域及び第2領域の不揮発性メモリセルからデータを読み出し、

前記制御情報の読み出し時は、複数の<u>前記</u>第2ビット線を選択し、<u>前記複数の第2ビット線を介して</u>複数ページに亘る<u>前記</u>第2領域の不揮発性メモリセルから<u>制</u>御情報を読み出すビット線選択手段を含む、

ことを特徴とする、請求項1に記載の不揮発性メモリ装置。

### 【請求項5】

前記ワード線選択手段は、前記制御情報の読み出しを行うコマンドから生成されるワード線選択用の制御信号及び前記第1ワード線からの信号の入力を受け、前記第2ワード線の活性/非活性を決定する信号を出力するワード線切替手段を有することを特徴とする請求項1に記載の不揮発性メモリ装置。

#### 【請求項6】

前記ワード線選択手段は、前記制御情報の読み出しを行うコマンドから生成されるワード線選択用の制御信号及び前記第2ワード線からの信号の入力を受け、前記第1ワード線の活性/非活性を決定する信号を出力するワード線切替手段を有することを特徴とする請求項1に記載の不揮発性メモリ装置。

## 【請求項7】

前記第1及び第2ビット線と前記第2領域の不揮発性メモリセルとの間に設けられるビット線切替手段をさらに有し、

前記ビット線切替手段は、前記制御情報の読み出しを行うコマンドが入力される場合は、前記第2領域の不揮発性メモリセルと対応する<u>前記</u>第2ビット線とを接続し、前記コマンドが入力されない場合は、<u>前記第1及び</u>前記第2領域の不揮発性メモリセルと対応する前記第1ビット線とを接続することを特徴とする請求項4に記載の不揮発性メモリ装置。

### 【請求項8】

前記ビット線切替手段は、互いに異なる極性の第1スイッチング素子及び第2スイッチング素子を含むことを特徴とする請求項7に記載の不揮発性メモリ装置。

## 【請求項9】

前記不揮発性メモリアレイは、データの消去単位であり複数ページを含むブロックを複数含んで構成され、

前記ワード線選択手段は、前記制御情報の読み出し時において、1ブロック内における第2領域の不揮発性メモリセルに接続される前記複数の第2ワード線を活性化し、

前記ビット線選択手段は、前記ブロック内の第 2 領域から<u>前記</u>複数の第 2 ビット線を介して前記制御情報を読み出すことを特徴とする請求項 4 に記載の不揮発性メモリ装置。

## 【請求項10】

40

30

10

20

前記不揮発性メモリアレイは、データの消去単位であり複数ページを含むブロックを複数含んで構成され、

前記ワード線選択手段は、前記制御情報の読み出し時において、<u>前記</u>第2領域の不揮発性メモリセルに接続される前記第2ワード線のいずれかをプロック毎に活性化し、

前記ビット線選択手段は、前記各ブロックのいずれか 1 つの第 2 領域それぞれから対応する各前記第 2 ビット線を介して前記制御情報を読み出すことを特徴とする請求項 4 に記載の不揮発性メモリ装置。

## 【請求項11】

前記第2領域を複数ページに亘って一度に読み出すためのコマンドを備えることを特徴とする請求項1に記載の不揮発性メモリ装置。

【請求項12】

前記不揮発性メモリアレイは、データの消去単位であり複数ページを含むブロックを複数含んで構成され、

前記コマンドは、ブロック内の第 2 領域を複数ページに亘って一度に読み出す命令、あるいは異なるブロック内の第 2 領域を複数ページに亘って一度に読み出す命令であることを特徴とする請求項 1 1 に記載の不揮発性メモリ装置。

#### 【発明の詳細な説明】

#### 【技術分野】

[00001]

本発明は、初期化に要する時間を短縮可能な不揮発性メモリ装置に関する。

## 【背景技術】

[0002]

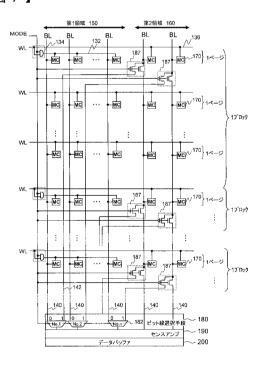

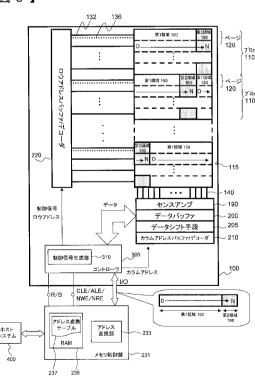

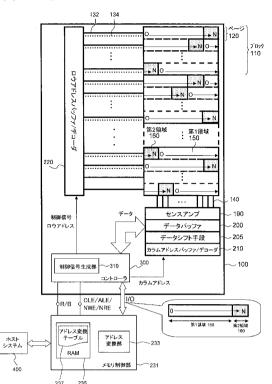

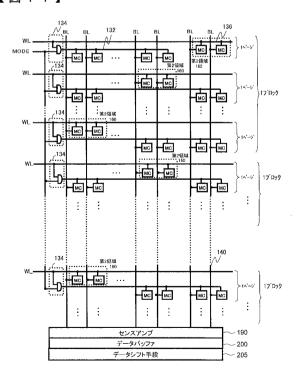

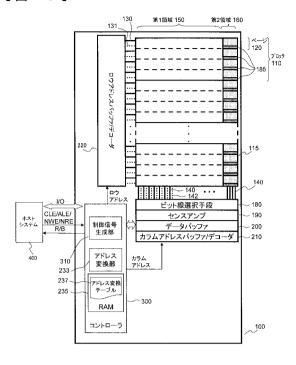

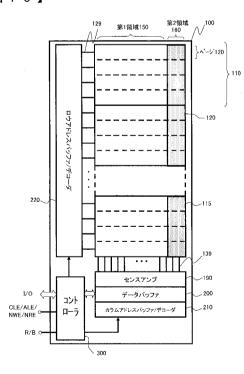

例えば、特許文献 1 に記載のフラッシュメモリ、特にNAND型のフラッシュメモリでは、ページ単位(5 1 2 バイト~2 0 4 8 バイト)での書き込み・読み出しが行えるように構成されている。図 1 6 及び図 1 7 は、前記特許文献 1 に記載されたNAND型フラッシュメモリ装置 1 0 0 は、不揮発性メモリアレイ 1 1 5、センスアンプ 1 9 0、データバッファ 2 0 0、カラムアドレスバッファ / デコーダ 2 1 0、ロウアドレスバッファ / デコーダ 2 2 0、コントローラ 3 0 0 を含む。

[0003]

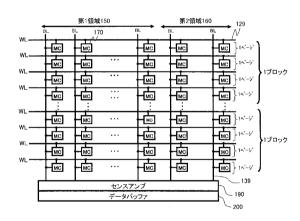

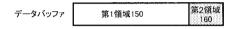

不揮発性メモリアレイ115内の複数の不揮発性メモリセル170は、図17に示すように互いに交差するワード線129及びビット線139の交点に配置されている。また、不揮発性メモリアレイ115は、データの消去単位であるブロック110を複数個含み、ブロック110はデータの読み出しまたは書き込みの単位であるページ120を複数個含む。さらに、各ページ120は、第1領域150及び第2領域160を含む。第1領域150には、フラッシュメモリ装置100外部に読み出されるデータや外部から書き込まれたデータが記憶されている。一方、第2領域160には、第1領域150のデータに付随する情報が記憶されている。

[0004]

コントローラ300は、フラッシュメモリ装置100外部からの各種コマンドや不揮発性メモリアレイ115へのアクセスのためのアドレスを受け付ける。ロウアドレスバッファ/デコーダ220は、入力されるロウアドレスに基づいて該当するワード線129を選択し、カラムアドレスバッファ/デコーダ210は、入力されるカラムアドレスに基づいて該当するビット線139を選択する。ここで、不揮発性メモリアレイ115のデータの読み出しや書き込みはページ単位で行われる。書き込みの場合は、データバッファ200は、フラッシュメモリ装置100外部から入力されるデータをページ単位で一旦格納し、ページ単位で不揮発性メモリセルに書き込ませる。一方、読み出しの場合は、データバッファ200は、センスアンプ190を介してページ単位で読み出されたデータを一旦格納し、フラッシュメモリ装置100外部へ出力する。

10

20

30

40

#### [00005]

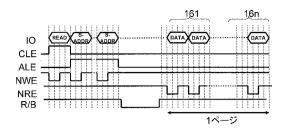

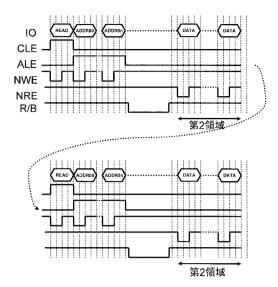

図18は、フラッシュメモリ装置100からデータを読み出す場合のタイミングチャートである。データを読み出すためのREADコマンドは、外部信号CLEとともにコントローラ300に入力される。続いて、外部信号ALEとともに、読み出すデータのアドレスADDR00~ADDR0nがコントローラ300に入力されると、該当するページ120の不揮発性メモリセルからデータがセンスアンプ190を介してデータバッファ200に格納される。ここで、R/B信号がローからハイに変化した後、外部コマンドNREが変化すると、データバッファ200に格納されたデータが読み出される。

【特許文献1】特許3392839号公報

【発明の開示】

【発明が解決しようとする課題】

[0006]

不揮発性メモリアレイ115に書き込みを行う場合、不良ブロックや既にデータの書込みがされているブロックを避け、消去済みブロックにデータの書き込みを行う必要がある。そこで、ブロックに書き込まれたデータとそのデータの論理アドレスとの対応をとるための情報や不良ブロックの情報は、第2領域160に書き込まれる。また、第2領域160から読み出された情報は、RAM(Random Access Memory)等の揮発性メモリセルに記憶されるため、電源がOFFされると情報が揮発する。そのため、電源投入時の初期化毎に第2領域160から情報を読み出す必要がある。従って、フラッシュメモリ装置100では、電源投入時に第2領域160の情報を読み出して、前述のデータとアドレスとの対応や不良ブロックの位置を知る初期化処理を行う必要がある。

[0007]

初期化処理時に、フラッシュメモリ装置100では、まず不揮発性メモリアレイ115にアクセスし、第2領域160の情報をページ単位で読み出す。図19は、ページ単位でデータバッファ200に読み出されたデータのデータ構造である。図19に示すように、データバッファ200に読み出されたデータは、第1領域150及び第2領域160のデータから構成される。フラッシュメモリ装置100外部のメモリ制御部は、この読み出されたデータのうち第2領域の情報に基づいて、例えばデータとアドレスとの対応付けを行うアドレス変換テーブルを生成し、記憶する。

[00008]

ここで、例えば、初期化処理で全てのブロック110における先頭ページ120の第2領域160を読み出すとする。また、フラッシュメモリ装置100の不揮発性メモリの容量が64Mビット、ページが512バイトの第1領域と16バイトの第2領域とからなり、1プロックが32ページ、1ページの読み出し時間が25μsであるとする(ブロックサイズが16Kバイト、ブロック数512個)。このとき、第2領域160の情報を読み出すには、約13msを要する。さらに容量が大きな8Gビットの不揮発性メモリ容量の場合、ページが2048バイトの第1領域と64バイトの第2領域とからなり、1ブロックが64ページ、1ページの読み出し時間が25μsであると(ブロックサイズが128Kバイト、ブロック数8192個)、第2領域160の情報を読み出すには約230msを要する。

[0009]

このように、フラッシュメモリ装置100の不揮発性メモリ容量が大容量化するに伴い、初期化処理に要する時間が増大し、不揮発性メモリアレイ115のデータを正しく読み書き可能になるまでの時間が増大する。

[0010]

そこで、本発明は、初期化処理に要する時間を短縮できる不揮発性メモリ装置を提供することを目的とする。

【課題を解決するための手段】

[0011]

本願第1発明は、上記の課題を解決するために、データの読み出し単位であり、複数の

10

20

30

40

不揮発性メモリセルから構成されるページを複数個含む不揮発性メモリアレイを有する不揮発性メモリ装置であって、前記ページそれぞれは、データを記憶する第 1 領域と、前記第 1 領域のデータに付随する制御情報を記憶する第 2 領域とを有し、

前記ページからデータを読み出す読出手段と、前記読出手段によりページから読み出されたデータを一時記憶するデータバッファとを含み、前記制御情報の読み出し時において、前記読出手段は、前記第2領域を複数ページに亘って一度に読み出すことを特徴とする不揮発性メモリ装置を提供する。

## [0012]

第2領域の制御情報が、一度に複数ページに渡って読み出され、データバッファに記憶される。よって、制御情報の読み出し時間を短縮することができる。そのため、初期化に要する時間が短縮され、不揮発性メモリ装置にアクセス可能となるまでの時間を短縮することができる。ここで、制御情報は、第1領域のデータに付随する論理アドレスやエラー情報を含む。例えば制御情報としては、第1領域で発生した不良の不揮発性メモリセルを冗長セルに置換するための置換情報、どのブロックに不良が発生したかを示す不良ブロック情報及び第1領域のデータに対する誤り訂正符号などが挙げられる。そして、制御情報は初期化時に第2領域から読み出され、読み出された制御情報に基づいてアドレス変換のためのアドレス変換テーブルが作成される。

#### [0013]

本願第2発明は、第1発明において、前記読出手段と前記第1及び第2領域の不揮発性メモリセルとの間を接続するビット線をさらに含み、複数ページに亘る第2領域の読み出し単位内の不揮発性メモリセルは、互いに異なるビット線に接続されていることを特徴とする不揮発性メモリ装置を提供する。

#### [0014]

第 2 領域の不揮発性メモリセル内の制御情報の読みだしは、互いに異なるビット線を介して行われる。よって、制御情報の衝突を防ぎつつ一度に複数ページに渡って制御情報を読み出すことができる。

#### [0015]

本願第3発明は、第1発明において、前記読出手段により複数ページに亘って一度に読み出された第2領域の制御情報に基づいて、前記不揮発性メモリ装置を制御するシステムから入力される論理アドレスと不揮発性メモリアレイの物理アドレスとの対応付けを行うアドレス変換テーブルを作成するメモリ制御部をさらに含むことを特徴とする不揮発性メモリ装置を提供する。

#### [0016]

制御情報が一度に複数ページに亘って読み出されると、アドレス変換テーブルの作成するためのデータが一度に読み出される。そのため、短時間でアドレス変換テーブルを作成でき、初期化に要する時間、つまり、不揮発性メモリ装置にアクセス可能となるまでの時間を短縮することができる。

### [0017]

本願第4発明は、第3発明において、前記メモリ制御部は、前記不揮発性メモリ装置へのアクセスのために入力される論理アドレスを、前記アドレス変換テーブルに基づき物理アドレスに変換することを特徴とする不揮発性メモリ装置を提供する。

#### [0018]

本願第5発明は、第1発明において、複数ページに亘る第2領域の読み出し単位内の不揮発性メモリセルそれぞれに接続される複数の第2ビット線をさらに含み、前記読出手段は、前記制御情報の読み出し時は、複数ページに亘る第2領域の不揮発性メモリセルから対応する複数の第2ビット線を介して制御情報を読み出すことを特徴とする不揮発性メモリ装置を提供する。

#### [0019]

第 2 領域の不揮発性メモリセル内の制御情報の読みだしは、各不揮発性メモリセルのそれぞれの第 2 ビット線を介して制御情報が読みだされる。よって、衝突を防止しつつ複数

10

20

30

40

ページに亘って一度に制御情報を読み出すことができる。

## [0020]

本願第6発明は、第5発明において、前記第1及び第2領域の不揮発性メモリセルは行列状に配置されており、行方向に配置されており、前記ページ毎に前記第1領域の不揮発性メモリセルに共通に接続される複数の第1ワード線と、行方向に配置されており、前記第1及び第2領域の列方向に配置された不揮発性メモリセルに共通に接続される複数の第2ワード線数の第1ビット線と、前記制御情報の読み出し時は、複数ページに直に接続される複数の第2ワード線を活性化し、前記制御情報の読み出し時は、複数ページに直に接続でするワード線を活性化するワード線選択手段とをさらに含む。ここで前記読出ので複数の第2ワード線を活性化するワード線選択手段とをさらに含む。ここで前記読出ので複数の第2ワード線を選択し、1ページの第1領域及び第2領域の不揮発性メモリセルから前記複数の第1ビット線を介してデータを読み出し、前記制御情報の読み出し時は、複数の第2ビット線を選択し、複数ページに亘る第2領域の不揮発性メモリセルから前記複数の第2ビット線を透択し、複数ページに亘る第2領域の不揮発性メモリセルから前記複数の第2ビット線を過去で表数ページに重る第2領域の不揮発性メモリセルから前記複数の第2ビット線を過去で表数ページに重る第2領域の不揮発性メモリセルから前記複数の第2ビット線を過去で表数ページに重る第2領域の不揮発性メモリセルから前記複数の第2ビット線を過去で表数ページに重る第2領域の不揮発性メモリセルから前記複数の第2ビット線を過去で表数ページに重る第2領域の不揮発性メモリを記述を表数ページに重る第2領域の不揮発性メモリ装置を提供する。

#### [0021]

第1及び第2領域の不揮発性メモリセルそれぞれは第1ビット線と接続されており、第2領域の不揮発性メモリセルは、さらに第2ビット線と接続されている。なお、第2領域の不揮発性メモリセルは、共通の第1ビット線に接続されている。つまり、第2領域の不揮発性メモリセルは、不揮発性メモリアレイ上において、カラムアドレスを共通とするように縦方向に一列または複数列に配置されている。ここで、通常時は、第1ビット線を介して該当ページの第1及び第2領域から1ページ分のデータが読み出される。一方、制御情報の読み出し時は、複数ページに亘って第2領域の第2ワード線が活性となり、第2ビット線を介して複数ページに亘る第2領域へのアクセスが行われる。よって、第2領域に記憶されている制御情報を効率よく読み出すことができる。

### [0022]

本願第7発明は、第1発明において、前記第1及び第2領域の不揮発性メモリセルは行列状に配置されており、前記第1及び第2領域の列方向に配置された不揮発性メモリセルに共通に接続される複数の第1ビット線をさらに含み、複数ページに亘る第2領域の読み出し単位内の不揮発性メモリセルは、それぞれ異なる第1ビット線に接続されることを特徴とする不揮発性メモリ装置を提供する。

## [0023]

第2領域の不揮発性メモリセル内の制御情報の読みだしは、各不揮発性メモリセルのそれぞれの第1ビット線を介して制御情報が読みだされる。ここで、第2領域の不揮発性メモリセルは、その列方向がそれぞれ異なるように配置されているため、衝突を防止しつつ複数ページに亘って一度に制御情報を読み出すことができる。

## [0024]

本願第8発明は、第7発明において、行方向に配置されており、前記ページ毎に前記第1領域の不揮発性メモリセルに共通に接続される複数の第1ワード線と、行方向に配置されており、前記ページ毎に前記第2領域の不揮発性メモリセルに共通に接続される複数の第2ワード線と、前記制御情報の読み出し時以外(以下、通常時という)は、ページ毎に第1及び第2ワード線を活性化し、前記制御情報の読み出し時は、複数ページに亘って複数の第2ワード線を活性化するワード線選択手段とをさらに含む。ここで、前記読出手段は、前記通常時は、複数の第1ビット線を選択し、1ページの第1領域及び第2領域の不揮発性メモリセルから対応する前記複数の第1ビット線を介してデータを読み出し、前記制御情報の読み出し時は、複数の第1ビット線を選択し、複数ページに亘る第2領域の不揮発性メモリセルから前記複数の第1ビット線を選択し、複数ページに亘る第2領域の不揮発性メモリセルから前記複数の第1ビット線を過じて制御情報を読み出すビット線選択手段を含むことを特徴とする、不揮発性メモリ装置を提供する。

#### [0025]

第1及び第2領域の不揮発性メモリセルそれぞれは、第1ビット線に接続されている。

10

20

30

40

また、第2領域の不揮発性メモリセルは、それぞれ異なる第1ビット線に接続される。つまり、第2領域の不揮発性メモリセルは、不揮発性メモリアレイ上において、カラムアドレスが異なるように配置されている。ここで、制御情報の読み出し時は、複数ページに亘って第2領域の第2ワード線が活性となり、それぞれ異なる第1ビット線を介して複数ページに亘る第2領域のみへのアクセスが行われる。よって、第2領域に記憶されている制御情報を効率よく読み出すことができる。

#### [0026]

本願第9発明は、第5または第7発明において、前記ワード線選択手段は、前記制御情報の読み出しを行うコマンドから生成されるワード線選択用の制御信号及び前記第1ワード線からの信号の入力を受け、前記第2ワード線の活性/非活性を決定する信号を出力するワード線切替手段を有することを特徴とする不揮発性メモリ装置を提供する。

#### [0027]

例えばワード線選択手段をOR回路で形成すると、制御情報の読み出し時において複数ページの第2領域を一度に読み出すためのコマンドに基づいて"H"が入力されると、第1ワード線の入力の如何によらず複数ページの第2ワード線が活性化され"H"となる。一方、通常のコマンドが入力され、OR回路の入力が"L"である場合は、第1ワード線の入力に応じて第2ワード線の活性/非活性が決定される。よって、制御情報の読み出し時は、複数ページの第2ワード線が活性となり、複数ページに亘る第2領域の不揮発性メモリセルから第2ビット線を介して制御情報が効率的に読み出される。

#### [0028]

また、第1ワード線は、入力アドレスをデコードすることにより選択される。ワード線切替手段には、その第1ワード線の信号が入力されるため、アドレスにより指定されたページのデータを読み出すことができる。

#### [0029]

本願第10発明は、第5または第7発明において、前記ワード線選択手段は、前記制御情報の読み出しを行うコマンドから生成されるワード線選択用の制御信号及び前記第2ワード線からの信号の入力を受け、前記第1ワード線の活性/非活性を決定する信号を出力するワード線切替手段を有することを特徴とする不揮発性メモリ装置を提供する。本願第9発明と同様の作用効果を有する。

## [0030]

本願第11発明は、第6発明において、前記第1及び第2ビット線と前記第2領域の不揮発性メモリセルとの間に設けられるビット線切替手段をさらに有し、前記ビット線切替手段は、前記制御情報の読み出しを行うコマンドが入力される場合は、前記第2領域の不揮発性メモリセルと対応する前記第2ビット線とを接続し、前記コマンドが入力されない場合は、前記第2領域の不揮発性メモリセルと対応する第1ビット線とを接続することを特徴とする不揮発性メモリ装置を提供する。

## [0031]

ビット線切替手段は、コマンドが入力される場合は、第1ビット線からのデータの読み出しを無効として第2ビット線からのデータの読み出しを有効にする。このとき、コマンドの入力により、ワード線選択手段は複数ページに亘って第2ワード線を活性化する。よって、ビット線選択手段は、第2領域の不揮発性メモリセルから第2ビット線を介して複数ページに亘って制御情報を読み出す。一方、通常時はビット線切替手段は、複数ページの不揮発性メモリセルにおいて共通に接続される第1ビット線を有効とし、ワード線選択手段はアクセス先のページの第1及び第2ワード線のみを活性化する。よって、アクセス先のページの不揮発性メモリセルから第1ビット線を介してデータが読み出される。このように、制御情報読み出し時は、ビット線切替手段により第2ビット線に切り替えて制御情報読み出すことで、データの衝突を防ぎつつ複数ページに亘って一度に効率よく制御情報を読み出すことができる。

#### [0032]

本願第12発明は、第11発明において、前記ビット線切替手段は、互いに異なる極性

20

10

30

40

の第 1 スイッチング素子及び第 2 スイッチング素子を含むことを特徴とする不揮発性メモリ装置を提供する。

#### [0033]

本願第13発明は、第6発明において、前記不揮発性メモリアレイは、データの消去単位であり複数ページを含むブロックを複数含んで構成され、前記ワード線選択手段は、前記制御情報の読み出し時において、1ブロック内における第2領域の不揮発性メモリセルに接続される複数の第2ワード線を活性化し、前記ビット線選択手段は、前記ブロック内の第2領域から複数の第2ビット線を介して前記制御情報を読み出すことを特徴とする不揮発性メモリ装置を提供する。ブロック内の第2領域の制御情報を複数ページに亘って読み出すことができる。

[0034]

本願第14発明は、第6発明において、前記不揮発性メモリアレイは、データの消去単位であり複数ページを含むブロックを複数含んで構成され、前記ワード線選択手段は、前記制御情報の読み出し時において、第2領域の不揮発性メモリセルに接続される第2ワード線のいずれかを各ブロック毎に活性化し、前記ビット線選択手段は、前記各ブロック毎のいずれか1つの第2領域それぞれから対応する各第2ビット線を介して前記制御情報を読み出すことを特徴とする不揮発性メモリ装置を提供する。複数ブロックの第2領域の制御情報を複数ページに亘って読み出すことができる。

[0035]

本願第15発明は、第1発明において、前記第2領域を複数ページに亘って一度に読み出すためのコマンドを備えることを特徴とする不揮発性メモリ装置を提供する。

[0036]

メモリ装置外部のメモリ制御部は、不揮発性メモリ装置の複数ページに亘る第 2 領域の制御情報を読み出すためのコマンドを発行することで、複数ページに亘る第 2 領域を一度に読み出すことができる。

[0037]

本願第16発明は、第15発明において、前記不揮発性メモリアレイは、データの消去単位であり複数ページを含むブロックを複数含んで構成され、前記コマンドは、ブロック内の第2領域を複数ページに亘って一度に読み出す命令、あるいは異なるブロック内の第2領域を複数ページに亘って一度に読み出す命令であることを特徴とする不揮発性メモリ装置を提供する。

[0038]

コマンドがブロック内の第 2 領域を複数ページに亘って一度に読み出す命令である場合は、同一ブロック内の第 2 領域を一度に読み出すことができる。また、コマンドが異なるブロック内の第 2 領域を複数ページに亘って一度に読み出す命令である場合は、異なるブロックの第 2 領域を複数ページに亘って一度に読み出すことができる。

【発明の効果】

[0039]

本発明の不揮発性メモリ装置を用いれば、初期化に要する時間を短縮し、不揮発性メモリ装置にアクセス可能となるまでの時間を短縮することができる。

【発明を実施するための最良の形態】

[0040]

<発明の概要>

不揮発性メモリ装置は、不揮発性メモリアレイ、読出手段及びデータバッファを含む。 不揮発性メモリアレイは、データの消去単位であるブロックを複数個含む。このブロックには、データの読み出し及び書き込みの単位であるページが複数個含まれる。また、ページは、不揮発性メモリ装置外部に読み出すデータや外部から書き込まれるデータが記憶される第1領域と、第1領域のデータに付随する制御情報を記憶する第2領域とから構成されている。ここで、電源投入時などの初期化処理時において、読出手段は、複数ページに亘る第2領域に同時にアクセスし、第2領域の制御情報を読み出す。読み出された制御情 10

20

30

40

報は、データバッファに一旦格納される。その後、不揮発性メモリ装置外部のメモリ制御 部がその制御情報に基づいてアドレス変換テーブルを作成する。

#### [0041]

このように、第 2 領域の制御情報が、一度に複数ページに渡って読み出されるため、制御情報の読み出しを高速に行うことができる。そのため、アドレス変換テーブルの作成など初期化処理を高速に行うことができ、不揮発性メモリ装置にアクセス可能となるまでの時間を短縮することができる。

### [0042]

<第1実施形態例>

## 「構成]

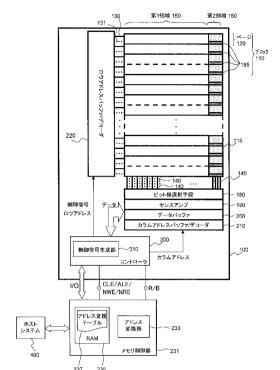

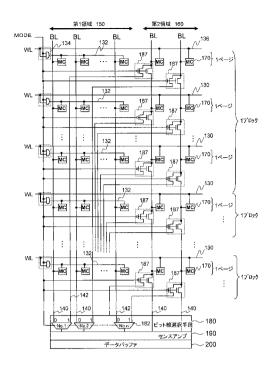

図1は、第1実施形態例に係る不揮発性メモリ装置の構成図、図2は、図1の不揮発性メモリ装置に搭載される不揮発性メモリアレイ及びビット線選択手段の構成図である。

### [0043]

不揮発性メモリ装置 1 0 0 は、不揮発性メモリアレイ 1 1 5 、ビット線選択手段 1 8 0 、センスアンプ 1 9 0 、データバッファ 2 0 0 、カラムアドレスバッファ / デコーダ 2 1 0 、ロウアドレスバッファ / デコーダ 2 2 0 、制御信号生成部 3 1 0 を有するコントローラ 3 0 0 を含む。また、不揮発性メモリ装置 1 0 0 は、アドレス変換部 2 3 3 、R A M 2 3 5 及びアドレス変換テーブル 2 3 7 を含むメモリ制御部 2 3 1 と接続されている。各部の構成を以下に説明する。

## [0044]

(1) 不揮発性メモリ装置

(1-1) 不揮発性メモリアレイ

不揮発性メモリアレイ 1 1 5 は、データの消去単位であるブロック 1 1 0 を複数個含む。ブロック 1 1 0 は、データの読み出しまたは書き込みの単位であるページ 1 2 0 を複数個含む。各ページ 1 2 0 は、第 1 領域 1 5 0 及び第 2 領域 1 6 0 から構成されている。

### [0045]

不揮発性メモリアレイ115の不揮発性メモリセル170は、図2に示すように複数のワード線と複数のビット線の交点に位置するようにマトリックス状に配置されている。ワード線は、複数ページの第1領域150から1ページの第1領域150を選択するための第1ワード線130及び複数ページの第2領域160から1ページの第2領域160を選択するための第2ワード線131を含む。ビット線は、第1ビット線140及び第2ビット線142を含む。第1ビット線140は、通常時に第1領域150及び第2領域160からビット線選択手段180を介してセンスアンプ190にデータを読み出す、またはビット線選択手段180を介してセンスアンプ190にデータを読み出す、またはビット線選択手段180を介して第1領域150及び第2領域160の不揮発性メモリセルにデータを書き込む場合に使用される。また、第2ビット線142は、初期化処理時、つまり制御情報の読み出し時に第2領域160の不揮発性メモリセル170から制御情報を読み出すために使用される。なお、通常時とは、制御情報読み出し時を除く動作モードをいうものとする。

## [0046]

第1領域150の不揮発性メモリセル170は、第1ワード線130及び第1ビット線 140に接続されている。ここで、同一ページ内の第1領域150において、不揮発性メモリセル170は、第1ワード線130を共有するとともに、それぞれ異なる第1ビット線140に接続されている。なお、第1領域の第1ビット線140それぞれは、カラムアドレスが共通である、複数ページに亘る不揮発性メモリセルにより共有されている。

## [0047]

一方、第2領域160の不揮発性メモリセル170は、第2ワード線131、第1ビット線140及び第2ビット線142に接続されている。ここで、同一ページ内の第2領域160において、不揮発性メモリセル170は、第2ワード線131を共有するとともに、それぞれ異なる第1ビット線140及び第2ビット線142に接続されている。なお、第2領域160の第1ビット線140それぞれは、カラムアドレスが共通である、複数ペ

10

20

30

40

ージに亘る第2領域の不揮発性メモリセル170により共有されている。つまり、第2領域160は、縦方向に同じ位置に配置されている。一方、第2領域160の第2ビット線142は、第2領域160の不揮発性メモリセルそれぞれに接続されている。また、第1ビット線140及び第2ビット線142は、それぞれビット線選択手段180と接続される。

## [0048]

#### (1-2)制御情報

第1領域150では、不揮発性メモリ装置100外部に読み出されるデータや外部から書き込まれたデータが記憶される。一方、第2領域160では、第1領域のデータに付随する論理アドレスやエラー情報等を含む制御情報が記憶される。例えば制御情報としては、第1領域で発生した不良の不揮発性メモリセルを冗長セルに置換するための置換情報、どのブロックに不良が発生したかを示す不良ブロック情報、第1領域のデータに対する誤り訂正符号、及び読み出し・書き込み・消去時における電圧値などの各種制御データなどが挙げられる。そして、第2領域のデータを読み出すためのコマンドが入力されると、第2領域160から制御情報が読み出される。後述のメモリ制御部231は、この制御情報に基づいてアドレス変換のためのアドレス変換テーブルを作成する。

#### [0049]

具体的に例示すると、不揮発性メモリアレイ115に書き込みを行う場合、不良ブロックや既にデータの書込みがされているブロックを避け、消去済みブロックにデータの書き込みを行う必要がある。このような場合に、書き込まれたデータとデータの論理アドレスとの対応をとるために、後述のメモリ制御部231は、制御情報に基づいてアドレス変換テーブルを作成する。そして、データの読み出し及び書き込み時には、アドレス変換テーブルに基づいてアドレス変換を行う。

#### [0050]

また、この制御情報は、出荷前に行ったテストや、不揮発性メモリ装置100の使用時に発生した不良セルのアドレスや置換情報に基づいて不揮発性メモリ装置100外部のメモリ制御部231により、第1領域150にデータを書き込む際に第2領域160に書き込まれる。

## [0051]

## (1-3)コントローラ及び制御信号生成部

コントローラ300は、制御信号生成部310を有しており、不揮発性メモリ装置100外部のメモリ制御部231からデータ、アドレス、各種コマンド、及び外部信号などを受信する。各種コマンドとしては、例えば、読み出しを行うためのREADコマンド、書き込みを行うためのWRITEコマンド、制御情報の読み出しを行うコマンドS-CMDなどが挙げられる。また、外部信号としては、外部信号CLE、ALE、NWE、NRE等が挙げられる。ここで、外部信号CLEはI/O端子に入力される情報がコマンドであることを示し、外部信号ALEはI/O端子に入力される情報がアドレスであることを示し、外部信号NWEはI/O端子に入力されるデータの書込みストローブであり、外部信号NREはI/O端子から出力されるデータの読出しストローブである。また、コントローラ300は、不揮発性メモリ装置100へのアクセスが可能か否かを示す信号をR/Bピンから出力する。

## [0052]

さらに、コントローラ300は、READコマンド、WRITEコマンドや外部信号を解釈し、通常の読み出し及び書き込み動作を行うための内部信号を生成する。一方、制御信号生成部310は、制御情報の読み出しを行うコマンドS-CMD及び外部信号を解釈し、第2領域160の制御情報の読み出しを制御する制御信号を生成する。また、制御信号生成部310は、READコマンド及び外部信号を解釈することにより、第2領域160の制御情報の読み出しを制御する制御信号を生成することもできるし、制御情報の読み出しを行うコマンドS-CMD、READコマンド及び外部信号を解釈することにより、制御信号を生成することもできる。制御信号は、例えばワード線及びビット線の選択を制

10

20

30

40

10

20

30

40

50

御する信号などであり、後述のMODE信号は、この制御信号に基づいて生成される。

## [0053]

さらに、コントローラ300は、メモリ制御部231においてホストシステム400側から入力される論理アドレスから不揮発性メモリアレイ115の物理アドレスにアドレス変換されたロウアドレス及びカラムアドレスを受信する。後述のメモリ制御部231は、第2領域の制御情報に基づいて生成されたアドレス変換テーブルを有しており、このアドレス変換テーブルに基づいてアドレス変換を行う。

### [0054]

コントローラ300は、生成した内部信号、物理アドレスであるロウアドレス及びカラムアドレスをロウアドレスバッファ / デコーダ220及びカラムアドレスバッファ / デコーダ210に出力する。また、制御信号生成部310は、生成した制御信号をロウアドレスバッファ / デコーダ210に出力する。

#### [0055]

(1-4)ワード線切替手段

ワード線切替手段133は、第2ワード線131を活性にするかを制御する手段であり、ページ毎に対応するようにそれぞれ設けられている。また、ワード線切替手段133は、図2に示すようにMODE信号の入力及び第1ワード線130からの信号の入力を受ける。このワード線切替手段133に入力されるMODE信号は、制御情報の読み出しを行うコマンドS・CMDに基づいて生成され、ワード線切替手段133に入力される信号である。ここで、制御情報の読み出しは、例えば第2領域160を読み出すためのコマンドS・CMD、READコマンド及びアドレスの組み合わせによるコマンド、S・CMD及びアドレスの組み合わせによるコマンドなどが入力されることにより行われる。これらのコマンドは、不揮発性メモリ装置100外部のメモリ制御部231からコントローラ300に入力される。

#### [0056]

以下、第1実施形態例では、第2領域160を読み出すためのS-CMDが不揮発性メモリ装置100外部からコントローラ300内の制御信号生成部310に入力されるものとする。このとき、制御信号生成部310は、S-CMDに基づいて、第2領域160の読み出しを制御する制御信号を生成する。そして、ロウアドレスバッファノデコーダ220は、この制御信号に基づくMODE信号を生成してワード線切替手段133に入力する。そして、ワード線切替手段133は、MODE信号の入力及び第1ワード線130からの信号の入力に応じて、第2ワード線131の活性ノ非活性を決定する信号を出力する。

#### [0057]

例えば、図2に示すようにワード線選択手段133がOR回路で形成されているとする。S-CMDが制御信号生成部310に入力されると、OR回路には"H"のMODE信号が入力されるものとする。"H"のMODE信号が入力されると、第1ワード線130の入力の如何によらずOR回路の出力が"H"となり、第2ワード線131が活性化される。なお、図2においては、MODE信号は、ページそれぞれに設けられる複数のワード線切替手段133に一度に入力される。よって、複数ページに亘る第2領域160の第2ワード線131が一度に活性化される。

## [0058]

一方、通常のコマンドが入力され、OR回路にはMODE信号として"L"が入力される場合は、第1ワード線130の入力に応じて第2ワード線131の活性/非活性が決定される。つまり、第1ワード線130が活性であれば第2ワード線131も活性となり、第1ワード線130が非活性であれば第2ワード線131も非活性となる。なお、ワード線選択手段133は、MODE信号に応じて第1ワード線130及び第2ワード線131の活性/非活性を制御できれば良く、OR回路に限定されない。

## [0059]

(1-5)ビット線切替手段

ビット線切替手段185は、第1ビット線140及び第2ビット線142と第2領域1

10

20

30

40

50

60の不揮発性メモリセル170との間に設けられ、不揮発性メモリセル170に第1ビット線140又は第2ビット線142のいずれかを切り替えて接続する。第2領域160の第1ビット線140それぞれは、カラムアドレスを共通にする第2領域160の複数の不揮発性メモリセル170に共有されている。ここで、複数ページに亘って第2領域160の制御情報を読み出す場合、第2ビット線142に切り替えて制御情報を読み出すことで、データの衝突を防止することができる。

#### [0060]

具体的には、ビット線切替手段185は、図2に示すように例えばPMOSトランジスタ及びNMOSトランジスタから構成される。PMOSトランジスタは、第2領域160の不揮発性メモリセル170と第1ビット線140との間に設けられ、NMOSトランジスタは、第2領域160の不揮発性メモリセル170と第2ビット線142との間に設けられる。そして、PMOSトランジスタ及びNMOSトランジスタのゲートは、MODE信号の入力を受ける。ここで、MODE信号は、前述の通り第2領域160を読み出すためのS・CMDに基づいて制御信号生成部310及びロウアドレスバッファ/デコーダ220により生成される信号である。

#### [0061]

制御情報の読み出し時でありS-CMDが制御信号生成部310に入力され、各トランジスタのゲートに"H"のMODE信号が入力される場合は、NMOSトランジスタがOFFし、第2領域160の不揮発性メモリセル170と第2ビット線142とが接続される。一方、通常のコマンドが入力され、MODE信号として"L"が入力される場合は、NMOSトランジスタがOFFしてPMOSトランジスタがONし、第2領域160の不揮発性メモリセル170と第1ビット線140とが接続される。つまり、ビット線切替手段185は、"H"のMODE信号が入力される場合は、第1ビット線140からのデータの読み出しを無効として第2ビット線142からのデータの読み出しを有効にする。このとき、"H"のMODE信号がワード線切替手段133に入力されることにより、複数ページに亘って第2ワード線131が活性化されている。よって、後述のビット線選択手段180は、第2領域160の不揮発性メモリセル170から第2ビット線142を介して複数ページに亘って制御情報を読み出すことができる

## [0062]

一方、通常時は、MODE信号は"L"であり、ビット線切替手段185は、複数ページの不揮発性メモリセル170において共通に接続される第1ビット線140を有効にする。このとき、後述のロウアドレスバッファ/デコーダ220によりアクセス先のページの第1ワード線130及び第2ワード線131のみが活性化されている。よって、アクセス先のページの不揮発性メモリセル170から第1ビット線140を介して1ページ分のデータが読み出される。

## [0063]

なお、ビット線切替手段185は、第1ビット線140と第2領域を複数ページに亘って読み出すための第2ビット線142とを切替できる構成であれば良く、上記のPMOS及びNMOSトランジスタの構成に限定されない。

## [0064]

#### (1-6)ロウアドレスバッファ/デコーダ

ロウアドレスバッファ / デコーダ 2 2 0 は、コントローラ 3 0 0 を介して入力されるロウアドレスをデコードして、入力アドレスに対応する第 1 ワード線 1 3 0 及び第 2 ワード線 1 3 1 を選択する。また、ロウアドレスバッファ / デコーダ 2 2 0 は、コントローラ 3 0 0 が生成した、通常の読み出しまたは書き込みを制御する内部信号を受信し、読み出しまたは書き込みの制御を行う。さらに、ロウアドレスバッファ / デコーダ 2 2 0 は、制御信号を生成 3 1 0 がコマンド S - C M D に基づいて生成した制御信号を受信し、M O D E 信号を生成する。そして、ロウアドレスバッファ / デコーダ 2 2 0 は、生成した M O D E 信号をワード線切替手段 1 3 3、ビット線切替手段 1 8 5、後述のセレクタ 1 8 2 に入力

する。

### [0065]

ここで、MODE信号は、前述のように、第2領域160の読み出すためのコマンドS-CMDに応じてワード線の選択を制御するワード線選択用制御信号及びビット線の選択を制御するビット線選択用制御信号であるとともに、コマンドに応じて後述のセレクタ182を制御し、センスアンプ190にデータを読み出すビット線を選択する制御信号である。また、上述の通り、通常時と第2領域読み出し時とでMODE信号のレベルを変更することで、第2領域160の読み出し制御が行われる。

#### [0066]

なお、ロウアドレスバッファ / デコーダ 2 2 0 は、前述のワード線切替手段 1 3 3 を含んで構成されていても良い。つまり、図 2 では、ワード線切替手段 1 3 3 は、不揮発性メモリアレイ 1 1 5 内に設けられ、ロウアドレスバッファ / デコーダ 2 2 0 とは別の構成となっているが、ワード線切替手段 1 3 3 が不揮発性メモリアレイ 1 1 5 外のロウアドレスバッファ / デコーダ 2 2 0 と一体に構成されていても良い。この場合には、ワード線切替手段 1 3 3 の分だけ不揮発性メモリアレイ 1 1 5 の面積を小さくできるので好ましい。

#### [0067]

(1-7)カラムアドレスバッファ/デコーダ

カラムアドレスバッファ / デコーダ 2 1 0 は、制御信号生成部 3 1 0 を介して入力されるカラムアドレスをデコードする。つまり、カラムアドレスバッファ / デコーダ 2 1 0 は、センスアンプ 1 9 0 を介して不揮発性メモリセル 1 7 0 からデータバッファ 2 0 0 に読み出された 1 ページ分のデータのカラムアドレスを指定する。

#### [0068]

(1-8)ビット線選択手段

ビット線選択手段180は、第1ビット線140及び第2ビット線142が接続され、カラムアドレスバッファ/デコーダ210によりデコードされたアドレスに基づいて不揮発性メモリセル170からデータをビット線を介して読み出す、あるいは不揮発性メモリセル170にデータをビット線を介して書き込む。

#### [0069]

また、ビット線選択手段180は、複数のセレクタ182を有しており、セレクタ182それぞれには、第1ビット線140及び第2ビット線142が接続される。また、セレクタ182には、MODE信号が入力される。

## [0070]

ビット線選択手段180と第1ビット線140及び第2ビット線142との接続は、例えば次のように行われる。図2中の1番目のセレクタ182(図2中、NO1のセレクタ182)は、1番目の第1ビット線140と接続され、さらに1番目のブロックの1番目のページに位置する第2領域160の不揮発性メモリセル170(図2中、Aの不揮発性メモリセル)に連結する第2ビット線142に接続される。同様に、2番目のセレクタ182(図2中、NO2のセレクタ)は、2番目の第1ビット線140と接続され、さらに1番目のブロックの1番目のページに位置する第2領域160の不揮発性メモリセル170(図2中、Bの不揮発性メモリセル)に連結する第2ビット線142に接続される。また、3番目のセレクタ182(図示せず)は、3番目の第1ビット線140と接続される。また、3番目のブロックの2番目のページに位置する第2領域160の不揮発性メモリセル170に連結する第2ビット線142に接続される。このように、その他のセレクタ182にも同様に、第1ビット線140及び第2ビット線142が対になって接続される

## [0071]

セレクタ182は、MODE信号に応じて、第1ビット線140または第2ビット線142のいずれかを選択する。具体的には、セレクタ182は、制御情報の読み出し時は、S-CMDに基づく"H"のMODE信号の入力を受け、第2ビット線142を選択する。読み出された制御情報は、後述のセンスアンプ190を介してデータバッファ200

10

20

30

40

に出力される。一方、通常時は、セレクタ182は第1ビット線140を選択する。

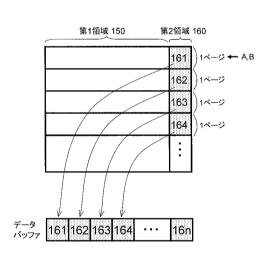

## [0072]

図3は、第2領域160に蓄積されている制御情報が、データバッファ200に格納される様子を示す模式図である。第2領域160において、1番目、2番目、3番目、4番目…のページの第2領域をそれぞれ第2領域161、162、163、164…16nとする。すると、制御情報読み出し時における第2領域へのアクセスにより、第2領域161、162、163、164…16nの制御情報が一度にデータバッファ200に読み出されている。また、図3の1番目の第2領域161には、図2の1番目のページの第2領域に位置する不揮発性メモリA及びBが含まれている。このように、上述の構成により、制御情報読み出し時には、複数ページに亘る第2領域161、162、163、164…16nに記憶されている制御情報が、データバッファ200に一度に読み出される。ここで、データバッファ200のバッファ容量が1ページ分の容量である場合、1ページ分の制御情報が読み出される。

## [0073]

一方、通常のコマンドが入力された場合、セレクタ182は、第1ビット線140を選択する。ここで、データバッファ200に読み出されたデータの構成は、前述の図16に示す構成と同様であり、データバッファ200には第1領域150及び第2領域160を含む1ページ分のデータが読み出される。

#### [0074]

(1-9)センスアンプ

センスアンプ190は、ビット線選択手段180を介して不揮発性メモリセル170からページ単位で読みだされたデータを増幅する。そして、センスアンプ190は、増幅したデータをデータバッファ200に出力する。

## [0075]

(1-10)データバッファ

データバッファ200は、ページ単位で読み出されたデータを、センスアンプを介して 受信し、一旦格納して不揮発性メモリ装置100外部のメモリ制御部231に出力する。

## [0076]

(2) メモリ制御部

メモリ制御部231は、ホストシステム400側と不揮発性メモリ装置100との間に接続されており、不揮発性メモリ装置100に対してコマンドを発行したり、ホストシステム400側と不揮発性メモリ装置100との間のデータ、アドレス及びコマンドなどの送受信を行う。

## [0077]

さらに、メモリ制御部231は、アドレス変換部233、RAM235を含む。そして、メモリ制御部231は、電源投入時などの初期化処理時において、第2領域の制御情報を読み出し、読み出した制御情報に基づいてホストシステム400側からのアクセスに対応するためのアドレス変換テーブルを作成する。具体的には、メモリ制御部231のRAM235は、制御情報読み出し時に第2領域160から読み出された制御情報に基づくアドレス変換情報を格納する。メモリ制御部231は、制御情報に基づいて、ホストシステム400側から入力される論理アドレスと不揮発性メモリアレイ115の物理アドレスとの対応付けを行うアドレス変換テーブルを作成する。アドレス変換テーブルは、RAM235に記憶される。

## [0078]

アドレス変換部 2 3 3 は、 R A M 2 3 5 に格納されているアドレス変換テーブル 2 3 7 に基づいて、メモリ制御部 2 3 1 が受信したロウアドレス及びカラムアドレスの論理アドレスを物理アドレスに変換し、コントローラ 3 0 0 に出力する。

#### [0079]

[制御情報の読み出しフロー]

次に、第1実施形態例に係る不揮発性メモリアレイ115の制御情報の読み出しの流れ

10

20

30

40

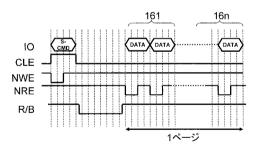

について説明する。図4は、開始コマンドS-CMDの入力により、第1実施形態例に係る不揮発性メモリ装置100から制御情報を読み出す場合のタイミングチャートの一例である。

#### [0800]

制御情報の読み出し時は、メモリ制御部231は、ホストシステム400側からのコマンド入力に基づいて、外部信号CLEとともに、制御情報の読み出しを開始する開始コマンドS-CMDを制御信号生成部310に入力する。ここで、R/B信号がローからハイに変化した後、外部信号NREを変化させると、不揮発性メモリアレイ115の第2領域160から制御情報が読み出される。図2では、1ページの第2領域160は、2つの不揮発性メモリセル170を有しており、図4に示すように1番目の第2領域161からは2つのデータが読み出されている。

#### [0081]

具体的には、メモリ制御部231は、S-CMDを制御信号生成部310に入力する。制御信号生成部310及びロウアドレスバッファ/デコーダ220は、S-CMDに基づいてMODE信号を生成し、ワード線切替手段133、ビット線切替手段185及びビット線選択手段180のセレクタ182に入力する。ここで、S-CMDが入力されると、"H"のMODE信号が生成される。ワード線切替手段133は、ページ毎にそれぞれ設けられており、"H"のMODE信号の入力を受けて第2領域160に対応する、複数ページの第2ワード線131を活性化する。ビット線切替手段185は、"H"のMODE信号が入力されると、第1ビット線140と第2領域160の不揮発性メモリセル170との接続を遮断し、第2ビット線142と第2領域160の不揮発性メモリセル170とを接続する。また、ビット線選択手段180のセレクタ182は、"H"のMODE信号の入力を受けて第2ビット線142からのデータの読み出しを有効にする。そして、制御情報は、第2ビット線142からセンスアンプ190を介して読み出され、データバッファ200に一旦格納され後、不揮発性メモリ装置100外部へ出力される。

### [0082]

よって、複数ページに亘って第2ワード線131が活性化され、複数ページに亘る第2領域160それぞれから対応する第2ビット線142を介して、制御情報がデータバッファ200に一旦格納される。このように、制御情報が一度に複数ページに渡って読み出されるため、制御情報の読み出し時間を短縮することができる。ここで、メモリ制御部231は、読み出された制御情報に基づいてアドレス変換テーブル作成する。よって、制御情報が一度に複数ページに亘って読み出されると、アドレス変換テーブルの作成するためのデータが一度に読み出される。そのため、短時間でアドレス変換テーブルを作成できるなど、不揮発性メモリ装置にアクセス可能となるまでの時間を短縮することができる。

## [0083]

なお、データバッファ 2 0 0 のバッファ容量は、通常は1または数ページ分の容量であるため、一度に全てのページの制御情報を読み出すことはできない。従って、例えばブロックアドレスなどを用いて所定の領域のみを選択して、データバッファ容量を超えないように制御情報を読み出すこともできる。

## [0084]

<第2実施形態例>

#### 「構成 ]

図5は、図1の第1実施形態例に係る不揮発性メモリ装置に搭載される不揮発性メモリアレイの別の構成図である。第2実施形態例では、第1実施形態例と比較して、以下に説明する不揮発性メモリアレイ、ワード線切替手段134及びビット線切替手段187の構成が異なり、その他の全体構成は第1実施形態例の図1と同様であるので説明は省略する

## [0085]

(1) 不揮発性メモリアレイ

ワード線は、複数ページの第1領域150から1ページの第1領域150を選択するた

20

10

30

40

10

20

30

40

50

めの第1ワード線132及び複数ページの第2領域160から1ページの第2領域160 を選択するための第2ワード線136を含む。ここで、第1領域150の不揮発性メモリセル170は、第1ワード線132及び第1ビット線140に接続されている。一方、第2領域160の不揮発性メモリセル170は、第2ワード線136、第1ビット線140 及び第2ビット線142に接続されている。

#### [0086]

(2)ワード線切替手段

ワード線切替手段 1 3 4 は、第 1 ワード線 1 3 2 または第 2 ワード線 1 3 6 のいずれを活性にするかを切り替える手段であり、ページ毎に対応するようにそれぞれ設けられている。また、ワード線切替手段 1 3 4 は、第 1 実施形態例のワード線切替手段 1 3 4 と異なり、図 5 に示すように例えば A N D 回路で構成されている。

[0087]

第2実施形態例では、制御情報読み出し時は、第1実施形態例と同様に第2領域160を読み出すためのS-CMDが制御信号生成部310に入力されるものとする。また、ロウアドレスバッファ/デコーダ220は、制御信号生成部310がコマンドS-CMDに基づいて生成した制御信号を受信し、AND回路のワード線切替手段134に"L"のMODE信号を入力するものとする。さらに、ロウアドレスバッファ/デコーダ220は、制御信号に基づいて複数ページの第2ワード線136を選択するための信号を生成する。この生成された信号により複数ページに亘る第2ワード線136が活性化される。あるいは、S-CMDに所定の第2ワード線136を選択するためのアドレスを含ませておき、このアドレスに基づいて複数ページに亘る第2ワード線136を活性化するようにしても良い。この第2ワード線136の信号が、AND回路のワード線切替手段134に入力されるものとする。

[0088]

ここで、AND回路に"L"のMODE信号が入力されるとその出力が"L"となり、該当する第1ワード線132が非活性化される。さらに、上述の通り複数ページに亘る第2領域160の第2ワード線136を一度に活性化することができる。

[0089]

一方、通常のコマンドが入力される場合は、入力アドレスに対応して第1ワード線132及び第2ワード線136の活性/非活性が決定される。具体的には、入力アドレスに応じて第2ワード線136が活性であれば第1ワード線132も活性となり、第2ワード線136が非活性であれば第1ワード線132も非活性となる。つまり、通常時は、ロウアドレスバッファ/デコーダ220が入力アドレスをデコードした結果、該当する第1ワード線132及び第2ワード線136のみが活性化される。

[0090]

なお、ワード線選択手段134は、S-СМDに応じて第1ワード線132及び第2ワード線136の活性/非活性を制御できれば良く、AND回路に限定されない。

[0091]

(3)ビット線切替手段

ビット線切替手段 1 8 7 は、図 5 に示すように例えば P M O S トランジスタ及び N M O S トランジスタから構成される。 N M O S トランジスタは、第 2 領域 1 6 0 の不揮発性メモリセル 1 7 0 と第 1 ビット線 1 4 0 との間にそれぞれ設けられ、 P M O S トランジスタは、第 2 領域 1 6 0 の不揮発性メモリセル 1 7 0 と第 2 ビット線 1 4 2 との間にそれぞれ設けられる。

[0092]

ここで、制御情報の読み出し時は、第2領域160を読み出すためのS-CMDに基づいて"L"のMODE信号が生成される。そして、NMOSトランジスタ及びPMOSトランジスタのゲートが、"L"のMODE信号の入力を受けると、PMOSトランジスタがONしてNMOSトランジスタがOFFし、第2領域160の不揮発性メモリセル170と第2ビット線142とが接続される。このとき、S-CMDに基づいて複数ページに

亘って複数の第2ワード線136が活性化されている。よって、ビット線選択手段180は、第2領域160の不揮発性メモリセル170から第2ビット線142を介して、複数ページに亘って制御情報を読み出すことができる。

#### [0093]

一方、通常のコマンドが入力され、"H"のMODE信号が各ゲート入力されると、PMOSトランジスタがOFFしてNMOSトランジスタがONし、第2領域160の不揮発性メモリセル170と第1ビット線140とが接続される。このとき、ロウアドレスバッファ/デコーダ220によりアクセス先のページの第1ワード線132及び第2ワード線136のみが活性化されている。よって、アクセス先のページの不揮発性メモリセル170から第1ビット線140を介してデータが読み出される。

[0094]

「制御情報の読み出しフロー ]

次に、第2実施形態例に係る不揮発性メモリアレイ115の制御情報の読み出しの流れについて、再び図4を用いて説明する。

#### [0095]

制御信号生成部310及びロウアドレスバッファ / デコーダ220は、メモリ制御部231からS-CMDの入力を受けて、"L"のMODE信を生成するとともに複数の第2ワード線136を活性する。このとき、S-CMDに所定の第2ワード線136を複数ページに亘って活性化するためのアドレスを含ませておいても良い。

## [0096]

ワード線切替手段134は、"L"のMODE信号の入力を受けて第1領域150の第1ワード線132を非活性にする。このとき、複数ページに亘る第2ワード線131が活性化されている。ビット線切替手段187は、"L"のMODE信号が入力されると、第1ビット線140と第2領域160の不揮発性メモリセル170との接続を遮断し、第2ビット線142と第2領域160の不揮発性メモリセル170とを接続する。また、ビット線選択手段180のセレクタ182は、"L"のMODE信号の入力を受けて第2ビット線142からのデータの読み出しを有効にする。このようにして、第2ビット線142から読み出された制御情報は、データバッファ200に一旦格納された後、不揮発性メモリ装置100外部へ出力される。

## [0097]

よって、制御情報が一度に複数ページに渡って読み出されるため、制御情報の読み出し時間を短縮することができる。そのため、制御情報に基づくアドレス変換テーブルの作成など、初期化に要する時間が短縮され、不揮発性メモリ装置にアクセス可能となるまでの時間を短縮することができる。

[0098]

<第3実施形態例>

[構成]

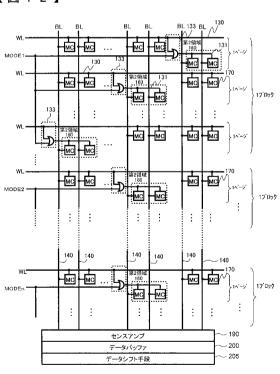

図6は、第3実施形態例に係る不揮発性メモリ装置の構成図、図7は、図6の不揮発性メモリ装置に搭載される不揮発性メモリアレイ及びビット線選択手段の構成図である。

#### [0099]

第3実施形態例では、図6及び図7に示すように、ワード線切替手段134及びビット線切替手段187が各ブロックの先頭ページに位置する第2領域160に対応して設けられている点が第2実施形態例と異なる。そして、各ブロックの先頭ページの第1領域150は、ワード線切替手段134の出力である第1ワード線132に接続され、先頭ページの第2領域160は、第2ワード線136に接続されている。また、各ブロックの先頭ページ以外のページでは、第1領域150及び第2領域160がともに共通の共通ワード線137に接続されている。その他の構成は、第2実施形態例と同様であるので説明を省略まる。

## [0100]

[制御情報の読み出しフロー]

10

20

30

次に、第3実施形態例に係る不揮発性メモリアレイ115の制御情報の読み出しの流れについて、再び図4を用いて説明する。

### [0101]

制御信号生成部310及びロウアドレスバッファ / デコーダ220は、メモリ制御部231からS-СMDの入力を受けて、"L"のMODE信を生成するとともに、各ブロックの複数の先頭ページに対応する第2ワード線136を活性化する。ビット線切替手段187及びセレクタ182の動作は、第1実施形態例と同様である。よって、複数の先頭ページの第2領域136から一度に制御情報を読み出すことができる。第3実施形態例の場合、ワード線切替手段134及びビット線切替手段187が各ブロックの先頭ページにのみ設けられているため、先頭ページの複数の第2領域160の第2情報のみを一度に読み出すことができる。

10

## [0102]

一方、各ブロックの先頭ページ以外の第2領域136にアクセスする場合には、1ページごとに共通ワード線137を活性化する。そして、1ページ毎に第2領域160から制御情報を読み出す。

#### [0103]

以上のように、第2領域160の制御情報を読み出す際に、複数ページに亘って第2領域160にアクセス可能な構成と、ページ毎に第2領域160にアクセス可能な構成とを混載しても良い。複数ページに亘って第2領域160にアクセスする場合には、制御情報の読み出し時間を短縮することができる。

20

#### [0104]

<第4実施形態例>

## [構成]

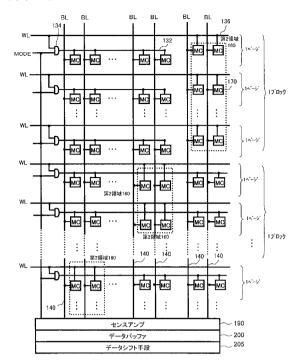

図8は、第4実施形態例に係る不揮発性メモリ装置の構成図、図9は、図8の不揮発性メモリ装置に搭載される不揮発性メモリアレイ構成図である。前述の第1乃至第3実施形態例においては、第2領域160は不揮発性メモリアレイ115においてカラムアドレスを共通にする、つまり縦方向に同じ位置するように形成されている。一方、第4実施形態例では、第2領域がブロックごとに異なる位置に配置されている。さらに、第4実施形態例では、データシフト手段205が設けられているが、ビット線切替手段及びビット線選択手段は設けられていない。以下に、第4実施形態例について説明する。なお、第1乃至第3実施形態例と同様の構成については説明を省略する。

30

## [0105]

#### (1)不揮発性メモリアレイ

第2領域160は、不揮発性メモリアレイ115上においてブロックごとに配置がシフトされ、ブロック間において第2領域160のカラムアドレスが異なるように位置している。つまり、第2領域160は、ブロック毎に異なる第1ビット線140に接続されている。例えば、図8に示すように、最初のブロックでは第2領域160が不揮発性メモリアレイ115上で右端に位置しているが、2番目のブロックでは第2領域160が最初のブロックの第2領域よりも1つ左にシフトされて配置されている。

40

### [0106]

## (2) データシフト手段

不揮発性メモリ装置100は、データシフト手段205を有している。データシフト手段205は、不揮発性メモリ装置100に入力されたデータの不揮発性メモリアレイ115上での配置をシフトさせる。

#### [0107]

不揮発性メモリ装置100は、不揮発性メモリセル内に書き込むデータとともにページアドレスやブロックアドレスを外部から受信する。このとき、不揮発性メモリ装置100に入力される1ページ分のデータは、図8のI/Oに吹き出しにより示したように、ページアドレスやブロックアドレスに関係なく常に同じ並びである。データシフト手段205は、データとともに入力されるページアドレスやブロックアドレスに基づいて、どれだけ

シフトするかを解釈し、データをシフトさせる。なお、データシフト手段205は、ブロックごとにどれだけシフトさせるかを記憶しているものとする。データの読み出しの際は逆に、読み出されたデータのページアドレスやブロックアドレスに基づいて、シフトされたデータを元の配置に戻す。つまり、I/Oにおいてやりとりされるデータの配置は、常に一定である。

#### [0108]

図8を用いてより具体的に説明すると、ホストシステム 4 0 0 側から不揮発性メモリセルへのアクセスの為の論理アドレスが入力されると、まずメモリ制御部231のアドレス変換部233が、アドレス変換テーブル237に基づいて論理アドレスを物理アドレスに変換する。 I / O から不揮発性メモリ装置 1 0 0 に、データとともにアドレスが入力されると、データシフト手段205は、次のようにデータのシフトを行う。最初のブロックに対するデータ書き込みの場合は、最初のブロックの第1領域160の最初(図中、0番目)が不揮発性メモリアレイ115上で左端に位置し、右に向かって順にその物理アドレスが増加するようにデータをシフトする。また、2番目のブロックに対するデータ書き込みの場合は、2番目のブロックの第1領域160の最初(図中、0番目)が、最初のブロックの第2領域160に対応するように位置し、右端に向かってその物理アドレスが増加し、右端に到達した後はさらに左端から順に右に向かって物理アドレスが増加するようにデータをシフトする。

## [0109]

[制御情報の読み出しフロー]

次に、第4実施形態例に係る不揮発性メモリアレイ115の制御情報の読み出しの流れについて、再び図4を用いて説明する。

#### [0110]

制御信号生成部310及びロウアドレスバッファ/デコーダ220は、メモリ制御部231から第2領域160を読み出すためのS-CMDの入力を受けて、"L"のMODE信を生成するとともに複数の第2ワード線136を活性にするための信号を生成する。

#### [0111]

ワード線切替手段134は、"L"のMODE信号の入力を受けて第1領域150の第1ワード線132を非活性にする。例えば、図9に示すようにワード線切替手段134はAND回路で構成されており、"L"のMODE信号の入力により第1ワード線132を非活性化する。ここで、同一ブロック内の第2領域160では、第1ビット線140を共有しており、異なるブロック間では、それぞれの第2領域160に接続される第1ビット線140が異なる。よって、ロウアドレスバッファ/デコーダ220は、S-CMDに基づいて、ブロックごとに1本の第2ワード線136を活性化し、複数ブロックに亘って、複数ページの第2ワード線136を複数本、活性化するのかを指定するアドレスを含ませておいても良い。このようにして、第1ビット線140から読み出された制御情報は、データバッファ200に一旦格納された後、不揮発性メモリ装置100外部へ出力される。

#### [0112]

なお、ワード線切替手段134は、第1ワード線132及び第2ワード線136の活性 / 非活性を制御できれば良く、AND回路に限定されない。

#### [0113]

このように、ブロック毎に第2領域160の配置をシフトさせて複数ブロックに亘って第2領域160から制御情報を読み出すことで、第1実施形態例で示すビット線切替手段及びビット線選択手段や第2ビット線を設ける必要がなく、不揮発性メモリ装置の小型化を図ることができる。また、制御情報に基づくアドレス変換テーブルの作成など、初期化に要する時間が短縮され、不揮発性メモリ装置にアクセス可能となるまでの時間を短縮することができる。なお、上述の通り、複数ページに亘る第2領域から制御情報が読み出される場合であっても、異なる第1ビット線から制御情報が読み出されるため、制御情報の衝突は生じない。

10

20

30

#### [0114]

<第5実施形態例>

### 「構成]

図10は、第5実施形態例に係る不揮発性メモリ装置の構成図、図11は、図10の不揮発性メモリ装置に搭載される不揮発性メモリアレイの構成図である。前述の第4実施形態例においては、第2領域160がブロックごとに異なる位置に配置されている。一方、第5実施形態例では、第2領域がページごとに異なる位置に配置されている。また、第5実施形態例においても同様に、ビット線切替手段及びビット線選択手段は設けられていない。以下に、第5実施形態例について説明する。なお、第4実施形態例と同様の構成については説明を省略する。

10

## [0115]

(1)不揮発性メモリアレイ

第2領域160は、不揮発性メモリアレイ115上においてページごとに配置がシフトされ、ページ間において第2領域160のカラムアドレスが異なるように位置している。つまり、第2領域160は、ページ毎に異なる第1ビット線140に接続されている。例えば、図11に示すように、最初のブロックの最初のページでは第2領域160が不揮発性メモリアレイ115上で右端に位置しているが、2番目のページでは第2領域160が最初のページの第2領域160よりも1つ左にシフトされて配置されている。

[ 0 1 1 6 ]

ここで、全てのページの第 2 領域が異なるように形成されても良いし、ブロック内において第 2 領域の配置がページ毎に異なるようにしても良い。

20

#### [ 0 1 1 7 ]

(2) データシフト手段

「制御情報の読み出しフロー ]

第5実施形態例の不揮発性メモリ装置100は、第4実施形態例と同様のデータシフト 手段205を有している。

[0118]

図10を用いてより具体的に説明すると、不揮発性メモリ装置100にI/Oから配置が一定のデータとともにアドレスが入力されると、データシフト手段205は、次のようにデータのシフトを行う。

[0119]

30

最初のブロックの最初のページに対するデータ書き込みの場合は、第2領域160が不揮発性メモリアレイ115上で右端に位置するようにデータをシフトする。より具体的には、第1領域160の最初(図中、0番目)が不揮発性メモリアレイ115上で左端に位置し、右に向かって順にその物理アドレスが増加するようにシフトする。また、最初のブロックの2番目のページに対するデータ書き込みの場合は、第2領域160が最初のページの第2領域よりも1つ左に位置するようにデータをシフトする。より具体的には、2番目のページでは、第1領域160の最初(図中、0番目)が、最初のページの第2領域160に対応するように位置し、右端に向かってその物理アドレスが増加し、右端に到達した後はさらに左端から順に右に向かって物理アドレスが増加するようにシフトする。

40

次に、第5実施形態例に係る不揮発性メモリアレイ115の制御情報の読み出しの流れについて、再び図4を用いて説明する。

## [0120]

ワード線切替手段134は、例えば図11に示すようにAND回路で構成されており、制御信号生成部310及びロウアドレスバッファ/デコーダ220から"L"のMODE信号の入力を受けて第1領域150の第1ワード線132を非活性にする。ここで、同一ブロック内の第2領域160の不揮発性メモリセルは、ページ毎に異なる第1ビット線140に接続されている。よって、ロウアドレスバッファ/デコーダ220は、第2領域160を読み出すためのS・CMDに基づいて、1ブロック内の複数ページに亘る第2ワード線136を一度に活性化する。そして、1プロック単位で複数の第2ワード線136を

順に活性化する。ここで、S-СМDに所定のブロック内の複数の第2ワード線136を活性化するためのアドレスを含ませておいても良い。活性化された第2ワード線136及び第1ビット線140により読み出された制御情報は、データバッファ200に一旦格納された後、不揮発性メモリ装置100外部へ出力される。

## [0121]

このように、ブロック内のページ毎に第 2 領域 1 6 0 の配置をシフトさせ、ブロック内の複数ページに亘って第 2 領域 1 6 0 から制御情報を読み出すことで、第 1 実施形態例で示すビット線切替手段及びビット線選択手段や第 2 ビット線を設ける必要がなく、不揮発性メモリ装置の小型化を図ることができる。また、制御情報に基づくアドレス変換テーブルの作成など、初期化に要する時間が短縮され、不揮発性メモリ装置にアクセス可能となるまでの時間を短縮することができる。なお、上述の通り、複数ページに亘る第 2 領域から制御情報が読み出される場合であっても、異なる第 1 ビット線から制御情報が読み出されるため、制御情報の衝突は生じない。

## [0122]

<第6実施形態例>

#### 「構成 ]

図12は、図10の第5実施形態例に係る不揮発性メモリ装置に搭載される不揮発性メモリアレイの別の構成図である。

#### [0123]

第6実施形態例では、第5実施形態例と同様に不揮発性メモリアレイ115上における第2領域160の位置をシフトさせ、第1実施形態例と同様にワード線切替手段133としてOR回路を用いている。ワード線切替手段133の入力には、第1領域150に接続される第1ワード線130と、MODE信号(図12中、MODE1、MODE2…)とが接続され、出力には、第2領域160に接続される第2ワード線131が接続される。また、ワード線切替手段133には、ブロックごとに異なるMODE信号、つまり最初のブロックにはMODE2が入力されている。このように異なるMODE信号を入力することで、第2領域160の不揮発性メモリセルされるデータの衝突を避けることができる。また、第2領域160の不揮発性メモリセルは、図12に示すように異なるブロック間において第1ビット線140を共有する。その他の構成は、第1または第5実施形態例と同様であるので説明を省略する。

### [0124]

## [制御情報の読み出しフロー]

次に、第6実施形態例に係る不揮発性メモリアレイ115の制御情報の読み出しの流れについて、再び図4を用いて説明する。

## [0125]

制御信号生成部310及びロウアドレスバッファ / デコーダ220は、メモリ制御部231から第2領域160を読み出すためのS-CMDの入力を受けて、" H "のMODE信を生成する。また、ロウアドレスバッファ / デコーダ220は、S-CMDの入力を受けて、ブロック単位で順に活性化されるように各ブロック単位で複数ページに亘る第2ワード線131を活性化する。このとき、S-CMDにどのブロックの複数ページを活性化するのかを指定するアドレスを含ませておいても良い。

#### [0126]

ワード線切替手段 1 3 3 は、例えば図 1 2 に示すようにOR回路で構成されており、 " H "のM O D E 信号の入力を受けて、第 1 ワード線 1 3 0 の入力の如何によらず、複数ページに亘る第 2 領域 1 6 0 の第 2 ワード線 1 3 1 を活性にする。よって、複数ページに亘る第 2 領域 1 6 0 それぞれから対応する第 1 ビット線 1 4 0 を介して、制御情報がセンスアンプ 1 9 0 に読み出され、データバッファ 2 0 0 に一旦格納された後、メモリ装置外部へ出力される。

## [0127]

以上の構成により、第5実施形態例と同様の効果を得ることができる。

10

20

30

10

20

30

40

50

#### [0128]

#### <第7実施形態例>

第7実施形態例では、制御情報の読み出しにおける別のフローを説明する。図13は、READコマンド及び複数のアドレスの入力により、不揮発性メモリ装置100から制御情報を読み出す場合のタイミングチャートの一例である。例えば、第2実施形態例に示す図5の不揮発性メモリ装置100を用いて、別の制御情報の読み出しフローを説明する。

#### [0129]

制御情報の読み出し時は、メモリ制御部231は、まず外部信号CLEとともに、通常のページ読み出しのREADコマンドを入力する。次に、外部信号ALEとともに複数の所望のアドレスS-ADDRを入力する。ここで、R/B信号がローからハイに変化した後、外部信号NREが変化すると、不揮発性メモリアレイ115の複数ページに亘る第2領域160から制御情報が読み出される。

#### [0130]

具体的には、制御情報の読み出し時は、制御信号生成部310及びロウアドレスバッファ/デコーダ220は、受信したREADコマンドから"L"のMODE信号を生成し、ワード線切替手段134、ビット線切替手段187及びビット線選択手段180のセレクタ182に入力する。さらに、ロウアドレスバッファ/デコーダ220は、入力されたアドレス変換後のアドレスをデコードし、該当する第2ワード線136を活性にする。このとき、ロウアドレスバッファ/デコーダ220は、図13に示すように、複数入力されたアドレスに対応する、複数ページの第2ワード線136を活性化する。ワード線切替手段134は、ページ毎にそれぞれ設けられており、生成された"L"のMODE信号を受けて第1領域の第1ワード線132を非活性にする。

#### [0131]

ビット線切替手段187及びビット線選択手段180のセレクタ182は、"L"のMODE信号の入力を受けて第2ビット線142からのデータの読み出しを有効にする。そして、複数ページに亘る第2領域160それぞれから対応する第2ビット線142を介して、制御情報がセレクタ182に読み出され、データバッファ200に一旦格納される。

[0132]

このように、制御情報が一度に複数ページに渡って読み出されるため、制御情報の読み出し時間を短縮することができる。また、コマンドの入力とともにアドレスが入力されることで、ブロックごとに第2領域160を読み出したり、アドレスにより指定された第2領域160を読み出すことができる。前述の第1、第3至第6実施形態例においても同様に、第7実施形態例の図13に示す読み出しフローにより制御情報を読み出しすることが可能である。例えば、図6及び図7に示す第3実施形態例では、アドレス指定により各ブロックの複数の先頭ページのみを活性化する。図8及び図9に示す第4実施形態例では、アドレス指定により各ブロックから1ページずつ、複数ブロックに亘って活性化する。図10~図12に示す第5、第6実施形態例では、アドレス指定によりブロック毎に、ブロック内の複数ページを活性化する。

## [0133]

また、このようにアドレスを指定することにより第2領域から読み出す制御情報の大き さを調整することができる。

#### [0134]

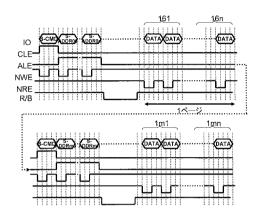

## <第8実施形態例>

第8実施形態例では、制御情報の読み出しにおけるさらに別のフローを説明する。図14は、第2領域160を読み出すためのS-CMD及び複数のアドレスの入力により、不揮発性メモリ装置100から制御情報を読み出す場合のタイミングチャートの別の一例である。例えば、第2実施形態例に示す図5の不揮発性メモリ装置100を用いて、別の制御情報の読み出しフローを説明する。

#### [0135]

不揮発性メモリ装置100のメモリ容量が増加すると、ページ数が増加し、一回のコマ

ンド入力では必要な第2領域160の制御情報を全て読み出せない場合がある。

#### [0136]

そこで、制御情報の読み出し時は、メモリ制御部231は、まず外部信号CLEとともに、S-CMDを入力する。次に、外部信号ALEとともに、所望の第2領域160を含む複数のページを指定するためのアドレスS-ADDR00~SADDR0nを入力する。ここで、R/B信号がローからハイに変化した後、外部信号NREが変化すると、不揮発性メモリアレイ115の第2領域160から制御情報が読み出される。ここでは、1回目の読み出しにより第2領域161~161nの制御情報が読み出される。続いて、同様に所望の第2領域を含むアドレスS-ADDRm0~SADDRmnを入力する。するのは、図14に示すように第2領域1m0~1mnの制御情報を読み出すことができる。このように、1回の制御情報の読み出しでは、全ての読み出しデータが読み出されない場合、つまり、読み出しの必要な制御情報の容量がデータバッファ200の容量をこえている場合は、図14に示すように数回に分けて読み出す。このように、コマンドの入力とともにアドレスが入力することを繰り返すことで、複数回にわたって第2領域160の制御情報を読み出すことができる。

### [0137]

前述の第1、第3乃至第6実施形態例においても同様に、第8実施形態例の図14に示す読み出しフローにより制御情報を読み出しすることが可能である。

#### [0138]

<その他の実施形態例>

(A)

前述の実施形態例では、アドレス変換部233、RAM235及びアドレス変換テーブル237は、不揮発性メモリ装置100外部のメモリ制御部231内に設けられている。これらのアドレス変換部233、RAM235及びアドレス変換テーブル237は、図15に示すように不揮発性メモリ装置100内部に設けられていても良い。

### [0139]

その場合、不揮発性メモリ装置100の電源投入時に、第2領域160から制御情報が読み出される。不揮発性メモリ装置100内部のコントローラ300は、この制御情報に基づいてアドレス変換のためのアドレス変換テーブルを作成し、RAM235にアドレス変換テーブルを記憶する。データの読み出し書き込み時には、アドレス変換部233がアドレス変換テーブルに基づいてアドレス変換を行う。

[0140]

(B)

上記実施形態例では、第1領域150及び第2領域160の不揮発性メモリセルは、それぞれ異なるワード線に接続されている。例えば、図1の不揮発性メモリ装置100の第1領域150は第1ワード線130に接続されており、第2領域160は第2ワード線131に接続されている。そして、第2領域160の制御情報を読みだす場合には、対応する第2ワード線131を活性化する。このとき、第1ワード線130は非活性の状態にある。しかし、例えば第1領域150及び第2領域160が共通のワード線に接続されるのよび第2領域160が共通のワード線に接続されるのド線を活性化し、対応する第2ビット線を介して第2領域160から制御情報を読みだす。このとき、第1領域150及び第2領域160が共通のワード線に接続されているのとき、第1領域150のワード線に接続されているの、その共通のワード線に接続されている第1領域150のワード線も活性化されているの、その共通のワード線に接続されている第1領域150のワード線も活性化されているの共通のワード線に接続されている第1領域150のワード線も活性化されているには、第1領域150の第1ビット線140は選択されず、第1領域150からはデータは読みだされない。以上のようにワード線を共通化することで、構成を簡単化することができる。また、第1ワード線130または第2ワード線131のいずれかを活性化するためのワード線切替手段133も不要であり構成が簡単になる。

【産業上の利用可能性】

[0141]

10

20

30

本発明にかかる不揮発性メモリ装置は、電源投入時の初期化処理時間を短縮できる構成を有し、メモリカード等の外部記憶装置に用いるメモリとして有用である。また携帯電話、デジタルカメラ等 AV機器に内蔵する記憶装置の用途にも応用できる。

## 【図面の簡単な説明】

- [0142]

- 【図1】第1実施形態例に係る不揮発性メモリ装置の構成図。

- 【図2】図1の不揮発性メモリ装置に搭載される不揮発性メモリアレイ及びビット線選択手段の構成図。

- 【図3】データバッファ200に格納される様子を示す模式図。

- 【図4】第1実施形態例に係る不揮発性メモリ装置100から制御情報を読み出す場合の 10 タイミングチャートの一例。

- 【図 5 】図 1 の第 1 実施形態例に係る不揮発性メモリ装置に搭載される不揮発性メモリアレイの別の構成図。

- 【図6】第3実施形態例に係る不揮発性メモリ装置の構成図。

- 【図7】図6の不揮発性メモリ装置に搭載される不揮発性メモリアレイ及びビット線選択手段の構成図。

- 【図8】第4実施形態例に係る不揮発性メモリ装置の構成図。

- 【図9】図8の不揮発性メモリ装置に搭載される不揮発性メモリアレイの構成図。

- 【図10】第5実施形態例に係る不揮発性メモリ装置の構成図。

- 【図11】図10の不揮発性メモリ装置に搭載される不揮発性メモリアレイの構成図

- 【図12】図10の第5実施形態例に係る不揮発性メモリ装置に搭載される不揮発性メモリアレイの別の構成図。

- 【図13】不揮発性メモリ装置100から制御情報を読み出す場合のタイミングチャートの一例。

- 【図14】不揮発性メモリ装置100から制御情報を読み出す場合のタイミングチャートの別の一例。

- 【図15】不揮発性メモリ装置のその他の構成図。

- 【図16】従来の不揮発性メモリ装置の構成図。

- 【図17】従来の不揮発性メモリ装置のメモリセルアレイの接続を示す説明図。

- 【図18】従来の不揮発性メモリ装置における第2領域の読み出し動作を示すタイミング 30 チャート。

- 【図19】従来の不揮発性メモリ装置における読み出し時のデータバッファのデータ構成図。

## 【符号の説明】

- [0143]

- 100: 不揮発性メモリ装置

- 110:不揮発性メモリ装置のブロック

- 120:不揮発性メモリ装置のページ

- 130、132:第1ワード線

- 131、136:第2ワード線

- 1 4 0 : 第 1 ビット線

- 1 4 2 : 第 2 ビット線

- 150:第1領域

- 1 6 0 : 第 2 領域

- 180:ビット線選択手段

- 190:センスアンプ

- 200:データバッファ

- 230:コントローラ

40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

## 【図13】

【図14】

【図15】

【図16】

【図17】

# 【図18】

# 【図19】

## フロントページの続き

(72)発明者 外山 昌之

大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72)発明者 清原 督三

大阪府門真市大字門真1006番地 松下電器産業株式会社内

審査官 外山 毅

(56)参考文献 特開2002-373496(JP,A)

特開昭61-243545 (JP,A)

特開2003-015929(JP,A)

米国特許出願公開第2004/0145952(US,A1)

(58)調査した分野(Int.CI., DB名)

G11C 16/00 - 16/34