# (19) **日本国特許庁(JP)**

# (12) 公開特許公報(A)

(11)特許出願公開番号

特開2004-247593 (P2004-247593A)

(43) 公開日 平成16年9月2日(2004.9.2)

(51) Int.C1.<sup>7</sup>

FI

テーマコード (参考)

HO1L 29/78 HO1L 21/336 HO1L 29/78 655B HO1L 29/78 652L HO1L 29/78 653A HO1L 29/78 658A

審査請求 未請求 請求項の数 12 OL (全 17 頁)

(21) 出願番号 (22) 出願日 特願2003-37004 (P2003-37004) 平成15年2月14日 (2003.2.14) (71) 出願人 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74)代理人 100075812

弁理士 吉武 賢次

(74) 代理人 100088889

弁理士 橘谷 英俊

(74) 代理人 100082991

弁理士 佐藤 泰和

(74) 代理人 100096921

弁理士 吉元 弘

(74) 代理人 100103263

弁理士 川崎 康

最終頁に続く

#### (54) 【発明の名称】半導体装置及びその製造方法

# (57)【要約】

【課題】アノードショート状態の発生を阻止した、オン 電圧特性及びスイッチング特性に優れた半導体装置及び その製造方法を提供する。

【解決手段】第2導電型ドレイン層と、前記第2導電型ドレイン層上に形成された第1導電型バッファ層と、前記第1導電型バッファ層上に形成された第1導電型高抵抗層と、前記第1導電型高抵抗層の表面に形成された第2導電型ベース層の表面に形成された第1導電型ソース層の表面がら前記第1導電型と、前記第1導電型ソース層の表面から前記第1導電型高抵抗層に達するトレンチの内壁に形成された絶縁膜と、前記トレンチの内部に形成されたゲート電極と、前記第2導電型ベース層及び前記第1導電型ソース層の表面に形成されたソース電極と、前記第2導電型ドレイン層の表面に形成されたドレイン電極と、を備え、前記第1導電型バッファ層の不純物濃度を、前記第2導電型ドレイン層側における表面近傍において相対的に低濃度とする。

【選択図】 図1

### 【特許請求の範囲】

# 【請求項1】

第2導電型ドレイン層と、

前記第2導電型ドレイン層上に形成された第1導電型バッファ層と、

前記第1導電型バッファ層上に形成され、前記第1導電型バッファ層よりも不純物濃度の低い第1導電型高抵抗層と、

前記第1導電型高抵抗層の表面領域に形成された第2導電型ベース層と、

前記第2導電型ベース層の表面領域に形成された第1導電型ソース層と、

前記第1導電型ソース層の表面から前記第2導電型ベース層を貫通して前記第1導電型高抵抗層に達するトレンチの底面及び周壁に形成された絶縁膜と、

前記トレンチの内部に前記絶縁膜を介して形成されたゲート電極と、

前記第2導電型ベース層及び前記第1導電型ソース層の表面に形成されたソース電極と、

前記第2導電型ドレイン層の表面に形成されたドレイン電極と、を備え、

前記第1導電型バッファ層の不純物濃度は、前記第2導電型ドレイン層側における表面近傍において相対的に低濃度であることを特徴とする半導体装置。

#### 【請求項2】

第2導電型ドレイン層と、

前記第2導電型ドレイン層上に形成された第1導電型バッファ層と、

前記第1導電型バッファ層上に形成され、前記第1導電型バッファ層よりも不純物濃度の低い第1導電型高抵抗層と、

前記第1導電型高抵抗層の表面領域に形成された第2導電型ベース層と、

前記第2導電型ベース層の表面領域に形成された第1導電型ソース層と、

前記第1導電型ソース層、前記第2導電型ベース層、前記第1導電型高抵抗層の表面に形成された絶縁膜と、

前記絶縁膜の表面に形成されたゲート電極と、

前 記 第 2 導 電 型 ベ ー ス 層 及 び 前 記 第 1 導 電 型 ソ ー ス 層 の 表 面 に 形 成 さ れ た ソ ー ス 電 極 と 、

前記第2導電型ドレイン層の表面に形成されたドレイン電極と、を備え、

前記第1導電型バッファ層の不純物濃度は、前記第2導電型ドレイン層側における表面近傍において相対的に低濃度であることを特徴とする半導体装置。

### 【請求項3】

前記第1導電型バッファ層の前記第2導電型ドレイン層側における表面近傍の不純物濃度は、前記ドレイン電極が前記第1導電型バッファ層を貫通して前記第2導電型ドレイン層に接触した状態のときにオーミック接触を形成しない程度に低いことを特徴とする請求項1又は2に記載の半導体装置。

# 【請求項4】

前記第1導電型バッファ層はn型バッファ層であり、前記ドレイン電極はアルミニウムを 主体とする金属により構成されており、

前記第1導電型バッファ層の表面近傍の不純物濃度は、1.0×10<sup>19</sup> cm<sup>・3</sup> 以下であることを特徴とする請求項1乃至3のいずれかに記載の半導体装置。

#### 【請求項5】

前記第1導電型バッファ層はn型バッファ層であり、前記ドレイン電極はアルミニウムを 主体とする金属により構成されており、

前記第1導電型バッファ層の表面近傍の不純物濃度は、5.0×10<sup>18</sup> cm<sup>-3</sup> 以下であることを特徴とする請求項1乃至3のいずれかに記載の半導体装置。

#### 【請求項6】

前記第1導電型バッファ層はn型バッファ層であり、前記ドレイン電極は、クロム、銀及び金の少なくともいずれかを主体とする金属により構成されており、

前記第1導電型バッファ層の表面近傍の不純物濃度は、1.0×10<sup>18</sup> cm<sup>-3</sup> 以下であることを特徴とする請求項1乃至3のいずれかに記載の半導体装置。

# 【請求項7】

50

40

10

20

前 記 第 1 導 電 型 バ ッ フ ァ 層 は n 型 バ ッ フ ァ 層 で あ り 、 前 記 ド レ イ ン 電 極 は 、 ク ロ ム 、 銀 及 び金の少なくともいずれかを主体とする金属により構成されており、

前記第1導電型バッファ層の表面近傍の不純物濃度は、7.0×10<sup>1 7</sup> cm<sup>・ 3</sup> 以下で あることを特徴とする請求項1乃至3のいずれかに記載の半導体装置。

前 記 第 1 導 電 型 バ ッ フ ァ 層 は p 型 バ ッ フ ァ 層 で あ り 、 前 記 ド レ イ ン 電 極 は 、 ク ロ ム 、 銀 及 び金の少なくともいずれかを主体とする金属により構成されており、

前記第1導電型バッファ層の表面近傍の不純物濃度は、9.0×10<sup>16</sup> c m <sup>・3</sup> 以下で あることを特徴とする請求項1乃至3のいずれかに記載の半導体装置。

#### 【請求項9】

前 記 第 1 導 電 型 バ ッ フ ァ 層 は p 型 バ ッ フ ァ 層 で あ り 、 前 記 ド レ イ ン 電 極 は 、 ク ロ ム 、 銀 及 び金の少なくともいずれかを主体とする金属により構成されており、

前記第1導電型バッファ層の表面近傍の不純物濃度は、1.5×10<sup>16</sup> cm<sup>-3</sup> 以下で あることを特徴とする請求項1乃至3のいずれかに記載の半導体装置。

# 【請求項10】

前 記 第 1 導 電 型 バ ッ フ ァ 層 の 低 不 純 物 濃 度 領 域 は 、 前 記 第 1 導 電 型 バ ッ フ ァ 層 の 前 記 第 2 導電型ドレイン層側における表面から 1 . 0 μ m 以下の領域であることを特徴とする請求 項1乃至8のいずれかに記載の半導体装置。

# 【請求項11】

第1導電型基板の表面領域に第2導電型ベース層を形成し、

前記第2導電型ベース層の表面領域に第1導電型ソース層を形成し、

前 記 第 1 導 電 型 ソ - ス 層 の 表 面 か ら 前 記 1 導 電 型 基 板 に 達 す る ト レン チ を 形 成 し た 後 、 前 記トレンチの内壁に絶縁膜を形成し、

前記トレンチの内部にゲート電極を形成し、

前記第2導電型ベース層及び前記第1導電型ソース層の表面にソース電極を形成し、

前 記 第 1 導 電 型 基 板 の 裏 面 か ら 第 1 導 電 型 不 純 物 を 1 M e V 以 上 の 加 速 エ ネ ル ギ ー で 打 ち 込んで、前記第1導電型基板の裏側方向における表面近傍の不純物濃度が相対的に低濃度 の 第 1 導 電 型 バ ッ フ ァ 層 を 形 成 し 、

前 記 第 1 導 電 型 バ ッ フ ァ 層 に 第 2 導 電 型 不 純 物 を 打 ち 込 ん で 第 2 導 電 型 ド レ イ ン 層 を 形 成

前記第2導電型ドレイン層の表面にドレイン電極を形成する、

ことを特徴とする半導体装置の製造方法。

#### 【 請 求 項 1 2 】

第1導電型基板上に、前記第1導電型基板の不純物濃度よりも不純物濃度の低い第1導電 型高抵抗層をエピタキシャル成長させ、

前記第1導電型高抵抗層の表面領域に第2導電型ベース層を形成し、

前記第2導電型ベース層の表面領域に第1導電型ソース層を形成し、

前 記 第 1 導 電 型 ソ - ス 層 の 表 面 か ら 前 記 1 導 電 型 基 板 に 達 す る ト レン チ を 形 成 し た 後 、 前 記トレンチの内壁に絶縁膜を形成し、

前記トレンチの内部にゲート電極を形成し、

前記第2導電型ベース層及び前記第1導電型ソース層の表面にソース電極を形成し、

前 記 第 1 導 電 型 基 板 の 裏 面 か ら 第 2 導 電 型 不 純 物 を 打 ち 込 ん で 第 2 導 電 型 ド レ イ ン 層 を 形 成するとともに、前記第1導電型基板の前記第2導電型ドレイン層側における表面近傍の 不純物濃度を相対的に下げ、

前記第2導電型ドレイン層の表面にドレイン電極を形成する、

ことを特徴とする半導体装置の製造方法。

【発明の詳細な説明】

# [00001]

# 【発明の属する技術分野】

本 発 明 は 、 半 導 体 装 置 及 び そ の 製 造 方 法 に 関 し 、 例 え ば 、 絶 縁 ゲ ー ト バ イ ポ ー ラ ト ラ ン ジ

30

20

10

40

(4)

スタ(IGBT: Insulating Gate Bi-polar Transis tor)及びその製造方法に関する。

### [0002]

#### 【従来の技術】

近年、絶縁ゲートバイポーラトランジスタ(IGBT:Insulating GateBi-polar Transistor)に関する技術は著しく進歩し、過去十数年の間に、例えばIGBTのオン電圧の低減化やスイッチング速度の高速化は著しく進んだ。これによって、現在では、例えば耐圧が600V系のIGBTにおいて、電流のフォールタイムが100ns、電流密度が150A/cm²、オン電圧が1.8V以下の製品が開発されており、さらなるオン電圧の低減化及びスイッチング速度の高速化が要求されている。一方で、スイッチング速度の高速化に伴って、スイッチングの際に生じる誘起ノイズの低減も求められている。

# [0003]

# [0004]

このIGBTの構造について詳細に説明する。

p \* 型基板(ドレイン層)31上に、 n型バッファ層32及び n 型高抵抗層33が順次エピタキシャル成長法により形成されている。この n型バッファ層32は、 p \* 型基板(ドレイン層)31から n 型高抵抗層33へのキャリアの注入効率を下げてスイッチスを変えるためのものである。この n 型高抵抗層33の表面には p 型ベース層34が形成されている。この p 型ベース層34の表面の一部は、 D 型ベース層34の表面の一部は、 D 型ベース層34の表面の一部には、 上記高濃度領域と一部重なった状態で n \* 型ソース領域35が形成されている。これら p 型ベース領域35の表面に接してソース電極39が形成されている。 n \* 型ソース領域35の表面から内部へ向けて n 型高抵抗層33に接するトレンチ36が形成されている。このトレンチ36の底面及び周壁にはゲートの達するトレンチ36が形成されている。一方、 p \* 型基板31の下面にはドレイン電極40が形成されている。

# [0005]

上述したIGBTは、例えばエピタキシャル基板(エピタキシャルウェハ)を用いて製造される。しかし、エピタキシャル基板は、製造コストが高く付くため、その結果IGBTの製造コストも高く付いてしまう。

# [0006]

また、上のIGBTでは、n型高抵抗層33におけるキャリア・ライフタイムを短くするため、ウエハプロセスの終了後に全域に電子線を照射している。これにより、確かに、n型高抵抗層33中のキャリア濃度は低下し、スイッチング速度は高速化される。

# [0007]

しかし、 n <sup>-</sup> 型高抵抗層 3 3 のキャリア濃度が低下すると、通電時における n <sup>-</sup> 型高抵抗層 3 3 の電圧降下が大きくなる問題が生じる。即ち、オン電圧が高くなる問題が生じる。

# [0008]

仮に、上述したキャリア・ライフタイム制御を行わなければ n 型高抵抗層 3 3 のキャリア濃度の低下は抑制されオン電圧を低できるが、スイッチング速度(ターンオフ時間)は極端に遅くなる。

# [0009]

このように、オン電圧とターンオフ時間とはトレードオフの関係にあり、また、キャリア・ライフタイム制御によるオン電圧 - ターンオフ時間のトレードオフ特性は良くないため、上述のIGBTの構造では素子特性の向上に限界があった。

20

30

30

40

50

[0010]

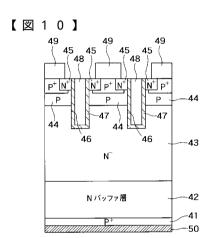

図10は、従来の別の縦型IGBTを示す縦断面図である。

このIGBTは、上で述べたIGBTの特性を改善したものである。

[0011]

より詳しくは、このIGBTは、図10から分かるように、パンチスルー型を有し、低ドーズ量により形成された、つまり低注入量のp<sup>+</sup> 型ドレイン層41を備えている。この低ドーズ量によるp<sup>+</sup> 型ドレイン層41はノンパンチスルー型のIGBTで広く用いられているものである。この低注入量によるp<sup>+</sup> 型ドレイン層41を用いることでn 型高抵抗層43へのキャリアの注入効率を抑えることができる。これにより上述のしたトレードオフ特性の悪いキャリア・ライフタイム制御を行うことなくスイッチング速度の高速化を図ることができる。なお、このIGBTは、このn 型高抵抗層43とp <sup>+</sup> 型ドレイン層41との間に形成したn型バッファ層42によって特に耐圧を維持するものであるので、n型高抵抗層43の厚さを薄くできる特徴を有する。

[0012]

[0013]

【特許文献1】

特開平11-274484号公報

【特許文献2】

米国特許第5466951号明細書

【特許文献3】

米国特許第5506153号明細書

【非特許文献1】

T. Matsudai他3名 "Advanced 60µm Thin 600V Punch-Through IGBT Concept for Extremely Low Forward Voltage and Low Turn-Off Loss" Thursday, June 7, Proceedings of 2001 International Symposium on Power Semiconductor Devices & ICs(ISPSD'01), p441-44

【非特許文献2】

T.matsudai他2名 "New 600V Trech Gate Punch-Through IGBT Concept with Very Thin Wafer and Low Efficiency p-emitter, having an On-state Voltage Drop lower than Diodes" April 3-7, 2000, International Power Electronics Conference (IPEC-TOKYO 2000), P292-296

【非特許文献3】

T. Laska他4名"The Field Stop IGBT(FS IGBT)

- A New Power Device Concept with a Great Improvement Potential" May 22-25, 2000,

The 12th International Symposium on Power Semiconductor Devices & ICs(ISPSD'2000), P355-358

# 【非特許文献4】

J.G.Bauer他5名"6.5kV-Modules using IGBTs with Field Stop Technology" JUNE 4-7, 2001 Proceedings of 13th International Symposium on Power Semiconductor Dvieces & ICs(ISPSD'01), P121-124

#### 【非特許文献5】

Katsumi Nakamura他5名"Advanced Wide Cell Pitch CSTBTs Having Light Punch-Through (LPT) Structures"Proceedings of 14th International Symposium on Power Semiconductor Devices & ICs 2002, P277-280

#### [ 0 0 1 4 ]

# 【発明が解決しようとする課題】

しかしながら、 p <sup>+</sup> 型ドレイン層 4 1 の厚さは非常に薄いため、製造プロセス中に、何らかの原因で、 p <sup>+</sup> 型ドレイン層 4 1 中に欠損が生じる可能性が高い。例えば、製造工程中に空気中のダストが p <sup>+</sup> 型ドレイン層 4 1 に付着したことが原因となって物理的に欠損が生じることがある。また、 p <sup>+</sup> 型ドレイン層 4 1 の表面にアルミニウムによるドレイン電極 5 0 を形成する際にアルミスパイクが生成され、このアルミスパイクによって p <sup>+</sup> 型ドレイン層 4 1 が部分的に欠損することがある。このように p <sup>+</sup> 型ドレイン層 4 1 に欠損が生じると、この p <sup>+</sup> 型ドレイン層 4 1 の欠損部分を介してドレイン電極 5 0 と n 型バッファ層 4 2 とが電気的に接続した状態、いわゆるアノードショート状態が生じ、素子不良となる。

# [0015]

以上に述べたところをまとめると以下のようになる。

図 9 に示すような厚い p <sup>†</sup> 型基板 3 1 を用いた I G B T では、トレードオフ特性の悪いキャリア・ライフタイム制御が必須となるため、素子特性の向上には限界があった。

# [0016]

また、図10に示すような薄いp<sup>+</sup> 型ドレイン層41とn 型高抵抗層43との間にn型バッファ層42を形成し、このn型バッファ層42で耐圧を維持するIGBTでは、IGBTの製造工程中に、薄いp<sup>+</sup> 型ドレイン層42に欠損が生じる恐れが高かった。薄いp<sup>+</sup> 型ドレイン層42に欠損が生じた場合、この欠損部分を介してnバッファ層42とドレイン電極50とが電気的に接続するアノードショート状態が発生し、素子不良となることを防ぐのは困難であった。

# [0017]

本発明は、上記問題点に鑑みてなされたものであり、その目的は、アノードショート状態の発生を阻止した半導体装置及びその製造方法を、オン電圧特性及びスイッチング特性に優れたものとして提供することにある。

# [0018]

# 【課題を解決するための手段】

本発明の第1の半導体装置は、第2導電型ドレイン層と、前記第2導電型ドレイン層上に 形成された第1導電型バッファ層と、前記第1導電型バッファ層上に形成され、前記第1 導電型バッファ層よりも不純物濃度の低い第1導電型高抵抗層と、前記第1導電型高抵抗層の表面領域に形成された第2導電型ベース層と、前記第2導電型ベース層の表面領域に 形成された第1導電型ソース層と、前記第1導電型ソース層の表面から前記第2導電型ベース層を貫通して前記第1導電型高抵抗層に達するトレンチの底面及び周壁に形成された 絶縁膜と、前記トレンチの内部に前記絶縁膜を介して形成されたゲート電極と、前記第2 10

20

30

40

導電型ベース層及び前記第1導電型ソース層の表面に形成されたソース電極と、前記第2 導電型ドレイン層の表面に形成されたドレイン電極と、を備え、前記第1導電型バッファ 層の不純物濃度は、前記第2導電型ドレイン層側における表面近傍において相対的に低濃 度であるものとして構成される。

(7)

#### [0019]

本発明の第2の半導体装置は、第2導電型ドレイン層と、前記第2導電型ドレイン層上に 形成された第1導電型バッファ層と、前記第1導電型バッファ層上に形成され、前記第1 導電型バッファ層よりも不純物濃度の低い第1導電型高抵抗層と、前記第1導電型高抵抗 層の表面領域に形成された第2導電型ベース層と、前記第2導電型ベース層の表面領域に 形成された第1導電型ソース層と、前記第1導電型ソース層、前記第2導電型ベース層、 前記第1導電型高抵抗層の表面に形成された絶縁膜と、前記絶縁膜の表面に形成されたゲ ート電極と、前記第2導電型ベース層及び前記第1導電型ソース層の表面に形成されたソ - ス 電 極 と 、 前 記 第 2 導 電 型 ド レ イ ン 層 の 表 面 に 形 成 さ れ た ド レ イ ン 電 極 と 、 を 備 え 、 前 記第1導電型バッファ層の不純物濃度は、前記第2導電型ドレイン層側における表面近傍 において相対的に低濃度であるものとして構成される。

本発明の第1の半導体装置の製造方法は、第1導電型基板の表面領域に第2導電型ベース 層を形成し、前記第2導電型ベース層の表面領域に第1導電型ソース層を形成し、前記第 1 導電型ソース層の表面から前記 1 導電型基板に達するトレンチを形成した後、前記トレ ン チ の 内 壁 に 絶 縁 膜 を 形 成 し 、 前 記 ト レ ン チ の 内 部 に ゲ ー ト 電 極 を 形 成 し 、 前 記 第 2 導 電 型 ベ ー ス 層 及 び 前 記 第 1 導 電 型 ソ ー ス 層 の 表 面 に ソ ー ス 電 極 を 形 成 し 、 前 記 第 1 導 電 型 基 板 の 裏 面 か ら 第 1 導 電 型 不 純 物 を 1 M e V 以 上 の 加 速 エ ネ ル ギ ー で 打 ち 込 ん で 、 前 記 第 1 導電型基板の裏側方向における表面近傍の不純物濃度が相対的に低濃度の第1導電型バッ ファ 層を形成 し、 前 記 第 1 導 電 型 バッファ 層 に 第 2 導 電 型 不 純 物 を 打 ち 込 ん で 第 2 導 電 型 ドレイン層を形成し、前記第2導電型ドレイン層の表面にドレイン電極を形成するものと して構成される。

# [ 0 0 2 1 ]

本発明の第2の半導体装置の製造方法は、第1導電型基板上に、前記第1導電型基板の不 純物濃度よりも不純物濃度の低い第1導電型高抵抗層をエピタキシャル成長させ、前記第 1導電型高抵抗層の表面領域に第2導電型ベース層を形成し、前記第2導電型ベース層の 表 面 領 域 に 第 1 導 電 型 ソ ー ス 層 を 形 成 し 、 前 記 第 1 導 電 型 ソ ー ス 層 の 表 面 か ら 前 記 1 導 電 型 基 板 に 達 す る ト レ ン チ を 形 成 し た 後 、 前 記 ト レ ン チ の 内 壁 に 絶 縁 膜 を 形 成 し 、 前 記 ト レ ン チ の 内 部 に ゲ ー ト 電 極 を 形 成 し 、 前 記 第 2 導 電 型 ベ ー ス 層 及 び 前 記 第 1 導 電 型 ソ ー ス 層 の表面にソース電極を形成し、前記第 1 導電型基板の裏面から第 2 導電型不純物を打ち込 んで第2導電型ドレイン層を形成するとともに、前記第1導電型基板の前記第2導電型ド レイン層側における表面近傍の不純物濃度を相対的に下げ、前記第2導電型ドレイン層の 表面にドレイン電極を形成するものとして構成される。

# [0022]

# 【発明の実施の形態】

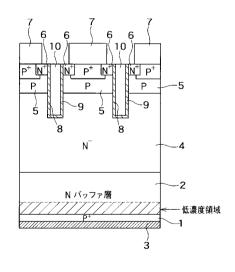

以下、図面を参照しながら、本発明の実施の形態について説明する。 図1は、本発明の実施の形態としての縦型IGBTを示す縦断面図である。

この縦型IGBTは、薄いp^ドレイン層1を備え、製造プロセス中にこの薄いp^ドレ イン 層 1 に 欠 損 が 生 じ 、 薄 い p <sup>†</sup> ド レ イ ン 層 1 の 欠 損 部 分 を 貫 通 し て n 型 バ ッ フ ァ 層 2 と ドレイン電極 3 とが接触しても、オーミック接触を形成しない程度に、n型バッファ層 2 のドレイン電極 3 側における表面近傍の不純物濃度が低くされていることを大きな特徴の 一つとして有する。

### [0024]

以下、この縦型IGBTについて詳しく述べる。 まず、この縦型IGBTの構造について説明する。

20

30

40

# [ 0 0 2 5 ]

図1に示すように、不純物の注入量の少ない薄いp \* 型ドレイン層1が形成されている。このp \* 型ドレイン層1上にはn型バッファ層2が形成されており、このn型バッファ層2が形成されており、このn型バッフェ層5 が形成されている。このn゚型にはn型ボッファ層5 が形成されている。このn゚型は、ソース層5 の表面の一部は、ソース層5 の表面領域には、上述のp \* 型高濃度領域と□・型ソース領域6 の表面に接でn゚型ソース領域6 が形成されている。これらp \* 型高濃度領域とn \* 型ソース領域6 の表面に接してる。これらp \* 型高濃度領域とn \* 型ソース領域6 の表面に接近て高抵流空のよるではが形成されている。このトレンチ8の内部にはゲートを経済2 に達するトレンチ8が形成されている。このトレンチ8の内部にはゲート電極10が形成されており、このゲート絶縁膜9を介してトレンチ8の内部にはゲート電極10が形成されている。一方、p \* ドレイン電極3 の材料にはアルミニウム(A1)が用いられている。(Ag)、金(トレイン電極3 の材料として、その他の金属、例えばクロム(Cr)、銀(Ag)、金(Au)等を用いてもよい。

# [0026]

次に、この縦型IGBTの動作について説明する。

まず、ターンオンモードについて説明する。

ドレイン電極3を正、ソース電極7を負とする電圧を印加した状態で、ゲート電極10に、ある閾値以上の正の電圧を印加すると、トレンチ8周りのp型ベース層5に反転層(チャネル)が形成される。このチャネルを経由して、n 型 リース領域6から n 型 高抵抗層4に電子が注入される。この n 型 高抵抗層4に注入された電子により、n型バッファ層2の電位がp 型 ドレイン層1に対して低下し、p 型 ドレイン層1から n 型 高抵抗層4に正孔が注入される。このようにして n 型 高抵抗層4に正孔が注入される。このようにして n 型 高抵抗層4に正孔が注入される。 このようにして n 型 高抵抗層4に伝導度変調を起こさせる。即ち、n 型 高抵抗層4の抵抗は極めて小さくり、オン状態になる。このオン状態でp 型 ドレイン層1から注入された正孔は、p型ベース層5を通過して、ソース電極7からの電子と結合し、これにより電流が流れる。

# [0027]

次に、ターンオフモードについて説明する。

オン状態において、ゲート電極10の正の電圧を下げると、トレンチ8周りに形成されたチャネルが消滅し、n \* 型ソース領域6からn 型高抵抗層4への電子の注入が止まる。このため、n型バッファ層2の電位が上昇し、p \* 型ドレイン層1からn 型高抵抗層4に注入されていた正孔も減じる。このn 型高抵抗層4中に蓄積されたキャリア(電子、ホール)は、n 型高抵抗層4の中で対となって消滅する。あるいは、n 型高抵抗層4中の電子はp \* 型ドレイン層1からドレイン電極3へ流出し、n 型高抵抗層4中の正孔はベース層5を通過してソース電極7からの電子と結合消滅する。n 型高抵抗層4の中の蓄積キャリアが全て消滅すると、n 型高抵抗層4の抵抗は極めて高くなり、オフ状態となる。

# [0028]

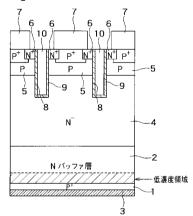

図 2 は、上述の縦型 I G B T を構成する各層における厚さと、各層における不純物濃度との関係を示すグラフである。

#### [0029]

以下、図 2 を参照しながら、 n 型バッファ層 2 及び p <sup>+</sup> 型ドレイン層 1 の不純物濃度及び層厚について説明する。

まず、n型バッファ層2の不純物濃度について説明する。

図 2 中の斜線で示すように、 n 型バッファ層 2 のドレイン電極 3 側における表面近傍の不純物濃度は例えば 1 .  $0 \times 1$  0 1 5 c m 3 以下となっている。この不純物濃度は、後に

10

20

30

40

詳述するように、 n 型バッファ層 2 とドレイン電極 3 (図 1 参照)とが接触してもオーミック接触を形成しない程度に十分に低いものである。別の言い方をすれば、この不純物濃度は、製造工程中にアルミスパイク等により p ・型ドレイン層 1 に欠損部が生じた場合に、ドレイン電極 3 と n 型バッファ層 2 とが接触してもアノードショート状態とならない程度に十分に低い値である。このように n 型バッファ層 2 のドレイン電極 3 側の不純物濃度を低くすることによって、 n 型バッファ層 2 とドレイン電極 3 とがオーミック接触を形成することを防いだ理由について簡単に述べれば以下の通りである。

[0030]

一般に、接触抵抗は、例えば、シリコンと接触する金属の種類、シリコンにドープされた不純物の型(p型、n型)、シリコンの表面の状態など、種々の条件によって変わってくる。この内、接触抵抗を変えるのに特に有効な手段は、半導体表面(シリコンの表面)の不純物濃度を変えてシリコンの表面の状態を変える方法であると本発明者は把握した。このような認識に基づき、本発明者は、上述のようにn型バッファ層2のp <sup>+</sup> ドレイン層1側における不純物濃度を十分に低いものとしたのである。

[0031]

次に、n型バッファ層2の層厚について説明する。

n型バッファ層 2 の低不純物濃度領域部の厚さは、製造工程中にアルミスパイクの入る深さを考慮して、 0 . 5 μ m 以上が望ましく、より好ましくは図 2 に示すように、 1 . 0 μ m 以上である。また、この n 型バッファ層 2 の全体の厚さは、図 2 に示すように、例えば 1 5 . 0 μ m であるが、この厚さに限定されるものではない。

[0032]

ここで、 n 型バッファ層 2 の低不純物濃度領域に用いて好適な不純物濃度を、ドレイン電極 3 として用いる金属材料別に説明する。

[ 0 0 3 3 ]

図 3 は、不純物半導体と、クロム(Cr)・銀(Ag)・金(Au)及びアルミニウム(A1)との接触抵抗を示す表である。

[0034]

[ 0 0 3 5 ]

次に、図3に示すように、金属としてCr、AgあるいはAuをn型不純物半導体に用いた場合は、不純物濃度7.0×10<sup>17</sup>cm<sup>23</sup>以下で非オーミックとなる。従って、n型バッファ層2の低不純物濃度領域の不純物濃度は、接触性が悪くなる1.0×10<sup>18</sup>cm<sup>3</sup>以下が好ましく、非オーミックとなる7.0×10<sup>17</sup>cm<sup>3</sup>以下が最適である。

[0036]

一方、図 3 に示すように、導電型が p 型の不純物半導体においては、金属として C r 、 A g あるいは A u を用いた場合、不純物濃度  $1.5 \times 10^{1.6}$  c m  $^{-3}$  以下で非オーミックとなる。従って、バッファ層(n 型バッファ層 2 参照)として p 型の不純物半導体層を用いた場合は、このバッファ層の低不純物濃度領域の不純物濃度は、接触性が悪くなる  $9.0 \times 10^{1.6}$  c m  $^{-3}$  以下が好ましく、非オーミックとなる  $1.5 \times 10^{1.6}$  c m  $^{-3}$  以下が最適であるといえる。

[0037]

次に、p<sup>†</sup>型ドレイン層1の不純物濃度について説明する。

20

30

40

40

50

$p^+$  型ドレイン層 1 (図 1 参照)の不純物濃度は、 $n^-$  型の高抵抗層 4 へのホールの注入効率を抑えるため、望ましくは  $1 \times 1$   $0^{19}$  c  $m^{-3}$  以下、より好ましくは  $5 \times 1$   $0^{18}$  c  $m^{-3}$  以下である。従って、図 2 に示す  $p^+$  型ドレイン層 1 の不純物濃度  $2 \times 1$   $0^{18}$  c  $m^{-3}$  は好ましい値であるといる。また、 $p^+$  型ドレイン層 1 の不純物総量も、 $n^-$  型の高抵抗層 4 へのホールの注入効率を抑えるため、 $5 \times 1$   $0^{14}$  c  $m^{-2}$  以下と少なくすることが望ましい。

#### [0038]

このように p <sup>+</sup> 型ドレイン層 1 の不純物濃度を低く及び不純物総量を少なくすることにより、 n 型の高抵抗層 4 へのホールの注入効率を抑えて、スイッチング速度を高速化することができる。即ち、 n 型高抵抗層 4 のライフタイムを短くすることなくスイッチング速度を高速化できる。

#### [0039]

また、このように n 型高抵抗層 4 のライフタイムを短くする必要がないので、 n 型高抵抗層 4 において高いキャリア濃度を得ることができる。即ち、低オン電圧を得ることができる。例えば、電圧降下を例えば 1 . 2 V以下と、従来の縦型 I G B T よりも 0 . 5 V 程度低くした好適なオン電圧特性を得ることができる。

# [0040]

次に、p<sup>†</sup>型ドレイン層1の層厚について説明する。

図 2 に示すように、  $p^+$  型ドレイン層 1 の層厚は、上に述べた理由で不純物総量を少なくするべく、例えば 0 . 3  $\mu$  m と薄くされている。このように  $p^+$  型ドレイン層 1 の層厚が薄くても本実施の形態によれば従来技術のところで述べたアノードショート状態を生じさせない。

# [0041]

即ち、上にも述べたように、 p <sup>+</sup> 型ドレイン層 1 は薄く形成されているため、製造プロセス中に p <sup>+</sup> 型ドレイン層 1 に欠損が生じる場合がある。具体的には、例えば空気中のダストが p <sup>+</sup> 型ドレイン層 1 に付着したことが原因となって物理的に欠損の生じる場合や、製造工程中に生成されたアルミスパイクによって p <sup>+</sup> 型ドレイン層 1 に欠損が生じると、この欠損部分を貫通して、ドレイン電極 3 と n 型バッファ層 2 とが接触することが避けられない。しかし、 n 型バッファ層 2 の p <sup>+</sup> 型ドレイン層 1 側の不純物濃度は、上述したように、 n 型バッファ層 2 とドレイン電極 3 とが接触してもオーミック接触を形成しない程度に低くしてある。よって、 p <sup>+</sup> 型ドレイン層 1 が欠損してドレイン電極 3 と n 型バッファ層 2 とが接触しても、アノードショート状態にはならず、素子の不良の発生を阻止することができる。

# [ 0 0 4 2 ]

以上のようなアノード状態の発生を阻止した構造を有する縦型 I G B T において、 n 型バッファ層 2 の厚さ方向における不純物濃度分布を変えることによって、スイッチング速度を高速化したリオン電圧の低減化したりする等、目的によった素子特性を実現することができる。

# [0043]

例えば、縦型 I G B T D 特性として特にスイッチング速度の高速化が要求される場合は、図 2 に示すように、例えば n 型バッファ層 2 のほぼ中心部の不純物濃度を、例えば 5  $\times$  1 0  $^{1}$   $^{6}$  c m  $^{-3}$  以上とするのがよい。この不純物濃度は、n 型バッファ層 2 が十分な厚みを有することから、耐圧維持の観点からも十分な値である。

#### [0044]

また、この縦型 I G B T の特性として特にオン電圧の低減化が要求される場合は、例えば n 型バッファ層 2 のほぼ中心部の不純物濃度を、例えば 5 × 1 0 <sup>1 6</sup> c m <sup>- 3</sup> 以下とするのがよい。

# [ 0 0 4 5 ]

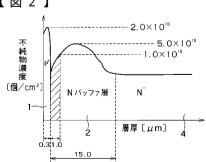

以上、本発明をトレンチ型の縦型IGBTに適用した例について説明したが、本発明は、

30

50

例えば、図4に示すプレーナ型の縦型IGBTについても当然に適用することができる。 このプレーナ型の縦型IGBTの構造について簡単に説明しておく。

#### [0046]

即ち、薄いp<sup>+</sup> 型ドレイン層 2 1 上にn型バッファ層 2 2 が形成されており、このn型バッファ層 2 2 上にはn 型エピタキシャル層(高抵抗層) 2 4 が形成されており、このp型ベース層 2 5 が形成されており、このp型ベース層 2 5 が形成されており、このp型ベース層 2 5 が形成されており、このp型ベース層 2 5 が形成されている。これらp<sup>+</sup> 型ソース領域 2 6 が形成されている。これらp<sup>+</sup> 型ソース領域 2 6 の表面に接してソース電極 2 7 が形成されている。p<sup>+</sup> 型ソース領域 2 6 及びn 型エピタキシャル層(高抵抗層) 2 4 上には1 の下を記録してゲート電極 1 0 が形成されている。一方、p<sup>+</sup> ドレイン層 2 1 が形成されている。では、 n 型バック層 2 2 のドレイン電極 2 3 側における表面近傍の不純物濃度とされている。即ちて、 n 型バッファ解型 1 G B T についての説明から分かるように低い不純物濃度とされている。即ちても、 市型ドレイン層 2 1 が欠損してドレイン電極 2 3 と n 型バッファ層 2 2 が接触ける表面近傍の濃度を低くしてある。これにより、プレーナ型の縦型 I G B T においても、 前述したトレンチ型の縦型 I G B T と同様に、 薄いり プレーナ型の縦型 I G B T と同様に、 薄いり プレーナ型の縦型 I G B T と同様に、 薄いり が 数 型 I G B T と同様に、 薄いり が 数 型 I G B T と同様に、 薄いり が 数 型 I G B T と同様に、 薄いり が 数 型 I G B T と同様に、 薄いり が 数 型 I G B T と同様に、 薄いり が 数 型 I G B T と同様に、 薄いり が 数 型 I G B T と同様に、 薄いりかできる。

#### [0047]

次に、図1に示す縦型IGBTの製造方法を説明する。より詳しくは、この縦型IGBTの製造方法を、通常のウエハ(Rawウエハ)、つまりエピタキシャルウエハでないウエハを用いて製造する方法と、エピタキシャルウエハを用いて製造する方法とに分けて、それぞれ説明する。

# [0048]

まず、通常のウエハを用いてIGBTを製造する方法について説明する。

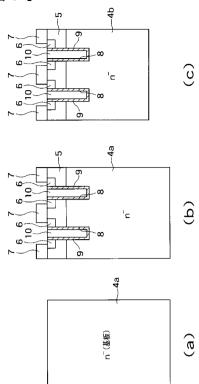

図 5 ( a ) ~ ( c ) 及び図 6 ( a ) ~ ( c ) は、通常のウエハを用いて縦型 I G B T を製造する工程を示す製造工程断面図である。

#### [0049]

以下、通常のウエハを用いて縦型IGBTを製造する工程について説明する。

まず、図 5 ( a )に示すように、 n ~型のウエハ( n ~型基板) 4 a を用意する。

### [0050]

#### [ 0 0 5 1 ]

次に、図 5 ( c )に示すように、 n 型ウエハ 4 a の裏面を化学機械研磨等を用いて研磨し、所定の厚さまで薄くして n 型ウエハ ( n 型ドリフト層) 4 b とする。具体的には、耐圧 6 0 0 V の I G B T の場合、 n 型ドリフト層の厚さはおよそ 6 0 ~ 8 0 μ m が適しているので、 n 型ドリフト層の厚さが 6 0 ~ 8 0 μ m となるように n 型ウエハ 4 a の裏面を研磨して薄くする。なお、 n 型ドリフト層の厚さが 6 0 ~ 8 0 μ m である I G

20

30

40

50

BTの総厚は、従来のIGBTに比べて、十分に薄い。

# [0052]

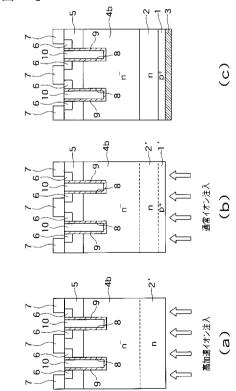

次に、図6(a)に示すように、ウエハ4bの裏面からリン(不純物)を例えば1MeVで高加速イオン注入し、素子の裏面から十分に内側にまで不純物を打ち込む。これにより不純物濃度のピークが素子の裏面から十分奥に形成されたn型バッファ層2,が形成される(図2参照)。即ち、中程度の加速エネルギー240keVで不純物を打ち込むと不純物濃度のピークは素子の裏面から0.3μm内側の浅い部分に形成されるのに対し、上述のような1MeVの高加速エネルギーで不純物を打ち込むと、素子の裏面から1.0~1.1μm内側の深い部分に不純物のピークが形成される。これにより、図2に示すように、ドレイン層側の不純物濃度を低くしたn型バッファ層を形成することができる。

[0053]

次に、図 6 ( b )に示すように、 n 型バッファ層 2 'の裏面からボロンを通常の速度でイオン注入して、 p <sup>+</sup> 型ドレイン層 1 'を形成する。

[0054]

次に、レーザーアニール、フラッシュアニール、シンター、熱拡散等の熱処理を行って、図 6 (b)に示す n 型バッファ層 2 ′及び p <sup>+</sup> 型ドレイン層 1 ′をそれぞれ図 6 (c)に示すように n バッファ層 2 及び p <sup>+</sup> 型ドレイン層 1 とする。この後、 p <sup>+</sup> ドレイン層 1 の表面にドレイン電極 3 を形成して縦型 I G B T のアノード側を完成させる。

[0055]

上述した縦型IGBTの製造工程では図6(b)に示すn型バッファ層2,とp <sup>+</sup> 型ドレイン層1,の熱処理工程を同時に行ったが、n型バッファ層2,とp <sup>+</sup> 型ドレイン層1,の熱処理工程をそれぞれ別個に行っても良い。即ち、まず、図6(a)に示すようにリンをn゚型ウエハ4bに高加速イオン注入した後に1度目の熱処理工程をし、次に、図6(b)に示すように、ボロンをn型バッファ層2,にイオン注入した後に2度目の熱処理工程を行うようにしてもよい。これによれば、n型バッファ層2,は2回の熱処理工程を経ることとなるので、n型バッファ層2,に打ち込まれたリンは十分に拡散されることとなる。

[0056]

また、上述した縦型IGBTの製造工程では、n型バッファ層2及びp<sup>→</sup> 型ドレイン層1の形成(図6(c)参照)前にソース電極7を形成(図5(b)参照)したが、n型バッファ層2及びp<sup>→</sup> 型ドレイン層1の形成後にソース電極7を形成してもよい。

[0057]

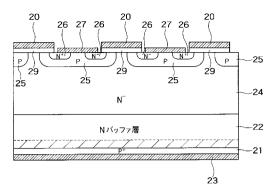

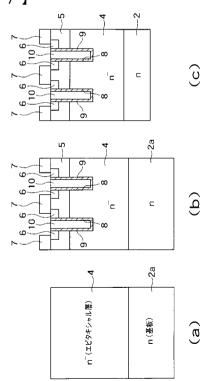

次に、エピタキシャルウエハを用いて縦型IGBTを製造する方法について説明する。図7(a)~(c)及び図8(a)~(c)は、エピタキシャルウエハを用いて縦型IGBTを製造する工程を示す製造工程断面図である。

[0058]

以下、エピタキシャルウエハを用いて縦型 I G B T を製造する工程について説明する。まず、図 7 (a)に示すように、 n 型ウエハ(n 型基板) 2 a を用意する。この n 型ウエハ 2 a の一部が最終的に n 型バッファ層となる。この n 型ウエハ 2 a に、エピタキシャル成長により、 n 型高抵抗層(n 型エピタキシャル層) 4 を形成する。この n 型高抵抗層 4 の一部が、最終的に n 型ドリフト層となる。

[0059]

次に、図7(b)に示すように、n`型高抵抗層4の表面にカソード領域を形成する。即ち、p型ベース層5、n`型ソース層6、ゲート絶縁膜9、ゲート電極10、ソース電極7を、上述した方法(図5(b)参照)等を用いて形成する。

[0060]

[0061]

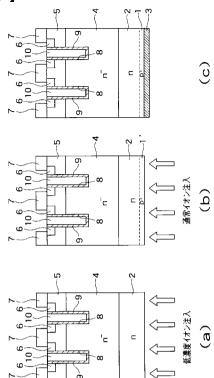

次に、図8(a)に示すように、 n 型バッファ層 2 の裏面から p 型不純物を非常に低不純物総量でイオン注入し、 n 型バッファ層 2 の裏面に近い部分の n 型不純物濃度を実質的に下げる。

[0062]

次に、図8(b)に示すように、通常の条件でボロンをイオン注入することにより、p<sup>→</sup>型ドレイン層1<sup>→</sup>を形成すると同時に、n型バッファ層2のp<sup>→</sup>型ドレイン層3<sup>→</sup>側における表面近傍の不純物濃度を低くする(図2参照)。

[0063]

次に、レーザーアニール、フラッシュアニール、シンター、熱拡散等の熱処理を行って、図8(b)に示すp<sup>†</sup>型ドレイン層1<sup>'</sup>を、図8(c)に示すようにp<sup>†</sup>型ドレイン層1 とする。この後、図8(c)に示すように、p<sup>†</sup>型ドレイン層1の裏面にドレイン電極3 を形成してこの縦型IGBTのアノード側を完成させる。なお、上述した通常のウエハを用いた縦型IGBTの製造方法と同様、n型バッファ層2及びp<sup>†</sup>型ドレイン層1を形成した後にソース電極7を形成してもよい。

[0064]

以上、本発明の実施の形態について説明したが、本発明の適用の範囲は上述した内容に限定されることはなく、本発明の要旨を変えない範囲において、種々の変形を加えて実施できる。

[0065]

【発明の効果】

本発明によれば、第1導電型バッファ層の第2導電型ドレイン層側における表面近傍の不純物濃度を低くしたので、この第2導電型ドレイン層に欠損が生じてドレイン電極と第1導電型のバッファ層とが接触してもアノードショート状態とならない。従って、好適なスイッチング特性及びターンオフ特性を有する半導体素子を、アノードショート状態の発生を阻止しつつ実現できる。

【図面の簡単な説明】

- 【図1】本発明の実施の形態としての縦型IGBT(トレンチ型)の縦断面図を示す。

- 【図2】図1の縦型IGBTを構成する各層の層厚と各層における不純物濃度との関係を示すグラフである。

- 【図3】不純物半導体に対するA1とCr・Ag・Auの接触抵抗を示す表である。

- 【図4】本発明の実施の形態としての縦型IGBT(プレーナ型)の縦断面図を示す。

- 【図5】通常のウエハを用いて縦型IGBT(トレンチ型)を製造する工程の途中までを示す製造工程断面図である。

- 【図 6 】図 5 に続いて、縦型IGBT(トレンチ型)を製造する工程を示す製造工程断面図である。

- 【図7】エピタキシャルウエハを用いて縦型IGBT(トレンチ型)を製造する工程の途中までを示す製造工程断面図である。

- 【図8】図7に続いて、縦型IGBT(トレンチ型)を製造する工程を示す製造工程断面図である。

- 【図9】従来の縦型IGBT(トレンチ型)の縦断面図を示す。

- 【図10】従来の別の縦型IGBT(トレンチ型)の縦断面図を示す。

【符号の説明】

- 1 p <sup>+</sup> 型ドレイン層 (第2導電型ドレイン層)

- 2 n型バッファ層(第1導電型バッファ層)

- 2 a n型基板

- 3 ドレイン電極

- 4 n 型 エ ピ タ キ シ ャ ル 層 ( 第 1 導 電 型 高 抵 抗 層 )

- 4 a n 型基板

- 4 b n 型基板 (n 型ドリフト層)

30

20

40

- (14)

- 5 p 型 ベ ー ス 層 ( 第 2 導 電 型 ベ ー ス 層 )

- 6 n <sup>†</sup> 型ソース層(第1導電型ソース層)

- 7 ソース電極

- トレンチ

- ゲート絶縁膜(絶縁膜)

- 1 0 ゲート電極

# 【図1】

# 【図2】

# 【図3】

|     | 不純物半導体(                  | こ対するCr・A             | 不純物半導体に対するCr・Ag・AuとAlの接触抵抗 | 触抵抗                  |

|-----|--------------------------|----------------------|----------------------------|----------------------|

| 導行型 | 不純物半導体<br>の比柢抗<br>(〇・cm) | 不純物濃度<br>[個/cm³]     | Al<br>[Ω·cm²]              | Cr·Ag·Au<br>[Ω·cm²]  |

|     | 0.001                    | 1.5×10 <sup>20</sup> | 1.2×10 <sup>-6</sup>       | 1.2×10 <sup>-6</sup> |

|     | 0.002                    | $6.0 \times 10^{19}$ |                            | $4.0 \times 10^{-6}$ |

| 5   | 0.01                     | 1.0×10 <sup>19</sup> | 2.3×10 <sup>-5</sup>       | 3.0×10 <sup>-5</sup> |

| a . | 0.1                      | $6.0 \times 10^{17}$ | 1.1×10 <sup>-4</sup>       | 1.5×10 <sup>-4</sup> |

|     | 0.3                      | 9.0×10 <sup>16</sup> |                            | $4.8 \times 10^{-4}$ |

|     | 1.0                      | 1.5×10 <sup>16</sup> | $1.0 \times 10^{-3}$       | 非オーミック               |

|     | 0.001                    | $1.0 \times 10^{20}$ | 1.9×10 <sup>-6</sup>       | 1.2×10 <sup>-6</sup> |

|     | 0.007                    | 1.0×10 <sup>19</sup> |                            | 8.0×10 <sup>-5</sup> |

| _   | 0.01                     | 5.0×10 <sup>18</sup> | 非オーミック                     | 2.1×10 <sup>-4</sup> |

|     | 0.03                     | 7.0×10 <sup>17</sup> | 非オーミック                     | 非オーミック               |

| 抵抗   |

|------|

| 接触   |

| A B  |

| AukA |

| 18.  |

| ₹Cr. |

| 43   |

| 衣出   |

| 導体   |

| 3巻半  |

【図4】

【図5】

【図6】

【図7】

-32

-31

N バッファ層

P<sup>+</sup>

# フロントページの続き

(72) 発明者 末 代 知 子

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝マイクロエレクトロニクスセンター内