(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第4622905号 (P4622905)

最終頁に続く

(45) 発行日 平成23年2月2日(2011.2.2)

(24) 登録日 平成22年11月12日(2010.11.12)

| (51) Int.Cl.                         | FΙ                                          |                     |           |          |           |

|--------------------------------------|---------------------------------------------|---------------------|-----------|----------|-----------|

| HO1L 21/336 (                        | <b>(2006.01)</b> HO1L                       | 29/78 €             | 858F      |          |           |

| HO1L 29/78 (                         | <b>(2006.01)</b> HO1L                       | 29/78 €             | 552K      |          |           |

|                                      | HO1L                                        | 29/78 €             | 552H      |          |           |

|                                      | HO1L                                        | 29/78 €             | 853A      |          |           |

|                                      | HO1L                                        | 29/78 €             | 858G      |          |           |

|                                      |                                             |                     | 請求項の数 6   | (全 12 頁) | 最終頁に続く    |

| (21) 出願番号 特願2006-83611 (P2006-83611) |                                             | (73) 特許権者 000003207 |           |          |           |

| (22) 出願日 平成                          | 18年3月24日 (2006.3.24)                        |                     | トヨタ自動車構   | 式会社      |           |

| (65) 公開番号 特開                         | \$\frac{1}{2007} - 258582 (P2007 - 258582A) |                     | 愛知県豊田市ト   | ヨタ町1番地   |           |

| (43) 公開日 平成                          | 対9年10月4日 (2007.10.4)                        | (74) 代理人            | 110000291 |          |           |

| 審査請求日 平成                             | 20年5月21日 (2008.5.21)                        |                     | 特許業務法人コ   | スモス特許事   | <b>務所</b> |

|                                      |                                             | (72) 発明者            | 宮城 恭輔     |          |           |

|                                      |                                             |                     | 愛知県豊田市ト   | ヨタ町1番地   | トヨタ自動     |

|                                      |                                             |                     | 車株式会社内    |          |           |

|                                      |                                             | (72)発明者             | 西脇 剛      |          |           |

|                                      |                                             |                     | 愛知県豊田市ト   | ヨタ町1番地   | トヨタ自動     |

|                                      |                                             |                     | 車株式会社内    |          |           |

|                                      |                                             | (72) 発明者            | 高谷 秀史     |          |           |

|                                      |                                             |                     | 愛知県豊田市ト   | ヨタ町1番地   | トヨタ自動     |

|                                      |                                             |                     | 車株式会社内    |          |           |

(54) 【発明の名称】絶縁ゲート型半導体装置の製造方法

# (57)【特許請求の範囲】

# 【請求項1】

トレンチゲート構造を有する絶縁ゲート型半導体装置の製造方法において、

半導体基板の上面からトレンチ部を形成するトレンチ部形成工程と、

前記トレンチ部内に,前記トレンチ部を閉塞しない膜厚の第1絶縁層を形成する第1絶縁層形成工程と,

前記第1絶縁層形成工程の後に,前記トレンチ部内に,前記トレンチ部を閉塞する膜厚の第2絶縁層を形成する第2絶縁層形成工程と,

前記第1絶縁層の一部および前記第2絶縁層の一部をウェットエッチングにより同時に除去するウェットエッチング工程と,

前記ウェットエッチング工程の後に,前記トレンチ部の壁面にゲート絶縁膜を形成する ゲート絶縁膜形成工程と,

前記ゲート絶縁膜形成工程の後に,前記トレンチ部内にゲート電極層を形成するゲート電極層形成工程と含み,

前記第2絶縁層は,前記第1絶縁層よりも前記ウェットエッチング工程でのウェットエッチング速度が速いことを特徴とする絶縁ゲート型半導体装置の製造方法。

### 【請求項2】

請求項1に記載する絶縁ゲート型半導体装置の製造方法において、

前記第1絶縁層形成工程の後であって前記第2絶縁層形成工程の前に,前記トレンチ部内に,前記トレンチ部を閉塞しない膜厚の中間絶縁層を形成する中間絶縁層形成工程を含

み,

前記中間絶縁層の前記ウェットエッチング工程でのウェットエッチング速度は,前記第 1 絶縁層よりも速く,前記第 2 絶縁層よりも遅いことを特徴とする絶縁ゲート型半導体装置の製造方法。

(2)

### 【請求項3】

請求項1または請求項2に記載する絶縁ゲート型半導体装置の製造方法において、

前記第2絶縁層は,リンを添加したシリコン酸化膜であることを特徴とする絶縁ゲート型半導体装置の製造方法。

#### 【請求項4】

請求項3に記載する絶縁ゲート型半導体装置の製造方法において、

前記第2絶縁層形成工程では,リンの供給源となるガスの流量を時間とともに増加させることを特徴とする絶縁ゲート型半導体装置の製造方法。

#### 【請求項5】

請求項1から請求項4のいずれか1つに記載する絶縁ゲート型半導体装置の製造方法において、

前記ウェットエッチング工程の前に,前記第 1 絶縁層の一部および前記第 2 絶縁層の一部をドライエッチングにより同時に除去するドライエッチング工程を含むことを特徴とする絶縁ゲート型半導体装置の製造方法。

#### 【請求項6】

請求項 1 から請求項 5 のいずれか 1 つに記載する絶縁ゲート型半導体装置の製造方法において、

前記第1絶縁膜形成工程の前に,前記トレンチ部の底部から不純物を注入する不純物注 入工程を含むことを特徴とする絶縁ゲート型半導体装置の製造方法。

【発明の詳細な説明】

### 【技術分野】

## [0001]

本発明は,トレンチゲート構造を有する絶縁ゲート型半導体装置の製造方法に関する。 さらに詳細には,ドリフト領域中にドリフト領域と異なる導電型の拡散層を設けることに よってドリフト層にかかる電界を緩和する絶縁ゲート型半導体装置の製造方法に関するも のである。

### 【背景技術】

# [0002]

従来から,パワーデバイス用の絶縁ゲート型半導体装置として,トレンチゲート構造を 有するトレンチゲート型半導体装置が提案されている。このトレンチゲート型半導体装置 では,一般的に高耐圧化と低オン抵抗化とがトレードオフの関係にある。

#### [0003]

この問題に着目したトレンチゲート型半導体装置として,本願出願人は図4に示すような絶縁ゲート型半導体装置を提案している(特許文献1)。この絶縁ゲート型半導体装置900は,N<sup>+</sup> ソース領域31と,N<sup>+</sup> ドレイン領域11と,P<sup>-</sup> ボディ領域41と,N<sup>-</sup> ドリフト領域12とが設けられている。また,半導体基板の上面側の一部を掘り込むことによりN<sup>+</sup> ソース領域31およびP<sup>-</sup> ボディ領域41を貫通するゲートトレンチ21が形成されている。また,ゲートトレンチ21の底部には,絶縁物の堆積による絶縁層23が形成されている。さらに,絶縁層23上には,ゲート電極22が形成されている。ゲート電極22は,ゲートトレンチ21の壁面に形成されているが一ト絶縁膜24を介して,N<sup>+</sup> ソース領域31およびP<sup>-</sup> ボディ領域41と対面している。さらに,N<sup>-</sup> ドリフト領域12内には,フローティング状態のP拡散領域51が形成されている。そして,ゲートレンチ21の下端は,P拡散領域51内に位置している。

### [0004]

絶縁ゲート型半導体装置900は,N<sup>-</sup>ドリフト領域12内にフローティング状態のP 拡散領域51が設けられている(以下,このような構造を「フローティング構造」とする 10

20

30

40

)ことにより,次のような特性を有する。

### [00005]

絶縁ゲート型半導体装置900では,ゲート電圧のオフ時に,N・ドリフト領域12とP・ボディ領域41との間のPN接合箇所から空乏層が広がる。そして,その空乏層がP拡散領域51にまで到達することで,P拡散領域51がパンチスルー状態となって電位が固定される。さらに,P拡散領域51とのPN接合箇所からも空乏層が広がるため,P・ボディ領域41との間のPN接合箇所とは別に,P拡散領域51とのPN接合箇所にも電界強度のピークが形成される。すなわち,電界強度のピークを2箇所に形成でき,最大ピーク値を低減することができる。従って,高耐圧化が図られる。また,高耐圧であることから,N・ドリフト領域12の不純物濃度を上げて低オン抵抗化を図ることができる。

[0006]

なお,特許文献1のように電界強度のピークを2箇所に形成して電界集中を緩和する構造とは異なるが,例えば特許文献2にゲート酸化膜よりも膜厚が厚い酸化膜をトレンチの底部に形成することにより,トレンチの底部の電界集中を緩和する技術が開示されている。また,フローティング構造とは異なるが,例えば特許文献3や特許文献4にゲート絶縁膜の下部の厚さを徐々に厚くすることでゲート絶縁膜の下部の電界集中を緩和する技術が開示されている。

【特許文献 1 】特開 2 0 0 5 - 1 4 2 2 4 3 号公報

【特許文献2】特開平10-98188号公報

【特許文献3】特開2002-299619号公報

【特許文献4】特開2005-19668号公報

【発明の開示】

【発明が解決しようとする課題】

[0007]

しかしながら,前記したトレンチゲート構造の絶縁ゲート型半導体装置には,次のような問題があった。すなわち,トレンチゲート構造の絶縁ゲート型半導体装置900では,ゲート電極22が深さ方向に対して急激に終端する形状になっている。そのため,ゲート電極22の底部近傍では,等電位線の間隔が狭く,局所的な電界集中が生じる。よって,2箇所の電界強度のピーク位置(図5の×1,×2)に合わせた耐圧設計を行ったとしても,ゲート電極22の底部近傍の部位(図5の×)が耐圧を決定してしまう。従って,設計耐圧が得られない。

[00008]

また,特許文献 2 にはゲートトレンチおよびゲート電極の底部に丸みを有する角部が開示されているが,具体的にゲートトレンチの底部の角部に丸みを設ける方法が開示されていない。そのため,実際には,絶縁ゲート型半導体装置900と同様に急激に終端する形状となるか,あるいは複雑な製造工程が必要となると考えられる。

[0009]

また,ゲートトレンチの全体形状をテーパ状にすることでゲート電極の急激な終端を回避することも考えられるが,P拡散領域 5 1 を形成する際のイオン注入で,トレンチの底部の他に側壁部にも不純物が打ち込まれてしまう。そのため,全体をテーパ状にすることは好ましくない。

[0010]

また,通常,ゲート電極下の絶縁層の中心部分は,両側壁部から堆積した絶縁膜が張り合わされてなる。そのため,ウェットエッチングを行うと,絶縁層の上面の中心部分にくさび状の溝が形成されることがある。この溝によってゲート電極の急激な終端を回避することも考えられる。しかし,溝の深さを制御することができないため,耐圧を制御することができない。

[0011]

また,特許文献3には,ゲート電極の底部が階段状となる半導体装置およびその製造方法が開示されている。この階段状の底部によってゲート電極の急激な終端を回避すること

10

20

30

40

も考えられる。しかし、特許文献3に開示されている製造方法では、熱酸化処理とエッチングとを何度も繰り返す必要がある。そのため、製造に手間がかかる。また、特許文献4には、ゲート電極の底部がゆるやかに終端する半導体装置が開示されている。しかし、このような形状となるための製造方法が開示されていない。特許文献3に開示されている階段状のゲート電極の製造方法を応用し、段数を多くすることで緩やかに終端するゲート電極を形成することも可能であるが、製造が益々複雑になる。

#### [0012]

本発明は,前記した従来のトレンチゲート構造の絶縁ゲート型半導体装置が有する問題点を解決するためになされたものである。すなわちその課題とするところは,ゲート電極の下端近傍の局所的な電界集中を回避した絶縁ゲート型半導体装置を高精度でかつ容易に作製することができる製造方法を提供することにある。

【課題を解決するための手段】

### [0013]

この課題の解決を目的としてなされた絶縁ゲート型半導体装置の製造方法は,トレンチゲート構造を有する絶縁ゲート型半導体装置の製造方法であって,半導体基板の上面からトレンチ部を形成するトレンチ部形成工程と,トレンチ部内にそのトレンチ部を閉塞しない膜厚の第1絶縁層を形成する第1絶縁層形成工程と,第1絶縁層形成工程の後に,トレンチ部内にそのトレンチ部を閉塞する膜厚の第2絶縁層を形成する第2絶縁層形成工程と,第1絶縁層の一部および第2絶縁層の一部をウェットエッチングにより同時に除去するウェットエッチング工程と,ウェットエッチング工程の後に,トレンチ部内にゲート電極層を形成するゲート電極層形成工程と含み,第2絶縁層は,第1絶縁層よりもウェットエッチング工程でのウェットエッチング速度が速いことを特徴としている。

#### [0014]

すなわち、本発明の製造方法では、トレンチ部を形成した後に、そのトレンチ部内に少なくとも2種類の絶縁膜を形成する。このうち、トレンチ部の幅方向の中央側に位置する、すなわち後に形成される第2絶縁膜の方が、トレンチ部の幅方向の側壁側に位置する、すなわち先に形成される第1絶縁膜と比較して、後のウェットエッチング工程でのウェットエッチング速度が速い。そのため、ウェットエッチング工程によるエッチバックにより、トレンチ部内に残る各絶縁膜の深さ方向の厚さは、第1絶縁膜が第2絶縁膜より厚い。また、ウェットエッチング速度差によって生じる段差部分は、積極的にエッチバックされる。つまり、エッチバック後にトレンチ部内に生じるスペースの底部は、ゆるやかに終端する突起状をなしている。

### [0015]

このスペース内にゲート電極層を形成する。これにより,ゲート電極層の底部が深さ方向に対してゆるやかに終端する形状となる。よって,本製造方法によって作製される絶縁 ゲート型半導体装置は,ゲート電極層の底部近傍での局所的な電界集中が緩和される。

### [0016]

また,本発明の製造方法では,1回のウェットエッチングにより深さ方向に対してゆるやかに終端する形状のゲート電極層を形成している。そのため,製造工程がシンプルである。

# [0017]

また,エッチバックの深さを絶縁膜の膜種によって制御することができる。よって,ゲート電極層の底部の形状を意図的にテーパ形状もしくはR形状とすることができる。すなわち,ゲート電極層の底部の形状を制御できる。

# [0018]

また,本発明の製造方法では,第1絶縁層形成工程の後であって第2絶縁層形成工程の前に,トレンチ部内にそのトレンチ部を閉塞しない中間絶縁層を形成する中間絶縁層形成工程を含み,中間絶縁層のウェットエッチング工程でのウェットエッチング速度は,第1絶縁層よりも速く,第2絶縁層よりも遅いこととするとよりよい。ゲート電極層下の絶縁

20

10

30

40

層の構成を3層以上とすることで,ゲート電極層の底部はより滑らかに終端する形状となる。また,絶縁層の膜数が増えたとしても1回のウェットエッチングによってゲート電極層の底部について所望の形状を得ることができる。よって,製造工程はシンプルである。

#### [0019]

具体的に,本発明の第 2 絶縁層形成工程では,第 2 絶縁層として例えばリンを添加したシリコン酸化膜を形成するとよい。一般的に,リンを添加したシリコン酸化膜は,無添加のシリコン酸化膜や熱酸化膜と比較してウェットエッチング速度が速い。そのため,第 1 絶縁層を無添加の酸化膜や熱酸化膜とすれば,リンを添加したシリコン酸化膜をウェットエッチング速度が速い第 2 絶縁膜として適用可能である。また,リンの添加量が多いほどウェットエッチング速度は速い。そこで,リンを添加したシリコン酸化膜にて第 2 絶縁層を形成する際,リンの供給源となるガスの流量を時間とともに増加させることとするとよい。すなわち,リン濃度を徐々に濃くすることでより滑らかに終端するゲート電極層を形成することができる。

# [0020]

また,本発明の製造方法では,ウェットエッチング工程の前に,第1絶縁層の一部および第2絶縁層の一部をドライエッチングにより同時に除去するドライエッチング工程を含むこととするとよりよい。すなわち,反応性イオンエッチング法等のドライエッチングにてボディ領域の下面近傍までエッチバックした後にウェットエッチングを行う。これにより,ゲート電極層全体をテーパ形状にすることなく,底部のみを突起状にすることができる。つまり,突起状とする範囲を限定することができ,より高精度にゲート電極層の底部の形状を制御できる。

#### [0021]

また,本発明の製造方法では,第 1 絶縁膜形成工程の前に,トレンチ部の底部から不純物を注入する不純物注入工程を含むことで,トレンチ部の底部周辺にフローティング状態の拡散層を形成することができる。すなわち,トレンチの底部周辺にフローティング状態の拡散層を形成することで,ゲート電圧のオフ時に電界強度のピーク値を 2 箇所に形成する。これにより,フローティング構造の絶縁ゲート型半導体装置を形成することができる

### 【発明の効果】

# [0022]

本発明によれば、1回のウェットエッチングにより、ゲート電極層の底部の形状を意図的にテーパ形状もしくはR形状とすることができる。また、その形状を各絶縁膜の膜種や不純物濃度によって高精度に制御することができる。よって、ゲート電極の下端近傍の局所的な電界集中を回避した絶縁ゲート型半導体装置を高精度でかつ容易に作製することができる製造方法が実現されている。

【発明を実施するための最良の形態】

# [0023]

以下,本発明を具体化した実施の形態について,添付図面を参照しつつ詳細に説明する。なお,本実施の形態は,絶縁ゲートへの電圧印加により,ドレイン・ソース間の導通をコントロールするパワーMOSに本発明を適用したものである。

# [0024]

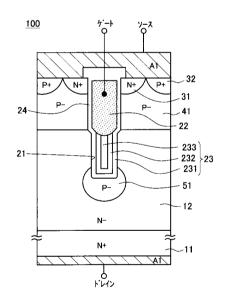

実施の形態に係る絶縁ゲート型半導体装置100(以下,「半導体装置100」とする)は,図1の断面図に示す構造を有している。なお,本明細書においては,出発基板と,出発基板上にエピタキシャル成長により形成した単結晶シリコンの部分とを合わせた全体を半導体基板と呼ぶこととする。

# [0025]

半導体装置100では,半導体基板内における図1中の上面側に, $N^+$  ソース領域31が設けられている。一方,下面側には $N^+$  ドレイン領域11が設けられている。それらの間には上面側から順に, $P^-$  ボディ領域41および $N^-$  ドリフト領域12が設けられている。また,半導体基板の上面側の一部を掘り込むことによりゲートトレンチ21が形成さ

10

20

30

40

20

30

40

50

れている。ゲートトレンチ 2 1 は ,  $N^+$  ソース領域 3 1 および  $P^-$  ボディ領域 4 1 を貫通している。

# [0026]

ゲートトレンチ21の底部には、絶縁物の堆積による絶縁層23が形成されている。具体的に、本形態の絶縁層23は、3層構造をなしており、ゲートトレンチ21の側壁側から熱酸化膜231、ノンドープシリコン酸化膜232(以下、「NSG膜232」とする)、リンドープシリコン酸化膜233(以下、「PSG膜233」とする)が順に積層されている。また、絶縁層23の上面は、PSG膜233を底部とする凹面となっている。さらに、絶縁層23上には、ゲート電極22が形成されている。ゲート電極22の下端は、P、ボディ領域41の下面より下方に位置している。また、ゲート電極22の下面は、絶縁層23の上面の形状に合わせて凸面をなしている。すなわち、ゲート電極22は深さ方向に対して徐々に幅が狭くなる、つまりゆるやかに終端する形状になっている。そのため、ゲート電極22の底部近傍での局所的な電界集中が緩和されている。

#### [0027]

また,ゲート電極 2 2 は,ゲートトレンチ 2 1 の壁面に形成されているゲート絶縁膜 2 4 を介して,半導体基板のN<sup>+</sup> ソース領域 3 1 および P ボディ領域 4 1 と対面している。すなわち,ゲート電極 2 2 は,ゲート絶縁膜 2 4 によりN<sup>+</sup> ソース領域 3 1 および P ボディ領域 4 1 から絶縁されている。

### [0028]

このような構造を持つ半導体装置 1 0 0 では,ゲート電極 2 2 への電圧印加により  $P^-$ ボディ領域 4 1 にチャネル効果を生じさせ,もって  $N^+$  ソース領域 3 1 と  $N^+$  ドレイン領域 1 1 との間の導通をコントロールしている。

# [0029]

さらに、半導体装置100には、ゲートトレンチ21の底部の周囲に、N ドリフト領域12に囲まれ、フローティング状態のP拡散領域51が形成されている。P拡散領域51はゲートトレンチ21の底面から不純物を注入することにより形成された領域である。半導体装置100の製造方法についての詳細は後述する。P拡散領域51の断面は、各トレンチの底部を中心とした略円形形状となっている。なお、フローティング構造にて高耐圧化を図るには、ゲート電圧のオフ時の電界強度のピークがP ボディ領域41とN ドリフト領域12のPN接合箇所と、P拡散領域51とN ドリフト領域12のPN接合箇所との2箇所(図5の×1,×2)に形成される位置に埋め込み領域であるP拡散領域51を配置する。さらに好ましくは、両ピーク値が同等となるように配置する。

#### [0030]

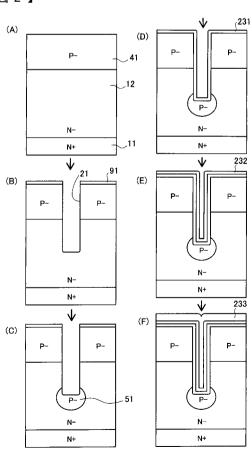

続いて,半導体装置100の製造プロセスについて,図2ないし図3を基に説明する。まず,あらかじめ, $N^+$  ドレイン領域11となる $N^+$  基板上に, $N^-$  型シリコン層をエピタキシャル成長により形成しておく。この $N^-$  型シリコン層(エピタキシャル層)は, $N^+$  ドリフト領域12, $P^-$  ボディ領域41, $N^+$  ソース領域31,コンタクト $P^+$  領域32の各領域となる部分である。なお, $P^-$  ボディ領域41および $N^-$  ドリフト領域12を合わせた領域(以下,「エピタキシャル層」とする)の厚さは,80V耐圧でおよそ7.0  $\mu$  m(そのうち, $P^-$  ボディ領域41の厚さは,およそ1.2  $\mu$  m)である。なお,耐圧に応じて寸法が異なるのは言うまでもない。

#### **[** 0 0 3 1 ]

次に、半導体基板の上面側に、イオン注入等によって P がディ領域 4 1 を形成する。これにより、図 2 ( A )に示すように、基板上面に P がディ領域 4 1 を有する半導体基板が形成される。

# [0032]

次に,半導体基板上にパターンマスク91を形成し,トレンチドライエッチングを行う。このトレンチドライエッチングにより,図2(B)に示すように, $N^+$  ソース領域31 および $P^-$  ボディ領域41を貫通するゲートトレンチ21が形成される。なお,ゲートトレンチ21は,その深さが2.0 $\mu$  m~3.0 $\mu$  mであり,その幅が0.4 $\mu$  m~0.5

20

30

40

50

μmである。また,トレンチ側壁のテーパ角度は,85.0度~89.0度である。その後,適当な洗浄処理を行い,さらにケミカルドライエッチング法等の等方的エッチング手法を利用してゲートトレンチ21の壁面を平滑化する。

#### [0033]

次に,所望の厚さの熱酸化膜(犠牲酸化膜)を形成する。その後,イオン注入により各トレンチの底面から不純物を打ち込む。その後,熱拡散処理を行うことにより,図2(C)に示すように,P拡散領域51が形成される。なお,熱拡散処理は,後述の絶縁層23を形成する際に行ってもよい。その後,犠牲酸化膜およびパターンマスク91を除去し,清浄なシリコン表面を露出させる。

# [0034]

次に,3種の絶縁膜によってゲートトレンチ 2 1 内を充填する。まず,熱酸化処理により,図 2 ( D ) に示すように,清浄なシリコン表面に薄層の熱酸化膜 2 3 1 を形成する。 具体的に熱酸化膜 2 3 1 の成膜条件としては,例えば反応ガスを  $O_2$  ,  $O_2$  を含む混合ガスとし,酸化温度を 8 0 0 ~ 1 1 0 0 とし, 2 0 n m~ 1 0 0 n m の膜厚の熱酸化膜を形成する。

#### [0035]

次に,熱酸化膜 2 3 1 上に,熱酸化膜よりウェットエッチング速度が速い絶縁膜を成膜する。本形態では,図 2 (E)に示すように,C V D (Chemical Vapor Deposition)法によってゲートトレンチ 2 1 内に N S G 膜 2 3 2 を堆積する。 N S G 膜 2 3 2 としては,例えば S i H 4 を原料とし,成膜温度を 7 5 0 ~ 8 2 5 とした減圧 C V D によって形成された S i O 2 膜が該当する。またこの他, T E O S (Tetra-Ethyl-Orso-Silicate)を原料とし,成膜温度を 6 0 0 ~ 7 0 0 とした減圧 C V D 法によって形成される S i O 2 膜,あるいはオゾンと T E O S とを原料とした C V D 法によって形成される S i O 2 膜が該当する。

#### [0036]

ただし、絶縁層23は3層構造であり、次の工程で成膜するPSG膜をゲートトレンチ21内に形成するためのスペースを確保しなければならない。すなわち、NSG膜232でゲートトレンチ21内を充填してはならない。そのため、2層目に相当するNSG膜232は、ゲートトレンチ21の間口を閉塞しない膜厚とする必要がある。本形態では、NSG膜232の膜厚を50nm~150nmとする。

### [0037]

次に,NSG膜232上に,NSG膜よりウェットエッチング速度が速い絶縁膜を成膜し,ゲートトレンチ21内を完全に充填する。本形態では,図2(F)に示すように,CVD法によってゲートトレンチ21内にPSG膜233を堆積する。PSG膜233としては,例えばTEOSおよびTMP(Trimethyl Phosphite)を原料とし,成膜温度を600~700 とした減圧CVD法によって形成されるSiO2膜が該当する。またこの他,オゾン,TEOS,およびTMPを原料としたCVD法によって形成されるSiO2膜が該当する。

# [0038]

なお,PSG膜233の埋め込み性を向上させるため,PSG膜の代わりにボロンリンドープシリコン膜(以下,「BPSG膜」とする)を形成してもよい。ただし,ボロンを多く添加した酸化膜はNSG膜よりもウェットエッチング速度が遅くなる。そのため,ウェットエッチング速度がNSG膜232よりも速くなる範囲内にボロンの添加量を留める必要がある。

#### [0039]

また,PSG膜233は非常に狭いスペースに堆積する。そのため,埋め込み性が課題となる。そこで,PSG膜あるいはBPSG膜のリフロー性を利用し,熱処理を加えることとしてもよい。

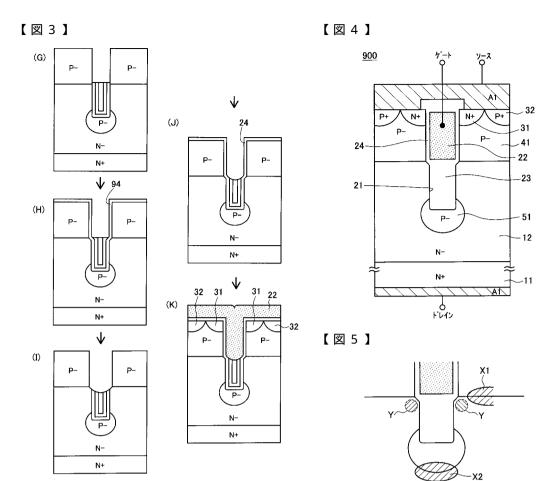

### [0040]

次に,ドライエッチングにより,図3(G)に示すように,熱酸化膜231,NSG膜

20

30

40

50

232, PSG膜233の一部を除去する。具体的には,ドライエッチングより,絶縁層23の上面がP<sup>-</sup> ボディ領域41の下面と同等の位置になるまで絶縁層23をエッチバックする。これにより,ゲート電極22を内蔵するためのスペースが確保される。ドライエッチングでは,酸化膜の疎密性やSi-O結合力の強弱に関わらず異方的にエッチングされる。そのため,PSG膜233の張り合わせ面に存在するボイドはエッチバックに影響しない。また,膜種間のエッチング速度差も極めて小さい。よって,絶縁層23は均等にエッチバックされ,その上面は平坦である。

### [0041]

次に,特開2005-340552号公報に開示されているように,酸化性雰囲気下でアニール処理を行うことにより,図3(H)に示すように,シリコンの露出面,特にゲートトレンチ21の側壁に酸化膜94を形成する。具体的に酸化膜94の成膜条件としては,例えば反応ガスをO2,H2O,あるいはO2を含む混合ガスとし,酸化温度を800~1100 とし,20nm~100nmの膜厚の犠牲酸化膜を形成する。この酸化アニール処理は,PSG膜233の張り合わせ面におけるシームの解消,シリコン原子の未結合子が酸素と反応することによる化学的結合力の強化等の役割を有する。

#### [0042]

次に,ウェットエッチングにより,ゲートトレンチ21の側壁の酸化膜94を除去し,図3(I)に示すように,清浄なシリコン面を露出させる。このとき,絶縁層23の各膜のウェットエッチング速度は,

(1層目:熱酸化膜) (2層目:NSG膜) (3層目:PSG膜) となっている。また,ウェットエッチング速度差によって生じる段差部分は積極的にエッチバックされる。そのため,エッチバックされた絶縁層23の上面は,PSG膜233に向かって徐々に深くなる凹形状となる。具体的にエッチバックの条件としては,薬液を希フッ酸あるいはバッファドフッ酸とし,熱酸化膜231に対して100nm~300nmの厚さ分のエッチバックを行う。なお,エッチバックの深さは,絶縁層23中のリン添加量によって制御することができる。そのため,絶縁層23の上面の形状を高精度に作製することができる。エッチバック後は,清浄なシリコン表面を得るために適当な洗浄処理を行う。

### [0043]

次に,図3(J)に示すように,熱酸化処理またはCVD法による成膜処理あるいはこれらの兼用により,ゲート絶縁膜24を形成する。具体的に熱酸化処理を行う場合には,例えば反応ガスを $O_2$ , $H_2O$ ,あるいは $O_2$ を含む混合ガスとし,酸化温度を800~1100 とした熱酸化処理によって形成される熱酸化膜が該当する。また,CVD法による酸化膜を形成する場合には,例えばSi $H_4$ を原料とし,成膜温度を750 ~825 とした減圧CVDによって形成されたSi $O_2$  膜が該当する。またこの他,TEOSを原料とし,成膜温度を600 ~700 とした減圧CVD法によって形成されるSi $O_2$  膜が該当する。本形態のゲート絶縁膜24の膜厚は,50nm~100nmの範囲内とする。

### [0044]

次に,図3(K)に示すように,エッチバックにて確保したスペースに対し,ゲート材 2 2 を堆積する。具体的にゲート材 2 2 の成膜条件としては,例えば反応ガスをSiH $_4$  を含む混合ガスとし,成膜温度を 5 8 0 ~ 6 4 0 とし,常圧CVD法によって 8 0 0 n m程度の膜厚のポリシリコン膜を形成する。ポリシリコン膜 2 2 の下面は,ゲートトレンチ 2 1 の幅方向の中央部に向かってゆるやかに深くなる形状をなしている。すなわち,ポリシリコン膜 2 2 は深さ方向に対してゆるやかに終端する形状になっている。そのため,ポリシリコン膜 2 2 (すなわちゲート電極 2 2)の底部近傍での局所的な電界集中が緩和される。

# [0045]

次に,ポリシリコン膜 2 2 に対してエッチングを行う。これにより,ゲート電極 2 2 が 形成される。その後,その  $P^-$  ボディ領域 4 1 が形成されている部分に,ボロンやリン等 のイオン注入およびその後の熱拡散処理により N<sup>+</sup> ソース領域 3 1 およびコンタクト P<sup>+</sup> 領域 3 2 を形成する。なお,ゲートトレンチ 2 1 の形成前に, N<sup>+</sup> ソース領域 3 1 およびコンタクト P<sup>+</sup> 領域 3 2 をあらかじめ形成しておいてもよい。さらに,半導体基板上に層間絶縁膜等を形成し,最後に,ソース電極,ドレイン電極を形成することにより,図 1 に示したトレンチゲート型の半導体装置 1 0 0 が作製される。

#### [0046]

なお,絶縁層23は,熱酸化膜231(1層目),NSG膜232(2層目),PSG膜233(3層目)の3層構造に限るものではない。すなわち,ゲートトレンチ21の幅方向の中央部に向かってウェットエッチング速度が速くなる構成であればよい。例えば,2層目を低濃度のPSG膜とし,3層目を高濃度のPSG膜としてもよい。

# [0047]

また,3層構造に限るものではない。すなわち,2層構造であってもよいし,4層以上の構造であってもよい。また,PSG膜あるいはBPSG膜を利用する場合,膜中のリン濃度をゆるやかに増加させるとよい。このようにすることで,より滑らかに終端する絶縁層の上面を形成することができる。なお,具体的には,PSG膜(BPSG膜)の成膜時にリンの供給源となるガスの流量を時間とともに増加させる。これにより,リン濃度に勾配を持たせることができる。

## [0048]

以上詳細に説明したように本形態の半導体装置100は,ゲート電極22の下に位置する絶縁層23を,ゲートトレンチ21の壁面側から順に,熱酸化膜231(1層目),NSG膜232(2層目),PSG膜233(3層目)の3層構造とすることとしている。すなわち,ゲートトレンチ21の幅方向の中央部に向かってウェットエッチング速度が速り他縁膜群を形成することとしている。そのため,ウェットエッチングによるエッチバックでは,ゲートトレンチ21の幅方向の中央部に向かうほどより多くの絶縁膜が除去される。よって,エッチバックによって生じるゲートトレンチ21内のスペースは,突起状をなすこととなる。このスペース内にゲート電極22を形成する。これにより,ゲート電極22の底部が深さ方向に対してゆるやかに終端する形状,すなわちゲート電極22の底部は深さ方向に向かってその幅が徐々に狭くなる形状となる。よって,半導体装置100は,ゲート電極22の底部近傍での局所的な電界集中が緩和される。

## [0049]

また,本発明の半導体装置100の製造方法では,ウェットエッチング速度が異なる3層構造の絶縁層23を形成した後,1回のウェットエッチングによりゲート電極22のためのスペースを確保している。すなわち,1回のウェットエッチングにより,深さ方向に対してゆるやかに終端する形状のゲート電極22を形成している。そのため,製造工程がシンプルである。

### [0050]

また,本発明の半導体装置100の製造方法では,ゲート電極22の底部の突起部分の大きさを絶縁層23の膜種あるいは濃度によって制御することができる。よって,ゲート電極22の底部の形状を意図的にテーパ形状もしくはR形状とすることができる。すなわち,ゲート電極層の底部の形状を容易に制御できる。従って,ゲート電極の下端近傍の局所的な電界集中を回避した絶縁ゲート型半導体装置を高精度でかつ容易に作製することができる製造方法が実現している。

### [0051]

なお,本実施の形態は単なる例示にすぎず,本発明を何ら限定するものではない。したがって本発明は当然に,その要旨を逸脱しない範囲内で種々の改良,変形が可能である。例えば,各半導体領域については,P型とN型とを入れ替えてもよい。また,半導体についても,シリコンに限らず,他の種類の半導体(SiC,GaN,GaAs等)であってもよい。また,実施の形態の絶縁ゲート型半導体装置は,IGBTに対しても適用可能である。

# 【図面の簡単な説明】

10

20

30

### [0052]

- 【図1】実施の形態にかかる絶縁ゲート型半導体装置の構造を示す断面図である。

- 【図2】実施の形態にかかる絶縁ゲート型半導体装置の製造工程を示す図(その1)である。

- 【図3】実施の形態にかかる絶縁ゲート型半導体装置の製造工程を示す図(その2)である。

- 【図4】従来の絶縁ゲート型半導体装置の構造を示す断面図である。

- 【図5】フローティング構造を有する絶縁ゲート型半導体装置の電界集中箇所を示す図である。

【符号の説明】 10

# [0053]

- 1 1 N<sup>+</sup> ドレイン領域

- 12 N<sup>-</sup>ドリフト領域

- 2 1 ゲートトレンチ (トレンチ部)

- 22 ゲート電極 (ゲート電極層)

- 2 3 絶縁層

- 231 熱酸化膜(第1絶縁膜)

- 2 3 2 N S G 膜 (中間絶縁膜)

- 2 3 3 P S G 膜 ( 第 2 絶 縁 膜 )

- 2 4 ゲート絶縁膜

- 3 1 N + ソース領域

- 32 コンタクト P + 領域

- 4.1 P<sup>-</sup> ボディ領域

- 5 1 P 拡散領域

- 100 絶縁ゲート型半導体装置

# 【図1】

# 【図2】

FΙ

# フロントページの続き

(51) Int.CI.

H 0 1 L 29/78 6 5 8 A

審査官 原 和秀

(56)参考文献 米国特許第6355974(US,B1)

特表2003-532293(JP,A)

特表2003-509836(JP,A)

特表2005-510087(JP,A)

(58)調査した分野(Int.CI., DB名)

H01L 21/336

H01L 29/78

H01L 21/8242

H01L 27/108