# (12) UK Patent Application (19) GB (11) 2 322 267 (13) A

(43) Date of Printing by UK Office 19.08.1998

- (21) Application No 9810283.3

- (22) Date of Filing 27.11.1996

- (30) Priority Data (31) **07309422**

- (32) 28.11.1995

- (33) JP

- (86) International Application Data PCT/JP96/03481 Jp 27.11.1996

- (87) International Publication Data WO97/20417 Jp 05.06.1997

- (71) Applicant(s)

Sanyo Electric Co Ltd (Incorporated in Japan) 5-5 Keihan-Hondori 2-chome, Moriguchi-shi, Osaka 570, Japan

(72) Inventor(s)

linuma Toshinori

- (51) INT CL<sup>6</sup> H04L 27/22

- (52) UK CL (Edition P )

H4P PAPD PJ

- (56) Documents Cited by ISA

JP 600093862 A JP 030274844 A

- (58) Field of Search by ISA INT CL<sup>6</sup> H04L 27/18 27/20 27/22 Jitsuyo Shinan Koho, Kokai Jitsuyo Shinan Koho

- (74) Agent and/or Address for Service

R G C Jenkins & Co

26 Caxton Street, LONDON, SW1H ORJ,

United Kingdom

# (54) Abstract Title Digital demodulator

(57) A digital demodulator which demodulates phase-modulated signals like the PSK (Phase Shift Keying) etc., do. An adder (46) adds a correction value held by a phase correcting section (45) to phase difference data outputted from a comparator (43). A subtractor (47) performs delay detection by subtracting phase difference data which are delayed by one symbol period by means of a delay circuit (44) from the phase difference data to which the correction value is added. Therefore, the demodulator can receive and demodulate signals even when their frequencies are not integral multiples of the master clock, and an oscillator having a frequency which is not an integral multiple of that of input signals to be demodulated can be used.

- a ... received signal

- b ... master clock

- c ... demodulated data

- 41 ... phase detecting section

- 42 ... frequency divides

- 43 ... comparator

- 44 ... delay circuit

- 45 ... phase correcting section

- 45 ... clock reproducing section

- 49 ... discriminating section

FIG. 6

FIG. 7

### CLAIMS

(An amendment to Claim 1 was filed with the letter of December 11, 1997)

What is claimed is:

- 1 1. (Amended) A digital demodulator comprising:

- 2 phase difference data output means for comparing a

- 3 phase-modulated input signal with a clock signal which is not in

- 4 synchronization with the carrier wave component of the input

- 5 signal, and outputting phase difference data which corresponds

- 6 to the phase difference between the input signal and the clock

- 7 signal;

- 8 delaying means for delaying the phase difference data

- 9 outputted from said phase difference data output means by a

- 10 predetermined period of time;

- 11 compensation value hold means for holding as a

- 12 compensation value a fixed value which corresponds to a phase

- 13 shift caused by the frequency difference between the carrier

- 14 wave component and the clock signal;

- delay detection means for detecting a delay of the phase

- 16 difference data outputted from said phase difference data output

- 17 means using the phase difference data outputted from said phase

- 18 difference data output means, the compensation value held by

- 19 said compensation value hold means, and the phase difference

- 20 data delayed by said delaying means by the predetermined period

- 21 of time; and

- demodulation means for demodulating the input signal

23 based on the result of the delay detection.

\_\_

•

# **SPECIFICATION**

### TITLE OF THE INVENTION

### DIGITAL DEMODULATOR

# FIELD OF THE INVENTION

The present invention relates to a digital demodulator for demodulating signals which have been phase-modulated by such methods as PSK (Phase Shift Keying).

# BACKGROUND OF THE INVENTION

15

In recent years, digital communication devices have transmitted information signals after modulating carrier signals using digital information signals (baseband signals) to achieve efficient transmission. Such modulation has been performed using methods such as ASK (Amplitude Shift Keying) in which amplitudes of carrier signals are shifted based on digital baseband signals (modulating signals), FSK (Frequency Shift Keying) in which frequencies of carrier waves are shifted based on modulating signals, and QAM (Quadrature Amplitude Modulation) in which amplitudes and phases of carrier waves are independently changed based on modulating signals.

These digital modulation methods are currently used in various mobile communication systems. Digital demodulators in practical use which demodulate information signals transmitted

in the above manner have a common feature (not identical, though) in that a baseband signal is detected from an input signal using a clock signal which has a frequency equal to an integral multiple of the frequency of the input signal.

5

15

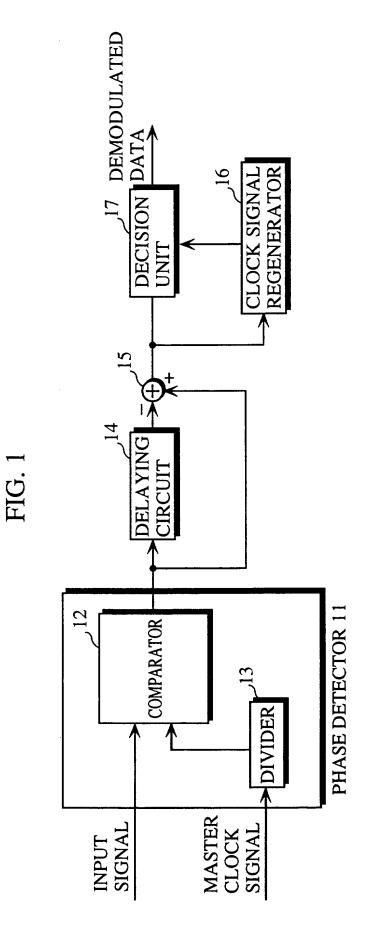

FIG. 1 is a block diagram of a digital demodulator of This digital demodulator demodulates signals the prior art. which have been phase-modulated by QPSK (Quaternary Phase Shift Keying). A radio signal inputted via an antenna is received by a radio unit (not shown) and then sent to a comparator 12 in a 10 phase detector 11 as an input signal. A master clock signal has a frequency which is set at an integral multiple of the frequency of the input signal. The frequency of the master clock signal is divided by a divider 13 in the phase detector 11 and then compared with the frequency of the input signal by the comparator 12, which outputs phase difference data. frequency of the input signal is equal to that of the divided master clock signal.

The phase difference data outputted from the phase detector 11 is sent to a delaying circuit 14, by which it is delayed by one information symbol period. The phase difference data is also sent directly to a subtractor 15, which subtracts the delayed phase difference data from the original phase difference data. The subtraction result data is processed by a decision unit 17, which then outputs demodulated data. decision unit 17 operates based on an operation clock signal generated by a clock signal regenerator 16, which generates operation clock signals in synchronization with the information symbol period.

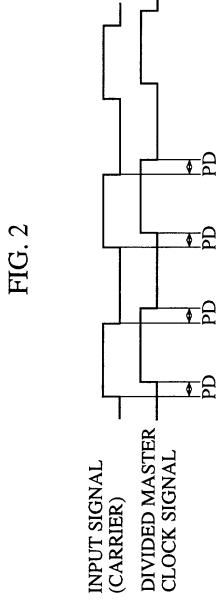

5 (carrier wave) to be inputted to the digital demodulator and a divided master clock signal. The input signal is an unmodulated carrier signal, i.e., a carrier wave itself. A divided master clock signal is given by dividing the frequency of a master clock signal, which is an integral multiple of the frequency of the input signal. In this division, the frequency of the divided master clock signal is made equal to that of the input signal.

The phase difference between an input signal and a divided master clock signal is the constant value Pd. When an input signal is modulated, the phase difference Pd is shifted by the amount of modulation, and the modulated input signal can be demodulated based on the amount of shift.

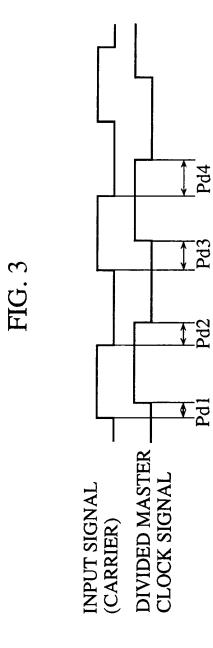

However, when the frequency of a master clock signal is not an integral multiple of the frequency of an input signal, the input signal (carrier) is not in synchronization with the divided master clock signal, as shown in FIG. 3. Here, the phase difference varies, as shown by PD1, PD2, PD3, and PD4. When an input signal is modulated, the amount of modulation is added to this varying phase difference so that it is difficult to demodulate the modulated input signal based on the phase

20

25

difference as it is.

10

As shown in the above prior art, phase detectors of digital demodulators in practical use require each master clock signal to have a frequency which is an integral multiple of the frequency of each input signal.

With such configuration, however, an input signal needs to have a frequency which is an integral multiple of the frequency of a master clock signal, otherwise, the input signal can not be received.

This configuration also imposes restrictions on device design, since an oscillator needs to have a frequency which is an integral multiple of the frequency of an input signal to be demodulated.

To eliminate these problems, the present invention aims to provide a digital demodulator which imposes no restrictions on device design, regardless of the frequencies of input frequencies.

# SUMMARY OF THE INVENTION

The digital demodulator of the present invention includes: a phase data output unit for comparing a phase-modulated input signal with a clock signal which is not in synchronization with the carrier wave of the input signal, and then outputting phase data which corresponds to the phase difference between the input signal and the clock signal; a

delaying unit for delaying the phase data outputted from the phase data output means by a predetermined period of time; a compensation value hold unit for holding a compensation value which corresponds to the phase shift caused by the frequency difference between the carrier wave of the input signal and the clock signal; a delay detection unit for detecting the delay time of the phase data from the phase data output unit, using the phase data outputted from the phase data output unit, the compensation value held by the compensation value hold unit, and the phase data delayed by the delaying unit by the predetermined period of time; and a demodulation unit for demodulating the input signal based on the result of the delay time calculation.

10

15

In such digital demodulator, the delay detection unit is capable of calculating a delay time using the compensation value held by the compensation value hold unit, so that an input signal can be received and demodulated even if its frequency is not an integral multiple of the frequency of a master clock signal. Furthermore, an oscillator having a frequency which is not an integral multiple of the frequency of an input signal to be demodulated can be employed in this digital demodulator, allowing more freedom in device design, regardless of the frequencies of input signals.

The delay detection unit of such digital demodulator includes an addition unit for adding the phase data from the

phase data output unit and the compensation value held by the compensation value hold unit, and a substraction unit for subtracting the phase data delayed by the delaying unit by the predetermined period of time from the addition result by the addition unit.

The installation of such addition unit and subtraction unit enables calculation of the delay time using the compensation value held by the compensation value hold unit.

# BRIEF DESCRIPTION OF THE DRAWINGS

20

These and other objects, advantages and features of the invention will become apparent from the following description thereof taken in conjunction with the accompanying drawings which illustrate a specific embodiment of the invention. In the drawings:

15 FIG. 1 is a block diagram of a digital demodulator of the prior art.

FIG. 2 is a time chart of an unmodulated input signal (carrier wave) to be inputted to the digital demodulator and a divided master clock signal.

FIG. 3 is a time chart of an input signal (carrier) and a divided master clock signal, where the frequency of the master clock signal is not an integral multiple of the frequency of the input signal.

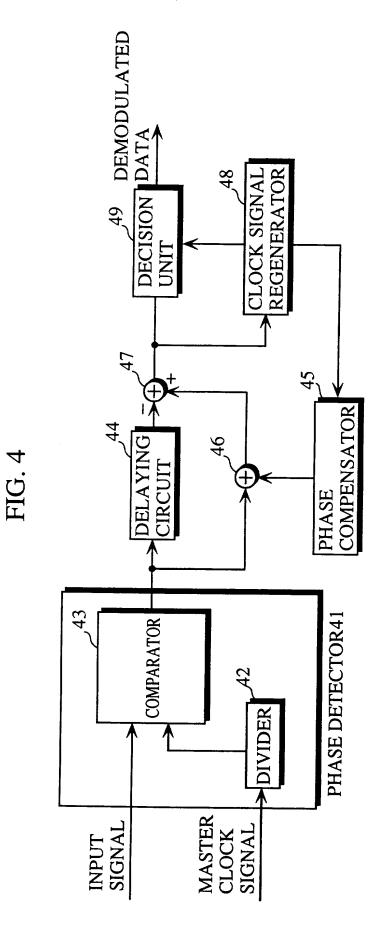

FIG. 4 is a block diagram of a digital demodulator of

an embodiment of the present invention.

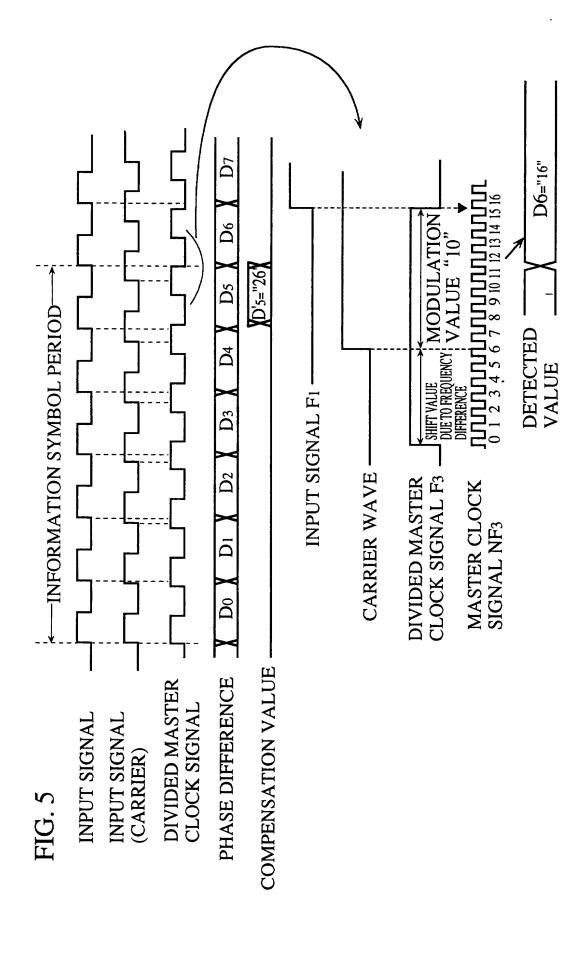

FIG. 5 is a time chart of input and other signals.

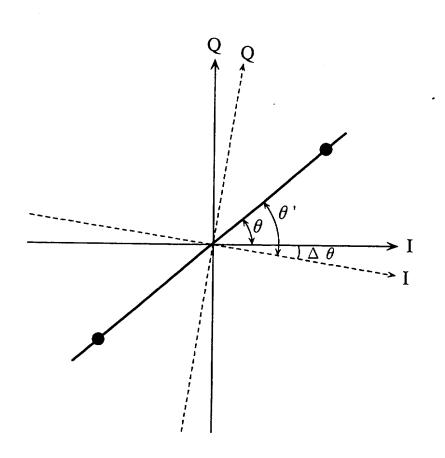

FIG. 6 shows a subtraction result of a subtractor 47, using P and Q coordinates.

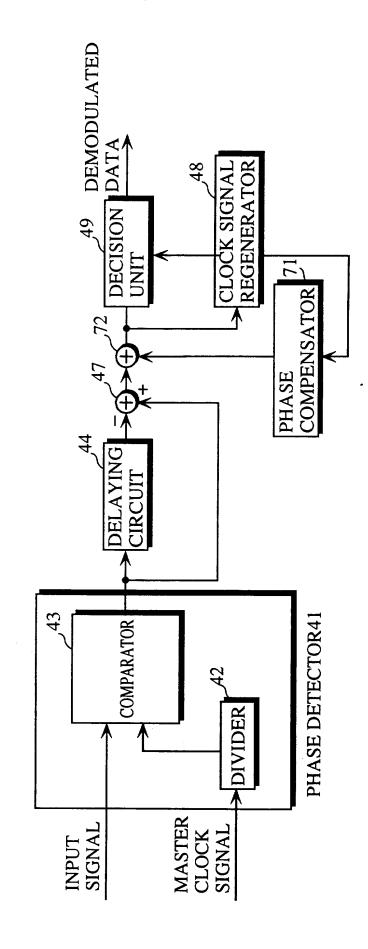

FIG. 7 shows a modification of the digital demodulator of the embodiment.

## PREFERRED EMBODIMENTS OF THE INVENTION

10

15

20

FIG. 4 shows the configuration of the digital demodulator of this embodiment. This digital demodulator demodulates signals which have been phase-modulated by QPSK. It comprises a phase detector 41, a divider 42, a comparator 43, a delaying circuit 44, a phase compensator 45, an adder 46, a subtractor 47, a clock signal regenerator 48, and a decision unit 49.

In the phase detector 41, which includes the divider 42 and the comparator 43, an input signal is compared with a divided master clock signal, and phase difference data is then outputted. As in the prior art, the input signal is a signal outputted from a radio unit (not shown in the figure) which receives transmitted radio signals transmitted via an antenna. Such input signal has a modulating signal as a phase difference of the input signal. The frequency of a master clock signal is not an integral multiple of the frequency of the input signal and it is generated by an oscillator which is independent of the

clock signal regenerator 48.

5

The divider 42 receives the master clock signal and divides it so that the frequency of the master clock signal becomes equal to the frequency of the input signal.

The comparator 43 operates in accordance with master clock signals. It compares the input signal with the divided master clock signal from the divider 42 and then outputs the phase shift of the input signal as phase difference data. phase difference data contains an amount of the phase shift 10 which is caused by the frequency difference between the input signal and the divided signal, as well as the phase difference which corresponds to the amount of modulation of the input Such phase difference data is outputted by the comparator 43 as 5-bit numerical data which represents 0 to 15 31.

The delaying circuit 44 latches the phase difference data outputted from the comparator 43 and delays it by one information symbol period.

The phase difference compensator 45 is formed by a register and holds a phase compensation value 20 exclusively determined by the amount of a phase shift determined by the frequency difference between a divided master clock signal and an input signal. The amount of phase shift in one information symbol period is given by the following formula:

5

10

This amount of shift is then converted into a 5-bit integer (0-31) to give the phase compensation value.

The adder 46 adds the phase compensation value held by the phase compensator 45 to the phase difference data outputted from the comparator 43 in every information symbol period.

The subtractor 47 subtracts the phase difference data plus the phase compensation value from the phase difference data delayed by one information symbol period by the delaying circuit 44. The amount of phase of a phase difference corresponding to the amount of modulation of each input signal in one information symbol period is thus calculated.

The clock signal regenerator 48 is formed by a PLL circuit and regenerates an operation clock signal in synchronization with one information symbol period according to an input signal. The delaying circuit 44, the phase compensator 45, the adder 46, the subtractor 47, and the decision unit 49 operate in accordance with the operating clock signal regenerated from the clock signal regenerator 48.

The decision unit 49 outputs demodulated data in

accordance with the subtraction result from the subtractor 47.

The following explanation is for the operation of the digital demodulator. Referring now to the time chart in FIG. 5, the upper half of the figure shows an input signal, an unmodulated input signal, a divided master clock signal, a phase difference, and a compensation value. In the lower half of the figure, an enlarged detail of the time chart is shown. For ease of explanation, the start edge of every signal has been aligned, as can be seen from the left edge of the time chart in the upper half of the figure.

The first signal at the top in the figure is an input signal. The pulse width of this input signal varies depending on the amount of modulation. The input signal carries a modulating signal which has 6 cycles as one information symbol period. The second signal from the top is an unmodulated input signal, i.e., the carrier wave of the input signal. The first input signal has a smaller pulse width than that of the carrier wave as a result of modulation. The phase difference between the carrier wave and the input signal is the amount of the modulation caused by the modulating signal. The second input signal (carrier) is shown here for ease of explanation, but in practice, this kind of signal is not inputted to the demodulator of this embodiment.

The third signal from the top is a signal obtained by dividing a master clock signal using the divider 42. The

comparator 43 compares this divided signal with the input signal and outputs the rise time difference as the phase difference between the divided signal and the input signal. This phase difference between the input signal and the divided signal is indicated as DO, D1, D2, ... on the fourth line in FIG. 5. The phase difference is outputted by the comparator 43 for every cycle of each input signal.

In the lower half of the figure is shown an enlarged detail of the input signal, the unmodulated input signal, and the divided signal, in conjunction with a master clock signal, where D5 is outputted as phase difference data.

The phase difference data represents the rise time difference between the input signal and the divided master clock signal, and more specifically, it is 5-bit numerical data showing the number of cycles by which the rise time difference is represented. In this embodiment, for example, the comparator 43 contains a counter (not shown in the figure) which operates in accordance with master clock signals and outputs the counter data "16" as phase difference data. As can be seen from the figure, such phase difference data includes the amount of modulation of the input signal and the amount of phase shift caused by the frequency difference between the input signal (carrier) and the divided signal. In this example, the amount of modulation is 10 while the amount of phase shift is 6.

20

The fifth line from the top shows that a compensation

value held by the phase compensator 45 is outputted to the adder 46 in one information symbol period (more specifically, in the last cycle of one information symbol period). embodiment, "6" is outputted as the value of the phase shift 5 caused by the frequency difference between the input signal (carrier) and the divided signal.

6 shows P and Q coordinates by which the subtraction result by the subtractor 47 is represented.  $oldsymbol{ heta}$  is a phase value which varies depending on modulation systems (in the case of QPSK,  $oldsymbol{ heta}$  is 0,  $\pm\pi/2$ , or  $\pi$ ).  $\Deltaoldsymbol{ heta}$  represents the amount of the phase shift caused by the frequency difference between the input signal (carrier) and the divided signal. phase shift value is equal to the phase compensation value held by the phase compensator 45.  $oldsymbol{ heta}$  represents the phase difference 15 which is a result outputted by the subtractor 47 in the case where neither phase compensator 45 nor adder 46 is provided. Without the phase compensator 45 and the adder 46, a phase shift value  $\Delta\, heta$  is caused due to the frequency difference between the input signal (carrier) and the divided signal. By providing the 20 phase compensator 45 and others, however, the phase shift value  $\Delta\, oldsymbol{ heta}$  can be eliminated and a desired phase value  $\Delta\, oldsymbol{ heta}$  can be obtained.

10

In the above explanation, the comparator 43 outputs numerical data as phase difference data from a counter (not shown in the figure) in accordance with a master clock signal,

but other ways may be employed as long as the phase difference between an input signal and a divided signal is given.

In this embodiment, one compensation value is added to phase difference data once per information symbol period, as shown in the time chart in FIG. 5, although such a compensation value may be divided into several parts which are then added separately to the phase difference data.

In this embodiment, a compensation value is added to phase difference data which is not delayed by one information symbol period, as shown by the phase compensator 45 and the adder 46 in FIG. 4, but the addition is not necessarily performed there. As shown by the phase compensator 71 and the adder 72 in FIG. 7, for instance, a compensation value can be added to the result of the subtraction by the subtractor 47.

10

A compensation value held by the phase compensator 45 can be subtracted from phase difference data right after the delaying process by the delaying circuit 44 or from the previous phase difference data. That is, a compensation value is added so that a value to be inputted to the decision unit 49 is (A - 20 B + x), where A is phase difference data, B is phase difference data delayed by one information symbol period, and x is a compensation value.

As described so far, the digital demodulator of the present invention imposes no restrictions on device design, regardless of the frequencies of input signals, because a

compensation value corresponding to the phase difference between a divided master clock signal and a carrier wave of an input signal is added in synchronization with information symbol periods. As a result, demodulation can be carried out even if the frequency of the master clock signal is not an integral multiple of that of the input signal.

Although the present invention has been fully described by way of examples with reference to the accompanying drawings, it is to be noted that various changes and modifications will be apparent to those skilled in the art. Therefore, unless such changes and modifications depart from the scope of the present invention, they should be construed as being included therein.

# INDUSTRIAL FIELD IN WHICH THE INVENTION CAN BE UTILIZED

The digital demodulator of the present invention is

effective in communication systems which use digital modulation

methods for demodulating phase modulation, with PSK (Phase Shift

Keying) being the most desirable method.

### CLAIMS

### What is claimed is:

- 1 1. A digital demodulator comprising:

- 2 phase difference data output means for comparing a

- 3 phase-modulated input signal with a clock signal which is not in

- 4 synchronization with the carrier wave component of the input

- 5 signal, and outputting phase difference data which corresponds

- 6 to the phase difference between the input signal and the clock

- 7 signal;

- 8 delaying means for delaying the phase difference data

- 9 outputted from said phase difference data output means by a

- 10 predetermined period of time;

- 11 compensation value hold means for holding a compensation

- 12 value which corresponds to a phase shift caused by the frequency

- 13 difference between the carrier wave component and the clock

- 14 signal;

- delay detection means for detecting a delay of the phase

- 16 difference data outputted from said phase difference data output

- 17 means using the phase difference data outputted from said phase

- 18 difference data output means, the compensation value held by

- 19 said compensation value hold means, and the phase difference

- 20 data delayed by said delaying means by the predetermined period

- 21 of time; and

- demodulation means for demodulating the input signal

- 23 based on the result of the delay detection.

- 1 2. A digital demodulator according to Claim 1, wherein said

- 2 delay detection means comprises:

- 3 addition means for adding the phase difference data

- 4 outputted from said phase difference data output means and the

- 5 compensation value held by said compensation value hold means;

- 6 and

- 7 subtraction means for subtracting the phase difference

- 8 data delayed by said delaying means by the predetermined period

- 9 of time from the result of the addition by said addition

- 10 means.

- 1 3. A digital demodulator according to Claim 1, wherein said

- 2 delay detection means comprises:

- 3 subtraction means for subtracting the phase difference

- 4 data delayed by said delaying means by the predetermined period

- 5 of time from the phase difference data outputted from said phase

- 6 difference data output means; and

- 7 addition means for adding the subtraction result of said

- 8 subtraction means and the compensation value held by said

- 9 compensation value hold means.

- 1 4. A digital demodulator according to Claim 1, wherein said

- 2 delay detection means comprises:

- first subtraction means for subtracting the compensation

- 4 value held by said compensation value hold means from the phase

- 5 difference data delayed by said delaying means by the

- 6 predetermined period of time; and

- 7 second subtraction means for subtracting the subtraction

- 8 result of said first subtraction means from the phase difference

- 9 data outputted from said phase difference data output means.

- 1 5. A digital demodulator comprises:

- 2 phase difference data output means for comparing an

- 3 input signal with a clock signal and outputting phase difference

- 4 data of the input signal;

- 5 compensation value hold means for holding a compensation

- 6 value which corresponds to a phase shift caused by the frequency

- 7 difference between the input signal and the clock signal;

- first subtraction means for subtracting the compensation

- 9 value held by said compensation value hold means from the phase

- 10 difference data outputted from said phase difference data output

- 11 means;

- 12 delaying means for delaying phase difference data which

- 13 is the subtraction result of said first subtraction means by a

- 14 predetermined period of time;

- second subtraction means for subtracting the phase

- 16 difference data delayed by said delaying means by the

- 17 predetermined period of time from the phase difference data

- 18 outputted from said phase data output means; and

- demodulation means for demodulating the input signal

- 20 based on the subtraction result of said second subtraction

- 21 means.

- 1 6. A digital demodulator according to one of Claims 1 to 5,

- 2 wherein said addition means and said subtraction means perform

- 3 addition and subtraction, respectively, in accordance with a

- 4 second clock signal which is in synchronization with information

- 5 symbol periods.

- 1 7. A digital demodulator according to one of Claims 1 to 6,

- 2 wherein the predetermined delay period of time caused by said

- 3 delaying means is the information symbol period.

# INTERNATIONAL SEARCH REPORT

International application No.

PCT/JP96/03481

|                                   | ASSIFICATION OF SUBJECT MATTER  . C1 <sup>6</sup> H04L27/22                                                              |                                                                                 |                               |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-------------------------------|

|                                   | ,                                                                                                                        | ath maties of allowing at the LING                                              |                               |

|                                   | to International Patent Classification (IPC) or to b LDS SEARCHED                                                        | on national classification and IPC                                              |                               |

|                                   | ocumentation searched (classification system follower                                                                    | d by classification symbols)                                                    |                               |

| Int                               | . C1 <sup>6</sup> H04L27/18-27/22                                                                                        | ,                                                                               |                               |

| -                                 |                                                                                                                          |                                                                                 |                               |

| Documentat                        | tion searched other than minimum documentation to the                                                                    |                                                                                 | the fields searched           |

|                                   | suyo Shinan Koho<br>ai Jitsuyo Shinan Koho                                                                               | 1926 - 1996<br>1971 - 1996                                                      |                               |

|                                   | ata base consulted during the international search (name                                                                 |                                                                                 | terms used)                   |

|                                   |                                                                                                                          | •                                                                               | ,                             |

|                                   |                                                                                                                          |                                                                                 |                               |

| C. DOCU                           | MENTS CONSIDERED TO BE RELEVANT                                                                                          |                                                                                 |                               |

| Category*                         | Citation of document, with indication, where                                                                             | ·                                                                               | Relevant to claim             |

|                                   | JP, 60-93862, A (NEC Corp                                                                                                | .),                                                                             |                               |

| x                                 | May 25, 1985 (25, 05, <b>85)</b><br>Page 2, lower right column                                                           | (Family: none)                                                                  | 1 2 2                         |

|                                   | upper right column, line 15; Figs. 5, 7, 8 5, 6, 7                                                                       |                                                                                 | 1, 2, 3, 5, 6, 7              |

|                                   |                                                                                                                          |                                                                                 |                               |

|                                   | JP, 3-274844, A (Japan Rac<br>December 5, 1991 (05. 12.                                                                  | 91)                                                                             |                               |

| & EP, 449146, A2 & US, 5097220, A |                                                                                                                          | 7220, A                                                                         |                               |

| Х                                 | 1                                                                                                                        |                                                                                 | 1, 2, 3,                      |

|                                   | left column, line 5; Fig.                                                                                                | 1                                                                               | 5, 6, 7                       |

|                                   |                                                                                                                          |                                                                                 |                               |

|                                   |                                                                                                                          |                                                                                 |                               |

|                                   |                                                                                                                          |                                                                                 |                               |

|                                   |                                                                                                                          |                                                                                 |                               |

| 1                                 |                                                                                                                          |                                                                                 |                               |

|                                   |                                                                                                                          |                                                                                 |                               |

|                                   |                                                                                                                          | į                                                                               |                               |

|                                   |                                                                                                                          |                                                                                 |                               |

| Further                           | documents are listed in the continuation of Box C                                                                        | See patent family annex.                                                        |                               |

|                                   | stegories of cited documents:                                                                                            | T later document published after the inter                                      | national filing date or price |

| to be of p                        | defining the general state of the art which is not considered articular relevance                                        | the principle of theory underlying the                                          | iovention                     |

| " document                        | cument but published on or after the international filing dan<br>which may throw doubts on priority claim(s) or which is | considered novel or cannot be consid                                            | cred to involve an inven      |

| C1100 10 E                        | stablish the publication date of another citation or otherson (as specified)                                             | step when the document is taken alone "Y" document of particular relevance; the | •                             |

|                                   | referring to an oral disclosure, use, exhibition or other                                                                | considered to involve an inventive combined with one or more other such of      | Sien when the documen         |

| document                          | published prior to the international filing date but later than                                                          | being obvious to a person skilled in th                                         | e art                         |

|                                   |                                                                                                                          | "&" document member of the same patent                                          |                               |

|                                   | nual completion of the international search eary 10, 1997 (10. 02. 97)                                                   | Date of mailing of the international sear                                       | •                             |

|                                   |                                                                                                                          | February 25, 1997                                                               | (25. 02. 97                   |

|                                   | ling address of the ISA/                                                                                                 | Authorized officer                                                              |                               |

|                                   | ese Patent Office                                                                                                        |                                                                                 |                               |

| simile No.                        |                                                                                                                          | Telephone No.                                                                   |                               |

| PCT/ISA/                          | 210 (second sheet) (July 1992)                                                                                           |                                                                                 |                               |