### (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

DA13 DA15 EA10 EB01 FB14 FB20 GB10 HA08 JA20

最終頁に続く

特開2012-231160 (P2012-231160A)

(43) 公開日 平成24年11月22日(2012.11.22)

| (51) Int.Cl.  HO1L 29/786  HO1L 21/336  GO9F 9/30  HO1L 21/265          | (2006.01) HO1L<br>(2006.01) HO1L                                                                                                                                            | 29/78 6 1 6 V<br>29/78 6 2 7 F<br>29/78 6 2 6 C<br>9/30 3 3 8 | テーマコード (参考)<br>5CO94<br>5F11O<br>(全 25 頁) 最終頁に続く |

|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|--------------------------------------------------|

| (21) 出願番号<br>(22) 出願日<br>(62) 分割の表示<br>原出願日<br>(31) 優先権主張番号<br>(32) 優先日 | 特願2012-148421 (P2012-148421)<br>平成24年7月2日 (2012.7.2)<br>特願2012-1720 (P2012-1720)<br>の分割<br>平成13年8月14日 (2001.8.14)<br>特願2000-256530 (P2000-256530)<br>平成12年8月25日 (2000.8.25) | (71) 出願人 000153878<br>株式会社半導体<br>神奈川県厚木市<br>(72) 発明者 磯部 敦生    | エネルギー研究所<br>長谷398番地<br>長谷398番地 株式会社              |

| (33) 優先権主張国                                                             | 日本国 (JP)                                                                                                                                                                    | 神奈川県厚木市<br>半導体エネルギ<br>(72)発明者 荒尾 達也                           | 長谷398番地 株式会社                                     |

(54) 【発明の名称】半導体装置の作製方法、および半導体装置

## (57)【要約】

【課題】低温プロセスを実現する半導体装置の作製方法、及び半導体装置を提供する。

【解決手段】結晶構造を有する半導体層の一部にp型を付与する不純物元素及び水素を同時に添加することによって、一部の上層部分を非晶質化するとともに、一部の下層部分に結晶質を残存させ、加熱処理を行うことによって、一部の中の水素を拡散させる。

### 【選択図】なし

#### 【特許請求の範囲】

### 【請求項1】

結晶構造を有する半導体層の一部にp型を付与する不純物元素及び水素を同時に添加することによって、前記一部の上層部分を非晶質化するとともに、前記一部の下層部分に結晶質を残存させ、

加熱処理を行うことによって、前記一部の中の前記水素を拡散させることを特徴とする半導体装置の作製方法。

### 【請求項2】

結晶構造を有する半導体層上にゲート絶縁膜を形成し、

前記ゲート絶縁膜上にゲート電極を形成し、

前記ゲート電極をマスクとして用いて、前記半導体層の一部にp型を付与する不純物元素及び水素を同時に添加することによって、前記一部の上層部分を非晶質化するとともに、前記一部の下層部分に結晶質を残存させ、

加熱処理を行うことによって、前記一部の中の前記水素を拡散させることを特徴とする半導体装置の作製方法。

#### 【請求項3】

請求項1又は請求項2において、

前記加熱処理は、水素化処理であることを特徴とする半導体装置の作製方法。

#### 【請求項4】

請求項1乃至請求項3のいずれか一において、

全ての製造プロセス温度を 3 5 0 以下の温度で行うことを特徴とする半導体装置の作製方法。

#### 【請求項5】

半導体層と、

前記半導体層上のゲート絶縁膜と、

前記ゲート絶縁膜上のゲート電極と、を有し、

前記半導体層は、第1の領域と、第2の領域と、第3の領域と、を有し、

前記第1の領域は、前記第2の領域と前記第3の領域との間に配置されており、

前記ゲート電極は、前記第1の領域と重なり、

前記第2の領域及び前記第3の領域には、p型を付与する不純物元素及び水素が含有されており、

前記第1の領域は、結晶構造を有し、

前記第2の領域の上層部分及び前記第3の領域の上層部分は、非晶質構造を有し、

前記第2の領域の下層部分及び前記第3の領域の下層部分は、結晶構造を有することを 特徴とする半導体装置。

### 【請求項6】

プラスチック基板と、

前記プラスチック基板上の半導体層と、

前記半導体層上のゲート絶縁膜と、

前記ゲート絶縁膜上のゲート電極と、を有し、

前記半導体層は、第1の領域と、第2の領域と、第3の領域と、を有し、

前記第1の領域は、前記第2の領域と前記第3の領域との間に配置されており、

前記ゲート電極は、前記第1の領域と重なり、

前記第2の領域及び前記第3の領域には、p型を付与する不純物元素及び水素が含有されており、

前記第1の領域は、結晶構造を有し、

前記第2の領域の上層部分及び前記第3の領域の上層部分は、非晶質構造を有し、

前記第2の領域の下層部分及び前記第3の領域の下層部分は、結晶構造を有することを特徴とする半導体装置。

### 【請求項7】

20

10

30

40

請求項6において、

前記プラスチック基板は、ポリイミド、アクリル、ポリエチレンテレフタレート、ポリカーボネイト、ポリアリレート、ポリエーテルエーテルケトン、ポリエーテルスルホン、ポリエーテルニトリル、ナイロン、ポリスルホン、ポリエーテルイミド、又はポリブチレンテレフタレートのいずれかを有することを特徴とする半導体装置。

#### 【請求項8】

請求項5乃至請求項7のいずれか一において、

前記非晶質構造とは前記結晶構造を有する第1の領域よりも結晶性が低いことを特徴とする半導体装置。

### 【請求項9】

請求項5乃至請求項8のいずれか一において、

前記結晶構造は、ラマン散乱測定で 5 0 0 ~ 5 2 0 c m <sup>- 1</sup> の範囲にスペクトルの極大値を示すことを特徴とする半導体装置。

【発明の詳細な説明】

#### 【技術分野】

### [0001]

本発明は薄膜トランジスタ(以下、TFTという)で構成された回路を有する半導体装置およびその作製方法に関する。例えば、液晶表示パネルに代表される電気光学装置およびその様な電気光学装置を部品として搭載した電子機器に関する。

#### [0002]

なお、本明細書中において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指し、電気光学装置、発光装置、半導体回路および電子機器は全て半導体装置である。

#### 【背景技術】

### [0003]

近年、絶縁表面を有する基板上に形成された半導体薄膜(厚さ数~数百nm程度)を用いて薄膜トランジスタ(TFT)を構成する技術が注目されている。薄膜トランジスタはICや電気光学装置のような電子デバイスに広く応用され、特に画像表示装置(液晶表示装置やEL表示装置)のスイッチング素子として開発が急がれている。

#### [0004]

スイッチング素子として用いられているTFTにおいては、半導体層としてアモルファスシリコン膜やポリシリコン膜が用いられており、ガラス基板を用いる場合、TFTの作製プロセスにおける処理温度は400 ~600 程度であった。なお、ポリシリコン膜は、レーザー結晶化、または固相結晶化(600~1000 )により形成している。

#### [0005]

現在、ガラス基板や石英基板が多く使用されているが、割れやすく、重いという欠点がある。また、大量生産を行う上で、ガラス基板や石英基板は大型化が困難であり、不向きである。そのため、可撓性を有する基板、代表的にはフレキシブルなプラスチックフィルムの上にTFT素子を形成することが試みられている。

### [0006]

また、TFTの作製プロセスにおいて、ソース領域及びドレイン領域を形成するため、 不純物元素のドーピングは必要不可欠であり、極めて重要な位置を占めている。代表的な 不純物元素のドーピング法としては、イオン注入法やイオンドーピング法が挙げられる。

#### [0007]

これらの不純物元素のドーピング法によって、半導体層にp型を付与する不純物元素を添加した後には、活性化させるための熱処理、またはレーザー等の強光照射処理が必須となっていた。

### [0008]

一般的に不純物元素の活性化には1000 近い高温での熱処理が必要であると言われているが、ガラス基板を用いる場合は基板の歪み点以上の熱処理を行うことができないた

10

20

30

40

10

20

30

40

50

め、長時間での熱処理(500~600)が必要となり、スループットが悪化していた。ガラス基板を用いる場合、熱処理で活性化するTFTの作製プロセスにおいては、この処理温度(500~600)がプロセス温度の最高温度となっていた。

### [0009]

また、プラスチック基板を用いる場合、さらに耐熱性が低いためプロセスの最高温度を低くせざるを得ず、結果的にガラス基板上に形成する時ほど良好な電気特性のTFTを形成できないのが現状である。そのため、プラスチックフィルムを用いた高性能な液晶表示装置や発光素子は実現されていない。

### [0010]

特に、イオンドーピング法を用いた場合、 p 型を付与する不純物元素を添加する際、結晶質半導体層のドーピングされた領域は不純物元素により損傷を受けて非晶質な領域となって、高抵抗化していた。そのため従来では、 5 0 0 ~ 6 0 0 の熱処理やレーザーの照射処理によって、ソース領域及びドレイン領域の結晶性を回復させて低抵抗化していた

### [0011]

また、イオン質量分離を利用したイオン注入法を用いた場合、不純物濃度や注入深さを 正確に制御できるが、イオン注入装置のイオンビーム幅は微小であるため、大型基板を用 いた大量生産には不向きであった。

## [0012]

また、活性化としてレーザー光を用いた場合は、低温での活性化処理が可能となるが、 制御性が悪く、基板 1 枚毎に行う必要があるのでスループットも悪い。

また、ドーピングされた基板にレーザー処理を行うとチャンバー汚染が生じる恐れがあり、活性化するために専用のレーザー装置、あるいは装置の改造が別途必要となるため、設備コスト増大に繋がってしまう問題が生じる。

#### 【発明の概要】

【発明が解決しようとする課題】

#### [0013]

上記従来技術によるTFTの作製工程において、基板を400 以上に加熱しなければならないため、基板としてガラス基板を用いた場合には問題とならないが、プラスチック基板のような低耐熱性基板を用いた場合は、その加熱温度に耐えられないという問題が生じていた。

## [0014]

本発明は、さらなる低温プロセス(300 以下、好ましくは250 以下) を実現し、素子形成基板として低耐熱性のプラスチック基板を用いることを可能とすると ともに、工程簡略化とスループットの向上を実現することを課題とする。

### 【課題を解決するための手段】

#### [ 0 0 1 5 ]

従来、ドーピングの際に形成されるソース領域及びドレイン領域の非晶質部分を数時間の高温熱処理(500~600)、またはレーザ処理によって結晶性を回復させなければ低抵抗化させるのは困難であった。本発明は、このような高温の熱処理やレーザー光の照射を行うことなく、ソース領域またはドレイン領域を低抵抗化させることができるものである。

### [0016]

本発明は、イオンドーピング法を用いて結晶構造を有する半導体層(結晶質半導体層)にp型不純物元素及び水素元素を低加速電圧で添加した後、100~300、好ましくは150~250 の熱処理を行うことにより、低抵抗なソース領域およびドレイン領域を形成することを特徴としている。即ち、本発明は、短時間、且つ、低温で低抵抗なソース領域およびドレイン領域を形成することができる。

### [0017]

本発明において、イオンドーピングの際、p型を付与する不純物元素と同時に添加され

る水素をソース領域及びドレイン領域に高濃度で存在させることが重要であり、イオンドーピング後に  $1\ 0\ 0\ \sim\ 3\ 0\ 0$  、好ましくは  $1\ 5\ 0\ \sim\ 2\ 5\ 0$  の熱処理を行って水素拡散させることによってソース領域またはドレイン領域の低抵抗化を可能とした。なお、イオンドーピング直後、ソース領域及びドレイン領域に含まれる水素濃度は、  $1\ \times\ 1\ 0^{19}\ \sim\ 1\ \times\ 1\ 0^{22}\ /\ c\ m^3$ 、好ましくは、  $1\ \times\ 1\ 0^{21}\ \sim\ 1\ \times\ 1\ 0^{22}\ /\ c\ m^3$ 以上とする。

#### [ 0 0 1 8 ]

また、本発明において、イオンドーピング以降の工程での熱処理は400 以下、好ましくは350 以下とすることが重要である。なぜなら、400 程度の熱処理を行うと半導体膜中から水素が脱離して抜けてしまうからである。即ち、イオンドーピング以降の工程では、膜中から水素が脱離する熱処理やレーザー光の照射を行わないことを特徴としている。

[0019]

また、本発明において、ソース領域及びドレイン領域は、イオンドーピングにより非晶質化されるが、完全に非晶質化されないようなドーピング条件とすることが好ましい。例えば、低加速電圧10kV以下でドーピングすることによって、ソース領域及びドレイン領域は全体的に損傷をうけて非晶質となる。また、非晶質となった部分には不純物元素が多く添加され、不純物元素と同時にドーピングされる水素元素も多く添加されると推測できる。即ち、本発明において、水素と不純物元素とを同時にドーピングすることが望ましい。水素だけをドーピングした場合には、質量数やイオン半径が小さいので膜厚の薄い半導体膜を突き抜けてしまい、上層部分のみに添加することは非常に困難である。

[0020]

また、本発明の熱処理(100~300 )以降に高温の熱処理を行わなければ、不純物元素がドーピングされて非晶質となった領域(非晶質領域とも呼ぶ)は、TFTの作製完了時において、そのままの状態である。即ち、本発明においては、TFTの作製完了時において、不純物元素がドーピングされないチャネル形成領域は主に結晶構造を有し、ソース領域及びドレイン領域は主に非晶質を有している。従来ではソース領域及びドレイン領域を非晶質のままの状態とすることはなく、熱処理やレーザー光などによって再結晶化させていた。

[0021]

本明細書で開示する発明の構成は、同一の絶縁表面上に画素部及び駆動回路を含む電気光学装置において、 前記画素部及び駆動回路は p チャネル型 T F T で形成され、 前記 p チャネル型 T F T のチャネル形成領域は、主に結晶構造であり、且つ、前記 T F T のソース領域またはドレイン領域は、主に非晶質構造であることを特徴とする半導体装置である。ここで「主に」とは 5 0 %以上を指している。

[0022]

上記構成において、前記絶縁表面は、プラスチック基板上に設けられた絶縁膜表面である ことを特徴としている。

[0023]

また、前記pチャネル型TFTの半導体層は、スパッタ法、PCVD法、LPCVD法 、真空蒸着法、または光CVD法により形成されたことを特徴としている。

[ 0 0 2 4 ]

従来、プラスチック基板は耐熱性の面で限界があるため、プラスチック基板上に特性の優れたTFTを作製することは非常に困難であった。

[0025]

また、本発明は、p型の不純物元素のドーピング後に100~300 、好ましくは150~250 の熱処理を行なえばよく、工程順序は特に限定されない。

[0026]

また、上記熱処理に代えて水素化処理(水素プラズマ処理、あるいは水素雰囲気での熱処理等)を100~300 、好ましくは150~250 で行えば、さらに高濃度の水素を膜中に含有させることができ、相乗効果を得ることができる。この場合、熱処理工程

20

10

30

40

が削減でき、スループットが向上する。また、水素化処理以外のTFT作製工程、例えば、成膜処理を100~300 で行っても同様の効果(ソース領域及びドレイン領域の低抵抗化)を得ることができる。

#### [0027]

また、TFTの構造は特に限定されず、トップゲート型TFTであってもボトムゲート 型TFTであってもよい。

#### [0028]

また、同一基板上における全ての回路、即ち駆動回路と画素TFTをPチャネル型TFTのみで作製すればマスク数の低減となり、歩留まりも向上する。

### [0029]

また、上記構造を実現するための発明の構成は、 絶縁表面上に結晶構造を有する半導体層を形成する第1の工程と、前記結晶構造を有する半導体層上に絶縁層を形成する第2の工程と、前記絶縁層上に導電層を形成する第3の工程と、イオンドーピング法により前記結晶構造を有する半導体層の一部にp型を付与する不純物元素及び水素を同時に添加して非晶質領域を形成する第4の工程と、熱処理を行って前記非晶質領域の抵抗値を低減させ、前記非晶質領域をソース領域またはドレイン領域とする第5の工程と、を有することを特徴とする半導体装置の作製方法である。なお、これらの工程によりトップゲート型TFTが形成される。

#### [0030]

上記構成において、前記導電層はゲート電極であり、前記p型を付与する不純物元素及び水素を添加する際、前記導電層をマスクとして前記半導体層の上層部分に添加することを特徴としている。

### [0031]

また、本発明の他の発明の構成は、絶縁表面上に導電層を形成する第1の工程と、導電層上に絶縁層を形成する第2の工程と、前記絶縁層上に結晶構造を有する半導体層を形成する第3の工程と、イオンドーピング法により前記結晶構造を有する半導体層の一部にp型を付与する不純物元素及び水素を添加添加して非晶質領域を形成する第4の工程と、熱処理を行って前記非晶質領域の抵抗値を低減させ、前記非晶質領域をソース領域またはドレイン領域とする第5の工程と、を有することを特徴とする半導体装置の作製方法である。なお、これらの工程によりボトムゲート型TFTが形成される。

## [0032]

上記構成において、前記熱処理は、100~300 の熱処理で行い、ソース領域及びドレイン領域を低抵抗化させる。また、前記熱処理は、水素雰囲気での熱処理であってもよい。

### [0033]

あるいは、上記構成において、前記熱処理は、100~300 の水素プラズマ処理で行ってソース領域及びドレイン領域を低抵抗化させてもよい。

#### [0034]

また、上記各構成において、前記絶縁表面は、プラスチック基板上に設けられた絶縁膜表 面である。

## [ 0 0 3 5 ]

また、上記各構成において、 p 型を付与する不純物元素及び水素を添加する工程以降の製造プロセス温度が 3 5 0 以下、好ましくは 3 0 0 以下であることを特徴としている

## [0036]

また、上記各構成において、 p 型を付与する不純物元素及び水素を添加する工程以降の 製造プロセスで前記非晶質領域を再結晶化させないことを特徴としている。

#### [0037]

また、本発明は、低温での熱処理でソース領域及びドレイン領域の電気抵抗値を低減するものであるため、非常にプラスチック基板に適したものであるが、ガラス基板や石英基

10

20

30

40

板にも適用することができることは言うまでもない。ガラス基板や石英基板に適用する場合においても、プロセス温度の低下によるコスト低減やスループットの向上といった効果が得られる。

### 【発明の効果】

[0038]

本発明によれば、低温(300 、好ましくは250 以下)での熱処理(数分間)によりソース領域及びドレイン領域の低抵抗化できるので、耐熱性の低いプラスチック基板を素子形成基板として用いる場合であっても十分にシート抵抗値が低いTFTを作製することができる。従って、フレキシブルなプラスチックフィルムの上にTFT素子を形成することも可能である。

[0039]

また、本発明によって、非常に少ない工程数、且つ低温・短時間で電気光学装置を作製することができる。そのため、歩留まり及びスループットが向上し、製造コストを低減することが可能である。

[0040]

また、安価な電気光学装置を作製できるようになったことで、それを表示部に用いる様々な電気器具を安価な価格で提供することができる。

【図面の簡単な説明】

[0041]

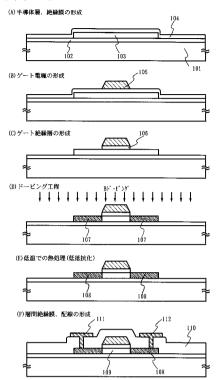

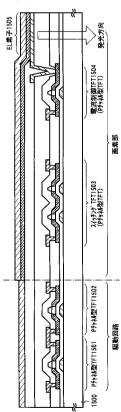

- 【図1】TFTの作製工程を示す図。

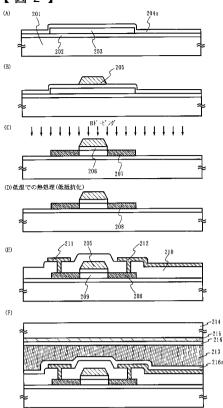

- 【図2】AM-LCDの作製工程を示す図。(実施例1)

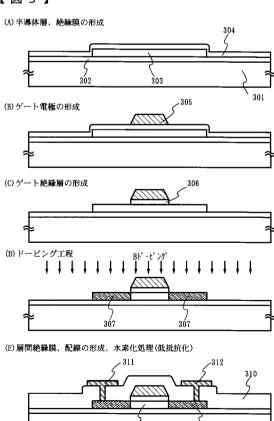

- 【図3】TFTの作製工程を示す図。(実施例2)

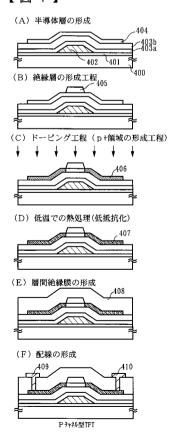

- 【図4】 TFTの作製工程を示す図。(実施例3)

- 【図5】AM-LCDの外観を示す図。

- 【 図 6 】 A M L C D の 回 路 ブロック 図 を 示 す 図 。

- 【図7】膜厚50nmの実験結果を示すグラフ。

- 【図8】膜厚70nmの実験結果を示すグラフ。

- 【 図 9 】 膜 厚 1 0 0 n m の 実 験 結 果 を 示 す グ ラ フ 。

- 【図10】ラマン散乱スペクトルを示す図。

- 【図11】画素部の上面図を示す図。

- 【図12】画素部の断面図を示す図。

- 【図13】アクティブマトリクス型EL表示装置の構成を示す図。

- 【図14】EL表示装置の上面図を示す図。

- 【図15】EL表示装置の回路ブロック図を示す図。

- 【図16】電子機器の一例を示す図。

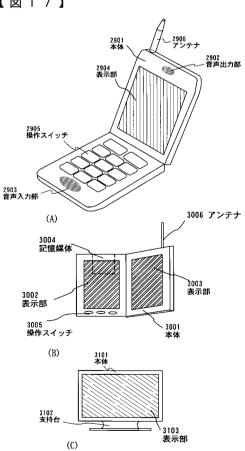

- 【図17】電子機器の一例を示す図。

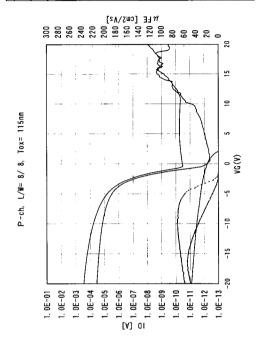

- 【図18】TFTの電気特性(V-I特性)を示す図。

- 【発明を実施するための形態】

- [0042]

本発明の実施形態について、以下に説明する。本発明のTFT作製方法の一例を図1に示す。

[0043]

まず、基板101上に下地絶縁膜102を形成する。基板101はプラスチック基板を用い、例えば、ポリイミド、アクリル、PET(ポリエチレンテレフタレート)、ポリカーボネイト(PC)、ポリアリレート(PAR)、PEEK(ポリエーテルエーテルケトン)、PES(ポリエーテルスルホン)、PEN(ポリエーテルニトリル)、ナイロン、ポリスルホン(PSF)、ポリエーテルイミド(PEI)、ポリブチレンテレフタレート(PBT)等からなるプラスチック基板を用いることができる。ここでは350 の熱処理に十分耐え得るポリイミドからなる基板を用いた例を示す。

[0044]

50

10

20

30

下地絶縁膜102はスパッタ法を用いて成膜する。プラズマCVD法を用いる場合は基板温度を室温~300 として成膜すればよい。

### [0045]

次いで、下地絶縁膜102上に非晶質半導体膜を公知の技術(スパッタ法、PCVD法、LPCVD法、真空蒸着法、光CVD法等)により形成する。次いで、非晶質半導体膜を公知の技術により結晶化させ、結晶質半導体膜を形成する。

ただし、プラスチック基板を用いた場合、400 を越える熱処理には耐えられないので、レーザー光の照射により結晶化させることが好ましい。なお、レーザー光の照射により結晶化させる場合には、照射する前に非晶質半導体膜の含有水素量を5atom%以下とする必要があるため、成膜直後の段階で水素濃度が低い成膜方法、あるいは成膜条件とすることが好ましい。

[0046]

レーザー光としては、エキシマレーザー等の気体レーザーや、YVO4レーザーやYAGレーザーなどの固体レーザーや、半導体レーザーを用いればよい。また、レーザー発振の形態は、連続発振、パルス発振のいずれでもよく、レーザービームの形状も線状、矩形状、円状、楕円状のいずれでもよい。また、使用する波長は、基本波、第2高調波、第3高調波のいずれでもよい。また、走査方法は、縦方向、横方向、斜め方向のいずれでもよく、さらに往復させてもよい。

[0047]

次いで、結晶質半導体膜をパターニングしてTFTの活性層となる半導体層103を形成する。次いで、半導体層103を覆うゲート絶縁膜104を形成する。(図1(A))ゲート絶縁膜104は、スパッタ法あるいはプラズマCVD法を用いて成膜する。

[0048]

次いで、ゲート絶縁膜上にゲート電極105を形成する。(図1(B))ゲート電極1 05は、スパッタ法で形成した導電膜を所望の形状にパターニングして形成する。

[0049]

次いで、ゲート電極 1 0 5 をマスクとして絶縁膜のエッチングを行い、ゲート絶縁膜 1 0 6 を形成する。(図 1 ( C ))

[0050]

次いで、イオンドーピング法を用いてp型を付与する不純物元素(ボロン)を自己整合的にドーピングする。(図1(D))このドーピングでは、ボロンと同時に水素を添加することが重要であり、ボロン及び水素が添加された半導体領域の上層部分は非晶質化される。例えば、BH、B2Hxを用いてドーピングする。

また、この時の加速電圧は1~20kV程度として行う。なお、ドーピング条件(加速電圧等)を適宜調節することが好ましい。また、ボロンと比較して多く水素が添加するようにドーピング条件(ドーピング処理室の圧力等)を適宜調節とすることが好ましい。

[0051]

次いで、150~300 の熱処理によりソース領域及びドレイン領域の低抵抗化を行う。(図1(E))この低温での熱処理により水素が拡散して、ソース領域またはドレイン領域となる半導体領域107を低抵抗化させる。ただし、ボロンが添加された領域は非晶質状態のままである。この熱処理の温度(300 以下)では、ドーピングにより非晶質化した領域の結晶性は回復しない。

[0052]

次いで、層間絶縁膜110を形成し、ソース領域またはドレイン領域に達するコンタクトホールを形成した後、ソース領域に電気的に接続するソース配線111、ドレイン領域に電気的に接続するドレイン配線112を形成する。

[0053]

次いで、TFT特性を向上させるために水素化処理を行う。この水素化としては、水素雰囲気中での熱処理、あるいは低温でプラズマ水素化を行う。ここでは水素雰囲気中で350、1時間の熱処理を行う。

10

20

30

40

40

#### [0054]

以上の作製工程により、400 以下のプロセス温度でプラスチック基板上にトップゲート型のTFTが完成する。(図1(F))なお、水素化処理でプラズマ水素化を低温で行えば、300 以下のプロセス温度でプラスチック基板上にTFTが完成する。

#### [0055]

こうして得られたTFTのソース領域またはドレイン領域は、非晶質状態であるにも関わらず、そのシート抵抗が非常に低い値を示している。ドーピング直後のシート抵抗は約2k / の値を示すのに対して、低温(250 ~ 350 、4時間)での熱処理後のシート抵抗は、900 / 以下の値を示し、よいものでは約700 / と非常に低い値を示した。

[0056]

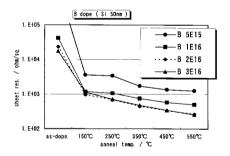

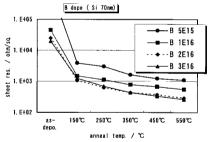

また、以下のような実験を行った。

### [0057]

まず、基板上にアモルファスシリコン膜をスパッタ法で成膜してレーザー処理(X e C 1 レーザ、3 0 H z 、 1 m m / sec )を行い結晶化させたポリシリコン膜にボロンをイオンドープ法を用いて添加した。アモルファスシリコン膜のスパッタ条件は基板温度 1 5 0 、成膜圧力を 0 . 4 P a 、スパッタ電力を 3 k W 、A r 流量を 5 0 s c c m とした。また、水素で希釈されたジボランガスを用い、ドーピングのドーズ量はそれぞれ 5 × 1 0 15 / 1 × 1 0 16 / 1 c 15 / 1 × 1 1 16 / 15 / 15 / 15 / 15 15 / 15 15 / 15 15 / 15 15 / 15 15 / 15 15 / 15 15 / 15 15 / 15 15 / 15 15 / 15 15 / 15 15 / 15 15 / 15 15 / 15 15 / 15 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15 / 15

[0058]

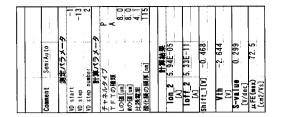

それぞれのドーズ量でボロンが添加されたポリシリコン膜が設けられた基板に150 、250 、350 、450 、550 (比較例)とで条件を振った。また、それぞれの温度で4時間の熱処理を行い、その後でそれぞれの電気抵抗値、ここではシート抵抗値を測定した。

[0059]

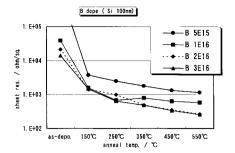

なお、ポリシリコン膜の膜厚が 5 0 n m の測定結果を図 7 に示し、ポリシリコン膜の膜厚が 7 0 n m の測定結果を図 8 に示し、ポリシリコン膜の膜厚が 1 0 0 n m の測定結果を図 9 に示した。

[0060]

図7の測定結果に示したように、熱処理後で抵抗が大きく低減する。熱処理温度を150にした場合で、不純物を添加した半導体領域が急激に低抵抗化している。熱処理前と熱処理後を比較した場合、熱処理後のシート抵抗値は、熱処理前の約半分に低減した。これは、膜中を水素が自由自在に拡散しはじめる温度(水素ガラスの平衡温度(130 付近))によるものだと考えられる。この水素の拡散はダングリングボンド密度が高いほど、不純物元素濃度(ボロン濃度)が高いほど容易に起こる。

[0061]

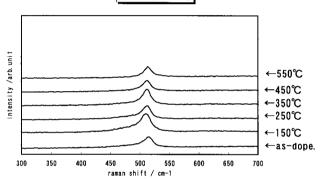

図10は、膜厚50nmのポリシリコン膜にボロンをドーピングした後でのシリコン膜のラマン散乱スペクトルを示す図である。このドーピングされたシリコン膜はTFTを作製した場合におけるソース領域またはドレイン領域と同一と見なせる。波数500~520cm<sup>1</sup>の範囲において、散乱強度に関して極大値を有している。550 以下の加熱では、ほとんどが非晶質であることを示している。このことから、TFTを作製した場合、550 以下の熱処理では、ソース領域及びドレイン領域は再結晶化せず、主に非晶質のままであることが分かる。このように本発明により、ソース領域及びドレイン領域が非晶質であってもシート抵抗値を低くすることができる。

[0062]

本明細書で結晶質とは、シリコン膜のラマン散乱スペクトルにおいて、波数 5 0 0 ~ 5 2 0 c m <sup>- 1</sup>の範囲において強いピークを有した結晶構造を指している。

[0063]

また、150 の熱処理において、時間依存性の実験も行ったところ、初期段階(数分

10

20

30

40

)でシート抵抗値は大きく減少することを見出した。この実験結果より本発明の熱処理(1 0 0 ~ 3 0 0 、好ましくは 1 5 0 ~ 2 5 0 )に必要な時間は数分程度でも十分である。

#### [0064]

また、窒素雰囲気下での熱処理と、水素雰囲気下での熱処理とを比較したところ、水素雰囲気下のほうがシート抵抗値が下がった。 3 5 0 、 4 時間の熱処理を窒素雰囲気下で行ったサンプルのシート抵抗は、 8 3 9 / の値を示したのに対して、 3 5 0 、 4 時間の熱処理を水素雰囲気下で行ったサンプルのシート抵抗は、 5 8 2 / と非常に低い値を示した。

### [0065]

また、イオンドーピング法により不純物元素の添加と同時にプロトンを注入して活性化する技術が特開平6-104280号公報に示されているが、イオンドーピング工程と同時に不純物元素及びプロトンが添加された領域は、最終的には結晶化されて多結晶状態となっており、本発明とは異なっている。また、同公報においては、ドーピング直後でシート抵抗値が低いものとなっており、本発明とは異なっている。本発明において、ドーピング直後のシート抵抗値は約20k / と非常に高い。また、この自己活性化技術は、高いドーズ量及び高い加速電圧によって半導体層が非常に高温となるため、プラスチック基板には不向きである。

## [0066]

また、ドーピング法により不純物原子の添加と同時にシリサイドを形成し、ソース領域及びドレイン領域を低抵抗化させる技術が特開平8-181302号公報に示されているが、同様に不純物元素が添加された領域は、結晶化されて多結晶状態となっており、本発明とは異なっている。同公報においては、ドーピング直後でシート抵抗値が低いものとなっており、本発明とは異なっている。また、本発明において、ドーピング直後のシート抵抗値は約20k / と非常に高い。また、シリサイドを形成するため、シリサイドを形成する金属元素が原因となるTFT特性の低下が懸念される。

### [0067]

また、従来のレーザー活性化とは異なり、本発明の低温(350 以下)での熱処理は、一度に大量の基板を処理することができるのでスループットが向上する。

## [0068]

また、本発明は図1の構造に限定されず、必要があればチャネル形成領域とドレイン領域(またはソース領域)との間にLDD領域を有する低濃度ドレイン(LDD:Lightly Doped Drain)構造としてもよい。この構造はチャネル形成領域と、高濃度に不純物元素を添加して形成するソース領域またはドレイン領域との間に低濃度に不純物元素を添加した領域を設けたものであり、この領域をLDD領域と呼んでいる。さらにゲート絶縁膜を介してLDD領域をゲート電極と重ねて配置させた、いわゆるGOLD(Gate-drain Ove rlapped LDD)構造としてもよい。また、これらのLDD領域またはGOLD領域に水素元素を高濃度に含む領域または層を形成してもよい。

#### [0069]

以上の構成でなる本発明について、以下に示す実施例でもってさらに詳細な説明を行うこととする。

#### 【 実 施 例 1 】

### [0070]

本発明では350 以下の低温プロセスで画素部および駆動回路をすべてpチャネルTFTで形成することを特徴としている。そこで、本実施例ではプラスチック基板上に画素TFTを形成する作製工程について以下に説明する。

#### [0071]

まず、有機物からなるプラスチック基板 2 0 1 を用意する。本実施例では、ポリイミドからなる基板 2 0 1 を用いる。このポリイミドからなる基板の耐熱温度は約 3 9 9 であり、基板自体の色は透明ではなく、褐色である。次いで、基板 2 0 1 上に下地絶縁膜 2 0

10

20

30

40

2 を形成する。この下地絶縁膜はプロセス温度が 3 0 0 を越えない成膜方法であれば特に限定されず、ここではスパッタ法を用いて形成した。

#### [0072]

次いで、非晶質半導体膜を形成し、レーザー照射により結晶化させて結晶質半導体膜を形成する。非晶質半導体膜はプロセス温度が300 を越えない成膜方法であれば特に限定されず、ここではスパッタ法を用いて形成した。次いで、結晶質半導体膜を所望の形状にパターニングして半導体層203を形成する。次いで、半導体層203を覆うゲート絶縁膜204を形成する。ゲート絶縁膜はプロセス温度が300 を越えない成膜方法であれば特に限定されず、ここではスパッタ法を用いて形成した。(図2(A))

### [0073]

次いで、ゲート電極205を形成する。(図2(B))ゲート電極205としては、Ta、W、Ti、Mo、A1、Cu、Cr、Ndから選ばれた元素、または前記元素を主成分とする合金材料若しくは化合物材料で形成してもよい。また、リン等の不純物元素をドーピングした多結晶シリコン膜に代表される半導体膜を用いてもよい。また、AgPdCu合金を用いてもよい。

#### [0074]

次いで、ゲート電極をマスクとしてゲート絶縁膜を自己整合的にエッチングしてゲート 絶縁膜206を形成するとともに、半導体層の一部を露呈させてから半導体層の一部にp 型を付与する不純物元素、ここではボロンを添加(ドーピング)して不純物領域207を 形成する。(図2(C))

#### [0075]

本実施例ではゲート絶縁膜のエッチングを行った後にドーピングを行ったが、ゲート電極を形成した後、ゲート絶縁膜を通過させてドーピングを行ってもよい。この場合、不純物元素はゲート絶縁膜を通過し、ゲート電極をマスクとして自己整合的にドーピングされる。

### [0076]

次いで、 1 5 0 ~ 3 5 0 、少なくとも 2 分、マージンを考えると 1 0 分以上の熱処理を行って、半導体層に含まれる水素の作用によりシート抵抗の低い不純物領域 2 0 8 を形成する。(図 2 ( D ) )

### [0077]

次いで、層間絶縁膜210を形成し、ソース領域またはドレイン領域に達するコンタクトホールを形成した後、ソース領域に電気的に接続するソース配線211、ドレイン領域に電気的に接続する画素電極212を形成する。

### [0078]

次いで、TFT特性を向上させるために水素化処理を行う。この水素化としては、水素雰囲気中での熱処理(350 、1時間)、あるいは低温でプラズマ水素化を行う。

#### [0079]

以上の作製工程により、400 以下のプロセス温度でプラスチック基板上にトップゲート型のTFTが完成する。(図2(E))本実施例に従って完成したTFTのソース領域及びドレイン領域は、主に非晶質であるのにシート抵抗値が約680 と非常に低い値となった。なお、必要があれば無機絶縁膜からなるパッシベーション膜を形成してもよい

### [0800]

本実施例に従って完成したTFT(シングルゲート構造)の電気的特性は、良好な値を示した。図18にそのTFT特性(V-I特性)を示す。また、V-I特性グラフにおける立ち上がり点での電圧値を示すしきい値(Vth)は、-2.644Vとなっている。また、S値は0.299(V/dec)、移動度(μ<sub>FE</sub>)は72.5(cm²/Vs)と優れたものとなっている。

### [0081]

この後、配向膜216a形成、ラビング処理、配向膜216bと対向電極215を備え

10

20

30

40

た対向基板 2 1 4 の貼り合わせ、液晶 2 1 3 注入等の工程を経て反射型液晶表示装置が完成する。

### [0082]

ここでは、画素電極212として、反射性を有する金属材料、例えばA1、Ag等を主成分とする材料を用いた。なお、本実施例では反射型の液晶表示装置の例を示したが、画素電極として透明導電膜、例えばITO(酸化インジウム酸化スズ合金)、酸化インジウム酸化亜鉛合金(In₂O₃ ZnO)、酸化亜鉛(ZnO)等を用いれば透過型液晶表示装置を形成することができる。

### [0083]

本実施例で示す P チャネル型 T F T を用いて基本論理回路を構成したり、さらに複雑なロジック回路(信号分割回路、オペアンプ、 補正回路など)をも構成することができる

#### [0084]

なお、本実施例に示すTFTは、チャネル形成領域となる半導体に周期表の15族に属する元素(好ましくはリン)もしくは周期表の13族に属する元素(好ましくはボロン)を添加することによりエンハンスメント型とデプレッション型とを作り分けることができる。

#### [0085]

また、Pチャネル型TFTを組み合わせてPMOS回路を形成する場合、エンハンスメント型TFT同士で形成する場合(以下、EEMOS回路という)と、エンハンスメント型とデプレッション型とを組み合わせて形成する場合(以下、EDMOS回路という)がある。これらの回路を組み合わせて、液晶表示装置の駆動回路を全てPチャネル型TFTで構成することも可能である。

#### 【実施例2】

#### [0086]

本実施例では、水素化での熱処理の際、同時に不純物領域の低抵抗化を行う例を図3に示す。なお、ドーピング工程までは実施例1と同一であるため、詳細な説明は省略する。

#### [0087]

まず、実施例1に従って、基板301上に下地絶縁膜302、半導体層303、ゲート 絶縁膜304を形成する。(図3(A))次いで、実施例1と同様に、ゲート電極305 を形成する。(図3(B))。次いで、実施例1と同様に、エッチングしてゲート絶縁膜306を形成する。(図3(C))。

#### [ 0 0 8 8 ]

次いで、実施例 1 と同様に、ゲート電極 3 0 5 をマスクとして自己整合的に不純物元素 を添加して不純物領域を形成する。(図 3 ( D ))

#### [0089]

次いで、熱処理を行わずに層間絶縁膜310を形成し、ソース領域またはドレイン領域に達するコンタクトホールを形成した後、ソース領域に電気的に接続するソース配線31 1、ドレイン領域に電気的に接続するドレイン電極312を形成する。

#### [0090]

次いで、TFT特性を向上させるために水素化処理を行う。この水素化としては、水素雰囲気中での熱処理(350 、1~4時間)を行う。この水素化と同時にソース領域及びドレイン領域の低抵抗化も行われる。本実施例(水素雰囲気中で350 、4時間の熱処理)に従って完成したTFTのソース領域及びドレイン領域は、主に非晶質であるのにシート抵抗値が約580k と非常に低い値となった。

## [0091]

こうして、低温での熱処理でソース領域及びドレイン領域の低抵抗化が可能であることから、活性化のためだけに行われていた熱処理工程を省略し、水素化と同時にソース領域 及びドレイン領域の低抵抗化させることができた。

### [0092]

50

10

20

30

なお、本実施例では水素化と同時にソース領域及びドレイン領域の低抵抗化を行った例を示したが、特に限定されず、ドーピング工程以降の工程のうち、100~300、好ましくは150~250 の熱処理が加えられる工程(例えば、層間絶縁膜の成膜、パッシベーション膜の成膜等)と同時に行うことが可能である。

### 【実施例3】

### [0093]

実施例1では、TFTとしてトップゲート構造のTFT(具体的にはプレーナ型TFT)を例示したが、本発明はTFT構造に限定されるものではなく、ボトムゲート構造のTFTにも実施できる。

#### [0094]

本実施例では、代表的には逆スタガTFTに実施する例を図4に示す。

#### [0095]

まず、有機物からなるプラスチック基板 4 0 0 を用意する。なお、基板からの不純物の拡散を防止してTFTの電気特性を向上させるための下地絶縁膜 4 0 1 を設ける。その下地絶縁膜の材料としては、酸化シリコン膜、窒化シリコン膜、窒化酸化シリコン膜(SiOx Ny )、またはこれらの積層膜等を 1 0 0 ~ 5 0 0 n m の膜厚範囲で用いることができ、形成手段としては熱 C V D 法、プラズマ C V D 法、蒸着法、スパッタ法、減圧熱 C V D 法等の形成方法を用いることができる。

### [0096]

次いで、単層構造または積層構造を有するゲート配線(ゲート電極含む)402を形成する。ゲート配線402の形成手段としては熱CVD法、プラズマCVD法、減圧熱CVD法、蒸着法、スパッタ法等を用いて10~1000nm、好ましくは30~300nmの膜厚範囲の導電膜を形成した後、公知のパターニング技術で形成する。また、ゲート配線402の材料としては、導電性材料または半導体材料を主成分とする材料、例えばTa(タンタル)、Mo(モリブデン)

、Ti(チタン)、W(タングステン)、クロム(Cr)等の高融点金属材料、これら金属材料とシリコンとの化合物であるシリサイド、N型又はP型の導電性を有するポリシリコン等の材料、低抵抗金属材料Cu(銅)、Al(アルミニウム)等を主成分とする材料層を少なくとも一層有する構造であれば特に限定されることなく用いることができる。

### [0097]

次いで、ゲート絶縁膜を形成する。ゲート絶縁膜としては、酸化シリコン膜、窒化シリコン膜、窒化酸化シリコン膜(SiOx Ny)、有機樹脂膜(BCB(ベンゾシクロブテン)膜)、またはこれらの積層膜等を100~400nmの膜厚範囲で用いることができる。下地膜の形成手段としては熱CVD法、プラズマCVD法、減圧熱CVD法、蒸着法、スパッタ法、塗布法等の形成方法を用いることができる。ここでは図4(A)に示すように、積層構造のゲート絶縁膜403a、403bを用いた。下層のゲート絶縁膜403aは、基板やゲート配線からの不純物の拡散を効果的に防止する窒化シリコン膜等を膜厚10nm~60nmの膜厚範囲で形成する。

### [0098]

次いで、非晶質半導体膜を成膜する。非晶質半導体膜404としては、シリコンを主成分とする非晶質シリコン膜を20~100nm、より好ましくは20~60nmの膜厚範囲で用いることができる。非晶質半導体膜の形成手段としては熱CVD法、プラズマCVD法、減圧熱CVD法、蒸着法、スパッタ法等の形成方法を用いることができる。

### [0099]

なお、上記ゲート絶縁膜403a、403bと非晶質半導体膜とを大気にさらすことなく連続成膜すれば、不純物がゲート絶縁膜と非晶質半導体膜との界面に混入しないため良好な界面特性を得ることができる。

### [0100]

次いで、非晶質半導体膜の結晶化処理を行い、結晶質半導体膜を形成した後、得られた 結晶質半導体膜を所望の形状にパターニングする。(図4(A))なお、半導体膜のパタ 10

20

30

40

ーニングを行う工程順序は特に限定されず、例えば不純物元素の添加後に行ってもよい。結晶化処理としては、レーザー光の照射による結晶化方法を用いればよい。また、この結晶化処理の直前に非晶質半導体膜表面の自然酸化膜をバッファーフッ酸等のフッ酸系のエッチャントで除去すると、表面付近のシリコンの結合手が水素終端されて不純物と結合しにくくなり、良好な結晶質半導体膜を形成することができるため好ましい。

### [0101]

次いで、結晶質半導体層404上に絶縁層405を形成する。この絶縁層405は不純物元素の添加工程時にチャネル形成領域を保護する。この絶縁層405としては、酸化シリコン膜、窒化シリコン膜、窒化シリコン膜(SiOx Ny)、有機樹脂膜(BCB膜)、またはこれらの積層膜等を100~400nmの膜厚範囲で用いることができる。絶縁層405は、公知のパターニング技術、例えば通常の露光や裏面露光等を用いて形成する。(図4(B))

[0102]

次いで、絶縁層405をマスクに用いて、結晶質半導体膜にp型を付与する不純物元素を添加するドーピング工程を行ない、不純物領域406を形成する。(図4(C))半導体材料に対してp型を付与する不純物元素としては、15族に属する不純物元素、例えばBを用いることができる。この工程では、プラスマドーピング法によりドーピング条件(ドーズ量、加速電圧等)を適宜設定して表面が露出している結晶質半導体膜にB(ボロン)を添加する。他のドーピング方法としてイオン注入法を用いることもできる。また、この不純物領域406は高濃度不純物領域であり、後のソース/ドレイン領域となる。

[ 0 1 0 3 ]

次いで、熱処理(150~350 、1時間以上)を行って、半導体層に含まれる水素の作用によりシート抵抗の低い不純物領域407を形成する。本実施例に従って完成した TFTのソース領域及びドレイン領域は、主に非晶質であるのにシート抵抗値が約5k と非常に低い値となった。

[0104]

次いで、全面に層間絶縁膜408を形成する。層間絶縁膜408としては酸化シリコン膜、窒化シリコン膜、酸化窒化シリコン膜、有機性樹脂膜(ポリイミド膜、BCB膜等)のいずれか或いはそれらの積層膜を用いることができる。

[0105]

次いで、公知の技術を用いてコンタクトホールを形成した後、配線409、410を形成して、図4(F)に示す状態を得る。この配線409、410はソース配線またはドレイン配線として機能する。最後に水素雰囲気中で熱処理を行い、全体を水素化してPチャネル型TFTが完成する。

[0106]

また、上記本実施例においては、活性層のパターニングを絶縁層405の形成前に行う例を示したが、特に限定されず、例えば結晶化工程前、またはドーピング前、または熱処理の後に行ってもよい。

[0107]

また、上記本実施例においてチャネル形成領域へ微量な不純物元素の添加を行ない、TFTのしきい値制御を行う工程(チャネルドーピング工程とも呼ぶ)を加えてもよい。

[0108]

また、本実施例は実施例2と組み合わせることができる。

【実施例4】

[0109]

実施例1乃至3のいずれか一により得られるアクティブマトリクス基板を用いて液晶表示パネルを作製する例を以下に示す。

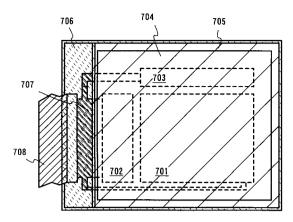

[0110]

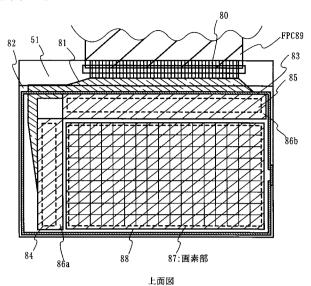

図 5 に示す上面図は、画素部、駆動回路、FPC(フレキシブルプリント配線板:Flex ible Printed Circuit)を貼り付ける外部入力端子、外部入力端子と各回路の入力部まで

10

20

30

40

を接続する配線 8 1 などが形成されたアクティブマトリクス基板と、カラーフィルタなどが設けられた対向基板 8 2 とがシール材 8 3 を介して貼り合わされている。

#### [0111]

ゲート側駆動回路84と重なるように対向基板側に遮光層86aが設けられ、ソース側駆動回路85と重なるように対向基板側に遮光層86bが形成されている。また、画素部87上の対向基板側に設けられたカラーフィルタ88は遮光層と、赤色(R)、緑色(G)、青色(B)の各色の着色層とが各画素に対応して設けられている。実際に表示する際には、赤色(R)の着色層、緑色(G)の着色層、青色(B)の着色層の3色でカラー表示を形成するが、これら各色の着色層の配列は任意なものとする。

### [0112]

ここでは、カラー化を図るためにカラーフィルタ88を対向基板に設けているが特に限定されず、アクティブマトリクス基板を作製する際、アクティブマトリクス基板にカラーフィルタを形成してもよい。

### [0113]

また、カラーフィルタにおいて隣り合う画素の間には遮光層が設けられており、表示領域以外の箇所を遮光している。また、ここでは、駆動回路を覆う領域にも遮光層86a、86bを設けているが、駆動回路を覆う領域は、後に液晶表示装置を電子機器の表示部として組み込む際、カバーで覆うため、特に遮光層を設けない構成としてもよい。また、アクティブマトリクス基板を作製する際、アクティブマトリクス基板に遮光層を形成してもよい。

#### [0114]

また、上記遮光層を設けずに、対向基板と対向電極の間に、カラーフィルタを構成する着色層を複数層重ねた積層で遮光するように適宜配置し、表示領域以外の箇所(各画素電極の間隙)や、駆動回路を遮光してもよい。

#### [ 0 1 1 5 ]

また、外部入力端子にはベースフィルムと配線から成るFPC89が異方性導電性樹脂で貼り合わされている。さらに補強板で機械的強度を高めている。

#### [0116]

以上のようにして作製される液晶表示装置は各種電子機器の表示部として用いることができる。

#### [0117]

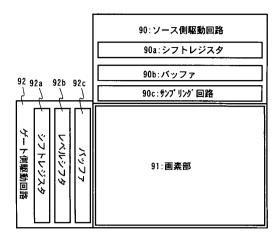

また、上記液晶表示装置におけるブロック図を図6に示す。なお、図6はアナログ駆動を行うための回路構成である。本実施例では、ソース側駆動回路90、画素部91及びゲート側駆動回路92を有している。なお、本明細書中において、駆動回路とはソース側処理回路およびゲート側駆動回路を含めた総称である。

### [0118]

ソース側駆動回路 9 0 は、シフトレジスタ 9 0 a、バッファ 9 0 b、サンプリング回路 (トランスファゲート) 9 0 cを設けている。また、ゲート側駆動回路 9 2 は、シフトレジスタ 9 2 a、レベルシフタ 9 2 b、バッファ 9 2 cを設けている。また、必要であればサンプリング回路とシフトレジスタとの間にレベルシフタ回路を設けてもよい。

## [0119]

また、本実施例において、画素部91は複数の画素を含み、その複数の画素に各々TFT 素子が設けられている。

## [0120]

これらソース側駆動回路90およびゲート側駆動回路92は全てPチャネル型TFTで 形成され、全ての回路はEEMOS回路を基本単位として形成されている。ただし、従来 のCMOS回路に比べると消費電力は若干上がってしまう。

#### [0121]

なお、図示していないが、画素部 9 1 を挟んでゲート側駆動回路 9 2 の反対側にさらに ゲート側駆動回路を設けても良い。 10

20

30

40

#### [ 0 1 2 2 ]

また、本実施例は実施例1乃至3のいずれかーと自由に組み合わせることができる。

#### 【実施例5】

#### [ 0 1 2 3 ]

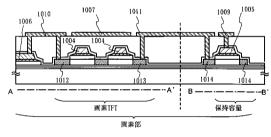

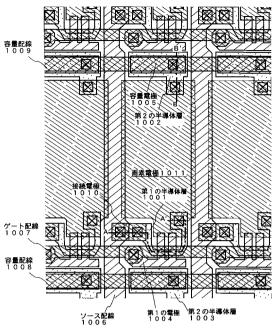

本実施例では画素構造を図11に示し、断面構造を図12に示す。それぞれ、A-A'断面図、B-B'断面図を示した。

#### [0124]

本実施例では保持容量は、第2の半導体層1002上の絶縁膜を誘電体として、第2の半導体層1002と、容量電極1005とで形成している。なお、容量電極1005は、容量配線1009と接続されている。また、容量電極1005は、第1の電極1004及びソース配線1006と同じ絶縁膜上に同時に形成される。また、容量配線は、画素電極1011、接続電極1010、ゲート配線1007と同じ絶縁膜上に同時に形成される。

### [0125]

また、本実施例では、不純物領域 1 0 1 2 ~ 1 0 1 4 には p 型を付与する不純物元素が添加されている。なお、 1 0 1 2 はソース領域、 1 0 1 3 はドレイン領域である。

#### [0126]

また、本実施例では、ゲート電極とソース配線を同時に形成する例を示したが、マスクを 1 枚増やし、さらにゲート電極と第 1 の電極及び容量配線を別の工程で形成してもよい。即ち、まず、半導体層と重なりゲート電極となる部分だけを形成し、 p 型の不純物元素を添加し、低温での熱処理を行った後、ゲート電極と重ねて第 1 の電極を形成する。この際、コンタクトホールの形成を行うことなく、単なる重ね合わせでゲート電極と第 1 の電極とのコンタクトを形成する。また、第 1 の電極と同時にソース配線、容量配線を形成する。こうすることによって第 1 の電極及びソース配線の材料として低抵抗なアルミニウムや銅を用いることが可能となる。また、容量配線に重なる半導体層に p 型の不純物元素を添加して保持容量の増加を図ることができる。

#### [0127]

なお、本実施例は実施例1乃至4のいずれか一と自由に組み合わせることができる。

#### 【実施例6】

## [0128]

本実施例は、上記実施例3で得られるTFTを用いてEL(エレクトロルミネセンス)表示装置を作製した例について図13を用い、以下に説明する。なお、本実施例は、画素部及び駆動回路に使用するTFTを全てPチャネル型TFTで構成したEL表示装置の例である。

### [0129]

同一の絶縁体上に画素部とそれを駆動する駆動回路を有した発光装置の例(但し封止前の状態)を図13に示す。なお、駆動回路には基本単位となるMOS回路を示し、画素部には一つの画素を示す。

#### [0130]

図 1 3 において、 1 5 0 1 はプラスチック基板であり、まず、実施の形態に従い、プラスチック基板 1 5 0 1 上に下地絶縁膜を形成する。

## [0131]

下地絶縁膜上にはPチャネル型TFT1504、Pチャネル型TFT1505からなる駆動回路、Pチャネル型TFTからなるスイッチングTFT1506およびPチャネル型TFTからなる電流制御TFT1507が形成されている。なお、Pチャネル型TFTの説明は実施例1を参照すれば良いので省略する。また、本実施例では、TFTはすべてボトムゲート型TFTで形成されている。

#### [0132]

また、スイッチングTFTはソース領域およびドレイン領域の間に二つのチャネル形成領域を有した構造(ダブルゲート構造)となっているが、特に限定されることなく、チャネル形成領域が一つ形成されるシングルゲート構造もしくは三つ形成されるトリプルゲート

10

20

30

40

構造であっても良い。

### [0133]

また、電流制御TFTのドレイン領域の上には第2層間絶縁膜が設けられる前に、第1層間絶縁膜にコンタクトホールが設けられている。これは第2層間絶縁膜にコンタクトホールを形成する際に、エッチング工程を簡単にするためである。

第2層間絶縁膜にはドレイン領域に到達するようにコンタクトホールが形成され、ドレイン領域に接続された画素電極が設けられている。画素電極はEL素子の陰極として機能する電極であり、周期表の1族もしくは2族に属する元素を含む導電膜を用いて形成されている。本実施例では、リチウムとアルミニウムとの化合物からなる導電膜を用いる。

### [0134]

また、画素電極の端部を覆うように設けられた絶縁膜を本明細書中ではバンクと呼ぶ。バンクは珪素を含む絶縁膜もしくは樹脂膜で形成すれば良い。樹脂膜を用いる場合、樹脂膜の比抵抗が  $1\times10^6\sim1\times10^{12}$  m (好ましくは  $1\times10^8\sim1\times10^{10}$  m)となるようにカーボン粒子もしくは金属粒子を添加すると、成膜時の絶縁破壊を抑えることができる。

#### [ 0 1 3 5 ]

また、EL素子1505は画素電極(陰極)、EL層および陽極からなる。陽極は、仕事関数の大きい導電膜、代表的には酸化物導電膜が用いられる。酸化物導電膜としては、酸化インジウム、酸化スズ、酸化亜鉛もしくはそれらの化合物を用いれば良い。

#### [0136]

なお、本明細書中では発光層に対して正孔注入層、正孔輸送層、正孔阻止層、電子輸送層 、電子注入層もしくは電子阻止層を組み合わせた積層体をEL層と定義する。

#### [0137]

なお、ここでは図示しないが陽極を形成した後、EL素子1505を完全に覆うようにしてパッシベーション膜を設けることは有効である。パッシベーション膜としては、炭素膜、窒化珪素膜もしくは窒化酸化珪素膜を含む絶縁膜からなり、該絶縁膜を単層もしくは組み合わせた積層で用いる。

#### [0138]

次いで、EL素子を保護するための封止(または封入)工程まで行った。その後のEL表示装置について図14を用いて説明する。

#### [0139]

図 1 4 は、 E L 素子の封止までを行った状態を示す上面図である。点線で示された 7 0 1 は画素部、 7 0 2 はソース側駆動回路、 7 0 3 はゲート側駆動回路である。また、 7 0 4 はカバー材、 7 0 5 は第 1 シール材、 7 0 6 は第 2 シール材である。

### [0140]

なお、708はソース側駆動回路702及びゲート側駆動回路703に入力される信号を伝送するための配線であり、外部入力端子となるFPC(フレキシブルプリントサーキット)708からビデオ信号やクロック信号を受け取る。なお、ここではFPCしか図示されていないが、このFPCにはプリント配線基盤(PWB)が取り付けられていても良い

## [0141]

また、Pチャネル型TFTのみでゲート側駆動回路およびソース側駆動回路を形成することにより画素部および駆動回路をすべてpチャネル型TFTで形成することが可能となる。従って、アクティブマトリクス型の電気光学装置を作製する上でTFT工程の歩留まりおよびスループットを大幅に向上させることができ、製造コストを低減することが可能となる。

#### [0142]

なお、ソース側駆動回路もしくはゲート側駆動回路のいずれか片方を外付けのICチップとする場合にも本実施例は実施できる。

### [0143]

50

10

20

30

また、本実施例は、上方に発光する例を示したが、EL素子の構成を適宜変更して下方に発光する構造としてもよい。

### [0144]

なお、本実施例は、実施例1、実施例2と自由に組み合わせることが可能である。また、本実施例では逆スタガ型TFTを用いたが特に限定されず、実施例1に示したようなトップゲート型TFTを用いることもできる。

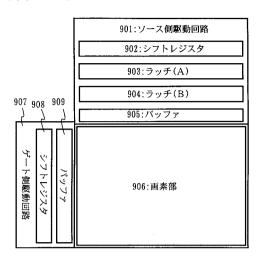

#### 【実施例7】

### [0145]

本実施例では実施例6に示したEL表示装置の回路構成例を図15に示す。なお、本実施例ではデジタル駆動を行うための回路構成を示す。本実施例では、ソース側駆動回路901、画素部906及びゲート側駆動回路907を有している。なお、本明細書中において、駆動回路とはソース側処理回路およびゲート側駆動回路を含めた総称である。

#### [ 0 1 4 6 ]

ソース側駆動回路 9 0 1 は、シフトレジスタ 9 0 2 、ラッチ( A ) 9 0 3 、ラッチ( B ) 9 0 4 、バッファ 9 0 5 を設けている。なお、アナログ駆動の場合はラッチ( A ) 、( B ) の代わりにサンプリング回路(トランスファゲート)を設ければ良い。また、ゲート側駆動回路 9 0 7 は、シフトレジスタ 9 0 8 、バッファ 9 0 9 を設けている。

#### [0147]

また、本実施例において、画素部906は複数の画素を含み、その複数の画素にEL素子が設けられている。このとき、EL素子の陰極は電流制御TFTのドレインに電気的に接続されていることが好ましい。

#### [ 0 1 4 8 ]

なお、図示していないが、画素部906を挟んでゲート側駆動回路907の反対側にさらにゲート側駆動回路を設けても良い。この場合、双方は同じ構造でゲート配線を共有しており、片方が壊れても残った方からゲート信号を送って画素部を正常に動作させるような構成とする。

### 【実施例8】

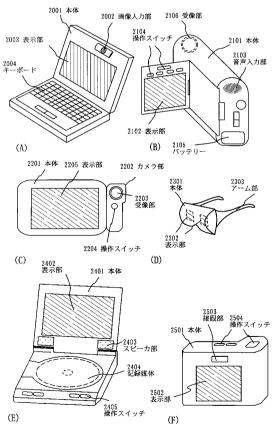

#### [0149]

本発明を実施して形成された駆動回路や画素部は様々な電気光学装置(アクティブマトリクス型液晶ディスプレイ、アクティブマトリクス型 ELディスプレイ、アクティブマトリクス型 ECディスプレイ)に用いることができる。即ち、それら電気光学装置を表示部に組み込んだ電子機器全てに本発明を実施できる。

#### [0150]

その様な電子機器としては、ビデオカメラ、デジタルカメラ、ヘッドマウントディスプレイ(ゴーグル型ディスプレイ)、カーナビゲーション、カーステレオ、パーソナルコンピュータ、携帯情報端末(モバイルコンピュータ、携帯電話または電子書籍等)などが挙げられる。それらの一例を図16及び図17に示す。

#### [0151]

図16(A)はパーソナルコンピュータであり、本体2001、画像入力部2002、表示部2003、キーボード2004等を含む。本発明を画像入力部2002、表示部2003やその他の駆動回路に適用することができる。

#### [0152]

図 1 6 ( B ) はビデオカメラであり、本体 2 1 0 1 、表示部 2 1 0 2 、音声入力部 2 1 0 3 、操作スイッチ 2 1 0 4 、バッテリー 2 1 0 5 、受像部 2 1 0 6 等を含む。本発明を表示部 2 1 0 2 やその他の駆動回路に適用することができる。

## [ 0 1 5 3 ]

図 1 6 ( C ) はモバイルコンピュータ(モービルコンピュータ)であり、本体 2 2 0 1 、カメラ部 2 2 0 2 、受像部 2 2 0 3 、操作スイッチ 2 2 0 4 、表示部 2 2 0 5 等を含む。本発明は表示部 2 2 0 5 やその他の駆動回路に適用できる。

### [0154]

50

10

20

30

10

20

30

図 1 6 ( D ) はゴーグル型ディスプレイであり、本体 2 3 0 1 、表示部 2 3 0 2 、アーム部 2 3 0 3 等を含む。本発明は表示部 2 3 0 2 やその他の駆動回路に適用することができる。

[0155]

図16(E)はプログラムを記録した記録媒体(以下、記録媒体と呼ぶ)を用いるプレーヤーであり、本体2401、表示部2402、スピーカ部2403、記録媒体2404、操作スイッチ2405等を含む。なお、このプレーヤーは記録媒体としてDVD(Digtial Versatile Disc)、CD等を用い、音楽鑑賞や映画鑑賞やゲームやインターネットを行うことができる。本発明は表示部2402やその他の駆動回路に適用することができる。

[0156]

図16(F)はデジタルカメラであり、本体2501、表示部2502、接眼部2503、操作スイッチ2504、受像部(図示しない)等を含む。本発明を表示部2502やその他の駆動回路に適用することができる。

[0157]

図17(A)は携帯電話であり、本体2901、音声出力部2902、音声入力部2903、表示部2904、操作スイッチ2905、アンテナ2906等を含む。本発明を表示部2904やその他の駆動回路に適用することができる。

[0158]

図 1 7 ( B ) は携帯書籍(電子書籍)であり、本体 3 0 0 1 、表示部 3 0 0 2 、 3 0 0 3 、記憶媒体 3 0 0 4 、操作スイッチ 3 0 0 5 、アンテナ 3 0 0 6 等を含む。本発明は表示部 3 0 0 2 、 3 0 0 3 やその他の駆動回路に適用することができる。

[0159]

図17(C)はディスプレイであり、本体3101、支持台3102、表示部3103 等を含む。本発明は表示部3103に適用することができる。本発明のディスプレイは特に大画面化した場合において有利であり、対角10インチ以上(特に30インチ以上)のディスプレイには有利である。

[0160]

以上の様に、本発明の適用範囲は極めて広く、あらゆる分野の電子機器に適用することが可能である。また、本実施例の電子機器は実施例 1 ~ 7 のどのような組み合わせからなる構成を用いても実現することができる。

### 【図1】

## 【図2】

## 【図3】

## 【図4】

【図5】

【図6】

【図7】

【図8】

Si 50nm, B 70sccm, 5uA, 10kV

|          | B 5E15    | B 1E16    | B 2E16    | B 3E16    |

|----------|-----------|-----------|-----------|-----------|

| as-dope. | 1. 26E+06 | 4. 18E+04 | 2. 33E+04 | 1. 75E+04 |

| 150℃     | 3. 58E+03 | 1. 17E+03 | 9. 56E+02 | 1. 14E+03 |

| 250℃     | 3. 39E+03 | 1. 07E+03 | 6. 90E+02 | 7. 05E+02 |

| 350℃     | 1. 71E+03 | 7. 46E+02 | 4. 45E+02 | 4. 74E+02 |

| 450°C    | 1. 34E+03 | 5. 75E+02 | 3. 37E+02 | 3. 40E+02 |

| 550℃     | 1. 25E+03 | 4. 97E+02 | 2. 62E+02 | 2. 55E+02 |

| _3 | i runma, B | IUSCCM, SUA, | IUK¥      |           |           |

|----|------------|--------------|-----------|-----------|-----------|

| Е  |            | B 5E15       | B 1E16    | B 2E16    | B 3E16    |

|    | as-depo.   | 1. 06E+06    | 4. 52E+04 | 2. 50E+04 | 1. 98E+04 |

|    | 150°C      | 3. 90E+03    | 1. 48E+03 | 1. 07E+03 | 1. 24E+03 |

|    | 250°C      | 3. 02E+03    | 1. 11E+03 | 6. 20E+02 | 6. 89E+02 |

|    | 350℃       | 1. 61E+03    | 7. 72E+02 | 4. 32E+02 | 4. 30E+02 |

| Г  | 450°C      | 1. 22E+03    | 6. 70E+02 | 3. 69E+02 | 3. 33E+02 |

| -  | EEU OC     | 1 005103     | E 47E LOG | 2 075102  | 2 615100  |

## 【図9】

#### Si 100nm, B 70sccm, 5uA, 10kV

|          | B 5E15    | B 1E16    | B 2E16    | B 3E16    |

|----------|-----------|-----------|-----------|-----------|

| as-depo. | 1. 15E+06 | 3. 94E+04 | 2. 15E+04 | 1. 42E+04 |

| 150℃     | 3. 80E+03 | 1. 59E+03 | 1. 42E+03 | 1. 47E+03 |

| 250℃     | 2. 52E+03 | 6. 71E+02 | 9. 93E+02 | 6. 37E+02 |

| 350℃     | 1. 80E+03 | 7. 91E+02 | 4. 88E+02 | 4. 82E+02 |

| 450°C    | 1. 33E+03 | 6. 31E+02 | 3. 47E+02 | 3. 35E+02 |

| 550°C    | 1. 15E+03 | 5. 83E+02 | 2. 62E+02 | 2. 55E+02 |

## 【図10】

## Bドープ ( Si 50nm)

## 【図12】

## 【図11】

## 【図13】

【図14】

【図15】

【図16】

【図17】

# 【図18】

### フロントページの続き

(51) Int.CI. F I テーマコード (参考)

H 0 1 L 29/78 6 2 7 E H 0 1 L 21/265 F

Fターム(参考) 5F110 AA17 BB02 BB03 CC02 CC08 DD01 DD12 DD13 DD14 DD15

EE02

EE03

EE04

EE05

EE06

EE09

EE14

EE28

EE43

EE44

EE45

FF01

FF02

FF03

FF04

FF09

FF28

FF30

GG02

GG06

GG13

GG25

GG42

GG43

GG45

GG47

GG48

HJ01

HJ12

HJ13

HJ22

HL02

HL03

HL07

HM07

HM15

NN02

NN03

NN12

NN14

NN22

NN23

NN24

NN27

NN72

NN73

PP03

PP04

PP06

QQ09

QQ11 QQ12 QQ24 QQ25