#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

# (19) World Intellectual Property **Organization**

International Bureau

(10) International Publication Number WO 2017/196369 A1

(51) International Patent Classification: G11C 13/00 (2006.01)

G11C 14/00 (2006.01)

(21) International Application Number:

PCT/US2016/032428

(22) International Filing Date:

13 May 2016 (13.05.2016)

(25) Filing Language:

**English**

(26) Publication Language:

English

(54) Title: STATIC RANDOM ACCESS MEMORIES WITH PROGRAMMABLE IMPEDANCE ELEMENTS AND METHODS

- (71) Applicant: ADESTO TECHNOLOGIES CORPO-RATION [US/US]; 1250 Borregas Ave, Sunnyvale, California 94089 (US).

- (72) Inventors: GOPINATH, Venkatesh; 47636 Pima Street, Fremont, California 94539 (US). GONZALES, Nathan; 7210 Chantilley Ct, San Jose, California 95139 (US).

- (74) Agent: SAKO, Bradley; P.O. Box 2008, Livermore, California 94551-2008 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, JP, KE, KG, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, ST, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK,

AND DEVICES INCLUDING THE SAME

EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

#### **Published:**

with international search report (Art. 21(3))

WO 2017/196369 A1 |||

208 204 (+V)  $\S \nabla$ 8 FIG. 2 M22 M20 206' 206 202 (GND) BLB

(57) Abstract: An integrated circuit device can include a plurality of SRAM cells, each including a pair of latching devices having controllable current paths connected to first and second latching nodes, and control terminals cross-coupled between the first and second data latching nodes, and first and second resistive elements disposed over the latching devices that are conductively connected to the first and second data latching nodes by first and second vertical connections; wherein each resistive element comprises at least one memory layer that is capable of being re-programmed between at least a high and lower resistance state by application of electric fields, the resistive elements having only the high resistance state to store data in a volatile manner in the SRAM cells.

# STATIC RANDOM ACCESS MEMORIES WITH PROGRAMMABLE IMPEDANCE ELEMENTS AND METHODS AND DEVICES INCLUDING THE SAME

# **TECHNICAL FIELD**

The present disclosure relates generally to integrated circuits (ICs) that include static random access memories (SRAMs), and more particularly to ICs that can utilize programmable resistance elements as pull-up resistors in SRAM cells.

# **BACKGROUND**

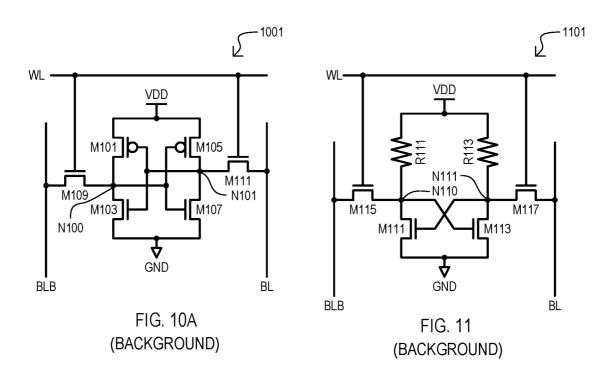

Static random access memory (SRAM) cells can have rapid access times, as compared to other memory types, and so can serve as important storage elements in integrated circuit devices. Various conventional SRAM cells are known. FIG. 10A shows a conventional six transistor (6T) SRAM cell 1001, which can include n-channel and p-channel transistors pairs (M101/M103, M105/M107) each in a CMOS inverter configuration. The CMOS inverters are cross-coupled between two nodes (N100, N101) to form a latch. Thus, nodes N100/N101 will be latched at complementary values (i.e., N100 high, N101 low, or vice versa). 6T SRAM cell 1001 also includes two access transistors M109/M111 which connect nodes N100/N101 to bit lines BLB and BL, respectively.

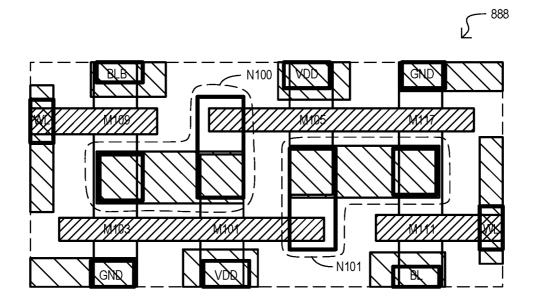

FIG. 10B shows an integrated circuit layout for a 6T SRAM cell like that of FIG. 10A. Like items are identified with the same reference characters. Because a 6T SRAM has both p-channel (i.e., latch pull-up) transistors and n-channel (i.e., latch pull-down) transistors, the memory cell can require substrate portions of different conductivity types (e.g., n-well for p-channel devices). As a result, a conventional 6T SRAM cell requires that some area be dedicated to well isolation or other similar structures.

Other SRAM cells are also known.

5

10

15

20

25

30

35

FIG. 11 shows a conventional four transistor (4T) SRAM cell 1101, which can include an n-channel transistors pair (M111/M113) cross-coupled between two nodes (N110, N111) as well as two pull-up resistors R111 and R113. Pull-up resistors (R111/R113) can be connected between the nodes N110/N111, respectively, and a high power supply voltage VDD. In this arrangement, nodes N110/N111 can be latched between complementary values. Conventional 4T SRAM cell 1101 can also include two access transistors M115/M117 which connect nodes N110/N111 to bit lines BLB and BL, respectively. Pull-up resistors R111/R113 are typically patterned from a layer of polysilicon.

While conventional 4T SRAM cell 1101 can provide a more compact cell size than a 6T SRAM cell, if the pull-up resistors (R111/R113) are made from the same layer as the transistor gates additional spacing constraints can be imposed on the cell. Further, polysilicon pull-up resistors can require additional processing steps, such as doping in order to increase their resistance. Still further, polysilicon resistors can require additional process steps and/or complexity, such as a dual polysilicon process and/or the use of "buried" contacts to connect pull-up resistors to substrate areas.

# DISCLOSURE OF INVENTION

An integrated circuit (IC) device can include a plurality of static random access memory (SRAM) cells, each

SRAM cell including a pair of latching devices cross coupled between first and second data latching nodes. One or more access devices can connect a data latching node to a bit line. An SRAM cell can also include first and second resistive elements that are disposed above a substrate, and connected to the data latching nodes by vertical conductive connections. Each resistive element can include at least one memory layer that is capable of being reprogrammed between at least a high and lower resistance state by application of electric fields, the resistive elements having only the high resistance state to store data in a volatile manner in the SRAM cells.

5

10

15

20

25

An IC device can also include a SRAM array comprising a plurality of SRAM cells. Each SRAM cell including a pair of cross-coupled latching devices and first and second resistive elements disposed over the substrate and conductively connected to the first and second latching nodes by vertical connections. Each resistive element can include at least one memory layer. The IC device can also include a resistive memory (RRAM) array comprising a plurality of RRAM cells, each RRAM cell including a storage element disposed over the substrate and conductively connected to a storage node by a vertical connection. Each storage element including the at least one memory layer. The memory layer of both the SRAM and RRAM cells is capable of being re-programmed between at least a high and lower resistance state by application of electric fields. The memory layer of the SRAM cells can be maintained in the high resistance state, while the memory layer of RRAM cells can be programmed between resistance states to store data.

A method can include: forming pairs of cross-coupled latching devices in a substrate for SRAM cells; forming a plurality of interconnect layers over the substrate, including to first and second latching nodes of the latching device; and forming at least one memory layer over and in contact with the first and second vertical connections to create static first resistive elements for the SRAM cells. The memory layer is capable of being reprogrammed between at least a high and lower resistance state by application of electric fields. However, the resistive elements have only the high resistance state to store data in a volatile manner in the SRAM cells.

# BRIEF DESCRIPTION OF DRAWINGS

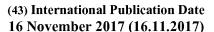

- FIG. 1 is a block schematic diagram of a static random access memory (SRAM) cell according to an embodiment.

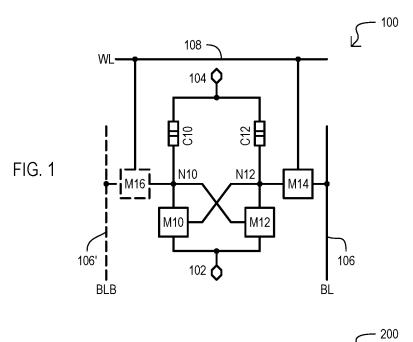

- FIG. 2 is a schematic diagram of a SRAM cell according to another embodiment.

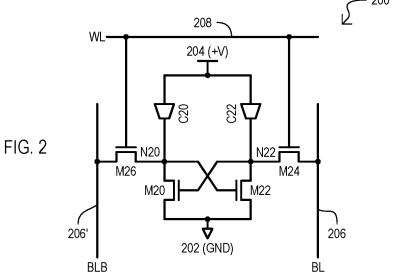

- FIG. 3 is a side cross sectional view of a SRAM cell according to an embodiment.

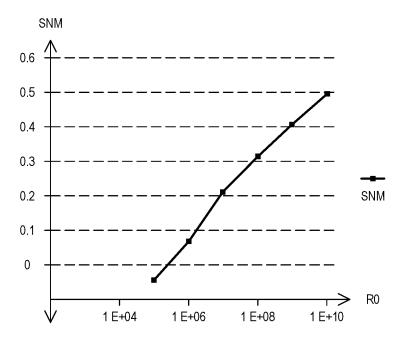

- FIGS. 4A and 4B are simulation results for a SRAM cell like that shown in FIG. 2.

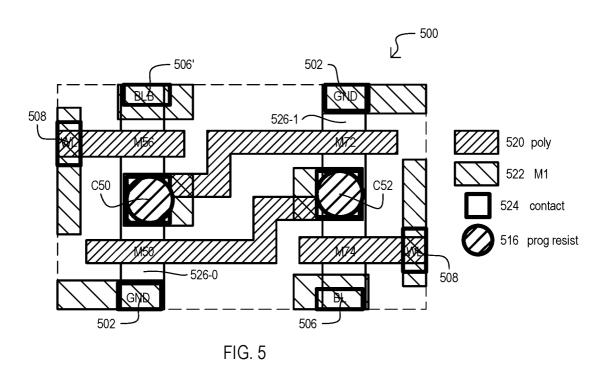

- FIG. 5 is a plan view of a SRAM cell according to one particular embodiment.

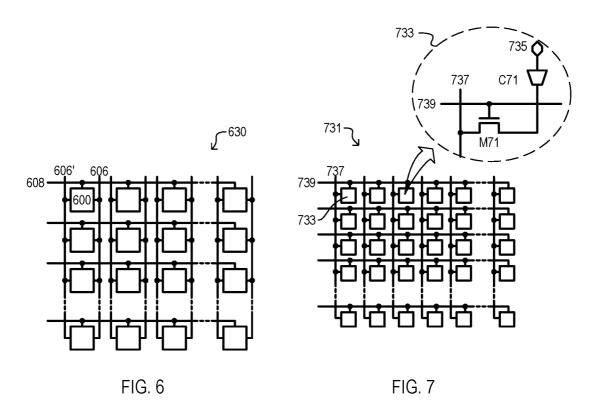

- FIG. 6 is a block schematic diagram of a SRAM array according to an embodiment.

- FIG. 7 is a block schematic diagram of a resistive RAM (RRAM) array that can be included in embodiments.

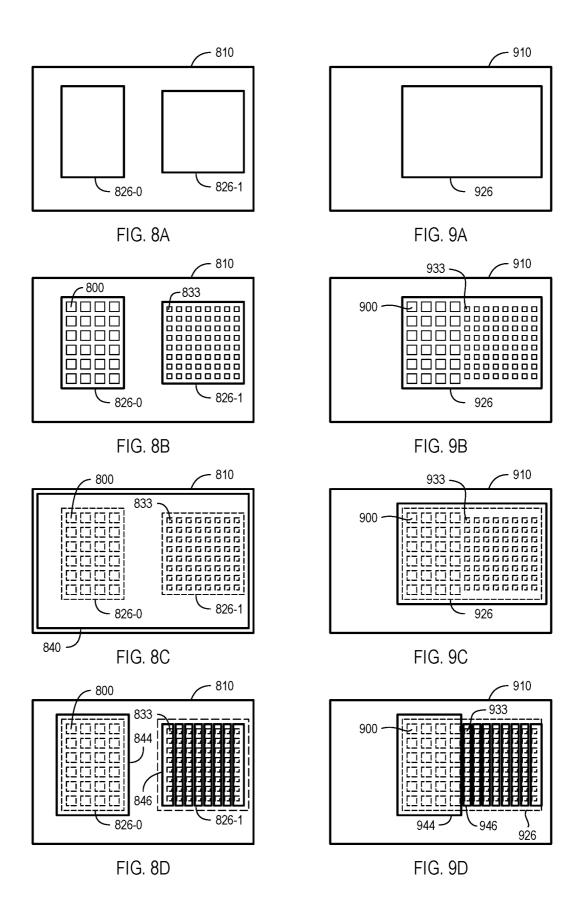

- FIGS. 8A to 8D are a series of top plan views showing a method of making an integrated circuit (IC) according to an embodiment.

- FIGS. 9A to 9D are a series of top plan views showing a method of making an IC according to another embodiment.

- FIGS. 10A and 10B are diagrams showing a conventional six transistor SRAM cell.

- FIG. 11 is a diagrams of a conventional four transistor SRAM cell.

#### DETAILED DESCRIPTION OF THE EMBODIMENTS

Embodiments can include static random access memory (SRAM) cells, SRAM arrays, integrated circuit devices including SRAM cells, and related methods in which SRAM cells include pull-up resistors formed all, or in part, by programmable resistance elements.

5

10

15

20

25

30

35

In some embodiments the programmable resistance elements are fabricated in a high resistance state, and remain unprogrammed to provide high resistance pull-up resistors for SRAM cells.

In some embodiments the programmable resistance elements are formed on a fabrication layer above a gate layer, and thus pull-up resistors may only require the space of a contact in the area occupied by an SRAM cell.

In some embodiments an integrated circuit (IC) device can include SRAM cells with pull-up resistors formed with programmable resistance elements, as well as nonvolatile storage cells that include programmable resistance elements as nonvolatile storage elements. The programmable resistance elements of the SRAM cells are maintained in the high resistance state, while the programmable resistance elements of the nonvolatile storage cells are programmed between two or more resistance states to store data.

In some embodiments an IC device can include programmable resistance elements having at least three vertically stacked layers, with groups of programmable resistance elements having a top layer formed by, or conductively connected to, horizontally disposed plate structures. Some of the programmable resistance elements can be pull-up resistors for SRAM cells, and connected to a same plate structure, which can be maintained at a predetermined voltage to latch data in the SRAM cells. Other of the programmable resistance elements can be storage elements of nonvolatile memory cells connected to plate structures that can be driven to different voltages to program programmable resistance elements between resistance states. Thus, an IC device can include one or more SRAM plate structures that are maintained at a constant voltage while data are stored in the SRAM cells, as well as multiple nonvolatile memory plate structures that can be driven between different voltages to store data in nonvolatile memory cells.

In some embodiments programmable resistance elements can be capable of being programmed between different resistance states by the application of electric fields which induce an oxidation-reduction reaction to cause changes in resistance.

In particular embodiments programmable resistance elements can be conductive bridging random access memory (CBRAM) type elements.

FIG. 1 is a block schematic diagram of a SRAM cell 100 according to an embodiment. SRAM cell 100 can include latching devices M10, M12, resistance elements (C10, C12), an access device M14, a word line 108, and bit line 106. Latching devices M10/M12 can each be three terminal devices having controllable current paths and control nodes. Latching devices M10/M12 can be cross-coupled between data storage nodes N10 and N12, with latching device M10 having a control terminal connected to node N12 and a first current path terminal connected to node N10, and latching device M12 having a control terminal connected to node N10 and a first current path terminal connected to node N12. Second current path terminals for both latching devices M10/M12 can be commonly connected to a first voltage node 102. In some embodiments, latching devices M10/M12 can be transistors.

Resistance element C10 can be a two-terminal element connected between data storage node N10 and a second voltage node 104. Resistance element C12 can be a two-terminal element connected between data storage node N12 and second voltage node 104. Resistance elements C10/C12 are capable of being programmed between two or more different resistance states, but according to some embodiments, are maintained in a high resistance state during data storage operations, to thus serve as pull-up resistors in the SRAM cell 100. Thus, in some embodiments, resistance elements C10/C12 are fabricated to have an initial high resistance state or are initially programmed to a high resistance state. While the resistance elements C10/C12 are capable of being programmed to a low resistance state, they are never programmed to a low resistance state, or are not so programmed while the SRAM cell 100 is to operate as a data storage cell.

5

10

15

20

25

30

35

In particular embodiments, resistance elements C10/C12 can be two terminal elements having one or more layers that are programmable between two or more resistance states by application of electric fields. In some embodiments, application of electric fields can induce an oxidation-reduction reaction that can result in changes in resistance. In particular embodiments, a layer can be programmable by ion conduction induced by application of electric fields. In addition or alternatively, resistance elements C10/C12 can be formed by vertically stacked layers, including one or more programmable resistance layers.

Referring still to FIG. 1, an access device M14 can be a three terminal device having a controllable current path connected between a data storage node (in this example N12) and a bit line 106, and can have a control node connected to word line 108. Optionally, SRAM cell 100 can include a second access device M16 having a controllable current path connected between the other data storage node (in this example N10) and a bit line 108', and can have a control node connected to word line 108. In such an arrangement bit lines 108/108' are understood to carry complementary values (e.g., high and low).

In a write operation, first and second voltage nodes 102/104 are driven to suitable supply voltages. A bit line (e.g., 106) can be driven to a high or low voltage depending upon a data value to be stored (or two bit lines 106/106' driven to complementary values). Word line 108 can then be activated to turn on access device M14 (or access devices M14/M16) and the voltages on bit line(s) will drive storage nodes N10/N12 to latch the data value. In a read operation, word line 108 can be activated to turn on M14 (or M14/M16) and the bit line(s) will "split" (be driven toward different voltages). Such a split can be amplified to generate an output read voltage.

It is understood that first and second voltage nodes 102/104 change according to operation (higher difference for faster operation, lower difference to reduce power consumption, and/or both to same voltage to disable the SRAM cell, etc.).

FIG. 2 is a schematic diagram of a four transistor (4T) SRAM cell 200 according to a particular embodiment. In a particular embodiment, SRAM cell 200 can be one very particular implementation of that shown in FIG. 1.

SRAM cell 200 can include a configuration like that of FIG. 1, however, latching devices M20/M22 can be n-channel insulated gate field effect transistors (referred to herein as MOS type transistors, but not indicating any particular gate insulator type). Transistors M20/M22 can have cross-coupled gates and drains, with sources commonly connected to a first (e.g., low) voltage node 202. SRAM cell 200 can also include two access devices

M24/M26, which can also be n-channel MOS type transistors, connected to complementary bit lines 206/206'. Gates of access transistors M24/M26 can be commonly connected to word line 208.

5

10

15

20

25

30

35

In the embodiment of FIG. 2, resistance elements C20/C22 can be CBRAM type elements having anode terminals commonly connected to a second (e.g., high) voltage node 204 and cathode terminals connected to storage nodes N20/N22, respectively. In some embodiments, an anode terminal can include one or more elements that are ion conductible in a memory layer of the CBRAM type element. Further, in some elements, changes in conduction in a memory layer can be brought about by the formation of conductive paths through a memory layer by the ion conduction of one or more metals, semi-metals, or semiconductors.

An embodiment like that of FIG. 2 can include latching devices M20/M22 and access devices M24/M26 formed by transistors of the same conductivity type. Thus, a cell size can be advantageously compact as a layout will not require well isolation structures or the like. However, alternate embodiments can include transistors of different conductivity types. For example, latching transistors can be n-channel MOS type transistors, while access transistor(s) can be p-channel MOS type transistors, or vice versa. Further, while FIG. 2 shows an SRAM cell 200 with n-channel transistors, an alternate embodiment can include all p-channel MOS type transistors. In embodiments with p-channel latching transistors, such latching transistors can have cross-coupled gates and drains, with sources commonly connected to a high voltage node, and pull-up resistance elements can be connected between storage nodes and a low voltage node.

FIG. 3 is a side cross sectional view of a portion of a SRAM cell 300 according to one particular embodiment. FIG. 3 shows how a programmable resistance element serving as a pull-up resistor can be formed over a substrate and connected to transistors of the SRAM cell by one or more vertical interconnect layers. FIG. 3 shows two transistors M30/M36 formed in a substrate 310. Transistors M30/M36 can be MOS type transistors of an SRAM cell according to any of the embodiments described herein or equivalents. In a particular embodiment, one transistor (e.g., M30) can be a latching transistor, while the other transistor (e.g., M36) can be an access transistor. Alternate embodiments can include transistor types other than MOS transistors. Further, while FIG. 3 shows a MOS type transistors having a channel in a uniformly flat substrate, alternate embodiments can include MOS type transistors including different orientations, including "FinFET" type transistors, or the like.

A programmable resistance element C30 can be formed over substrate 310, and connected to transistors M30/M36 by a conductive path. In such an arrangement, each pull-up resistor in an SRAM layout can only require the areas of a contact at lower levels. In FIG. 3, a conductive connection between programmable resistance element C30 and substrate 310 can include a contact 314 and a number of other conductive structures 316-0 to 316-n, such as vias (vertical connections) and metallization patterns (portions of a larger lateral interconnection layer). While FIG. 3 shows a relatively straight vertical connection, in other embodiments, connections can have segments that move in a lateral direction.

In the embodiment shown, a programmable resistance element C30 can be formed by a vertical arrangement of layers, including one or more programmable layers 312-1 formed between a first (bottom) electrode 312-0 and a second (top) electrode 312-2. In the embodiment shown, a bottom electrode 312-0 can be formed, all or in part, by a conductive structure 316-n (i.e., a via or metallization pattern). In some embodiments, programmable

layer(s) 312-1 and/or second electrode 312-2 can extend, not only over SRAM cell 300, but over multiple such SRAM cells (e.g., extend over an SRAM array or a portion of an array). A second electrode 312-2 that extends over multiple SRAM cells can be commonly connected to multiple programmable resistance elements, and thus can serve as a "plate" structure, as will be described in embodiments below. However, while FIG. 3 shows programmable layer(s) 312-1 and second electrode 312-2 extending over an SRAM cell, in other embodiments, programmable resistance elements can have a confined structure, being separate structures from one another. Additionally, while FIG. 3 shows a programmable resistance element having vertical layers, alternate embodiments can include programmable resistance elements having one or more layers with other orientations with respect to one another.

5

10

15

20

25

30

35

For some embodiments, programmable resistance elements used as pull-up resistors can have a resistance between about  $10M\Omega$  and  $10G\Omega$  without requiring polysilicon resistors. In particular embodiments, such programmable resistance elements can be CBRAM type elements formed well above the substrate after all, or most, metallization layers have been formed. The CBRAM elements can reliably provide a high resistance (e.g., between about  $10M\Omega$  and  $10G\Omega$ ) for good pull-up resistor performance.

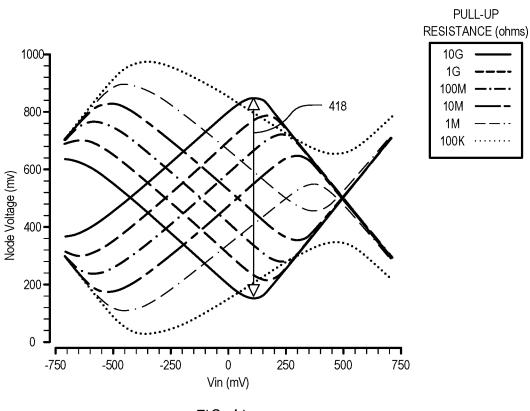

FIG. 4A is a diagram showing simulation results examining the signal noise margin (SNM) for a 4T SRAM cell like that of FIG. 2. FIG. 4A shows SRAM cell SNM for pull-up resistors of different values ( $100k\Omega$ ,  $1M\Omega$ ,  $10M\Omega$ ,  $100M\Omega$ ,  $1G\Omega$  and  $10G\Omega$ ) and a power supply of one volt. SNM can be calculated from the distance between the two switching curves (which can represent the two load/transistor pairs that drive the storage node). As shown, a pull-up resistance of  $10G\Omega$  (shown by arrow 418) can provide the greatest SNM from among the resistance values. For some applications, SNM can be unacceptably low at resistances of about 1M and below.

FIG. 4B is a diagram showing SNM versus pull-up resistance for a SRAM cell like that of FIG. 2. For many applications, an SNM greater than 200mV can provide good performance. As shown, pull-up resistances of about  $10M\Omega$  or greater can deliver a SNM greater than 200mV.

From FIGS. 4A and 4B, it is shown that pull-up resistors formed from programmable resistance elements having a resistance greater than  $10M\Omega$  can provide good SRAM cell performance. Further, when embodiments include CBRAMs, SRAM cells can have broad process stability, providing good SNM over a wide range of expected CBRAM resistance (e.g.,  $10M\Omega$  and  $10G\Omega$ ).

It is noted that in a conventional six transistor (6T) SRAM cell, like that of FIG. 10A, p-channel pull-up transistors (e.g., M101 or M105) have a leakage current when in operation. As but one very particular example, for a transistor having width/length (W/L) dimensions of 0.9/.036 um, at a power supply of 1.32V, and a temperature range of 25°C to 125°C, a leakage current can range from about 0.2nA to 5.0nA. In contrast, a  $10G\Omega$  resistor, such as a CBRAM serving as a pull-up resistor, can have a leakage current of about 0.1nA. Accordingly, a 4T transistor according to embodiments can have low leakage currents, for advantageously low power consumption.

FIG. 5 is a top plan view of a SRAM cell 500 according to one, very particular embodiment. In one arrangement, SRAM cell 500 can be one implementation of that shown in FIG. 2. FIG. 5 shows a polysilicon layer 520, a metallization layer 522, contacts 524, and the location of programmable resistance elements 516. As shown,

latching devices M50/M52 and access devices M54/M56 can be MOS type transistors formed with a polysilicon layer 520. In some embodiments, latching and access devices (M50 to M56) can be transistors of the same conductivity type, and thus not require well isolation.

Contacts 524 can extend upward from active areas 526-0/1 to metallization layers 522, and eventually to bit lines 506/506', voltage node 502, a word line 508, and programmable resistance elements CB50/CB52. As shown, area for programmable resistance elements CB50/CB52 at this level can include only a contact, allowing for a compact cell size.

It is understood that FIG. 5 represents but one very particular layout for a 4T SRAM cell, and should not be construed as limiting. Embodiments can include any suitable SRAM cell that employs pull-up (or pull-down) resistors.

10

15

20

25

30

5

FIG. 6 is a block schematic diagram of a SRAM cell array 630 according to an embodiment. SRAM cell array 630 can include SRAM memory cells (one shown as 600) arranged into rows and columns. Rows of SRAM memory cells can be commonly connected to a same word line (one shown as 608). Columns of SRAM memory cells can be commonly connected to a same bit line pair (one pair shown as 606/606'). SRAM memory cells (e.g., 600) can take of the form of any of those described in embodiments herein, or equivalents. Accordingly, while FIG. 6 shows columns of SRAM cells connected to bit line pairs, alternate embodiment can include columns of SRAM cells connected to single bit lines.

While embodiments can include SRAM cells and arrays, embodiments can also include integrated circuit (IC) devices that advantageously incorporate such SRAM cells and/or SRAM arrays with other circuits. In some embodiments, such other circuits can include resistive random RAM (RRAM) type memory arrays that include programmable resistance elements that are programmed between different resistance states to store data. Such RRAM type cells can be nonvolatile memory cells. FIG. 7 is one example of such a RRAM array.

FIG. 7 is a block schematic diagram of a RRAM array 731 that can be included in embodiments. RRAM array 731 can include RRAM memory cells (one shown as 733) arranged into rows and columns. Rows of RRAM memory cells can be commonly connected to a same word line (one shown as 739). Columns of RRAM memory cells can be commonly connected to a same bit line (one shown as 737).

FIG. 7 shows one example of a conventional RRAM cell 733. RRAM cell 733 can include a transistor M71 having a source-drain path connected between a bit line 737 and a first terminal programmable resistance element C71. A second terminal of programmable resistance element C71 can be connected to node 735. Node 735 can be a plate node common to multiple RRAM cells.

While FIG. 7 shows an RRAM array 733 having a one-transistor one-resistor (1T-1R) type cell, alternate embodiments can include any suitable RRAM array configuration, including but not limited to "cross-point" array architectures, that do not include access devices.

35

FIG. 8A to 8D are a series of top plan views showing methods of fabricating an IC device according to an embodiment.

In FIG. 8A, separate active regions 826-0/1 can be formed in a substrate 810.

In FIG. 8B, SRAM cells (one shown as 800) can be formed in active region 826-0. SRAM cells can take the form of any of those shown herein, or equivalents, in which programmable resistance elements have a top electrode. RRAM cells (one shown as 833) can be formed in the other active region 826-1. RRAM cells can take the form of any of those shown herein, or equivalents, but can also have programmable resistance elements have a top electrode. In particular embodiments, programmable resistance elements for SRAM cells (e.g., serving as pull-up resistors) can be the same as those for RRAM cells.

In FIG. 8C a plate layer 840 can be formed over SRAM cells and RRAM cells. A plate layer 840 can have a conductive connection to programmable resistance elements in each SRAM cell and RRAM cell. In some embodiments, a plate layer 840 can form, or can be conductively connected to, a terminal of two programmable resistance elements serving as pull-up resistors in each 4T SRAM cell, while at the same time forming, or providing a conductive connection to, terminals of programmable resistance elements in RRAM cells. In particular embodiments, a first plate layer 840 can form, or can be conductively connected to, an anode of CBRAM type elements serving as pull-up resistors in 4T SRAM cell and as storage elements in RRAM cells.

FIG. 8D shows a patterning of a plate layer into a SRAM plate 844 and a number of RRAM plate elements (one shown as 846). Each RRAM plate element (e.g., 846) can be driven separately to different voltages to enable programmable resistance elements in the RRAM cells to be selected for programming or reading operations. In contrast, first plate layer 840 can provide a conductive connection to programmable resistance elements in all SRAM cells, enabling terminals pull-up resistors in such cells to be maintained at a same voltage while storing data in the SRAM cells.

20

25

30

35

5

10

15

FIG. 9A to 9D are a series of top plan views showing methods of fabricating an IC device according to another embodiment. In FIGS. 9A to 9D, structures to those of FIGS. 8A to 8D are shown by the same reference character but with the leading digit being a "9".

FIGS. 9A to 9D differ from FIGS. 8A to 8D in that there can be one active area 926 in which both SRAM cells (one shown as 900) and RRAM cells (one shown as 933) can be fabricated in (FIG. 9B). That is, SRAM cells and RRAM cells can both be formed of transistors of a same conductivity type. A plate layer 940 can be patterned as described for FIG. 8D, providing a common SRAM plate 944 and separate RRAM plate elements (e.g., 946).

It should be appreciated that reference throughout this description to "one embodiment" or "an embodiment" means that a particular feature, structure or characteristic described in connection with the embodiment is included in at least one embodiment of an invention. Therefore, it is emphasized and should be appreciated that two or more references to "an embodiment" or "one embodiment" or "an alternative embodiment" in various portions of this specification are not necessarily all referring to the same embodiment. Furthermore, the particular features, structures or characteristics may be combined as suitable in one or more embodiments of the invention.

It is also understood that other embodiments of this invention may be practiced in the absence of an element/step not specifically disclosed herein.

Similarly, it should be appreciated that in the foregoing description of exemplary embodiments of the

invention, various features of the invention are sometimes grouped together in a single embodiment, figure, or description thereof for the purpose of streamlining the disclosure aiding in the understanding of one or more of the various inventive aspects. This method of disclosure, however, is not to be interpreted as reflecting an intention that the claims require more features than are expressly recited in each claim. Rather, inventive aspects lie in less than all features of a single foregoing disclosed embodiment. Thus, the claims following the detailed description are hereby expressly incorporated into this detailed description, with each claim standing on its own as a separate embodiment of this invention.

5

# IN THE CLAIMS

What is claimed is:

1. An integrated circuit (IC) device, comprising:

a plurality of static random access memory (SRAM) cells, each SRAM cell including

a pair of latching devices having controllable current paths connected to first and second data latching nodes, and control terminals cross-coupled between the first and second data latching nodes, and

first and second resistive elements disposed over the latching devices, the first resistive element conductively connected to the first data latching node by a first vertical connection, the second resistive element conductively connected to the second data latching node by a second vertical connection; wherein

each resistive element comprises at least one memory layer that is capable of being programmed between at least a high and lower resistance state by application of electric fields, the resistive elements having only the high resistance state to store data in a volatile manner in the SRAM cells.

15

10

5

2. The IC device of claim 1, wherein

the resistive elements of the plurality of SRAM cells include a contiguous memory layer common to all the SRAM cells.

20 3. The IC device of claim 1, further including

a common conductive plate layer in contact with the at least one memory layer of the resistive elements for the plurality of SRAM cells.

- 4. The IC device of claim 1, wherein

- the latching devices are latching transistors of a first conductivity type formed in a well of a second conductivity type.

- 5. The IC device of claim 4, further including

at least one access device having a control terminal coupled to a word line and a controllable current path coupled between the first data latching node and a bit line.

6. The IC device of claim 1, wherein

the first and second vertical connections include portions of a plurality of metallization patterns formed at different vertical levels above a substrate of the IC device.

35

30

7. The IC device of claim 1, further including:

a plurality of resistive memory cells, each resistive memory cell including

at least one memory access device a control terminal coupled to a memory word line and a controllable current path coupled between a storage node and a memory bit line, and

a memory resistive element disposed over the at least one memory access device, the resistive memory element being conductively connected to the storage node by a third vertical connection;

5 wherein

10

15

20

25

30

35

each memory resistive element comprises the at least one memory layer, the memory resistive elements being programmed between the at least high and lower resistance state to store data in a nonvolatile manner.

8. An integrated circuit (IC) device, comprising:

a static random access memory (SRAM) array comprising a plurality of SRAM cells, each SRAM cell including

a pair of cross-coupled latching devices formed in a substrate and configured to store complementary data values at first and second latching nodes, and

first and second resistive elements disposed over the substrate and conductively connected to the first and second latching nodes by first and second vertical connections, respectively, each resistive element including at least one memory layer; and

a resistive memory (RRAM) array comprising a plurality of RRAM cells, each RRAM cell including at least one storage element disposed over the substrate and conductively connected to a storage node by a third vertical connection, each storage element including the at least one memory layer, and

an access device formed in the substrate and configured to conductively couple the storage node to an RRAM bit line; wherein

the memory layer is capable of being re-programmed between at least a high and lower resistance state by application of electric fields, the memory layer of the SRAM cell first and second resistive elements being maintained in the high resistance state, the memory layer of the storage elements being programmed between at least the high and lower resistance states to store data.

9. The IC device of claim 8, wherein the SRAM cells are four transistor (4T) SRAM cells, each 4T SRAM cell including

the cross-coupled latching devices being latching transistors,

a first SRAM cell access transistor having a source-drain path coupled between the first latching node and an SRAM array bit line, and

a second SRAM cell access transistor having a source-drain path coupled between the second latching node and a complementary SRAM array bit line,

10. The IC device of claim 9, wherein the RRAM cells are one transistor – one resistor (1T-1R) RRAM cells, each including an access transistor of the same conductivity type as the latching transistors.

11. The IC device of claim 8, wherein SRAM array and RRAM array are formed in at least one well formed in the substrate.

12. The IC device of claim 11, wherein SRAM array and RRAM array are formed in the same well.

5

15

20

25

30

35

- 13. The memory element of claim 8, wherein the memory layer of the first and second resistance elements of the SRAM cells in the SRAM array is a contiguous structure across a plurality of SRAM cells.

- 14. The memory element of claim 8, wherein the memory layer of the storage elements of the RRAM cells in the RRAM array is a contiguous structure across a plurality of SRAM cells.

- 15. The memory element of claim 8, wherein the memory layer of the first and second resistance elements of the SRAM cells and of the storage elements of the RRAM cells is the same contiguous structure.

# 16. A method, comprising:

forming pairs of latching devices in a substrate for static random access memory (SRAM) cells, the latching devices having controllable current paths connected to first and second latching nodes, and control terminals cross-coupled between the first and second data latching nodes;

forming a plurality of interconnect layers over the substrate, the interconnect layers forming corresponding conductive first vertical connections to each first latching node, and a corresponding conductive second vertical connections to each second latching node; and

forming at least one memory layer over and in contact with the first and second vertical connections to create static first resistive elements having a conductive connection to each first vertical connection, and static second resistive elements having a conductive connection to each second vertical connection; wherein

the at least one memory layer is capable of being re-programmed between at least a high and lower resistance state by application of electric fields, the resistive elements having only the high resistance state to store data in a volatile manner in the SRAM cells.

17. The method of claim 16, further including:

forming access devices in the substrate for resistive memory (RRAM) cells, the access devices having controllable current paths connected between a storage node and a bit line, and a control terminal coupled to a word line;

forming the plurality of interconnect layers further includes forming corresponding conductive third vertical connections to each storage node; and

forming the at least one memory layer over and in contact with the third vertical connections to create programmable resistive elements having a conductive connection to each third vertical connection; wherein

the at least one memory layer of the RRAM cells is programmed between at least the high and lower resistance states to store data in the RRAM cells.

18. The method of claim 17, further including forming a conductive plate layer over at least a portion of the memory layer formed over the SRAM cells.

- 5 19. The method of claim 18, wherein forming a conductive plate layer includes:

- forming one contiguous conductive SRAM plate section over the SRAM cells to conductively connect all first and second resistive elements to a common SRAM plate node; and

forming a plurality of contiguous conductive RRAM plate sections over the RRAM cells, each RRAM plate section conductively connecting groups of third resistive elements to different RRAM plate nodes.

10

- 20. The method of claim 17, wherein:

- forming the pairs of latching devices includes forming pairs of cross-coupled latching transistors of a first conductivity type; and

forming the access devices includes forming access transistors of the first conductivity type.

15

FIG. 4A

FIG. 4B

FIG. 10B (BACKGROUND)

# INTERNATIONAL SEARCH REPORT

International application No.

PCT/US 16/32428

|                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                 |                             | PCT/US 16/32428                                                                              |                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------|----------------------------------------------------------------------------------------------|---------------------------------------|

| A. CLASSIFICATION OF SUBJECT MATTER IPC(8) - G11C 13/00; G11C 14/00 (2016.01) CPC - G11C 11/5614; G11C 13/0011; G11C 14/009; H01L 27/1112 According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                            |                                                                                                                 |                             |                                                                                              |                                       |

| B. FIELDS SEARCHED                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                 |                             |                                                                                              |                                       |

| Minimum documentation searched (classification system followed by classification symbols) IPC(8) - G11C 13/00; G11C 14/00 (2016.01) CPC - G11C 11/5614; G11C 13/0011; G11C 14/009; H01L 27/1112                                                                                                                                                                                                        |                                                                                                                 |                             |                                                                                              |                                       |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched IPC(8)- G11C13/00; G11C14/00 (2016.01); CPC - G11C11/5614,5678,5685; G11C13/0002,0004,0007,0009,0011,0014,0016,0019; G11C14/009; H01L27/1112; USPC-365/46,148,189.2                                                                                                      |                                                                                                                 |                             |                                                                                              |                                       |

| Electronic data base consulted during the international search (name of data base and, where practicable, search terms used) PatBase, Proquest Dialog, Google Patents, Google Scholar Search terms used: SRAM, latch, RRAM, ReRAM, CBRAM, memristor, programmable, variable, memory, pull-up, resistor, volatile, vertical connection, permanent, only, maintained, high, upper, resistance, impedance |                                                                                                                 |                             |                                                                                              |                                       |

| C. DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                 |                             |                                                                                              |                                       |

| Category*                                                                                                                                                                                                                                                                                                                                                                                              | Citation of document, with indication, where an                                                                 | propriate, of the relevant  | passages                                                                                     | Relevant to claim No.                 |

| Α                                                                                                                                                                                                                                                                                                                                                                                                      | US 7,599,210 B2 (OKAZAKI et al.) 06 October 2009 (01, In 18-29, col 7, In 51-col 8, In 27, col 9, In 9-11       | 6.10.2009), Fig 1, 2, 4A, 4 | B, abstract, col                                                                             | 1-20                                  |

| A                                                                                                                                                                                                                                                                                                                                                                                                      | US 6,944,050 B2 (KANG et al.) 13 September 2005 (13.09.2005), Fig 8, abstract, col 2, In 29-38, col 8, In 40-50 |                             |                                                                                              | 1-20                                  |

| А                                                                                                                                                                                                                                                                                                                                                                                                      | US 7,436,694 B2 (BERTHOLD et al.) 14 October 2008 (14.10.2008), Fig 3, abstract, col 5, ln 20 -31               |                             |                                                                                              | 1-20                                  |

| A                                                                                                                                                                                                                                                                                                                                                                                                      | US 8,687,403 B1 (DERHACOBIAN et al.) 01 April 2014 (01.04.2014), Fig 17, abstract, col 11, ln 53-col 12, ln 6   |                             |                                                                                              | 1-20                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                 |                             |                                                                                              |                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                 |                             |                                                                                              |                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                 |                             |                                                                                              |                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                 |                             |                                                                                              |                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                 |                             |                                                                                              |                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                 |                             |                                                                                              |                                       |

| -                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                 |                             |                                                                                              |                                       |

| Further documents are listed in the continuation of Box C.                                                                                                                                                                                                                                                                                                                                             |                                                                                                                 |                             |                                                                                              |                                       |

| <ul> <li>Special categories of cited documents:</li> <li>"A" document defining the general state of the art which is not considered to be of particular relevance</li> <li>"Bater document published after the international filing date date and not in conflict with the application but cited to the principle or theory underlying the invention</li> </ul>                                        |                                                                                                                 |                             |                                                                                              | ation but cited to understand         |

| "E" earlier application or patent but published on or after the international "X" document of particular relevance; the filing date                                                                                                                                                                                                                                                                    |                                                                                                                 |                             | claimed invention cannot be ered to involve an inventive                                     |                                       |

| special reason (as specified) considered to involve                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                 |                             | Sular relevance; the claimed invention cannot be olve an inventive step when the document is |                                       |

| "O" document referring to an oral disclosure, use, exhibition or other means combined with one or more other such being obvious to a person skilled in the document published prior to the international filing date but later than "&" document member of the same patent                                                                                                                             |                                                                                                                 |                             | art                                                                                          |                                       |

| the priority date claimed  Date of the actual completion of the international search  Date of mailing of the international search report                                                                                                                                                                                                                                                               |                                                                                                                 |                             |                                                                                              | · · · · · · · · · · · · · · · · · · · |

| 16 August 2016 (16.08.2016)                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                 | 14 SEP 2016                 |                                                                                              |                                       |

Authorized officer:

PCT Helpdesk: 571-272-4300 PCT OSP: 571-272-7774 Lee W. Young

Mail Stop PCT, Attn: ISA/US, Commissioner for Patents P.O. Box 1450, Alexandria, Virginia 22313-1450

Name and mailing address of the ISA/US

Facsimile No. 571-273-8300