# (19) 国家知识产权局

# (12) 发明专利

(10) 授权公告号 CN 115148253 B (45) 授权公告日 2024.05.17

- (21)申请号 202110352502.0

- (22)申请日 2021.03.31

- (65) 同一申请的已公布的文献号 申请公布号 CN 115148253 A

- (43) 申请公布日 2022.10.04

- (73)专利权人 长鑫存储技术有限公司 地址 230601 安徽省合肥市经济技术开发 区空港工业园兴业大道388号

- (72) 发明人 张良

- (51) Int.CI.

G11C 11/4096 (2006.01)

- (56) 对比文件

- CN 101017703 A,2007.08.15

- CN 105895148 A, 2016.08.24

- CN 112349319 A,2021.02.09

- JP 2009170016 A,2009.07.30

- JP 2012089191 A,2012.05.10

- KR 20020086080 A,2002.11.18

- US 2013336073 A1,2013.12.19

- US 5815451 A.1998.09.29

- US 8699291 B1,2014.04.15

胡乔乔等.DRAM 存储调度算法研究.中 国知网.2013,全文.

审查员 夏永强

权利要求书4页 说明书16页 附图4页

#### (54) 发明名称

存储器电路、存储器预充电的控制方法及设 备

#### (57) 摘要

本发明涉及一种存储器电路、存储器预充电 的控制方法及计算机设备,包括:预充电电路,包 括第一预充电单元,第二预充电单元,第一电源 端,第二申源端,第一控制端,第二控制端及数据 端;第一预充电单元与第一电源端、第一控制端 及数据端连接;第二预充电单元与第二电源端、 第二控制端及数据端连接;第一电源端输入第一 预充电压,第二电源端输入第二预充电压;及控 制电路,用于当存储器处于行激活状态,目未进 行读写操作时,通过第二预充电单元控制数据端 与第二电源端之间断开,且通过第一预充电单元 四 控制数据端与第一电源端之间断开。上述存储器 25 电路能够避免在存储器处于行激活状态且未进 行读写操作时对电流的浪费,同时还能够提升读 写速度。

1.一种存储器电路,其特征在于,包括:

预充电电路,包括第一预充电单元,第二预充电单元,第一电源端,第二电源端,第一控制端,第二控制端及数据端;所述第一预充电单元与所述第一电源端、所述第一控制端及所述数据端连接;所述第二预充电单元与所述第二电源端、所述第二控制端及所述数据端连接;所述第一电源端输入第一预充电压,所述第二电源端输入第二预充电压;及

控制电路,所述控制电路的第一输出端与所述第一控制端连接,所述控制电路的第二输出端与所述第二控制端连接;所述控制电路用于:

当存储器未处于行激活状态时,通过所述第二预充电单元控制所述数据端与所述第二 电源端之间导通,且通过所述第一预充电单元控制所述数据端与所述第一电源端之间断 开;

当所述存储器处于行激活状态,且未进行读写操作时,通过所述第二预充电单元控制 所述数据端与所述第二电源端之间断开,且通过所述第一预充电单元控制所述数据端与所 述第一电源端之间断开;

当所述存储器处于行激活状态,且第一次读写操作开始后的预设时间内,通过所述第二预充电单元控制所述数据端与所述第二电源端之间断开,且通过所述第一预充电单元控制所述数据端与所述第一电源端之间导通;

当所述存储器处于行激活状态,且第一次读写操作开始后的预设时间之后,通过所述 第二预充电单元控制所述数据端与所述第二电源端之间断开,且通过所述第一预充电单元 控制所述数据端与所述第一电源端之间断开;

当所述存储器处于行激活状态,且第一次读写操作完成后的预设时间内,通过所述第二预充电单元控制所述数据端与所述第二电源端之间断开,且通过所述第一预充电单元控制所述数据端与所述第一电源端之间断开;

当所述存储器处于行激活状态,且第一次读写操作完成后的预设时间之后,通过所述 第二预充电单元控制所述数据端与所述第二电源端之间断开,且通过所述第一预充电单元 控制所述数据端与所述第一电源端之间导通。

- 2.根据权利要求1所述的存储器电路,其特征在于,所述第一预充电压为所述存储器的电源电压,所述第二预充电压为所述存储器的电源电压的一半。

- 3.根据权利要求1所述的存储器电路,其特征在于,所述存储器在行激活状态的一个周期内进行多次读写操作,在所述存储器的行激活状态的一个周期内,每次读写操作完成后的预设时间之后,所述控制电路通过所述第一预充电单元控制所述数据端与所述第一电源端之间导通,并在下次读写操作开始后的预设时间之后,通过所述第一预充电单元控制所述数据端与所述第一电源端之间断开。

- 4.根据权利要求1至3任一项所述的存储器电路,其特征在于,所述控制电路的第一输入端输入行激活信号,所述控制电路的第二输入端输入读写信号;当所述行激活信号为低电平时,所述存储器未处于行激活状态;当所述行激活信号为高电平时,所述存储器处于行激活状态;当所述读写信号为低电平时,所述存储器未进行读写操作;当所述读写信号为高电平时,所述存储器进行读写操作。

- 5.根据权利要求4所述的存储器电路,其特征在于,所述控制电路包括第一反相单元、延时单元、三输入或非门、第二反相单元、第三反相单元以及锁存单元,所述锁存单元包括

第一输入端、第二输入端及输出端;其中,

所述第一反相单元的输入端与所述锁存单元的第一输入端连接并作为所述控制电路的第一输入端,所述第一反相单元的第一输出端和第二输出端均用于输出所述行激活信号反相后的信号;所述第一反相单元的第一输出端为所述控制电路的第二输出端;

所述三输入或非门的第一输入端与所述第一反相单元的第二输出端连接;

所述延时单元的输入端与所述第二反相单元的输入端连接并作为所述控制电路的第二输入端,所述延时单元的输出端与所述三输入或非门的第二输入端连接;所述延时单元用于将所述读写信号延迟所述预设时间后输出;所述第二反相单元用于输出所述读写信号反相后的信号;

所述锁存单元的第二输入端与所述第二反相单元的输出端连接,所述锁存单元的输出端与所述三输入或非门的第三输入端连接;

所述第三反相单元的输入端与所述三输入或非门的输出端连接,所述第三反相单元的输出端作为所述控制电路的第一输出端;所述第三反相单元用于将输入端输入的信号进行反相后输出。

6.根据权利要求5所述的存储器电路,其特征在于,所述第一反相单元包括N个依次串接的反相器,所述第一反相单元中的最后一个反相器的输出端为所述第一反相单元的第一输出端,所述第一反相单元中的第N<sub>x</sub>个反相器的输出端为所述第一反相单元的第二输出端;

其中,N、N、均为正奇数且N、小于N。

7.根据权利要求5所述的存储器电路,其特征在于,所述延时单元包括M个依次串联的反相器;

其中,M为正偶数。

8.根据权利要求5所述的存储器电路,其特征在于,所述第二反相单元包括Q个依次串接的反相器:

其中,Q为正奇数。

9.根据权利要求5所述的存储器电路,其特征在于,所述第三反相单元包括P个依次串接的反相器:

其中,P为正奇数。

- 10.根据权利要求5所述的存储器电路,其特征在于,所述锁存单元包括锁存器。

- 11.根据权利要求10所述的存储器电路,其特征在于,所述锁存单元包括:第一与非门及第二与非门;其中,

所述第一与非门的第一输入端作为所述锁存单元的第一输入端,所述第一与非门的第二输入端与所述第二与非门的输出端连接,所述第一与非门的输出端作为所述锁存单元的输出端与所述三输入或非门的第三输入端及所述第二与非门的第一输入端连接;

所述第二与非门的第二输入端作为所述锁存单元的第二输入端。

12.根据权利要求1所述的存储器电路,其特征在于,所述数据端包括第一数据端和第二数据端,所述第一数据端和所述第二数据端接收互为相反的数据信号;所述第一预充电单元包括第一开关单元和第二开关单元,所述第一开关单元的第一电连接端和所述第二开关单元的第一电连接端均与所述第一电源端连接,所述第一开关单元的控制端和所述第二

开关单元的控制端均与所述第一控制端连接,所述第一开关单元的第二电连接端与所述第一数据端连接,所述第二开关单元的第二电连接端与所述第二数据端连接;

所述第二预充电单元包括第三开关单元和第四开关单元,所述第三开关单元的第一电连接端和所述第四开关单元的第一电连接端均与所述第二电源端连接,所述第三开关单元的控制端和所述第四开关单元的控制端均与所述第二控制端连接,所述第三开关单元的第二电连接端与所述第一数据端连接,所述第四开关单元的第二电连接端与所述第二数据端连接。

13.根据权利要求12所述的存储器电路,其特征在于,所述第一开关单元和所述第二开关单元均包括PMOS管,所述第一开关单元的第一电连接端和所述第二开关单元的第一电连接端均为所述PMOS管的源极,所述第一开关单元的第二电连接端和所述第二开关单元的第二电连接端均为所述PMOS管的漏极,所述第一开关单元的控制端和所述第二开关单元的控制端均为所述PMOS管的栅极;

所述第三开关单元和所述第四开关单元均包括NMOS管,所述第三开关单元的第一电连接端和所述第四开关单元的第一电连接端均为所述NMOS管的源极,所述第三开关单元的第二电连接端和所述第四开关单元的第二电连接端均为所述NMOS管的漏极,所述第三开关单元的控制端和所述第四开关单元的控制端均为所述NMOS管的栅极。

14.一种存储器预充电的控制方法,应用于存储器的预充电电路,其特征在于,所述预充电电路包括第一预充电单元,第二预充电单元,第一电源端,第二电源端,第一控制端,第二控制端及数据端;所述第一预充电单元与所述第一电源端、所述第一控制端及所述数据端连接;所述第二预充电单元与所述第二电源端、所述第二控制端及所述数据端连接;所述第一电源端输入第一预充电压,所述第二电源端输入第二预充电压;所述方法包括:

当所述存储器未处于行激活状态时,通过所述第二预充电单元控制所述数据端与所述 第二电源端之间导通,且通过所述第一预充电单元控制所述数据端与所述第一电源端之间 断开:

当所述存储器处于行激活状态,且未进行读写操作时,通过所述第二预充电单元控制 所述数据端与所述第二电源端之间断开,且通过所述第一预充电单元控制所述数据端与所 述第一电源端之间断开;

当所述存储器处于行激活状态,且第一次读写操作开始后的预设时间内,通过所述第二预充电单元控制所述数据端与所述第二电源端之间断开,且通过所述第一预充电单元控制所述数据端与所述第一电源端之间导通;

当所述存储器处于行激活状态,且第一次读写操作开始后的预设时间之后,通过所述 第二预充电单元控制所述数据端与所述第二电源端之间断开,且通过所述第一预充电单元 控制所述数据端与所述第一电源端之间断开;

当所述存储器处于行激活状态,且第一次读写操作完成后的预设时间内,通过所述第二预充电单元控制所述数据端与所述第二电源端之间断开,且通过所述第一预充电单元控制所述数据端与所述第一电源端之间断开;

当所述存储器处于行激活状态,且第一次读写操作完成后的预设时间之后,通过所述 第二预充电单元控制所述数据端与所述第二电源端之间断开,且通过所述第一预充电单元 控制所述数据端与所述第一电源端之间导通。

- 15.根据权利要求14所述的存储器预充电的控制方法,其特征在于,所述存储器在行激活状态的一个周期内进行多次读写操作,在所述存储器的行激活状态的一个周期内,每次读写操作完成后的预设时间之后,控制电路通过所述第一预充电单元控制所述数据端与所述第一电源端之间导通,并在下次读写操作开始后的预设时间之后,通过所述第一预充电单元控制所述数据端与所述第一电源端之间断开。

- 16.一种计算机设备,包括存储器和处理器,所述存储器存储有计算机程序,其特征在于,所述处理器执行所述计算机程序时实现权利要求14或15所述的控制方法的步骤。

# 存储器电路、存储器预充电的控制方法及设备

### 技术领域

[0001] 本申请涉及集成电路技术领域,特别是涉及一种存储器电路、存储器预充电的控制方法及计算机设备。

## 背景技术

[0002] DRAM(Dynamic Random Access Memory, 动态随机存取存储器)是一种易失性的存储器,通常包括多个读取电路,用于读取呈阵列的存储单元中的信息,每个读写操作往往需要在一个时间周期内完成。在存储器工作过程中,需要将数据线预充电到预定的电压,即进行预充电(Precharge)操作。

[0003] 传统的存储器每次进入行激活状态,则存储阵列(array)中的数据线被输入预定的电压,从而为后续的读写操作做准备。如此,会增加激活(active)电流IDD0,若在行激活状态下没有进行后续的读写操作,则这部分电流被浪费掉,导致存储器耗电量大。

### 发明内容

[0004] 基于此,有必要针对现有技术中的存储器在没有读写操作时,激活电流被浪费的问题提供一种存储器电路、存储器预充电的控制方法及计算机设备。

[0005] 为了实现上述目的,一方面,本发明提供了一种存储器电路,包括:预充电电路,包括第一预充电单元,第二预充电单元,第一电源端,第二电源端,第一控制端,第二控制端及数据端;所述第一预充电单元与所述第一电源端、所述第一控制端及所述数据端连接;所述第二预充电单元与所述第二电源端、所述第二控制端及所述数据端连接;所述第一电源端输入第一预充电压,所述第二电源端输入第二预充电压;及

[0006] 控制电路,所述控制电路的第一输出端与所述第一控制端连接,所述控制电路的第二输出端与所述第二控制端连接;所述控制电路用于:

[0007] 当存储器未处于行激活状态时,通过所述第二预充电单元控制所述数据端与所述 第二电源端之间导通,且通过所述第一预充电单元控制所述数据端与所述第一电源端之间 断开;

[0008] 当所述存储器处于行激活状态,且未进行读写操作时,通过所述第二预充电单元控制所述数据端与所述第二电源端之间断开,且通过所述第一预充电单元控制所述数据端与所述第一电源端之间断开;

[0009] 当所述存储器处于行激活状态,且第一次读写操作开始后的预设时间内,通过所述第二预充电单元控制所述数据端与所述第二电源端之间断开,且通过所述第一预充电单元控制所述数据端与所述第一电源端之间导通;

[0010] 当所述存储器处于行激活状态,且第一次读写操作开始后的预设时间之后,通过 所述第二预充电单元控制所述数据端与所述第二电源端之间断开,且通过所述第一预充电 单元控制所述数据端与所述第一电源端之间断开;

[0011] 当所述存储器处于行激活状态,且第一次读写操作完成后的预设时间内,通过所

述第二预充电单元控制所述数据端与所述第二电源端之间断开,且通过所述第一预充电单元控制所述数据端与所述第一电源端之间断开;

[0012] 当所述存储器处于行激活状态,且第一次读写操作完成后的预设时间之后,通过所述第二预充电单元控制所述数据端与所述第二电源端之间断开,且通过所述第一预充电单元控制所述数据端与所述第一电源端之间导通。

[0013] 在其中一个实施例中,所述第一预充电压为所述存储器的电源电压,所述第二预充电压为所述存储器的电源电压的一半。

[0014] 在其中一个实施例中,所述存储器在行激活状态的一个周期内进行多次读写操作,在所述存储器的行激活状态的一个周期内,每次读写操作完成后的预设时间之后,所述控制电路通过所述第一预充电单元控制所述数据端与所述第一电源端之间导通,并在下次读写操作开始后的预设时间之后,通过所述第一预充电单元控制所述数据端与所述第一电源端之间断开。

[0015] 在其中一个实施例中,所述控制电路的第一输入端输入行激活信号,所述控制电路的第二输入端输入读写信号;当所述行激活信号为低电平时,所述存储器未处于行激活状态;当所述行激活信号为高电平时,所述存储器处于行激活状态;当所述读写信号为低电平时,所述存储器未进行读写操作;当所述读写信号为高电平时,所述存储器进行读写操作。

[0016] 在其中一个实施例中,所述控制电路包括第一反相单元、延时单元、三输入或非门、第二反相单元、第三反相单元以及锁存单元,所述锁存单元包括第一输入端、第二输入端及输出端;其中,

[0017] 所述第一反相单元的输入端与所述锁存单元的第一输入端连接并作为所述控制电路的第一输入端,所述第一反相单元的第一输出端和第二输出端均用于输出所述行激活信号反相后的信号;所述第一反相单元的第一输出端为所述控制电路的第二输出端:

[0018] 所述三输入或非门的第一输入端与所述第一反相单元的第二输出端连接;

[0019] 所述延时单元的输入端与所述第二反相单元的输入端连接并作为所述控制电路的第二输入端,所述延时单元的输出端与所述三输入或非门的第二输入端连接;所述延时单元用于将所述读写信号延迟所述预设时间后输出;所述第二反相单元用于输出所述读写信号反相后的信号;

[0020] 所述锁存单元的第二输入端与所述第二反相单元的输出端连接,所述锁存单元的输出端与所述三输入或非门的第三输入端连接;

[0021] 所述第三反相单元的输入端与所述三输入或非门的输出端连接,所述第三反相单元的输出端作为所述控制电路的第一输出端;所述第三反相单元用于将输入端输入的信号进行反相后输出。

[0022] 在其中一个实施例中,所述第一反相单元包括N个依次串接的反相器,所述第一反相单元中的最后一个反相器的输出端为所述第一反相单元的第一输出端,所述第一反相单元的第N、个反相器的输出端为所述第一反相单元的第二输出端;

[0023] 其中,N、N、均为正奇数且N、小于或等于N。

[0024] 在其中一个实施例中,所述延时单元包括M个依次串联的反相器;

[0025] 其中,M为正偶数。

[0026] 在其中一个实施例中,所述第二反相单元包括Q个依次串接的反相器:

[0027] 其中,Q为正奇数。

[0028] 在其中一个实施例中,所述第三反相单元包括P个依次串接的反相器;

[0029] 其中,P为正奇数。

[0030] 在其中一个实施例中,所述锁存单元包括锁存器。

[0031] 在其中一个实施例中,所述锁存单元包括:第一与非门及第二与非门;其中,

[0032] 所述第一与非门的第一输入端作为所述锁存单元的第一输入端,所述第一与非门的第二输入端与所述第二与非门的输出端连接,所述第一与非门的输出端作为所述锁存单元的输出端与所述三输入或非门的第三输入端及所述第二与非门的第一输入端连接;

[0033] 所述第二与非门的第二输入端作为所述锁存单元的第二输入端。

[0034] 在其中一个实施例中,所述数据端包括第一数据端和第二数据端,所述第一数据端和所述第二数据端接收互为相反的数据信号;所述第一预充电单元包括第一开关单元和第二开关单元,所述第一开关单元的第一电连接端和所述第二开关单元的第一电连接端均与所述第一电源端连接,所述第一开关单元的控制端和所述第二开关单元的控制端均与所述第一控制端连接,所述第一开关单元的第二电连接端与所述第一数据端连接,所述第二开关单元的第二电连接端与所述第二数据端连接;

[0035] 所述第二预充电单元包括第三开关单元和第四开关单元,所述第三开关单元的第一电连接端和所述第四开关单元的第一电连接端均与所述第二电源端连接,所述第三开关单元的控制端和所述第四开关单元的控制端均与所述第二控制端连接,所述第三开关单元的第二电连接端与所述第一数据端连接,所述第四开关单元的第二电连接端与所述第二数据端连接。

[0036] 在其中一个实施例中,所述第一开关单元和所述第二开关单元均包括PMOS管,所述第一开关单元的第一电连接端和所述第二开关单元的第一电连接端均为所述PMOS管的源极,所述第一开关单元的第二电连接端和所述第二开关单元的第二电连接端均为所述PMOS管的漏极,所述第一开关单元的控制端和所述第二开关单元的控制端均为所述PMOS管的栅极;

[0037] 所述第三开关单元和所述第四开关单元均包括NMOS管,所述第三开关单元的第一电连接端和所述第四开关单元的第一电连接端均为所述NMOS管的源极,所述第三开关单元的第二电连接端和所述第四开关单元的第二电连接端均为所述NMOS管的漏极,所述第三开关单元的控制端和所述第四开关单元的控制端均为所述NMOS管的栅极。

[0038] 本发明还提供了一种存储器预充电的控制方法,应用于存储器的预充电电路,所述预充电电路包括第一预充电单元,第二预充电单元,第一电源端,第二电源端,第一控制端,第二控制端及数据端;所述第一预充电单元与所述第一电源端、所述第一控制端及所述数据端连接;所述第二预充电单元与所述第二电源端、所述第二控制端及所述数据端连接;所述第一电源端输入第一预充电压,所述第二电源端输入第二预充电压;所述方法包括:

[0039] 当所述存储器未处于行激活状态时,通过所述第二预充电单元控制所述数据端与所述第二电源端之间导通,且通过所述第一预充电单元控制所述数据端与所述第一电源端之间断开;

[0040] 当所述存储器处于行激活状态,且未进行读写操作时,通过所述第二预充电单元

控制所述数据端与所述第二电源端之间断开,且通过所述第一预充电单元控制所述数据端与所述第一电源端之间断开;

[0041] 当所述存储器处于行激活状态,且第一次读写操作开始后的预设时间内,通过所述第二预充电单元控制所述数据端与所述第二电源端之间断开,且通过所述第一预充电单元控制所述数据端与所述第一电源端之间导通;

[0042] 当所述存储器处于行激活状态,且第一次读写操作开始后的预设时间之后,通过 所述第二预充电单元控制所述数据端与所述第二电源端之间断开,且通过所述第一预充电 单元控制所述数据端与所述第一电源端之间断开;

[0043] 当所述存储器处于行激活状态,且第一次读写操作完成后的预设时间内,通过所述第二预充电单元控制所述数据端与所述第二电源端之间断开,且通过所述第一预充电单元控制所述数据端与所述第一电源端之间断开;

[0044] 当所述存储器处于行激活状态,且第一次读写操作完成后的预设时间之后,通过所述第二预充电单元控制所述数据端与所述第二电源端之间断开,且通过所述第一预充电单元控制所述数据端与所述第一电源端之间导通。

[0045] 在其中一个实施例中,所述存储器在行激活状态的一个周期内进行多次读写操作,在所述存储器的行激活状态的一个周期内,每次读写操作完成后的预设时间之后,所述控制电路通过所述第一预充电单元控制所述数据端与所述第一电源端之间导通,并在下次读写操作开始后的预设时间之后,通过所述第一预充电单元控制所述数据端与所述第一电源端之间断开。

[0046] 本发明还提供了一种计算机设备,包括存储器和处理器,所述存储器存储有计算机程序,所述处理器执行所述计算机程序时实现如上任一实施例中所述的控制方法的步骤。

[0047] 上述存储器电路及存储器预充电的控制方法当存储器处于行激活状态,且未进行读写操作时,通过第二预充电单元控制数据端与第二电源端之间断开,且通过第一预充电单元控制数据端与第一电源端之间断开,此时没有向数据端输入第一预充电压,也没有向数据端输入第二预充电压,使得存储器在未进行读写操作时,即使处于行激活状态也不会向数据线进行预充电,从而能够避免在存储器处于行激活状态且未进行读写操作时对激活电流的浪费;当读写操作的命令到来时,再将数据端拉至第一预充电压,这样既能够减少耗电,又不会影响存储器的正常工作。同时,在第一次读写操作完成后的预设时间之后,存储器电路即通过数据端向数据线输入第一预充电压,使得存储器在后续的读写操作周期中,无需单独的预设时间进行预充电,提升了存储器的读写速度。

#### 附图说明

[0048] 为了更清楚地说明本申请实施例或传统技术中的技术方案,下面将对实施例或传统技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本申请的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

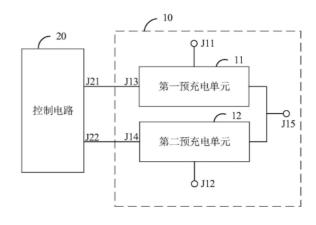

[0049] 图1为一实施例中提供的存储器电路的结构框图;

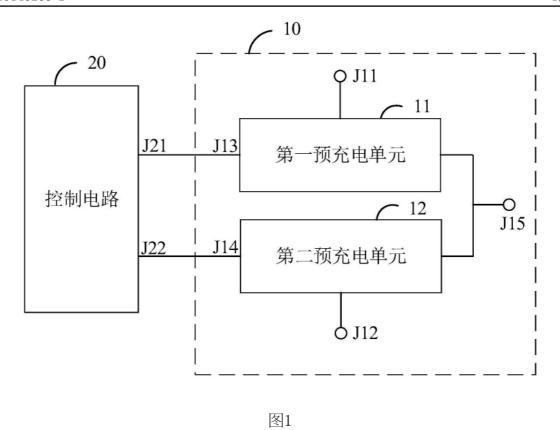

[0050] 图2为一实施例中提供的存储器电路中各信号的波形图:

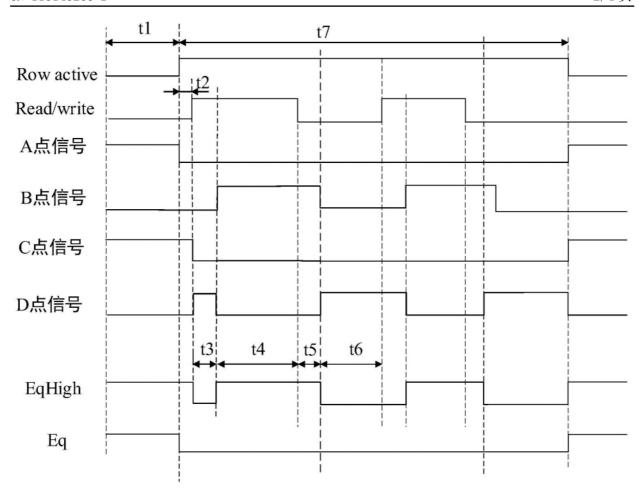

[0051] 图3为一实施例中提供的控制电路的电路图:

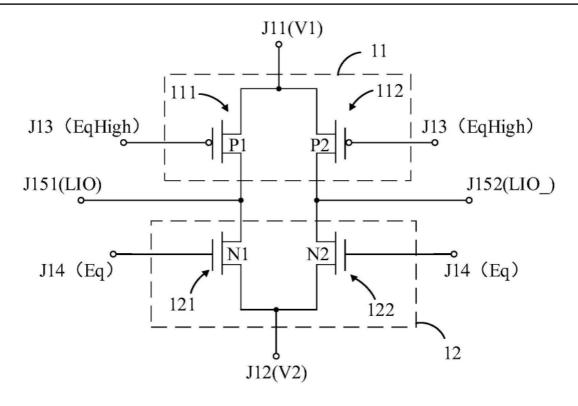

[0052] 图4为一实施例中提供的预充电电路的电路图;

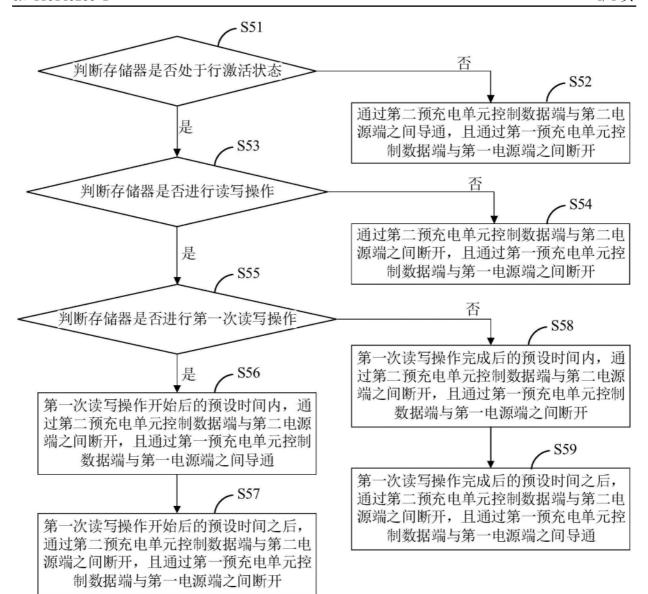

[0053] 图5为一实施例中提供的存储器预充电的控制方法的流程图。

[0054] 附图标记说明:

[0055] 10、预充电电路;11、第一预充电单元;111、第一开关单元;112、第二开关单元;12、第二预充电单元;121、第三开关单元;122、第四开关单元;20、控制电路;21、第一反相单元;22、延时单元;23、第二反相单元;24、锁存单元;25、三输入或非门;26、第三反相单元;27、反相器。

## 具体实施方式

[0056] 为了便于理解本申请,下面将参照相关附图对本申请进行更全面的描述。附图中给出了本申请的首选实施例。但是,本申请可以以许多不同的形式来实现,并不限于本文所描述的实施例。相反地,提供这些实施例的目的是使对本申请的公开内容更加透彻全面。

[0057] 除非另有定义,本文所使用的所有的技术和科学术语与属于本申请的技术领域的技术人员通常理解的含义相同。本文中在本申请的说明书中所使用的术语只是为了描述具体的实施例的目的,不是旨在于限制本申请。

[0058] 应当明白,当元件或层被称为"在...上"、"与...相邻"、"连接到"或"耦合到"其它元件或层时,其可以直接地在其它元件或层上、与之相邻、连接或耦合到其它元件或层,或者可以存在居间的元件或层。相反,当元件被称为"直接在...上"、"与...直接相邻"、"直接连接到"或"直接耦合到"其它元件或层时,则不存在居间的元件或层。应当明白,尽管可使用术语第一、第二、第三等描述各种元件、部件、区、层、掺杂类型和/或部分,这些元件、部件、区、层、掺杂类型和/或部分不应当被这些术语限制。这些术语仅仅用来区分一个元件、部件、区、层、掺杂类型或部分与另一个元件、部件、区、层、掺杂类型或部分。因此,在不脱离本发明教导之下,下面讨论的第一元件、部件、区、层、掺杂类型或部分可表示为第二元件、部件、区、层或部分;举例来说,可以将第一预充电单元称为第二预充电单元,且类似地,可以将第二预充电单元称为第一预充电单元;第一预充电单元与第二预充电单元为不同的预充电单元。

[0059] 空间关系术语例如"在...下"、"在...下面"、"下面的"、"在...之下"、"在...之上"、"上面的"等,在这里可以用于描述图中所示的一个元件或特征与其它元件或特征的关系。应当明白,除了图中所示的取向以外,空间关系术语还包括使用和操作中的器件的不同取向。例如,如果附图中的器件翻转,描述为"在其它元件下面"或"在其之下"或"在其下"元件或特征将取向为在其它元件或特征"上"。因此,示例性术语"在...下面"和"在...下"可包括上和下两个取向。此外,器件也可以包括另外地取向(譬如,旋转90度或其它取向),并且在此使用的空间描述语相应地被解释。

[0060] 在此使用时,单数形式的"一"、"一个"和"所述/该"也可以包括复数形式,除非上下文清楚指出另外的方式。还应明白,当术语"组成"和/或"包括"在该说明书中使用时,可以确定所述特征、整数、步骤、操作、元件和/或部件的存在,但不排除一个或更多其它的特征、整数、步骤、操作、元件、部件和/或组的存在或添加。同时,在此使用时,术语"和/或"包括相关所列项目的任何及所有组合。

[0061] 图1为一实施例中的存储器电路的结构框图。如图1所示,存储器电路包括预充电电路10及控制电路20。预充电电路10包括第一预充电单元11,第二预充电单元12,第一电源端J11,第二电源端J12,第一控制端J13,第二控制端J14及数据端J15。第一预充电单元11与第一电源端J11、第一控制端J13及数据端J15连接,第一控制端J13即为第一预充电单元11的控制端。第二预充电单元12与第二电源端J12、第二控制端J14及数据端J15连接,第二控制端J14即为第二预充电单元12的控制端。第一电源端J11输入第一预充电压,第二电源端J12输入第二预充电压。

[0062] 控制电路20的第一输出端J21与第一控制端J13连接,控制电路20通过控制其第一输出端J21的信号控制第一预充电单元11工作,具体为通过第一预充电单元11控制第一电源端J11与数据端J15之间导通,从而向数据端J15输入第一预充电压,或者通过第一预充电单元11控制第一电源端J11与数据端J15之间断开,从而停止向数据端J15输入第一预充电压;控制电路20的第二输出端J22与第二控制端J14连接,控制电路20还通过控制其第二输出端J22的信号控制第二预充电单元12工作,具体为通过第二预充电单元12控制第二电源端J12与数据端J15之间导通,从而向数据端J15输入第二预充电压,或者通过第二预充电单元12控制第二电源端J12与数据端J15之间断开,从而停止向数据端J15输入第二预充电压。第一预充电压和第二预充电压可以根据实际需求进行设置,两者可以设置为不相等。数据端J15可以连接存储器中的数据线,从而可以通过存储器电路对数据线的预充电进行控制。本实施例中的数据线可以是存储器中的局部数据线(LI0,local input output,也可以称为本地输入输出线)。

[0063] 具体的,控制电路20用于:

[0064] 当存储器未处于行激活状态时,通过第二预充电单元12控制数据端J15与第二电源端J12之间导通,且通过第一预充电单元11控制数据端J15与第一电源端J11之间断开;

[0065] 当存储器处于行激活状态,且未进行读写操作时,通过第二预充电单元12控制数据端J15与第二电源端J12之间断开,且通过第一预充电单元11控制数据端J15与第一电源端J11之间断开;

[0066] 当存储器处于行激活状态,且第一次读写操作开始后的预设时间内,通过第二预充电单元12控制数据端J15与第二电源端J12之间断开,且通过第一预充电单元11控制数据端J15与第一电源端J11之间导通;

[0067] 当存储器处于行激活状态,且第一次读写操作开始后的预设时间之后,通过第二 预充电单元12控制数据端J15与第二电源端J12之间断开,且通过第一预充电单元11控制数据端J15与第一电源端J11之间断开;

[0068] 当存储器处于行激活状态,且第一次读写操作完成后的预设时间内,通过第二预充电单元12控制数据端J15与第二电源端J12之间断开,且通过第一预充电单元11控制数据端J15与第一电源端J11之间继续断开;

[0069] 当存储器处于行激活状态,且第一次读写操作完成后的预设时间之后,通过第二 预充电单元12控制数据端J15与第二电源端J12之间断开,且通过第一预充电单元11控制数据端J15与第一电源端J11之间导通。

[0070] 在一些示例中,控制电路20可以具有第一输入端(图1未示出)和第二输入端(图1未示出)。控制电路20的第一输入端可以与存储器的行激活信号线连接,从而获取存储器的

行激活信号,控制电路20可以根据存储器的行激活信号判断存储器是否处于行激活状态。 控制电路20的第二输入端可以与存储器的读写信号线连接,从而获取存储器的读写信号, 控制电路20可以根据存储器的读写信号判断存储器是否开始读写操作。

[0071] 在其他示例中,控制电路20也可以通过其他方式来判断存储器是否处于行激活状态及是否开始读写操作。

[0072] 在一些示例中,当控制电路20根据存储器的行激活信号判断存储器是否处于行激活状态,且根据存储器的读写信号判断存储器是否开始读写操作时,请参阅图1和图2,当行激活信号Row active为高电平时存储器处于行激活状态,当行激活信号Row active为低电平时存储器未处于行激活状态;当读写信号Read/Write为高电平时存储器进行读写操作,当读写信号Read/Write为低电平时存储器未进行读写操作。控制电路20根据行激活信号Row active控制向预充电电路10的第一控制端J13(第一预充电单元11的控制端)输出的第一控制信号EqHigh,第一预充电单元11根据第一控制信号EqHigh控制第一电源端J11与数据端J15之间是否导通,从而控制是否向数据端J15输入第一预充电压。控制电路20根据读写信号Read/Write控制向预充电电路10的第二控制端J14(第二预充电单元12的控制端)输出的第二控制信号Eq,第二预充电单元12根据第二控制信号Eq控制第二电源端J12与数据端J15之间是否导通,从而控制是否向数据端J15输入第二预充电压。

[0073] 在t1时间段内,行激活信号Row active为低电平,存储器未处于行激活状态。控制电路20控制其第二输出端J22输出的第二控制信号Eq为高电平,第二预充电单元12的控制端接收到高电平后控制第二电源端J12与数据端J15之间导通;控制电路20还控制其第一输出端J21输出的第一控制信号EqHigh为高电平,第一预充电单元11的控制端接收到高电平后控制第一电源端J11与数据端J15之间断开;从而当存储器未处于行激活状态时,存储器电路通过数据端J15向数据线输入第二预充电压。

[0074] 在t2时间段内,行激活信号Row active为高电平,存储器处于行激活状态;且读写信号Read/Write为低电平,存储器未进行读写操作。控制电路20控制其第二输出端J22输出的第二控制信号Eq为低电平,第二预充电单元12的控制端接收到低电平后控制第二电源端J12与数据端J15之间断开;控制电路20还控制其第一输出端J21输出的第一控制信号EqHigh为高电平,第一预充电单元11的控制端接收到高电平后控制第一电源端J11与数据端J15之间断开;从而当存储器处于行激活状态,且未进行读写操作时,存储器电路没有通过数据端J15向数据线输入第一预充电压,也没有通过数据端J15向数据线输入第二预充电压,此时虽然存储器已经处于行激活状态,但读写信号Read/Write为低电平,存储器未进行读写操作,也没有进行预充电操作。

[0075] 在第一次读写操作开始后的预设时间t3时间段内,行激活信号Row active为高电平,存储器处于行激活状态;且读写信号Read/Write为高电平,存储器开始进行读写操作。控制电路20控制其第二输出端J22输出的第二控制信号Eq为低电平,第二预充电单元12的控制端接收到低电平后控制第二电源端J12与数据端J15之间断开;控制电路20还控制其第一输出端J21输出的第一控制信号EqHigh为低电平,第一预充电单元11的控制端接收到低电平后控制第一电源端J11与数据端J15之间导通;从而当存储器处于行激活状态,且第一次读写操作开始后的预设时间t3时间段内,存储器电路通过数据端J15向数据线输入第一预充电压,为后续进行数据读写做准备。

[0076] 在t4时间段内,行激活信号Row active为高电平,存储器处于行激活状态;且读写信号Read/Write为高电平,第一次读写操作开始(读写信号Read/Write当上升沿到来时,存储器开始进行读写操作)后的预设时间t3之后,直至第一次读写操作结束(读写信号Read/Write当下降沿到来时,存储器开始结束读写操作)。控制电路20控制其第二输出端J22输出的第二控制信号Eq为低电平,第二预充电单元12的控制端接收到低电平后控制第二电源端J12与数据端J15之间断开;控制电路20还控制其第一输出端J21输出的第一控制信号EqHigh为高电平,第一预充电单元11的控制端接收到高电平后控制第一电源端J11与数据端J15之间断开;从而当存储器处于行激活状态,且第一次读写操作开始后的预设时间t3之后,直至第一次读写操作结束,存储器电路没有通过数据端J15向数据线输入第一预充电压,也没有通过数据端J15向数据线输入第二预充电压。此时存储阵列正在进行数据读写,当读操作时,数据线上的电压由存储单元中存储的数据(0或1)决定;当写操作时,数据线上的电压由外部写入的数据决定。

[0077] 在第一次读写操作完成后的预设时间t5时间段内,行激活信号Row active为高电平,存储器处于行激活状态;且读写信号Read/Write为低电平,存储器未进行读写操作。控制电路20控制其第二输出端J22输出的第二控制信号Eq为低电平,第二预充电单元12的控制端接收到低电平后控制第二电源端J12与数据端J15之间断开;控制电路20还控制其第一输出端J21输出的第一控制信号EqHigh为高电平,第一预充电单元11的控制端接收到高电平后控制第一电源端J11与数据端J15之间继续断开;从而当存储器处于行激活状态,且第一次读写操作完成后的预设时间t5时间段内,存储器电路没有通过数据端J15向数据线输入第一预充电压,也没有通过数据端J15向数据线输入第二预充电压。

[0078] 在t6时间段内,行激活信号Row active为高电平,存储器处于行激活状态;且读写信号Read/Write为低电平,第一次读写操作完成后的预设时间t5之后,控制电路20控制其第二输出端J22输出的第二控制信号Eq为低电平,第二预充电单元12的控制端接收到低电平后控制第二电源端J12与数据端J15之间断开;控制电路20还控制其第一输出端J21输出的第一控制信号EqHigh为低电平,第一预充电单元11的控制端接收到低电平后控制第一电源端J11与数据端J15之间导通;从而当存储器处于行激活状态,且第一次读写操作完成后的预设时间t5之后,存储器电路通过数据端J15向数据线输入第一预充电压。t6时间段结束后开始第二次读写操作。

[0079] 在另一些实施例中,还可以配置为:

[0080] 当行激活信号Row active为高电平时,存储器未处于行激活状态,控制电路20控制其自身的第一输出端J21输出的第一控制信号EqHigh为高电平;控制电路20还控制其自身的第二输出端J22输出的第二控制信号Eq为高电平。

[0081] 当行激活信号Row active为低电平时,存储器处于行激活状态,且读写信号Read/Write为高电平时,存储器未进行读写操作,控制电路20控制其自身的第一输出端J21输出的第一控制信号EqHigh为高电平;控制电路20还控制其自身的第二输出端J22输出的第二控制信号Eq为低电平。

[0082] 当行激活信号Row active为低电平时,存储器处于行激活状态,且读写信号Read/Write为低电平时,存储器进行第一次读写操作,第一次读写操作开始后的预设时间内,控制电路20控制其自身的第一输出端J21输出的第一控制信号EqHigh为低电平;控制电路20

还控制其自身的第二输出端J22输出的第二控制信号Eq为低电平。

[0083] 当行激活信号Row active为低电平时,存储器处于行激活状态,且读写信号Read/Write为低电平时,存储器进行第一次读写操作,第一次读写操作开始后的预设时间之后,控制电路20控制其自身的第一输出端J21输出的第一控制信号EqHigh为高电平;控制电路20还控制其自身的第二输出端J22输出的第二控制信号Eq为低电平。

[0084] 当行激活信号Row active为低电平时,存储器处于行激活状态,且读写信号Read/Write为高电平时,存储器第一次读写操作完成后的预设时间内,控制电路20继续控制其自身的第一输出端J21输出的第一控制信号EqHigh为高电平;控制电路20还控制其自身的第二输出端J22输出的第二控制信号Eq为低电平。

[0085] 当行激活信号Row active为低电平时,存储器处于行激活状态,且读写信号Read/Write为高电平时,存储器第一次读写操作完成后的预设时间之后,控制电路20控制其自身的第一输出端J21输出的第一控制信号EqHigh为低电平;控制电路20还控制其自身的第二输出端J22输出的第二控制信号Eq为低电平。

[0086] 在又一些实施例中,还可以配置为:

[0087] 当行激活信号Row active为低电平时,存储器未处于行激活状态,控制电路20控制其自身的第一输出端J21输出的第一控制信号EqHigh为低电平;控制电路20还控制其自身的第二输出端J22输出的第二控制信号Eq为低电平。

[0088] 当行激活信号Row active为高电平时,存储器处于行激活状态,且读写信号Read/Write为低电平时,存储器未进行读写操作,控制电路20控制其自身的第一输出端J21输出的第一控制信号EqHigh为低电平;控制电路20还控制其自身的第二输出端J22输出的第二控制信号Eq为高电平。

[0089] 当行激活信号Row active为高电平时,存储器处于行激活状态,且读写信号Read/Write为高电平时,存储器进行第一次读写操作,第一次读写操作开始后的预设时间内,控制电路20控制其自身的第一输出端J21输出的第一控制信号EqHigh为高电平;控制电路20还控制其自身的第二输出端J22输出的第二控制信号Eq为高电平。

[0090] 当行激活信号Row active为高电平时,存储器处于行激活状态,且读写信号Read/Write为高电平时,存储器进行第一次读写操作,第一次读写操作开始后的预设时间之后,控制电路20控制其自身的第一输出端J21输出的第一控制信号Eq为高电平。

[0091] 当行激活信号Row active为高电平时,存储器处于行激活状态,且读写信号Read/Write为低电平时,存储器第一次读写操作完成后的预设时间内,控制电路20继续控制其自身的第一输出端J21输出的第一控制信号EqHigh为低电平;控制电路20还控制其自身的第二输出端J22输出的第二控制信号Eq为高电平。

[0092] 当行激活信号Row active为高电平时,存储器处于行激活状态,且读写信号Read/Write为低电平时,存储器第一次读写操作完成后的预设时间之后,控制电路20控制其自身的第一输出端J21输出的第一控制信号EqHigh为高电平;控制电路20还控制其自身的第二输出端J22输出的第二控制信号Eq为高电平。

[0093] 在其他示例中,行激活信号Row active与存储器的行激活状态,读写信号Read/Write与存储器读写状态,控制电路20的输入端与输出端的控制关系以及预充电电路10的

控制关系还可以是其他方式,此处不再一一赘述。

[0094] 上述存储器电路当存储器处于行激活状态,且未进行读写操作时,通过第二预充电单元12控制数据端J15与第二电源端J12之间断开,且通过第一预充电单元11控制数据端J15与第一电源端J11之间断开,此时没有向数据端J15输入第一充电电压,也没有向数据端J15输入第二充电电压,使得不会向数据线进行预充电,从而能够避免在存储器处于行激活状态且未进行读写操作时对电流的浪费。同时,在第一次读写操作完成后的预设时间之后,存储器电路即通过数据端J15向数据线输入第一预充电压,为后续的读写操作做准备,使得存储器在后续的读写操作周期中,无需单独的预设时间进行预充电,提升了存储器的读写速度。

[0095] 在一些示例中,第一预充电压为存储器的电源电压VCCA,第二预充电压为存储器的电源电压的一半即1/2VCCA。在其他示例中,也可以根据实际需求设置第一预充电压和第二预充电压的大小。

[0096] 在一些示例中,存储器在行激活状态的一个周期内进行多次读写操作,在所述存储器的行激活状态的一个周期内,每次读写操作完成后的预设时间之后,控制电路20通过第一预充电单元11控制数据端J15与第一电源端J11之间导通,存储器电路即通过数据端J15向数据线输入第一预充电压,为后续的读写操作做准备,提升了存储器的读写速度;并在下次读写操作开始后的预设时间之后,通过第一预充电单元11控制数据端J15与第一电源端J11之间断开,此时存储阵列正在进行数据读写。

[0097] 仅示例性的,仍然参阅图2,在存储器的行激活状态的一个周期t7内,读写信号Read/Write出现多个高电平即进行多次读写。读写信号Read/Write第一个上升沿到来时,即第一次读写开始,控制电路20的第一输出端J21输出的第一控制信号EqHigh跳变为低电平,并维持低电平预设时间t3后跳变到高电平。直到第一次读写操作完成后的预设时间之后,控制电路20的第一输出端J21输出的第一控制信号EqHigh再次跳变到低电平,并维持低电平至下一个读写操作开始后的预设时间后,跳变为高电平。以此类推,直到存储器未处于行激活状态。在存储器的行激活状态的一个周期结束时,行激活信号Row active由高电平跳变至低电平,同时,读写信号Read/Write维持在低电平,A点信号由低电平跳变至高电平,B点信号维持在低电平,C点信号由低电平跳变至高电平,所述第一控制信号EqHigh由低电平跳变至高电平,第二控制信号Eq由低电平跳变至高电平,所述第一控制信号EqHigh由低电平跳变至高电平,第二控制信号Eq由低电平跳变至高电平。

[0098] 本实施例中,当第一控制信号EqHigh为低电平时,第一预充电电路10控制第一电源端J11和数据端J15之间导通,第一电源端J11向数据端J15输入第一预充电压;当第一控制信号EqHigh为高电平时,第一预充电电路10控制第一电源端J11和数据端J15之间断开,第一电源端J11停止向数据端J15输入第一预充电压。

[0099] 在一些示例中,控制电路20的第一输入端J23输入行激活信号Row active,控制电路20的第二输入端J24输入读写信号Read/Write;当行激活信号Row active为低电平时,存储器未处于行激活状态;当行激活信号Row active为高电平时,存储器处于行激活状态;当读写信号Read/Write为低电平时,存储器未进行读写操作;当读写信号Read/Write为高电平时,存储器进行读写操作。

[0100] 在一些示例中,请参阅图1至图3,控制电路20包括第一反相单元21、延时单元22、

第二反相单元23、锁存单元24、三输入或非门25、第三反相单元26;锁存单元24包括第一输入端、第二输入端及输出端。

[0101] 第一反相单元21的输入端与锁存单元24的第一输入端连接并作为控制电路20的第一输入端J23,即第一反相单元21的输入端输入的信号为行激活信号Row active;第一反相单元21的第一输出端和第二输出端(参阅图3中A点)均用于输出行激活信号Row active 反相后的信号。第一反相单元21的第一输出端为控制电路20的第二输出端J22,使得控制电路20输出给第二预充电单元12的控制端的第二控制信号Eq为行激活信号Row active 反相后的信号。

[0102] 三输入或非门25的第一输入端与第一反相单元21的第二输出端连接,三输入或非门25的第一输入端输入的信号即为行激活信号Row active反相后的信号。

[0103] 延时单元22的输入端与第二反相单元23的输入端连接并作为控制电路20的第二输入端J24,延时单元22的输出端(参阅图3中B点)与三输入或非门25的第二输入端连接,即三输入或非门25的第二输入端输入的信号为读写信号Read/write延迟预设时间后的信号;延时单元22用于将读写信号Read/write延迟预设时间后输出;第二反相单元23用于输出读写信号Read/write反相后的信号。

[0104] 锁存单元24的第二输入端与第二反相单元23的输出端连接,即锁存单元24的第一输入端输入的信号为行激活信号Row active,锁存单元24的第二输入端输入的信号为读写信号Read/write反相后的信号,锁存单元24的输出端(参阅图3中C点)与三输入或非门25的第三输入端连接。

[0105] 第三反相单元26的输入端与三输入或非门25的输出端(参阅图3中D点)连接,第三反相单元26的输出端作为控制电路20的第一输出端J21;第三反相单元26用于将输入端输入的信号进行反相后输出,第三反相单元26的输出端为控制电路20的第一输出端J21。

[0106] 具体的,在t1时间段内,在t1时间段内,第一反相单元21的输入端输入的行激活信号Row active为低电平,存储器未处于行激活状态,经过第一反相单元21反相后,第一反相单元21的第一输出端输出的第二控制信号Eq为高电平,第二预充电单元12的控制端接收到高电平后控制第二电源端J12与数据端J15之间导通,第二电源端J12向数据端J15输入第二预充电压;锁存单元24的第一输入端输入的行激活信号Row active为低电平,从而输出的信号,即C点信号为高电平。

[0107] 在t2时间段内,第一反相单元21的输入端输入的行激活信号Row active为高电平,存储器处于行激活状态,经过第一反相单元21反相后,第一反相单元21的第二输出端输出的信号,即A点信号为低电平;即三输入或非门25的第一输入端输入的信号为低电平;延时单元22的输入端和第二反相单元23的输入端输入的信号均为读写信号Read/Write,为低电平,存储器未进行读写操作,延时单元22向三输入或非门25的第二输入端输入的信号为读写信号Read/Write延时预设时间后的信号,即B点信号,仍然为低电平。锁存单元24的第一输入端输入的行激活信号Row active为高电平,锁存单元24的第二输入端输入的读写信号Read/write反相后的信号为高电平,锁存单元24的输出端输出的信号,即C点信号维持上一状态不变,为高电平;从而三输入或非门25输出端输出的信号即D点信号为低电平。经过第三反相单元26的反相后,第三反相单元26的输出端向第一预充电单元11的控制端输入高电平,从而第一预充电单元11控制第一电源端J11和数据端J15之间断开,第一电源端J11未

向数据端J15输入第一预充电压。

[0108] 在第一次读写操作开始后的预设时间t3内,第一反相单元21的输入端输入的行激活信号Row active为高电平,存储器处于行激活状态,经过第一反相单元21反相后,第一反相单元21的第二输出端输出的信号即A点信号为低电平,即三输入或非门25的第一输入端输入的信号为低电平;延时单元22的输入端和第二反相单元23的输入端输入的读写信号Read/Write为高电平,存储器进行读写操作,延时单元22向三输入或非门25的第二输入端输入的信号为读写信号Read/Write延时预设时间t3后的信号,即B点信号,仍然为低电平;锁存单元24的第一输入端输入的行激活信号Row active为高电平,锁存单元24的第二输入端输入的读写信号Read/write反相后的信号为低电平,锁存单元24的输出端输出的信号,即C点信号产生跳变,变为低电平;从而三输入或非门25输出端输出的信号,即D点信号为高电平。经过第三反相单元26的反相后,第三反相单元26的输出端向第一预充电单元11的控制端输入低电平,从而第一预充电单元11控制第一电源端J11和数据端J15之间导通,第一电源端J11向数据端J15输入第一预充电压。

[0109] 在第一次读写操作开始后的预设时间t3之后,直至第一次读写操作结束的t4时间段内,第一反相单元21的输入端输入的行激活信号Row active为高电平,存储器处于行激活状态,经过第一反相单元21反相后,第一反相单元21的第二输出端输出的信号,即A点信号为低电平,即三输入或非门25的第一输入端输入的信号为低电平;延时单元22的输入端和第二反相单元23的输入端输入的读写信号Read/Write为高电平,存储器进行读写操作,延时单元22向三输入或非门25的第二输入端输入的信号为读写信号Read/Write延时预设时间t3后的信号,即B点信号,变为高电平;锁存单元24的第一输入端输入的行激活信号Rowactive为高电平,锁存单元24的第二输入端输入的读写信号Read/write反相后的信号为低电平,锁存单元24的输出端输出的信号,即C点信号保持不变,为低电平;从而三输入或非门25输出端输出的信号,即D点信号为低电平。经过第三反相单元26的反相后,第三反相单元26的输出端向第一预充电单元11的控制端输入高电平,从而第一预充电单元11控制第一电源端J11和数据端J15之间断开,第一电源端J11停止向数据端J15输入第一预充电压。

[0110] 在第一次读写操作完成后的预设时间t5内,第一反相单元21的输入端输入的行激活信号Row active为高电平,存储器处于行激活状态,经过第一反相单元21反相后,第一反相单元21的第二输出端输出的信号,即A点信号为低电平,即三输入或非门25的第一输入端输入的信号为低电平;延时单元22的输入端和第二反相单元23的输入端输入的读写信号Read/Write为低电平,存储器未进行读写操作,延时单元22向三输入或非门25的第二输入端输入的信号为读写信号Read/Write延时预设时间t5后的信号,即B点信号仍为高电平;锁存单元24的第一输入端输入的行激活信号Row active为高电平,锁存单元24的第二输入端输入的读写信号Read/write反相后的信号为高电平,锁存单元24的输出端输出的信号,即C点信号维持上一状态不变,为低电平;从而三输入或非门25输出端输出的信号,即D点信号为低电平。经过第三反相单元26的反相后,第三反相单元26的输出端向第一预充电单元11的控制端输入高电平,从而第一预充电单元11控制第一电源端J11仍然停止向数据端J15输入第一预充电压。

[0111] 在第一次读写操作完成后的预设时间t5之后,直至下一次读写操作开始的t6时间段内,第一反相单元21的输入端输入的行激活信号Row active为高电平,存储器处于行激

活状态,经过第一反相单元21反相后,第一反相单元21的第二输出端输出的信号,即A点信号为低电平,即三输入或非门25的第一输入端输入的信号为低电平;延时单元22的输入端和第二反相单元23的输入端输入的读写信号Read/Write为低电平,存储器未进行读写操作,延时单元22向三输入或非门25的第二输入端输入的信号为读写信号Read/Write延时预设时间t5后的信号,即B点信号变为低电平;锁存单元24的第一输入端输入的行激活信号Row active为高电平,锁存单元24的第二输入端输入的读写信号Read/write反相后的信号为高电平,锁存单元24的输出端输出的信号,即C点信号维持上一状态不变,为低电平;从而三输入或非门25输出端输出的信号,即D点信号为高电平。经过第三反相单元26的反相后,第三反相单元26的输出端向第一预充电单元11的控制端输入低电平,从而第一预充电单元11控制第一电源端J11和数据端J15之间导通,第一电源端J11向数据端J15输入第一预充电压。

[0112] 在整个t7时间段内,第一反相单元21的输入端输入的行激活信号Row active为高电平,存储器处于行激活状态,经过第一反相单元21反相后,第一反相单元21的第一输出端输出的第二控制信号Eq为低电平,第二预充电单元12的控制端接收到低电平后控制第二电源端J12与数据端J15之间断开,第二电源端J12停止向数据端J15输入第二预充电压。

[0113] 在一些示例中,请参阅图3,第一反相单元21包括N个依次串接的反相器27,第一反相单元21中的最后一个反相器27的输出端为第一反相单元21的第一输出端,第一反相单元21中的第N<sub>x</sub>个反相器27的输出端为第一反相单元21的第二输出端。其中,N、N<sub>x</sub>均为正奇数且N<sub>y</sub>小于或等于N。图3示例中,N等于3,N<sub>x</sub>等于1。

[0114] 在一些示例中,请参阅图3,延时单元22包括M个依次串联的反相器27。其中,M为正偶数。图3示例中,M等于6。在其他示例中,延时单元22也可以采用其他为本领域技术人员所熟知的任意电路结构。

[0115] 在一些示例中,请参阅图3,第二反相单元23包括Q个依次串接的反相器27。其中,Q为正奇数。图3示例中,Q等于1。

[0116] 在一些示例中,请参阅图3,第三反相单元26包括P个依次串接的反相器27。其中,P为正奇数。图3示例中,P等于1。

[0117] 需要说明的是,第一反相单元21中N和N<sub>x</sub>、延时单元22中M、第二反相单元23中Q以及第三反相单元26中P均不限于图3示例中的数量。

[0118] 在一些示例中,请参阅图3,锁存单元24包括锁存器。在其他示例中,锁存单元24也可以采用本领域技术人员所熟知的任意电路结构。

[0119] 在一些示例中,请参阅图3,锁存单元24包括:第一与非门28及第二与非门29。其中,第一与非门28的第一输入端作为锁存单元24的第一输入端,第一与非门28的第二输入端与第二与非门29的输出端连接,第一与非门28的输出端作为锁存单元24的输出端与三输入或非门25的第三输入端及第二与非门29的第一输入端连接,第二与非门29的第二输入端作为锁存单元24的第二输入端。

[0120] 在一些示例中,请参阅图1和图4,数据端J15包括第一数据端J151和第二数据端J152,第一数据端J151和第二数据端J152接收互为相反的数据信号。譬如,第一数据端J151可以与局部数据线连接,从而接收LI0信号;第二数据端J152可以与互补局部数据线连接,从而接收LI0\_信号。第一预充电单元11包括第一开关单元111和第二开关单元112,第一开

关单元111的第一电连接端和第二开关单元112的第一电连接端均与第一电源端J11连接,第一电源端J11输入第一预充电压V1;第一开关单元111的控制端和第二开关单元112的控制端均与第一控制端J13连接,从而获取第一控制信号EqHigh。第一开关单元111的第二电连接端与第一数据端J151连接,第二开关单元112的第二电连接端与第二数据端J152连接;[0121] 在一些示例中,第一开关单元111和第二开关单元112的开关特性可以相同,控制电路20的第一输出端J21输出的第一控制信号EqHigh控制第一开关单元111的第一电连接端和第二电连接端之间导通,同时还控制第二开关单元112的第一电连接端和第二电连接端之间导通,使得第一电源端J11同时向第一数据端J151和第二数据端J152输入第一预充电压V1;或者控制电路20的第一输出端J21输出的第一控制信号EqHigh控制第一开关单元11的第一电连接端和第二电连接端之间断开,同时还控制第二开关单元112的第一电连接端和第二电连接端之间断开,同时还控制第二开关单元112的第一电连接端和第二电连接端之间断开,同时还控制第二开关单元112的第一电连接端和第二电连接端之间断开,使得第一电源端J11同时停止向第一数据端J151和第二数据端J152输入第一预充电压V1。

[0122] 在一些示例中,第二预充电单元12包括第三开关单元121和第四开关单元122,第 三开关单元121的第一电连接端和第四开关单元122的第一电连接端均与第二电源端J12连接,从而输入第二预充电压V2;第三开关单元121的控制端和第四开关单元122的控制端均与第二控制端J14连接,从而获取第二控制信号Eq。第三开关单元121的第二电连接端与第一数据端J151连接,第四开关单元122的第二电连接端与第二数据端J152连接。

[0123] 在一些示例中,第三开关单元121和第四开关单元122的开关特性可以相同,控制电路20的第二输出端J22输出的第二控制信号Eq控制第三开关单元121的第一电连接端和第二电连接端之间导通,同时还控制第四开关单元122的第一电连接端和第二电连接端之间导通,使得第二电源端J12同时向第一数据端J151和第二数据端J152输入第二预充电压V2;或者控制电路20的第二输出端输出的第二控制信号Eq控制第三开关单元121的第一电连接端和第二电连接端之间断开,同时还控制第四开关单元122的第一电连接端和第二电连接端之间断开,使得第二电源端J12同时停止向第一数据端J151和第二数据端J152输入第二预充电压V2。

[0124] 在一些示例中,第一开关单元111和第二开关单元112均包括PMOS管,第一开关单元111的第一电连接端和第二开关单元112的第一电连接端均为PMOS管的源极,第一开关单元111的第二电连接端和第二开关单元112的第二电连接端均为PMOS管的漏极,第一开关单元111的控制端和第二开关单元112的控制端均为PMOS管的栅极。譬如,可以参阅图4,第一开关单元包括PMOS管P1,第二开关单元包括PMOS管P2。

[0125] 具体的,当第一控制信号EqHigh为高电平时,PMOS管P1的源极和漏极之间断开且PMOS管P2的源极和漏极之间断开,第一电源端J11停止向第一数据端J151和第二数据端J152输入第一预充电压V1;当第一控制信号EqHigh为低电平时,PMOS管P1的源极和漏极之间导通且PMOS管P2的源极和漏极之间导通,第一电源端J11向第一数据端J151和第二数据端J152输入第一预充电压V1。

[0126] 在一些示例中,第三开关单元121和第四开关单元122均包括NMOS管,第三开关单元121的第一电连接端和第四开关单元122的第一电连接端均为NMOS管的源极,第三开关单元121的第二电连接端和第四开关单元122的第二电连接端均为NMOS管的漏极,第三开关单元121的控制端和第四开关单元122的控制端均为NMOS管的栅极。譬如,可以参阅图4,第三

开关单元包括NMOS管N1,第四开关单元包括NMOS管N2。

[0127] 具体的,当第二控制信号Eq为高电平时,NMOS管N1的源极和漏极之间导通且NMOS管N2的源极和漏极之间导通,第二电源端J12向第一数据端J151和第二数据端J152输入第二预充电压V2;当第二控制信号Eq为低电平时,NMOS管N1的源极和漏极之间断开且NMOS管N2的源极和漏极之间断开,第二电源端J12停止向第一数据端J151和第二数据端J152输入第二预充电压V2。

[0128] 本申请还提供一种存储器预充电的控制方法,存储器预充电的控制方法应用于存储器的预充电电路。请继续参阅图1,预充电电路包括第一预充电单11,第二预充电单元12,第一电源端J11,第二电源端J12,第一控制端J13,第二控制端J14及数据端J15;第一预充电单元11与第一电源端J11、第一控制端J13及数据端J15连接;第二预充电单元12与第二电源端J12、第二控制端J14及数据端J15连接;第一电源端J11输入第一预充电压,第二电源端J12输入第二预充电压。如图5所示,存储器预充电的控制方法包括:

[0129] 步骤S51:判断存储器是否处于行激活状态。

[0130] 若是,则执行步骤S53;否则,执行步骤S52。

[0131] 步骤S52:通过第二预充电单元12控制数据端J15与第二电源端J12之间导通,且通过第一预充电单元11控制数据端J15与第一电源端J11之间断开。

[0132] 步骤S53:判断存储器是否进行读写操作。

[0133] 若是,则执行步骤S55;否则,执行步骤S54。

[0134] 步骤S54:通过第二预充电单元12控制数据端J15与第二电源端J12之间断开,且通过第一预充电单元11控制数据端J15与第一电源端J11之间断开。

[0135] 步骤S55:判断存储器是否进行第一次读写操作。

[0136] 若是,则依次执行步骤S56及S57;否则,依次执行步骤S58及S59。

[0137] 步骤S56:第一次读写操作开始后的预设时间内,通过第二预充电单元12控制数据端J15与第二电源端J12之间断开,且通过第一预充电单元11控制数据端J15与第一电源端J11之间导通。

[0138] 步骤S57:第一次读写操作开始后的预设时间之后,通过第二预充电单元12控制数据端J15与第二电源端J12之间断开,且通过第一预充电单元11控制数据端J15与第一电源端J11之间断开。

[0139] 步骤S58:第一次读写操作完成后的预设时间内,通过第二预充电单元12控制数据端J15与第二电源端J12之间断开,且通过第一预充电单元11控制数据端J15与第一电源端J11之间断开。

[0140] 步骤S59:第一次读写操作完成后的预设时间之后,通过第二预充电单元12控制数据端J15与第二电源端J12之间断开,且通过第一预充电单元11控制数据端J15与第一电源端J11之间导通。

[0141] 上述存储器预充电的控制方法当存储器处于行激活状态,且未进行读写操作时,通过第二预充电单元12控制数据端J15与第二电源端J12之间断开,且通过第一预充电单元11控制数据端J15与第一电源端J11之间断开,此时没有向数据端J15输入第一充电电压,也没有向数据端J15输入第二充电电压,使得不会对数据线进行预充电;当读写操作的命令到来时,再将数据端J15拉至第一预充电压,这样既能够减少耗电,又不会影响存储器的正常

工作。同时,在第一次读写操作完成后的预设时间之后,存储器电路即通过数据端J15向数据线输入第一预充电压,使得存储器在后续的读写操作周期中,无需单独的预设时间进行预充电,提升了存储器的读写速度。

[0142] 应该理解的是,虽然图5的流程图中的各个步骤按照箭头的指示依次显示,但是这些步骤并不是必然按照箭头指示的顺序依次执行。除非本文中有明确的说明,这些步骤的执行并没有严格的顺序限制,这些步骤可以以其它的顺序执行。而且,图5中的至少一部分步骤可以包括多个步骤或者多个阶段,这些步骤或者阶段并不必然是在同一时刻执行完成,而是可以在不同的时刻执行,这些步骤或者阶段的执行顺序也不必然是依次进行,而是可以与其它步骤或者其它步骤中的步骤或者阶段的至少一部分轮流或者交替地执行。

[0143] 在一些示例中,存储器在行激活状态的一个周期内进行多次读写操作,在存储器的行激活状态的一个周期内,每次读写操作完成后的预设时间之后,控制电路20通过第一预充电单元11控制数据端J15与第一电源端J11之间导通,并在下次读写操作开始后的预设时间之后,通过第一预充电单元11控制数据端J15与第一电源端J11之间断开。

[0144] 上述存储器预充电的控制方法既保证了在每次数据读写之前对数据线预充电到电源电压,为后续数据读写做准备,又能够避免在存储器处于行激活状态且还未进行读写操作时对电流的浪费。

[0145] 本申请还提供一种计算机设备,包括存储器和处理器,存储器存储有计算机程序,处理器执行计算机程序时实现上述任一实施例中提供的存储器预充电的控制方法的步骤。

[0146] 以上所述实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

[0147] 以上所述实施例仅表达了本申请的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对申请专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本申请构思的前提下,还可以做出若干变形和改进,这些都属于本申请的保护范围。因此,本申请专利的保护范围应以所附权利要求为准。

图2

图4

图5