# Übersetzung der europäischen Patentschrift

(97) EP 0 924 532 B1

(21) Deutsches Aktenzeichen: **698 34 235.6** (96) Europäisches Aktenzeichen: **98 121 826.6** (96) Europäischer Anmeldetag: **17.11.1998**

(97) Erstveröffentlichung durch das EPA: 23.06.1999

(97) Veröffentlichungstag

der Patenterteilung beim EPA: **19.04.2006** (47) Veröffentlichungstag im Patentblatt: **04.01.2007**

(30) Unionspriorität:

66161 P 19.11.1997 US 98870066 01.04.1998 EP 98110800 12.06.1998 EP

(73) Patentinhaber:

IMEC vzw, Leuven Heverlee, BE

(74) Vertreter:

Bird, W., MA. CEng. MIEE, Pat.-Anw., Winksele, BE

(51) Int CI.8: **G01S 5/14** (2006.01)

(84) Benannte Vertragsstaaten:

AT, BE, CH, DE, DK, ES, FI, FR, GB, GR, IT, LI, LU, NL, SE

(72) Erfinder:

Rabaeijs, Alain, 3200 Aarschot, BE; Aardoom, Erik, 3000 Leuven, BE; Gyselinckx, Bert, 3001 Leuven, BE; Engels, Marc, 3018 Wijgmaal, BE

(54) Bezeichnung: Verfahren und Vorrichtung zum Empfang von GPS/GLONASS-Signalen

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelegt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

#### **Beschreibung**

**[0001]** Die vorliegende Erfindung bezieht sich auf ein elektronisches System und dessen Komponenten und auf Verfahren zum Betreiben des Systems und seiner Komponenten für das Empfangen von Frequenzspreizsignalen für z.B. Signale von einem Global-Positioniersystem, wie z.B. GPS und/oder GLONASS.

#### TECHNISCHER HINTERGRUND

**[0002]** Eine zunehmende Anzahl von Applikationen und Systemen für Kommunikationsinformation gebraucht heutzutage die Frequenzspreiztechnik. Die Frequenzspreiztechnik ist eine digitale Modulationstechnik, in welcher ein digitales Signal über ein breites Frequenzband gespreizt wird, so dass es ein rausch-ähnliches Spektrum besitzt. Dies kann durch Aufbrechen oder "Chopping" bzw. "Zerhacken" jedes Datenbits des Digitalsignals in viele Unter-Bits (allgemein Chips genannt) durchgeführt werden, welche dann moduliert und auf eine Trägerfrequenz auf konvertiert werden. Das Zerhacken kann durch Multiplizieren des digitalen Informationssignals mit einem sogenannten Pseudozufallscode oder PN-Code durchgeführt werden. Durch Nutzen orthogonaler Codes für unterschiedliche Kommunikationsverbindungen kann das gleiche Frequenzband für verschiedene simultane Kommunikationsverbindungen benutzt werden.

**[0003]** Indem der gleiche PN-Code als Sender benutzt wird, kann ein Empfänger das empfangene gespreizte Signal korrelieren und das Datensignal rekonstruieren, während andere Empfänger, welche andere Codes oder andere Übertragungstechniken benutzen, dies nicht können. Einer der Vorteile des Nutzens der Frequenzspreizkommunikationstechnik besteht in der Robustheit gegenüber Schmalbandinterferenzsignalen. Da die Frequenzspreizempfänger sehr schnell in Applikationen und Systeme eingeführt werden, welche für den Consumermarkt bestimmt sind, sind die Kosten für das Empfängersystem ein Hauptbestimmungsfaktor um wettbewerbsfähig zu bleiben.

**[0004]** Eine spezielle Klasse von Frequenzspreizsystemen sind Vorrichtungen und Empfänger für die Positionsbestimmung. Derartige Vorrichtungen gewinnen sowohl für den Consumermarkt als auch für hochpräzise Anwendungen an Bedeutung. Die meisten der bestehenden Systeme basieren auf dem amerikanischen Global-Positioniersystem (GPS)-System. Da dies auch ein militärisches System ist, kann eine präzise Positionsbestimmung durch den Satellitenoperator schwierig gemacht werden, indem Fehler bewusst eingeführt werden (genannt "Gegen-Beschwindeln"). Außerdem kann in vielen Bereichen die Anzahl von sichtbaren Satelliten zu sehr eingeschränkt sein, um eine genaue Position zu bestimmen. Diese beiden Probleme können reduziert werden, indem auch ein zweites Positioniersystem benutzt wird, wie z.B. das russische globale Orbit-Navigationssatellitensystem (GLONASS)-System.

**[0005]** Über kombinierte GPS- und GLONASS-Empfänger wurde berichtet, z.B. von S. Riley, N. Howard, E. Aardoom, R. Daly und P. Silvestrin in "A combined GPS/GLONASS high precision receiver for space applications", ION-GPS 95, Palm Springs, USA, September 1995, oder in der japanischen Patentanmeldung JP 7128423 – 950519, "Receiver Common to GPS and GLONASS".

**[0006]** Ein GPS-Empfänger ist aus US 5,293,170 bekannt, welcher mit P-Code-modulierten Signalen benutzt werden kann, welche mit einem unbekannten Code moduliert wurden. Implementierungen dieser bekannten Vorrichtung erfordern eine große Anzahl von Registern.

**[0007]** Im US 5,600,670 wird ein GPS-Empfänger beschrieben, welcher eine hierarchische Kette von Kanalmodulen beinhaltet, welche Untermodule und Mastermodule beinhalten. Das bekannte System liefert keine ausreichende Flexibilität. Im US 5,293,170 wird ein GPS-Empfänger und ein Verfahren nach den Präambeln der unabhängigen Ansprüche 1 und 4 veröffentlicht.

#### ZIELE DER ERFINDUNG

**[0008]** Eine Aufgabe der vorliegenden Erfindung besteht darin, ein Verfahren und ein Gerät zum Bearbeiten von empfangenen Frequenzspreizsignalen zu liefern, speziell von Signalen von einem globalen Navigationssystem, welches eine optimale Flexibilität in den Verarbeitungsmöglichkeiten gestattet, während der Leistungsverbrauch und die Herstellkosten reduziert werden.

**[0009]** Es ist eine weitere Aufgabe der vorliegenden Erfindung, ein Verfahren und ein Gerät zum Verarbeiten empfangener Frequenzspreizsignale zu liefern, speziell von Signalen von einem globalen Navigationssystem, welches für das Implementieren von mindestens einem Teilsystem als ein ASIC geeignet ist, während eine op-

timale Flexibilität an Verarbeitungsmöglichkeiten aufrecht erhalten wird und wobei der Leistungsverbrauch und die Chipfläche reduziert werden.

#### ZUSAMMENFASSUNG DER ERFINDUNG

[0010] Die Erfindung wird durch die Merkmale der unabhängigen Ansprüche 1 und 4 definiert.

#### KURZE BESCHREIBUNG DER ZEICHNUNGEN

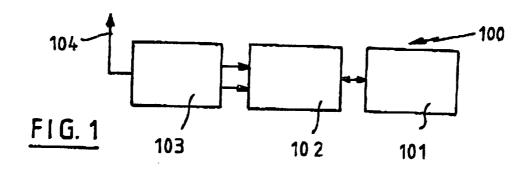

**[0011]** Fig. 1 ist ein schematisches Blockschaltbild, welches die Hauptkomponenten eines Frequenzspreizempfängers zeigt.

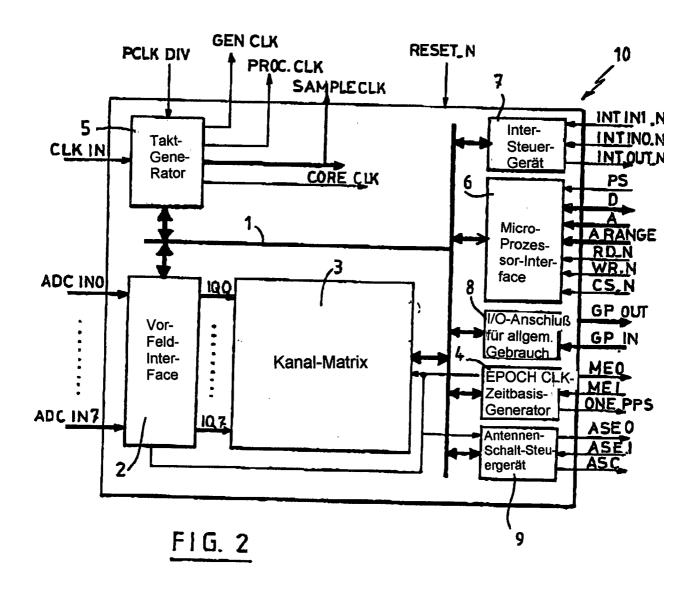

[0012] Fig. 2 ist eine schematische Darstellung eines Teils der Korrelationseinheit.

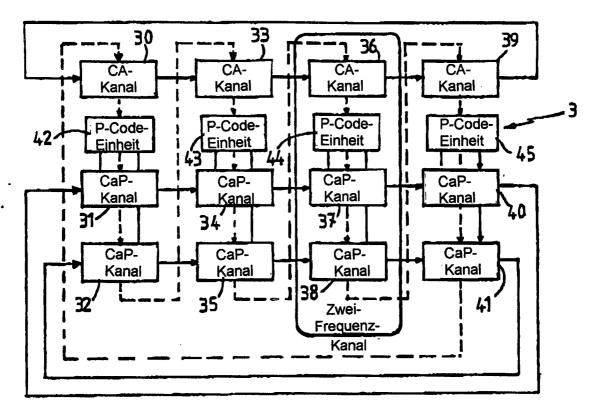

[0013] Fig. 3 ist eine schematische Darstellung einer Kanalmatrix.

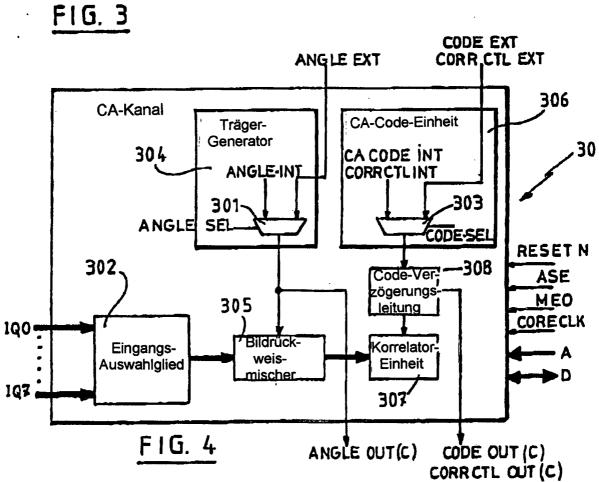

[0014] Fig. 4 ist eine schematische Darstellung eines CA-Kanalmoduls.

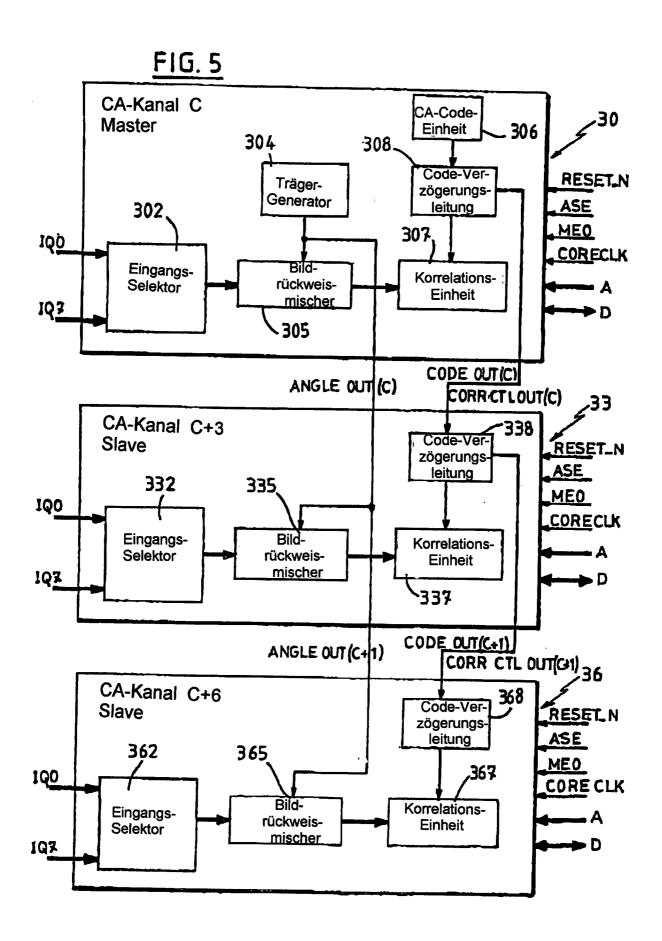

[0015] Fig. 5 ist eine schematische Darstellung einer hierarchischen Kette von CA-Kanalmodulen.

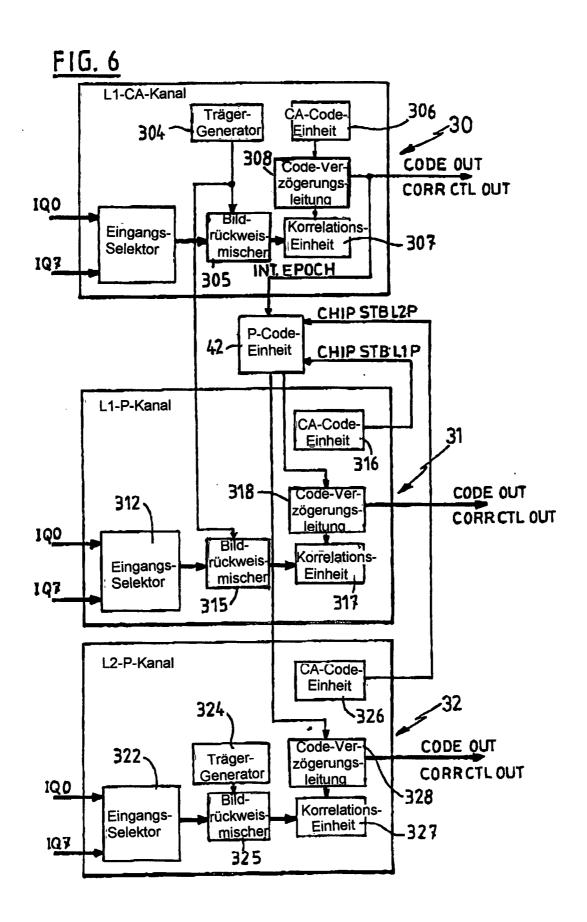

[0016] Fig. 6a ist eine schematische Darstellung eines Zweifrequenzkanals.

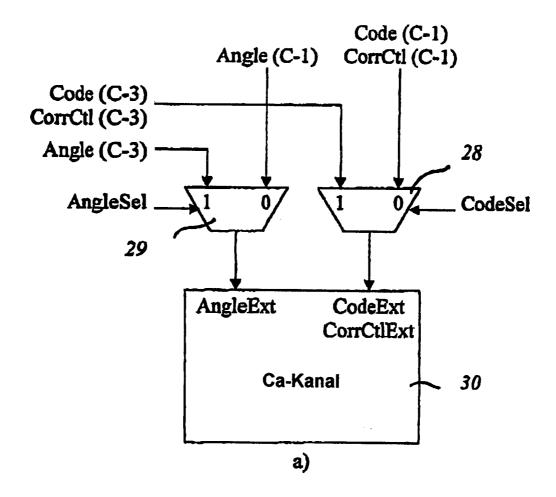

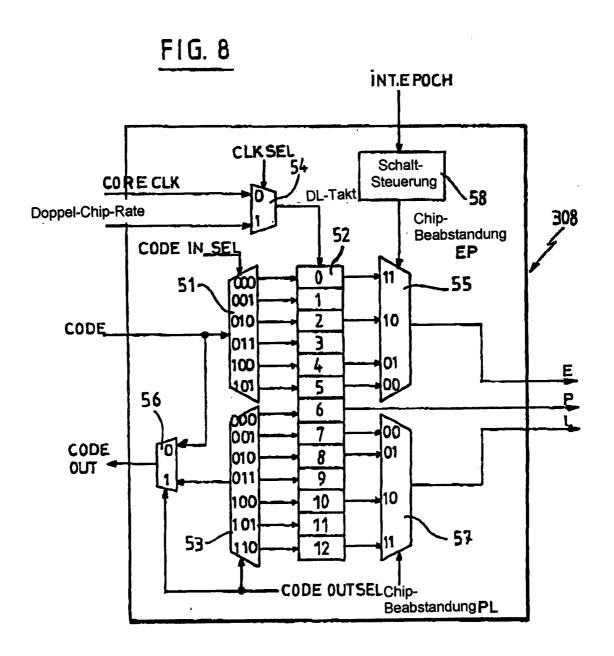

**[0017]** Fig. 7a und b sind eine schematische Darstellung von Nebensteuerschaltungen jeweils für ein CA-Kanalmodul und ein CaP-Kanalmodul.

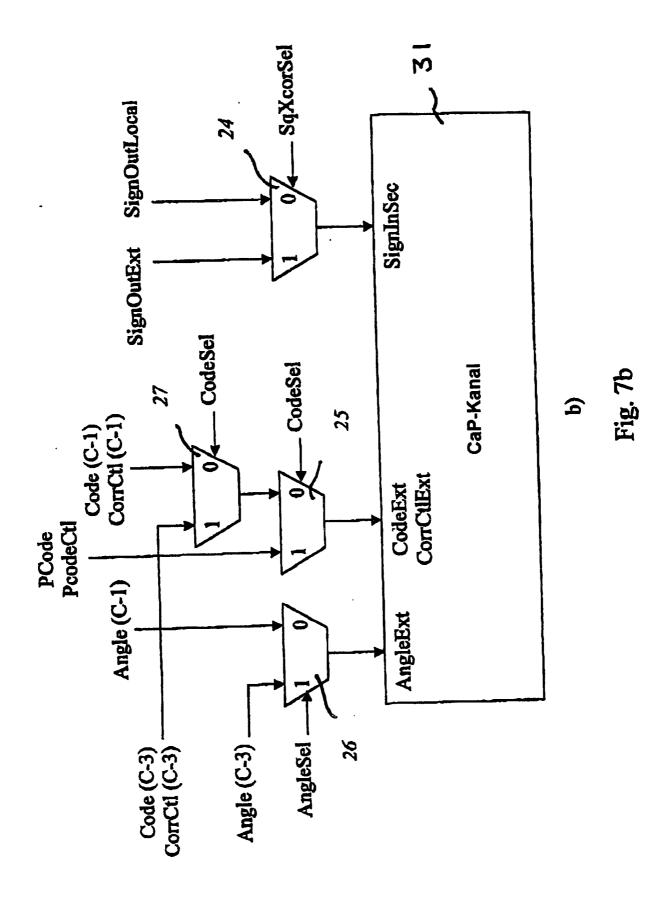

[0018] Fig. 8 ist eine schematische Darstellung einer Code-Verzögerungsleitungseinheit.

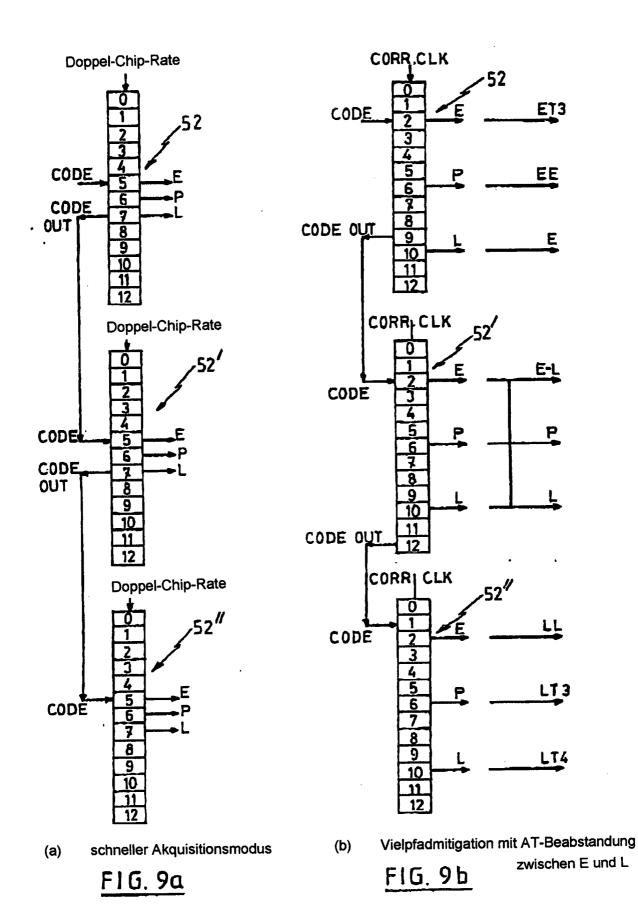

**[0019]** Fig. 9a und b sind zwei Beispiele für drei Kanalmodule mit untergeordneten Code-Verzögerungsleitungen.

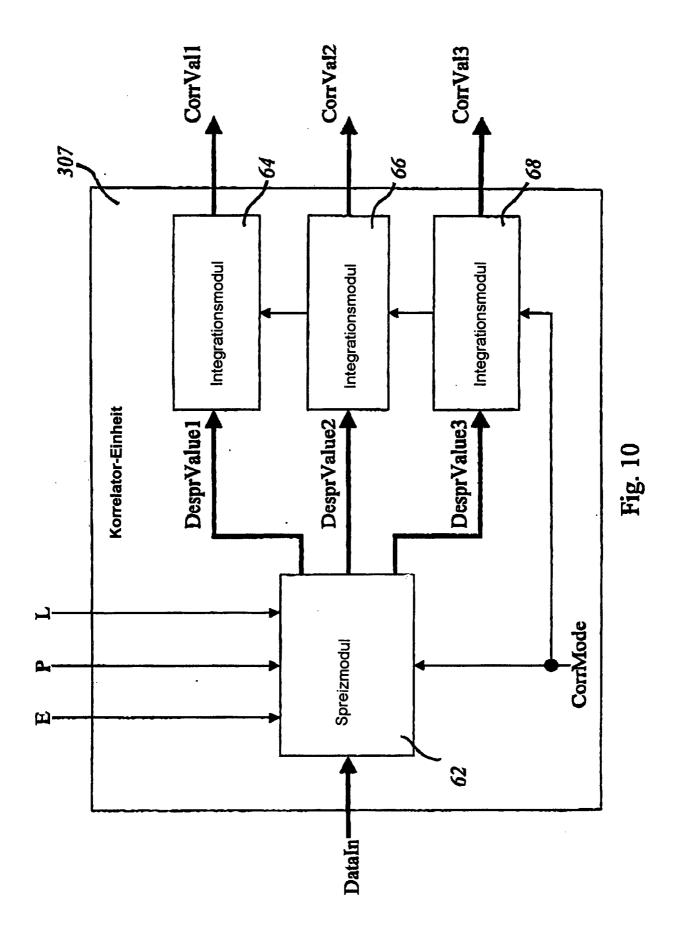

[0020] Fig. 10 ist eine schematische Darstellung einer Korrelationseinheit.

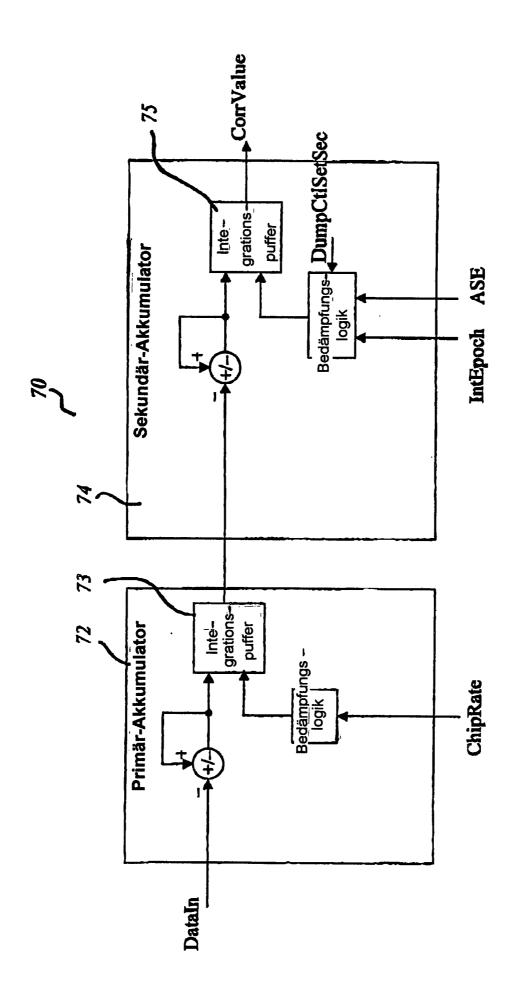

[0021] Fig. 11 ist eine schematische Darstellung eines CA-Code-Integrationsmoduls.

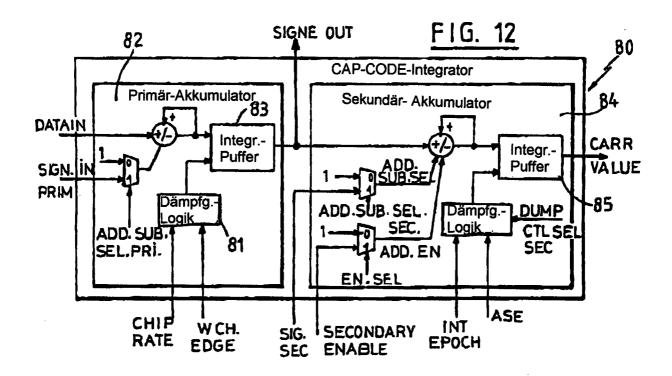

[0022] Fig. 12 ist eine schematische Darstellung eines CaP-Code-Integrationsmoduls.

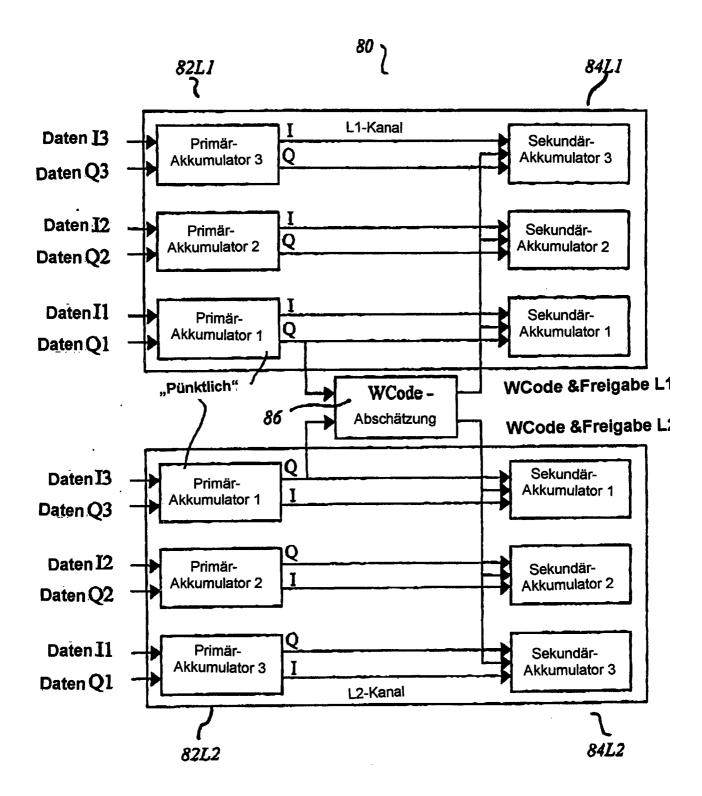

**[0023]** Fig. 13 ist eine schematische Darstellung eines CaP-Code-Integrationsmoduls, welches ein Y-Code-Schätzglied beinhaltet.

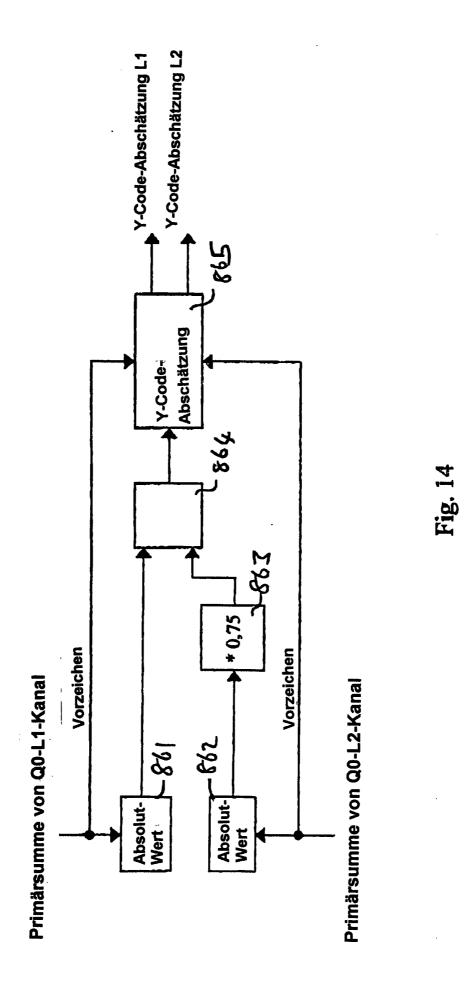

[0024] Fig. 14 ist eine schematische Darstellung eines Y-Code-Schätzgliedes.

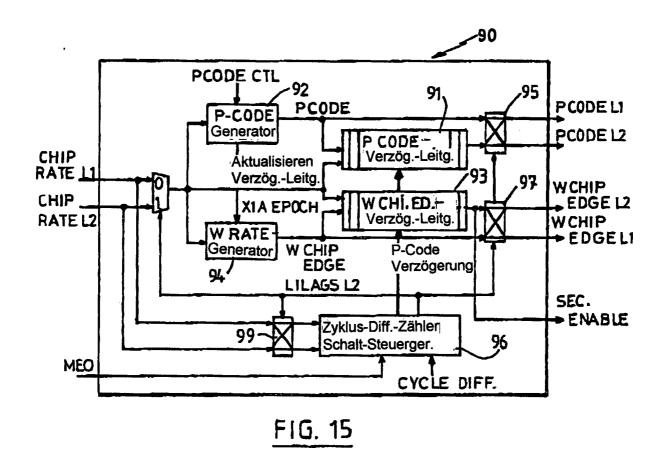

**[0025]** Fig. 15 ist eine schematische Darstellung einer P-Code-Einheit entsprechend einer Ausführungsform der vorliegenden Erfindung.

### **DEFINITIONEN**

**[0026]** Kanal: Die Funktionalität oder die Hardware, welche erforderlich ist, einen Pseudorauschcode auf einer einzelnen Frequenz zu verfolgen, z.B. einen Navigationscode wie z.B. CA auf L1 oder SV3 oder P auf L2 von SV19. Zum Beispiel müssen nicht alle Kanäle des AGGR identisch in ihrer Funktionalität sein. Zum Beispiel können einige nur in der Lage sein, den CA-Code zu verfolgen, andere auch den P-Code. Einige können als Master in einer Master-Slave-Konfiguration sein und einige nicht.

**[0027]** Zwei-Frequenz-Kanal: Die Funktionalität und die Hardware, welche benötigt wird, um alle drei Bereichssignale zu verfolgen, welche durch einen GPS- oder einen GLONASS-Satelliten übertragen werden, sind auf einem Träger (L1) plaziert und der gleiche P-Code ist auf einem zweiten Träger (P auf L2) plaziert. Ein Zweifrequenzkanal ist durch Gruppieren von drei Einzelfrequenzkanälen gebildet.

**[0028]** Messgrößen: Information, welche von dem AGGR gelesen wird, außer der Korrelationswerte (z.B. Trägerfrequenzzykluszähler, Phasen- und Code-Trägerfrequenzzykluszähler und Phase für jeden Kanal).

[0029] Pseudo-Bereichsmessungen: Synonym für Code-Phasen-Messung.

[0030] RF-Konditioniereingang: Der Eingang, an welchen die Antenne angeschlossen ist.

**[0031]** Messen des Epoch-Signals: Periodisches Abtastsignal, welches das Aktualisieren der Messgrößen steuert, gebräuchlich für alle Kanäle.

**[0032]** Integrations-Epochen-Signal: Periodisches Abtastsignal, welches das Aktualisieren der Frequenzund/oder der Phase des internen Codes und der Trägerkopiersignale steuert, individuell für jeden Kanal. Dieses Signal aktualisiert auch die Korrelationsausgangsregister.

**[0033]** Antennen-Schalt-Epochen-Signal: Abtastsignal, welches das Aktualisieren der Korrelationsausgangsregister steuert.

**[0034]** Code-Epochen-Signal: Periodisches Abtastsignal, welches ein einzigartiges Muster anzeigt (entsprechend zu dem Dauer-Eins-Zustand des Code-Erzeugungsschieberegisters) in dem erzeugten oder empfangenen Pseudo-Zufallsrauschcode.

**[0035]** GNSS-Signale: Kombination aus GPS-, GLONASS- und verschiedenen Vergrößerungssignalen, z.B. EGNOS, WAAS, MTSAT.

[0036] Komplexes Signal: Ein Signal, welches in In-Phase (I)- und quadratische (Q)-Komponenten aufgespalten ist.

**[0037]** Interkanal-Bezugswert: Mittlerer Fehler zwischen zwei Kanälen, welche das gleiche Satellitensignal verfolgen.

#### Bit-Numerierung und Benennungskonventionen

**[0038]** Freigegebene Signale werden von dem am wenigsten signifikanten (LSB) bis zu dem am meisten signifikanten Bit (MSB) indiziert. Das LSB hat den Index 0, während das MSB eines Vektors der Länge N den Index N–1 besitzt. Ein Suffix von "N" zu einem Signalnamen zeigt an, dass ein Signal aktiv niedrig ist. Zum Beispiel ist ResetN ein aktives niedriges Signal.

#### Liste der Abkürzungen

ADC: Analog/Digital-Wandler

ADSP21020: Digital-Signalprozessor 21020 für Analogvorrichtungen

AGC: Automatische Verstärkungssteuerung

AGGR Hochentwickelter GPS/GLONASS-Empfänger AGGA: Hochentwickelter GPS/GLONASS-ASIC

AOCS: Lage- und Umlauf-Steuersystem

AS: Gegen-Verschleierung bzw. Gegen-Manipulation, Technik, mit welcher der GPS-P-Code ver-

schlüsselt wird

ASIC: Applikationsspezifische integrierte Schaltung

CA-Code: Grob-Akquisitions-Code

CaP-Kanal: Kanal, welcher CA- und P-Codes bearbeiten kann

CDMA: Codemultiplex-Vielfachzugriff

DAC: Digital/Analog-Wandler

DSP: Digitalsignalverarbeitung

E: Frühkorrelation

EGNOS: Europäisches geostationäres Navigationsüberlagerungssystem

EOW: Ende der Woche

ERC32: Eingebetteter Echtzeitkern, 32-Bit-Sparc-Microprozessor

GLONASS: Globales Umlaufnavigationssatellitensystem

GNSS: Globale Navigationssatellitensysteme

GPS: Globales Positioniersystem

I: In-Phase

IF: Zwischenfrequenz

IO: Eingabe-Ausgabe bzw. Eingang-Ausgang

L: Spätkorrelation

L1: Trägerfrequenz (1575,42 MHz für GPS, 1602,0 +9/16\* ch MHz für GLONASS)

L2: Trägerfrequenz (1227,6 MHz für GPS, 1246,0 +7/16\* ch MHz für GLONASS)

LFSR: Lineares Rückkopplungsschieberegister

LSB: Am wenigsten signifikantes Bit

MSB: Am meisten signifikantes Bit

MSPS: Mega-Abtastungen pro Sekunde

MTSAT: Mobiles Transport-Satellitensystem

NCO: Numerisch gesteuerter Oszillator

P: Pünktliche Korrelation

PCB: Leiterplatte

P-Code: Präzisionscode

PLL: Phasengelockte Schleife

PN-Code: Pseudo-Rausch-Code

POD: Präzise Umlaufberechnung

PRN: Pseudo-Zufallsrauschen

Q: Quadratur RF: Funkfrequenz

SR: Selektive Verfügbarkeit

SM: Vorzeichen-/Absolutwert

SNR: Singal-Rauschverhältnis

SV: Weltraumfahrzeug

W-Code: Code, welcher zum Verschlüsseln des GPS P-Codes benutzt wird, um den Y-Code zu bilden

WAAS: Weiträumiges Vergrößerungssystem

Y-Code Verschlüsselter GPS P-Code

#### BESCHREIBUNG DER ERLÄUTERNDEN AUSFÜHRUNGSFORMEN

[0039] Die vorliegende Erfindung wird mit Bezug auf spezielle Ausführungsformen und mit Bezug auf bestimmte Zeichnungen beschrieben, jedoch ist die Erfindung nicht darauf beschränkt, sondern nur durch die Ansprüche. Außerdem wird die vorliegende Erfindung hauptsächlich mit Bezug auf globale Positionier- und Navigationssysteme, wie z.B. GLONASS oder GPS beschrieben, jedoch ist die vorliegende Erfindung nicht auf diese beschränkt, sondern nur durch die Ansprüche. Speziell kann die vorliegende Erfindung bei Frequenzspreiz-Kommunikations-systemen allgemein Anwendung finden, speziell mit Direkt-Folge CDMA-Systemen, den (DS-CDMA)-Systemen. Speziell wird die funktionelle Spezifikation für das Gestalten eines fortschrittlichen GPS- und/oder GLONASS-Empfängers (AGGR) veröffentlicht. Das AGGR wird vorzugsweise zusammen mit wenigstens einem Untersystem hergestellt, welches als eine applikationsspezifische integrierte Schaltung (ASIC) implementiert ist. Die ASIC-Implementierung des AGGR wird als AGGA bezeichnet. Die AGGR und speziell die ASIC (AGGA) kann bei einer Vielzahl von kombinierten GPS/GLONASS-Empfängern für eine große Menge von Applikationen genutzt werden, wobei, als nicht eingrenzende Aufzählung, das Synchronisieren von Mobiltelefonsystem, Personenortseinrichtungen, hochpräzise wissenschaftlichen Instrumente und Satelliten-Lage und Umlauf-Steuersysteme beinhaltet sind.

[0040] Die Hauptfunktionseinheiten eines AGGR 100 entsprechend einer Ausführungsform der vorliegenden Erfindung werden schematisch in Fig. 1 gezeigt. Das AGGR 100 kann eine lineare Anordnung eines Microprozessors 101, einen digitalen Korrelator 102, ein analoges Vorfeld 103 und eine Antenne oder Antennen, z.B. ein Antenntenfeld 104, aufweisen. Der Microprozessor 101 betreibt die Applikationssoftware und steuert den Betrieb des AGGR 100. Der Korrelator 102 weist eine Anzahl von Kanälen oder Kanalmodulen auf, welche Frequenzspreizsignale erfassen und/oder verfolgen können, z.B. diejenigen, welche von globalen Positionssatelliten empfangen werden. Der Korrelator 102 kann die Fähigkeit der Vielpfad-Mitigation bzw. – Minderung und/oder Kalibrierung und/oder schnellen Akquisition besitzen. Das Vorfeld 103 wandelt die RF-Signale, welche durch die Antenne 104 eingefangen werden, in zeitdiskrete Digitalsignale um, welche von dem Korrelator 102 genutzt werden können. Eine geeignete Vorfeldeinheit 103 ist aus der zusammenhängenden europäischen Patentanmeldung, 97870164,7 "Method and Apparatus for receiving and converting spread spectrum signals" bekannt.

[0041] Der Korrelator 102 kann einen AGGA 10 beinhalten, aber die vorliegende Erfindung ist nicht darauf beschränkt und andere Schaltungsformen können benutzt werden, z.B. PCP's. Ein schematisches Funktionsblockschaltbild eines AGGA 10, entsprechend der vorliegenden Erfindung, wird in Fig. 2 gezeigt. Der AGGA 10 weist acht Hauptfunktionsblöcke auf: ein Vorfeldinterface 2, welches das Interface zwischen dem Vorfeld

103 bildet, eine Kanalmatrix 3, einen Zeitbasisgenerator 4, einen Taktgenerator 5, ein Microprozessorinterface 6, welches das Interface mit dem Empfängermicroprozessor 101 bildet, eine Unterbrechungssteuereinrichtung 7, einen IO-Anschluss 8 für allgemeine Zwecke und eine Antenntenschaltsteuereinrichtung 9. Das ResetN-Eingangssignal wird an alle Module 1–9 verteilt. Die Module 1–9 können zusammen über einen internen Bus 1 angeschlossen werden.

**[0042]** In der folgenden Beschreibung kann Bezug auf die Register genommen werden. Diese Register werden in den Zeichnungen nicht gezeigt, aber sie können auf dem Chip plaziert sein, d.h. auf dem gleichen Chip wie der AGGA **10** ASIC. Eine Speicherabbildung kann vorgesehen sein, so dass der Adressort jedes Registers für den Microprozessor **101** bekannt sein kann unabhängig von der speziellen Gestaltung dieses Microprozessors **101**.

[0043] Das Vorfeldinterface 2 akzeptiert die digitalisierte Zwischenfrequenz (IF)-Eingangssignale ADCIn0–7 von dem analogen Vorfeld 103. Das IF-Signal kann z.B. real oder komplex sein. Wenn es real ist, kann das Signal in einen in Phase(I)- und einen Quadratur(Q)-Wert umgewandelt werden, um durch eine festgelegte Frequenz gleich einem Viertel der Abtastfrequenz, heruntergewandelt werden. Wenn das Eingangs-IF-Signal komplex ist, wird es als ein In-Phase(I)- und ein Quadratur(Q)-Wert auf zwei benachbarten Eingängen dargestellt. Die Herunterwandlungsstufe wird dann umgangen. Das AGGA 10 kann adaptiert sein, um eine große Menge an Eingangsformaten zu unterstützen, z.B. Vorzeichen/Absolutwert, ohne Vorzeichen, Zweierkomplement und Komparatorausgang für drei Pegel. Außerdem kann eine Abschätzung der Eingangsenergie (Signal-plus-Rauschen) gemessen werden, um für automatische Verstärkungssteuerungs(AGC)-Zwecke genutzt zu werden, z.B. kann ein Signalpegeldetektor (nicht gezeigt) die Signal-plus-Rausch-Leistung des I- oder des Q-Zweiges eines komplexen Signales abschätzen und dies kann von allen Eingängen gleichzeitig genutzt werden.

**[0044]** Die Kanalmatrix **3** enthält eine Vielzahl (N) von unabhängigen Kanälen und kann allgemein für das Spreizen der Frequenzspreizsignale benutzt werden. Speziell kann in Übereinstimmung einer Ausführungsform der vorliegenden Erfindung jeder Kanal für das Verarbeiten von L1 oder L2 CA-Codes befähigt sein. Diese Kanäle können auch in Gruppen von drei konfiguriert sein, um bis zu N/3 unabhängige Zweifrequenzverfolgungskanäle zu bilden, welche in der Lage sind, CA-Code auf L1 oder L2 und P-Code auf L1 und L2 zu verfolgen. Außerdem können die Kanäle auf verschiedene andere Weise gruppiert sein, um Funktionen wie z.B. die schnelle Akquisition, die Lagebestimmung mit Hilfe von interferometrischen Trägerphasenmessungen und die Vielpfadabschwächung zu unterstützen.

[0045] Die Anzahl der Kanäle N in einem AGGA 10 wird dadurch bestimmt, wie viele in der gewählten Technologie integriert werden können. Jeder Kanal kann unabhängig konfiguriert sein, um ein GNSS-Signal zu verfolgen. Zwei Frequenzkanäle unterstützen das P-Code- und Y-Code-Verfolgen. Am Ende jeder Messungsepoche bzw. -periode, werden Träger- und Code-Phasenwerte für alle Kanäle in einen Satz von beobachtbaren Registern (nicht gezeigt) gelatcht bzw. geklinkt. Am Ende der Integrationsepoche (für jeden Kanal individuell) werden die Codekorrelationswerte in einen Satz von Korrelationsregistern (nicht gezeigt) geklinkt. Die Korrelationswerte werden durch die Empfängerfirmware benutzt, um die Verfolgungsschleifen zu schließen, wobei Träger- und Code-Phasenfehlerberechnungen, die Applikationen von Schleifenfiltern und das Abschätzen der Signal-/Rausch-Amplitude beinhaltet sind. Die Messgrößen werden durch die Empfängerfirmware benutzt, um die Position, die Zeit, die Geschwindigkeit und in einigen Fällen die Lage abzuleiten. Die Messepoche wird durch den Zeitbasisgenerator 4 geliefert und ist für alle Kanäle gemeinsam.

[0046] Der Zeitbasisgenerator 4 stellt vorzugsweise drei periodische Abtastsignale EpochCIK, MEO und OnePPS für das genaue Zeiteinhalten des Empfängers und die beobachtbaren Messungen her. Das EpochCIK-Ausgangssignal hat eine nominelle Frequenz von 1 KHz und ist das Taktsignal für die Integrationspegelepochenerzeugung, die Messungsepochenerzeugung und das Antennenschaltsteuergerät. Das Messepochenausgangssignal MEO wird angefügt, um das Ende jeder Messepoche anzuzeigen. Das Messepocheneingangssignal MEI akzeptiert das MEO Abtastsignal von einem anderen AGGA 10, um die Synchronisation der beobachtbaren Messungen in Konfigurationen mit mehr als einem AGGA 10 freizugeben. Der Zeitbasisgenerator 4 erzeugt auch ein Signal mit einem Puls pro Sekunde (OnePPS), mit dem ein externes Gerät synchronisiert werden kann.

[0047] Der Taktgenerator 5 produziert ein internes Taktsignal CoreClk und drei externe Taktsignale Sample-Clk, GenClk und ProClk, welche alle von einem externen Takt abgeleitet werden. Zum Beispiel kann das AGGA 10 Taktsignale für die ADC's und die interne Kanalmatrix 3, ein GP2010 Vorfeld, wie es von GEC Plessey Semiconductors, UK, hergestellt wird und den Empfänger-Microprozessor 101 erzeugen. Die unterschiedlichen

Taktfrequenzen können individuell programmiert werden. Drei dedizierte Eingangssignale werden geliefert, um das Taktteilverhältnis der Microprozessor-Uhr zu programmieren.

[0048] Ein Microprozessor 101 kann auf das AGGA 10 über das Microprozessor-Interface 6 zugreifen. Das AGGA 10 kann sich wie eine generische Speicherkartenperipherie verhalten. Ein interner Adressdekodierer (nicht gezeigt) kann in dem Microprozessorinterface 6 vorgesehen sein, welcher es dem Microprozessor 101 gestattet, bis zu vier AGGA's 10 zu adressieren, wobei nur eine einzelne Chipauswahlleitung benutzt wird. Zwei dedizierte Eingänge bzw. Eingangssignale werden vorgesehen, um den gültigen Adressbereich des AGGA 10 auszuwählen. Das Interface 6 ist vorzugsweise direkt kompatibel mit den Analogeinrichtungen ADSP21020 und dem ERC32 Sparc-Chipsatz. Es ist 32-Bit groß und erfordert keine Wartezustände an den spezifizierten Prozessort-Taktfrequenzen von 20 MHz und 14 MHz jeweils für die ADSP21020 und ERC32, unter der Bedingung, dass die CoreClk-Frequenz des AGGA 10 die MicroprozessorTaktfrequenz überschreitet. Andernfalls muss der Microprozessor 101 Wartezustände einfügen, um sicherzustellen, dass eine Lese- oder Schreib-Operation, die CoreClk-Taktzeit überschreitet.

[0049] Wenn verschiedene Module innerhalb des AGGA 10 eine Aktion durch den Microprozessor 101 erfordern, kann dies über die Unterbrechungsanforderungen signalisiert werden. Das AGGA-Unterbrechungssteuergerät 7 empfängt diese Unterbrechungsanforderungen, speichert sie in einem Unterbrechungsstatusregister (nicht gezeigt) und erzeugt eine externe Unterbrechnungsanforderung. Um viele AGGA's 10 mit einem einzelnen Unterbrechungssignal mit dem Microprozessor 101 zu unterbrechen, kann das Unterbrechungssteuergerät 7 zwei externe Unterbrechungseingänge besitzen, wodurch es gestattet wird, dass eine Anzahl von AGGA's 10 verbunden wird, z.B. als ein binärer Baum.

**[0050]** Das parallele IO-Interface **8** unterstützt die Funktionalität wie z.B. das Überwachen des Systems und das Steuern von Funktionen, z.B. das Überwachen der DAC-Indikatoren des externen Frequenzabwärtkonvertierungssynthesizers oder das Leistungsabschalten externer Schaltaufbauten. Der Ausgangsanschluss **8** kann z.B. für das Steuern paralleler DAC's für die Vorfeld-AGC-Funktionen genutzt werden. Alle IO-Anschlüsse sind vorzugsweise nur in einer Richtung ausgelegt, um Unfallkurzschlüsse aufgrund inkorrekten Programmierens der Richtung der IO-Treiber zu verhindern.

[0051] Das Antennenschaltsteuergerät 9 liefert eine Vorrichtung um das Atennenschalten bis hinauf zu vier Antenneneinheiten 104 zu steuern, z.B. in einem hybriden Parallel-Multiplex-Lagebestimmungs-GNSS-Empfänger 100. Es stellt auch ein Antennenschaltepochenabtastsignal her, welches einen Antennenschaltvorgang signalisiert und welches benutzt wird, um Korrelationslesen aller Kanäle zu speichern, welche als Nebenkanäle ausgeführt sind. In Anordnungen mit mehr als einem AGGA 10 muss nur das Antennenschaltsteuergerät 9 eines Master-AGGA 10 freigegeben werden, während alle anderen Neben- bzw. Unter-AGGA's 10 vorzugsweise den Antennenschaltepochenausganq (ASE) des Master-AGGA 10 benutzen, um ihre jeweiligen Korrelatoren 102 zu steuern.

[0052] Eine Struktur der Kanalmatrix 3 entsprechend einer Ausführungsform der vorliegenden Erfindung wird schematisch in Fig. 3 gezeigt. Die Kanalmatrix 3 beinhaltet eine Vielzahl von Verarbeitungskanälen 30 bis 41. Zwölf Kanäle werden gezeigt, jedoch ist die Erfindung nicht auf diese beschränkt. Alle Kanäle 30 bis 41 haben vorzugsweise identische Funktionalität für das CA-Code-Verfolgen. Jeder beliebige Kanal 30 bis 41 kann auch so konfiguriert sein, dass er unmodulierte Eingangssignale verarbeitet, ein Merkmal, welches für das Kalibrieren der RF-Vorfeldgruppen-Verzögerungsvariationen vorgesehen ist. Die Kanäle 30, 33, 36, 39, welche nur den CA-Code verfolgen können, werden die CA-Kanäle genannt, während die CaP-Kanäle 31, 32, 34, 35, 37, 38, 40, 41 zusätzliche Funktionalität besitzen, um sie in die Lage zu versetzen, auch P-Code- oder Y-Code-modulierte Signale zu verfolgen. Eine getrennte P-Code-Einheit 42 bis 45 pro Zweifrequenzkanal erzeugt den Kopier-P-Code für das Paar von CaP-Kanälen, z.B. 37, 38, wenn ein CA-Kanal 36 und zwei CaP-Kanäle 37, 38 gruppiert werden, um einen Zweifrequenzkanal (eine Spalte der Kanalmatrix 3 wie gezeigt) zu bilden.

[0053] Die Kanäle 30–41 können selektiv untergeordnet werden, wie dies durch die gestrichelten oder durchgezogenen Linien in Fig. 3 gezeigt wird. Das Unterordnen bedeutet wenigstens, dass gewisse Signale oder Signalparameter, welche durch den Masterkanal (gewöhnlich ein CA-Kanal) erzeugt werden, durch den nächsten Kanal in der Folge oder Kette genutzt werden. Kanäle können hierarchisch miteinander verkettet werden. Zum Beispiel können für eine schnelle Erfassung alle CA-Kanäle 30, 33, 36, 39 zusammen untergeordnet werden, wobei der Zeitablauf für die Verteilungsoperation, welche von einem Kanal benutzt wird, auf den nächsten Kanal in der Folge übergeleitet wird, welcher eine Verzögerung hinzufügt, eine Korrelation mit dem empfangenen Signal versucht und den verzögerten Zeitablauf an den nächsten Kanal leitet usw. Durch das Unterordnen kann das unnötige Zurückrechnen von Signalparametern, welche bereits zuvor in dem Kanal berechnet oder

benutzt wurden, vermieden werden. Speziell kann die Geschwindigkeit der Erfassung bzw. Akquisition erhöht werden.

[0054] Der Betrieb der Kanalmatrix 3 wird vorzugsweise insgesamt durch den externen Microprozessor 101 gesteuert. Die Grundfunktionen jedes Kanals 30–41 sind: Auswahl eines aus acht komplexen Ausgangssignalen IQ0–7 aus dem Vorfeld-Interface 2, Herunterwandeln der ausgewählten komplexen Vorzeichen-Amplituden-Signale IQ0–7 auf das Grundband, Verteilen der komplexen Grundbandsignale mit dem auf dem Chip erzeugten CA- oder P-Kopiercode und Integration über ein programmierbares Zeitintervall. Das Ergebnis dieser Integrationen sind die Korrelationswerte. Zusammen mit den Messgrößen, welche die Träger- und Code-Frequenz und Phasenmessungen sind, sind diese die Ausgangssignale der Kanäle 30–41.

[0055] Ein CA-Kanal 30, 33, 36, 39 kann vorzugsweise L1- oder L2-CA-Code-modulierte GNSS-Signale bearbeiten, jedoch nicht P-Code- oder Y-Code-modulierte Signale. Ein Blockschaltbild eines CA-Kanals 30 entsprechend einer Ausführungsform der vorliegenden Erfindung wird schematisch in Fig. 4 gezeigt. Ein Eingangsauswahlgerät 302 wählt eines der acht komplexen Vorfeldinterfaceausgangssignale IQ0–7 mit einer Abtastrate gleich der CoreClk-Rate aus. In einem Bildrückweismischer 305 wird jede Grundträgerfrequenz durch Drehen des ausgewählten komplexen Signals um einen Winkel, der durch einen Trägergenerator 304 bestimmt wird, entfernt, was zu einem komplexen Grundbandsignal führt. Eine Korrelationseinheit 307 verteilt dann dieses Signal, wobei drei CA-Code-Sequenzkombinationen E, P und L (früh, pünktlich und spät) benutzt werden und integriert das Ergebnis während einer programmierbaren Integrationsperiode. Daher beinhaltet die Korrelationseinheit 307 sechs Akkumulatoren: drei für jedes der I- und Q-Zweige (nicht gezeigt). Die Ausgangssignale der Korrelationseinheit 307 sind die Korrelationswerte. Im Falle einer hybriden Parallel-Multiplex-Lagebestimmung kann die Integrationsperiode durch Abtasten der Antennenschaltepoche (ASE) gesteuert werden.

**[0056]** Die drei CA-Code-Sequenzen, E, P und L werden von einer einzelnen CA-Code-Sequenz abgeleitet, welche durch die CA-Code-Einheit **306** erzeugt wird. Die Verzögerungen zwischen den E-, den P- und den L-Sequenzen werden durch Einstellungen der CA-Code-Verzögerungsleitungseinheit **308** festgelegt. Die CA-Code-Chip-Rate wird durch den Code bestimmt, welcher numerisch durch den Oszillator (NCO, nicht gezeigt) der CA-Code-Eiheit **306** gesteuert wird. Die CA-Code-Einheit **306** steuert auch die Länge des Integrationsintervalls. Die Messgrößen werden auf der MEO-Abtastung abgetastet. Die Daten und die Adressbusse D und A werden von dem Microprozessor **101** genutzt, um auf die Register in dem Kanal zuzugreifen.

[0057] Innerhalb eines AGGA 101 kann jeder CA-Kanal 30, 33, 36, 39 oder CaP-Kanal 31, 32, 34, 35, 37, 38, 40, 41, welcher ausschließlich als ein CA Kanal arbeitet, einem anderen Kanal untergeordnet werden, wie es durch die gestrichelten oder gepunkteten Linien in Fig. 3 gezeigt wird. Die Signale, welche für das Unterordnen benutzt werden können sind vorzugsweise AngleExt, CodeExt und CorrCtlExt (jeweils der Trägerdrehwinkel, der lokal erzeugte Code und die damit verbundenen Korrelationssteuersignale). Es wird in Übereinstimmung mit der vorliegenden Erfindung vorgezogen, wenn nicht jeder Kanal mit einem anderen Kanal untergeordnet werden kann, da dies das Verschwenden von Ressourcen bedingt und nur eine kleine Verarbeitungsverbesserung erbringt. Die Slave-Kanalauswahlregel für die Kanäle, welche in Fig. 3 gezeigt werden, können wie folgt zusammengefasst werden: irgendein Kanal C∈(0 ... N-1) kann einem Kanal untergeordnet werden, welcher (C-1 mod N) oder (C-3 mod N) genügt. Dies bedeutet, dass ein Kanal entweder ein Slave bzw. Untergeordneter seines vorherigen Nachbarn in der gleichen Spalte (oder am unteren Ende der vorherigen Spalte, wenn C am oberen Ende einer Spalte ist) sein kann, oder ein Slave des Kanals in der entsprechenden Position in der vorherigen Spalte (oder in der letzten Spalte, falls C in der ersten Spalte ist). Die Leistungsfähigkeit des Empfängers entsprechend der vorliegenden Erfindung, um einen von wenigstens zwei Kandidat-Kanal-Modulen für den nächsten Modul in einer Kette auszuwählen, ist ein signifikanter Vorteil gegenüber dem bekannten Empfänger aus US 5,600,670.

[0058] Fig. 5 zeigt schematisch eine Ausführungsform, welche einen Master 30- und zwei Slave-Kanäle 33, 36 besitzen, welche nur modulierte CA-Code-Signale verfolgen. Jeder der CA-Kanäle 30, 33, 36 kann identisch sein, Komponenten der Kanäle, welche nicht in dieser Ausführungsform benutzt werden, werden der Klarheit wegen nicht gezeigt. Alternativ können einer oder mehrere der Kanäle 30, 33, 36 CaP-Kanäle 31, 32, 34, 35, 37, 38, 40, 41 sein, von denen nur die Komponenten gezeigt werden, welche für die CA-Code-Akquisition erforderlich sind. Diese Konfiguration kann für eine schnelle CA-Code-Akquisition benutzt werden und für differenzielle Trägerphasenmessungen bei einer Applikation der Bestimmung der Lage. Der Trägerdrehwinkel (AngleOut) für alle Kanäle wird durch die Master-Träger-NCO-Einheit 304 erzeugt und an alle SlaveKanäle 33, 36 verteilt. In ähnlicher Weise werden die Code (CodeOut)- und die damit verbundenen Korrelationssteuersignale (CorrCtlOut) für alle Kanäle 30–36 durch die Master-Code-Einheit 306 erzeugt und an die Code-Verzö-

gerungsleitungs-einheit **338** des ersten Slave-Kanals **33** verteilt, welcher diese Signale weiter in der Kette nach unten verteilt.

[0059] Die Kopie CA-Code-Sequenzen können oder können nicht durch die Code-Verzögerungsleitungs-Einheiten 308, 338, 368 der Master- und Slave-Kanäle 30, 33, 36 verzögert werden, abhängig von der Applikation. Die Code-Verzögerungsleitungs-Einheiten 308, 338, 368 können unterschiedlich für eine schnelle Akquisition und eine Lagebestimmung jeweils programmiert werden. Für eine schnelle Akquisition werden die Vorfeldeingangsselektoren 302, 332, 362 aller Kanäle 30, 33, 36 auf den gleichen Ausgang des Vorfeldes 103 gesetzt und alle Verzögerungsleitungseinheiten 308, 338, 368 werden auf eine 1/2 oder 1 CA-Code-Chip-Verzögerung programmiert. Die Korrelationseinheiten 307, 337, 367 korrelieren die individuell verzögerte CA-Code-Sequenz mit dem empfangenen Signal – je mehr Kanäle das gleiche Signal gleichzeitig verarbeiten, desto schnellere Synchronisation wird erreicht. Die gleichen Signale aus dem Vorfeld 103 werden durch eine auswählbare Anzahl von Kanälen bis hinauf zu einer Maximalanzahl von Kanälen bearbeitet, welche der Akquisitionsaufgabe zugeordnet werden können, was deshalb zu einer schnellen Akquisition führt.

[0060] Auf der anderen Seite werden für die Lagebestimmung alle Eingangsselektoren 302, 332, 362 auf einen unterschiedlichen Vorfeldausgang gelegt (d.h. sie empfangen alle das gleiche Grundsignal, aber jeder von einer unterschiedlichen Antenne 104) und die Verzögerungsleitungseinheiten 308, 338, 368 werden für eine Nullverzögerung programmiert, so dass alle Slave-Kanäle 33, 36 CA-Code-Sequenzen von der Master-CA-Code-Einheit 306 mit identischer Phase empfangen. Es ist ein spezieller Gesichtspunkt der vorliegenden Erfindung, dass die Verzögerungsleitungseinheiten, wie z.B. 308, für eine aus einer Vielzahl von vorher festgelegten Verzögerungen auswählbar sind oder für keine Verzögerung, abhängig von der Applikation.

[0061] Wie schematisch in Fig. 6 gezeigt, enthält ein gemeinsamer CA- und P-(CaP)-Kanal, z.B. 31 oder 32, die gesamte Funktionalität für eine CA-Code-Operation, wie oben mit Bezug auf die Fig. 3–Fig. 5 beschrieben, z.B. das Gebrauchen des Bildrückweismischers 315, 325, mit zusätzlichen Verstärkungen für die Korrelationseinheiten 317, 327 für die P-Code- und Y-Code-Operation. Eine getrennte P-Code-Einheit 42–45 pro Zwei-Frequenz-Kanal erzeugt die GPS- und GLONASS-P-Codes und die damit verbundene Integration der Steuersignale. Jede CaP-Code-Korrelationseinheit 317, 327 ist speziell für die Integration von P-Code- und Y-Code-Signalen adaptiert. Größere Details werden später mit Bezug auf die codelose Akquisition der Y-codierten Signale entsprechend der vorliegenden Erfindung geliefert.

[0062] Normalerweise liefert ein CA-Kanal wie z.B. 30 den Trägerdrehwinkel für den L1-P-Kanal, wie z.B. 31. Jedoch kann der L1-P-Kanal 31 auch seinen internen Trägergenerator (nicht gezeigt in Fig. 6 für 31, jedoch ähnlich zu 324 von 32) nutzen, um den Trägerdrehwinkel zu erzeugen (dies kann für eine bessere Trägerphasenleistungsfähigkeit in Gegenwart eines Multipfades nützlich sein). Die Korrelationseinheiten 317, 327 der CaP-Kanäle 31, 32 werden durch das CA-Kanal-IntEpoch-Ausgangssignal gesteuert, welches ein Teil des CorrCtl-Busses ist. Deshalb integrieren die Korrelationseinheiten 307, 317, 327 jeweils des CA-Kanals, des L1-P-Kanals und des L2-P-Kanals eines Zwei-Frequenz-Kanals über die gleiche Zeitperiode. Das IntEpoch-Signal wird auch für das Triggern des P-Code-Generators während der P-Code-Akquisition benutzt und wird deshalb auch direkt in die P-Code-Einheit 42 eingegeben. Die Rate, bei welcher der P-Code für die L1- und L2-Kanäle 31, 32 erzeugt wird, wird in dem Code NCO's der CA-Code-Einheiten 316, 326 jeweils des L1-P-Kanals 31 und eines L2-P-Kanals 32 programmiert.

**[0063]** Es wird vorgezogen, wenn nur zwei Zwei-Frequenz-Kanäle untergeordnet werden können, entsprechend den Regeln, wie sie durch die gestrichelten Linien in <u>Fig. 3</u> definiert sind. Derartiges Unterordnen verdoppelt die Anzahl der Korrelationseinheiten, welche für das Verfolgen des P-Codes auf L1 und des P-Codes auf L2 verfügbar sind, ein Merkmal, welches für die Vielpfad-Mitigation vorgesehen ist (für Kosten der halben Anzahl von verfügbaren Kanälen).

[0064] Einige Hardware ist entsprechend der vorliegenden Erfindung vorgesehen, um zu gestatten, dass unterschiedliche Kanalgruppen zusammen untergeordnet werden. Je mehr Möglichkeiten erlaubt sind, Kanäle zusammen zu gruppieren, desto größer ist der Overhead an Signalleitungen und Multiplexern. Außerdem ist, bei aktuellen Taktfrequenzen, die Summe aller Verzögerungen, welche zugelassen werden können, durch die Wiederholrate der empfangenen Signale begrenzt. Deshalb sind die Anforderungen für das Kanalunterordnen innerhalb eines AGGA 10 entsprechend der vorliegenden Erfindung vorzugsweise bis zu vier Einzelfrequenzkanäle oder bis hinauf zu zwei Zwei-Frequenz-Kanälen. Wenn ein Kanal so konfiguriert ist, dass er einen externen Trägerphasenwinkel, Code- und Korrelationssteuersignale akzeptiert, sind die unterordnenden Multiplexer der Kanalmatrix 3 vorzugsweise programmierbar, um die gewünschten Unterordnungsquellen zu selektieren. Die Auswahl kann mit Hilfe von Multiplexern oder Auswahl-Gates durchgeführt werden, wie dies sche-

matisch in Fig. 7a und b gezeigt wird. Mit Bezug auf Fig. 4 kann der Drehwinkel für die Korrektur der Trägerphase intern oder extern geliefert werden, wobei die Auswahl durch eine Auswahlschaltung, z.B. einen Multiplexer 304, durchgeführt wird. Das externe Angle- bzw. Winkelsignal kann von einem von zwei anderen vorherigen Kanälen kommen, abhängig wie die Verbindung in der untergeordneten Kette gebildet ist, entweder dem vorherigen Nachbarn (C-1) oder von dem einen, drei zurück (C-3). Deshalb wird eine Auswahlschaltung, wie sie in Fig. 7a gezeigt wird geliefert, z.B. ein Multiplexer 29, welcher zwischen dem Angle-Signal, welches entweder durch C-1- oder den C-3-Kanal geliefert wird, auswählt, abhängig von dem Angle-Sel-Signal. In ähnlicher Weise wird die Auswahl zwischen den externen oder internen Code-Signalen in Fig. 3 durch eine Auswahlschaltung durchgeführt, z.B. durch einen Multiplexer 303. Welches externe Code-Signal für den Kanal 30 ausgewählt wird, wird durch eine Auswahlschaltung bestimmt, z.B. einen Multiplexer 28, abhängig von dem Code SEL-Signal. Die Signale, welche vorzugsweise untergeordnet werden können, sind Angle-, Code-(CA-oder P-Code) und verschiedene Steuersignale, welche in CorrCtl gruppiert sind, wie dies in Fig. 7a und b gezeigt wird. Zwei diesbezügliche Signale DoubleChipRate und IntEpoch sind als Teil des CorrCtl-Busses gruppiert, um die Blockdiagramme zu vereinfachen.

[0065] Die Steuerschaltung, welche in Fig. 7b für einen CaP-Kanalmodul gezeigt wird, ähnelt denen der Fig. 7a, z.B. sind die Selektoren 26 und 27 jeweils äquivalent zu den Selektoren 29 und 28. Zusätzlich ist ein weiterer Selektor 26 erforderlich, um auszuwählen, ob der P-Code von einer P-Code-Einheit genommen wird oder im Slave-Mode empfangen wird. Zusätzlich ist ein Selektor 24 erforderlich, um zu steuern, ob das SignlnSec extern oder lokal ist. Dieses Signal wird später mit Bezug auf das Extrahieren der Y-codierten Signale beschrieben.

[0066] Die Code-Verzögerungsleitungs-Einheiten wie z.B. 308 können Early bzw. Früh-(E), Punctual bzw. Pünktlich(P) und Late bzw. Spät-(L)-Versionen des Kopiercodes und optional eine Version von IntEpoch herstellen. Die Code-Verzögerungs-Einheiten entsprechend der vorliegenden Erfindung, wie z.B. 308, können in Frequenzspreizsystemen allgemein Gebrauch finden z.B. in direkter Sequenz CDMA. Die Verzögerungen zwischen den E-, dem P- und L-Ausgangssignalen sind programmierbar. Die drei Code-Ausgangssignal-Sequenzen werden von den Korrelationseinheiten wie z.B. 307 benutzt, um das komplexe Grundbandsignal zu spreizen

[0067] Fig. 8 zeigt schematisch ein Code-Verzögerungsleitungs-Blockschaltbild in Übereinstimmung mit einer Ausführungsform der vorliegenden Erfindung. Eine Code-Verzögerungsleitungs-Einheit, z.B. 308, wählt drei Code-Phasen E, P, L von einer dreizehnstufigen Verzögerungsleitung 52 aus. Die Ausgangsseguenzen werden durch Vielfache von entweder einem halben Code-Chip oder einer CoreClk-Periode beabstandet. Das vorherige ist nur für Code-Chip-Raten kleiner als ein Viertel der CoreClk-Rate gültig. Die Taktquelle wird durch einen Selektor 54 ausgewählt, um entweder die CoreClk- oder die Double-Chip-Rate zu sein. Die P-Version des Codes wird von einem Anschluss der Verzögerungsleitung 52 genommen. Die Verzögerung von dem Eingangs-Code-Signal zu der P-Version desselben ist wenigstens zwei DLClock-Perioden und höchstens sieben DLClock-Perioden (Standardwert). CodeOut (welcher an den nächsten Kanalmodul in der Kette, falls eine existiert, geleitet wird) ist entweder eine nicht verzögerte oder eine verzögerte Version des Codes und wird für das Kanalunterordnen benutzt. Die Auswahl zwischen der nicht Verzögerten und der Verzögerten wird in der Selektorschaltung 56 durchgeführt. Zum Konfigurieren der Kanäle für die Lagebestimmung ist eine Nullverzögerung zwischen Code und CodeOut wählbar. Durch die selektive Operation der zwei Selektorschaltungen 51 und 53 kann die Verzögerung von Code gegenüber der verzögerten Version des CodeOut zwischen zwei und dreizehn DLClock-Perioden betragen. Durch die selektive Operation der Selektorschaltungen 51 und 55 kann die Verzögerung von Code gegenüber E zwischen einer und sechs DLClock-Perioden betragen.

[0068] Die Verzögerungsleitungseinheiten wie z.B. 308 von verschiedenen Kanälen können kaskadiert werden, um Code-Sequenzen mit Verzögerungen größer als jene herzustellen, welche mit einer einzelnen Verzögerungsleitung 52 möglich sind. Dieses Merkmal ist für die schnelle Akquisition und die Multipfadmitigation bzw. -minderung vorgesehen. Ein Schaltsteuermodul 58 unterstützt das Zeitmultiplexen der Codesequenzen bei unterschiedlichen Codeabständen. Diese Technik kann für Multipfadmitigation benutzt werden, wobei das Korrelationsprofil gemessen wird. Es ist jedoch bei Applikationen mit hoher Dynamik nicht vorzuziehen.

**[0069]** Das Chip-Spacing-PL-Feld des DelayLineMode-Registers bzw. Verzögerungsleitungsmodusregisters (z.B. Teil eines Einchip-Speichers) setzt einen Chipabstand zwischen den P- und L-Codesequenzen fest. Die folgenden Chipabstände zwischen den E- und P-Sequenzen oder den P- und L-Sequenzen können programmiert werden, wobei die Selektoren **51**, **55**, **57**: T, 2T, 4T, 6T und 1/2 Chip, 1 Chip, 2 Chips oder 3 Chips benutzt werden, wobei T die CoreClk-Periode ist. Folglich können die folgenden Chipabstände zwischen E- und L-Sequenzen programmiert werden: 2T, 3T, 4T, 5T, 6T, 7T, 8T, 10T, 12T und 1 Chip, 1,5 Chips, 2 Chips, 2,5 Chips,

3 Chips, 3,5 Chips, 4 Chips, 5 Chips oder 6 Chips. Das Beabstanden in Chips kann nur benutzt werden, wenn die CoreClk-Frequenz wenigstens vier Mal die Chiprate ist. Wenn dies nicht der Fall ist, wird vorzugsweise eine Chipbeabstandung in Vielfachen der CoreClk-Periode benutzt.

**[0070]** Der Eingangsselektor **51** wird für das Kaskadieren der Code-Verzögerungsleitungen oder Slave-Kanäle benutzt. Der Zweck desselben besteht darin, eine programmierbare Verzögerung zwischen den Korrelationsmessungen der Slave-Kanäle zu liefern. Speziell gestattet es ein programmierbares Chipbeabstanden für schnelle Akquisition und Multipfadmitigation. Die Eingangs-Codesequenz kann am Anschluß 0 bis 5 der Verzögerungsleiting **52** eingefügt werden. Für ein korrektes Verhalten sollte der Eingangsselektor **51** einen Verzögerungsleitungsanschluß mit einer Nummer kleiner oder gleich der Anzahl des Anschlusses wählen, welcher für die E-Sequenz gewählt wurde.

**[0071]** Der kaskadierende Ausgang CodeOut kann mit einem der Anschlüsse 6 bis 12 der Verzögerungsleitung **51** oder direkt mit dem Code-Eingang verbunden werden. Durch das Verbinden der Ausgangsselektion einer Code-Verzögerungsleitungseinheit mit dem Eingang einer anderen Verzögerungsleitungseinheit kann eine einzelne lange Verzögerungsleitung, welche aus verschiedenen Slave-Verzögerungsleitungen oder unterschiedlichen Kanälen besteht, geschaffen werden. Dieser Ausgang kann unabhängig vom Chipabstand programmiert werden.

[0072] Eine Schaltsteuerfunktionalität wird für das zeitgleiche Nutzen eines einzelnen Korrelators oder unterschiedlicher Code-Sequenzen benutzt. Dies gestattet das Korrelationsprofil zu messen, ohne dass extra Korrelatoren benötigt werden und dies ist allgemein für das Spreizen von Frequenzspreizsignalen anwendbar. Wenn diese Technik genutzt wird, wird ein unterschiedliches Chipbeabstanden (vor dem Zeitablauf im Bezug auf P) für die E-Sequenz durch die Selektorschaltung 55 bei jedem IntEpoch-Interval ausgewählt, es wird jedoch ein einzelner Korrelator benutzt, um die Ergebnisse von jeder Auswahl zu akkumulieren. Die Fähigkeit, selektiv die Zeitdifferenz zu bestimmen, d.h. die Verzögerung oder das vorherige Auftreten, zwischen den Eund P- oder den P- und L-Sequenzen für jede Integrationsperiode ist ein signifikanter Vorteil der vorliegenden Erfindung. Ein Vorteil dieses Verfahrens besteht darin, dass die Anzahl von getrennten Korrelatoren, welche erforderlich sind, um das Korrelationsprofil zu messen, reduziert ist. Die zeitliche Seguenz wird durch das Schalt-Steuermodul 58 gesteuert. Dieses ist vorzugsweise voll programmierbar um über zwei bis vier Zyklusperioden zu sequenzialisieren. Dies beinhaltet die Anzahl der Zeitmultiplex-Anschlüsse (1 bis 4), ebenso wie die Anschluß-Sequenz. Zum Beispiel für eine Schaltsequenz von drei, kann die Schalt-Steuersequenz programmiert werden, um T, 2T und 4T oder T, 4T und 6T etc. zu sein. Das Setzen wird in einem Register bei einer IntEpoch-Abtastung gepuffert, so dass der Microprozessor 101 lesen kann, mit welchem E-P-Abstand die Integrationswerte korrespondieren. Die IntEpoch-Abtastung wird benutzt, um die Übergänge zu der nächsten Schalteinstellung des Integrationsintervalls zu synchronisieren. Das Vorsehen eines programmierbaren Schalters 58 ist ein signifikanter Vorteil der vorliegenden Erfindung, da es die sequenzielle Bestimmung der Korrelationswerte für die E-Sequenzen bei einem unterschiedlich fortschrittlichem Zeiteinstellen in Bezug auf die P-Sequenz gestattet, wobei deshalb das Erzeugen eines Korrelationsprofils gestattet wird, ohne dass ein getrennter Korrelator für jede unterschiedliche fortschrittliche Zeiteinteilung der E-Sequenz erforderlich ist. Obwohl die vorliegende Erfindung mit Bezug auf das Schalt-Steuermodul 58 beschrieben wurde, welches die Operation der frühen Verzögerungsleitung 55 steuert, beinhaltet die Erfindung auch innerhalb ihres Umfangs ein Schalt-Steuermodul zum Steuern der Operation der späten Verzögerungsleitung 57 in einer ähnlichen Weise.

**[0073]** Fig. 9a und b zeigen zwei Beispiele der Unterordnungs- bzw. Slave-Fähigkeit des AGGA entsprechend der vorliegenden Erfindung. Fig. 9a zeigt eine mögliche Konfiguration mit drei Kanälen, welche für eine schnelle Akquisition aufgebaut sind. Die Verzögerungsleitungseinheiten 52, 52' und 52" werden durch das DoubleChipRate-Signal getaktet. Neun komplexe Integratoren sind so angeordnet, dass die neun Codesequenzen, welche durch 0,5; 1; 1,5; 2; 2,5; 3; 3,5 und 4 Codechips relativ zu dem ersten E-Ausgangsanschluß beabstandet sind, korrelieren. Fig. 9b zeigt drei Verzögerungsleitungen 52, 52' und 52", welche für Multipfadmitigation untergeordnet sind. Die neun Korrelatoren sind so angeordnet, dass die neuen Codesequenzen, welche ET3, EE, E, E-L, P, L, LL, LT3, LT4 sind, korrelieren. Bei einer CoreClk-Rate von 30 MHz, ist der EL-Abstand ungefähr 8/3 GPS-P-Code-Chips oder 8/30 GPS-CA-Code-Chips.

[0074] Die Verzögerungsleitungseinheiten, wie z.B. 308, unterstützen die Vielpfadmitigation in zweifacher Weise: im Kanalunterordnen und im Zeitmultiplexen. Das Kanalunterordnen gestattet, dass viele Korrelatoren so kaskadiert werden, dass mehrere Abtastungen der Korrelationsfunktion erhalten werden können, Fig. 9b zeigt ein Beispiel von drei Kanälen mit untergeordneten Code-Verzögerungsleitungen. Der Abstand zwischen zwei benachbarten Sequenzen ist 4T. Mit einem CoreClk von 20 MHz ist dies äquivalent zu zwei P-Co-

de-Chips. Der rechts äußerste Teil der <u>Fig. 9b</u> wird in einem Spreizmodul einer Korrelationseinheit durchgeführt.

[0075] Ein Korrelationseinheitsblockschaltbild wird in Fig. 10 gezeigt. Eine Korrelationseinheit wie z.B. 307 entsprechend der vorliegenden Erfindung besteht aus einem komplexen Spreizmodul 62 und drei komplexen Integrationsmodulen 64, 66, 68. Das Spreizmodul 62 multipliziert das komplexe Ausgangssignal (Dataln) des Bildrückweismixers mit drei Codesequenzen. Jedes Integrationsmodul 62, 64, 66 integriert eine gespreizte Datensequenz über ein programmierbares Integrationsintervall gleich für alle Integratoren 62, 64, 66 einer Korrelationseinheit 307.

**[0076]** Das Spreizmodul **62** multipliziert das komplexe Grundbandsignal mit drei Codesequenzen. Jede Codesequenz ist eine Kombination der drei Frequenzspreizcodesequenzen E, P und L. Gültige Kombination der Codesequenzen E, P und L sind: (P, E, L), (P, E-L, Off), (P, E-L, E), (P, E-L, L), (P, P, Off) und (B, Off, Off), wobei Off für "nicht benutzt" und B für "Umgangen" steht. Der hauptsächliche Gebrauch für die unterschiedliche Kombinationen der Codesequenzen ist:

- (P, E, L): diese Kombination wird für schnelle Akquisition oder für das Messen von absoluten Korrelationswerten einer Datensequenz, welche mit E, P und L- Code-Sequenzen gespreizt ist, benutzt, z.B. für Vielpfadmitigationstechniken. Auch das Verfolgen mit getrennten E- und L-Messungen nutzt diese Kombination.

- (P, E-L, Off): Diese Kombination wird für den Verfolgungsmodus benutzt und wenn keine Information über die absoluten E- oder L-Korrelationswerte benötigt wird.

- (P, E-L, E): Diese Kombination wird für den Verfolgungsmodus für Vielpfadidentifikation benutzt. Eine extra E-Messung wird erhalten, wenn drei Kanäle entsprechend zu **Fig.** 9(b) untergeordnet sind.

- (P, E-L, L): Diese Kombination wird für den Verfolgungsmodus für Vielpfadidentifikation genutzt. Eine extra L-Messung wird erhalten, wenn drei Kanäle untergeordnet sind, wie dies in **Fig.** 9(b) gezeigt ist.

- (P, P, Off): Diese Kombination nutzt nur die P-Sequenz. Dies wird in dem Slave-Kanal benutzt, welcher für den hybriden Paralell-Multiplex-Lagebestimmungsmodus konfiguriert ist.

- (B, Off, Off): Diese Kombination wird im Kalibriermodus benutzt. Der Spreizer **62** wird umgangen und nur der erste Integrator wird genutzt.

**[0077]** Der Ausgang des Spreizmoduls **62** sind drei komplexe Sequenzen der gespreizten Daten des DesprValue1–3. Der I- und Q-Wert des DesprValue ist entweder –3, –1, 0, 1 oder 3. Der Wert 0 wird nur in E-L-Konfiguration auftreten, in diesem Fall werden die Korrelationswerte auch durch zwei dividiert.

**[0078]** Ein Integrationsmodul **64**, **66**, **68** ist ein komplexer Integrator. Das Integrationsmodul **64**, **66**, **68** der vorliegenden Erfindung kann allgemeine Anwendung im Spreizen von Frequenzspreizsignalen finden, z.B. in CDMA-Empfängern mit direkter Sequenz. Die Korrelationseinheit eines CA-Kanals enthält CA-Code-Integratoren, während die Korrelationseinheit eines CaP-Kanals CaP-Code-Integratoren enthält. Ein Blockschaltbild des CA-Code-Integratormoduls **70** wird in **Fig. 11** gezeigt.

[0079] Ein CA-Code-Integrator agiert als ein 22-Bit-Additionsglied. Dieses wird jedoch vorzugsweise als Zweistufenintegrator realisiert, welcher aus einer niedrigen Anzahl von Bit-Akkumulatoren besteht, z.B. einem 9-Bit Zweierkomplement-Primär-Akkumulator 72 und einem Akkumulator mit Vollanzahl von Bits, z.B. einem 22-Bit-Zweierkomplement-Sekundär-Akkumulator 74. Das Ergebnis des Primär-Akkumulators 72 wird bei einer Rate gleich zu der CA-Code-Chip-Rate in einem ersten Integrationspuffer 73 ausgegeben. Der zweite Akkumulator 74 integriert den ausgegebenen Inhalt des ersten Akkumulators 72 über eine längere Periode, z.B. eine IntEpoch-Periode. Das Ergebnis wird doppelt in einem zweiten Integrationspuffer 75 gepuffert und bis zum Ende der nächsten Integrationsperiode gehalten, wenn es durch den neuen Integrationswert überschrieben wird. Ein Vorteil dieser Zweistufenintegration besteht in der Tatsache, dass der Leistungsverbrauch dramatisch reduziert werden kann. Nur der kleine Primär-Akkumulator 72 arbeitet bei der hohen Taktrate, während der große Sekundär-Akkumulator 74 nur bei der Chip-Rate läuft. Das Benutzen eines Zweistufenintegrators für den CA-Code ist einer der großen Vorteile verglichen mit den bekannten Integratoren der EP 508 621.

[0080] Im hybriden Parallel-Multiplex-Lagebestimmungsmodus können die Integrationswerte auch in den Sekundär-Akkumulator-Integrationspuffern **75** bei einer ASE-Abtastung gespeichert werden. Zusammen mit der Auswahl der (P, P, Off)-Code-Sequenz-Kombination in dem Spreizmodul **62**, wird ein komplexer Integrator **64**, **66**, **68** programmiert, um die Sekundär-Akkumulator-Integrationspuffer **75** bei einer IntEpoch-Abtastung zu aktualisieren, während der andere freigegebene Komplexintegrator **64**, **66**, **68** die Integrationspuffer bei einer ASE-Abtastung aktualisieren wird. Die Integratoren selbst werden dann bei beiden IntEpoch- und ASE-Abtastungen zurückgesetzt.

[0081] Ein CaP-Code-Integrationsmodul 80 entsprechend der vorliegenden Erfindung kann konfiguriert werden, um die CA-Code-modulierten Signale, die P-Code-modulierten Signale oder die verschlüsselten P-Code-modulierten Signale zu akkumulieren, d.h. die Y-Code-modulierten Signale. Ein Blockschaltbild des CaP-Code-Integrationsmoduls entsprechend dieser Ausführungsform wird in Fig. 12 gezeigt. Ein CaP-Code-Integrator 80 entsprechend einer Ausführungsform der vorliegenden Erfindung besteht aus einer niedrigen Anzahl Primär-Akkumulator miteiner geringen Anzahl von Bits, z.B. einem 9-Bit-Zweier-Komplement-Primär-Akkumulator 82 und einem Sekundär-Akkumulator mit voller Anzahl von Bits, z.B. einem 22-Bit-Zweier-Komplementär-Sekundär-Akkumulator 84. Bei normalem Betrieb werden beide Akkumulatoren 82, 84 niemals überfließen und es gehen keine Daten zwischen dem ersten und zweiten Akkumulator verloren. Die folgenden Betriebsmoden können unterschieden werden:

CA-Modus: Der CaP-Code-Integrator **80** ist konfiguriert, um die CA-Code-modulierten Signale zu verfolgen und verhält sich identisch zu dem CA-Code-Integratormodul **70**, welcher oben beschrieben wurde. Die Ergebnisse des Primär-Akkumulators **82** werden bei einer Rate gleich zu der CA-Code-Chip-Rate in einen Integrationspuffer **83** ausgegeben. Der zweite Akkumulator **84** ist konfiguriert, um nur ein Addierglied zu sein und ist immer freigegeben.

Lagebestimmungsmodus: Im Lagebestimmungsmodus wird der CaP-Code-Integrator sowohl bei der IntE-poch- als auch ASE-Abtastung zurückgesetzt. Dieser Modus korrespondiert zu dem (P, P, Off)-Spreizmodus. P-Modus: Der CaP-Code-Integrator 80 ist konfiguriert, um die P-Code-modulierten Signale zu verfolgen. Der einzige Unterschied zwischen dem CA-Modus und dem P-Modus besteht in der primären Ausgabelogik 81. Die SecondaryEnable-Abtastung steuert den Übergang der Primär-Akkumulator-Inhalte zu dem Sekundär-Akkumulator 84, während die WChipEdge-Abtastung das Puffern und das Zurücksetzen des Primär-Akkumulators 82 steuert. Der Sekundär-Akkumulator 84 ist konfiguriert, um nur ein Addierglied zu sein und ist immer freigegeben (EnableSel ist 0). Die Sekundär-Akkumulator-Integrationspuffer 85 werden auf Befehl der IntEpoch-Abtastung aktualisiert.

Y-Modus: In dem Y-Modus wird ein Signal empfangen, welches aus einem P-Code besteht, welcher mit einem unbekannten W-Code moduliert ist. Ein exaktes Spreizen ist nicht möglich, da es notwendig ist, abzuschätzen, ob der W-Code ausreichend die Zeitablauf- und Phasendaten der empfangenen Signale erhält. Um ein derartiges Signal zu dekodieren wird eine W-Code-Schätzfähigkeit zwischen dem Primär- und Sekundär-Akkumulator 82, 84 eines Zweifrequenzkanals entsprechend der Erfindung geliefert, wie dies schematisch in Fig. 13 gezeigt wird. Es gibt mehrere Moden, in welchen das CaP-Integrationsmodul 80 W-codierte und P-codierte Signale bearbeiten kann, von denen jedes eine Ausführungsform der vorliegenden Erfindung ist:

Im Allgemeinen integriert jeder Primär-Akkumulator **82L1**, **82L2** jedes Kanals L1 und L2 die eingehenden Daten (möglicherweise mit dem bekannten P-Code gespreizt), während einer W-Chip-Periode (erzeugt in dem W-Raten-Generator, welcher später beschrieben wird). Basierend auf diesem Ergebnis schätzt die W-Code-Schätzeinheit **86** den entsprechenden Wert der W-Rate ab.

[0082] Codeloses Quadrieren: Funktionell arbeitet der CaP-Code-Integrator 80 als ein einzelnes Addierglied, welches eine Folge von Abtastungen über eine IntEpoch-Periode addiert. Diese codelose Quadriertechnik erfordert eine Schaltung (nicht gezeigt), welche das eingehende Signal vor den Addierbearbeitungen quadriert. Eingehende Abtastungen, welche nicht durch die lokal generierten P-Code-Kopierfolge gespreizt wurden, werden in den ersten Akkumulatoren 82L1, 82L2 über eine Zeitperiode hinweg integriert, z.B. ein W-Code-Intervall (als bekannt angenommen), welches durch WchipEdge signalisiert ist. Die Primär- und Sekundär-Akkumulatoren 82, 84 (82L1, 82L2; 84L1, 84L2) werden im Addiermodus konfiguriert und sind immer freigegeben. Die zweiten Integrationspuffer 85 werden bei den IntEpoch-Abtastungen aktualisiert.

[0083] Codiertes Quadrieren: Funktionell arbeitet der erste Akkumulator 82 als ein Addierglied, welches eine Sequenz von gespreizten (mit einer lokal erzeugten Kopie des W-Code) Abtastungen über ein W-Code-Intervall, welches durch WchipEdge signalisiert wird. Der Sekundär-Akkumulator 84 arbeitet als ein Addierglied, welches die absoluten Werte des ersten Akkumulators 82 addiert. Der Sekundär-Akkumulator 84 ist konfiguriert, um absolute primäre Akkumulationswerte durch Auswählen des SignInSec-Eingangsbits auszuwählen (dies ist eine Art von "Quadrieren"). Dieses Bit ist vorzugsweise das Vorzeichenbit des Wertes von dem Q-Zweig des komplexen Primär-Akkumulators 82, welcher die "Pünktlich-Code-Kopie (P von E, P, L) des ersten Integrators 82 bearbeitet (dieser Zweig hat normalerweise die größte Stärke des relevanten Signals, jedoch ist die vorliegende Erfindung nicht darauf beschränkt). Die Sekundär-Akkumulator-Integrationspuffer 85 werden bei IntEpoch-Abtastungen aktualisiert.

**[0084]** Codierte Kreuzkorrelation: Funktionell arbeitet der Primär-Akkumulator **82** als ein Addierglied, welches eine Sequenz von gespreizten (mit einer lokal erzeugten Kopie des P-Codes) Abtastungen über ein W-Code-Intervall, welches durch WchipEdge signalisiert ist, addiert. Der Sekundär-Akkumulator **84** arbeitet als ein Addierglied, welches die primären bzw. ersten Werte eines L1-(alternativ L2-)Kanals addiert, multipliziert mit

dem Vorzeichenbit des L2-(alternativ L1-)Primär- Akkumulators. Der Sekundär-Akkumulator **84** ist konfiguriert, um absolute Erstakkumulationswerte durch Auswählen des SignlnSec-Eingangsbits zu addieren. Für einen L1-(L2)-Kanal ist dieses Bit das Vorzeichenbit des Q-Zweiges des komplexen primären-Akkumulatorwertes des ersten Integrators **82** des L2-(L1)-Kanals. Der sekundär-Akkumulator 84 wird durch die SecondaryEnable-Abtastung freigegeben, welche durch die P-Code-Generatoreinheit erzeugt wird. Die Sekundär-Akkumulator-Integrationspuffer **85** werden bei den IntEpoch-Abtastungen aktualisiert.

[0085] Kombinierte Y-Code-Abschätzung: In einer weiteren Ausführungsform der vorliegenden Erfindung arbeitet der Primär-Akkumulator 82 funktionell als ein Addierglied, welches eine Folge von gespreizten (mit einer lokal erzeugten Kopie des P-Codes) Abtastungen über ein W-Code-Intervall addiert, welches durch WchipEdge signalisiert ist. Der Sekundär-Akkumulator 84 arbeitet als ein Kombinierglied, welches die Primärwerte des Primär-Akkumulators 82 und des abgeschätzten bzw. voraussichtlichen W-Code-Chips kombiniert. Ein Verfahren des Kombinierens beinhaltet das Aufsummieren der Werte, welche durch den Primär-Akkumulator 82 ausgegeben werden, multipliziert durch den abgeschätzten W-Code-Chipwert. Zum Beispiel beinhaltet die vorliegende Erfindung das Kombinieren der Ausgangssignale des Primär-Akkumulators 82 in Abhängigkeit von einem Vertrauensgrad bzw. einer Confidence-Zahl bei jedem Ausgangssignal des Akkumulators 82. Der voraussichtliche W-Code-Chip wird durch Vergleichen der Absolutwerte des ersten Akkumulators des Q-Zweiges des komplexen Primär-Akkumulator-Wertes des ersten Integrators 82 des L1- und L2-Kanals erhalten. Der voraussichtliche bzw. geschätzte W-Code-Chipwert (oder Y-Codewert) ist das Vorzeichenbit des größten Wertes aus diesem Vergleich. Wegen der niedrigeren Übertragungsleistung kann ein Skalierwert an dem L2-Signal angelegt werden, welches gebräuchlicherweise leistungsfähiger ist als das L1-Signal. Ein Wert von 0,75 ist gebräuchlich. Die Sekundär-Akkumulator-Integrationspuffer 85 werden bei den IntEpoch-Abtastungen aktualisiert. Fig. 14 zeigt eine Ausführungsform der Auswahllogik, welche zum Liefern der Y-Code-Abschätzung, welche oben angezeigt ist, erforderlich ist. Die Ausgangssignale der Primär-Akkumulatoren 82L1 und 82L2 für die L1- und L2-Kanäle werden jeweils an die Absolutwertschaltungen 861, 862 angelegt, wohingegen das Vorzeichen jeder dieser primär akkumulierten Ausgangssignale zu einem Y-Code-Schätzselektor (oder W-Code-Chip-Schätzselektor) 865 übertragen wird. In den Absolutwertschaltungen 861, 862 wird der Absolutwert des jeweiligen ersten Akkumulators bestimmt. Der Absolutwert des Ausgangssignals aus der Schaltung 862 kann modifiziert werden, um empfangene Leistungsdifferenzen zwischen den L1- und L2-Signalen zuzulassen, z.B. es kann mit einem Faktor wie z.B. 0,75 (durch das Multiplizierglied 864) multipliziert werden. Die modifizierten Absolutwerte werden an einen Komparator 864 eingegeben, welcher die zwei Absolutwerte vergleicht und ein Signal an einen Y-Code-Schätzselektor 865 ausgibt, wobei angezeigt wird, welches der Signale von L1 oder L2 den größten Absolutwert besitzt. Der Selektor 865 wählt das Vorzeichen des Signals mit dem größten Absolutwert als den Wert für den W-Code-Chip aus oder, optional einen anderen Wert. Der optional andere Wert kann Null sein, z.B. wenn das Vertrauen in das Ergebnis niedrig ist. Das Ausgangssignal für den Y-Code-Schätzselektor 865 wird mit jedem der primär akkumulierten Werte der L1- und L2-Akkumulatoren 82L1 und 82L2 für den Gebrauch in den jeweiligen Sekundär-Akkumulatoren 84L1 und 84L2 kombiniert.

**[0086]** Eine P-Code-Einheit wie z.B. **42** besitzt zwei Hauptfunktionen: Erzeugen der Kopien der GPS- und GLONASS-P-Code-Sequenzen für L1 und L2 und Erzeugen der W-Code-Integrations-Steuer-Abtastsignale (WchipEdge) für L1 und L2. Das Letztere wird für das Verfolgen des GPS-Y-Code-Signal mit dem codierten Quadrieren, der codierten Cross-Korrelationstechnik und anderen Techniken, welche oben beschrieben wurden benutzt, speziell der kombinierten Y-Code-Abschätzungsausführungsform der vorliegenden Erfindung. Eine P-Code-Einheit **42–45** ist pro Zweifrequenzkanal vorgesehen.

[0087] Die P-Code-Sequenz und die Sequenz der W-Code-Integrations-Steuerabtastungen sind die gleichen für L1 und L2, jedoch mit einer relativen Verzögerung aufgrund von ionosphärischen und Vorfeldgruppen-Verzögerungen bei den zwei Frequenzen L1 und L2. Die gesamte Gruppenverzögerungsdifferenz zwischen L1 und L2 übersteigt nicht eine Mikrosekunde. Diese Verzögerung ist die Summe der maximal spezifizierten ionosphärischen Gruppenverzögerungen von 800 ns zwischen L2 nacheilend zu L1 und 200 ns aufgrund der Vorfeldgruppenverzögerungen. Deshalb kann die gesamte Gruppenverzögerung zwischen L1 und L2 zwischen –200 ns und 1 Mikrosekunde variieren. Eine Verzögerung von 1 Mikrosekunde ist äquivalent zu 10 GPS-P-Code-Chips oder 5 GLONASS-P-Code-Chips, während 200 ns mit 2 GPS-P-Code-Chips oder 1 GLONASS-P-Code-Chip korrespondieren. Diese Zahlen sind um einen Faktor von 10 niedriger für CA-Code-Chips.

[0088] Ein P-Code-Einheit-Blockschaltbild entsprechend einer Ausführungsform der vorliegenden Erfindung wird in Fig. 19 gezeigt. Die Hauptmodule derselben sind der P-Code-Generator 92, der W-Rate-Generator 94, der Umlaufdifferenzzähler und das Schaltsteuergerät 96, die P-Code- und WchipEdge-Verzögerungsleitungen 91, 93 und die Sequenzschalter 95, 97, 99. Der P-Code-Generator 92 enthält die Funktionalität zum Erzeugen von Kopien der GPS- und GLONASS-P-Code-Sequenzen, der P-Code-Messgrößen, und der Funktionalität,

um den P-Code zu initialisieren und das P-Code-Übergeben durchzuführen, welches das Freigeben des P-Codes steuert. Da beide Code-Sequenzen verzögerte Versionen des gleichen Codes sind, werden ein Einzel-P-Code-Generator 92 und ein Einzel-W-Rate-Generator 94 mit zusätzlicher Verzögerungsleitung 93 und eine Steuer- und Schaltlogik benutzt, um beide Sequenzen für L1 und L2 herzustellen. Die nachlaufende Sequenz wird von einer Verzögerungsleitung 91, 93 erhalten, welche durch den Umlauf- bzw. Zyklusdifferenzzähler 96 gesteuert wird, während die andere direkt von dem Generatorausgangssignal, welches die Kopie jeweils des P-Codes und des W-Chip-Edge ist, genommen wird. Der Zyklusdifferenzzähler 96 zeichnet die Phasendifferenz zwischen der L1-P-Code-Sequenz und der L2-P-Code-Sequenz als eine ganzzahlige Zahl der Code-Chips auf. Diese Phasendifferenz ist die gleiche für die L1-L2-W-Chip-Ränder. Eine Anfangsdifferenz wird durch den Mikroprozessor 101 programmiert und stellt die relative Verzögerung der L1- und der L2-Sequenzen dar. Es ist die genaue Berechnung dieser Differenz, welche durch die Akquisitionssoftware ausgeführt werden muss. Die Schaltsteuerung und die Schalter 95, 97, 99 geben den Mikroprozessor 101 frei, um auszuwählen, welche der zwei L1- oder L2-Sequenzen des P-Code und der W-Chip-Ränder dem anderen hinterherläuft.

**[0089]** Der GLONASS-P-Code ist eine binäre Sequenz mit einer nominellen Chiprate von 5,11 MHz, welche durch den Code NCO und eine Sequenzdauer von präzise einer Sekunde erzeugt wird. Der P-Code ist der zehnte Anschluß eines 25-Anschluß-Linear-Rückkopplungsschieberegisters (LFSR) mit dem Erzeugen eines Polynoms, welches definiert ist als:

$$G_p = 1 + X^3 + X^{25}$$

**[0090]** Die Code-Sequenz ist kurz im Zyklus bis zu einer Länge von 5,110,000 Chips, dies korrespondiert mit dem LFSR-Zustand von "0CBE669" Hexadezimal. Der Anfangszustand des P-Code-Generators ist ein Vektor von 25·Eins. Dieser Zustand koinzidiert mit der Einsekundenmarke in der GLONASS-Navigationsnachricht.

**[0091]** Der GPS-P-Code ist eine binäre Sequenz mit einer nominellen Chiprate von 10,23 MHz, welche durch den Code NCO und einer Sequenzdauer von präzise einer Woche erzeugt wird. Der GPS-P-Code ist eine Modulo-2-Addition von zwei Sequenzen, der X1-Sequenz und der X2-Sequenz. Der Code für SV wird durch Verzögern der X2-Sequenz durch Chips erhalten, welche vor der 2-Modulo-Addition gegenüber der X1-Sequenz sind, wobei ein Wert auftritt, welcher von 1 bis 37 reicht. Der X1-Code wird durch die Modulo-2-Addition von zwei kurzzyklischen Sequenzen maximaler Länge erzeugt, dessen Erzeugungspolynome definiert sind als:

$$X1A = 1 + X^6 + X^8 + X^{11} + X^{12}$$

$$X1B = 1 + X^{1} + X^{2} + X^{5} + X^{8} + X^{10} + X^{11} + X^{12}$$

**[0092]** Die X1A-Sequenz ist zyklisch kurz bis zu einer Länge von 4092, während die X1B-Sequenz zyklisch kurz bis zu einer Länge von 4093 ist. Die X1-Sequenz besitzt eine Periode von 3750 X1A-Perioden, welche 15,345,000-P-Code-Chips oder 1,5 Sekunden entspricht. Wenn die X1B LFSR ihre 3749-te Periode vollendet, wird sie für die Dauer von 343-Chip-Perioden gehalten (bis die X1A LFSR ihre 3750-te Periode vollendet). Bei der Vollendung jeder X1-Periode werden beide X1 LFSRs auf ihre Anfangszustände zurückgesetzt, wie dies in Tabelle 1 definiert ist. Die X1-Epoche zeigt das Ende jeder X1-Periode an.

**[0093]** Ähnlich zu dem X1-Code wird der X2-Code durch die Modulo-2-Addition von zwei Sequenzen mit kurzem Zyklus und maximaler Länge erzeugt, deren Erzeugungspolynom definiert ist als:

$$X2A = 1 + X^{1} + X^{3} + X^{4} + X^{5} + X^{7} + X^{8} + X^{9} + X^{10} + X^{11} + X^{12}$$

$$X2B = 1 + X^2 + X^3 + X^4 + X^8 + X^9 + X^{12}$$

**[0094]** Die X2A-Sequenz ist zyklisch kurz bis zu einer Länge von 4092, während die X2B-Sequenz zyklisch kurz ist bis zu einer Länge von 4093. Ähnlich zu der X1-Sequenz enthält die X2-Periode 3750 X2A-Perioden. Wenn die X2B LFSR ihre 3749-te Periode vollendet, wird sie anfangs für die Dauer von 343-P-Code-Chip-Perioden gehalten. Wenn die X2A LFSR ihre 3750-te Periode vollendet, wird sie auch gehalten. Nachfolgend werden sowohl die X2A- und die X2B-LFSRs für eine weitere Dauer von 37P-Code-Chip-Perioden gehalten, was dazu führt, dass die X2-Periode 37 Chip-Perioden länger als die X1-Periode ist. Nach dieser Verzögerung werden die X2A- und die X2B-LFSRs auf die Anfangszustände zurückgesetzt, wie dies in Tabelle 2 gezeigt wird.

Tabelle 1

| LFSR | Anfangszustand |

|------|----------------|

| X1A  | 001001001000   |

| X1B  | 010101010100   |

| X1A  | 100100100101   |

| X2B  | 010101010100   |

**[0095]** Der Z-Zähler, welcher in den P-Code-Einheiten wie z.B. 42 plaziert ist, ist ein 19-Bit-Zähler, mit einem gültigen Bereich von 0 bis 403,199 (Periode von 403,200). Dieser Zähler zählt die Anzahl der abgelaufenen X1-Epochen seit dem Start der Woche, im Allgemeinen als das Z-Zählen bezeichnet. In seinem Endzustand signalisiert der Z-Zähler End Of Week (EOW) bzw. Ende der Woche. Während der letzten X1A-Periode einer Woche und nach Erreichen ihrer Endzustände werden die X1B-, X2A- und X2B-Generatoren gehalten, bis der X1A-Generator seinen Endzustand erreicht. Die End-X1A-Epoche löst aus, dass alle Generatoren von ihren jeweiligen Anfangszuständen neu gestartet werden und dass Z-Zählen auf 0 zurückgesetzt wird.

**[0096]** Wenn der Initialisierprozess des P-Code-Generators **92** getriggert wird, wird der X1-Generator auf die Anfangszustände, welche in Tabelle 1 gezeigt werden, initialisiert. Um die korrekte relative Phase zwischen den X1- und den X2-Sequenzen entsprechend der programmierten Z-Zählung zu erstellen, wird der X1-Generator automatisch 37 Mal der Z-Zählung getaktet. Nachdem der X1-Generator seinen korrekten Zustand erreicht, wird der X2-Generator auf die Anfangszustände, welche in Tabelle 1 gezeigt werden initialisiert. Darauffolgend werden beide Generatoren bis zum Auftreten einer X1-Epoche getaktet und dann angehalten. Dieser Initialisierprozess dauert eine Anzahl von Zyklen, entsprechend einer exakt vollen X1-Periode von 1,5 s, d.h. 15,345,000 Zyklen.

[0097] Nachdem der P-Code-Generator 92 initialisiert wurde, startet das Übergeben des P-Codes die Erzeugung einer P-Code-Sequenz bei dem korrekten Zeitpunkt. Dieser Mechanismus erfordert das Zusammenwirken von Hardware und Firmware. Nach dem Initialisieren sollte der P-Code-Generator 92 nicht frei gegeben werden, bis das erste Bit der Präambel des nächsten Unterrahmens empfangen wurde. Da das Dekodieren der Navigationsdaten eine Aufgabe der Firmware ist, muss dieses Ereignis durch die Firmware signalisiert werden. Der P-Code-Generator 92 wird dann auf das Folgende aktive IntEpoch freigegeben. Nach dem Übergeben wird das Einstellen automatisch zurückgesetzt.

**[0098]** Die P-Code-Messgröße wird benutzt, um einen hochpräzisen Pseudo-Bereich zu finden. Er wird aus einem 24-Bit-Zähler erhalten, welcher die Anzahl von P-Code-Chips zählt. Er wird zurückgesetzt, nachdem er eine Zahl gleich der nominalen Zahl des P-Code-Chips pro Sekunde für GLONASS und für 1,5 Sekunden für GPS erreicht hat. Die Anzahl ist gleich zu 5,110,000 GLONASS-P-Code-Chips oder 15,345,000 GPS-P-Code-Chips. Am Ende jeder Messepoche wird die P-Code-Chip-Zählung in einem Messgrößenregister gespeichert. Der P-Code-Chip-Zähler wird bei dem P-Code-Übergeben zurückgesetzt.

**[0099]** Der W-Rate-Generator **94** erzeugt die Steuerabtastsignale für das Bedämpfen der ersten Akkumulatorstufen der CaP-Integrationsmodule **80**. Es ist ein programmierbarer 5-Bit-Decrementer, welcher die P-Code-Chips zählt. Jedes Mal wenn der Decrementer 0 erreicht, wird ein WchipEdge-Signal erzeugt und der Decrementer wird wieder aufgeladen. Die M-Abtastsignale werden mit einer Periode von A-P-Code-Chips erzeugt, welche durch N-Abtastsignale bei einer Rate von B-P-Code-Chips gefolgt wird. Die Sequenz wird bis zu einer X1A-Epoche wiederholt, welche durch den P-Code-Generator erzeugt wird. Der Start einer neuen Sequenz kann durch S-P-Code-Chips verzögert werden.

[0100] Der Zyklusdifferenzzähler 96 ist ein 5-Bit-Zähler, welcher das Verfolgen der Verzögerung zwischen den L1- und L2-P-Codes beibehält, ausgedrückt in P-Code-Chips. In Verbindung mit der variablen Verzögerungsleitung 91, 93 leitet er eine verzögerte Version einer P-Code-Sequenz ab. Ähnlich zu dem P-Code, werden L1- und L2-W-Code-Chips-Ränder von einem einzelnen W-Rate-Generator 94 erzeugt. Das Schaltsteuergerät 96 hält das Verfolgen aufrecht, welche Sequenz L1 oder L2 der anderen nachläuft. Der Wechsel in der Phasendifferenz wird ferner indirekt durch Programmieren der Frequenz und der Phase des Codes NCO-s gesteuert, welcher den P-Code-Generator 92 treibt, welche die Taktsignale sind, welche den Zyklusdifferenzzähler und das Schaltsteuergerät 96 triggern. Wenn der L1-Code NCO (nicht gezeigt, plaziert in den CA-Code-Generatoren) einen Taktpuls herstellt, wird ein programmierbarer Zähler inkrementiert und wenn der L2-Code NCO einen Taktpuls herstellt, wird er dekrementiert. Wenn beide NCOs einen Taktpuls erzeugen, wird der Zähler ge-

hindert bzw. gesperrt. Um das unkorrekte Steuern der Verzögerungsleitung **91**, **93** zu verhindern, wird der Zyklusdifferenzzähler gesperrt, wenn er seine maximale Verzögerung von 10 erreicht.

**[0101]** Aufgrund der Vorfeldgruppenverzögerungsdifferenzen zwischen den L1- und den L2-RF-Abschnitten, kann der L2-P-Code den L1-P-Code anführen. Deshalb ist es möglich, den L1-P-Code relativ zum L2-P-Code zu verzögern, indem die L1- und L2-Eingänge und damit verbundene Ausgänge getauscht werden, wann immer die L1-L2-Verzögerung die Nulllinie kreuzt. Diese Funktionalität wird durch das Schaltsteuergerät **96** und die damit verbundenen Schalter **95**, **97** gesteuert. Das Gebrauchen der Verzögerungsleitung **91** mit nur verzögernden Zeitabläufen und des Schalters **95**, um zwischen den L1- und den L2-Signalen zu schalten, reduziert die Größe der Verzögerungsleitung **91**, verglichen zu herkömmlichen Designs bzw. Gestaltungen, was ein signifikanter Vorteil, verglichen mit dem Korrelator ist, welcher aus EP 508 621 bekannt ist.

**[0102]** Der Zyklusdifferenzzähler **96** wird auf ein IntEpoch-Abtastsignal hin programmiert. Der Wert des Zyklusdifferenzzählers **96** ist eine Messgröße, welche am Ende jedes Messintervalls gespeichert wird, d.h. zur gleichen Zeit wie die anderen Code- und Träger-Phasen-Messgröße-Register. Die L1-L2-Verzögerungsmessgröße wird durch Aufsummieren der Inhalte dieser Messgröße und der Differenz der L1- und L2-Code-NCO-Phasen-Register erhalten.

[0103] In jeder P-Code-Einheit 90 gibt es eine P-Code-Verzögerungsleitung 91 und eine W-Rate-Verzögerungsleitung 93 der Länge 10. Beide Verzögerungsleitungen 91, 93 werden durch die Chiprate der führenden Sequenzverschiebung der Bits in der Verzögerungsleitung 91, 93 getaktet, ähnlich zu einem Zuerst-Ein-Zuerst-Aus-Puffer. Dessen Eingabe ist ein P-Code-Chip für die P-Code-Verzögerungsleitung 91 und ein W-Edge für die W-Rate-Verzögerungsleitung 93. Der Ausgang ist ein Anschluß von 1 bis 10, welcher durch den Zyklus-Differenzzähler 96 gesteuert wird. Ein Zyklus-Differenzzählerwert von Null wählt den Eingang der Verzögerungsleitung 91, 93.

**[0104]** Obwohl spezielle Ausführungsformen mit Bezug auf spezielle Applikationen und Architekturen beschrieben wurden, liegen Modifikationen und Veränderungen der dargestellten Ausführungsformen innerhalb des Umfangs der Erfindung, wie sie in den angehängten Ansprüchen definiert sind.

#### **Patentansprüche**

1. Vorrichtung zum Verarbeiten von L1- und L2-Frequenzspreizsignalen, welche von mindestens einem Satelliten eines Global-Positioning-Systems empfangen werden, wobei jedes der Frequenzspreizsignale einen eigenen Frequenzträger mit einem darauf modulierten bekannten Pseudozufallscode aufweist, umfassend: einen Generator (92) zum Erzeugen einer ersten Kopie des bekannten Codes ohne eine wesentliche Verzögerung;

eine Verzögerungsleitung (91), die mit dem Generator (92) verbunden ist und die erste Kopie des bekannten Codes empfängt, wobei die Verzögerungsleitung (91) eine Mehrzahl von Anschlüssen aufweist, von denen eine verzögerte Version der bekannten Code-Kopie mit verschiedenen relativen Phasen derselben erhältlich ist:

gekennzeichnet durch

einen mit dem Generator (92) verbundenen ersten Kanal (31; 32), zum Korrelieren eines der empfangenen L1und L2-Signale mit einer ersten Kopie des bekannten Codes ohne wesentliche Verzögerung;

einen zweiten Kanal (32; 31), der wahlweise zu jedem der Anschlüsse der Verzögerungsleitung angeschlossen werden kann, um das andere der empfangenen L1- und L2-Signale mit einer zweiten verzögerten Kopie des bekannten Codes zu korrelieren; und

einen ersten Kanal (31; 32), der wahlweise zu jedem der Anschlüsse der Verzögerungsleitung angeschlossen werden kann, um das andere der empfangenen L1- und L2-Signale mit einer zweiten verzögerten Kopie des bekannten Codes zu korrelieren; und

einen Schalter (95) zum wahlweisen Schalten der Korrelation des anderen empfangenen L1- und L2-Signals mit dem zweiten Kanal (32; 31) zur ersten Kopie des bekannten Codes ohne eine wesentliche Verzögerung, und zum Schalten der Korrelation des einen empfangenen L1- und L2-Signals zur Korrelation mit dem ersten Kanal (31; 32) mit der zweiten verzögerten Kopie des bekannten Codes.

2. Vorrichtung nach Anspruch 1, wobei der bekannte Pseudozufallscode ein pseudozufälliger P-Code ist und jedes der Frequenzspreizsignale ferner durch einen unbekannten Code moduliert ist, und wobei die Vorrichtung ferner umfasst:

einen ersten Integrator zum wiederholten und separaten Integrieren des einen demodulierten L1- oder L2-Signals über Zeitspannen, die mit dem unbekannten Code in Beziehung stehen;

einen zweiten Integrator zum wiederholten und separaten Integrieren des anderen demodulierten L1- oder L2-Signals über Zeitspannen, die mit dem unbekannten Code in Beziehung stehen;

einen Korrelator zum Korrelieren eines Ergebnisses des Integrationsschrittes von jedem der zwei L1- und L2-Signalpfade mit dem integrierten Signal des jeweils anderen L1- oder L2-Signalpfads; und

einen Phasenanpasser zum Anpassen der Phasen der lokal erzeugten P-Code-Kopien bezüglich der eingehenden L1- und L2-Signale, um die Leistung der korrelierten L1- und L2-Signale zu maximieren; wobei der Korrelator umfasst: