## (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2011-54812 (P2011-54812A)

(43) 公開日 平成23年3月17日(2011.3.17)

| (51) Int.Cl. |        |           | F I        |      | テーマコード(参考) |

|--------------|--------|-----------|------------|------|------------|

| HO1L         | 29/786 | (2006.01) | HO1L 29/78 | 618B | 5 F 1 1 O  |

| HO1L         | 21/336 | (2006.01) | HO1L 29/78 | 616U |            |

|              |        |           | HO1L 29/78 | 616V |            |

|              |        |           | HO1L 29/78 | 616K |            |

|                       |                                                      | 審査請求     | 未請求 請求項の数 20 OL (全 15 頁)                        |

|-----------------------|------------------------------------------------------|----------|-------------------------------------------------|

| (21) 出願番号<br>(22) 出願日 | 特願2009-203274 (P2009-203274)<br>平成21年9月3日 (2009.9.3) | (71) 出願人 | 000005108<br>株式会社日立製作所<br>東京都千代田区丸の内一丁目6番6号     |

|                       |                                                      | (74)代理人  | 100100310<br>弁理士 井上 学                           |

|                       |                                                      | (74)代理人  | 100098660<br>弁理士 戸田 裕二                          |

|                       |                                                      | (72) 発明者 | 河村 哲史<br>東京都国分寺市東恋ケ窪一丁目280番地<br>株式会社日立製作所中央研究所内 |

|                       |                                                      | (72) 発明者 | 内山 博幸<br>東京都国分寺市東恋ケ窪一丁目280番地                    |

|                       |                                                      |          | 株式会社日立製作所中央研究所内                                 |

|                       |                                                      |          | 最終百に続く                                          |

(54) 【発明の名称】薄膜トランジスタおよびその製造方法

## (57)【要約】

【課題】 ソース・ドレイン電極の加工にドライエッチ ングを用いてトップコンタクト型TFTを形成する際の TFT特性バラツキの増大、歩留まりの低下、さらには TFTオン電流の低減を抑制することにある。

【解決手段】 薄膜トランジスタの製造方法において、 金属酸化物半導体から成る導電層上に金属酸化物半導体 から成る犠牲層を形成し、前記犠牲層上に金属膜を形成 し、前記金属膜をドライエッチングにより加工し、前記 ドライエッチングにより露出した前記犠牲層へウェット エッチングを行なう。

【選択図】 図1

#### 【特許請求の範囲】

## 【請求項1】

薄膜トランジスタの製造方法において、

金属酸化物半導体から成る導電層上に金属酸化物半導体から成る犠牲層を形成し、

前記犠牲層上に金属膜を形成し、

前記金属膜をドライエッチングにより加工し、

前記ドライエッチングにより露出した前記犠牲層へウェットエッチングを行うことを特 徴とする薄膜トランジスタの製造方法。

#### 【請求項2】

請求項1記載の製造方法において、

前記導電層のエッチングレートは、前記犠牲層のエッチングレートより低いことを特徴 とする製造方法。

#### 【請求項3】

請求項1記載の製造方法において、

前記導電層のSn濃度は、前記犠牲層のSn濃度より高いことを特徴とする製造方法。

#### 【請求項4】

請求項1記載の製造方法において、

前記導電層の緻密度は、前記犠牲層の緻密度より高いことを特徴とする製造方法。

#### 【 請 求 項 5 】

請求項3記載の製造方法において、

前記導電層は、Zn-Sn-O、In-Sn-Oの何れか一つから成り、

前記犠牲層は、In-Ga-Zn-O、Zn-O、In-Zn-O、Al-Zn-O、

Ga-Zn-O、Zn-Sn-Oの何れか一つから成ることを特徴とするの製造方法。

#### 【請求項6】

薄膜トランジスタの製造方法において、

金属酸化物半導体から成る導電層上に金属酸化物半導体から成るエッチストッパ層を形 成し、

前記エッチストッパ層上に金属酸化物半導体から成る犠牲層を形成し、

前記犠牲層上に金属膜を形成し、

前記金属膜をドライエッチングにより加工し、

前記ドライエッチングにより露出した前記犠牲層へウェットエッチングを行うことを特 徴とする薄膜トランジスタの製造方法。

#### 【請求項7】

請求項6記載の製造方法において、

前記エッチストッパ層のエッチングレートは、前記犠牲層のエッチングレートより低い ことを特徴とする製造方法。

#### 【請求項8】

請求項6記載の製造方法において、

前記エッチストッパ層のSn濃度は、前記犠牲層のSn濃度より高いことを特徴とする 製造方法。

## 【請求項9】

請求項6記載の製造方法において、

前記導電層の緻密度は、前記犠牲層の緻密度より高いことを特徴とする製造方法。

# 【請求項10】

請求項8記載の製造方法において、

前記エッチストッパ層は、Zn-Sn-O、In-Sn-Oの何れか一つから成り、 前記犠牲層は、In-Ga-Zn-O、Zn-O、In-Zn-O、Al-Zn-O、

Ga-Zn-O、Zn-Sn-Oの何れか一つから成ることを特徴とする製造方法。

# 【請求項11】

金属酸化物半導体から成る導電層上に金属酸化物半導体から成る犠牲層を形成し、

10

20

30

40

前記犠牲層上に金属膜を形成し、

前記金属膜をドライエッチングにより加工し、

前記ドライエッチングにより露出した前記犠牲層へウェットエッチングを行うことにより製造されたことを特徴とする薄膜トランジスタ。

## 【請求項12】

請求項11記載の薄膜トランジスタにおいて、

前記導電層のエッチングレートは、前記犠牲層のエッチングレートより低いことを特徴とする薄膜トランジスタ。

## 【請求項13】

請求項11記載の薄膜トランジスタにおいて、

前記導電層のSn濃度は、前記犠牲層のSn濃度より高いことを特徴とする薄膜トランジスタ。

#### 【請求項14】

請求項11記載の薄膜トランジスタにおいて、

前記導電層の緻密度は、前記犠牲層の緻密度より高いことを特徴とする薄膜トランジスタ。

#### 【請求項15】

請求項13記載の薄膜トランジスタにおいて、

前記導電層は、Zn‐Sn‐O、In‐Sn‐Oの何れか一つから成り、

前記犠牲層は、In-Ga-Zn-O、Zn-O、In-Zn-O、A1-Zn-O、Ga-Zn-O、Zn-Sn-Oの何れか一つから成ることを特徴とする薄膜トランジスタ。

#### 【請求項16】

金属酸化物半導体から成る導電層上に金属酸化物半導体から成るエッチストッパ層を形成し、

前記エッチストッパ層上に金属酸化物半導体から成る犠牲層を形成し、

前記犠牲層上に金属膜を形成し、

前記金属膜をドライエッチングにより加工し、

前記ドライエッチングにより露出した前記犠牲層へウェットエッチングを行うことにより製造されたことを特徴とする薄膜トランジスタ。

#### 【請求項17】

請求項16記載の薄膜トランジスタにおいて、

前記エッチストッパ層のエッチングレートは、前記犠牲層のエッチングレートより低い ことを特徴とする薄膜トランジスタ。

## 【請求項18】

請求項16記載の薄膜トランジスタにおいて、

前記エッチストッパ層のSn濃度は、前記犠牲層のSn濃度より高いことを特徴とする薄膜トランジスタ。

## 【請求項19】

請求項16記載の薄膜トランジスタにおいて、

前記導電層の緻密度は、前記犠牲層の緻密度より高いことを特徴とする薄膜トランジスタ。

## 【請求項20】

請求項18記載の薄膜トランジスタにおいて、

前記エッチストッパ層は、Zn-Sn-O、In-Sn-Oの何れか一つから成り、 前記犠牲層は、In-Ga-Zn-O、Zn-O、In-Zn-O、Al-Zn-O、 Ga-Zn-O、Zn-Sn-Oの何れか一つから成ることを特徴とする薄膜トランジスタ。

## 【発明の詳細な説明】

## 【技術分野】

40

30

10

20

10

20

30

40

50

#### [00001]

本発明は、半導体装置に関し、特に、金属酸化物膜をチャネル層に用いる電界効果型トランジスタを含む半導体装置に関する。

## 【背景技術】

## [0002]

薄膜トランジスタ(Thin Film Transistor 以下、この明細書では単にTFTと称する場合がある)は、ガラスなどの絶縁体基板上に形成することができ、エレクトロニクス技術において重要な役割を担うデバイスである。現在TFTのチャネル層材料としては、アモルファスシリコンまたは多結晶シリコンが最も広く使われているが、近年、これらシリコン材料を置き換えるべく、金属酸化物半導体がTFTのチャネル層材料として注目を集めている。金属酸化物半導体はチャネル層としての特性が優れていることに加え、室温付近で形成できるという特徴を有する。そのため、プラスチックフィルムなどのいわゆるフレキシブル基板上へTFTを形成する際のチャネル層材料の有力候補の一つとしても考えられている。

#### [0003]

しかしながら、酸化物半導体はプラズマや加速粒子にさらされるとダメージを受け(酸素欠損)、抵抗が下がり、ときには導体化してしまうという短所を持つ。そのため、現在産業的に広く用いられているアモルファスシリコンTFTと同様の構造のトップコンタクト型TFTを形成するには次の2つの課題を解決する必要がある。第一の課題は、酸化物半導体上にスパッタ法など、プラズマや加速粒子を生成する方法により金属の膜を形成する際に、酸化物半導体が受けるダメージを除去するというものである。第二の課題は、金属膜を加工しソース・ドレイン電極を形成する際にドライエッチングを用いたときに酸化物半導体が受けるダメージを除去するというものである。金属膜のスパッタ法による形成は、膜質や成膜速度、均一性、歩留まりに優れるため、量産性が高く産業的に広く用いられている方法である。

#### [0004]

上述の2つの課題を解決する方法は非特許文献1および2で報告されている。非特許文献1では、In-Ga-Zn-Oチャネル層中のドライエッチングによりダメージを受けた厚さ30nm程の領域をウェットエッチングにより除去している。また、非特許文献2では、In-Ga-Zn-O(高抵抗半導体)でエッチスストッパ層を形成し、ソース・ドレイン電極のドライエッチング加工の際のダメージを吸収している。

# 【先行技術文献】

## 【非特許文献】

## [0005]

【非特許文献1】Electrochemical and Solid-State Letters, 12 (4) H95-H97 (2009)

【非特許文献 2】Journal of The Electrochemical Society, 156 (3) H184-H187 (2009)

# 【発明の概要】

【発明が解決しようとする課題】

## [0006]

非特許文献1に記載の方法では、上述のように、ドライエッチングによりダメージを受けた領域をウェットエッチングにより除去している。しかしながら、この方法では制御性の低いウェットエッチングによりチャネル層の厚さを決定するため、大面積に多数のTFTを形成する場合、チャネル層の厚さのバラツキ、従ってTFT特性のバラツキが増大し、製品の歩留まりが低下するという問題がある。

## [0007]

非特許文献 2 に記載の方法では、Cu-In-Ga-Zn-Oでソース・ドレイン電極

のドライエッチング加工の際のダメージを吸収しているが、この方法ではIn-Ga-Zn-Oチャネル層とソース・ドレイン電極の間に抵抗が大きいCu-In-Ga-Zn-O層が入るため、TFTのオン電流が低減するという問題がある。

[00008]

本発明は、上述のような事情に基づいてなされたものであり、その課題は次に示す通りである。すなわち、ソース・ドレイン電極の加工にドライエッチングを用いてトップコンタクト型TFTを形成する際のTFT特性バラツキの増大、歩留まりの低下、さらにはTFTオン電流の低減を抑制することにある。

【課題を解決するための手段】

[0009]

10

20

30

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のと おりである。

[0010]

すなわち、薄膜トランジスタの製造方法において、金属酸化物半導体から成る導電層上に金属酸化物半導体から成る犠牲層を形成し、前記犠牲層上に金属膜を形成し、前記金属膜をドライエッチングにより加工し、前記ドライエッチングにより露出した前記犠牲層へウェットエッチングを行なう。

【発明の効果】

[0011]

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば次のとおりである。すなわち、ソース・ドレイン電極の加工にドライエッチングを用いてトップコンタクト型TFTを形成する際に、TFT特性バラツキの増大、さらにはTFTのオン電流低減を抑制することができる。

【図面の簡単な説明】

[ 0 0 1 2 ]

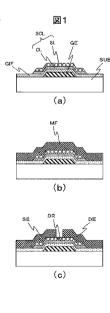

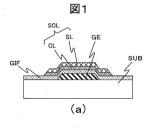

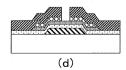

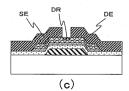

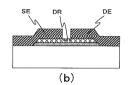

- 【図1】本発明の実施の形態1における半導体装置の構成および製造方法を示す断面図で ある。

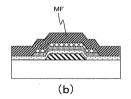

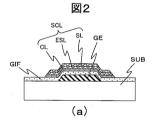

- 【図2】本発明の実施の形態2における半導体装置の構成および製造方法を示す断面図である。

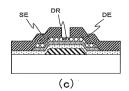

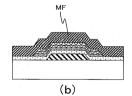

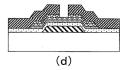

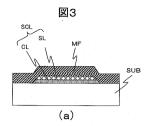

- 【図3】本発明の実施の形態3における半導体装置の構成および製造方法を示す断面図である。

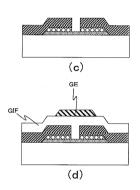

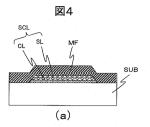

- 【図4】本発明の実施の形態4における半導体装置の構成および製造方法を示す断面図である。

- 【図5】本発明の実施の形態5における半導体装置(無線タグ)の構成を示すブロック図である。

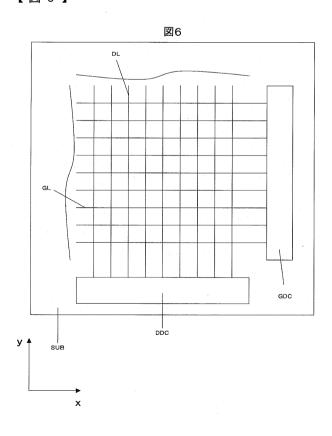

- 【図6】本発明の実施の形態6における半導体装置の構成を示す模式図である。

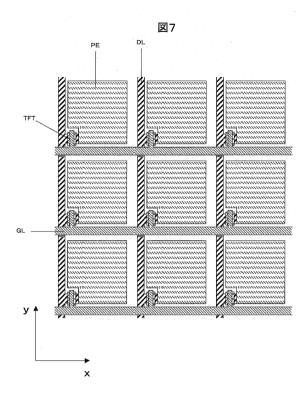

- 【 図 7 】 本 発 明 の 実 施 の 形 態 6 に お け る 半 導 体 装 置 を ア ク テ ィ ブ マ ト リ ク ス 型 液 晶 表 示 装 置 に 適 用 す る 構 成 を 示 す 模 式 図 で あ る 。

【発明を実施するための形態】

[0013]

40

50

(実施の形態1)

図1は、本実施の形態1における半導体装置の構成および製造方法を示す図である。半導体装置としていわゆるボトムゲート / トップコンタクト型酸化物TFTを挙げている。ここでいうボトムゲートとは、半導体層SCLよりも下層にゲート電極GEが形成されている構造のことであり、トップコンタクトとは、半導体層SCLよりも上層にソース電極SEおよびドレイン電極DEが形成されている構造のことを示している。

[0014]

本実施の形態1における半導体装置の製造方法は以下の通りである。まず、図1(a)に示すように、絶縁体基板SUB上にゲート電極GE、ゲート絶縁膜GIFF、導電層CL、犠牲層SLが形成される。

#### [0015]

基板SUBは、例えば、ガラス、石英、プラスチックフィルムなどからなり、必要に応じてゲート電極GEが形成される側の表面に絶縁膜のコーティングがなされている。

## [0016]

ゲート電極GEは、導電性の材料、例えば、モリブデン、クロム、タングステン、アルミ、銅、チタン、ニッケル、タンタル、銀、亜鉛、あるいはその他の金属の単膜、それらの合金膜、それらの積層膜、あるいはITO(In-Sn-O:インジウム錫酸化物)などの金属酸化物導電膜、それらと金属との積層膜、窒化チタン(Ti-N)などの金属窒化物導電膜、それらと金属との積層膜、室化チタン(Ti-N)などの金属窒化物導電膜、それらと金属との積層膜、その他の導電性金属化合物膜、それらと金属との積層膜、キャリアを高濃度に含む半導体、あるいは半導体と金属との積層膜からなり、その成膜はCVD法やスパッタ法などにより行ない、加工は一般的なフォトリソグラフィー技術とドライエッチング、あるいはウェットエッチングとの組み合わせにより行なう。

# [0017]

ゲート絶縁膜GIFFは、Si-O、A1-Oなどの酸化物絶縁膜を用いるのが好ましいが、Si-Nなど酸化物以外の無機絶縁膜、パリレンなどの有機絶縁膜を用いても良い。ゲート絶縁膜GIFFの成膜は、CVD法やスパッタ法、塗布法などにより行なう。

#### [0018]

導電層 C L 、犠牲層 S L は、 Z n - O、 I n - O、 G a - O、 S n - O、 I n - G a - Z n - O、 Z n - S n - O、 I n - S n - O、 I n - Z n - O、 G a - Z n - O、 I n - G a - Z n - O、 I n - G a - Z n - O、 I n - G a - Z n - O、 I n - G a - Z n - O、 I n - G a - Z n - O、 I n - G a - Z n - O、 I n - G a - Z n - O、 I n - G a - Z n - O、 I n - G a - Z n - O、 I n - G a - Z n - O、 I n - G a - Z n - O、 I n - G a - Z n - O、 I n - G a - Z n - O、 I n - G a - Z n - O、 I n - G a - Z n - O、 I n - G a - Z n - O、 I n - G a - Z n - O、 I n - G a - Z n - O、 I n - G a - Z n - O、 I n - G a - Z n - O、 I n - G a - Z n - O、 I n - G a - Z n - O、 I n - G a - Z n - O、 I n - G a - Z n - O、 I n - G a - Z n - O、 I n - G a - Z n - O、 I n - G a - Z n - O、 I n - G a - Z n - O、 I n - G a - Z n - O、 I n - G a - Z n - O、 I n - G a - Z n - O、 I n - G a - Z n - O、 I n - G a - Z n - O、 I n - G a - Z n - O、 I n - G a - Z n - O、 I n - G a - Z n - O、 I n - G a - Z n - O、 I n - G a - Z n - O、 I n - G a - Z n - O、 I n - G n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n 表 U n - G n A - G n A - G n A - G n A - G n A - G n A - G n A - G n A - G n A - G n A - G n A - G n A - G n A - G n A - G n A - G n A - G n A - G n A - G n A - G n A - G n A - G n A - G n A - G n

# [0019]

導電層 C L 、犠牲層 S L の組み合わせとしては上述の材料の中から種々の組み合わせが考えられる。中でも、例えば導電層 C L が Z n - S n - O、 I n - S n - Oの何れか一つから成り、犠牲層 S L が I n - G a - Z n - O、 Z n - O、 I n - Z n - O、 A 1 - Z n - O、 G a - Z n - O、 Z n - S n - Oの何れか一つから成るような組み合わせが好ましい。

## [0020]

導電層CL内のSn濃度を犠牲層SLよりも高くする方法としては、導電層CLを成膜する際の原材料中のSn濃度を犠牲層SLを成膜する際の原材料よりも高くする方法をとる。例えば、両層をスパッタ法やPLD法により形成する場合、導電層CL用のターゲット中のSn濃度を犠牲層SL用のターゲットよりも高くしたり、導電層CLの成膜の際のみSnターゲットを同時に置いたりする。また、導電層CLの緻密度を犠牲層SLよりも高くする方法としては、導電層CLの成膜レートを犠牲層SLよりも小さくする、導電層CLの成膜温度を犠牲層SLよりも低くするなどの方法をとる。

# [0021]

その後、図1(b)に示すように、犠牲層SLの上に金属膜MFを形成する。金属膜MFは、例えば、モリブデン、クロム、タングステン、アルミ、銅、チタン、ニッケル、タンタル、銀、亜鉛、あるいはその他の金属の単膜、それらの合金膜、それらの積層膜、あるいはITO(In-Sn-O:インジウム錫酸化物)などの金属酸化物導電膜、それらと金属との積層膜、窒化チタン(Ti-N)などの金属窒化物導電膜、それらと金属との積層膜、その他の導電性金属化合物膜、それらと金属との積層膜、キャリアを高濃度に含

10

20

30

40

10

20

30

40

50

む半導体、あるいは半導体と金属との積層膜によって形成される。

## [0022]

その後、図1(c)に示すように、金属膜MFを一般的なフォトリソグラフィー技術とドライエッチングの組み合わせによりソース電極SE、ドレイン電極DEの形状に加工する。その際、ソース電極SE・ドレイン電極DE間の開口部の下の犠牲層SLがプラズマおよび加速粒子にさらされるため、ダメージ領域DRが形成される。

#### [0023]

その後、図1(d)に示すように、ダメージ領域DRを無機酸、あるいは有機酸からなるエッチング液を用いたウェットエッチングにより除去する。このとき、導電層CLのほうが犠牲層SLよりもエッチレートが小さいため、ウェットエッチングは導電層CLの表面で自動的に停止し、実質的にウェットエッチングによる導電層CLの膜厚の減少はない。ここで、ドライエッチングではなく、ウェットエッチングを用いている理由は、ドライエッチングの際に導電層CLがプラズマや加速粒子にさらされ、ダメージを受けることを回避するためである。

#### [0024]

本実施の形態1によれば、制御性の低いウェットエッチングによってダメージ領域DRを除去しても実質的に導電層CLのオーバーエッチによる膜厚の減少がないため、TFTのチャネル層(本実施の形態1では導電層CL)の厚さのバラツキを抑制することができる。すなわち、TFTの特性バラツキの増大、TFTの歩留まりの低下を抑制することができる。また、ソース電極SEおよびドレイン電極DEとチャネル層(導電層CL)の間に挟まれるドライエッチダメージ吸収層(本発明では犠牲層SL)がCu-In-Ga-Zn-Oのような高抵抗半導体ではないため、TFTのオン電流の低減を抑制することができる。

#### (実施の形態2)

図2は、本実施の形態2における半導体装置の構成および製造方法を示す図である。実施の形態1との違いは半導体層SCLが3層からなる点であり、それ以外の点は実施の形態1と同一である。実施の形態1では、導電層CLのエッチレートを犠牲層SLよりも低くすることで、犠牲層SLのウェットエッチング除去の際に導電層CLの表面でウェットエッチングが自動的に停止したが、本実施の形態2では、エッチング停止機能を導電層CLと犠牲層SLの間に形成するエッチストッパ層ESLに担わせる。すなわち、エッチストッパ層ESLの表面でウェットエッチングが自動的に停止する。

# [0025]

# [0026]

エッチストッパ層 E S L 、犠牲層 S L の組み合わせとしては上述の材料の中から種々の組み合わせが考えられる。中でも、例えばエッチストッパ層 E S L が Z n - S n - O 、 I n - S n - O の何れか一つから成り、犠牲層 S L が I n - G a - Z n - O 、 Z n - O 、 I n - Z n - O 、 A 1 - Z n - O 、 G a - Z n - O 、 Z n - S n - O の何れか一つから成る

ような組み合わせが好ましい。

## [0027]

エッチストッパ層ESL内のSn濃度を犠牲層SLよりも高くする方法としては、エッチストッパ層ESLを成膜する際の原材料中のSn濃度を犠牲層SLを成膜する際の原材料よりも高くする方法をとる。例えば、両層をスパッタ法やPLD法により形成する場合、エッチストッパ層ESL用のターゲット中のSn濃度を犠牲層SL用のターゲットよりも高くしたり、エッチストッパ層ESLの成膜の際のみSnターゲットを同時に置いたりする。また、エッチストッパ層ESLの緻密度を犠牲層SLよりも高くする方法としては、エッチストッパ層ESLの成膜レートを犠牲層SLよりも小さくする、エッチストッパ層ESLの成膜レートを、サートを

[0028]

本実施の形態2によれば、実施の形態1と同様に、制御性の低いウェットエッチングによってダメージ領域DRを除去しても実質的にエッチストッパ層ESLのオーバーエッチによる膜厚の減少がないため、TFTのチャネル層(本実施の形態2では導電層CL+エッチストッパ層ESL)の厚さのバラツキを抑制することができる。すなわち、TFTの特性バラツキの増大、TFTの歩留まりの低下を抑制することができる。また、ソースで種SEおよびドレイン電極DEとチャネル層(導電層CL+エッチストッパ層ESL)の間に挟まれるドライエッチダメージ吸収層(本発明では犠牲層SL)がCu-In-Ga-Zn-Oのような高抵抗半導体ではないため、TFTのオン電流の低減を抑制することができる。加えて、導電性能の主要部分を導電層CLにより決定することができ、エッチング停止性能をエッチトップ層ESLにより決定することができる。これにより、TFTのチャネルの導電性と加工性を独立に制御することが可能になり、実施の形態1に比べて用いる材料の選択肢が増える。

(実施の形態3)

図3は、本実施の形態3における半導体装置の構成および製造方法を示す図である。半導体装置としていわゆるトップゲート / トップコンタクト型酸化物 T F T を挙げている。ここでいうトップゲートとは、半導体層 S C L よりも上層にゲート電極 G E が形成されている構造のことであり、トップコンタクトとは、半導体層 S C L よりも上層にソース電極 S E およびドレイン電極 D E が形成されている構造のことを示している。

[ 0 0 2 9 ]

本実施の形態3における半導体装置の製造方法は以下の通りである。まず、図3(a)に示すように、絶縁体基板SUB上に導電層CL、犠牲層SL、金属膜MFが形成される

[0030]

基板SUBは、例えば、ガラス、石英、プラスチックフィルムなどからなり、必要に応じて導電層CL、犠牲層SLからなる半導体層SCLが形成される側の表面に絶縁膜のコーティングがなされている。

[0031]

10

20

30

40

#### [0032]

導電層 C L 、犠牲層 S L の組み合わせとしては上述の材料の中から種々の組み合わせが考えられる。中でも、例えば導電層 C L が Z n - S n - O、 I n - S n - Oの何れか一つから成り、犠牲層 S L が I n - G a - Z n - O、 Z n - O、 I n - Z n - O、 A 1 - Z n - O、 G a - Z n - O、 Z n - S n - Oの何れか一つから成るような組み合わせが好ましい。

#### [0033]

導電層CL内のSn濃度を犠牲層SLよりも高くする方法としては、導電層CLを成膜する際の原材料中のSn濃度を犠牲層SLを成膜する際の原材料よりも高くする方法をとる。例えば、両層をスパッタ法やPLD法により形成する場合、導電層CL用のターゲット中のSn濃度を犠牲層SL用のターゲットよりも高くしたり、導電層CLの成膜の際のみSnターゲットを同時に置いたりする。また、導電層CLの緻密度を犠牲層SLよりも高くする方法としては、導電層CLの成膜レートを犠牲層SLよりも小さくする、導電層CLの成膜温度を犠牲層SLよりも低くするなどの方法をとる。

#### [0034]

金属膜MFは、例えば、モリブデン、クロム、タングステン、アルミ、銅、チタン、ニッケル、タンタル、銀、亜鉛、あるいはその他の金属の単膜、それらの合金膜、それらの積層膜、あるいはITO(In-Sn-O:インジウム錫酸化物)などの金属酸化物導電膜、それらと金属との積層膜、窒化チタン(Ti-N)などの金属窒化物導電膜、それらと金属との積層膜、キャリアを高濃度に含む半導体、あるいは半導体と金属との積層膜によって形成される。

#### [0035]

その後、図3(b)に示すように、金属膜MFを一般的なフォトリソグラフィー技術とドライエッチングの組み合わせによりソース電極SE、ドレイン電極DEの形状に加工する。その際、ソース電極SE・ドレイン電極DE間の開口部の下の犠牲層SLがプラズマおよび加速粒子にさらされるため、ダメージ領域DRが形成される。

## [0036]

その後、図3(c)に示すように、ダメージ領域DRを無機酸、あるいは有機酸からなるエッチング液を用いたウェットエッチングにより除去する。このとき、導電層CLのほうが犠牲層SLよりもエッチレートが低いため、ウェットエッチングは導電層CLの表面で自動的に停止し、実質的にウェットエッチングによる導電層CLの膜厚の減少はない。ここで、ドライエッチングではなく、ウェットエッチングを用いている理由は、ドライエッチングの際に導電層CLがプラズマや加速粒子にさらされ、ダメージを受けることを回避するためである。

## [ 0 0 3 7 ]

その後、図3(d)に示すように、半導体層SCL、ソース電極SE、ドレイン電極DEを被覆する形でゲート絶縁膜GIFを形成し、その上にゲート電極GEを形成する。

#### [0038]

ゲート絶縁膜GIFは、Si-O、A1-Oなどの酸化物絶縁膜を用いるのが好ましいが、Si-Nなど酸化物以外の無機絶縁膜、パリレンなどの有機絶縁膜を用いても良い。 ゲート絶縁膜GIFの成膜は、CVD法やスパッタ法、塗布法などにより行なう。

#### [0039]

ゲート電極GEは、導電性の材料、例えば、モリブデン、クロム、タングステン、アルミ、銅、チタン、ニッケル、タンタル、銀、亜鉛、あるいはその他の金属の単膜、それらの合金膜、それらの積層膜、あるいはITO(In-Sn-O:インジウム錫酸化物)などの金属酸化物導電膜、それらと金属との積層膜、窒化チタン(Ti-N)などの金属窒化物導電膜、それらと金属との積層膜、全の他の導電性金属化合物膜、それらと金属との積層膜、キャリアを高濃度に含む半導体、あるいは半導体と金属との積層膜からなり、その成膜はCVD法やスパッタ法などにより行ない、加工は一般的なフォトリソグラフィー技術とドライエッチング、あるいはウェットエッチングとの組み合わせにより行なう。

10

20

30

40

10

20

30

40

50

#### [0040]

本実施の形態3によれば、制御性の低いウェットエッチングによってダメージ領域DRを除去しても実質的に導電層CLのオーバーエッチによる膜厚の減少がないため、TFTのチャネル層(本実施の形態3では導電層CL)の厚さのバラツキを抑制することができる。すなわち、TFTの特性バラツキの増大、TFTの歩留まりの低下を抑制することができる。また、ソース電極SEおよびドレイン電極DEとチャネル層(導電層CL)の間に挟まれるドライエッチダメージ吸収層(本発明では犠牲層SL)がCu・In・Ga・Zn・Oのような高抵抗半導体ではないため、TFTのオン電流の低減を抑制することができる。

## (実施の形態4)

図4は、本実施の形態4における半導体装置の構成および製造方法を示す図である。実施の形態3との違いは半導体層SCLが3層からなる点であり、それ以外の点は実施の形態3と同一である。実施の形態3では、導電層CLのエッチレートを犠牲層SLよりも低くすることで、犠牲層SLのウェットエッチング除去の際に導電層CLの表面でウェットエッチングが自動的に停止したが、本実施の形態2では、エッチング停止機能を導電層CLと犠牲層SLの間に形成するエッチストッパ層ESLに担わせる。すなわち、エッチストッパ層ESLの表面でウェットエッチングが自動的に停止する。

#### [0041]

導電層CL、エッチストッパ層ESL、犠牲層SLはZn-O、In-O、Ga-O、Sn-O、In-Ga-Zn-O、Zn-Sn-O、In-Sn-O、In-Zn-O、Ga-O、Sn-O、In-Ga-Zn-O、In-Sn-O、In-Zn-O、Ga-O、Sn-O、In-Ga、Snの酸化物、Bn-O、In-Ga、Snの酸化物、およびそれらの複合酸化物によって形成されており、それらの成膜は、スパッタ法、PLD法、CVD法、塗布法、印刷法などにより行なう。導電層CL、エッチストッパ層ESLの厚さは30nm以上が望ましい、導電層CL、エッチストッパ層ESLの厚さは30nm以上が望ましいは、は、導電層CL、エッチストッパ層ESLの素子分離のための島状加工はの設めなフォトリソグラフィー技術とウェットエッチング、あるいはドライエッチングのみ合わせにより行なう。さらに、無機酸、あるいは有機酸からなるウェットエッチングが、よりも高くするためには、たとえばエッチストッパ層ESLの図を犠牲層SLよりも高くするなどの方法をとる。

# [0042]

エッチストッパ層ESL、犠牲層SLの組み合わせとしては上述の材料の中から種々の組み合わせが考えられる。中でも、例えばエッチストッパ層ESLがZn-Sn-O、In-Sn-Oの何れか一つから成り、犠牲層SLがIn-Ga-Zn-O、Zn-O、In-Zn-O、Al-Zn-O、Ga-Zn-O、Zn-Sn-Oの何れか一つから成るような組み合わせが好ましい。

#### [0043]

エッチストッパ層 E S L 内の S n 濃度を犠牲層 S L よりも高くする方法としては、エッチストッパ層 E S L を成膜する際の原材料中の S n 濃度を犠牲層 S L を成膜する際の原材料よりも高くする方法をとる。例えば、両層をスパッタ法や P L D 法により形成する場合、エッチストッパ層 E S L 用のターゲット中の S n 濃度を犠牲層 S L 用のターゲットよりも高くしたり、エッチストッパ層 E S L の成膜の際のみ S n ターゲットを同時に置いたりする。また、エッチストッパ層 E S L の緻密度を犠牲層 S L よりも高くする方法としては、エッチストッパ層 E S L の成膜レートを犠牲層 S L よりも小さくする、エッチストッパ層 E S L の成膜温度を犠牲層 S L よりも低くするなどの方法をとる。

#### [0044]

本実施の形態4によれば、実施の形態1と同様に、制御性の低いウェットエッチングによってダメージ領域DRを除去しても実質的にエッチストッパ層ESLのオーバーエッチによる膜厚の減少がないため、TFTのチャネル層(本実施の形態4では導電層CL+エ

ッチストッパ層ESL)の厚さのバラツキを抑制することができる。すなわち、TFTの特性バラツキの増大、TFTの歩留まりの低下を抑制することができる。また、ソース電極SEおよびドレイン電極DEとチャネル層(導電層CL+エッチストッパ層ESL)の間に挟まれるドライエッチダメージ吸収層(本発明では犠牲層SL)がCu-In-Ga-Zn-Oのような高抵抗半導体ではないため、TFTのオン電流の低減を抑制することができる。加えて、導電性能の主要部分を導電層CLにより決定することができ、エッチング停止性能をエッチトップ層ESLにより決定することができる。これにより、TFTのチャネルの導電性と加工性を独立に制御することが可能になり、実施の形態3に比べて用いる材料の選択肢が増える。

## (実施の形態5)

図 5 は本実施の形態 5 における半導体装置の構成を示す図である。実施の形態 1 ~ 4 に示す構造のTFTを用いてアンテナ共振回路AR、整流器RCT、変調器MOD、デジタル回路DGCなどを構成し、無線タグを形成している。無線タグはリーダRDまたはライタWRと無線で通信を行うことができるようになっている。

#### (実施の形態6)

図6は本実施の形態6における半導体装置の構成を示す図である。本実施の形態6では、前記実施の形態1~4の構造を有するTFTを構成要素とする素子が基板SUB上にアレイ状に配置されている。前記実施の形態1~4に示すTFTを、アレイ内の各素子のスイッチングや駆動用のトランジスタに用いることはもちろん、このTFTのゲート電極GEと接続されるゲート線GLに信号を送るゲート線駆動回路GDCや、このTFTのソース電極SEあるいはドレイン電極DEと接続されるデータ線DLに信号を送るデータ線駆動回路DDCを構成するトランジスタに用いてもよい。この場合、各素子のTFTとゲート線駆動回路GDCあるいはデータ線駆動回路DDC内のTFTを並行して形成することができる。

#### [0045]

アクティブマトリクス型液晶表示装置に上述したアレイを適用する場合、各素子は、例えば、図7に示すような構成になる。図中×方向に延在するゲート線GLに走査信号が供給されると、TFTがオンし、このオンされたTFTを通して、図中y方向に延在するデータ線DLからの映像信号が画素電極PEに供給される。なお、ゲート線GLは図中ッ方向に並設され、データ線DLは図中×方向に並設され、隣接する一対のゲート線GLと隣接する一対のドレイン線DLで囲まれる領域(画素領域)に画素電極PEが配置されている。この場合、例えば、データ線DLがソース電極SEと電気的に接続され、画素電極PEがドレイン電極DEと電気的に接続される。あるいは、データ線DLがソース電極SEを兼ねてもよい。また、液晶表示装置に限らず有機EL表示装置などに上述したアレイを適用してもよい。この場合、画素回路を構成するトランジスタにTFTを適用してもよい

#### [0046]

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能である。

#### 【産業上の利用可能性】

## [0047]

本発明における半導体装置は、無線タグ、記憶素子アレイなどを構成するトランジスタや周辺回路などに適用できる。また、透過型、反射型、半透過型の各液晶表示装置、並びに有機 EL表示装置などの各画素を駆動するトランジスタや周辺回路などにも適用できる

## 【符号の説明】

#### [0048]

AR アンテナ共振回路

10

20

30

C L 導電層

DDC データ線駆動回路

DE ドレイン電極

DGC デジタル回路

D L データ線

DR ダメージ領域

ESL エッチストッパ層

GDC ゲート線駆動回路

GE ゲート電極

GIF ゲート絶縁膜

G L ゲート線

M F 金属膜

MOD 変調器

PE 画素電極

RCT 整流器

RD リーダ

S C L 半導体層

SE ソース電極

S L 犠牲層

S U B 基板

TFT 酸化物TFT

WR ライタ

# 【図1】

# 【図2】

10

【図3】

【図5】

図5

【図4】

【図6】

# 【図7】

## フロントページの続き

(72)発明者 若菜 裕紀

東京都国分寺市東恋ケ窪一丁目280番地 株式会社日立製作所中央研究所内

(72)発明者 波多野 睦子

東京都国分寺市東恋ケ窪一丁目280番地 株式会社日立製作所中央研究所内

F ターム(参考) 5F110 AA03 AA07 BB01 CC07 DD01 DD02 DD03 DD11 EE01 EE02

EE03 EE04 EE07 EE14 EE44 EE45 FF01 FF02 FF03 FF27

FF28 FF29 GG01 GG25 GG42 GG43 GG44 HK01 HK02 HK04

HK07 HK08 HK21 HK32 HK33 HK34 NN72 QQ03