# (19) 대한민국특허청(KR)

## (12) 등록특허공보(B1)

(51) Int. Cl.

H01L 27/115 (2006.01) G11C 16/34 (2006.01)

(21) 출원번호 10-2005-7013970

(22) 출원일자(국제출원일자) **2003년12월18일** 심사청구일자 **2008년11월06일**

(85) 번역문제출일자 2005년07월28일

(65) 공개번호 10-2005-0116796

(43) 공개일자 2005년12월13일

(86) 국제출원번호 PCT/US2003/040361

(87) 국제공개번호 **WO 2004/070731** 국제공개일자 **2004년08월19일**

(30) 우선권주장

10/353,574 2003년01월28일 미국(US)

(56) 선행기술조사문헌

US06028794 A1

JP10320984 A

JP2001043143 A

JP11224491 A

전체 청구항 수 : 총 24 항

(45) 공고일자 2011년12월05일

(11) 등록번호 10-1089575

(24) 등록일자 2011년11월29일

(73) 특허권자

#### 가부시끼가이샤 도시바

일본국 도꾜도 미나또꾸 시바우라 1쪼메 1방 1고

#### 쌘디스크 코포레이션

미합중국, 캘리포니아주 95035, 밀피타스, 맥카시 볼레바드 601

(72) 발명자

## 천, 지안

미국, 캘리포니아 95129, 산 호세, 캐슬 글렌 애 비뉴 5476

#### 다나까, 도모하루

일본국, 도쿄, 요꼬하마, 고우난-쿠, 오쿠보 2-13-21-10

(74) 대리인

송범엽, 박경재

심사관 : 김기환

## (54) 사이클 카운트를 저장하는 대량 소거 블록들을 구비한비휘발성 반도체 메모리

#### (57) 요 약

복수 페이지들의 사용자 데이터가 각 블록에 저장되는 것으로 개별적으로 소거가능한 다수 블록들의 메모리 셀들로 분할되는 플래시 EEPROM 시스템에서, 각 블록에 가능한 소거 사이클 수의 카운트는 단지 한 페이지의 예비 셀들과 같은 블록 내에 한 위치에 저장되거나 복수 페이지들의 헤더 영역들 중에 분산된다. 블록 사이클 카운트를 포함한 페이지 혹은 페이지들은 초기에는 소거되고 있는 각 블록으로부터 위혀지고, 사이클 카운트는 일시적으로 저장되고, 소거된 블록 및 갱신된 사이클 카운트는 블록 위치에 다시 기입된다. 사용자 데이터는 필요시 블록의 개개의 페이지들에 프로그램된다. 사용자 데이터는 메모리 셀 저장요소당 2이상의 상태들로 저장되는 것이 바람 직하고, 이 경우 사이클 카운트는 소거 프로세스를 가속시키고 갱신된 사이클 카운트를 기입에 의해 야기될 수 있는 소거된 상태에의 교란 영향을 감소시키도록 2진으로 저장될 수 있다. 사이클 카운트로부터 계산된 오류 정정코드는 그와 함께 저장될 수 있으므로 저장된 사이클 카운트가 유효하게 될 수 있다.

## 대 표 도 - 도9

#### 특허청구의 범위

#### 청구항 1

삭제

#### 청구항 2

단위로서 함께 소거가 가능하고 복수 페이지들의 사용자 데이터를 개별적으로 저장하는 다수 블록들의 셀들로 구성된 메모리 셀 어레이를 구비하는 비휘발성 메모리를 동작시키는 방법에 있어서,

- (a) 오버헤드 데이터가 저장되는 블록의 동작에 관계된 정보의 개개의 블록들 내에, 해당 블록의 상기 오버헤드 데이터를 저장하는 단계;

- (b) 소거를 위해 하나 이상의 블록들을 어드레싱하고,

상기 하나 이상의 블록들로부터 상기 오버헤드 데이터를 독출하여 상기 독출된 오버헤드 데이터를 일시 저장하고,

상기 하나 이상의 블록들 내의 상기 메모리 셀들을 소거하고,

상기 독출된 오버헤드 데이터를 갱신하고,

상기 갱신된 오버헤드 데이터를 상기 하나 이상의 블록들 각각에 프로그램하여 상기 하나 이상의 블록 내의 페이지들을 이에 사용자 데이터를 프로그래밍하는데 사용될 수 있게 하는 단계를 포함하는, 소거 동작 단계;

(c) 그후에 사용자 데이터를 상기 하나 이상의 블록들의 페이지들에 프로그램하는 단계를 포함하고,

하나의 페이지는 사용자 데이터, 상기 사용자 데이터에 관계된 페이지 오버헤드 데이터, 및 상기 사용자 데이터 및 상기 페이지 오버헤드 데이터와 상이한 예비 셀로 구성되고,

상기 갱신된 오버헤드 데이터는 상기 하나 이상의 블록들 각각의 단일 페이지의 예비 셀들에 프로그램되는, 비휘발성 메모리 동작방법.

#### 청구항 3

삭제

#### 청구항 4

삭제

#### 청구항 5

삭제

#### 청구항 6

제2항에 있어서, 상기 개개의 블록들에 저장된 상기 오버헤드 데이터는 량을 포함하는 블록이 받은 소거 동작들의 횟수를 나타내는 량을 포함하고, 상기 오버헤드 데이터를 갱신하는 것은 현 소거 동작을 포함하도록 상기 소거 동작들을 갱신하는 것을 포함하는, 비휘발성 메모리 동작방법.

#### 청구항 7

삭제

### 청구항 8

제2항에 있어서, 상기 개개의 블록들 내에 저장된 상기 오버헤드 데이터로부터 용장성 코드를 계산하는 단계를 더 포함하고, 계산을 행하게 된 오버헤드 데이터를 포함하는 개개의 블록들 내에 용장성 코드를 저장하는 단계를 더 포함하는, 비휘발성 메모리 동작방법.

## 청구항 9

제8항에 있어서, 상기 오버헤드 데이터를 독출하는 단계는 오버헤드 데이터로부터 계산되고 이와 함께 저장된 용장성 코드를 독출하고, 상기 독출된 용장성 코드에 대해 상기 독출된 오버헤드 데이터를 체크하는 것을 포함 하며, 상기 갱신된 오버헤드 데이터를 프로그램하는 단계는 상기 갱신된 오버헤드 데이터로부터 용장성 코드를 계산하고 상기 계산된 용장성 코드를 동일 블록에 오버헤드 데이터로서 저장하는 것을 포함하는, 비휘발성 메모 리 동작방법.

#### 청구항 10

제9항에 있어서, 독출된 오버헤드 데이터를 독출된 용장성 코드에 대해 체크하는 것에서 오버헤드 데이터가 무효한 것으로 나타나면, 독출된 오버헤드 데이터 및 용장성 코드가 있는 블록을 이를 소거하는 대신 사용불가로서 마크하거나, 오버헤드 데이터를 갱신하거나, 갱신된 오버헤드 혹은 사용자 데이터로 블록을 프로그램하는 것인, 비휘발성 메모리 동작방법.

#### 청구항 11

제10항에 있어서, 상기 사용불가 블록 내에 상기 오버헤드 데이터의 일부로서 플래그를 셋 함으로써 상기 사용불가 블록을 무효한 것으로서 마크하는 단계를 더 포함하는, 비휘발성 메모리 동작방법.

#### 청구항 12

제2항에 있어서, 상기 오버헤드 데이터를 갱신하거나 상기 갱신된 오버헤드 데이터를 다시 상기 하나 이상의 블록들에 프로그램하기 전에 상기 오버헤드 데이터가 손실된 경우, 사용자 데이터를 상기 하나 이상의 블록들의 페이지들에 프로그램하는 대신 상기 하나 이상의 블록들을 사용불가로서 마크하는, 비휘발성 메모리 동작방법.

#### 청구항 13

제2항에 있어서, 사용자 데이터를 프로그램하는 것은 2이상의 상태들 중 하나로 개개의 메모리 셀 저장요소들을 프로그램하여 저장요소당 1비트 이상의 사용자 데이터를 저장하는 단계를 포함하는, 비휘발성 메모리 동작방법.

#### 청구항 14

제13항에 있어서, 상기 갱신된 오버헤드 데이터를 프로그램하는 단계는 개개의 메모리 셀 저장요소들을 정확히 두 저장상태들 중 한 상태로 프로그램하여 저장요소당 1비트의 오버헤드 데이터를 저장하는 것을 포함하는, 비휘발성 메모리 동작방법.

### 청구항 15

제14항에 있어서, 상기 메모리 셀들을 소거하는 단계는, 메모리 셀 저장요소들의 전하를 제1 범위로 구동하는 것을 포함하며, 상기 오버헤드 데이터를 프로그램하는 단계는 상기 메모리 셀 저장요소의 부분을 상기 오버헤드 데이터에 따라 제2 범위로 구동하는 것을 포함하며, 사용자 데이터를 프로그램하는 단계는 상기 제2 범위보다 상기 제1 범위로부터 더욱 제거되는 적어도 제3 및 제4 전하 범위들로 개개의 메모리 셀 저장요소들을 프로그램하는 것을 포함하는, 비휘발성 메모리 동작방법.

#### 청구항 16

제14항에 있어서, 상기 사용자 데이터를 프로그램하는 단계는 원하는 프로그램된 상태들에 도달될 때까지 셀들의 상태들의 검증에 의해 분리된 연속한 프로그래밍 펄스들을 인가하는 것을 포함하며, 개개의 펄스들은 제1 량만큼 크기가 증가하며, 상기 오버헤드 데이터를 프로그램하는 단계는 원하는 프로그램된 상태들에 도달될 때까지 셀들의 상태의 검증에 의해 분리된 연속한 프로그래밍 펄스들을 인가하는 것을 포함하며, 개개의 펄스들은 상기 제1 량보다 큰 제2 량만큼 크기가 증가하며, 그럼으로써 상기 사용자 데이터보다 빠르게 상기 오버헤드 데이터를 프로그램하는 것인, 비휘발성 메모리 동작방법.

#### 청구항 17

제15항에 있어서, 상기 메모리 셀 어레이는 NAND 어레이인, 비휘발성 메모리 동작방법.

### 청구항 18

제2항에 있어서, 상기 메모리 셀 어레이는 NAND 어레이인, 비휘발성 메모리 동작방법.

#### 청구항 19

제1 임계범위로 단위로서 함께 소거가 가능하고 상기 제1 임계범위에서 그리고 상기 제1 임계범위보다 연속적으로 큰 적어도 제2, 제3 및 제4 임계범위들에서 복수 페이지들의 사용자 데이터를 개별적으로 저장하는 다수 블록들의 셀들로 구성된 메모리 셀 어레이를 구비하는 비휘발성 메모리를 동작시키는 방법에 있어서,

- (a) 상기 블록들이 사이클된 횟수 데이터를 저장하는 단계로서, 상기 사이클 데이터는 상기 사이클 데이터가 관계된 블록들의 소정 수의 메모리 셀들 내에 저장되는, 단계;

- (b) 소거를 위해 하나 이상의 블록들을 어드레싱하고,

상기 하나 이상의 블록들 각각으로부터 상기 사이클 데이터를 독출하여 상기 독출된 사이클 데이터를 일시 저장하고,

상기 하나 이상의 블록들 내의 상기 메모리 셀들을 소거하고,

상기 독출된 사이클 데이터를 갱신하고,

상기 제3 혹은 제4 임계범위를 사용하지 않고, 상기 제1 임계범위에서 상기 제2 임계범위로 소정 수의 셀들의 적어도 일부의 임계레벨들을 구동함으로써 상기 갱신된 독출된 사이클 데이터를 상기 하나 이상의 블록들 각각에 프로그램하여 상기 하나 이상의 블록 내의 페이지들을 이에 사용자 데이터를 프로그래밍하는데 사용될 수 있게 하는 단계를 포함하는, 소거 동작 단계;

(c) 그후에 적어도 상기 제1, 제2, 제3, 및 제4 임계범위들을 사용함으로써 사용자 데이터를 상기 하나 이상의 블록들의 페이지들에 프로그램하는 단계를 포함하고,

하나의 페이지는 사용자 데이터, 상기 사용자 데이터에 관계된 페이지 오버헤드 데이터, 및 상기 사용자 데이터 및 상기 페이지 오버헤드 데이터와 상이한 예비 셀로 구성되고,

상기 갱신된 사이클 데이터는 상기 하나 이상의 블록들 각각의 단일 페이지의 예비 셀들에 프로그램되는, 비휘 발성 메모리 동작방법.

#### 청구항 20

삭제

#### 청구항 21

제19항에 있어서, 상기 사이클 데이터로부터 계산된 용장성 코드는 상기 사이클 데이터와 함께 한 블록에 저장되는, 비휘발성 메모리 동작방법.

#### 청구항 22

제19항에 있어서, 상기 사이클 데이터를 독출하는 단계는 상기 사이클 데이터로부터 계산되고 이와 함께 저장된 용장성 코드를 독출하고, 상기 독출된 용장성 코드에 대해 상기 독출된 사이클 데이터를 체크하는 것을 포함하 며, 상기 갱신된 사이클 데이터를 프로그램하는 단계는 상기 갱신된 사이클 데이터로부터 용장성 코드를 계산하 고 상기 계산된 용장성 코드를 동일 블록에 사이클 데이터로서 저장하는 것을 포함하는, 비휘발성 메모리 동작 방법.

#### 청구항 23

제22항에 있어서, 독출된 사이클 데이터 데이터를 독출된 용장성 코드에 대해 체크하는 것에서 상기 사이클 데이터가 무효한 것으로 나타나면, 상기 독출된 사이클 데이터 및 용장성 코드가 있는 블록을 이를 소거하는 대신 사용불가로서 마크하거나, 상기 사이클 데이터를 갱신하거나, 갱신된 사이클 혹은 사용자 데이터로 상기 블록을 프로그램하는 것인, 비휘발성 메모리 동작방법.

#### 청구항 24

제19항에 있어서, 상기 사이클 데이터를 갱신하거나 상기 갱신된 사이클 데이터를 다시 상기 하나 이상의 블록

들에 프로그램하기 전에 상기 사이클 데이터가 손실된 경우, 사용자 데이터를 상기 하나 이상의 블록들의 페이지들에 프로그램하는 대신 상기 하나 이상의 블록들을 사용불가로서 마크하는, 비휘발성 메모리 동작방법.

#### 청구항 25

제24항에 있어서, 상기 메모리 셀 어레이는 NAND 어레이인, 비휘발성 메모리 동작방법.

#### 청구항 26

제1 임계범위로 단위로서 함께 소거가 가능하고 상기 제1 임계범위에서 그리고 상기 제1 임계범위보다 연속적으로 큰 적어도 제2, 제3 및 제4 임계범위들에서 복수 페이지들의 사용자 데이터를 개별적으로 저장하는 다수 블록들의 셀들로 구성되고 NAND 구성으로 접속된 메모리 셀 어레이를 구비하는 비휘발성 메모리를 동작시키는 방법에 있어서,

- (a) 상기 블록들이 사이클된 횟수 데이터를 저장하는 단계로서, 상기 사이클 데이터는 상기 사이클 데이터가 관계된 블록들의 소정 수의 메모리 셀들 내에 저장되는, 단계;

- (b) 소거를 위해 하나 이상의 블록들을 어드레싱하고,

상기 하나 이상의 블록들 각각으로부터 상기 사이클 데이터를 독출하여 상기 독출된 사이클 데이터를 일시 저장 하고,

상기 하나 이상의 블록들 내의 상기 메모리 셀들을 소거하고,

상기 독출된 사이클 데이터를 갱신하고,

상기 제3 혹은 제4 임계범위를 사용하지 않고, 상기 제1 임계범위에서 상기 제2 임계범위로 소정 수의 셀들의 적어도 일부의 임계레벨들을 구동함으로써 상기 갱신된 독출된 사이클 데이터를 상기 하나 이상의 블록들 각각 에 프로그램하여 상기 하나 이상의 블록 내의 페이지들을 이에 사용자 데이터를 프로그래밍하는데 사용될 수 있 게 하는 단계를 포함하는, 소거 동작 단계;

(c) 그후에 적어도 상기 제1, 제2, 제3, 및 제4 임계범위들을 사용함으로써 사용자 데이터를 상기 하나 이상의 블록들의 페이지들에 프로그램하는 단계를 포함하고.

하나의 페이지는 사용자 데이터, 상기 사용자 데이터에 관계된 페이지 오버헤드 데이터, 및 상기 사용자 데이터 및 상기 페이지 오버헤드 데이터와 상이한 예비 셀로 구성되고,

상기 갱신된 사이클 데이터는 상기 하나 이상의 블록들 각각의 단일 페이지의 예비 셀들에 프로그램되는, 비휘 발성 메모리 동작방법.

#### 청구항 27

삭제

## 청구항 28

제26항에 있어서, 상기 사이클 데이터로부터 계산된 용장성 코드는 상기 사이클 데이터와 함께 블록에 저장되는, 비휘발성 메모리 동작방법.

## 청구항 29

제28항에 있어서, 상기 사이클 데이터를 독출하는 단계는 상기 사이클 데이터로부터 계산되고 이와 함께 저장된 용장성 코드를 독출하고, 상기 독출된 용장성 코드에 대해 상기 독출된 사이클 데이터를 체크하는 것을 포함하 며, 상기 갱신된 사이클 데이터를 프로그램하는 단계는 상기 갱신된 사이클 데이터로부터 용장성 코드를 계산하 고 상기 계산된 용장성 코드를 동일 블록에 사이클 데이터로서 저장하는 것을 포함하는, 비휘발성 메모리 동작 방법.

#### 청구항 30

제29항에 있어서, 독출된 사이클 데이터 데이터를 독출된 용장성 코드에 대해 체크하는 것에서 상기 사이클 데이터가 무효한 것으로 나타나면, 상기 독출된 사이클 데이터 및 용장성 코드가 있는 블록을 이를 소거하는 대신

사용불가로서 마크하거나, 상기 사이클 데이터를 갱신하거나, 갱신된 사이클 혹은 사용자 데이터로 상기 블록을 프로그램하는 것인, 비휘발성 메모리 동작방법.

#### 청구항 31

제26항에 있어서, 상기 사이클 데이터를 갱신하거나 상기 갱신된 사이클 데이터를 다시 상기 하나 이상의 블록들에 프로그램하기 전에 상기 사이클 데이터가 손실된 경우, 사용자 데이터를 상기 하나 이상의 블록들의 페이지들에 프로그램하는 대신 상기 하나 이상의 블록들을 사용불가로서 마크하는, 비휘발성 메모리 동작방법.

## 명 세 서

## 기술분야

[0001] 이 발명은 일반적으로 비휘발성 반도체 메모리들 및 이들의 동작에 관한 것으로, 특히 메모리 셀 블록 소거/기 입 사이클 카운트들의 사용에 관한 것이다.

#### 배경기술

- [0002] 플래시 EEPROM((Electrically Erasable and Programmable Read Only Memory) 셀 어레이를 사용하는 것으로 특히 소형 폼 팩터 카드들 형태인 최근에 사용되는 많은 상업적으로 성공한 비휘발성 메모리 제품들이 있다.

- [0003] NOR 어레이

- [0004] 전형적인 NOR 어레이에서, 메모리 셀들은, 셀들의 행들을 따라 연장하는 워드 라인들에 제어 게이트들이 접속되어 열(column) 방향으로 연장한 서로 이웃한 비트라인 소스 확산영역과 드레인 확산영역과의 사이에 접속된다. 한 전형적인 메모리 셀은 소스 확산영역과 드레인 확산영역 사이에 "분할-채널"을 갖는다. 셀의 전하 저장 요소는 채널의 한 부분 상에 배치되고 워드라인(제어 게이트라고도 함)은 전하 저장 요소만이 아니라다른 채널 부분 상에도 배치된다. 이것은 직렬의 두 개의 트랜지스터들을 구비한 한 셀을 효과적으로형성하며, 이 중 한 트랜지스터(메모리 트랜지스터)는 전하 저장 요소의 전하량과 워드라인의 전압과의 조합으로 이 트랜지스터의 채널 부분을 통해 흐를 수 있는 전류량이 제어되며, 다른 한 트랜지스터(선택 트랜지스터)는 이의 게이트로서만 작용하는 워드라인을 구비한다. 워드라인은 한 행의 전하 저장 요소들 위로 연장한다.이러한 셀들의 예들, 메모리 시스템들에서의 이들의 사용 및 이들을 제조하는 방법들은 미국특허제5,070,032호, 제5,095,344호, 제5,315,541호, 제5,343,063호, 및 제5,661,053호와 1999년 1월 27일 출원된미국특허 출원번호 09/239,073에 주어져 있다.

- [0005] 이러한 분할-채널 플래시 EEPROM 셀의 변형예는 전하 저장요소와 워드라인 사이에 위치한 스티어링 게이트를 추가한다. 어레이의 각각의 스티어링 게이트는 워드라인에 수직하여, 한 열의 전하 저장 요소들 위로 연장한다. 효과는 선택된 셀을 독출하거나 프로그램할 때 워드라인이 동시에 두 가지 기능들을 수행해야 하는 것에서 해방시키는 것이다. 이들 두 가지 기능들은 (1) 선택 트랜지스터의 게이트로서 작용하게 하여, 이에 따라 선택 트랜지스터를 턴 온 및 오프시키는 데에 있어 적절한 전압을 필요로 하는 것과, (2) 워드라인과 전하 저장요소 간전계 (용량성) 결합을 통해 전하 저장요소의 전압을 원하는 레벨로 구동시키는 것이다. 이들 기능들 둘 다를 단일 전압으로 최적으로 수행하기는 대부분 어렵다. 스티어링 게이트의 추가로, 워드라인은 기능 (1)을 수행하는 것만이 필요한 한편, 추가된 스티어링 게이트는 기능 (2)를 수행한다. 플래시 EEPROM 어레이에서 스티어링게이트들의 사용은 예를 들면 미국특허 제5,313,421호 및 제6,222,762호에 기술되어 있다.

- [0006] 기판으로부터 전자들을 게이트 절연체를 통해 플로팅 게이트 저장요소에 주입하는 다양한 프로그래밍 기술들이 있다. 가장 일반적인 프로그래밍 메커니즘들은 Brown and Brewer, Nonvolatile Semiconductor Memoyy Technology, IEEE Press, section 1. 2, pages 9-25 (1998) 책자에 기술되어 있다. 채널 "핫-전자 주입"(1.2.3 절)이라 하는 한 기술은 셀의 채널로부터의 전자들을 셀의 드레인에 이웃한 플로팅 게이트의 영역에 주입한다. "소스측 주입"(1.2.4 절)이라 하는 또 다른 기술은 드레인에서 떨어져 있는 채널의 영역에 전자 주입 조건들을 형성할 수 있게 메모리 셀 채널의 길이를 따라 기판 표면 전위를 제어한다. 소스측 주입은 Kamiya et al., "EPROM Cell with High Gate Injection Efficiency,"IEDM Technical Digest, 19829 pages 741-744 논문 및 미국특허 제4,622,656호 및 제5,313,421호에 기술되어 있다.

- [0007] 메모리 셀들을 소거하기 위해 전자 저장요소들로부터 전하를 제거하는 두 가지 기술들은 위에 기술된 두 유형들

의 NOR 메모리 셀 어레이들 모두에서 사용된다. 한 기술은 저장요소와 기판 사이의 유전층의 부분을 통해 전자들이 터널링되게 하는 적합한 전압들을 기판에 대해 소스, 드레인 및 다른 게이트(들)에 인가함으로써 소거하는 것이다. 다른 한 소거 기술은 저장요소로부터 또 다른 게이트에 이들 사이에 개재된 터널 유전층을 통해 전자들을 보내는 것이다. 전술한 제1 유형의 셀에서, 이 목적을 위해 제3 소거 게이트가 제공된다. 스티어링 게이트의 사용으로 인해 3개의 게이트들을 이미 구비한 전술한 제2 유형의 셀에서, 전하 저장요소는 제4 게이트를 추가할 필요없이 워드라인에 대해 소거된다. 이 기술이 워드라인에 의해 수행되어야 하는 제2 기능을 다시 추가할지라도, 이들 기능들은 서로 상이한 시간들에서 수행되므로, 두 기능들에 기인한 절충을 하지 않아도 된다. 어느 한 소거 기술이 이용될 때, "플래시"에서는 동시에 소거를 위해 상당수의 메모리 셀들이 그룹으로 형성된다. 한 방식에서, 그룹은 디스크 섹터에 저장된 일 분량의 사용자 데이터, 즉 512바이트와, 이에 더하여 얼마간의 오버헤드 데이터를 저장하기에 충분한 메모리 셀들을 포함한다. 또 다른 방식에서, 각 그룹은 많은 디스크 섹터만큼의 데이터와 동등한 량의 수천 바이트의 사용자 데이터를 유지하기에 충분한 셀들을 포함한다. 복수-블록 소거, 결함관리 및 그 외 플래시 EEPROM 시스템 특징들은 미국특허 제5,297,148호에 기술되어 있다.

- [0008] 대부분의 모든 집적회로 응용들에서처럼, 일부 집적회로 기능을 구현하는데 필요한 실리콘 기판면적을 줄이려는 압력이 플래시 EEPROM 시스템들에서도 존재한다. 주어진 크기의 메모리 카드 및 이외 다른 유형들의 패키지들 의 저장용량을 증가시키기 위해서, 혹은 용량을 줄임과 아울러 크기를 감소시키기 위해서, 실리콘 기판의 주어 진 면적 내에 저장될 수 있는 디지털 데이터량을 증가시키려는 것이 계속적으로 요구되고 있다. 데이터의 저장 밀도를 증가시키는 한 방법은 메모리 셀 당 한 비트 이상의 데이터를 저장하는 것이다. 이것은 저장요소의 전하 레벨 전압 범위의 윈도우를 2 상태 이상으로 분할함으로써 달성된다. 이러한 상태들을 4개 이용함으로써 각셀은 2비트의 데이터를 저장할 수 있고, 8 상태에 의해서는 셀 당 3비트의 데이터를 저장할 수 있고, 등등을 할수 있다. 복수 상태의 플래시 EEPROM 구조 및 동작은 미국특허 제5,043,940호 및 제5,172,338호에 기술되어 있다.

- [0009] 또 다른 유형의 메모리 셀은 각 저장요소가 복수상태들로 동작될 수 있는 2개의 저장요소들을 포함한다. 이러한 유형의 셀에서, 2개의 저장요소들은 소스 확산영역과 드레인 확산영역 사이에 선택 트랜지스터를 개재하여이들 사이에 채널 상에 포함된다. 각 열의 저장요소들을 따라 스티어링 게이트가 포함되고, 그 위에 각 행의 저장요소들을 따라 워드라인이 설치된다. 독출 혹은 프로그래밍을 위해 소정의 저장요소에 액세스할 때, 이 저장요소를 포함한 셀의 다른 저장요소 상의 스티어링 게이트는 이 다른 저장요소에 어떤 전하 레벨이 존재하든지 간에 이 저장요소 밑의 채널을 턴 온 시키기에 충분히 높게 상승된다. 이것은 동일 메모리 셀 내 상기 소정의 저장요소를 독출 혹은 프로그램하는데 있어 요인으로서 상기 다른 저장요소를 사실상 소거한다. 예를 들면, 셀의 상태를 읽어내는데 사용될 수 있는 것인 셀에 흐르는 전류량은 원하는 저장요소 상의 전하량의 함수이지 동일 셀 내 다른 저장요소의 함수는 아니다. 이러한 셀 어레이 구조 및 조작기술의 예들은 미국특허 제5,712,180호, 제6,103,573호 및 제6,151,248호에 기술되어 있다.

### [0010] <u>NAND</u> 어레이

[0011] 또 다른 플래시 EEPROM 구조는 NAND 어레이를 이용하는데, 2 이상, 예를 들면 16 혹은 32의 메모리 셀들의 직렬 스트링들이 개개의 비트라인들과 한 기준전위 사이에 하나 이상의 선택 트랜지스터들과 함께 접속되어 다수 열의 셀들을 형성한다. 워드라인들은 상당수의 이들 열들 내의 셀들을 가로질러 연장한다. 한 열 내의 한 개별 셀은 스트링 내 나머지 셀들을 강제로 턴 온 되게 하여 스트링에 흐르는 전류가 어드레스된 셀 내 저장된 전하의 레벨에 따르도록 함으로써 프로그램시 독출되고 검증된다. NAND 구조 어레이 및 메모리 셀의 일부로서의 이의 동작의 예는 미국특허 제5,570,315호, 제5,774,397호 및 제6,046,935호에 있다.

## [0012] 전하 저장요소

[0013] 현 플래시 EEPROM 어레이들 및 앞에서 참조한 특허들 및 논문들에 다루어진 전하 저장요소들은 통상 도핑된 폴리실리콘 재료로부터 형성되는, 대부분 일반적으로 전기적 도전성의 플로팅 게이트들이다. 플래시 EEPROM 시스템들에서 유용한 또 다른 유형의 메모리 셀은 비휘발성으로 전하를 저장하기 위해 도전성 플로팅 게이트 대신비도전성 유전재료를 이용한다. 이러한 셀은 Chan et al., "A True Single-Transistor Oxide-Nitride-Oxide EEPROM Device,"IEEE Electron Device Letters, Vol. EDL-8, No. 3, March 1987, pp. 93-95 논문에 기술되어있다. 산화실리콘, 질화실리콘 및 산화실리콘("ONO")로 형성된 3층의 유전층은 도전성 게이트 전극과 메모리셀 채널 상의 반도체 기판의 표면 사이에 개재된다. 셀은 셀로부터 전자들을 질화막에 주입함으로써 프로그램되고, 이들 전자들은 제한된 영역에 트랩되어 저장된다. 이 저장된 전하는 검출이 가능하게 셀의 채널 부분의임계전압을 변경한다. 셀은 핫 정공들을 질화막에 주입함으로써 소거된다. Nozaki et al., "A 1-Mb EEPROM

with MONOS Memory Cell for Semiconductor Disk Application," IEEE Journal of Solid-State Circuits, Vol. 26, No. 4, April 1991, pp. 497-501을 참조한다. 이 논문에는 별도의 선택 트랜지스터를 형성하기 위해 메모리 셀의 부분 위로 도핑된 폴리실리콘 게이트가 연장하는 분할-게이트 구성과 유사한 셀을 기술하고 있다.

- [0014] 미국특허 제5,851,881호는 메모리 셀의 채널 위에서 서로 인접하게 배치된 2개의 저장요소들의 사용을 기술하고 있고, 이중 한 저장요소는 유전성 요소이며 다른 하나는 도전성 플로팅 게이트이다. 2비트의 데이터가 저장되는데, 이중 한 비트는 유전성 요소에, 다른 비트는 플로팅 게이트에 저장된다. 메모리 셀은 두 게이트 각각을 2개의 서로다른 전하 레벨 범위들 중 하나로 프로그램함으로써, 4개의 저장상태들 중 하나를 나타내는, 4개의 서로 다른 임계 레벨 조합들 중 한 조합에 프로그램된다.

- [0015] 유전성 저장요소를 이용하는 각 셀에 2비트를 저장하는 또 다른 방식은 Eitan et al., "NROM: A Novel Localized Trapping, 2-Bit Nonvolatile Memory Cell," IEEE Electron Device Letters, vol. 21, no. 11, November 2000, pp. 543-545에 기술되어 있다. ONO 유전층은 소스 확산영역과 드레인 확산영역 사이으 채널을 가로질로 연장한다. 한 데이터 비트를 위한 전하는 드레인에 이웃한 유전층 내로 모이게 되고, 다른 데이터 비트를 위한 전하는 소스에 인접한 유전층 내로 모이게 된다. 복수-상태 데이터 저장은 유전층 내 공간적으로 이격된 전자 저장영역들의 2진 상태들을 개별적으로 독출함으로써 얻어진다.

- [0016] 대량 소거 블록들

- [0017] 전형적인 비휘발성 플래시 어레이의 메모리 셀들은 함께 소거되는 분리된 다수의 블록들의 셀로 분할된다. 즉, 블록이 소거 단위이다. 각 블록은 통상 한 페이지 이상의 데이터를 저장하며, 한 페이지는 프로그래밍 및 독출 단위인데, 그러나 한 페이지 이상이 단일 동작으로 프로그램 또는 독출될 수도 있다. 통상 각각의 페이지는 한 섹터 이상의 데이터를 저장하고, 한 섹터의 크기는 호스트 시스템에 의해 정의된다. 한 예는 자기 디스크 드라이브들에 정해진 표준에 따라, 한 섹터의 512 바이트의 사용자 데이터, 및 이에 더하여 사용자 데이터 및/또는 저장되는 블록에 관한 얼마간의 수 바이트의 오버헤드 정보이다.

- [0018] 블록 경험(Experience) 카운트

- [0019] 개개의 블록들의 메모리 셀들이 경험하는 소거 및 재-프로그래밍 사이클 횟수는 흔히, 메모리 시스템의 동작의 최적 제어의 일부로서 간수된다. 이렇게 하는 한 이유는 플래시 EEPROM 셀들이 지탱할 수 있는 한정된 횟수의 소거/기입 사이클들 때문이다. 성능 및 신뢰도는 대개는 이러한 사이클 횟수가 증가함으로써 열화되고, 허용될 수 있는 이러한 열화의 량은 시스템의 각종의 동작 파라미터들에 좌우된다. 어떤 메모리 셀 블록들은 정규의 동작에서 다른 블록들보다 더 사이클이 행해질 수 있다. 한 블록의 사이클 카운트가 기설정된 한도의 예상 내 구성에 이르렀을 때, 이 블록은 용장 블록을 사용하기 위해 시스템으로부터 맵(map)될 수 있다. 이의 예는 미 국특허 제5,268,870호에 기재되어 있는데, 각 블록의 경험 카운트는 블록 내에 오버헤드 데이터의 일부로서 저 장된다. 미국특허 제6.426,893호는 관계된 블록들과는 격리된 블록들에, 다른 오버헤드 데이터뿐만 아니라 블 록 경험 카운트들을 저장하는 시스템을 기술하고 있다. 또한, 경험 카운트는 시스템의 메모리 셀 블록의 사용 (마모)을 균등하게 하는데 사용될 수 있다. 상대적 블록 경험 카운트들은 시스템 제어기에 의해 감시되고, 사 용의 소정의 불균등이 검출된 것에 응하여, 낮은 경험 사이클 카운트들을 가진 블록들에 차후에 상당량의 재기 입이 되게 하기 위해서 블록들의 논리-물리(logical-to-physical) 어드레스 변환을 변경한다. 이러한 마모 균 등화 기술들의 예들은 미국특허 제6,081,447호에 있다. 관계된 블록들에 경험 카운트들을 유지하는 것에 대한 대안으로서, 이들 카운트들은 블록 오버헤드 정보를 위해 제공된 다른 블록들에 저장될 수도 있다. 이의 예는 2000년 2월 17일에 출원된 미국특허출원번호 09/505,555에 기술되어 있다. 블록을 대치할 목적으로 경험 카운 트를 사용하는 것 외에도, 사용이 증가함에 따라 최적전압들이 흔히 증가할 것이기 때문에, 프로그래밍, 독출 및/또는 소거 동작시에 사용되는 전압들을 설정하는 데에 있어 제어기에 의해 카운트가 사용될 수도 있다.

- [0020] 위에 인용한 특허, 특허출원, 논문 및 책자의 부분들을 참조로 배경기술 설명에 전체를 포함시킨다.

#### 발명의 상세한 설명

- [0021] 발명의 요약

- [0022] 동시에 소거될 수 있는 블록들의 셀들로 구성된 메모리 셀들을 구비한 비휘발성 메모리 시스템에서, 블록들은 개별적으로 프로그램가능하고 독출될 수 있는 복수 페이지들의 사용자 데이터로 더욱 분할된 것으로, 개개의 블록들에 관계된 오버헤드 데이터는 데이터가 관계된 블록 내에 저장되고 블록을 소거하는 사이클의 일부로서 갱신된다. 사이클 데이터가 한 블록의 단일 페이지의 예비 셀들에 저장된다면, 이 데이터는 그 페이지에의 단일

독출동작에 의해 읽혀질 수 있다. 또는, 사이클 데이터는 페이지들에 저장된 데이터 섹터들의 헤드들에서와 같이, 미사용 셀들에 블록의 2 이상의 페이지들에 걸쳐 분산될 수도 있다. 이들 기술들은 특히 NAND형의 플래시 메모리 시스템들에 적용될 수 있는데 다수 블록들의 메모리 셀들이 함께 소거되는 다른 유형들의 비휘발성 메모리 시스템들에서도 효과적으로 사용될 수 있다.

- [0023] 주어진 수의 메모리 셀들이 저장할 수 있는 데이터량을 증가시키는 추세이기 때문에, 각 저장요소마다 2이상의 프로그램된 상태들을 설정함으로써 각 메모리 셀 저장요소에 1비트 이상의 사용자 데이터를 저장하는 것이 바람 직하다. 그러나, 블록 사이클 카운트 데이터에 대해서는 이 데이터를 2상태로, 혹은 메모리 셀 저장요소당 1비트로 저장하는 것이 효과적이다. 사이클 카운트 데이터 프로그래밍이 향상되고, 이 프로그래밍은 기입될 새로이 소거된 블록의 교란량을 감소시키게 행해질 수 있다.

- [0024] 용장성 코드는 사이클 카운트 데이터로부터 계산될 수 있고 블록 오버헤드 데이터의 일부로서 더불어 프로그램 될 수 있다. 오류정정코드(ECC)는 사이클 카운트 데이터에 어떤 오류들을 정정할 수 있기 위해서 제공될 수 있게 하는 용장성의 예이며, 오류들이 너무 많아 정정할 수 없다면, 사이클 카운트 데이터는 무효한 것으로 확정한다. 무효할 때, 블록은 경험된 소거 사이클 수를 알지 못하기 때문에 시스템으로부터 맵되고, 이러한 불확실성은 블록의 동작에서 메모리 제어기에 의해 행해지는 판단에 악영향을 미칠 수 있다. 블록은 카운트가 휘발성 메모리에 일시 저장되고 있는 중에 파워가 나갔을 때 발생할 수 있는 것과 같은, 소거 동작시 사이클 카운트 데이터가 손실된 경우 시스템으로부터 맵될 수도 있다. 이것은 예를 들면 소거 사이클 중에, 파워를 제공하고 있는 호스트 시스템으로부터 메모리 카드를 사용자가 뺄 경우에 일어날 수 있다.

- [0025] 본 발명은 배경기술에서 설명된 플래시 EEROM 시스템들 및 그외 것들을 포함하여 많은 서로 다른 유형들의 비휘 발성 메모리 중 어느 하나에 동작한다. 플로팅 게이트 전하 저장요소들을 사용한 특정의 NOR 어레이 구조는 2001년 8월 8일에 출원된 미국특허출원번호 09/925,102, 및 2000년 9월 22일에 출원된 미국특허출원번호 09/667,344에 기술되어 있다. 유전 전하 저장요소들을 사용한 플래시 메모리 어레이들은 2002년 10월 25일에 출원된 미국특허출원번호 10/280,352에 기술되어 있다. 큰 메모리 셀 소거 블록들의 관리는 2000년 11월 22일에 출원된 미국특허출원번호 09/718,802, 및 2001년 1월 19일에 출원된 09/766,436에 기술되어 있다. NAND 어레이들의 프로그래밍은 2001년 6월 27일에 출원된 미국특허출원번호 09/893,277 및 특허 제6,456,528호에 기술되어 있다. 전술한 출원 및 특허를 참조로 이 발명의 요약에 전체를 포함시킨다.

- [0026] 본 발명의 여러 가지 면들의 추가의 목적, 특징 및 이점은 대표적인 실시예들의 다음의 설명에 포함되고, 이 설명은 첨부한 도면을 참조하여 취해진다.

### 실시예

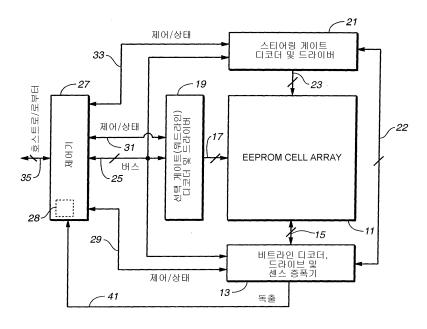

- [0036] 본 발명의 다양한 면들이 구현될 수 있는 한 예로서의 메모리 시스템을 도 1의 블록도로 도시하였다. 상당수의 개별적으로 어드레스가 가능한 메모리 셀들(11)은 행 및 열들의 규칙적인 어레이로 배열되나, 이외 다른 물리적 배열들의 셀들도 확실히 가능하다. 이 시스템은 배경기술 설명 및 여기 포함된 참조문헌들에 기술된 바와 같이, 어레이(11)를 특히 NOR형으로 한 것이다. 여기서는 셀 어레이(11)의 열들을 따라 연장하는 것으로 지정된 비트라인들은 라인들(15)을 통해 비트라인 디코더 및 드라이버 회로(13)에 전기적으로 접속된다. 본 설명에서는 셀 어레이(11)의 행들을 따라 연장하는 것으로 지정된 워드라인들은 라인들(17)을 통해 워드라인 디코더 및 드라이버 회로(19)에 전기적으로 접속된다. 어레이(11) 내 메모리 셀의 열들을 따라 연장하는 스티어링 게이트들은 라인들(23)을 통해 스티어링 게이트 디코더 및 드라이버 회로(21)에 전기적으로 접속된다. 디코더들 (13, 19, 21) 각각은 버스(25)를 통해 메모리 제어기(27)로부터 메모리 셀 어드레스들을 수신한다. 디코더 및 구동회로들은 또한 각각의 제어 및 상태 신호 라인들(29, 31, 33)을 통해 제어기(27)에 접속된다. 스티어링 게이트들 및 비트라인들에 인가되는 전압들은 디코더 및 드라이버 회로들(13, 21)을 상호접속하는 버스(22)를 통해 조정된다. 제어기는 여러 가지 유형들의 레지스터들과, 이외 휘발성 랜덤 액세스 메모리(RAM)(28)를 포함한 메모리를 포함한다.

- [0037] 제어기(27)는 라인들(35)을 통해 호스트 디바이스(도시생략)에 접속될 수 있다. 호스트는 개인용 컴퓨터, 노트북 컴퓨터, 디지털 카메라, 오디오 플레이어, 이외 각종의 휴대 전자 디바이스 등일 수 있다. 도 1의 메모리시스템은 일반적으로, PCMCIA, CompactFlsh 협회, MMC 협회, 그 외 이들 중 하나와 같은, 몇몇의 현존의 물리 및 전기 표준들 중 하나에 따라 카드에 구현될 것이다. 카드 형식으로 있을 때, 라인들(35)은 호스트 디바이스의 대응 커넥터와 인터페이스하는 카드 상의 커넥터의 단부를 이룬다. 대다수의 카드들의 전기적 인터페이스는 ATA 표준에 따르며, 메모리 시스템은 호스트에게는 자기 디스크 드라이브인 것처럼 보이게 된다. 이외 다

른 메모리 카드 인터페이스 표준들도 존재한다. 카드 형식에 대한 대안으로서, 도 1에 도시된 유형의 메모리 시스템은 호스트 디바이스에 영구적으로 내장될 수도 있다.

- [0038] 디코더 및 드라이버 회로들(13, 19, 21)은 프로그래밍, 독출, 소거 기능들을 실행하기 위해서, 각각의 제어 및 상태 라인들(29, 31, 33)에 제어신호들에 따라, 버스(25)를 통해 어드레스된 바와 같이, 어레이(11)의 각각의라인들에 적합한 전압들을 발생한다. 전압레벨들 및 이외 어레이 파라미터들을 포함한, 어떤 상태 신호들은 동일 제어 및 상태 라인들(29, 31, 33)을 통해 어레이(11)에 의해 제어기(27)에 제공된다. 회로(13) 내의 복수의센스 증폭기들은 어레이(11) 내 어드레스된 메모리 셀들의 상태들을 나타내는 전류 혹은 전압 레벨들을 수신하여, 독출동작 동안 라인들(41)을 통해 상기 상태들에 관한 정보를 제어기(27)에 제공한다. 많은 수의 센스 증폭기들은 일반적으로 많은 수의 메모리 셀들의 상태를 병렬로 독출할 수 있기 위해서 사용된다. 독출 동작 및 프로그램 동작시에, 통상적으로 한 행의 셀들은 회로들(13, 21)에 의해 선택되는 어드레스된 행 내의 다수의 셀들에 액세스하기 위한 회로들(19)을 통해 한번에 어드레스된다. 소거동작시, 많은 행들의 각 행 내 모든 셀들은 통상적으로 동시 소거를 위해 한 블록으로서 함께 어드레스된다.

- [0039] 도 1에 도시된 바와 같은 메모리 시스템의 동작은 전술한 배경기술 설명의 NOR 어레이 절에 특허들 및 논문들, 및 본원의 양수인인 샌드스크 사에 양도된 그외의 특허들에 기술되어 있다. 또한, 2001년 2월 26일에 출원된 미국특허출원번호 09/793,370는 데이터 프로그래밍 방법을 기술하고 있고 이 출원을 여기 참조로 포함시킨다.

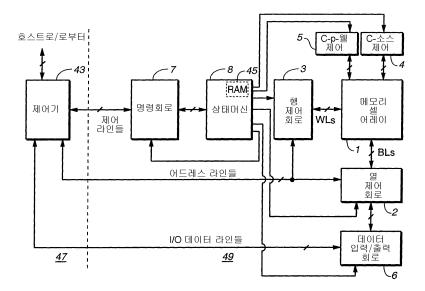

- [0040] 본 발명의 다양한 면들이 구현될 수 있는 또 다른 예의 메모리 시스템을 도 2의 블록도로 도시하였다. 매트릭스로 배열된 복수의 메모리 셀들(M)을 포함하는 메모리 셀 어레이(1)은 열 제어 회로(2), 행 제어회로(3), c-소스 제어회로(4) 및 c-p-웰 제어회로(5)에 의해 제어된다. 메모리 셀 어레이(1)은 배경기술 설명 및 참조로 여기 포함시킨 참조문헌들에 기술된 NAND형일 수 있다. 제어회로(2)는 메모리 셀들(M)에 저장된 데이터를 독출하고, 프로그램 동작시 메모리 셀들(M)의 상태를 판정하고, 프로그래밍을 증진시키거나 프로그래밍을 하지 못하게하기 위해 비트라인들(BL)의 전위레벨들을 제어하기 하기 위한 메모리 셀 어레이(1)의 비트라인들(BL)에 접속된다. 행 제어회로(3)는 워드라인들(WL) 중 하나를 선택하고, 독출전압들을 인가하고, 열 제어회로(2)에 의해 제어된 비트라인 전위레벨들이 더해진 프로그램 전압들을 인가하고, 메모리 셀들(M)이 형성된 p형 영역의 전압이결합된 소거 전압을 인가하기 위해 워드라인들(WL)에 접속된다. c-소스 제어회로(4)는 메모리 셀들(M)에 접속된 공통 소스라인(도 2에 "c-소스"으로서 표기된)을 제어한다. c-p-웰 제어회로(5)는 c-p-웰 전압을 제어한다.

- [0041] 메모리 셀들(M)에 저장된 데이터는 열 제어회로(2)에 의해 읽혀지고 I/O 라인 및 데이터 입력/출력 버퍼(6)을 통해 외부 I/O 라인들에 출력된다. 메모리 셀들에 저장될 프로그램 데이터는 외부 I/O 라인들을 통해 데이터 입력/출력 버퍼(6)에 입력되고, 열 제어회로(2)에 보내진다. 외부 I/O 라인들은 제어기(43)에 접속된다. 제어 기(43)는 각종 유형들의 레지스터들 및 그 외 다른 메모리로서, 전형적으로, 휘발성 랜덤 액세스 메모리를 포함한다.

- [0042] 플래시 메모리 디바이스를 제어하기 위한 명령 데이터는 제어기(43)에 접속된 외부 제어라인들에 접속된 명령회로들(7)에 입력된다. 명령 데이터는 어떤 동작이 요청되었는지를 플래시 메모리에 알린다. 입력된 명령은 열제어회로(2), 행제어회로(3), c-소스 제어회로(4), c-p-웰제어회로(5) 및 데이터 입력/출력 버퍼(6)를 제어하는 상태머신(8)에 보내진다. 상태머신(8)은 READY/BUSY 혹은 PASS/FAIL와 같은 플래시 메모리의 상태 데이터를 출력할 수 있다. 상태머신(8)은 다수의 레지스터들을 및 이외 휘발성 랜덤 액세스 메모리(45)를 포함한다.

- [0043] 제어기(43)는 개인용 컴퓨터, 디지털 카메라, 혹은 PDA(personal digital assistant)와 같은 호스트 시스템에 접속 혹은 접속될 수 있다. 이를테면 데이터를 메모리 어레이(1)에/로부터 저장 혹은 독출하거나, 이러한 데이터를 제공 혹은 수신하는 등의 명령들을 내는 것은 호스트이다. 제어기는 이러한 명령들을, 명령 회로들(7)에 의해 해석되어 실행될 수 있는 명령신호들로 전환한다. 제어기는 또한 통상적으로, 메모리 어레이에 혹은 이로부터 기입 혹은 독출되는 사용자 데이터를 위한 버퍼 메모리를 포함한다. 전형적인 메모리 시스템은 제어기(43)를 포함하는 하나의 집적회로 칩(47), 및 각각이 메모리 어레이 및 연관된 제어, 입력/출력 및 상태 머신 회로들을 포함한 하나 이상의 집적회로 칩들(49)을 포함한다. 물론, 추세는 시스템의 메모리 어레이 및 제어기회로들을 하나 이상의 집적회로 칩들에 집적시키는 것이다.

- [0044] 도 1 및 도 2의 메모리 시스템들 중 어느 것이든 호스트 시스템의 일부로서 내장될 수도 있고 혹은 호스트 시스템의 대응 소켓에 착탈가능하게 삽입될 수 있는 메모리 카드 내에 포함될 수도 있다. 이러한 카드는 메모리 시스템 전체를 포함할 수도 있고, 혹은 제어기 및 메모리 어레이는 연관된 주변회로들과 함께 별도의 카드들에 제공될 수도 있다. 몇몇의 카드 구현들이, 예를 들면, 참조로 전체를 여기 포함시키는 미국특허 제5,887,145에 기술되어 있다.

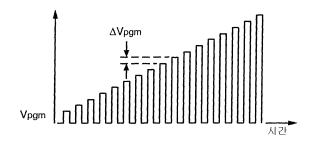

- [0045] 도 3은 메모리 셀 어레이들(1 혹은 11) 중 어느 하나의 저장요소들을 증분적으로 프로그래밍하기 위한 펼스기술을 예시한 것이다. 프로그래밍 전압(Vpgm) 파형이 도시되었다. 프로그래밍 전압(Vpgm)은 많은 펄스들로 분할되고, 펄스마다 ΔVpgm로 증분된다. 펄스와 펄스 사이의 기간에, 검증(독출) 동작들이 수행된다. 즉, 병렬로 프로그램되는 각 셀의 프로그램된 레벨은 프로그램되고 있는 검증레벨 이상인지를 판정하기 위해 각 프로그래밍 펄스 사이에서 읽혀진다. 주어진 메모리 셀의 임계 전압이 검증레벨을 초과한 것으로 판정되면, 이 주어진 셀의 직렬 셀 유닛이 접속된 비트 혹은 제어라인의 전압을 0V에서 Vdd로 상승시킴으로써 Vpgm이 제거된다. 병렬로 프로그램되는 셀들 중 다른 것들의 프로그래밍은 차례로 이들의 검증레벨들에 도달할 때까지 계속된다. 임계전압은 셀의 마지막 프로그래밍 펄스 동안에 검증레벨 미만으로부터 그 이상으로 옮겨진다.

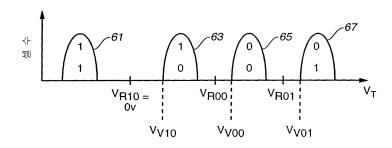

- [0046] 도 4는 저장요소당 4개의 상태들을 가진 메모리 어레이를 프로그래밍하는 기술을 도시한 것이다. 따라서, 2비트의 데이터가 각 저장요소에 저장된다. 프로그램된 저장요소들은 임계분포들(61,63, 65 혹은 67) 중 하나에 속하는 임계레벨들(V<sub>T</sub>)을 가진 메모리 셀 트랜지스터들을 형성한다. 분포(61)는 소거된 상태를 나타내며, 프로그램된 상태들 중 하나로서 이 예에선 "11"이다. 분포(61)는 음의 임계전압((V<sub>T</sub>)을 갖는 셀들을 포함한다. 양의 임계전압들을 포함하는 분포(63)는 데이터 비트 "10"을 나타낸다. 유사하게, 분포(65)는 "00"을 나타내며 분포(67)은 "01"을 나타낸다. 추가적인 다수의 상태들, 따라서 더 많은 비트들이 각 저장요소에 프로그램될 수도 있으나 예시를 위해 4 상태 시스템이 선택되었다.

- [0047] 개개의 셀들은 도 3에 도시된 바와 같은 일련의 펄스들에 의해 프로그램된다. 한 블록이 소거된 후에, 이의 메모리 셀 저장 트랜지스터들 전부는 분포(61) 내의 임계전압을 갖는다. 한 블록의 전부 혹은 일부를 이루는 다수의 메모리 셀들에 사용자 데이터 혹은 블록 오버헤드 데이터를 프로그래밍할 때에는 "11"에서 다른 어떤 것으로 변경된 상태를 가진 셀들에 프로그래밍 전압 펄스들이 인가된다. 소거로부터 제1 상태 "10"로 프로그램될 트랜지스터들에 대해서, 이들의 V<sub>T</sub>가 분포(63) 내의 검증레벨(V<sub>V10</sub>) 이상이 될 때, 펄스인가는 종료된다. 셀들의 상태들은 프로그래밍 펄스들 사이에서 검증된다. 유사하게, "00" 상태로 프로그램될 저장 트랜지스터들에 대해서 이들의 V<sub>T</sub>가 분포(65) 내의 검증레벨 V<sub>V00</sub> 이상이 될 때 펄스인가는 종료된다. 마지막으로, "01" 상태로 프로그램될 저장 트랜지스터들에 대해서 이들의 V<sub>T</sub>가 분포(67) 내의 검증레벨 V<sub>V01</sub>에 도달할 때 프로그램 펄스는 종료된다. 이 때, 일 그룹의 메모리 셀들의 병렬 프로그래밍이 완료된다.

- [0048] 개개의 프로그램 검증레벨들(V<sub>V10</sub>, V<sub>v00</sub>, V<sub>v01</sub>)은 이들의 각각의 분포들(63, 65, 67)의 하한들에 일치한다. 전형적인 프로그래밍에 있어서, 도 3의 프로그래밍 펄스들의 시작전압은 예로서 약 12볼트일 수 있고, 펄스들간 증분 ΔVpgm은 약 0.2볼트이다. 개개의 분산들(61, 63, 65, 67)의 폭은 대략 ΔVpgm와 같다.

- [0049] 도 4는 4개의 임계상태들 중 어느 것으로 셀이 프로그램되었는가를 판정함으로써 개개의 셀들로부터 데이터를 독출하는데 사용되는 전압들을 도시한 것이다. 전압들(V<sub>R10</sub>, V<sub>R00</sub>, V<sub>R01</sub>)은, 각각, "10", "00", "01" 저장상태들을 독출하는데 사용되는 기준전압들이다. 이들 전압들은 분포들(61, 63, 65, 67) 중 서로 이웃한 것들 사이에 대략 반 정도에 놓여진다. 이들은 독출되는 각 메모리 셀 트랜지스터의 임계 전압상태를 비교하는 임계전압들이다. 이것은 셀로부터 측정된 전류 혹은 전압을 기준 전류들 혹은 전압들과 각각 비교함으로써 달성된다.

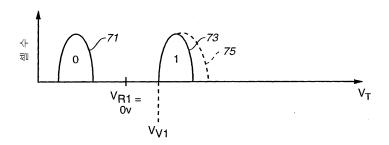

- [0050] 4개 이상의 저장 상태 시스템에서, 일부 셀들을 두 상태들 중 하나(2진)로 프로그램할 수 있는 것이 흔히 바람 직하다. 단일 어레이 내 복수-상태 및 2진 프로그래밍 둘 다의 사용이 여기 참조로 포함시키는 미국특허 제 5,930,167호, 및 앞서 언급한 미국특허출원번호 09/956,340에 기술되어 있다. 프로그래밍 전압들을 최소화하고 이에 따라 다른 메모리 셀들의 프로그램된 혹은 소거된 상태들의 교란들을 최소화하는 이러한 2중 프로그래밍의 또 다른 형태가 도 5에 도시되었다. 소거된 상태 "0"은 프로그램된 분포(71)로 도시된, 2개의 프로그램된 상태들 중 하나이다. 제2 프로그램된 상태 "1"은 분포(73)로 나타내었다. "1" 상태로의 프로그래밍은 검증레벨 (V<sub>V1</sub>)의 사용에 의해 달성된다. 데이터는 제로 볼트 V<sub>T</sub>에서 기준 레벨(V<sub>R1</sub>)을 사용하여 도 5의 2상태 메모리 셀들로부터 독출된다. 도 5의 분포들(71, 73)은 각각 도 4의 분포들(61, 63)에 대응한다. 2진 경우에 높은 임계 레벨 분포들(65, 67)을 회피함으로써, 2진으로 셀들을 프로그래밍한 결과로서 다른 셀들의 소거된 혹은 프로그램된 상태들에의 교란들이 최소로 된다.

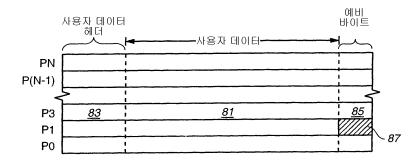

- [0051] 도 6은 전형적인 시스템에서 메모리 셀들의 상당수의 개별적으로 어드레스 가능한 블록들 중 하나의 구성예를 도시한 것이다. 한 블록의 메모리 셀들, 소거 유닛은 다수의 페이지들 PO 내지 PN으로 분할된다. 한 블록 내 페이지들의 수 N은 예로서, 8, 16 혹은 32일 수 있다. 각각의 단일 페이지는 프로그래밍 및 독출 단위이다. 하나 이상의 호스트 섹터 데이터는 각 페이지에 사용자 데이터로서 저장된다. 물리적으로, 한 페이지는 도 1

및 도 2의 시스템들의 어레이들(1 혹은 11) 중 어느 하나 내의 단일 행의 메모리 셀들로 형성될 수도 있다. 예를 들면, 도 6의 페이지(P3)는 사용자 데이터용의 공간(81)과 사용자 데이터에 관계된 오버헤드 데이터의 헤더용의 공간(83)을 포함한다. 메모리 공간(81)에 저장된 사용자 데이터로부터 계산된 ECC는 예를 들면 공간(83)에 저장된다. 어떤 메모리 어레이들은 사용자 공간(81) 내에 어떤 배드(bad) 바이트들을 대치하기 위해 공간(85)에 얼마간의 예비 바이트의 저장용량을 포함한다.

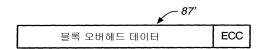

- [0052] 전체 블록의 오버헤드 정보 데이터를 저장하는데 사용되는 것은 블록의 한 페이지의 이들 예비 바이트들이다. 블록 오버헤드 데이터(87)는 예를 들면 페이지(P1)의 일부인 것으로 도시되었다. 데이터(87)의 일부로서 저장된 중요 정보는 흔히, 데이터(87)가 저장되는 블록이 소거된 횟수의 카운트이다. 아니면, 블록에 의해 경험된소거 사이클 수의 어떤 다른 표시가 저장될 수도 있다. 이 데이터는 어레이의 동작을 관리하는데 유용하다. 유용할 수 있는 이외 다른 블록 오버헤드 데이터(87)는 블록 메모리 셀들을 위한 최적 소거, 프로그래밍 및/또는 독출 전압들, 블록의 상태를 나타내는 플래그들, 블록의 논리 및/또는 물리적 어드레스들 및 어떤 대용 블록, 등을 포함한다. 블록 오버헤드 데이터(87)는 물리적 블록 자체의 정보를 제공하며, 페이지 오버헤드 데이터(83)는 이의 동일 페이지에 저장된 사용자 데이터의 정보를 제공한다. 이들 유형들의 오버헤드 데이터 중어느 하나 혹은 둘 다가, 관계된 블록과는 다른 블록(들)에 저장될 수 있을지라도, 도 6에 도시된 저장 위치들은 대부분의 애플리케이션들에 바람직하다.

- [0053] 사용자 데이터는 복수-상태로 각 페이지의 메모리 셀들에 저장되는 것이 바람직하다. 즉, 각 플로팅 게이트 혹은 메모리 셀들의 이 외 다른 저장요소는 각 저장요소 내 한 비트 이상의 데이터를 저장하기 위해서 2이상의 상태들 중 하나로 프로그램된다. 개개의 저장요소들이 4 상태들 중 한 상태로 프로그램된 도 4에 도시된 예가 편의상 구현된다. 이것은 주어진 량의 데이터를 저장하는데 필요한 메모리 셀들의 수를 감소시킨다. 그러나, 2 진으로 일 그룹의 셀들(87)에 블록 오버헤드 데이터를 프로그램하는 것이 흔히 바람직하다. 즉, 각 플로팅 게이트 혹은 메모리 셀들의 다른 저장요소는 정확히 2상태들 중 하나로 프로그램된다. 도 5에 도시된 예가 사용될 수 있다. 이것은 블록 오버헤드를 저장함에 있어 복수 상태에서 행해졌다면 이때보다 더 많은 메모리 셀들을 취할지라도, 데이터량이 작기 때문에 그에 따른 불리함은 적다. 잇점들은, 교란 및 전계 결합 효과에 대한 감소된 민감도와, 동일 혹은 이웃한 블록들 내 다른 메모리 셀들의 소거 혹은 프로그램된 상태에 교란 영향을 덜 미치면서, 감소된 시간내에 블록 오버헤드 데이터를 프로그램하는 능력을 포함한다.

- [0054] 블록 오버헤드 데이터의 2진 프로그래밍이 연속한 프로그래밍 펄스들의 사용과 도 3에 관하여 위에서 논한 바와 같은 개재한 상태 검증에 의해 달성되는 것이 바람직할지라도, 프로그래밍 프로세스를 실행하는데 필요한 시간은 시작펄스의 크기를 증가시킴으로써 및/또는 단계들 ΔVpgm의 크기를 증가시킴으로써 현저하게 감소될 수 있다. ΔVpgm이 복수 상태로 사용자 데이터를 프로그래밍하기 위한 0.2볼트의 값이라면, 0.4볼트와 같은 그보다 높은 값이 2진으로 블록 오버헤드 데이터를 프로그램하는데 사용될 수 있다. ΔVpgm의 증가로 도 5의 프로그램된 선택 분포(73)는 75로 나타낸 바와 같이 넓어지게 된다. 그러나, 상태(73)보다 높은 그 외의 프로그램된 상태들은 전혀 없기 때문에, 이 증가된 분포 폭은 아무 문제도 없다.

- [0055] 일반적으로, 블록 오버헤드 데이터는 도 6의 예를 든 블록 내의 페이지들 중 어느 한 페이지의 예비 셀들에 저장될 수 있다. 블록 오버헤드 데이터가 저장되는 각 블록 내의 페이지는 고정된 것일 수도 있고 아니면 블록마다 그리고 시간에 따라 달라지게 할 수도 있다. 예를 들면, 페이지(P1)이 결함 셀들을 대치함에 있어 그의 예비 셀들 중 일부의 사용을 요한다면, 그리고, 블록 오버헤드 데이터를 저장하는데 있어 남아있는 충분한 예비 셀들이 없다면, 그 블록에 대한 오버헤드 데이터는 또 다른 페이지에 저장될 수 있다. 또한, 블록 오버헤드 데이터용의 공간은 도 6에 도시된 바와 같이 반드시 한 페이지의 끝 혹은 이의 메모리 셀 행일 필요는 없고 그보다는 미사용 메모리 셀들이 존재하는 어떤 다른 위치가 될 수 있다. 또한, 연속한 셀 어드레스 위치들에 데이터가 저장된다면 메모리 제어기에 있어선 더 용이하게 될 것이라 하더라도, 블록 오버헤드 데이터는 반드시 인접하여 놓여진 메모리 셀들에 저장될 필요는 없다.

- [0056] 메모리 어레이가 NAND 형이라면, 블록 오버헤드 데이터를 저장함에 있어 다른 것들보다 유리한 어떤 페이지들이 있을 수 있다. 배경기술 설명에서 인용한 특허들에서 다루어진 NAND 플래시 메모리의 한 유형에서, 페이지들은 한 페이지를 프로그램하는 것이 다른 페이지들의 셀들의 프로그램된 상태들에 미치는 교란 영향을 감소시키기 위해서, 특정한 순서, 이를테면 PO 내지 PN으로만 프로그램되게 한다. 또한, 마지막 페이지들(PN 및 P(N-1))은 페이지들 중 다른 페이지들보다 교란 영향을 받기가 더 쉽다. 그러므로, 총 16페이지를 갖는 P4 혹은 P5의 블록들과 같은, 블록의 시작부분에 더 가까운 어떤 다른 페이지에 블록 오버헤드 데이터를 저장하는 것이 바람직하다.

- [0057] 블록 오버헤드 데이터가 메모리의 동작에 중요할 수 있기 때문에, ECC와 같은 용장성 코드가 블록 오버헤드 데이터로부터 계산될 수도 있고 동일 블록에 그 데이터와 함께 저장될 수도 있다. 그러면, ECC는 데이터 독출시 데이터를 검증하고 소수의 무효한 비트들을 정정하는 능력을 제공하는데 사용된다. 도 6의 블록 오버헤드 데이터(87)에 ECC를 포함하게 한 구성이 도 7에 도시되었다. 저장된 블록 오버헤드 데이터의 무효한 비트들의 수가 ECC가 정정할 수 있는 것을 초과한다면, 이 정보는 제어기에 유용하다. 저장되는 오버헤드 데이터의 유형이 메모리 시스템의 동작에 중요하다면, 이 데이터를 블록으로부터 독출하는 무능은 그 블록이 또 다시 사용되지 않도록 이 블록을 맵하기 위해 제어기에 의해 사용될 것이다. 이 블록이 사용되지 않을 것임을 나타내기 위해 블록 내에 플래그가 셋 될 수도 있고, 혹은 제어기는 무효 블록 리스트를 자주적으로 유지할 수 있다.

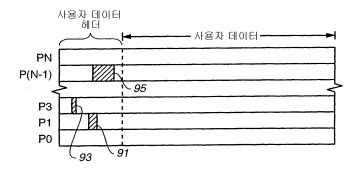

- [0058] 또 다른 정보를 제공하기 위해서, 도 6과는 다른 메모리 셀 블록 구성이 도 8에 도시되었다. 이 경우, 예비 셀들은 각 페이지에 포함되지 않는다. 그러므로, 블록 오버헤드 데이터는 블록 내 다른 어떤 곳에 저장될 필요가 있다. 도 8에 도시된 예는 이를테면 3개의 서로 다른 페이지 헤더들의 위치들(91, 93, 95)에, 블록의 페이지 헤더들 내에 상기 데이터를 예비 바이트들로 분포시킨다. 이것은 도 6의 예에서 한 블록의 단지 한 페이지만을 독출할 필요가 있는 것과는 반대로, 블록 오버헤드 데이터가 얻어질 수 있기 전에 모든 3개의 페이지들을 독출 해야 한다.

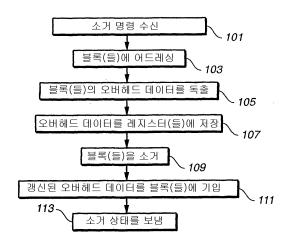

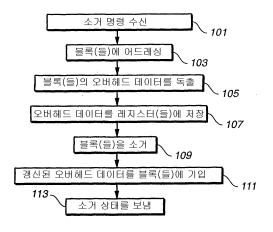

- [0059] 도 9를 참조하여, 위에 기술된 블록 오버헤드 데이터를 이용하는 예시한 소거 동작을 설명한다. 제1 단계 101에서는 단계 103에서 발행된 어드레스들에 의해 특정된 하나 이상의 다수의 블록들을 동시에 소거하기 위해서 제어기(도 1의 27 혹은 도 2의 43)에 의해 명령이 발행된다. 다음 단계 105에서, 제어기는 어드레스된 블록들 각각으로부터 블록 오버헤드 데이터를 읽는다. 통상의 시스템에서, 이것은 페이지가 프로그래밍 및 소거 단위이기 때문에 블록 오버헤드 데이터가 조정되는 각각의 어드레스된 블록의 전체 페이지(들)을 독출하는 것을 수반한다. 예를 들면, 오버헤드 데이터는 도 6의 데이터(87), 혹은 도 8의 데이터(91, 93, 95)일 수 있다. 블록 오버헤드 데이터가 사용자 데이터 및 이들의 헤더들보다 다른 수의 상태들로 저장된다면, 제어기는 사용자 데이터 및 헤더들을 독출시 사용되는 것보다 다른 한 세트의 기준 레벨들로 오버헤드 데이터를 독출한다. 이 독출된 데이터는 가장 편리하게는 각각의 제어기(27) 및 상태머신(8)의 일부로서 포함되는 랜덤-액세스-메모리 (RAM)(28 혹은 45)에, 제어기에 의해 시스템에 일시적으로 저장된다. 어드레스된 블록들 각각에 메모리 셀들은 단계 109에 따라, 함께 소거된다.

- [0060] 블록 오버헤드 데이터가 모든 ECC와 함께 혹은 데이터로부터 계산된 다른 용장성 코드와 함께 저장된다면, RAM에 기입하기 전에 데이터의 유효성이 체크된다. 유효한 것으로 판정된다면, 혹은 유효하게 되게 오류 오버헤드 데이터가 정정될 수 있다면, 프로세스는 기술된 바와 같이 진행된다. 그러나, 블록 오버헤드 데이터가 유효하기 않거나 유효하게 할 수 없다면, 블록의 이력을 모를 때 이 블록이 추후에 올바르게 동작될 수 없다는 우려 때문에 블록을 사용할 수 없게 하는 것이 바람직할 수 있다. 이어서 소거 프로세스가 그 블록에 관하여 중지되고 이의 어드레스가 제어기에 의해 유지된 배드(bad) 블록 리스트에 추가될 수도 있다. 아니면, 소거 프로세스는 계속될 수 있고 더 이상 사용되지 않음을 나타내기 위해 블록의 오버헤드 공간에 플래그가 기입될 수도 있다. 그러면, 제어기는 추후에 소거 및 프로그래밍 사이클들이 행해질 블록들을 판정시 이러한 프래그들을 찾는다.

- [0061] 또한, 어드레스된 블록들이 소거된 후에 메모리 시스템에의 전원공급이 중단되면, 블록 오버헤드 데이터는 통상의 경우인 휘발성 메모리에 데이터가 일시 저장되는 RAM이면 손실될 것이다. 이러한 상황에서, 제어기는, 일단전원이 복구되면, 소거된 블록들에 다시 기입할 어떤 블록 오버헤드 데이터도 갖고 있지 않다. 블록 오버헤드데이터가 존재하지 않을 때 이러한 데이터를 독출하는 것을 수반하는 블록들을 사용하려는 어떤 차후의 시도는 제어기로 하여금 이들의 어드레스들을 배드(bad) 블록 리스트에 추가하거나, 블록들에 플래그를 셋 하거나 이외어떤 다른 기술에 의해 블록들을 시스템으로부터 맵(map)하게 할 수 있다.

- [0062] 전술한 바와 같이, 중요한 블록 오버헤드 데이터는 개개의 블록이 소거 및 재-프로그래밍 사이클을 경험한 횟수일 수 있다. 이러한 횟수, 혹은, 포함된다면, 이 횟수에 관계된 소정 량은 소거 사이클의 일부로서 갱신된다. 제어기 RAM에 저장된 량은 RAM으로부터 독출되고 블록이 또 다른 소거 사이클에 의존함을 기록하기 위해, 소거되는 각 블록에 대해 갱신된다. 도 9의 단계 111로 나타낸 바와 같이, 갱신된 횟수는 관계된 각 블록에 기입된다. 가장 간단한 구현은 블록으로부터 읽혀진 소거 사이클을 1만큼 중분시키고, 소거된 후의 블록에 그 중분된 카운트를 다시 기입하는 것이다. 블록 오버헤드 데이터는 블록이 소거될 때마다 갱신되지 않는 다른 정보 데이터를 포함할 수도 있는데, 이 경우 이러한 유형의 데이터는 어떠한 변경없이 그 소거된 블록에 다시 기입된다. ECC 혹은 이외 다른 용장성 코드가 블록 오버헤드 데이터에 사용된다면, 이러한 코드는 블록에 다시 기입될 갱

신된 오버헤드 데이터로부터 계산되고 이어서 이 갱신된 오버헤드 데이터와 함께 블록에 프로그램된다.

- [0063] 소거 사이클의 마지막 단계는 단계 113에 나타낸 바와 같이, 어레이 및 이의 주변회로들이 완료 상태 신호를 다시 제어기에 보내는 것이다. 소거된 블록들은 블록 오버헤드 데이터가 프로그램된 위치(들)에는 제외하고, 소거된 상태에 있다. 그후에 사용자 데이터가 블록의 페이지들에 프로그램될 수 있다.

- [0064] 소거 사이클 카운트는 많은 서로 다른 방법들에 사용될 수 있다. 메모리 셀들의 어떤 특징들은 소거/프로그래 밍 사이클들의 횟수가 증가함에 따라 변하기 때문에, 어레이의 동작은 영향받은 동작 파라미터들도 변한다면 최적화된다. 이러한 동작 파라미터들의 예들은 소거 및 프로그래밍 전압들, 및 전하 레벨들을 최적 범위 내로 가져하기 위해 블록 내에 사용자 데이터가 리프레시되는 빈도를 포함한다. 낮은 사이클 카운트들을 갖는 블록들은 낮은 프로그래밍 및 소거 전압들로 동작될 수 있으므로 이들의 유용한 수명이 늘어난다. 데이터 리프레시는 너무 자주 행해지면 성능에 악영향을 미칠 수 있으므로 낮은 사이클 카운트들을 갖는 블록들은 높은 사이클 카운트들을 갖는 블록들은 높은 사이클 카운트들을 갖는 블록들만큼 자주 리프레시되지 않는다. 사이클 카운트는, 여러 블록들의 사용에 차이들이 어떤 기설정된 범위를 초과하였을 때 논리-물리적(logical-to-physical) 블록 어드레스 테이블을 변경함으로서 개개의 블록들의 사용(마모)을 균등하게 하는데 이용될 수도 있다. 또한, 어떤 블록들이 이들의 예상 유용한 수명을 초과하는 사이클 수를 경험한다면, 이들 블록들은 시스템으로부터 영구적으로 맵될 수 있다.

- [0065] 본 발명은 구체적인 실시예들에 관하여 기술되었어도, 본 발명은 첨부된 청구항들의 전 범위 내에서 보호된다.

#### 도면의 간단한 설명

- [0027] 도 1은 본 발명이 구현될 수 있는 제1 비휘발성 메모리 시스템의 블록도이다.

- [0028] 도 2는 본 발명이 구현될 수 있는 제2 비휘발성 메모리 시스템의 블록도이다.

- [0029] 도 3은 도 1 혹은 도 2의 메모리 시스템들 중 어느 하나에 데이터를 프로그램하는데 사용될 수 있는 전압파형을 도시한 것이다.

- [0030] 도 4는 4상태들 중 한 상태로 개별적으로 프로그램된 일 그룹의 비휘발성 메모리 셀들의 전압 임계값들의 분포를 도시한 것이다.

- [0031] 도 5는 2상태들 중 한 상태로 개별적으로 프로그램된 일 그룹의 비휘발성 메모리 셀들의 전압 임계값들의 분포를 도시한 것이다.

- [0032] 도 6은 복수 페이지들을 포함하는 한 블록의 메모리 셀들의 제1 구성예를 도시한 것이다.

- [0033] 도 7은 도 6에 도시된 유형의 블록들에 저장될 수 있는 블록 오버헤드 데이터를 도시한 것이다.

- [0034] 도 8은 복수 페이지들을 포함하는 한 블록의 메모리 셀들의 제2 구성예를 도시한 것이다.

- [0035] 도 9는 블록 오버헤드 데이터를 저장할 때 도 1 혹은 도 2의 메모리 시스템들 중 어느 하나의 소거동작을 도시 한 흐름도이다.

## 도면

## 도면1

## 도면2

## 도면3

## 도면4

## 도면5

## 도면6

## 도면7

## 도면8

## 도면9