#### (19) **日本国特許庁(JP)**

# (12) 特許公報(B2)

(11)特許番号

特許第6054621号 (P6054621)

(45) 発行日 平成28年12月27日(2016.12.27)

(24) 登録日 平成28年12月9日(2016.12.9)

| (51) Int.Cl. |        |           | FI   |        |         |          |       |

|--------------|--------|-----------|------|--------|---------|----------|-------|

| HO1L 2       | 21/338 | (2006.01) | HO1L | 29/80  | Н       |          |       |

| HO1L 2       | 29/778 | (2006.01) | HO1L | 29/78  | 3 O 1 B |          |       |

| HO1L 2       | 29/812 | (2006.01) | HO1L | 21/205 |         |          |       |

| HO1L 2       | 21/336 | (2006.01) |      |        |         |          |       |

| HO1L 2       | 29/78  | (2006.01) |      |        |         |          |       |

|              |        |           |      |        | 譜求項の数 6 | (全 37 百) | 最終百に続 |

(21) 出願番号 特願2012-81975 (P2012-81975) (22) 出願日 平成24年3月30日 (2012.3.30) (65) 公開番号 特開2013-211481 (P2013-211481A) (43) 公開日 平成25年10月10日 (2013.10.10) 審査請求日 平成27年3月5日 (2015.3.5)

||(73)特許権者 514107233

トランスフォーム・ジャパン株式会社 神奈川県横浜市港北区新横浜2-5-15 新横浜センタービル9F

||(74)代理人 100079108

弁理士 稲葉 良幸

|(74)代理人 100109346

弁理士 大貫 敏史

(74)代理人 100117189

弁理士 江口 昭彦

(74)代理人 100134120

弁理士 内藤 和彦

(74)代理人 100144325

弁理士 小澁 高弘

最終頁に続く

(54) 【発明の名称】化合物半導体装置及びその製造方法

# (57)【特許請求の範囲】

### 【請求項1】

二次元電子ガスが生成される化合物半導体積層構造と、

前記化合物半導体積層構造の上方に形成されたゲート電極と

# を含み、

前記化合物半導体積層構造は、前記二次元電子ガスの生成部位の下方に p 型半導体層を有しており、

前記p型半導体層は、前記ゲート電極の直下に位置整合する部分がその他の部分よりも イオン化アクセプタ量が多く、

前記 p 型半導体層は、前記その他の部分が不活性不純物を含有することを特徴とする化合物半導体装置。

# 【請求項2】

\_二次元電子ガスが生成される化合物半導体積層構造と、

前記化合物半導体積層構造の上方に形成されたゲート電極と

#### を含み、

\_ 前記化合物半導体積層構造は、前記二次元電子ガスの生成部位の下方に p 型半導体層を 有しており、

<u>前記 p 型半導体層は、前記ゲート電極の直下に位置整合する部分がその他の部分よりも</u> イオン化アクセプタ量が多く、

前記p型半導体層は、前記その他の部分が前記イオン化アクセプタ量の多い部分よりも薄

いことを特徴とする化合物半導体装置。

#### 【請求項3】

前記 p 型半導体層は、 p - G a N、 p - A 1 G a N、 p - I n A 1 N、及び p - A 1 N から選ばれた 1 種を材料とすることを特徴とする請求項 1 <u>または 2</u> に記載の化合物半導体装置。

#### 【請求項4】

二次元電子ガスが生成される化合物半導体積層構造を形成する工程と、

前記化合物半導体積層構造の上方にゲート電極を形成する工程とを含み、

前記化合物半導体積層構造を形成する際に、前記二次元電子ガスの生成部位の下方に相当する部分にp型半導体層を形成し、

<u>前記p型半導体層は、前記ゲート電極の直下に位置整合する部分がその他の部分よりも</u>イオン化アクセプタ量が多く、

前記 p 型半導体層は、前記その他の部分が不活性不純物を含有することを特徴とする化合物半導体装置の製造方法。

#### 【請求項5】

二次元電子ガスが生成される化合物半導体積層構造を形成する工程と、

前記化合物半導体積層構造の上方にゲート電極を形成する工程と

#### を含み、

前記化合物半導体積層構造を形成する際に、前記二次元電子ガスの生成部位の下方に相当する部分にp型半導体層を形成し、

<u>前記 p 型半導体層は、前記ゲート電極の直下に位置整合する部分がその他の部分よりも</u>イオン化アクセプタ量が多く、

前記p型半導体層は、前記その他の部分が前記イオン化アクセプタ量の多い部分よりも薄いことを特徴とする化合物半導体装置の製造方法。

#### 【請求項6】

前記p型半導体層は、p-GaN、p-AlGaN、p-InAlN、及びp-AlNから選ばれた1種を材料とすることを特徴とする請求項<u>4または5</u>に記載の化合物半導体装置の製造方法。

【発明の詳細な説明】

【技術分野】

[0001]

本発明は、化合物半導体装置及びその製造方法に関する。

#### 【背景技術】

[0002]

室化物半導体装置は、高い飽和電子速度及びワイドバンドギャップ等の特徴を利用し、高耐圧及び高出力の半導体デバイスとしての開発が活発に行われている。窒化物半導体デバイスとしては、電界効果トランジスタ、特に高電子移動度トランジスタ(High Electron Mobility Transistor: HEMT)についての報告が数多くなされている。特に、GaNを電子走行層として、A1GaNを電子供給層として用いたA1GaN/GaN・HEMTが注目されている。A1GaN/GaN・HEMTでは、GaNとA1GaNとの格子定数差に起因した歪みがA1GaNに生じる。これにより発生したピエゾ分極及びA1GaNの自発分極により、高濃度の二次元電子ガス(2DEG)が得られる。そのため、高耐圧及び高出力が実現できる。

【先行技術文献】

# 【特許文献】

[0003]

【特許文献1】特公平7-93428号公報

【特許文献 2 】特開 2 0 0 8 - 1 1 2 8 6 8 号公報

【発明の概要】

20

10

30

40

#### 【発明が解決しようとする課題】

### [0004]

室化物半導体デバイスを電力用途に用いる場合には、安全動作及び既存システムとの整合性の観点から、いわゆるノーマリオフが強く求められる。ところが、例えばA1GaN / GaN・HEMTでは、その強いピエゾ分極及び自発分極の作用により電子走行層の電子濃度が非常に高く、ノーマリオフの実現が比較的難しい。現在、ノーマリオフ化のためには様々な手法が検討されており、化合物半導体層に形成したリセスを埋め込むようにゲート電極を形成したゲートリセス構造、化合物半導体層とゲート電極との間にp-GaN層を形成したp-GaNキャップ構造等の様々な構造が提案されている。その中でも、p-GaNキャップ構造は、p型半導体層によるエネルギーバンドの持ち上げ効果を用いることにより、閾値の正方向へのシフトが大きく、ノーマリオフ化に適していることが知られている。

#### [0005]

しかしながら、p-GaNキャップ構造においては、p-GaN層の挿入により、必ずゲート電極と2DEGの生成部位との距離が増加するため、ピンチオフ特性の劣化、gmの低下を惹起するという問題があった。また更に、横方向の導電性を確保するため、ゲート電極の直下以外に位置するp-GaN層を除去する必要があるところ、この除去時のエッチングダメージにより、電流コラプス等のトラップ起因の特性劣化を惹起するという問題があった。

# [0006]

本発明は、上記の課題に鑑みてなされたものであり、電流コラプス等のトラップ起因の特性劣化を防止し、ピンチオフ特性及びgmを向上させるも、確実なノーマリオフを実現する信頼性の高い化合物半導体装置及びその製造方法を提供することを目的とする。

# 【課題を解決するための手段】

#### [0007]

化合物半導体装置の一態様は、二次元電子ガスが生成される化合物半導体積層構造と、前記化合物半導体積層構造の上方に形成された電極とを含み、前記化合物半導体積層構造は、前記二次元電子ガスの生成部位の下方に p 型半導体層を有しており、前記 p 型半導体層は、前記電極の下方に位置整合する部分がその他の部分よりもイオン化アクセプタ量が多い。

#### [0008]

化合物半導体装置の製造方法の一態様は、二次元電子ガスが生成される化合物半導体積層構造を形成する工程と、前記化合物半導体積層構造の上方に電極を形成する工程とを含み、前記化合物半導体積層構造を形成する際に、前記二次元電子ガスの生成部位の下方に相当する部分にp型半導体層を形成し、前記p型半導体層は、前記電極の下方に位置整合する部分がその他の部分よりもイオン化アクセプタ量が多い。

# 【発明の効果】

#### [0009]

上記の諸態様によれば、電流コラプス等のトラップ起因の特性劣化を防止し、ピンチオフ特性及びgmを向上させるも、確実なノーマリオフを実現する信頼性の高い化合物半導体装置が得られる。

#### 【図面の簡単な説明】

#### [0010]

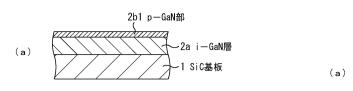

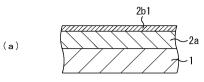

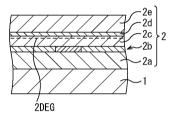

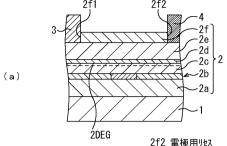

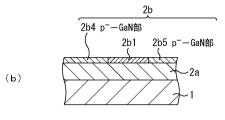

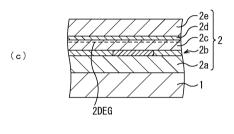

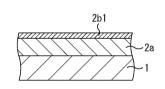

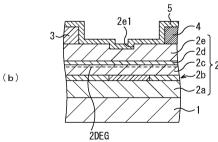

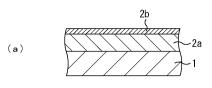

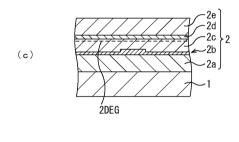

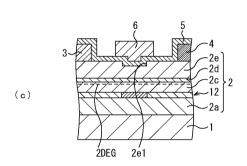

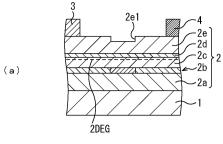

【図1】第1の実施形態によるAlGaN/GaN・HEMTの製造方法を工程順に示す概略断面図である。

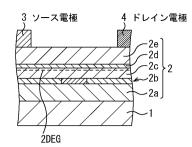

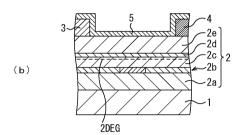

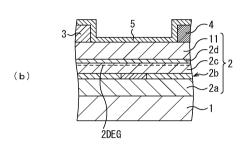

【図2】図1に引き続き、第1の実施形態によるAlGaN/GaN・HEMTの製造方法を工程順に示す概略断面図である。

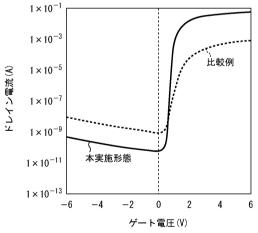

【図3】第1の実施形態によるAlGaN/GaN・HEMTにおける代表的な伝達特性 (ドレイン電流・ゲート電圧特性)について、従来のp・GaNキャップ構造を採用した 比較例のAlGaN/GaN・HEMTとの比較に基づいて調べた結果を示す特性図であ 10

20

30

40

る。

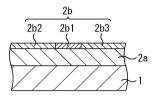

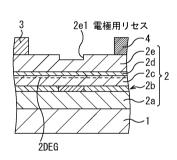

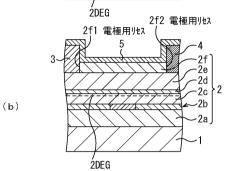

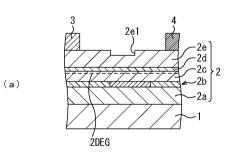

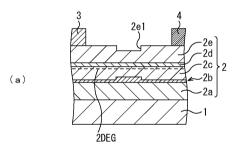

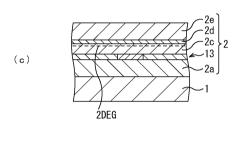

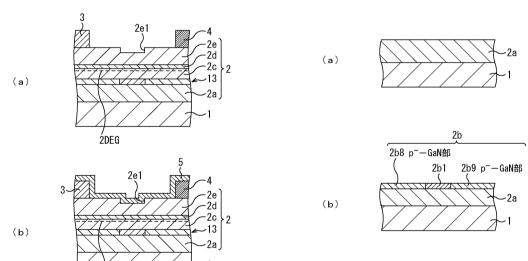

- 【図4】第2の実施形態によるA1GaN/GaN・HEMTの製造方法を工程順に示す 概略断面図である。

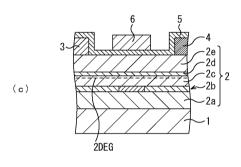

- 【図5】図4に引き続き、第2の実施形態によるAlGaN/GaN・HEMTの製造方 法を工程順に示す概略断面図である。

- 【図6】第3の実施形態によるA1GaN/GaN・HEMTの製造方法を工程順に示す 概略断面図である。

- 【図7】図6に引き続き、第3の実施形態によるA1GaN/GaN・HEMTの製造方 法を工程順に示す概略断面図である。

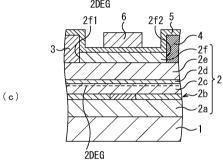

- 【図8】第4の実施形態によるA1GaN/GaN・HEMTの製造方法を工程順に示す 概略断面図である。

- 【図9】図8に引き続き、第4の実施形態によるAlGaN/GaN・HEMTの製造方 法を工程順に示す概略断面図である。

- 【図10】第5の実施形態によるA1GaN/GaN・HEMTの製造方法を工程順に示 す概略断面図である。

- 【図11】図10に引き続き、第5の実施形態によるAlGaN/GaN・HEMTの製 造方法を工程順に示す概略断面図である。

- 【図12】第6の実施形態によるInAlN/GaN・HEMTの製造方法を工程順に示 す概略断面図である。

- 【図13】図12に引き続き、第6の実施形態によるInAlN/GaN・HEMTの製 造方法を工程順に示す概略断面図である。

- 【図14】第7の実施形態によるA1GaN/GaN・HEMTの製造方法を工程順に示 す概略断面図である。

- 【図15】図14に引き続き、第7の実施形態によるAlGaN/GaN・HEMTの製 造方法を工程順に示す概略断面図である。

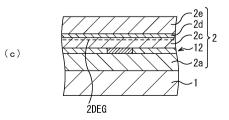

- 【図16】第8の実施形態によるA1GaN/GaN・HEMTの製造方法を工程順に示 す概略断面図である。

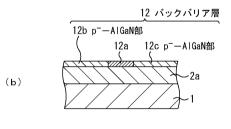

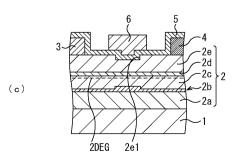

- 【図17】図16に引き続き、第8の実施形態によるAlGaN/GaN・HEMTの製 造方法を工程順に示す概略断面図である。

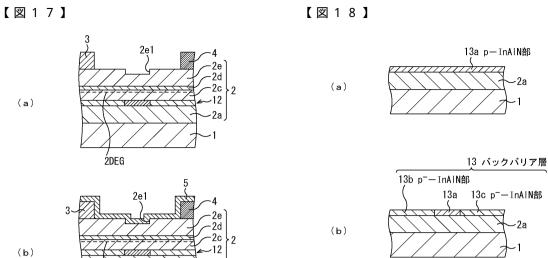

- 【図18】第9の実施形態によるA1GaN/GaN・HEMTの製造方法を工程順に示 す概略断面図である。

- 【図19】図18に引き続き、第9の実施形態によるAlGaN/GaN・HEMTの製 造方法を工程順に示す概略断面図である。

- 【図20】第10の実施形態によるAlGaN/GaN・HEMTの製造方法を工程順に 示す概略断面図である。

- 【図21】図20に引き続き、第10の実施形態によるAlGaN/GaN・HEMTの 製造方法を工程順に示す概略断面図である。

- 【図22】第1~第10の実施形態から選ばれたHEMTを用いたHEMTチップを示す 概略平面図である。

- 40 【図23】第1~第10の実施形態から選ばれたHEMTを用いたHEMTチップのディ スクリートパッケージを示す概略平面図である。

- 【図24】第11の実施形態によるPFC回路を示す結線図である。

- 【図25】第12の実施形態による電源装置の概略構成を示す結線図である。

- 【図26】第13の実施形態による高周波増幅器の概略構成を示す結線図である。

【発明を実施するための形態】

[0011]

以下、諸実施形態について図面を参照して詳細に説明する。以下の諸実施形態では、化合 物半導体装置の構成について、その製造方法と共に説明する。

なお、以下の図面において、図示の便宜上、相対的に正確な大きさ及び厚みに示してい ない構成部材がある。

10

20

30

#### [0012]

(第1の実施形態)

本実施形態では、化合物半導体装置としてショットキー型のAIGaN/GaN・HEMTを開示する。

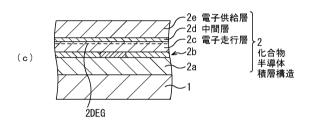

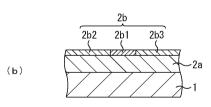

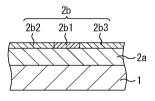

図1及び図2は、第1の実施形態によるAlGaN/GaN・HEMTの製造方法を工程順に示す概略断面図である。

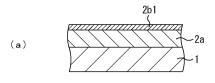

#### [0013]

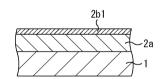

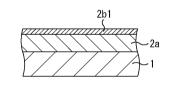

先ず、図1(a)に示すように、成長用基板として例えば半絶縁性のSiC基板1上に、i(インテンショナリ・アンドープ)-GaN層2a及びp-GaN部2b1となるp-GaN層を順次形成する。

成長用基板としては、SiC基板の代わりに、Si基板、サファイア基板、GaAs基板、GaN基板等を用いても良い。また、基板の導電性としては、半絶縁性、導電性を問わない。

# [0014]

SiC基板1上に、例えば有機金属気相成長(MOVPE: Metal Organic Vapor Phase Epitaxy)法により、i-GaN層2a及びp-GaN部2b1となるp-GaN層を順次成長する。MOVPE法の代わりに、分子線エピタキシー(MBE: Molecular Beam Epitaxy)法等を用いても良い。

i - GaN層2aは、i - GaNを例えば3 $\mu$ m程度の厚みに成長することで形成される。 p - GaN部2b1となるp - GaN層は、p - GaNを例えば50nm程度の厚みに成長することで形成される。

#### [0015]

GaNの成長には、原料ガスとしてGa源であるトリメチルガリウム(TMGa)ガス及びアンモニア(NH $_3$ )ガスの混合ガスを用いる。 TMGaガスの流量は適宜設定し、NH $_3$ ガスの流量は、100sccm~10slm程度とする。また、成長圧力は50Torr~300Torr程度、成長温度は1000~1200 程度とする。

#### [0016]

$GaNをp型として成長する際、即ちp-GaN部2b1となるp-GaN層の形成には、p型不純物であるMg、C、Zn等、例えばMgをGaNの原料ガスに添加する。ここでは、例えばMgを含む例えばCp2Mgガスを所定の流量で原料ガスに添加し、GaNにMgをドーピングする。Mgのドーピング濃度は、<math>1\times10^{16}/cm^3$ 程度~ $1\times10^{21}/cm^3$ 程度、例えば  $1\times10^{19}/cm^3$ 程度とする。

p - G a N 層を形成した後、400 ~ 1200 程度、例えば800 程度でp - G a N 層を熱処理し、p 型不純物である M g を活性化する。

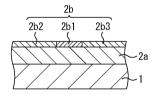

#### [0017]

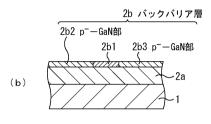

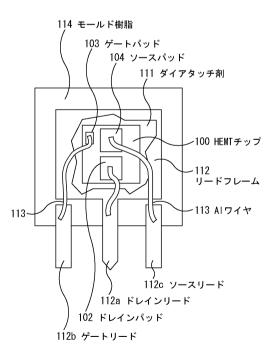

続いて、図1(b)に示すように、バックバリア層2bを形成する。

先ず、p-GaN層上にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、p-GaN層のゲート電極の形成予定位置の下方に位置整合する部分(p-GaN部2b1となる部分)を覆い、他の部分を開口するレジストマスクが形成される

#### [0018]

以上により、ゲート電極の形成予定位置の下方に位置整合する部分に形成されたp-G

10

20

30

40

a N 部 2 b 1 と、 p - G a N 部 2 b 1 の両側に形成された  $p^-$  - G a N 部 2 b 2 , 2 b 3 とを有するバックバリア層 2 b が形成される。バックバリア層 2 b では、 p - G a N 部 2 b 1 は、  $p^-$  - G a N 部 2 b 2 , 2 b 3 よりもイオン化アクセプタ量が多い、ここではイオン化アクセプタ濃度が高い部分となる。

### [0019]

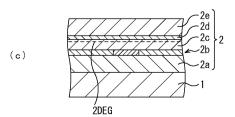

続いて、図1(c)に示すように、バックバリア層2b上に、電子走行層2c、中間層2d、及び電子供給層2eを順次形成する。

MOVPE法により、バックバリア層2b上に、電子走行層2c、中間層2d、及び電子供給層2eとなる各化合物半導体を順次成長する。電子走行層2cは、i-GaNを100nm程度の厚みに成長することで形成される。中間層2dは、i-AlGaNを5nm程度の厚みに成長することで形成される。電子供給層2eは、n-AlGaNを30nm程度の厚みに成長することで形成される。中間層2dは形成しない場合もある。電子供給層は、i-AlGaNを形成するようにしても良い。

### [0020]

GaNの成長には、原料ガスとして <math>Ga源であるトリメチルガリウム( TMGa)ガス及びアンモニア(  $NH_3$ )ガスの混合ガスを用いる。 AlGaNの成長には、原料ガスとして TMAl ガス、 TMGa ガスの混合ガスを用いる。成長する化合物半導体層に応じて、 TMAl ガス、 TMGa ガスの供給の有無及び流量を適宜設定する。共通原料である  $NH_3$  ガスの流量は、 100 s c c m  $\sim 10$  s 1 m程度とする。また、成長圧力は 50 Torr  $\sim 300$  Torr 程度、成長温度は 1000  $\sim 1200$  程度とする。

#### [0021]

AlgaNをn型として成長する際、即ち電子供給層 2e(n-AlgaN)の形成には、n型不純物をAlgaNの原料ガスに添加する。ここでは、例えば<math>Siを含む例えばシラン( $SiH_4$ )ガスを所定の流量で原料ガスに添加し、AlgaNにSiをドーピングする。Siのドーピング濃度は、 $1 \times 10^{18}$  /  $cm^3$ 程度~ $1 \times 10^{20}$  /  $cm^3$ 程度、例えば  $5 \times 10^{18}$  /  $cm^3$ 程度とする。

以上により、i-GaN層2a、バックバリア層2b、電子走行層2c、中間層2d、及び電子供給層2eが順次積層されてなる化合物半導体積層構造2が形成される。

### [0022]

続いて、素子分離構造を形成する。

詳細には、化合物半導体積層構造2の素子分離領域に例えばアルゴン(Ar)を注入する。これにより、化合物半導体積層構造2及びSiC基板1の表層部分に素子分離構造が形成される。素子分離構造により、化合物半導体積層構造2上で活性領域が画定される。

なお、素子分離は、上記の注入法の代わりに、例えばSTI(Shallow Trench Isolation)法を用いて行っても良い。

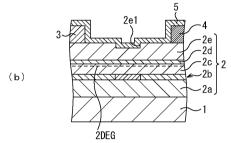

### [0023]

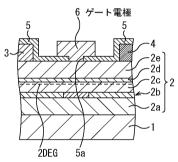

続いて、図2(a)に示すように、ソース電極3及びドレイン電極4を形成する。

電極材料として例えばTa/A1(下層がTa、上層がA1)を用いる。電極形成には、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを化合物半導体積層構造2上に塗布し、ソース電極及びドレイン電極の各形成予定位置を開口するレジストマスクを形成する。このレジストマスクを用いて、例えば蒸着法により、Ta/A1を堆積する。Taの厚みは20nm程度、A1の厚みは200nm程度とする。リフトオフ法により、庇構造のレジストマスク及びその上に堆積したTa/A1を除去する。その後、SiC基板1を、例えば窒素雰囲気中において400 ~1000 、例えば550 程度で熱処理し、残存したTa/A1を電子供給層2eとオーミックコンタクトさせる。なお、Ta/A1が熱処理を行わずとも電子供給層2eとオーミックコンタクトする場合には、当該熱処理を行わなくても良い。以上により、Ta/A1からなるソース電極3及びドレイン電極4が形成される。

### [0024]

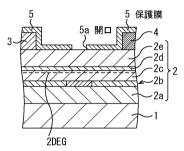

続いて、図2(b)に示すように、化合物半導体積層構造2の表面に、開口5aを有す

20

10

30

40

る保護膜5を形成する。

詳細には、先ず、ソース電極3上及びドレイン電極4上を含む化合物半導体積層構造2の全面にSiNを、プラズマCVD法又はスパッタ法等により例えば2nm程度~200nm、例えば20nm程度の厚みに堆積する。以上により、保護膜5が形成される。

### [0025]

次に、保護膜5の全面にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、保護膜5のゲート電極の形成予定位置を露出する開口を有するレジストマスクが形成される。

このレジストマスクを用いて、保護膜 5 を例えばフッ素系ガスをエッチングガスとして用いてドライエッチングする。これにより、保護膜 5 のゲート電極の形成予定位置に開口 5 a が形成される。レジストマスクは、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

#### [0026]

続いて、図2(c)に示すように、ゲート電極6を形成する。

電極材料として例えばNi/Au(下層がNi、上層がAu)を用いる。電極形成には、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを開口5a内を含む保護膜5上に塗布し、開口5aを含むゲート電極の形成予定位置を開口するレジストマスクを形成する。このレジストマスクを用いて、例えば蒸着法により、Ni/Auを堆積する。Niの厚みは30nm程度、Auの厚みは400nm程度とする。リフトオフ法により、庇構造のレジストマスク及びその上に堆積したNi/Auを除去する。これにより、開口5a内をゲートメタルで埋め込み化合物半導体積層構造2の表面とショットキー接触する、ゲート電極6が形成される。ゲート電極6は、開口5a内を埋め込み保護膜5上に乗り上げるNiと、Ni上に堆積したAuとから、いわゆるオーバーハング形状に形成される。

#### [0027]

しかる後、ソース電極3及びドレイン電極4、ゲート電極6の電気的接続等の諸工程を経て、ショットキー型のA1GaN/GaN・HEMTが形成される。

#### [0028]

本実施形態によるA1GaN/GaN・HEMTでは、化合物半導体積層構造2の2DEGの生成部位の下方にバックバリア層2bが形成されている。バックバリア層2bのイオン化アクセプタ濃度の比較的高いp-GaN部2b1により、確実なノーマリオフが実現する。更に、バックバリア層2bの形成位置が2DEGの生成部位の下方であることから、ゲート電極6と2DEGとの距離が短く保持され、gmが向上する。また、化合物半導体積層構造2の表面には、ドライエッチングしないためにエッチングダメージはなく、エッチングダメージに起因したトラップ起因の現象(電流コラプス等)も抑制される。

#### [0029]

バックバリア層 2 b は、 p - G a N 部 2 b 1 の両側に p - G a N 部 2 b 2 , 2 b 3 を 有している。従来の p - G a N キャップ構造、即ちチャネル直下に p - G a N を埋め込み、水平方向の濃度変調を施す構造においては、構造的に必ず再成長のプロセスが必須であり、再成長界面が存在する。この界面は、一旦結晶成長装置の外の雰囲気に曝されることもあり、様々な欠陥の原因となる。デバイスの高電圧動作時には、この欠陥がリークパスとなり、電源オフ時のリーク電流が増加することが懸念される。本実施形態では、電極間(即ちゲート電極 6 の直下以外の、ソース電極 3 - ゲート電極 6 間、ゲート電極 6 - ドレイン電極 4 間)の下方に位置整合する p - G a N 部 2 b 2 , 2 b 3 の存在により、再成長界面のリークパスが低減され、良好なピンチオフ特性を得ることができる。

# [0030]

本実施形態によるA1GaN/GaN・HEMTにおける代表的な伝達特性(ドレイン電流・ゲート電圧特性)について、従来のp-GaNキャップ構造を採用した比較例のA 1GaN/GaN・HEMTとの比較に基づいて調べた。その結果を図3に示す。

# [0031]

50

40

10

20

比較例では、ピンチオフ時のリーク電流が大きく、最大ドレイン電流(Id<sub>max</sub>)が小さいという問題がある。これに対して本実施形態では、ゲート電極と2DEGとの距離低減及び再成長界面のリークパス低減により、良好なピンチオフ特性が得られていることが判る。

# [0032]

以上説明したように、本実施形態によれば、電流コラプス等のトラップ起因の特性劣化を防止し、ピンチオフ特性及びgmを向上させるも、確実なノーマリオフを実現する信頼性の高いAIGaN/BaN・HEMTが得られる。

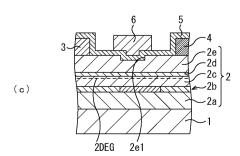

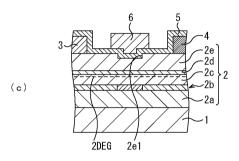

#### [0033]

(第2の実施形態)

本実施形態では、化合物半導体装置としてMIS型のAlGaN/GaN・HEMTを 開示する。

なお、第1の実施形態によるAIGaN/GaN・HEMTと同様の構成部材等については、同符号を付して詳しい説明を省略する。

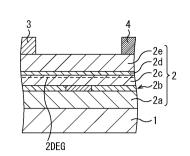

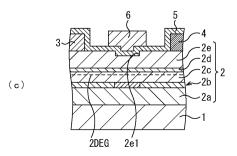

図4及び図5は、第2の実施形態によるA1GaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

#### [0034]

先ず、図 4 ( a )~図 5 ( a )に示すように、第 1 の実施形態の図 1 ( a )~図 2 ( a )の諸工程を経る。このとき、図 5 ( a )に示すように、ソース電極 3 及びドレイン電極 4 が形成される。

#### [0035]

続いて、図 5 ( b ) に示すように、化合物半導体積層構造 2 の表面に保護膜 5 を形成する。

詳細には、ソース電極3上及びドレイン電極4上を含む化合物半導体積層構造2の全面にSiNを、プラズマCVD法又はスパッタ法等により例えば2nm程度~200nm、例えば20nm程度の厚みに堆積する。以上により、保護膜5が形成される。本実施形態では、保護膜5はゲート絶縁膜としても機能する。

#### [0036]

続いて、図5(c)に示すように、ゲート電極6を形成する。

電極材料として例えばNi/Au(下層がNi、上層がAu)を用いる。電極形成には、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを保護膜5上に塗布し、ゲート電極の形成予定位置を開口するレジストマスクを形成する。このレジストマスクを用いて、例えば蒸着法により、Ni/Auを堆積する。Niの厚みは30nm程度、Auの厚みは400nm程度とする。リフトオフ法により、庇構造のレジストマスク及びその上に堆積したNi/Auを除去する。これにより、保護膜5上にゲート電極6が形成される。

# [0037]

しかる後、ソース電極3及びドレイン電極4、ゲート電極6の電気的接続等の諸工程を経て、MIS型のAlGaN/GaN・HEMTが形成される。

# [0038]

以上説明したように、本実施形態によれば、電流コラプス等のトラップ起因の特性劣化を防止し、ピンチオフ特性及びgmを向上させるも、確実なノーマリオフを実現する信頼性の高いAlGaN/GaN・HEMTが得られる。

# [0039]

(第3の実施形態)

本実施形態では、化合物半導体装置としてMIS型のAlGaN/GaN・HEMTを 開示する。

なお、第1の実施形態によるAlGaN/GaN・HEMTと同様の構成部材等については、同符号を付して詳しい説明を省略する。

図 6 及び図 7 は、第 3 の実施形態による A 1 G a N / G a N・H E M T の製造方法にお

10

20

30

40

20

30

40

50

ける主要工程を示す概略断面図である。

#### [0040]

先ず、図6(a)~図6(c)に示すように、第1の実施形態の図1(a)~図1(c)の諸工程を経る。このとき、図6(c)に示すように、化合物半導体積層構造2が形成される。

#### [0041]

続いて、素子分離構造を形成した後、図7(a)に示すように、電子供給層4eに電極用リセス4e1を形成した後、ソース電極3及びドレイン電極4を形成する。

詳細には、先ず、化合物半導体積層構造2の全面にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、電子供給層4eにおけるゲート電極の形成予定位置を露出する開口を有するレジストマスクが形成される。

このレジストマスクを用いて、電子供給層2eの表層の一部を、例えばフッ素系ガスをエッチングガスとして用いてドライエッチングする。これにより、電子供給層2eのゲート電極の形成予定位置に電極用リセス4e1が形成される。レジストマスクは、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

#### [0042]

次に、電極材料として例えばTa/A1(下層がTa、上層がA1)を用いる。電極形成には、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを化合物半導体積層構造2上に塗布し、ソース電極及びドレイン電極の各形成予定位置を開口するレジストマスクを形成する。このレジストマスクを用いて、例えば蒸着法により、Ta/A1を堆積する。Taの厚みは20nm程度、A1の厚みは200nm程度とする。リフトオフ法により、庇構造のレジストマスク及びその上に堆積したTa/A1を除去する。その後、SiC基板1を、例えば窒素雰囲気中において400~1000、例えば550 程度で熱処理し、残存したTa/A1を電子供給層2eとオーミックコンタクトさせる。なお、Ta/A1が熱処理を行わずとも電子供給層2eとオーミックコンタクトする場合には、当該熱処理を行わなくても良い。以上により、Ta/A1からなるソース電極3及びドレイン電極4が形成される。

#### [0043]

続いて、図 7 ( b ) に示すように、化合物半導体積層構造 2 の表面に保護膜 5 を形成する。

詳細には、ソース電極 3 上及びドレイン電極 4 上を含む化合物半導体積層構造 2 の全面に S i N を、プラズマ C V D 法又はスパッタ法等により例えば 2 n m程度 ~ 2 0 0 n m、例えば 2 0 n m程度の厚みに堆積する。以上により、保護膜 5 が形成される。本実施形態では、保護膜 5 はゲート絶縁膜としても機能する。

# [0044]

続いて、図7(c)に示すように、ゲート電極6を形成する。

電極材料として例えばNi/Au(下層がNi、上層がAu)を用いる。電極形成には、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを保護膜5上に塗布し、ゲート電極の形成予定位置を開口するレジストマスクを形成する。このレジストマスクを用いて、例えば蒸着法により、Ni/Auを堆積する。Niの厚みは30nm程度、Auの厚みは400nm程度とする。リフトオフ法により、庇構造のレジストマスク及びその上に堆積したNi/Auを除去する。これにより、電極用リセス4e1内を保護膜5を介してゲートメタルで埋め込むゲート電極6が形成される。ゲート電極6は、保護膜5を介して電極用リセス4e1内を埋め込み保護膜5上に乗り上げるNiと、Ni上に堆積したAuとから、いわゆるオーバーハング形状に形成される。

# [0045]

しかる後、ソース電極3及びドレイン電極4、ゲート電極6の電気的接続等の諸工程を経て、MIS型のAlGaN/GaN・HEMTが形成される。

#### [0046]

以上説明したように、本実施形態によれば、電流コラプス等のトラップ起因の特性劣化

を防止し、ピンチオフ特性及びgmを向上させるも、確実なノーマリオフを実現する信頼性の高いAlGaN/GaN・HEMTが得られる。

#### [0047]

(第4の実施形態)

本実施形態では、化合物半導体装置としてMIS型のAlGaN/GaN・HEMTを 開示する。

なお、第1の実施形態によるAlGaN/GaN・HEMTと同様の構成部材等については、同符号を付して詳しい説明を省略する。

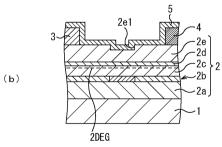

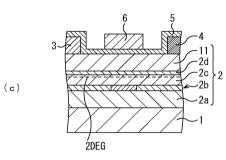

図8及び図9は、第4の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

[0048]

先ず、図 8 ( a ) ~ 図 8 ( b ) に示すように、第 1 の実施形態の図 1 ( a ) ~ 図 1 ( b ) の諸工程を経る。このとき、図 8 ( b ) に示すように、バックバリア層 2 b が形成される。

[0049]

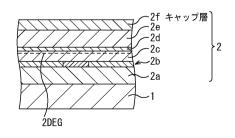

続いて、図8(c)に示すように、バックバリア層2b上に、電子走行層2c、中間層 2d、及び電子供給層2e、キャップ層2fを順次形成する。

MOVPE法により、バックバリア層 2 b 上に、電子走行層 2 c 、中間層 2 d 、電子供給層 2 e 、及びキャップ層 2 f となる各化合物半導体を順次成長する。電子走行層 2 c は、i - G a Nを 1 0 0 n m程度の厚みに成長することで形成される。中間層 2 d は、i - A 1 G a Nを 5 n m程度の厚みに成長することで形成される。電子供給層 2 e は、n - A 1 G a Nを 3 0 n m程度の厚みに成長することで形成される。キャップ層 2 f は、n - G a Nを 1 0 n m程度の厚みに成長することで形成される。中間層 2 d は形成しない場合もある。電子供給層は、i - A 1 G a Nを形成するようにしても良い。

[0050]

GaNの成長には、原料ガスとして <math>Ga源である TMGaガス及  $VNH_3$ ガスの混合ガスを用いる。 AlGaNの成長には、原料ガスとして TMAl ガス、 TMGaガス及  $VNH_3$ ガスの混合ガスを用いる。成長する化合物半導体層に応じて、 TMAl ガス、 TMGa ある  $VNH_3$  ガスの供給の有無及  $VNH_3$  が、量を適宜設定する。 共通原料である  $VNH_3$  が、  $VNH_3$  が、 VNH

[0051]

Al GaN、GaNをn型として成長する際、即ち電子供給層2e(n-Al GaN)及びキャップ層2f(n-GaN)の形成には、n型不純物をAl GaN、GaNの原料ガスに添加する。ここでは、例えばSiを含む例えばシラン(Si H<sub>4</sub>)ガスを所定の流量で原料ガスに添加し、Al GaN、GaNにSiをドーピングする。Siのドーピング濃度は、1 x 1 0  $^{18}$  / c m  $^{3}$ 程度~1 x 1 0  $^{20}$  / c m  $^{3}$ 程度、例えば5 x 1 0  $^{18}$  / c m  $^{3}$ 程度とする。

以上により、i-GaN層2a、バックバリア層2b、電子走行層2c、中間層2d、電子供給層2e、及びキャップ層2fが順次積層されてなる化合物半導体積層構造2が形成される。

[0052]

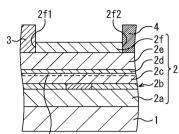

続いて、素子分離構造を形成した後、図9(a)に示すように、ソース電極3及びドレイン電極4を形成する。

詳細には、先ず、化合物半導体積層構造 2 の全面にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、電子供給層 4 e におけるソース電極及びドレイン電極の各形成予定位置を露出する開口を有するレジストマスクが形成される。

このレジストマスクを用いて、電子供給層 2 e の表面が露出するまで、例えばフッ素系ガスをエッチングガスとして用いてキャップ層 2 f をドライエッチングする。これにより、キャップ層 2 f ソース電極及びドレイン電極の各形成予定位置に電極用リセス 2 f 1 ,

10

20

30

40

2 f 2 が形成される。レジストマスクは、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

# [0053]

次に、電極材料として例えばTa/A1(下層がTa、上層がA1)を用いる。電極形成には、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを化合物半導体積層構造2上に塗布し、電極用リセス2f1,2f2を露出する開口を有するレジストマスクを形成する。このレジストマスクを用いて、例えば蒸着法により、Ta/A1を堆積する。Taの厚みは20nm程度、A1の厚みは200nm程度とする。リフトオフ法により、庇構造のレジストマスク及びその上に堆積したTa/A1を除去する。その後、SiC基板1を、例えば窒素雰囲気中において400~~1000 、例えば550 程度で熱処理し、残存したTa/A1を電子供給層2eとオーミックコンタクトさせる。なお、Ta/A1が熱処理を行わずとも電子供給層2eとオーミックコンタクトする場合には、当該熱処理を行わなくても良い。以上により、電極用リセス2f1,2f2を埋め込むように、Ta/A1からなるソース電極3及びドレイン電極4が形成される。

#### [0054]

続いて、図9(b)に示すように、化合物半導体積層構造2の表面に保護膜5を形成する。

詳細には、ソース電極 3 上及びドレイン電極 4 上を含む化合物半導体積層構造 2 の全面に S i Nを、プラズマ C V D 法又はスパッタ法等により例えば 2 n m程度 ~ 2 0 0 n m、例えば 2 0 n m程度の厚みに堆積する。以上により、保護膜 5 が形成される。本実施形態では、保護膜 5 はゲート絶縁膜としても機能する。

#### [0055]

続いて、図9(c)に示すように、ゲート電極6を形成する。

電極材料として例えばNi/Au(下層がNi、上層がAu)を用いる。電極形成には、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを保護膜5上に塗布し、ゲート電極の形成予定位置を開口するレジストマスクを形成する。このレジストマスクを用いて、例えば蒸着法により、Ni/Auを堆積する。Niの厚みは30nm程度、Auの厚みは400nm程度とする。リフトオフ法により、庇構造のレジストマスク及びその上に堆積したNi/Auを除去する。これにより、保護膜5上にゲート電極6が形成される。

# [0056]

しかる後、ソース電極3及びドレイン電極4、ゲート電極6の電気的接続等の諸工程を経て、MIS型のAlGaN/GaN・HEMTが形成される。

# [0057]

以上説明したように、本実施形態によれば、電流コラプス等のトラップ起因の特性劣化を防止し、ピンチオフ特性及びgmを向上させるも、確実なノーマリオフを実現する信頼性の高いAIGaN・HEMTが得られる。

### [0058]

(第5の実施形態)

本実施形態では、化合物半導体装置としてMIS型のAlGaN/GaN・HEMTを 聞示する。

なお、第1の実施形態によるAlGaN/GaN・HEMTと同様の構成部材等については、同符号を付して詳しい説明を省略する。

図10及び図11は、第5の実施形態によるA1GaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

#### [0059]

先ず、図10(a)に示すように、第1の実施形態の図1(a)の工程を実行し、SiC基板1上に、i-GaN層2a及びp-GaN部2b1となるp-GaN層が順次形成される。

10

20

30

40

#### [0060]

続いて、図10(b)に示すように、バックバリア層2bを形成する。

先ず、p-GaN層上にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、p-GaN層のゲート電極の形成予定位置の下方に位置整合する部分(p-GaN部2b1となる部分)を覆い、他の部分を開口するレジストマスクが形成される。本実施形態では、レジストマスクで覆われるp-GaN層の部分は、ゲート電極の形成予定位置の下方に位置整合する部分を含み、ドレイン電極の形成予定位置に位置整合する部分に偏倚するように延在している。

# [0061]

このレジストマスクを用いて、p - G a N の p 型不純物を不活性する不純物、例えばアルゴン(A r )を加速エネルギー 1 5 k e V 、ドーズ量 1  $\times$  1 0 14 / c  $m^2$  の条件でイオン注入する。不活性不純物として、A r 以外にホウ素(B ),酸素(O ),リン(P ),鉄(F e )等を用いても良い。このイオン注入により、p - G a N 層のゲート電極の形成予定位置以外の部分が不活性し、p - G a N となって p - G a N 部 2 b 4 ,2 b 5 が形成される。p - G a N 部 2 b 5 ,2 b 5 は、イオン化アクセプタ濃度がp - G a N 部 2 b 1 よりも低濃度である。レジストマスクは、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

#### [0062]

以上により、ゲート電極の形成予定位置の下方に位置整合する部分に形成されたp-GaN部2b1と、p-GaN部2b1の両側に形成されたp-GaN部2b4,2b5とを有するバックバリア層2bが形成される。バックバリア層2bでは、p-GaN部2b1は、p-GaN部2b1は、p-GaN部2b1は、p-GaN部2b1は、ゲート電極の形成予定位置の下方に位置整合する部分を含み、ドレイン電極の形成予定位置に位置整合する部分に偏倚するように延在している。

#### [0063]

続いて、図10(c)に示すように、バックバリア層2b上に、電子走行層2c、中間層2d、及び電子供給層2eを順次形成する。

MOVPE法により、バックバリア層2b上に、電子走行層2c、中間層2d、及び電子供給層2eとなる各化合物半導体を順次成長する。電子走行層2cは、<math>i-GaNを100nm程度の厚みに成長することで形成される。中間層2dは、<math>i-AlGaNを5nm程度の厚みに成長することで形成される。電子供給層2eは、<math>n-AlGaNを30nm程度の厚みに成長することで形成される。中間層2dは形成しない場合もある。電子供給層は、<math>i-AlGaNを形成するようにしても良い。

# [0064]

GaNの成長には、原料ガスとして<math>Ga源であるトリメチルガリウム(TMGa)ガス及びアンモニア( $NH_3$ )ガスの混合ガスを用いる。 $AlGaNの成長には、原料ガスとして TMAlガス、 TMGaガス及び<math>NH_3$ ガスの混合ガスを用いる。成長する化合物半導体層に応じて、 TMAlガス、 TMGaガスの供給の有無及び流量を適宜設定する。共通原料である $NH_3$ ガスの流量は、 100sccm-10slm程度とする。また、成長圧力は <math>50Torr-300Torr程度、成長温度は 1000-71200 程度とする。

#### [0065]

AlGaNをn型として成長する際、即ち電子供給層 2e(n-AlGaN)の形成には、n型不純物をAlGaNの原料ガスに添加する。ここでは、例えば<math>Siを含む例えばシラン( $SiH_4$ )ガスを所定の流量で原料ガスに添加し、AlGaNCSiをドーピングする。Siのドーピング濃度は、 $1 \times 10^{18}$ / $cm^3$ 程度~ $1 \times 10^{20}$ / $cm^3$ 程度、例えば $5 \times 10^{18}$ / $cm^3$ 程度とする。

以上により、i - GaN層2a、バックバリア層2b、電子走行層2c、中間層2d、及び電子供給層2eが順次積層されてなる化合物半導体積層構造2が形成される。

# [0066]

50

40

10

20

続いて、素子分離構造を形成した後、図11(a)に示すように、電子供給層4eに電極用リセス4e1を形成した後、ソース電極3及びドレイン電極4を形成する。

詳細には、先ず、化合物半導体積層構造 2 の全面にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、電子供給層 4 e におけるゲート電極の形成予定位置を露出する開口を有するレジストマスクが形成される。

このレジストマスクを用いて、電子供給層2eの表層の一部を、例えばフッ素系ガスをエッチングガスとして用いてドライエッチングする。これにより、電子供給層2eのゲート電極の形成予定位置に電極用リセス4e1が形成される。レジストマスクは、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

#### [0067]

次に、電極材料として例えばTa/A1(下層がTa、上層がA1)を用いる。電極形成には、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを化合物半導体積層構造2上に塗布し、ソース電極及びドレイン電極の各形成予定位置を開口するレジストマスクを形成する。このレジストマスクを用いて、例えば蒸着法により、Ta/A1を堆積する。Taの厚みは20nm程度、A1の厚みは200nm程度とする。リフトオフ法により、庇構造のレジストマスク及びその上に堆積したTa/A1を除去する。その後、SiC基板1を、例えば窒素雰囲気中において400~1000、例えば550 程度で熱処理し、残存したTa/A1を電子供給層2eとオーミックコンタクトさせる。なお、Ta/A1が熱処理を行わずとも電子供給層2eとオーミックコンタクトする場合には、当該熱処理を行わなくても良い。以上により、Ta/A1からなるソース電極3及びドレイン電極4が形成される。

#### [0068]

続いて、図11(b)に示すように、化合物半導体積層構造2の表面に保護膜5を形成する。

詳細には、ソース電極3上及びドレイン電極4上を含む化合物半導体積層構造2の全面にSiNを、プラズマCVD法又はスパッタ法等により例えば2nm程度~200nm、例えば20nm程度の厚みに堆積する。以上により、保護膜5が形成される。本実施形態では、保護膜5はゲート絶縁膜としても機能する。

### [0069]

続いて、図11(c)に示すように、ゲート電極6を形成する。

電極材料として例えばNi/Au(下層がNi、上層がAu)を用いる。電極形成には、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを保護膜5上に塗布し、ゲート電極の形成予定位置を開口するレジストマスクを形成する。このレジストマスクを用いて、例えば蒸着法により、Ni/Auを堆積する。Niの厚みは30nm程度、Auの厚みは400nm程度とする。リフトオフ法により、庇構造のレジストマスク及びその上に堆積したNi/Auを除去する。これにより、電極用リセス4e1内を保護膜5を介してゲートメタルで埋め込むゲート電極6が形成される。ゲート電極6は、保護膜5を介して電極用リセス4e1内を埋め込み保護膜5上に乗り上げるNiと、Ni上に堆積したAuとから、いわゆるオーバーハング形状に形成される。

#### [0070]

しかる後、ソース電極3及びドレイン電極4、ゲート電極6の電気的接続等の諸工程を経て、MIS型のAlGaN/GaN・HEMTが形成される。

### [0071]

以上説明したように、本実施形態によれば、電流コラプス等のトラップ起因の特性劣化を防止し、ピンチオフ特性及びgmを向上させるも、確実なノーマリオフを実現する信頼性の高いAlGaN/GaN・HEMTが得られる。

#### [0072]

# (第6の実施形態)

本実施形態では、化合物半導体装置としてMIS型のInAlN/GaN・HEMTを 開示する。 10

20

30

40

なお、第1の実施形態によるAIGaN/GaN・HEMTと同様の構成部材等については、同符号を付して詳しい説明を省略する。

図12及び図13は、第6の実施形態によるInAlN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

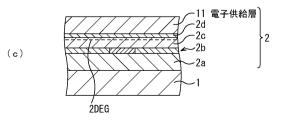

### [0073]

先ず、図12(a)~図12(b)に示すように、第1の実施形態の図1(a)~図1 (b)の諸工程を経る。このとき、図12(b)に示すように、バックバリア層2bが形成される。

# [0074]

続いて、図12(c)に示すように、バックバリア層2b上に、電子走行層2c、中間層2d、及び電子供給層11を順次形成する。

MOVPE法により、バックバリア層2b上に、電子走行層2c、中間層2d、及び電子供給層11となる各化合物半導体を順次成長する。電子走行層2cは、i-GaNを100nm程度の厚みに成長することで形成される。中間層2dは、i-AlGaNを5nm程度の厚みに成長することで形成される。電子供給層11は、i-InAlNを20nm程度の厚みに成長することで形成される。中間層2dは形成しない場合もある。電子供給層は、i-InAlNを形成するようにしても良い。

## [0075]

#### [0076]

以上により、i - GaN層2a、バックバリア層2b、電子走行層2c、中間層2d、及び電子供給層11が順次積層されてなる化合物半導体積層構造2が形成される。

# [0077]

続いて、素子分離構造を形成した後、図13(a)に示すように、ソース電極3及びドレイン電極4を形成する。

電極材料として例えばTa/A1(下層がTa、上層がA1)を用いる。電極形成には、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを化合物半導体積層構造2上に塗布し、ソース電極及びドレイン電極の各形成予定位置を開口するレジストマスクを形成する。このレジストマスクを用いて、例えば蒸着法により、Ta/A1を堆積する。Taの厚みは20nm程度、A1の厚みは200nm程度とする。リフトオフ法により、庇構造のレジストマスク及びその上に堆積したTa/A1を除去する。その後、SiC基板1を、例えば窒素雰囲気中において400~~1000 、例えば550 程度で熱処理し、残存したTa/A1を電子供給層11とオーミックコンタクトさせる。なお、Ta/A1が熱処理を行わずとも電子供給層11とオーミックコンタクトする場合には、当該熱処理を行わなくても良い。以上により、Ta/A1からなるソース電極3及びドレイン電極4が形成される。

# [0078]

続いて、図13(b)に示すように、化合物半導体積層構造2の表面に、開口5aを有する保護膜5を形成する。

詳細には、先ず、ソース電極 3 上及びドレイン電極 4 上を含む化合物半導体積層構造 2 の全面に S i Nを、プラズマ C V D 法又はスパッタ法等により例えば 2 n m程度 ~ 2 0 0 n m、例えば 2 0 n m程度の厚みに堆積する。以上により、保護膜 5 が形成される。

# [0079]

50

10

20

30

次に、保護膜5の全面にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、保護膜5のゲート電極の形成予定位置を露出する開口を有するレジストマスクが形成される。

このレジストマスクを用いて、保護膜 5 を例えばフッ素系ガスをエッチングガスとして用いてドライエッチングする。これにより、保護膜 5 のゲート電極の形成予定位置に開口 5 a が形成される。レジストマスクは、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

### [0800]

続いて、図13(c)に示すように、ゲート電極6を形成する。

電極材料として例えばNi/Au(下層がNi、上層がAu)を用いる。電極形成には、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを開口5a内を含む保護膜5上に塗布し、開口5aを含むゲート電極の形成予定位置を開口するレジストマスクを形成する。このレジストマスクを用いて、例えば蒸着法により、Ni/Auを堆積する。Niの厚みは30nm程度、Auの厚みは400nm程度とする。リフトオフ法により、庇構造のレジストマスク及びその上に堆積したNi/Auを除去する。これにより、開口5a内をゲートメタルで埋め込み化合物半導体積層構造2の表面とショットキー接触する、ゲート電極6が形成される。ゲート電極6は、開口5a内を埋め込み保護膜5上に乗り上げるNiと、Ni上に堆積したAuとから、いわゆるオーバーハング形状に形成される。

# [0081]

しかる後、ソース電極3及びドレイン電極4、ゲート電極6の電気的接続等の諸工程を経て、MIS型のInAlN/GaN・HEMTが形成される。

#### [0082]

以上説明したように、本実施形態によれば、電流コラプス等のトラップ起因の特性劣化を防止し、ピンチオフ特性及びgmを向上させるも、確実なノーマリオフを実現する信頼性の高いInAlN/GaN・HEMTが得られる。

#### [0083]

なお、本実施形態では、電子供給層11としてi - In A l N層を形成したが、i - In A l N層の代わりに、例えば In A l G a N層を形成しても良い。

# [0084]

(第7の実施形態)

本実施形態では、化合物半導体装置としてMIS型のAlGaN/GaN・HEMTを 開示する。

なお、第1の実施形態によるAlGaN/GaN・HEMTと同様の構成部材等については、同符号を付して詳しい説明を省略する。

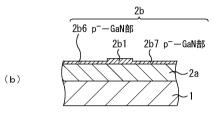

図14及び図15は、第7の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

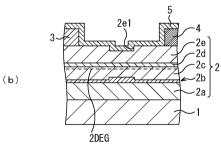

#### [0085]

先ず、図14(a)に示すように、第1の実施形態の図1(a)の工程を実行し、Si C基板1上に、i-GaN層2a及びp-GaN部2b1となるp-GaN層(例えば、 Mg濃度1×10<sup>19</sup>/cm<sup>3</sup>程度、膜厚50nm程度)が順次形成される。

#### [0086]

続いて、図14(b)に示すように、バックバリア層2bを形成する。

先ず、 p - G a N 層上にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、 p - G a N 層のゲート電極の形成予定位置の下方に位置整合する部分( p - G a N 部 2 b 1 となる部分)を覆い、他の部分を開口するレジストマスクが形成される

# [0087]

このレジストマスクを用いて、 p - G a N 層の他の部分を、塩素系ガスをエッチングガスとしてドライエッチングし、当該他の部分の膜厚を減少させる。ここでは、当該他の部

10

20

30

50

分の膜厚を10nm程度とする。

#### [0088]

以上により、ゲート電極の形成予定位置の下方に位置整合する部分に形成された p - G a N部 2 b 1 と、 p - G a N部 2 b 1 の両側で p - G a N部 2 b 1 よりも薄い p - G a N部 2 b 6 , 2 b 7 とを有するバックバリア層 2 b が形成される。バックバリア層 2 b では、 p - G a N部 2 b 1 と p - G a N部 2 b 6 , 2 b 7 とではイオン化アクセプタ濃度は同一であるが、 p - G a N部 2 b 1 が p - G a N部 2 b 6 , 2 b 7 よりも厚くイオン化アクセプタ量が多い部分となる。

# [0089]

続いて、図14(c)に示すように、バックバリア層2b上に、電子走行層2c、中間層2d、及び電子供給層2eを順次形成する。

MOVPE法により、バックバリア層2b上に、電子走行層2c、中間層2d、及び電子供給層2eとなる各化合物半導体を順次成長する。電子走行層2cは、i-GaNを10nm程度の厚みに成長することで形成される。中間層2dは、i-AlGaNを5nm程度の厚みに成長することで形成される。電子供給層2eは、n-AlGaNを30nm程度の厚みに成長することで形成される。中間層2dは形成しない場合もある。電子供給層は、i-AlGaNを形成するようにしても良い。

## [0090]

GaNの成長には、原料ガスとして <math>Ga源であるトリメチルガリウム( TMGa)ガス及びアンモニア(  $NH_3$ )ガスの混合ガスを用いる。 AlGaNの成長には、原料ガスとして <math>TMAlガス、 TMGaガス及び  $NH_3$ ガスの混合ガスを用いる。成長する化合物半導体層に応じて、 TMAl ガス、 TMGa ガスの供給の有無及び流量を適宜設定する。共通原料である  $NH_3$  ガスの流量は、 100sccm 10slm 程度とする。また、成長圧力は 50Torr 2000 程度とする。

#### [0091]

Al GaNをn型として成長する際、即ち電子供給層 2 e (n - Al GaN)の形成には、n型不純物をAl GaNの原料ガスに添加する。ここでは、例えばSiを含む例えばシラン (Si H<sub>4</sub>)ガスを所定の流量で原料ガスに添加し、Al GaNにSiをドーピングする。Siのドーピング濃度は、1 × 1 0  $^{18}$  / c m  $^3$  程度 ~ 1 × 1 0  $^{20}$  / c m  $^3$  程度、例えば 5 × 1 0  $^{18}$  / c m  $^3$  程度とする。

以上により、i - GaN層2a、バックバリア層2b、電子走行層2c、中間層2d、及び電子供給層2eが順次積層されてなる化合物半導体積層構造2が形成される。

#### [0092]

続いて、素子分離構造を形成した後、図15(a)に示すように、電子供給層4eに電極用リセス4e1を形成した後、ソース電極3及びドレイン電極4を形成する。

詳細には、先ず、化合物半導体積層構造 2 の全面にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、電子供給層 4 e におけるゲート電極の形成予定位置を露出する開口を有するレジストマスクが形成される。

このレジストマスクを用いて、電子供給層 2 e の表層の一部を、例えばフッ素系ガスをエッチングガスとして用いてドライエッチングする。これにより、電子供給層 2 e のゲート電極の形成予定位置に電極用リセス 4 e 1 が形成される。レジストマスクは、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

### [0093]

次に、電極材料として例えばTa/A1(下層がTa、上層がA1)を用いる。電極形成には、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを化合物半導体積層構造2上に塗布し、ソース電極及びドレイン電極の各形成予定位置を開口するレジストマスクを形成する。このレジストマスクを用いて、例えば蒸着法により、Ta/A1を堆積する。Taの厚みは20nm程度、A1の厚みは200nm程度とする。リフトオフ法により、庇構造のレジストマスク及びその上に堆積したTa/A1を除去する。その後、SiC基板1を、例えば窒素雰囲気中において400 ~1000

10

20

30

40

20

30

40

50

、例えば550 程度で熱処理し、残存したTa/A1を電子供給層2eとオーミックコンタクトさせる。なお、Ta/A1が熱処理を行わずとも電子供給層2eとオーミックコンタクトする場合には、当該熱処理を行わなくても良い。以上により、Ta/A1からなるソース電極3及びドレイン電極4が形成される。

### [0094]

続いて、図15(b)に示すように、化合物半導体積層構造2の表面に保護膜5を形成する

詳細には、ソース電極3上及びドレイン電極4上を含む化合物半導体積層構造2の全面にSiNを、プラズマCVD法又はスパッタ法等により例えば2nm程度~200nm、例えば20nm程度の厚みに堆積する。以上により、保護膜5が形成される。本実施形態では、保護膜5はゲート絶縁膜としても機能する。

[0095]

続いて、図15(c)に示すように、ゲート電極6を形成する。

電極材料として例えばNi/Au(下層がNi、上層がAu)を用いる。電極形成には、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを保護膜5上に塗布し、ゲート電極の形成予定位置を開口するレジストマスクを形成する。このレジストマスクを用いて、例えば蒸着法により、Ni/Auを堆積する。Niの厚みは30nm程度、Auの厚みは400nm程度とする。リフトオフ法により、庇構造のレジストマスク及びその上に堆積したNi/Auを除去する。これにより、電極用リセス4e1内を保護膜5を介してゲートメタルで埋め込むゲート電極6が形成される。ゲート電極6は、保護膜5を介して電極用リセス4e1内を埋め込み保護膜5上に乗り上げるNiと、Ni上に堆積したAuとから、いわゆるオーバーハング形状に形成される。

[0096]

しかる後、ソース電極3及びドレイン電極4、ゲート電極6の電気的接続等の諸工程を経て、MIS型のAlGaN/GaN・HEMTが形成される。

[0097]

以上説明したように、本実施形態によれば、電流コラプス等のトラップ起因の特性劣化を防止し、ピンチオフ特性及びgmを向上させるも、確実なノーマリオフを実現する信頼性の高いAlGaN/GaN・HEMTが得られる。

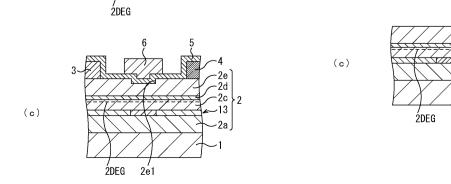

[0098]

(第8の実施形態)

本実施形態では、化合物半導体装置としてMIS型のAlGaN/GaN・HEMTを 開示する。

なお、第1の実施形態によるAlGaN/GaN・HEMTと同様の構成部材等については、同符号を付して詳しい説明を省略する。

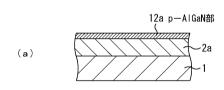

図16及び図17は、第8の実施形態によるA1GaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

[0099]

先ず、図16(a)に示すように、SiC基板1上に、i-GaN層2a及びp-A1GaN部12aとなるp-A1GaN層を順次形成する。

詳細には、SiC基板1上に、MOVPE法により、i-GaN層2a及びp-AlGaN部12aとなるp-AlGaN層を順次成長する。

i - GaN層 2 a は、i - GaNを例えば 3  $\mu$  m程度の厚みに成長することで形成される。 p - AlGaN部 1 2 a となる p - AlGaN層は、 p - AlGaNを例えば 5 0 n m程度の厚みに成長することで形成される。

[0100]

GaNの成長には、原料ガスとして <math>Ga源である TMGaガス及び  $NH_3$ ガスの混合ガスを用いる。 AlGaNの成長には、原料ガスとして <math>Ga源である TMGaガス、 Al 源である TMAl ガス、 及び  $NH_3$ ガスの混合ガスを用いる。 TMGa ガス、 TMAl ガスの流量は適宜設定し、  $NH_3$ ガスの流量は、 100sccm-10slm 程度とする。 ま

た、成長圧力は50Torr~300Torr程度、成長温度は1000 ~1200 程度とする。

### [0101]

$A 1 G a N を p 型 として成長する際、即ち p - A 1 G a N 部 1 2 a となる p - A 1 G a N 層の形成には、 p 型不純物である M g、 C、 Z n 等、 例えば M g を A 1 G a N の原料ガスに添加する。ここでは、 例えば M g を含む例えば C p 2 M g ガスを所定の流量で原料ガスに添加し、 A 1 G a N に M g を ドーピングする。 M g の ドーピング 濃度 は、 1 × 1 0 <math>^{16}$  / c m  $^3$  程度 ~ 1 × 1 0  $^{21}$  / c m  $^3$  程度、 例えば 1 × 1 0  $^{19}$  / c m  $^3$  程度とする。

p - A 1 G a N 層を形成した後、 4 0 0 ~ 1 2 0 0 程度、例えば 8 0 0 程度でp - A 1 G a N 層を熱処理し、p 型不純物である M g を活性化する。

[0102]

続いて、図16(b)に示すように、バックバリア層12を形成する。

先ず、 p - A 1 G a N層上にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、 p - A 1 G a N層のゲート電極の形成予定位置の下方に位置整合する部分( p - A 1 G a N部 1 2 a となる部分)を覆い、他の部分を開口するレジストマスクが形成される。

#### [0103]

このレジストマスクを用いて、 $p-AlGaNのp型不純物を不活性する不純物、例えばアルゴン(Ar)を加速エネルギー15keV、ドーズ量<math>1\times10^{14}/cm^2$ の条件でイオン注入する。不活性不純物として、Ar以外にホウ素(B),酸素(O),リン(P),鉄(Fe)等を用いても良い。このイオン注入により、p-AlGaN層のゲート電極の形成予定位置以外の部分が不活性し、<math>p-AlGaNとなってp-AlGaN部12b,12cが形成される。p-AlGaN部12b,12cは、イオン化アクセプタ濃度がp-AlGaN部12aよりも低濃度である。レジストマスクは、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

#### [0104]

以上により、ゲート電極の形成予定位置の下方に位置整合する部分に形成された p - A 1 G a N 部 1 2 a と、 p - A 1 G a N 部 1 2 a の両側に形成された p - A 1 G a N 部 1 2 b , 1 2 c とを有するバックバリア層 1 2 が形成される。バックバリア層 1 2 では、 p - A 1 G a N 部 1 2 b , 1 2 c よりもイオン化アクセプタ量が多い、ここではイオン化アクセプタ濃度が高い部分となる。

[0105]

続いて、図16(c)に示すように、バックバリア層12上に、電子走行層2c、中間層2d、及び電子供給層2eを順次形成する。

MOVPE法により、バックバリア層12上に、電子走行層2c、中間層2d、及び電子供給層2eとなる各化合物半導体を順次成長する。電子走行層2cは、i-GaNを100nm程度の厚みに成長することで形成される。中間層2dは、i-A1GaNを5nm程度の厚みに成長することで形成される。電子供給層2eは、n-A1GaNを30nm程度の厚みに成長することで形成される。中間層2dは形成しない場合もある。電子供給層は、i-A1GaNを形成するようにしても良い。

[0106]

GaNの成長には、原料ガスとして <math>Ga源である TMGaガス及びアンモニア  $(NH_3)$  ガスの混合ガスを用いる。 AlGaNO成長には、原料ガスとして TMAl ガス、 TMGa ガス及び  $NH_3$  ガスの混合ガスを用いる。成長する化合物半導体層に応じて、 TMAl ガス、 TMGa ガスの供給の有無及び流量を適宜設定する。共通原料である  $NH_3$  ガスの流量は、 100 s c c m  $\sim 10$  s 1 m程度とする。また、成長圧力は 50 Torr  $\sim 300$  Torr 程度、成長温度は 1000  $\sim 1200$  程度とする。

# [0107]

10

20

30

40

20

30

40

50

シラン(SiH<sub>4</sub>)ガスを所定の流量で原料ガスに添加し、AlGaNにSiをドーピングする。Siのドーピング濃度は、1 × 1  $0^{18}$  / c  $m^3$ 程度~1 × 1  $0^{20}$  / c  $m^3$ 程度、例えば 5 × 1  $0^{18}$  / c  $m^3$ 程度とする。

以上により、i - GaN層2a、バックバリア層12、電子走行層2c、中間層2d、及び電子供給層2eが順次積層されてなる化合物半導体積層構造2が形成される。

#### [0108]

続いて、素子分離構造を形成した後、図17(a)に示すように、電子供給層4eに電極用リセス4e1を形成した後、ソース電極3及びドレイン電極4を形成する。

詳細には、先ず、化合物半導体積層構造2の全面にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、電子供給層4eにおけるゲート電極の形成予定位置を露出する開口を有するレジストマスクが形成される。

このレジストマスクを用いて、電子供給層2eの表層の一部を、例えばフッ素系ガスをエッチングガスとして用いてドライエッチングする。これにより、電子供給層2eのゲート電極の形成予定位置に電極用リセス4e1が形成される。レジストマスクは、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

#### [0109]

次に、電極材料として例えばTa/A1(下層がTa、上層がA1)を用いる。電極形成には、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを化合物半導体積層構造2上に塗布し、ソース電極及びドレイン電極の各形成予定位置を開口するレジストマスクを形成する。このレジストマスクを用いて、例えば蒸着法により、Ta/A1を堆積する。Taの厚みは20nm程度、A1の厚みは200nm程度とする。リフトオフ法により、庇構造のレジストマスク及びその上に堆積したTa/A1を除去する。その後、SiC基板1を、例えば窒素雰囲気中において400~1000、例えば550 程度で熱処理し、残存したTa/A1を電子供給層2eとオーミックコンタクトさせる。なお、Ta/A1が熱処理を行わずとも電子供給層2eとオーミックコンタクトする場合には、当該熱処理を行わなくても良い。以上により、Ta/A1からなるソース電極3及びドレイン電極4が形成される。

# [0110]

続いて、図17(b)に示すように、化合物半導体積層構造2の表面に保護膜5を形成する。

詳細には、ソース電極3上及びドレイン電極4上を含む化合物半導体積層構造2の全面にSiNを、プラズマCVD法又はスパッタ法等により例えば2nm程度~200nm、例えば20nm程度の厚みに堆積する。以上により、保護膜5が形成される。本実施形態では、保護膜5はゲート絶縁膜としても機能する。

# [0111]

続いて、図17(c)に示すように、ゲート電極6を形成する。

電極材料として例えばNi/Au(下層がNi、上層がAu)を用いる。電極形成には、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを保護膜5上に塗布し、ゲート電極の形成予定位置を開口するレジストマスクを形成する。このレジストマスクを用いて、例えば蒸着法により、Ni/Auを堆積する。Niの厚みは30nm程度、Auの厚みは400nm程度とする。リフトオフ法により、庇構造のレジストマスク及びその上に堆積したNi/Auを除去する。これにより、電極用リセス4e1内を保護膜5を介してゲートメタルで埋め込むゲート電極6が形成される。ゲート電極6は、保護膜5を介して電極用リセス4e1内を埋め込み保護膜5上に乗り上げるNiと、Ni上に堆積したAuとから、いわゆるオーバーハング形状に形成される。

# [0112]

しかる後、ソース電極3及びドレイン電極4、ゲート電極6の電気的接続等の諸工程を経て、MIS型のAlGaN/GaN・HEMTが形成される。

#### [0113]

以上説明したように、本実施形態によれば、電流コラプス等のトラップ起因の特性劣化

20

30

40

50

を防止し、ピンチオフ特性及びgmを向上させるも、確実なノーマリオフを実現する信頼性の高いAlGaN/GaN・HEMTが得られる。

#### [0114]

(第9の実施形態)

本実施形態では、化合物半導体装置としてMIS型のAlGaN/GaN・HEMTを 開示する。

なお、第1の実施形態によるAlGaN/GaN・HEMTと同様の構成部材等については、同符号を付して詳しい説明を省略する。

図18及び図19は、第9の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

[0115]

先ず、図18(a)に示すように、SiC基板1上に、i-GaN層2a及びp-In A1N部13aとなるp-InA1N層を順次形成する。

詳細には、SiC基板1上に、MOVPE法により、i-GaN層2a及びp-InA 1N部13aとなるp-InA1N層を順次成長する。

i - GaN層 2 a は、i - GaNを例えば 3  $\mu$  m程度の厚みに成長することで形成される。 p - In AlN部 1 3 a となる p - In AlN層は、 p - In AlNを例えば 5 0 n m程度の厚みに成長することで形成される。

[0116]

GaNの成長には、原料ガスとして <math>Ga源である  $TMGaガス及び NH_3$ ガスの混合ガスを用いる。 InAlNの成長には、原料ガスとして <math>In源である  $TMInガス、Al源である <math>TMInガス、及び NH_3$ ガスの混合ガスを用いる。  $TMInガス、TMAlガスの流量は適宜設定し、 NH_3 ガスの流量は、 100sccm~10slm程度とする。また、成長圧力は 50 Torr~300 Torr程度、成長温度は 1000~1200 程度とする。$

[0117]

In Al Nを p型として成長する際、即ち p - In Al N部 1 3 a となる p - In Al N層の形成には、 p型不純物である Mg、 C、 Zn等、例えば Mgを In Al Nの原料ガスに添加する。ここでは、例えば Mgを含む例えば Cp 2 Mgガスを所定の流量で原料ガスに添加し、 In Al Nに Mgをドーピングする。 Mgのドーピング濃度は、 1 × 1 0  $^{16}$  / cm  $^3$ 程度 ~ 1 × 1 0  $^{21}$  / cm  $^3$ 程度、例えば 1 × 1 0  $^{19}$  / cm  $^3$ 程度とする。

p - I n A l N 層を形成した後、400 ~ 1200 程度、例えば800 程度で p - I n A l N 層を熱処理し、p 型不純物である M g を活性化する。

[0118]

続いて、図18(b)に示すように、バックバリア層13を形成する。

先ず、 p - I n A l N 層上にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、 p - I n A l N 層のゲート電極の形成予定位置の下方に位置整合する部分(p - I n A l N 部 1 3 a となる部分)を覆い、他の部分を開口するレジストマスクが形成される。

[0119]

このレジストマスクを用いて、p-InAlNop型不純物を不活性する不純物、例えばアルゴン (Ar)を加速エネルギー15 ke V、ドーズ量1 x 10  $^{14}$  / c  $m^2$  の条件でイオン注入する。不活性不純物として、Ar以外にホウ素(B),酸素(O),リン(P),鉄(Fe)等を用いても良い。このイオン注入により、p-AlGaN 層のゲート電極の形成予定位置以外の部分が不活性し、p-InAlN となって p-InAlN 部 13 b,13 c が形成される。p-InAlN 部 13 b,13 c は、イオン化アクセプタ濃度がp-InAlN 部 13 a よりも低濃度である。レジストマスクは、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

[0120]

以上により、ゲート電極の形成予定位置の下方に位置整合する部分に形成されたp-I

### [0121]

続いて、図18(c)に示すように、バックバリア層13上に、電子走行層2c、中間層2d、及び電子供給層2eを順次形成する。

MOVPE法により、バックバリア層13上に、電子走行層2c、中間層2d、及び電子供給層2eとなる各化合物半導体を順次成長する。電子走行層2cは、i‐GaNを100nm程度の厚みに成長することで形成される。中間層2dは、i‐A1GaNを5nm程度の厚みに成長することで形成される。電子供給層2eは、n‐A1GaNを30nm程度の厚みに成長することで形成される。中間層2dは形成しない場合もある。電子供給層は、i‐A1GaNを形成するようにしても良い。

# [0122]

#### [0123]

AlgaNをn型として成長する際、即ち電子供給層 2e(n-AlgaN)の形成には、n型不純物をAlgaNの原料ガスに添加する。ここでは、例えば<math>Siを含む例えばシラン( $SiH_4$ )ガスを所定の流量で原料ガスに添加し、AlgaNにSiをドーピングする。Siのドーピング濃度は、 $1 \times 10^{18}$  /  $cm^3$ 程度~ $1 \times 10^{20}$  /  $cm^3$ 程度、例えば  $5 \times 10^{18}$  /  $cm^3$ 程度とする。

以上により、i - GaN層2a、バックバリア層13、電子走行層2c、中間層2d、及び電子供給層2eが順次積層されてなる化合物半導体積層構造2が形成される。

### [0124]

続いて、素子分離構造を形成した後、図19(a)に示すように、電子供給層4eに電極用リセス4e1を形成した後、ソース電極3及びドレイン電極4を形成する。

詳細には、先ず、化合物半導体積層構造 2 の全面にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、電子供給層 4 e におけるゲート電極の形成予定位置を露出する開口を有するレジストマスクが形成される。

このレジストマスクを用いて、電子供給層 2 e の表層の一部を、例えばフッ素系ガスをエッチングガスとして用いてドライエッチングする。これにより、電子供給層 2 e のゲート電極の形成予定位置に電極用リセス 4 e 1 が形成される。レジストマスクは、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

#### [0125]

次に、電極材料として例えばTa/A1(下層がTa、上層がA1)を用いる。電極形成には、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを化合物半導体積層構造2上に塗布し、ソース電極及びドレイン電極の各形成予定位置を開口するレジストマスクを形成する。このレジストマスクを用いて、例えば蒸着法により、Ta/A1を堆積する。Taの厚みは20nm程度、A1の厚みは200nm程度とする。リフトオフ法により、庇構造のレジストマスク及びその上に堆積したTa/A1を除去する。その後、SiC基板1を、例えば窒素雰囲気中において400~1000、例えば550 程度で熱処理し、残存したTa/A1を電子供給層2eとオーミックコンタクトさせる。なお、Ta/A1が熱処理を行わずとも電子供給層2eとオーミックコンタクトする場合には、当該熱処理を行わなくても良い。以上により、Ta/A1からなるソース電極3及びドレイン電極4が形成される。

10

20

30

40

#### [0126]

続いて、図19(b)に示すように、化合物半導体積層構造2の表面に保護膜5を形成する。

詳細には、ソース電極 3 上及びドレイン電極 4 上を含む化合物半導体積層構造 2 の全面に SiNを、プラズマ CVD法又はスパッタ法等により例えば 2 nm程度 ~ 2 0 0 nm、例えば 2 0 nm程度の厚みに堆積する。以上により、保護膜 5 が形成される。本実施形態では、保護膜 5 はゲート絶縁膜としても機能する。

#### [0127]

続いて、図19(c)に示すように、ゲート電極6を形成する。

電極材料として例えばNi/Au(下層がNi、上層がAu)を用いる。電極形成には、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを保護膜5上に塗布し、ゲート電極の形成予定位置を開口するレジストマスクを形成する。このレジストマスクを用いて、例えば蒸着法により、Ni/Auを堆積する。Niの厚みは30nm程度、Auの厚みは400nm程度とする。リフトオフ法により、庇構造のレジストマスク及びその上に堆積したNi/Auを除去する。これにより、電極用リセス4e1内を保護膜5を介してゲートメタルで埋め込むゲート電極6が形成される。ゲート電極6は、保護膜5を介して電極用リセス4e1内を埋め込み保護膜5上に乗り上げるNiと、Ni上に堆積したAuとから、いわゆるオーバーハング形状に形成される。

#### [0128]

しかる後、ソース電極3及びドレイン電極4、ゲート電極6の電気的接続等の諸工程を経て、MIS型のAlGaN/GaN・HEMTが形成される。

#### [0129]

以上説明したように、本実施形態によれば、電流コラプス等のトラップ起因の特性劣化を防止し、ピンチオフ特性及びgmを向上させるも、確実なノーマリオフを実現する信頼性の高いAIGaN/BaN・HEMTが得られる。

# [0130]

なお、本実施形態では、バックバリア層として  $p-InAlN層(p-InAlN及び p^--InAlN)$  を形成したが、  $p-InAlN層の代わりに p-AlN層(p-AlN及び p^--AlN)$  を形成しても良い。

# [0131]

(第10の実施形態)

本実施形態では、化合物半導体装置としてMIS型のAlGaN/GaN・HEMTを 開示する。

なお、第1の実施形態によるAlGaN/GaN・HEMTと同様の構成部材等については、同符号を付して詳しい説明を省略する。

図20及び図21は、第10の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

#### [0132]

先ず、図20(a)に示すように、SiC基板1上に、i-GaN層2aを形成する。 詳細には、SiC基板1上に、MOVPE法により、i-GaNを例えば3μm程度の 厚みに成長し、i-GaN層2aを形成する。

#### [0133]

GaNの成長には、原料ガスとして<math>Ga源であるTMGaガス及び $NH_3$ ガスの混合ガスを用いる。AlGaNの成長には、原料ガスとして<math>Ga源であるTMGaガス、Al源であるTMAlガス、及び $NH_3$ ガスの混合ガスを用いる。TMGaガス、TMAlガスの流量は適宜設定し、 $NH_3$ ガスの流量は、 $100sccm \sim 10slm$ 程度とする。また、成長圧力は $50Torr \sim 300Torr$ 程度、成長温度は $1000 \sim 1200$  程度とする。

#### [0134]

続いて、図20(b)に示すように、バックバリア層2bを形成する。

10

20

30

先ず、i-GaN層2a上にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、i-GaN層2aのゲート電極の形成予定位置の下方に位置整合する部分(p-GaN部となる部分)を開口し、i-GaN層2aの他の部分を覆うレジストマスクが形成される。

# [0135]

このレジストマスクを用いて、 p型不純物である M g 、 C 、 Z n 等、例えば M g を i - G a N 層 2 a の表層部分にイオン注入する。 4 0 0 ~ 1 2 0 0 程度、例えば 8 0 0 程度で熱処理 1 0、 p型不純物である M g を活性化する。以上により、 1 - G a N 層 2 a の表層には、ゲート電極の形成予定位置の下方に位置整合する部分に 1 0 - G a N 部 1 0 1 が形成される。 1 0 - G a N 部 1 1 0 1 は、イオン化アクセプタ濃度が 1 × 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0

#### [0136]

次に、 p - G a N 部 2 b 1 上を含む i - G a N 層 2 a 上にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、 p - G a N 部 2 b 1 を覆い、 i - G a N 層 2 a の他の部分を開口するレジストマスクが形成される。

#### [0137]

このレジストマスクを用いて、 p型不純物である M g 、 C 、 Z n 等、 例えば M g を i - G a N 層 2 a の表層部分にイオン注入する。 400 ~ 1200 程度、 例えば 800 程度で熱処理 0 、 p型不純物である M g を活性化する。以上により、 i - G a N 層 2 a の表層には、 p - G a N 部 2 b 1 の両側に p - G a N 部 2 b 8 , 2 b 9 が形成される。 p - G a N 部 2 b 8 , 2 b 9 は、 厚みが p - G a N 部 2 b 1 と同一であり、 イオン化アクセプタ濃度が p - G a N 部 2 b 1 よりも低濃度である。 レジストマスクは、 アッシング処理又は所定の薬液を用いたウェット処理により除去される。

#### [0138]

以上により、ゲート電極の形成予定位置の下方に位置整合する部分に形成されたp-GaN部2b1と、p-GaN部2b1の両側に形成されたp‐-GaN部2b8,2b9とを有するバックバリア層2bが形成される。バックバリア層2bでは、p-GaN部2b1は、p‐-GaN部2b8,2b9よりもイオン化アクセプタ量が多い、ここではイオン化アクセプタ濃度が高い部分となる。

#### [0139]

続いて、図20(c)に示すように、バックバリア層2b上に、電子走行層2c、中間層2d、及び電子供給層2eを順次形成する。

MOVPE法により、バックバリア層2b上に、電子走行層2c、中間層2d、及び電子供給層2eとなる各化合物半導体を順次成長する。電子走行層2cは、i-GaNを10nm程度の厚みに成長することで形成される。中間層2dは、i-AlGaNを5nm程度の厚みに成長することで形成される。電子供給層2eは、n-AlGaNを30nm程度の厚みに成長することで形成される。中間層2dは形成しない場合もある。電子供給層は、i-AlGaNを形成するようにしても良い。

#### [0140]

#### [0141]

A 1 G a N を n 型として成長する際、即ち電子供給層 2 e (n - A 1 G a N) の形成には、 <math>n 型不純物を A 1 G a N の原料ガスに添加する。ここでは、例えば S i を含む例えばシラン( $S i H_4$ )ガスを所定の流量で原料ガスに添加し、A 1 G a N に S i をドーピン

10

20

30

40

20

30

40

50

グする。 S i のドーピング濃度は、  $1 \times 10^{18}$  / c m  $^3$  程度  $\sim 1 \times 10^{20}$  / c m  $^3$  程度、例えば  $5 \times 10^{18}$  / c m  $^3$  程度とする。

以上により、i - GaN層2a、バックバリア層2b、電子走行層2c、中間層2d、及び電子供給層2eが順次積層されてなる化合物半導体積層構造2が形成される。

# [0142]

続いて、素子分離構造を形成した後、図21(a)に示すように、電子供給層4eに電極用リセス4e1を形成した後、ソース電極3及びドレイン電極4を形成する。

詳細には、先ず、化合物半導体積層構造2の全面にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、電子供給層4eにおけるゲート電極の形成予定位置を露出する開口を有するレジストマスクが形成される。

このレジストマスクを用いて、電子供給層2eの表層の一部を、例えばフッ素系ガスをエッチングガスとして用いてドライエッチングする。これにより、電子供給層2eのゲート電極の形成予定位置に電極用リセス4e1が形成される。レジストマスクは、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

#### [0143]

次に、電極材料として例えばTa/A1(下層がTa、上層がA1)を用いる。電極形成には、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを化合物半導体積層構造2上に塗布し、ソース電極及びドレイン電極の各形成予定位置を開口するレジストマスクを形成する。このレジストマスクを用いて、例えば蒸着法により、Ta/A1を堆積する。Taの厚みは20nm程度、A1の厚みは200nm程度とする。リフトオフ法により、庇構造のレジストマスク及びその上に堆積したTa/A1を除去する。その後、SiC基板1を、例えば窒素雰囲気中において400~1000、例えば550 程度で熱処理し、残存したTa/A1を電子供給層2eとオーミックコンタクトさせる。なお、Ta/A1が熱処理を行わずとも電子供給層2eとオーミックコンタクトする場合には、当該熱処理を行わなくても良い。以上により、Ta/A1からなるソース電極3及びドレイン電極4が形成される。

#### [0144]

続いて、図21(b)に示すように、化合物半導体積層構造2の表面に保護膜5を形成する。

詳細には、ソース電極3上及びドレイン電極4上を含む化合物半導体積層構造2の全面にSiNを、プラズマCVD法又はスパッタ法等により例えば2nm程度~200nm、例えば20nm程度の厚みに堆積する。以上により、保護膜5が形成される。本実施形態では、保護膜5はゲート絶縁膜としても機能する。

# [0145]

続いて、図21(c)に示すように、ゲート電極6を形成する。

電極材料として例えばNi/Au(下層がNi、上層がAu)を用いる。電極形成には、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを保護膜5上に塗布し、ゲート電極の形成予定位置を開口するレジストマスクを形成する。このレジストマスクを用いて、例えば蒸着法により、Ni/Auを堆積する。Niの厚みは30nm程度、Auの厚みは400nm程度とする。リフトオフ法により、庇構造のレジストマスク及びその上に堆積したNi/Auを除去する。これにより、電極用リセス4e1内を保護膜5を介してゲートメタルで埋め込むゲート電極6が形成される。ゲート電極6は、保護膜5を介して電極用リセス4e1内を埋め込み保護膜5上に乗り上げるNiと、Ni上に堆積したAuとから、いわゆるオーバーハング形状に形成される。

#### [0146]

しかる後、ソース電極3及びドレイン電極4、ゲート電極6の電気的接続等の諸工程を経て、MIS型のAlGaN/GaN・HEMTが形成される。

#### [0147]

以上説明したように、本実施形態によれば、電流コラプス等のトラップ起因の特性劣化を防止し、ピンチオフ特性及びgmを向上させるも、確実なノーマリオフを実現する信頼

性の高いAlGaN/GaN・HEMTが得られる。

### [0148]

以上、第1~第10の実施形態を説明したが、これらの実施形態では、その特徴を適宜 組み合わせることができる。数例を以下に示す。

例えば、第6の実施形態によるInAlN/GaN・HEMTにおいて、第3の実施形態の特徴であるゲートリセス構造(電子供給層11に形成された電極リセスに(保護膜5を介して)ゲート電極6が形成される構造)を採用することができる。

また例えば、第6の実施形態によるInAIN/GaN・HEMTにおいて、第1の実施形態の特徴であるショットキー接触の構造(保護膜5の開口5aを通じてゲート電極6が化合物半導体積層構造2とショットキー接触する)構造)を採用することができる。

また例えば、第9又は第10の実施形態によるA1GaN/GaN・HEMTにおいて、第5の実施形態の特徴であるバックバリア層のイオン化アクセプタ量の多い部分の偏倚延在構造を採用することができる。

また例えば、第9又は第10の実施形態によるA1GaN/GaN・HEMTにおいて、第7の実施形態の特徴であるバックバリア層の膜厚を部分的に変えた構造を採用することができる。

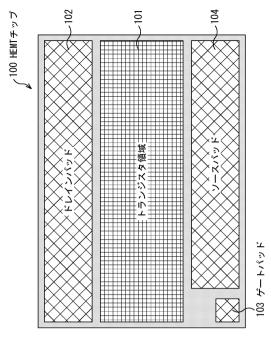

#### [0149]

第1~第10の実施形態によるHEMTは、いわゆるディスクリートパッケージに適用される。

このディスクリートパッケージでは、第1~第10の実施形態によるHEMTのチップが搭載される。以下、第1~第10の実施形態によるHEMTのチップ(以下、HEMTチップと言う)のディスクリートパッケージについて例示する。

#### [0150]

HEMTチップの概略構成を図22に示す。

HEMTチップ100では、その表面に、上述したA1GaN/GaN・HEMTのトランジスタ領域101と、ドレイン電極が接続されたドレインパッド102と、ゲート電極が接続されたゲートパッド103と、ソース電極が接続されたソースパッド104とが設けられている。

### [0151]

図23は、ディスクリートパッケージを示す概略平面図である。

ディスクリートパッケージを作製するには、先ず、HEMTチップ100を、ハンダ等のダイアタッチ剤111を用いてリードフレーム112に固定する。リードフレーム11 2にはドレインリード112aが一体形成されており、ゲートリード112b及びソースリード112cがリードフレーム112と別体として離間して配置される。

# [0152]

続いて、A1ワイヤ113を用いたボンディングにより、ドレインパッド102とドレインリード112a、ゲートパッド103とゲートリード112b、ソースパッド104とソースリード112cをそれぞれ電気的に接続する。

その後、モールド樹脂114を用いて、トランスファーモールド法によりHEMTチップ100を樹脂封止し、リードフレーム112を切り離す。以上により、ディスクリートパッケージが形成される。

#### [0153]

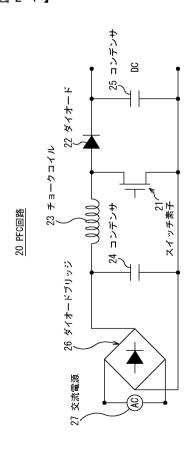

(第11の実施形態)

本実施形態では、第1~第10の実施形態から選ばれたHEMTを備えたPFC (Power Factor Correction) 回路を開示する。

図24は、PFC回路を示す結線図である。

#### [0154]

PFC回路20は、スイッチ素子(トランジスタ)21と、ダイオード22と、チョークコイル23と、コンデンサ24,25と、ダイオードブリッジ26と、交流電源(AC)27とを備えて構成される。スイッチ素子21に、第1~第10の実施形態から選ばれ

10

20

30

50

たHEMTが適用される。

#### [0155]

PFC回路20では、スイッチ素子21のドレイン電極と、ダイオード22のアノード端子及びチョークコイル23の一端子とが接続される。スイッチ素子21のソース電極と、コンデンサ24の一端子及びコンデンサ25の一端子とが接続される。コンデンサ24の他端子とチョークコイル23の他端子とが接続される。コンデンサ25の他端子とダイオード22のカソード端子とが接続される。コンデンサ24の両端子間には、ダイオードブリッジ26を介してAC27が接続される。コンデンサ25の両端子間には、直流電源(DC)が接続される。なお、スイッチ素子21には不図示のPFCコントローラが接続される。

10

## [0156]

本実施形態では、第1~第10の実施形態から選ばれたHEMTをPFC回路20に適用する。これにより、信頼性の高いPFC回路30が実現する。

# [0157]

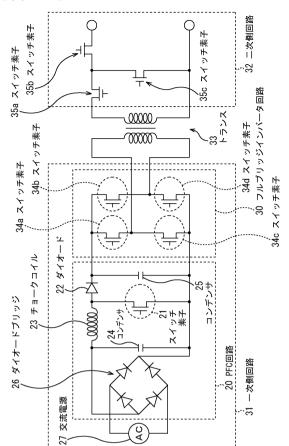

(第12の実施形態)

本実施形態では、第1~第10の実施形態から選ばれたHEMTを備えた電源装置を開示する。

図25は、第12の実施形態による電源装置の概略構成を示す結線図である。

#### [ 0 1 5 8 ]

本実施形態による電源装置は、高圧の一次側回路31及び低圧の二次側回路32と、一次側回路31と二次側回路32との間に配設されるトランス33とを備えて構成される。

一次側回路 3 1 は、第 1 1 の実施形態による P F C 回路 2 0 と、 P F C 回路 2 0 のコンデンサ 2 5 の両端子間に接続されたインバータ回路、例えばフルブリッジインバータ回路 3 0 とを有している。フルブリッジインバータ回路 3 0 は、複数 (ここでは 4 つ)のスイッチ素子 3 4 a , 3 4 b , 3 4 c , 3 4 d を備えて構成される。

二次側回路32は、複数(ここでは3つ)のスイッチ素子35a,35b,35cを備えて構成される。

#### [0159]

本実施形態では、一次側回路31を構成するPFC回路が第2の実施形態によるPFC回路20であると共に、フルブリッジインバータ回路30のスイッチ素子34a,34b,34c,34dが、第1~第10の実施形態から選ばれたHEMTとされている。一方、二次側回路32のスイッチ素子35a,35b,35cは、シリコンを用いた通常のMIS・FETとされている。

30

20

#### [0160]

本実施形態では、第11の実施形態によるPFC回路20と、第1~第10の実施形態から選ばれたHEMTとを、高圧回路である一次側回路31に適用する。これにより、信頼性の高い大電力の電源装置が実現する。

#### [0161]

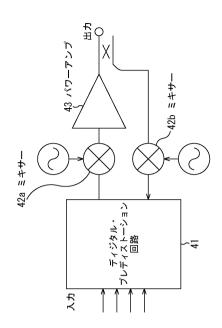

(第13の実施形態)

本実施形態では、第1~第10の実施形態から選ばれたHEMTを備えた高周波増幅器 40 を開示する。

図26は、第13の実施形態による高周波増幅器の概略構成を示す結線図である。

#### [0162]

本実施形態による高周波増幅器は、ディジタル・プレディストーション回路 4 1 と、ミキサー 4 2 a , 4 2 b と、パワーアンプ 4 3 とを備えて構成される。

ディジタル・プレディストーション回路41は、入力信号の非線形歪みを補償するものである。ミキサー42aは、非線形歪みが補償された入力信号と交流信号をミキシングするものである。パワーアンプ43は、交流信号とミキシングされた入力信号を増幅するものであり、第1の実施形態及び変形例のうちから選ばれた1種によるA1GaN/GaN・HEMTを有している。なお図26では、例えばスイッチの切り替えにより、出力側の

信号をミキサー42bで交流信号とミキシングしてディジタル・プレディストーション回路41に送出できる構成とされている。

#### [0163]

本実施形態では、第1~第10の実施形態から選ばれたHEMTを高周波増幅器に適用する。これにより、信頼性の高い高耐圧の高周波増幅器が実現する。

#### [0164]

以下、化合物半導体装置及びその製造方法、並びに電源装置及び高周波増幅器の諸態様を付記としてまとめて記載する。

#### [0165]

(付記1)二次元電子ガスが生成される化合物半導体積層構造と、

前記化合物半導体積層構造の上方に形成された電極と

を含み、

前記化合物半導体積層構造は、前記二次元電子ガスの生成部位の下方にp型半導体層を有しており、

前記p型半導体層は、前記電極の下方に位置整合する部分がその他の部分よりもイオン 化アクセプタ量が多いことを特徴とする化合物半導体装置。

#### [ 0 1 6 6 ]

(付記2)前記p型半導体層は、p-GaN、p-AlGaN、p-InAlN、及びp-AlNから選ばれた1種を材料とすることを特徴とする付記1に記載の化合物半導体装置。

[0167]

(付記3)前記p型半導体層は、前記その他の部分が不活性不純物を含有することを特徴とする付記1又は2に記載の化合物半導体装置。

#### [0168]

(付記4)前記p型半導体層は、前記その他の部分が前記イオン化アクセプタ量の多い部分よりも薄いことを特徴とする付記1又は2に記載の化合物半導体装置。

#### [0169]

(付記5)前記p型半導体層は、前記その他の部分が前記イオン化アクセプタ量の多い部分よりもイオン化アクセプタ濃度が低いことを特徴とする付記1又は2に記載の化合物半導体装置。

[0170]

(付記6)前記p型半導体層は、前記イオン化アクセプタ量の多い部分が前記電極の片方側に偏倚するように延在することを特徴とする付記1~5のいずれか1項に記載の化合物半導体装置。

# [0171]

(付記7)前記電極は、前記化合物半導体積層構造に接触して形成されることを特徴とする付記1~5のいずれか1項に記載の化合物半導体装置。

#### [0172]

(付記8)前記電極は、前記化合物半導体積層構造上で絶縁膜を介して形成されることを特徴とする付記1~5のいずれか1項に記載の化合物半導体装置。

[0173]

(付記9)前記電極は、前記化合物半導体積層構造に形成されたリセスを前記絶縁膜を介して埋め込むように形成されることを特徴とする付記8に記載の化合物半導体装置。

# [0174]

(付記10)二次元電子ガスが生成される化合物半導体積層構造を形成する工程と、前記化合物半導体積層構造の上方に電極を形成する工程と を含み、

前記化合物半導体積層構造を形成する際に、前記二次元電子ガスの生成部位の下方に相当する部分にp型半導体層を形成し、

前記p型半導体層は、前記電極の下方に位置整合する部分がその他の部分よりもイオン

10

20

30

40

化アクセプタ量が多いことを特徴とする化合物半導体装置の製造方法。

#### [0175]

(付記11)前記p型半導体層は、p-GaN、p-A1GaN、p-InA1N、及びp-A1Nから選ばれた1種を材料とすることを特徴とする付記10に記載の化合物半導体装置の製造方法。

#### [0176]

(付記12)前記p型半導体層は、前記その他の部分が不活性不純物を含有することを特徴とする付記10又は11に記載の化合物半導体装置の製造方法。

#### [0177]

(付記13)前記p型半導体層は、前記その他の部分が前記イオン化アクセプタ量の多い部分よりも薄いことを特徴とする付記10又は11に記載の化合物半導体装置の製造方法。

# [0178]

(付記14)前記p型半導体層は、前記その他の部分が前記イオン化アクセプタ量の多い部分よりもイオン化アクセプタ濃度が低いことを特徴とする付記10又は11に記載の化合物半導体装置の製造方法。

#### [0179]

(付記15)前記p型半導体層は、前記イオン化アクセプタ量の多い部分が前記電極の 片方側に偏倚するように延在することを特徴とする付記10~14のいずれか1項に記載 の化合物半導体装置の製造方法。

#### [0180]

(付記16)前記電極は、前記化合物半導体積層構造に接触して形成されることを特徴とする付記10~14のいずれか1項に記載の化合物半導体装置の製造方法。

#### [0181]

(付記17)前記電極は、前記化合物半導体積層構造上で絶縁膜を介して形成されることを特徴とする付記10~14のいずれか1項に記載の化合物半導体装置の製造方法。

#### [0182]

(付記18)前記電極は、前記化合物半導体積層構造に形成されたリセスを前記絶縁膜を介して埋め込むように形成されることを特徴とする付記17に記載の化合物半導体装置の製造方法。

#### [0183]

(付記19)変圧器と、前記変圧器を挟んで高圧回路及び低圧回路とを備えた電源回路 であって、

前記高圧回路はトランジスタを有しており、

前記トランジスタは、

二次元電子ガスが生成される化合物半導体積層構造と、

前記化合物半導体積層構造の上方に形成された電極と

#### を含み、

前記化合物半導体積層構造は、前記二次元電子ガスの生成部位の下方に p 型半導体層を有しており、

前記p型半導体層は、前記電極の下方に位置整合する部分がその他の部分よりもイオン 化アクセプタ量が多いことを特徴とする電源回路。

#### [0184]

(付記20)入力した高周波電圧を増幅して出力する高周波増幅器であって、

トランジスタを有しており、

前記トランジスタは、

二次元電子ガスが生成される化合物半導体積層構造と、

前記化合物半導体積層構造の上方に形成された電極と

#### を含み、

前記化合物半導体積層構造は、前記二次元電子ガスの生成部位の下方にp型半導体層を

20

10

30

40

#### 有しており、

前記p型半導体層は、前記電極の下方に位置整合する部分がその他の部分よりもイオン 化アクセプタ量が多いことを特徴とする高周波増幅器。

#### 【符号の説明】

# [0185]

- SiC基板

- 2 化合物半導体積層構造

- 2 a i GaN層

- 2 b , 1 2 , 1 3 バックバリア層

- 2 b 1 p G a N 部

- 2 b 2 , 2 b 3 , 2 b 4 , 2 b 5 , 2 b 6 , 2 b 7 , 2 b 8 , 2 b 9 p G a N 部

- 2 c 電子走行層

- 2 d 中間層

- 2 e , 1 1 電子供給層

- 2 e 1 , 2 f 1 , 2 f 2 電極用リセス

- 2 f キャップ層

- 3 ソース電極

- 4 ドレイン電極

- 5 保護膜

- 6 ゲート電極

- 12a p-AlGaN部

- 12b,12c p<sup>-</sup>-AlGaN部

- 13a p-InAlN部

- 13b,13c p<sup>-</sup>-InAlN部

- 2 0 PFC回路

- 21,34a,34b,34c,34d,35a,35b,35c スイッチ素子

- 22 ダイオード

- 23 チョークコイル

- 24,25 コンデンサ

- 26 ダイオードブリッジ

- 30 フルブリッジインバータ回路

- 3 1 一次側回路

- 二次側回路 3 2

- 33 トランス

- 4.1 ディジタル・プレディストーション回路

- 42a,42b ミキサー

- 43 パワーアンプ

- 100 HEMTチップ

- 101 トランジスタ領域

- 102 ドレインパッド

- 103 ゲートパッド

- 104 ソースパッド

- 111 ダイアタッチ剤

- 112 リードフレーム

- 112a ドレインリード

- 112b ゲートリード

- 1 1 2 c ソースリード

- 113 Al D 1 + 1

- 1 1 4 モールド樹脂

10

20

30

【図2】

(b)

(c)

【図4】

# 【図1】

# 【図3】

# 【図5】

(a)

# 【図6】

# 【図7】

(a)

(a)

# 【図9】

# 【図10】

# 【図11】

(a)

# 【図13】

# 【図14】

【図15】

【図16】

【図22】

【図21】

【図23】

【図24】

【図25】

【図26】

# フロントページの続き

(51) Int.CI. F I

H 0 1 L 21/205 (2006.01)

(72)発明者 多木 俊裕

神奈川県川崎市中原区上小田中4丁目1番1号 富士通株式会社内

審査官 小川 将之

(56)参考文献 特開2007-103451(JP,A)

特開2000-114275(JP,A)

特開2004-342810(JP,A)

特開2012-248632(JP,A)

(58)調査した分野(Int.CI., DB名)

H01L 29/778

H01L 29/78

H01L 29/812

H01L 21/336

H01L 21/338