## (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2008-72512 (P2008-72512A)

(43) 公開日 平成20年3月27日(2008.3.27)

| (51) Int.Cl. |                        | F I        |   | テーマコード(参考) |

|--------------|------------------------|------------|---|------------|

| HO4N 5/3     | 1 <b>3</b> 5 (2006.01) | HO4N 5/335 | P | 4M118      |

| HO1L 27/1    | 46 (2006.01)           | HO4N 5/335 | E | 5CO24      |

|              |                        | HO1L 27/14 | Α |            |

#### 審査請求 未請求 請求項の数 7 〇1. (全 12 百)

|           |                              | 普旦明小     | 不明不 明不頃の数 1 UL (主 12 貝) |  |  |

|-----------|------------------------------|----------|-------------------------|--|--|

| (21) 出願番号 | 特願2006-249952 (P2006-249952) | (71) 出願人 | 000001007               |  |  |

| (22) 出願日  | 平成18年9月14日 (2006. 9.14)      |          | キヤノン株式会社                |  |  |

|           |                              |          | 東京都大田区下丸子3丁目30番2号       |  |  |

|           |                              | (74) 代理人 | 100076428               |  |  |

|           |                              |          | 弁理士 大塚 康徳               |  |  |

|           |                              | (74) 代理人 | 100112508               |  |  |

|           |                              |          | 弁理士 高柳 司郎               |  |  |

|           |                              | (74) 代理人 | 100115071               |  |  |

|           |                              |          | 弁理士 大塚 康弘               |  |  |

|           |                              | (74) 代理人 | 100116894               |  |  |

|           |                              |          | 弁理士 木村 秀二               |  |  |

|           |                              | (72) 発明者 | 鈴木 聡史                   |  |  |

|           |                              |          | 東京都大田区下丸子3丁目30番2号 キ     |  |  |

|           |                              |          | ヤノン株式会社内                |  |  |

|           |                              |          | 最終頁に続く                  |  |  |

|           |                              |          | 東於貝に統く                  |  |  |

(54) 【発明の名称】撮像装置及びその制御方法、撮像システム

# (57)【要約】

【課題】高輝度の光量が入射されるダイナミックレンジ 拡張領域においても効果的なダイナミックレンジの拡大 を可能とすること。

【解決手段】撮像装置は、光を信号電荷に光電変換するフォトダイオード2と、フォトダイオード2に蓄積された信号電荷を一時的に蓄える浮遊拡散層7と、浮遊拡散層7に蓄積された信号電荷を除去するリセットスイッチ4、10と、フォトダイオード2から浮遊拡散層7に転送された信号電荷を電圧に変換して出力する出力部とを有する単位画素15を備える。撮像装置はまた、浮遊拡散層7に蓄積された信号電荷量を設定値と比較する比較器8と、を備える。リセットスイッチ4、10は、比較器8の比較結果に基づいて、浮遊拡散層7を異なるリセットレベルSVDD1、SVDD2でリセットする。

【選択図】図1

#### 【特許請求の範囲】

### 【請求項1】

光を信号電荷に光電変換する光電変換素子と、前記光電変換素子に蓄積された信号電荷を一時的に蓄える蓄積部と、前記蓄積部に蓄積された信号電荷を除去するリセット部とを有する画素を備える撮像装置であって、

前記蓄積部に蓄積された信号電荷量を設定値と比較する比較部を備え、

前記リセット部は、前記比較部の比較結果に基づいて前記蓄積部を異なるリセットレベルでリセットすることを特徴とする撮像装置。

#### 【請求項2】

前記リセット部は、前記蓄積部に蓄積された信号電荷量が前記設定値未満である場合には、前記蓄積部を第1のリセットレベルにリセットし、前記蓄積部に蓄積された信号電荷量が前記設定値以上の場合には、前記蓄積部を前記第1のリセットレベルとは異なる第2のリセットレベルにリセットすることを特徴とする請求項1に記載の撮像装置。

# 【請求項3】

前記画素は、前記光電変換素子から前記蓄積部に転送された信号電荷を電圧に変換して出力する出力部を更に有し、

当該撮像装置は、

前記出力部から出力された前記蓄積部の光信号成分とノイズ成分とを含む信号電荷を蓄積する第1の蓄積部と、

前記出力部から出力された前記蓄積部のリセット時のノイズ成分を含む信号電荷を蓄積する第2の蓄積部と、

前記第1の蓄積部に蓄積された信号電荷に基づく信号と前記第2の蓄積部に蓄積された信号電荷に基づく信号との差分信号を出力する差動出力部と、

を更に備えることを特徴とする請求項2に記載の撮像装置。

#### 【請求項4】

前記第2の蓄積部に蓄積された信号電荷に基づく信号を出力するノイズ信号モニタ部を更に備えることを特徴とする請求項3に記載の撮像装置。

#### 【請求項5】

前記ノイズ信号モニタ部による出力信号のレベルが前記第1のリセットレベルである場合には、前記差動出力部の出力信号をそのまま出力し、前記ノイズ信号モニタ部による出力信号のレベルが前記第2のリセットレベルである場合には、前記蓄積部を前記第2のリセットレベルにリセットするときに前記蓄積部に蓄積された信号電荷に基づく信号を前記差動出力部の出力信号に加算して出力する信号出力部を更に備えることを特徴とする請求項4に記載の撮像装置。

## 【請求項6】

光学系と、

請求項1乃至請求項5のいずれか1項に記載の撮像装置と、

を備える撮像システム。

# 【請求項7】

光を信号電荷に光電変換する光電変換素子と、前記光電変換素子に蓄積された信号電荷を一時的に蓄える蓄積部と、前記蓄積部に蓄積された信号電荷を除去するリセット部とを有する画素を備える撮像装置の制御方法であって、

前記蓄積部に蓄積された信号電荷量を設定値と比較する比較工程と、

前記比較工程での比較結果に基づいて前記蓄積部を異なるリセットレベルでリセットするリセット工程と、

を含むことを特徴とする撮像装置の制御方法。

# 【発明の詳細な説明】

### 【技術分野】

# [0001]

本発明は、光電変換素子を有する撮像装置及びその制御方法、撮像システムに関する。

10

20

30

50

40

#### 【背景技術】

# [0002]

従来、メモリ素子を有するメモリカードを記録媒体とし、CCDイメージセンサ、CMOSイメージセンサ等の撮像素子で撮像した画像を記録又は再生するデジタルカメラ等の撮像装置がある。特に、CMOSイメージセンサは、低電圧・低消費電力等の観点から、撮像装置に搭載する撮像素子として広く用いられている。

#### [00003]

図 6 ~図 8 は、従来の C M O S イメージセンサの構成及び駆動タイミングを示す図である。

# [0004]

図 6 は、従来の C M O S イメージセンサの構成を示す回路図である。単位画素 1 は、フォトダイオード 2 、転送スイッチ 3 、リセットスイッチ 4 、行選択スイッチ 5 、ソースフォロアアンプ 6 、浮遊拡散層(フローティングディフュージョン) 7 を備える。

# [0005]

フォトダイオード2は、光電変換素子であり、光を信号電荷に変換する。フォトダイオード2で生成された信号電荷は、パルスPTXにより駆動される転送スイッチ3を通口口アアンプ6のゲートに接続されたリセットスイッチ4に印加されるリセットパルスPRESによって、電位SVDDのレベルにリセットされる。浮遊拡散層7に蓄積された電声では、ソースフォロアアンプ6によって増幅される。行選択スイッチ5が選択される主により選択スイッチ5が選択されるされた信と、回路からの選択パルスPSELにより選択スイッチ5が選択されるれた信と、フォロワ回路により垂直出力線22に出力される。垂直出力線22に出力された信3に蓄積され、ノイズ出力パルスPTNにより駆動される転送ゲート24を通して転送を日口により駆動されるに蓄積され、ノイズ出力パルスPTNにより駆動される転送ゲート24を通して転送を日口により駆動されるに蓄積される。次いで、不図示の水平走査回路からの制御信号PHS、PHN30により駆動される転送スイッチ28、29を通して、ノイズ成分は容量CHN30にに号により駆動される転送スイッチ28、29を通して、ノイズ成分は容量CHN30にに号によりは容量CHS31に蓄積される。

# [0006]

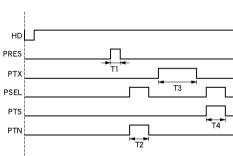

図7は、図6の撮像装置の駆動タイミングを示す図である。

# [0007]

まず、1水平走査期間の開始を示す信号HDの立下りに伴って、不図示の回路により、 垂直出力線22が設定された電位にリセットされる。

# [ 0 0 0 8 ]

T1の期間では、PRES信号がハイレベル(以下「H」という。)となり、これに応じてリセットスイッチ4がONされ、ソースフォロアアンプ6のゲートに接続された、浮遊拡散層7に蓄積された電荷が設定された電位SVDDにリセットされる。

# [00009]

T2の期間では、PRES信号がローレベル(以下「L」という。)となり、これに応じてリセットスイッチ4がOFFされる。また、PSEL信号がHとなり、これに応じて行選択スイッチ5と負荷電流源21で構成されたソースフォロワ回路が動作状態になり、垂直出力線22上にソースフォロアアンプ6のフローティングゲートのリセット電位に応じたノイズ出力がなされる。また、PTN信号がHとなり、転送容量CTN26が垂直出力線22と接続され、ノイズ成分の信号が転送容量CTN26に蓄積される。

# [0010]

次いで、フォトダイオード2で発生した信号電荷とノイズ成分との混合信号を蓄積する

## [0011]

まず、垂直出力線22は、不図示の回路により、設定された電位にリセットされる。

10

20

30

40

[ 0 0 1 2 ]

T3の期間では、PTX信号がHとなり、これに応じて転送スイッチ3がONされ、フォトダイオード2に蓄積された信号電荷がソースフォロアアンプ6のフローティングゲートに転送される。

[0013]

T4の期間では、PSEL信号がHとなり、これに応じて行選択スイッチ5と負荷電流源21で構成されたソースフォロワ回路が動作状態になり、垂直出力線22上にソースフォロアアンプ6のフローティングゲートのリセット電位に応じたノイズ出力がなされる。また、PTS信号がHとなり、「光信号成分+ノイズ成分」を蓄積する転送容量CTS27が垂直出力線22と接続され、「光信号成分+ノイズ成分」の信号が転送容量CTS27に保持される。

[0014]

このように、 1 行分のノイズ成分とフォトダイオードで発生した「光信号成分 + ノイズ成分」とが、転送容量 C T N 2 6 、転送容量 C T S 2 7 にそれぞれ蓄積される。

[0015]

次いで、これら 2 信号を不図示の水平走査回路により制御される制御パルス P H によって、容量 C H N 3 0 、容量 C H S 3 1 にそれぞれ転送する。容量 C H N 3 0 、容量 C H S 3 1 に蓄積されたノイズ成分と「光信号成分 + ノイズ成分」は、差動増幅器 3 2 によって、(光信号成分 + ノイズ成分) - ノイズ成分、すなわち光信号成分として出力される。

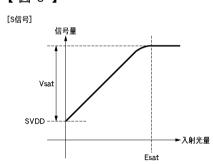

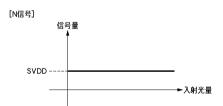

[0016]

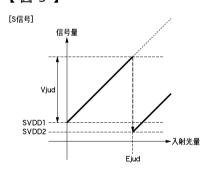

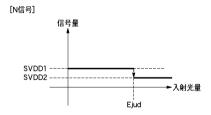

図8は、上述のCMOSイメージセンサを用いた撮像装置における「光信号成分+ノイズ成分」(以下「S信号」という。)及びノイズ成分(以下「N信号」という。)の入射光量に対する信号量の推移を表す図である。図8において、S信号は、一般的には飽和レベルVsatに達するか若しくはその近傍までは入射光量に比例して単調増加し、飽和レベルVsatに達する入射光量Esat以上の光量が入射した場合にはVsatを出力する。すなわち、このような撮像装置においては、Esat以上の入射光量は取り込めない。N信号は、入射光量によらず、浮遊拡散層7をリセットパルスPRESによってリセットする電位SVDDのレベルに相当する信号量となる。

[0017]

このような構造のCMOSイメージセンサやCCDイメージセンサを用いた撮像装置において、多くの光を取り込むために、ダイナミックレンジを拡大するための提案がなされている。従来は、飽和点近傍等の高輝度範囲における階調を落とすことによって、ダイナミックレンジを拡大している。

【発明の開示】

【発明が解決しようとする課題】

[0018]

しかしながら、従来の方法では、例えば、画像信号を記録した後、レベル補正等により、より高い輝度範囲の信号を中心に画像が構成されるように補正しようとしても、階調を落として記録されているため、満足のいく画像が得られない場合がある。すなわち、このような技術では、高輝度から低輝度までの広い輝度領域で満足のいく画像が得ることが困難であった。

[0019]

本発明は、上記の問題点に鑑みてなされたものであり、高輝度の光量が入射されるダイナミックレンジ拡張領域においても、効果的なダイナミックレンジの拡大を可能とすることを目的とする。

【課題を解決するための手段】

[0020]

本発明の第1の側面は、光を信号電荷に光電変換する光電変換素子と、前記光電変換素子に蓄積された信号電荷を一時的に蓄える蓄積部と、前記蓄積部に蓄積された信号電荷を除去するリセット部とを有する画素を備える撮像装置に係り、前記蓄積部に蓄積された信

10

20

30

. .

40

号電荷量を設定値と比較する比較部と、を備え、前記リセット部は、前記比較部の比較結果に基づいて前記蓄積部を異なるリセットレベルでリセットすることを特徴とする。

#### [0021]

本発明の第2の側面は、撮像システムに係り、光学系と、上記の撮像装置と、を備える

## [0022]

本発明の第3の側面は、光を信号電荷に光電変換する光電変換素子と、前記光電変換素子に蓄積された信号電荷を一時的に蓄える蓄積部と、前記蓄積部に蓄積された信号電荷を除去するリセット部とを有する画素を備える撮像装置の制御方法に係り、前記蓄積部に蓄積された信号電荷量を設定値と比較する比較工程と、前記比較工程での比較結果に基づいて前記蓄積部を異なるリセットレベルでリセットするリセット工程と、を含むことを特徴とする。

#### 【発明の効果】

# [0023]

本発明によれば、高輝度の光量が入射されるダイナミックレンジ拡張領域においても、 効果的なダイナミックレンジの拡大が可能となる。

【発明を実施するための最良の形態】

# [0024]

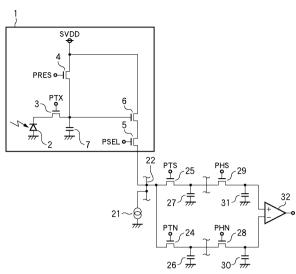

以下、図面を参照して本発明の好適な実施の形態を説明する。図1~図3は、本発明の好適な実施の形態に係るCMOSイメージセンサの構成及び駆動タイミングを示す図である。

#### [ 0 0 2 5 ]

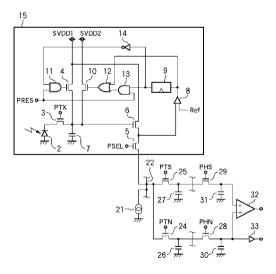

図1は、本発明の好適な実施の形態に係るCMOSイメージセンサの構成を示す回路図である。図4と同様の構成要素については、同じ参照符号を付している。単位画素15は、フォトダイオード2、フォトダイオード2、転送スイッチ3、リセットスイッチ4、行選択スイッチ5、ソースフォロアアンプ6、浮遊拡散層7、比較器8、ラッチ部9及びリセットスイッチ10を備える。単位画素15はまた、ANDゲート11、ORゲート12、ANDゲート13、インバーター14を備える。

# [0026]

フォトダイオード2は、光電変換素子であり、光を信号電荷に変換する。フォトダイオ ード2で生成された信号電荷は、パルスPTXにより駆動される転送スイッチ3を通して 浮遊拡散層7に転送される。転送された電荷は、浮遊拡散層7に蓄積される。浮遊拡散層 7は、ソースフォロアアンプ6のゲートに接続されたリセットスイッチ4に印加されるリ セットパルスPRESによって、電位SVDD1又はSVDD2のレベルにリセットされ る。浮遊拡散層7に蓄積された電荷は、ソースフォロアアンプ6によって増幅される。行 選択スイッチ 5 は、図 4 の垂直走査回路 2 2 0 からの制御パルスPSELにより選択され る。比較器8は、ソースフォロアアンプ6の出力をモニタし、そのレベル(電位)と予め 定められた基準レベルRef(電位)とを比較する。ラッチ部9は、比較器8の出力を1 水平期間固定する。リセットスイッチ10は、MOSトランジスタで構成され、浮遊拡散 層7の電位を電位SVDD2のレベルにリセットする。行選択スイッチ5が選択されると ソースフォロアアンプ 6 の出力が、行選択スイッチ 5 と負荷電流源 2 1により構成され たソースフォロワ回路により垂直出力線 2 2 に出力される。垂直出力線 2 2 は、図 4 の V SIG1~VSIGnのいずれかに対応する。垂直出力線22に出力された信号は、信号 出力パルスPTSにより駆動される転送ゲート25を通して転送容量CTS27に蓄積さ れ、ノイズ出カパルスPTNにより駆動される転送ゲート24を通して転送容量CTN2 6 に蓄積される。次いで、図4の水平走査回路からの制御パルスPHS、PHNにより駆 動される転送スイッチ28、29を通して、N信号は容量CHN30に、信号成分は容量 C H S 3 1 に蓄積される。 S 信号と N 信号との差分は、差動増幅器 3 2 によって画素信号 として出力される。また、出力アンプ33は、容量CHN30の蓄積容量をモニタするた めの出力アンプである。

30

20

10

40

#### [0027]

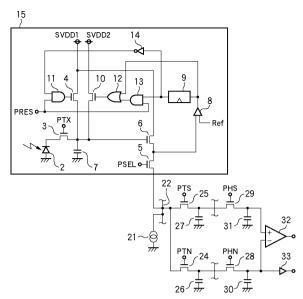

図2は、図1の撮像装置の駆動タイミングを示す図である。図2において水平走査期間 H1は蓄積期間中に入射光量が所定のレベル以上である場合の推移を表すものであり、水 平走査期間H2は入射光量が所定のレベル未満である場合の推移を表すものである。

# [0028]

まず、水平走査期間 H 1 の開始を示す信号 H D の立下りに伴って、不図示の回路により、垂直出力線 2 2 が設定された電位にリセットされる。

# [0029]

T 1 の期間では、 P R E S 信号が H となり、 ラッチ部 9 の出力が L であるため、 A N D ゲート 1 1 の 2 つの入力端子には、 H が入力される。 これにより、 A N D ゲート 1 1 が H を出力し、 リセットスイッチ 4 が O N され、 ソースフォロアアンプ 6 のゲートに接続された浮遊拡散層 7 が、 設定された第 1 の電位 S V D D 1 にリセットされる。 その後、 P R E S 信号が L となり、 A N D ゲート 1 1 が L を出力し、 リセットスイッチ 4 が O F F される

# [0030]

T2の期間では、PTX信号がHとなり、これに応じて転送スイッチ3がONし、フォトダイオード2に蓄積された信号電荷がソースフォロアアンプ6のフローティングゲートに転送され、浮遊拡散層7に蓄積される。PTX信号は、この信号電荷の蓄積期間中にハイレベルに維持され、比較器8により浮遊拡散層7に蓄積された信号電荷の量がモニタされる。浮遊拡散層7に蓄積された信号電荷量が設定値以上であれば、比較器8の出力はHとなる。比較器8の出力がHとなると、ORゲート12がHを出力し、リセットスイッチ10がONされ、浮遊拡散層7が第2の電位SVDD2にリセットされる。また、ラッチ部9の出力は、比較器8の出力がHになると、1水平期間H1ではHに固定される。蓄積期間T2後、PTX信号をローレベルとすることにより、転送スイッチ3がOFFされ、フォトダイオード2からの信号電荷の転送が停止される。

### [0031]

T3の期間では、PSEL信号がHとなり、これに応じて行選択スイッチ5と負荷電流源21で構成されたソースフォロワ回路が動作状態となる。そして、垂直出力線22上にソースフォロアアンプ6のフローティングゲートの電位に応じたS信号が出力される。また、PTS信号がHとなり、転送容量CTS27が垂直出力線22と接続され、S信号が転送容量CTS27に蓄積される。

# [0032]

次いで、N信号の転送が行われる。上述のように、T2の期間では、浮遊拡散層7に蓄積された信号電荷量が設定値以上となり、比較器8の出力がHとなっているため、ラッチ部9の出力はハイレベルに固定されている。

## [0033]

従って、T4の期間では、PRES信号がHとなり、ラッチ部9の出力がHであるため、ANDゲート4がLを出力し、ANDゲート11はHを出力する。これによって、リセットスイッチ4はOFFされ、リセットスイッチ10はONされて、浮遊拡散層7は第2の電位SVDD2にリセットされる。

# [0034]

T5の期間では、PSEL信号がHとなり、これに応じて行選択スイッチ5と負荷電流源21で構成されたソースフォロワ回路が動作状態になり、垂直出力線22上にソースフォロアアンプ6のフローティングゲートのリセット電位に応じたN信号が出力される。また、PTN信号がHとなり、N信号を蓄積する転送容量CTN26が垂直出力線22と接続され、N信号が転送容量CTN26に保持される。

#### [0035]

上述のように、1行分のフォトダイオードで発生したN信号とS信号とが、転送容量CTN26、転送容量CTS27にそれぞれ蓄積される。

# [0036]

40

10

20

30

次いで、これら2信号を図4の水平走査回路222により制御される制御パルスPHS、PHNによって、容量CHN30、容量CHS31にそれぞれ転送する。容量CHN30、容量CHS31に蓄積されたN信号とS信号は、差動増幅器32によって、S信号-N信号、すなわち光信号成分として出力される。

### [0037]

次いで、水平走査期間H2の開始を示す信号HDの立下りに伴って、不図示の回路により、垂直出力線22が設定された電位にリセットされる。

### [0038]

T11の期間では、PRES信号がHとなり、ラッチ部9の出力がLであるため、ANDゲート11の2つの入力端子には、Hが入力される。これにより、ANDゲート11がHを出力し、リセットスイッチ4がONされ、ソースフォロアアンプ6のゲートに接続された浮遊拡散層7が、設定された第1の電位SVDD1にリセットされる。その後、PRES信号がLとなり、ANDゲート11がLを出力し、リセットスイッチ4がOFFされる。

#### [0039]

T12の期間では、PTX信号がHとなり、これに応じて転送スイッチ3がONし、フォトダイオード2に蓄積された信号電荷がソースフォロアアンプ6のフローティングゲートに転送され、浮遊拡散層7に蓄積される。PTX信号は、この信号電荷の蓄積期間中にハイレベルに維持され、比較器8により浮遊拡散層7に蓄積された信号電荷の量がモニタされる。浮遊拡散層7に蓄積された信号電荷量が設定値以上であれば、比較器8の出力はHとなる。しかしながら、T12の期間では、浮遊拡散層7に蓄積された信号電荷量は設定値未満であり、比較器8の出力はLに固定される。蓄積期間T12後、PTX信号をローレベルとすることにより、転送スイッチ3がOFFされ、フォトダイオード2からの信号電荷の転送が停止される。

#### [0040]

T13の期間では、PSEL信号がHとなり、これに応じて行選択スイッチ5と負荷電流源21で構成されたソースフォロワ回路が動作状態になり、垂直出力線22上にソースフォロアアンプ6のフローティングゲートの電位に応じたS信号が出力される。また、PTS信号がHとなり、転送容量CTS27が垂直出力線22と接続され、S信号が転送容量CTS27に蓄積される。

#### [0041]

次いで、N信号の転送が行われる。上述のように、T12の期間では、浮遊拡散層7に蓄積された信号電荷量が設定値未満であり、比較器8の出力がLとなっているため、ラッチ部9の出力はローレベルに固定されている。

# [0042]

従って、T14の期間では、PRES信号がHとなり、ラッチ部9の出力がLであるため、ANDゲート4はHを出力し、ANDゲート11はLを出力する。その結果、リセットスイッチ4はONされ、リセットスイッチ10はOFFされて、浮遊拡散層7は第1の電位SVDD1にリセットされる。

### [0043]

T15の期間では、PSEL信号がHとなり、これに応じて行選択スイッチ5と負荷電流源21で構成されたソースフォロワ回路が動作状態となる。そして、垂直出力線22上にソースフォロアアンプ6のフローティングゲートのリセット電位に応じたノイズ出力がなされる。また、PTN信号がHとなり、N信号を蓄積する転送容量CTN26が垂直出力線22と接続され、N信号が転送容量CTN26に保持される。

# [ 0 0 4 4 ]

このように、水平走査期間 H 2 においても、水平走査期間 H 1 と同様に 1 行分の N 信号とフォトダイオードで発生した S 信号とが、転送容量 C T N 2 6 、転送容量 C T S 2 7 にそれぞれ蓄積される。

# [0045]

30

10

20

10

20

30

40

50

次いで、これら 2 信号を不図示の水平走査回路により制御される制御パルス P H によって、容量 C H N 3 0 、容量 C H S 3 1 にそれぞれ転送する。容量 C H N 3 0 、容量 C H S 3 1 に蓄積された N 信号と S 信号は、差動増幅器 3 2 によって、 S 信号 - N 信号、すなわち光信号成分として出力される。

# [0046]

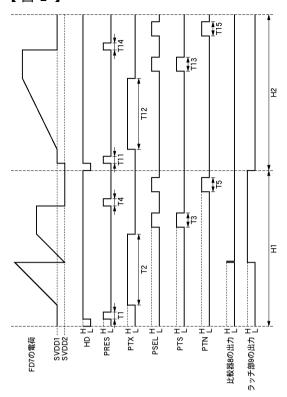

図3は、上述のCMOSイメージセンサを用いた撮像装置におけるS信号及びN信号の入射光量に対する信号量の推移を表す図である。図3において、S信号は、予め定められた判定レベルVjudに達する入射光量Ejud未満の範囲では、入射光量に比例して単調増加する。入射光量がEjud以上の範囲では、リセットスイッチ10がONされ、S信号が一旦電位SVDD2のレベルにリセットされる。その後、S信号は、Ejudに達した以降の入射光量、すなわち総入射光量からEjudを差し引いた光量分に比例して、リセット前と同じ傾きで単調増加する。N信号は、入射光量Ejud未満の範囲では、電位SVDD2のレベルに相当する信号量を出力し、入射光量がEjud以上の範囲では、SVDD2のレベルに相当する信号量を出力する。

# [0047]

従って、出力アンプ33によるN信号をモニタした結果、リセット電位SVDD1のレベルに相当する出力である場合には、入射光量が小さく、光信号蓄積中のリセットは行われていないと判断して、差動増幅器32の出力をそのまま光信号量とすればよい。

### [0048]

一方、出力アンプ33の出力が、リセット電位SVDD2のレベルに相当する出力である場合には、入射光量が大きく、光信号蓄積中のリセットが行われたと判断する。そして、図中の点線で示すような、差動増幅器32の出力に判定レベルVjudに相当する値を加えたものを光信号量とすればよい。

#### [0049]

以上のように、本発明の好適な実施の形態に係る撮像装置によれば、図6に示した飽和に達する入射光量Esat以上の入射光量を取り込むことが可能となり、ダイナミックレンジを拡大することができる。また、拡大されたダイナミックレンジ領域においても、通常時と同じ感度で入射光量を取り込むことができるため、階調性も失われない。

# [0050]

なお、本実施形態では、リセットする電位を1回だけ切り換える構成を例示的に説明したが、本発明はこれに限定されない。例えば、入射光量が所定の判定レベルVjudに達する度に、複数回信号電荷をリセットする構成を用いてもよい。この場合、リセットを行った回数を知るための手段としては、リセットレベルを3種類以上用意する手段を用いてもよいし、別途カウンタを用意して、リセット回数をカウントする手段を用いてもよい。

# [0051]

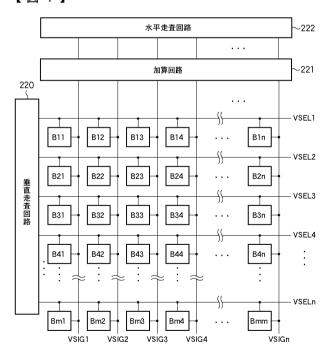

図4は、上述のCMOSイメージセンサを用いた撮像部の概観図である。B11~Bmn(m、nは整数である。以下同じ。)は撮像面に2次元に配置された画素15である。垂直走査回路220は、水平出力線VSEL1~VSELm毎に画素から電気信号を読み出す制御パルスを出力する。水平出力線VSEL1~VSELmにより選択された各画素の電気信号は、垂直出力線VSIGnにより読み出され、加算回路221に蓄積された電気信号は、水平走査回路222により順次読み出し走査が行われ、時系列的に出力される。水平出力線の制御パルスによって選択された各画素の電気信号は、垂直出力線VSIG1~VSIGnの制御パルスより加算回路21に読み出される。

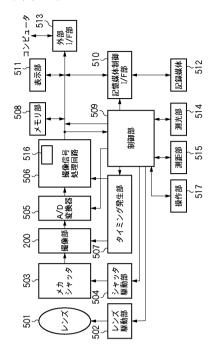

#### [0052]

図 5 は、図 4 の撮像部を用いた撮像システムの概略を示す図である。 5 0 1 は光学系としてのレンズ部(図 5 では「レンズ」と表記)、 5 0 2 はレンズ駆動部、 5 0 3 はメカニカルシャッタ(メカシャッタと表記)、 5 0 4 はメカニカルシャッタ駆動部(図 5 では「シャッタ駆動部」と表記)、 5 0 5 は A / D 変換器を示す。 2 0 0 は図 4 に示す構成を有する撮像部を示す。また、 5 0 6 は撮像信号処理回路、 5 0 7 はタイミング発生部、 5 0

8はメモリ部、509は制御部、510は記録媒体制御インターフェース部(図5では「記録媒体制御I/F部」と表記)、511は表示部を示す。また、512は記録媒体、513は外部インターフェース部(図5では「外部I/F部」と表記)、514は測光部、515は測距部を示す。撮像信号処理回路506は、A/D変換器505からの信号に基づいてホワイトバランス処理を行うWB回路516を含む。

[0053]

レンズ部 5 0 1 を通った被写体像は、撮像部 2 0 0 近傍に結像される。撮像部 2 0 0 近傍に結像した被写体像は、撮像部 2 0 0 により画像信号として取り込まれる。撮像信号処理回路 5 0 6 は、撮像部 2 0 0 から出力された画像信号を増幅し、アナログ信号からデジタル信号に変換(A/D変換)し、A/D変換後にR、G、G、Bの信号を得る。撮像信号処理回路 5 0 6 は、各種の補正、画像データの圧縮等を行う。

[0054]

レンズ部 5 0 1 は、レンズ駆動部 5 0 2 によってズーム、フォーカス、絞り等が駆動制御される。メカシャッタ 5 0 3 は、一眼レフカメラに使用されるフォーカルプレーン型型のシャッタの後幕に相当する幕のみを有するシャッタ機構である。メカシャッタ 5 0 3 は、シャッタ駆動部 5 0 4 によって駆動制御される。タイミング発生部 5 0 7 は、撮像 6 号処理回路 5 0 6 に各種タイミング信号を出力する。制御部 5 0 9 は、撮像 6 号処理回路 5 0 6 に各種タイミング信号を出力する。制御データを一時的に記録 媒体 5 1 2 に画像データを記録 媒体 5 1 2 に画像データを記録 媒体 5 1 2 に画像データを記録 はたり、記録 媒体 5 1 2 は、半導体メモリ等の着脱可能な記に画像でありに記録 像であり、記録 媒体 5 1 2 は、半導体メモリ等の着脱可能な記にのよいの表示を行う。記録 媒体 5 1 2 は、半導体メモリ等の着脱可能な記をのほのである。外部インターフェースである。別光部 5 1 4 は被写体の明るさ情報の検出を行い、測距部 5 1 5 は被写体までの距離情報を検出する。 5 1 6 は、ホワイトバランス回路、測距部 5 1 5 は被写体までの距離情報を検出する。 5 1 6 は、ホワイトバランス回路、

【図面の簡単な説明】

[0055]

【図1】本発明の好適な実施の形態に係るCMOSイメージセンサの構成を示す回路図である。

【図2】本発明の好適な実施の形態に係る撮像装置の駆動タイミングを示す図である。

【図3】本発明の好適な実施の形態に係る撮像装置における信号レベルの推移を表す図である。

【図4】CMOSイメージセンサを用いた撮像部の概観図である。

【図5】図4の撮像部を用いた撮像システムの概略を示す図である。

【図6】従来のCMOSイメージセンサの構成を示す回路図である。

【図7】従来の撮像装置の駆動タイミングを示す図である。

【図8】従来の撮像装置における信号レベルの推移を表す図である。

【符号の説明】

[0056]

2 フォトダイオード

4、10 リセットスイッチ

7 浮遊拡散層

8 比較器

15 単位画素

SVDD1、SVDD2 リセットレベル

20

10

30

【図1】

【図2】

【図3】

【図4】

# 【図5】

# 【図6】

# 【図7】

# 【図8】

# フロントページの続き

F ターム(参考) 4M118 AA02 AB01 BA14 CA02 DB09 DD04 DD12 FA06 FA34 FA42 5C024 CX43 GX03 GY35 GY38 HX28 HX29 HX35