# (19) 대한민국특허청(KR)

# (12) 등록특허공보(B1)

(51) 국제특허분류(Int. Cl.)

*G11C* 16/26 (2006.01) *G11C* 16/10 (2006.01) *G11C* 16/30 (2006.01) *G11C* 16/32 (2006.01)

(52) CPC특허분류

*G11C* 16/26 (2013.01) *G11C* 16/10 (2013.01)

(21) 출원번호 10-2017-0104140

(22) 출원일자 2017년08월17일

심사청구일자 **2020년08월11일** (65) 공개번호 **10-2019-0019364**

(43) 공개일자 **2019년02월27일**

(56) 선행기술조사문헌 KR1020150080819 A\* (뒷면에 계속)

전체 청구항 수 : 총 9 항

(45) 공고일자 2024년01월31일

(11) 등록번호 10-2631353

(24) 등록일자 2024년01월25일

(73) 특허권자

#### 삼성전자주식회사

경기도 수워시 영통구 삼성로 129 (매탄동)

(72) 발명자

#### 전수창

서울특별시 서초구 효령로49길 57, 201동 806호 (서초동, 서초2차이편한세상)

#### 고귀한

서울특별시 서초구 서초중앙로 206, E동 803호 ( 반포동, 삼호가든맨션)

(뒷면에 계속)

(74) 대리인

리앤목특허법인

심사관 : 한선경

#### (54) 발명의 명칭 비휘발성 메모리 장치 및 이의 동작 방법

#### (57) 요 약

비휘발성 메모리 장치 및 이의 동작 방법이 개시된다. 본 개시에 따른 비휘발성 메모리 장치의 동작 방법은 복수의 프로그램 루프들 중 제1 프로그램 루프에 대응하는 프로그램 동작을 수행하는 단계, 상기 프로그램 동작 중 긴급 독출을 위한 서스팬드 커맨드를 수신하는 단계, 상기 서스팬드 커맨드의 대응하여 상기 서스팬드 커맨드 수신 직후의 제1 시점 및 상기 제1 프로그램 루프에 대응하는 프로그램 동작 종료 후의 제2 시점 중 어느 하나를리커버리 시점으로 결정하는 단계 및 결정된 리커버리 시점에서 상기 프로그램 대상이 되는 선택 워드라인에 리커버리 전압을 인가함으로서 리커버리를 수행하는 단계를 포함할 수 있다.

### 대 표 도 - 도2

(52) CPC특허분류

*G11C* 16/30 (2013.01) *G11C* 16/32 (2013.01)

(72) 발명자

### 곽동훈

경기도 화성시 동탄공원로 21-40, 928동 1703호 ( 능동, 동탄푸른마을두산위브아파트)

#### 김진영

서울특별시 관악구 호암로16길 5, 101동 1303호 ( 신림동, 신림서초아파트) (56) 선행기술조사문헌

KR1020160028076 A\*

KR1020140059102 A

KR1020170059102 A

US20160210050 A1

US20140047167 A1

JP2014186787 A

JP2012043496 A

\*는 심사관에 의하여 인용된 문헌

#### 명세서

### 청구범위

#### 청구항 1

복수의 프로그램 루프들 중 제1 프로그램 루프에 대응하는 프로그램 동작을 수행하는 단계;

상기 프로그램 동작 중 긴급 독출 동작을 위한 서스팬드 커맨드를 수신하는 단계;

상기 제1 프로그램 루프에 대응하는 프로그램 동작 수행 중 수신하는 상기 서스팬드 커맨드를 카운팅하여 서스 팬드 카운트를 생성하는 단계;

상기 서스팬드 커맨드에 기초하여 상기 서스팬드 커맨드 수신 직후의 제1 시점 및 상기 제1 프로그램 루프에 대응하는 프로그램 동작 종료 후의 제2 시점 중 어느 하나를 리커버리 시점으로 결정하는 단계; 및

결정된 리커버리 시점에서 상기 프로그램 동작의 대상이 되는 선택 워드라인에 리커버리 전압을 인가함으로서 리커버리를 수행하는 단계;를 포함하고,

상기 결정하는 단계는,

상기 서스팬드 카운트가 기준 카운트 이상인 경우 상기 리커버리 시점을 상기 제2 시점으로 결정하는 단계를 포함하는 비휘발성 메모리 장치의 동작 방법.

#### 청구항 2

제1항에 있어서,

상기 리커버리를 수행하는 단계가 완료된 후 상기 긴급 독출 동작을 수행하는 단계;

상기 프로그램 동작을 수행하기 위한 리쥼 커맨드를 수신하는 단계; 및

상기 리쥼 커맨드에 대응하여 상기 프로그램 동작을 다시 수행하는 단계;를 더 포함하는 비휘발성 메모리 장치의 동작 방법.

#### 청구항 3

제2항에 있어서,

상기 프로그램 동작을 다시 수행하는 단계는,

상기 결정하는 단계에서 결정된 상기 리커버리 시점이 상기 제1 시점인 경우 상기 제1 프로그램 루프를 다시 수행하는 것을 특징으로 하는 비휘발성 메모리 장치의 동작 방법.

#### 청구항 4

제2항에 있어서,

상기 프로그램 동작을 다시 수행하는 단계는,

상기 결정하는 단계에서 결정된 상기 리커버리 시점이 상기 제2 시점인 경우, 상기 제1 프로그램 루프의 다음 루프에 해당하는 제2 프로그램 루프를 수행하는 것을 특징으로 하는 비휘발성 메모리 장치의 동작 방법.

#### 청구항 5

제1항에 있어서,

상기 제1 프로그램 루프에 대응하는 프로그램 동작을 수행하는 단계는 제k 공급 전압을 포함하는 제1 내지 제N 공급 전압(N은 1이상의 정수, k는 1 이상 N 이하의 정수)을 순차적으로 인가하는 단계를 포함하고,

상기 결정하는 단계는,

상기 제k 공급 전압이 인가된 이후에 상기 서스팬드 커맨드를 수신한 경우 상기 리커버리 시점을 상기 제2 시점

으로 결정하는 단계;를 포함하는 것을 특징으로 하는 비휘발성 메모리 장치의 동작 방법.

#### 청구항 6

제1항에 있어서,

상기 프로그램 동작을 수행하는 단계는 상기 선택 워드라인의 전압을 높이는 단계;를 더 포함하고,

상기 결정하는 단계는,

상기 서스팬드 커맨드를 수신한 시점에서의 상기 선택 워드라인의 전압이 기준 전압 이상인 경우 상기 리커버리 시점을 상기 제2 시점으로 결정하는 단계;를 포함하는 것을 특징으로 하는 비휘발성 메모리 장치의 동작 방법.

#### 청구항 7

제1항에 있어서,

상기 프로그램 동작을 수행하는 단계는 상기 선택 워드라인의 전압을 높이는 단계; 및

상기 선택 워드라인의 전압을 높이는 단계가 시작되는 시점부터 상기 서스팬드 커맨드를 수신하는 시점까지의 소요 시간을 카운팅하는 단계;를 더 포함하고,

상기 결정하는 단계는,

카운팅된 상기 소요 시간이 기준 시간 이상인 경우 상기 리커버리 시점을 상기 제2 시점으로 결정하는 단계;를 포함하는 것을 특징으로 하는 비휘발성 메모리 장치의 동작 방법.

#### 청구항 8

삭제

### 청구항 9

제1항에 있어서,

상기 제1 프로그램 루프에 대응하는 프로그램 동작을 수행하는 단계는 제k 공급 전압을 포함하는 제1 내지 제N 공급 전압(N은 1이상의 정수, k는 1 이상 N 이하의 정수)을 순차적으로 인가하는 단계를 포함하고,

상기 결정하는 단계는,

상기 서스팬드 카운트가 기준 카운트 이하이고 상기 제k 공급 전압이 인가되기 전에 상기 서스팬드 커맨드를 수신한 경우, 상기 리커버리 시점을 상기 제1 시점으로 결정하는 단계; 및

상기 서스팬드 카운트가 기준 카운트 이하이고 상기 제k 공급 전압이 인가된 이후에 상기 서스팬드 커맨드를 수 신한 경우, 상기 리커버리 시점을 상기 제2 시점으로 결정하는 단계;를 더 포함하는 것을 특징으로 하는 비휘발 성 메모리 장치의 동작 방법.

#### 청구항 10

프로그램 커맨드에 대응하여 제1 내지 제N 공급 전압(N은 1이상의 정수)을 순차적으로 인가함으로서 프로그램 대상이 되는 선택 워드라인의 전압 레벨을 증가시키는 단계;

긴급 독출 동작을 위한 서스팬드 커맨드를 수신하는 단계;

제1 프로그램 루프에 대응하는 프로그램 동작 수행 중 수신하는 상기 서스팬드 커맨드를 카운팅하여 서스팬드 카운트를 생성하는 단계;

상기 서스팬드 커맨드에 기초하여 리커버리 시점에 따른 리커버리 모드를 결정하는 단계;

결정된 상기 리커버리 모드에 따라서 리커버리를 수행하는 단계; 및

독출 커맨드에 대응하여 긴급 독출 동작을 수행하는 단계;를 포함하고,

상기 리커버리 모드는 상기 서스팬드 커맨드 수신 직후에 리커버리를 수행하는 캔슬 모드 및 상기 선택 워드라 인의 전압 레벨을 목표 전압까지 도달 시킨 후 리커버리를 수행하는 루프 모드 중 어느 하나이고, 상기 리커버리를 수행하는 단계는,

상기 서스팬드 카운트가 기준 카운트 이상인 경우 상기 리커버리 시점을 제2 시점으로 결정하는 단계를 포함하는 비휘발성 메모리 장치의 동작 방법.

#### 발명의 설명

### 기술분야

[0001] 본 개시의 기술적 사상은 메모리 장치에 관한 것으로서, 더욱 상세하게는 프로그램 동작 도중 긴급 독출 요청을 수행하는 비휘발성 메모리 장치에 관한 것이다.

#### 배경기술

- [0002] 반도체 메모리 장치(semiconductor memory device)는 실리콘(Si, silicon), 게르마늄(Ge, Germanium), 비화 갈륨(GaAs, gallium arsenide), 인화 인듐(InP, indium phospide) 등과 같은 반도체를 이용하여 구현되는 기억 장치이다. 반도체 메모리 장치는 크게 휘발성 메모리 장치(Volatile Memory Device) 및 비휘발성 메모리 장치 (Nonvolatile Memory Device)로 구분될 수 있다.

- [0003] 비휘발성 메모리 장치는 전원 공급이 차단되어도 저장하고 있던 데이터가 소멸하지 않는 메모리 장치이다. 비휘 발성 메모리 장치에는 ROM, PROM, EPROM, 플래시 메모리장치, PRAM, MRAM, RRAM, FRAM 등이 있다. 플래시 메모리 장치는 크게 노어 타입과 낸드 타입으로 구분될 수 있다.

#### 발명의 내용

# 해결하려는 과제

[0004] 본 개시의 기술적 사상이 해결하고자 하는 과제는 프로그램 동작 도중 수신하는 긴급 독출(Urgent Read) 요청을 효율적으로 수행하는 비휘발성 메모리 장치 및 이의 동작 방법을 제공하는데 있다.

#### 과제의 해결 수단

- [0005] 상기와 같은 목적을 달성하기 위하여, 본 개시의 기술적 사상의 일측면에 따른 비휘발성 메모리 장치의 동작 방법은 복수의 프로그램 루프들 중 제1 프로그램 루프에 대응하는 프로그램 동작을 수행하는 단계, 상기 프로그램 동작 중 긴급 독출을 위한 서스팬드 커맨드를 수신하는 단계, 상기 서스팬드 커맨드의 대응하여 상기 서스팬드 커맨드 수신 직후의 제1 시점 및 상기 제1 프로그램 루프에 대응하는 프로그램 동작 종료 후의 제2 시점 중 어느 하나를 리커버리 시점으로 결정하는 단계 및 결정된 리커버리 시점에서 상기 프로그램 대상이 되는 선택 워드라인에 리커버리 전압을 인가함으로서 리커버리를 수행하는 단계를 포함할 수 있다.

- [0006] 본 개시의 기술적 사상의 일측면에 따른 비휘발성 메모리 장치의 동작 방법은 프로그램 커맨드에 대응하여 제1 내지 제N 공급 전압(N은 1이상의 정수)을 순차적으로 인가함으로서 프로그램 대상이 되는 선택 워드라인의 전압 레벨을 증가시키는 단계, 서스팬드 커맨드에 대응하여 리커버리 시점에 따른 리커버리 모드를 결정하는 단계, 결정된 상기 리커버리 모드에 따라서 리커버리를 수행하는 단계 및 리드 커맨드에 대응하여 리드를 수행하는 단계를 포함하고, 상기 리커버리 모드는 상기 서스팬드 커맨드 수신 직후에 리커버리를 수행하는 캔슬 모드 및 상기 선택 워드라인의 전압 레벨을 목표 전압까지 도달 시킨 후 리커버리를 수행하는 루프 모드 중 어느 하나인 것을 특징으로 할 수 있다.

- [0007] 본 개시의 기술적 사상의 일측면에 따른 비휘발성 메모리 장치는 워드라인 및 비트라인과 연결되는 복수의 메모리 셀들을 포함하는 메모리 셀 어레이, 프로그램 커맨드에 대응하여 상기 워드라인 중 프로그램 대상이 되는 선택 워드라인의 전압 레벨을 증가시키기 위해 상기 선택 워드라인에 프로그램 전압을 인가하고, 상기 프로그램 동작 중 긴급 독출 동작을 위한 서스팬드 커맨드에 대응하여 리커버리 모드에 따라 상기 선택 워드라인에 리커버리 전압을 인가하는 제어 로직 및 상기 제어 로직에 상기 리커버리 전압을 인가하는 리커버리 시점에 대한 정보를 출력함으로서 상기 리커버리 모드를 결정하는 리커버리 모드 매니저를 포함하고, 상기 리커버리 모드는 상기 서스팬드 커맨드 수신 직후에 상기 리커버리 전압을 인가하는 캔슬 모드 및 상기 선택 워드라인의 전압 레벨을 목표 전압까지 도달 시킨 후 상기 리커버리 전압을 인가하는 루프 모드 중 어느 하나인 것을 특징으로 할 수있다.

#### 발명의 효과

[0008] 본 개시의 기술적 사상에 따른 비휘발성 메모리 장치는 프로그램 동작 도중 긴급 독출(Urgent Read)를 수행하기 위해 수신하는 서스팬드 커맨드에 대응하여, 미리 결정된 조건에 따라서 프로그램 대상이 되는 선택 워드라인의 리커버리 시점을 결정함으로서, 기입 지연 현상(Write Starvation)이 방지되고, 효율적인 긴급 독출 동작이 수행될 수 있다.

#### 도면의 간단한 설명

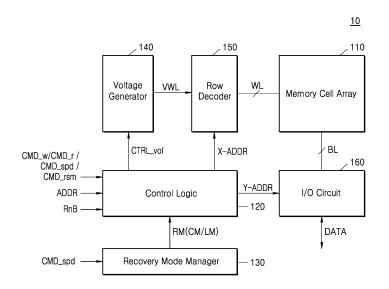

[0009] 도 1은 본 개시의 예시적 실시예에 따른 비휘발성 메모리 시스템을 나타내는 블록도이다.

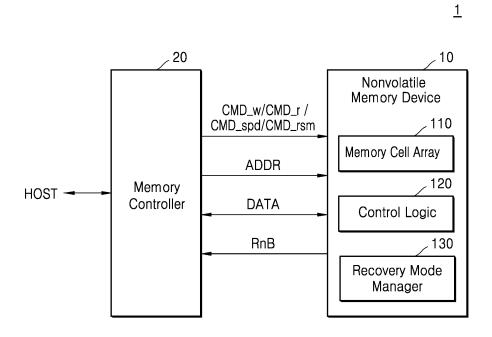

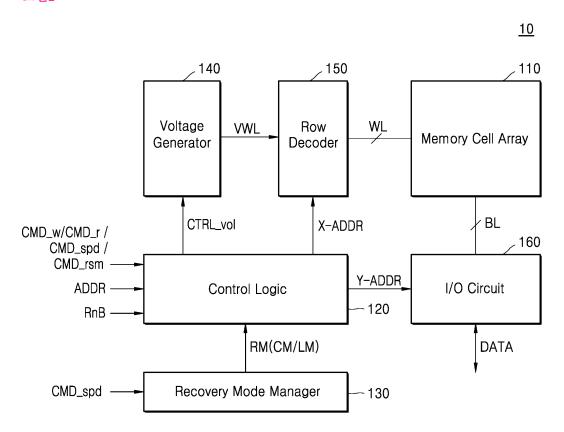

도 2는 본 개시의 예시적 실시예에 따른 비휘발성 메모리 장치를 나타내는 블록도이다.

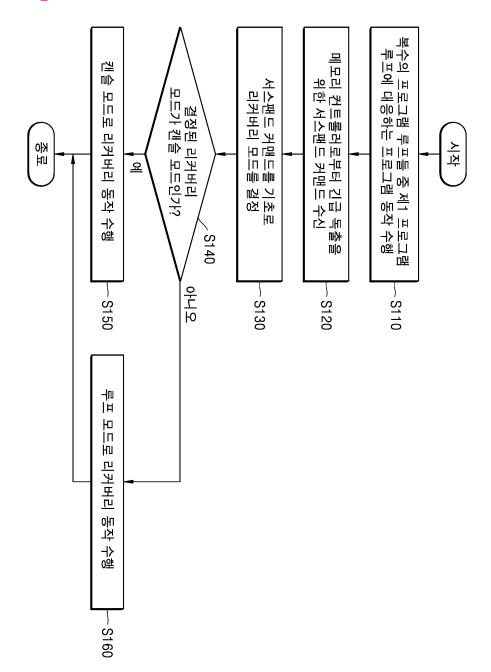

도 3은 본 개시의 예시적 실시예에 따른 비휘발성 메모리 장치의 동작을 나타내는 순서도이다.

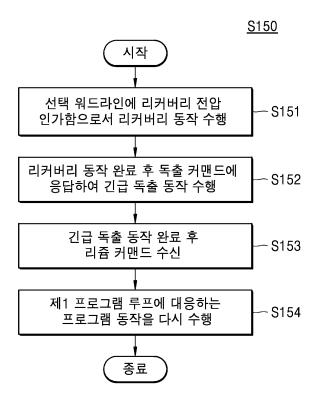

도 4a는 본 개시의 예시적 실시예에 따른 비휘발성 메모리 장치의 동작을 나타내는 순서도이다.

도 4b는 본 개시의 예시적 실시예에 따른 비휘발성 메모리 장치의 동작을 나타내는 순서도이다.

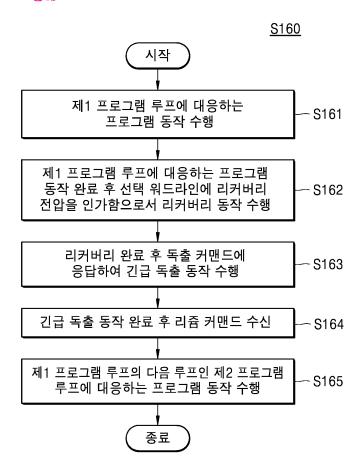

도 5는 본 개시의 예시적 실시예에 따른 메모리 셀 어레이에 포함된 메모리 블록을 나타내는 회로도이다.

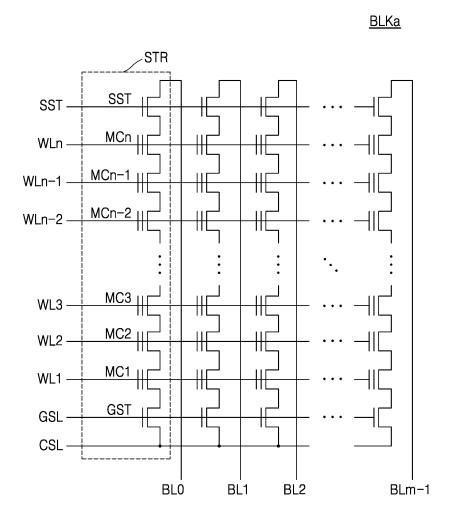

도 6는 본 개시의 예시적 실시예들에 따른 메모리 셀 어레이에 포함된 메모리 블록의 다른 예를 나타내는 회로 도이다.

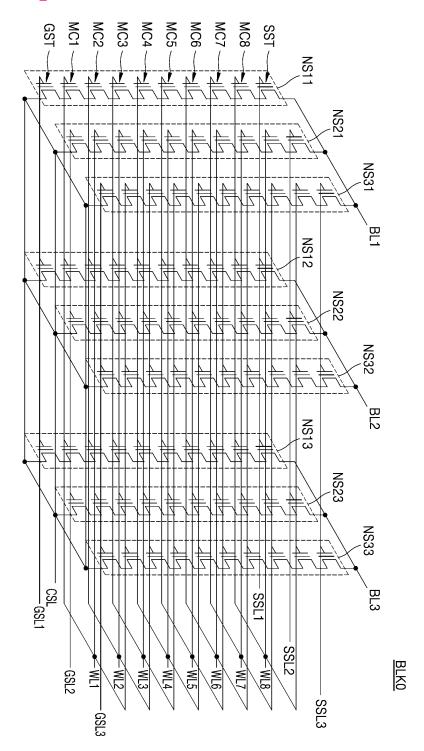

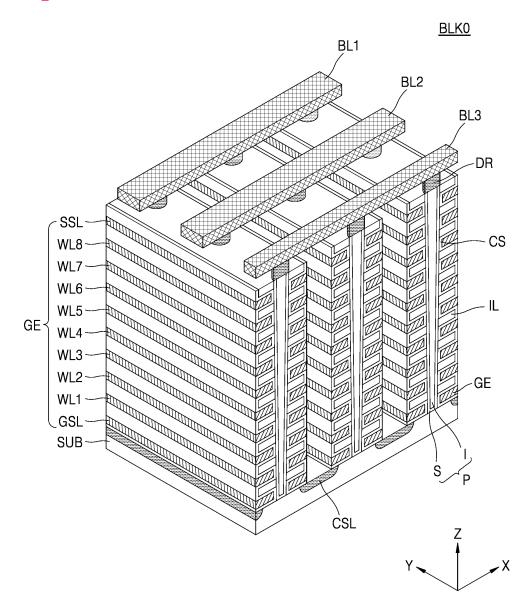

도 7은 도 6의 메모리 블록을 나타내는 사시도이다.

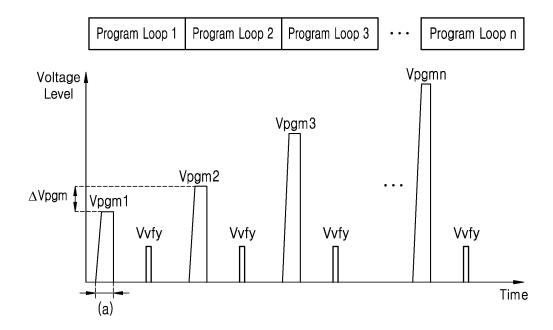

도 8는 본 개시의 예시적 실시예에 따른 비휘발성 메모리 장치의 프로그램 동작을 나타내는 그래프이다.

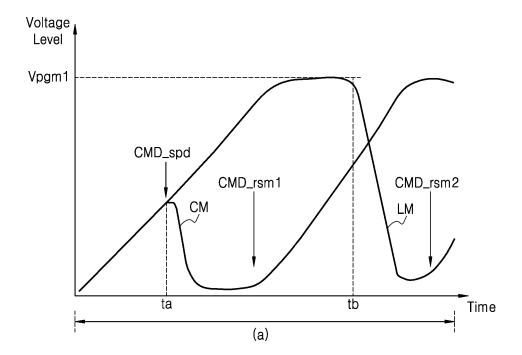

도 9는 본 개시의 예시적 실시예에 따른 비휘발성 메모리 장치의 선택 워드라인의 전압 레벨을 나타내는 그래프이다.

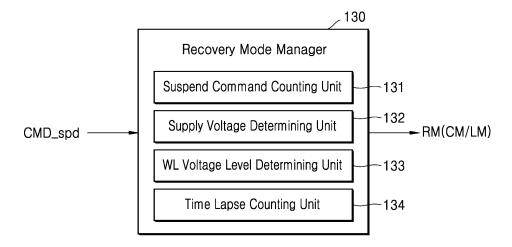

도 10은 본 개시의 예시적 실시예에 따른 리커버리 모드 매니저를 나타내는 블록도이다.

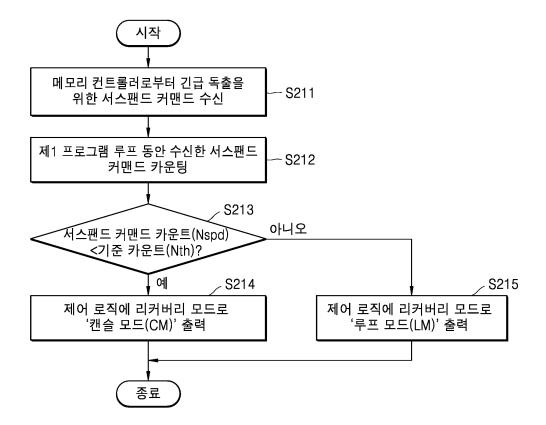

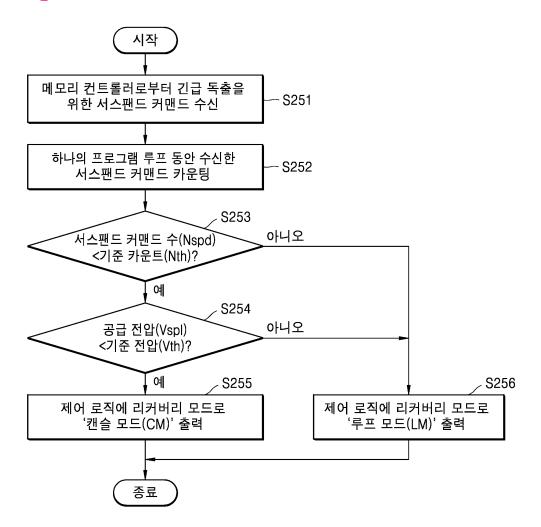

도 11a는 본 개시의 예시적 실시예에 따른 리커버리 모드 매니저의 동작을 나타내는 순서도이다.

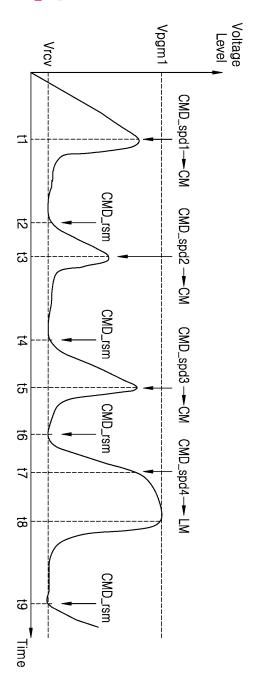

도 11b는 본 개시의 예시적 실시예에 따른 리커버리 모드 매니저의 동작을 나타내는 그래프이다.

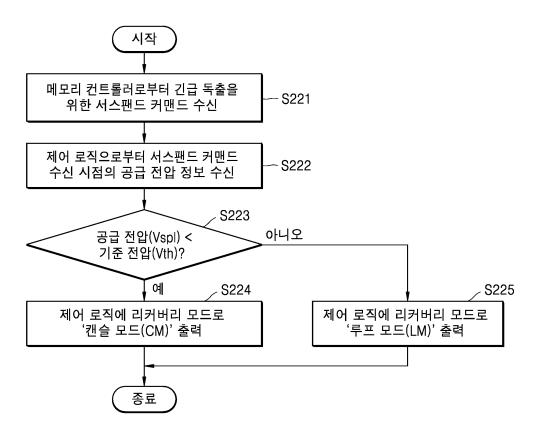

도 12a는 본 개시의 예시적 실시예에 따른 리커버리 모드 매니저의 동작을 나타내는 순서도이다.

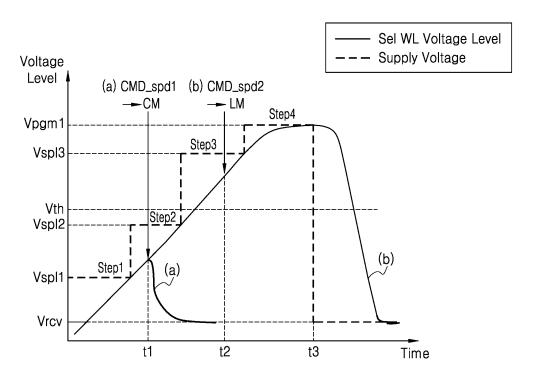

도 12b는 본 개시의 예시적 실시예에 따른 리커버리 모드 매니저의 동작을 나타내는 그래프이다.

도 13a는 본 개시의 예시적 실시예에 따른 리커버리 모드 매니저의 동작을 나타내는 순서도이다.

도 13b는 본 개시의 예시적 실시예에 따른 리커버리 모드 매니저의 동작을 나타내는 그래프이다.

도 14a는 본 개시의 예시적 실시예에 따른 리커버리 모드 매니저의 동작을 나타내는 순서도이다.

도 14b는 본 개시의 예시적 실시예에 따른 리커버리 모드 매니저의 동작을 나타내는 그래프이다.

도 15는 본 개시의 예시적 실시예에 따른 리커버리 모드 매니저의 동작을 나타내는 순서도이다.

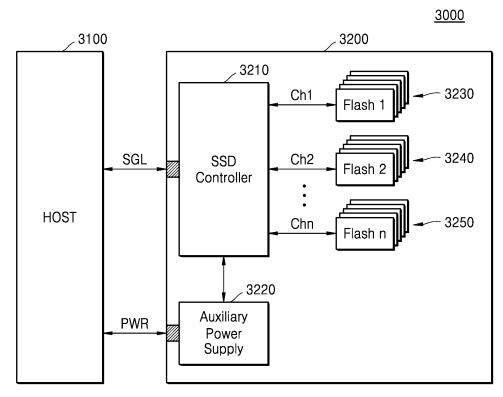

도 16은 본 개시의 예시적 실시예에 따른 비휘발성 메모리 장치를 SSD 시스템에 적용한 예를 나타내는 블록도이다.

#### 발명을 실시하기 위한 구체적인 내용

[0010]

도 1은 본 개시의 예시적 실시예에 따른 비휘발성 메모리 시스템을 나타내는 블록도이다.

[0011] 도 1을 참조하면, 비휘발성 메모리 시스템(1)은 워크스테이션, 넷북(net-book), PDA(Personal Digital Assistants), 포터블(portable) 컴퓨터, 웹 타블렛(web tablet), 무선 전화기(wireless phone), 모바일 폰, 스마트 폰, e-북(e-book), PMP(portable multimedia player), 휴대용 게임기, 네비게이션 장치, 블랙박스, 디지털 카메라, DMB (Digital Multimedia Broadcasting) 재생기, 디지털 음성 녹음기(digital audio recorder), 디지털 음성 재생기(digital audio player), 디지털 영상 녹화기(digital picture recorder), 디지털 영상 재생기(digital picture player), 디지털 동영상 녹화기(digital video recorder), 디지털 동영상 재생기(digital

video player) 등과 같은 컴퓨팅 시스템들 중 하나로 제공될수 있다.

- [0012] 비휘발성 메모리 시스템(1)은 메모리 컨트롤러(20) 및 비휘발성 메모리 장치(10)를 포함할 수 있다. 일 예시에서, 호스트(HOST), 메모리 컨트롤러(20) 및 비휘발성 메모리 장치(10) 각각은 하나의 칩, 하나의 패키지, 하나의 모듈 등으로 제공될 수 있다. 또는 메모리 컨트롤러(20) 및 비휘발성 메모리 장치(10)는 PoP(Package on Package), Ball grid arrays(BGAs), Chip scale packages(CSPs), Plastic Leaded Chip Carrier(PLCC), Plastic Dual In-Line Package(PDIP), Die in Waffle Pack, Die in Wafer Form, Chip On Board(COB), Ceramic Dual In-Line Package(CERDIP), Plastic Metric Quad Flat Pack(MQFP), Thin Quad Flatpack(TQFP), Small Outline(SOIC), Shrink Small Outline Package(SSOP), Thin Small Outline(TSOP), Thin Quad Flatpack(TQFP), System In Package(SIP), Multi Chip Package(MCP), Wafer-level Fabricated Package(WFP), Wafer-Level Processed Stack Package(WSP) 등과 같은 패키지들을 이용하여 실장되어 제공될 수 있다.

- [0013] 메모리 컨트롤러(20)는 호스트(HOST)로부터 수신된 기입 요청 또는 독출 요청에 응답하여 비휘발성 메모리 장치(10)를 제어할 수 있다. 예를 들어, 메모리 컨트롤러(20)는 호스트로부터 수신된 기입 요청 또는 독출 요청에 응답하여 기입 커맨드(CMD\_w) 또는 독출 커맨드(CMD\_r)를 비휘발성 메모리 장치(10)로 전송할 수 있다. 또는 메모리 컨트롤러(20)는 서스펜드 커맨드(CMD\_spd, suspend command), 리츔 커맨드(CMD\_rsm, resume command), 및 어드레스(ADDR)를 전송할 수 있다. 메모리 컨트롤러(20)가 비휘발성 메모리 장치(10)로 전송하는 어드레스(ADDR)는 비휘발성 메모리 장치(10)의 물리적 어드레스일 수 있다. 메모리 컨트롤러(20)는 비휘발성 메모리 장치(10)로부터 레디/비지 신호(RnB)를 수신할 수 있다.

- [0014] 비휘발성 메모리 장치(10)는 메모리 컨트롤러(20)로부터 수신된 신호들에 응답하여, 기입, 독출, 소거 등의 동작을 수행할 수 있다. 일 실시예에서, 비휘발성 메모리 장치(10)는 레디/비지 신호(RnB)를 메모리 컨트롤러(20)로 전송할 수 있다. 레디/비지 신호(RnB)는 비휘발성 메모리 장치(10)의 동작 유무를 가리키는 신호일 수 있다. 예를 들어, 비휘발성 메모리 장치(10)가 프로그램 동작을 수행하는 경우, 레디/비지 신호(RnB)는 비지 상태(예를 들어, 로직 로우)일 수 있다. 비휘발성 메모리 장치(10)가 기입, 독출, 소거 등의 동작을 수행하지 않는 경우 레디/비지 신호(RnB)는 레디 상태(예를 들어, 로직 하이)일 수 있다.

- [0015] 메모리 컨트롤러(20)는 레디/비지 신호(RnB) 및 호스트로부터 수신된 기입 요청 또는 독출 요청에 응답하여 서스펜드 커맨드(CMD\_spd)를 비휘발성 메모리 장치(10)로 전송할 수 있다.

- [0016] 메모리 컨트롤러(20)는 호스트로부터 우선순위(priority)가 높은 독출 요청을 수신할 수 있다. 본 명세서에서, 상기와 같이 높은 우선 순위를 갖는 독출 요청을 긴급 독출 요청이라고 칭한다. 메모리 컨트롤러(20)는 수신된 긴급 독출 요청에 응답하여 서스펜드 커맨드(CMD\_spd)를 비휘발성 메모리 장치(10)로 전송할 수 있다. 즉, 메모리 컨트롤러(20)는 레디/비지 신호(RnB)가 비지 상태인 경우, 높은 우선 순위를 갖는 독출 요청에 응답하여 서스펜드 커맨드(CMD\_spd)를 비휘발성 메모리 장치(10)로 전송할 수 있다. 비휘발성 메모리 장치(10)는 서스팬드 커맨드(CMD\_spd)에 대응하여, 프로그램 대상이 되는 선택 워드라인에 대해 리커버리 동작을 수행할 수 있다.

- [0017] 리커버리 동작이 완료되면, 비휘발성 메모리 장치(10)는 긴급 독출 요청에 대응한 독출 동작을 수행할 수 있다. 비휘발성 메모리 장치(10)는 긴급 독출 요청에 따른 독출 동작을 완료한 후 레디/비지 신호(RnB)로 레디 상태를 출력할 수 있고, 메모리 컨트롤러(20)는 이에 대응하여 리쥼 커맨드(CMD\_rsm)를 비휘발성 메모리 장치(10)에 출력함으로서 프로그램 동작을 재개할 수 있다.

- [0018] 비휘발성 메모리 장치(10)는 메모리 셀 어레이(110), 제어 로직(120) 및 리커버리 매니저(130)를 포함할 수 있다. 메모리 셀 어레이(110)는 복수의 메모리 셀들을 포함할 수 있다. 예를 들어, 복수의 메모리 셀들은 플래쉬 메모리 셀들일 수 있다. 이하에서는, 복수의 메모리 셀들이 낸드(NAND) 플래쉬 메모리 셀들인 경우를 예로 하여 실시예들을 상술하기로 한다. 그러나, 본 개시의 기술적 사상은 이에 제한되지 않고, 다른 실시예에서, 복수의 메모리 셀들은 RRAM(resistive RAM), PRAM(phase change RAM) 또는 MRAM(magnetic RAM)과 같은 저항형 메모리 셀들일 수 있다.

- [0019] 메모리 셀 어레이(110)는 3차원 (3D) 메모리 셀 어레이일 수 있다. 3차원 메모리 셀 어레이는 실리콘 기판 위에 배치되는 활성 영역과, 메모리 셀들의 동작과 관련된 회로로서 상기 기판 상에 또는 상기 기판 내에 형성된 회로를 가지는 메모리 셀 어레이들의 적어도 하나의 물리적 레벨에 모놀리식으로 형성된다. 상기 용어 "모놀리식"은 상기 어레이를 구성하는 각 레벨의 층들이 상기 어레이 중 각 하부 레벨의 층들의 바로 위에 적층되어 있음을 의미한다. 상기 3D 메모리 셀 어레이는 적어도 하나의 메모리 셀이 다른 메모리 셀의 위에 위치하도록 수

직 방향으로 배치된 낸드 스트링들을 포함한다. 상기 적어도 하나의 메모리 셀은 전하 트랩층을 포함할 수 있다. 그러나, 이에 제한되는 것은 아니며, 다른 실시예에 있어서, 메모리 셀 어레이(110)는 2차원 메모리 셀 어레이일 수 있다.

- [0020] 미국 특허공개공보 제7,679,133호, 동 제8,553,466호, 동 제8,654,587호, 동 제8,559,235호, 및 미국 특허출원 공개공보 제2011/0233648호는 3D 메모리 어레이가 복수 레벨로 구성되고 워드 라인들 및/또는 비트 라인들이 레벨들 간에 공유되어 있는 3D 메모리 어레이에 대한 적절한 구성들을 상술하는 것들로서, 본 명세서에 인용 형식으로 결합된다. 또한, 미국 특허출원공개공보 제2014-0334232호 및 미국특허공개공보 제8,488,381호는 본 명세서에 인용 형식으로 결합된다.

- [0021] 본 실시예에서, 메모리 셀 어레이(110)에 포함되는 각 메모리 셀은 2 비트 이상의 데이터를 저장하는 멀티 레벨 셀(multi level cell, MLC)일 수 있다. 예를 들어, 메모리 셀은 2 비트 데이터를 저장하는 멀티 레벨 셀(multi level cell, MLC)일 수 있다. 또 다른 예로서, 메모리 셀은 3 비트 데이터를 저장하는 트리플 레벨 셀(triple level cell, TLC)일 수 있다. 그러나, 본 개시는 이에 한정되지 않고, 다른 실시예에서, 메모리 셀 어레이(11 0)에 포함되는 일부 메모리 셀들은 1 비트 데이터를 저장하는 싱글 레벨 셀(single level cell, SLC)이고, 다른 일부 메모리 셀들은 멀티 레벨 셀(multi level cell, MLC)일 수 있다.

- [0022] 제어 로직(120)은 메모리 컨트롤러(20)로부터 수신한 커맨드(CMD), 어드레스(ADDR) 및 커맨드 (CMD\_w/CMD\_r/CMD\_spd/CMD\_rsm)를 기초로 하여, 비휘발성 메모리 장치(10) 내의 각종 동작을 전반적으로 제어할 수 있다. 예컨대, 제어 로직(120)은 메모리 셀 어레이(110)에 데이터를 기입하거나 메모리 셀 어레이(110)로부터 데이터를 독출하기 위한 각종 제어 신호를 출력할 수 있다. 또한, 제어 로직(120)은 선택 워드라인에 대한 리커버리를 수행하기 위한 제어 신호를 출력할 수 있다.

- [0023] 리커버리 매니저(130)는 서스팬드 커맨드(CMD\_spd)에 기초하여 리커버리 모드를 결정할 수 있다. 리커버리 모드는 리커버리 시점에 따라서, 서스팬드 커맨드(CMD\_spd)를 수신한 직후에 리커버리를 수행하는 캔슬 모드(Cancel Mode) 및 프로그램 동작에 포함되는 프로그램 루프를 수행한 후 리커버리를 수행하는 루프 모드(Loop Mode)를 포함할 수 있다. 본 개시의 일 실시예에서, 리커버리 매니저(130)는 서스팬드 커맨드(CMD\_spd)의 수신 시점에 따라서 리커버리 모드를 다르게 결정할 수 있다. 본 개시의 일 실시예에서 리커버리 매니저(130)는 수신한 서스팬드 커맨드(CMD\_spd)의 개수에 따라서 리커버리 모드를 다르게 결정할 수 있다. 캔슬 모드는 바로 리커버리를 수행하기 때문에 긴급 독출 요청에 대해서 바로 대응할 수 있는 장점이 있는 반면 프로그램 동작이 지연되는 단점이 있을 수 있다. 반면, 루프 모드는 프로그램 동작을 우선 완료하고 긴급 독출 요청에 대해서 대응하기 때문에 프로그램 동작이 지연되지 않지만, 긴급 독출 요청에 대한 대응이 늦어지는 단점이 있다. 본 개시의 기술적 사상에 따르면, 리커버리 매니저(130)가 서스팬드 커맨드(CMD\_spd)에 기초하여 리커버리 모드를 서로 다르게 결정함으로서, 프로그램 요청이 지연되는 기입 지연 현상(Write Starvation)이 방지되고, 효율적인 긴급 독출 동작이 수행될 수 있다.

- [0024] 본 명세서에서는 프로그램 동작 중 긴급 독출 요청을 수신한 경우에 대해서 설명하나 소거 동작 중 긴급 독출 요청을 수신한 경우에도 유추 적용될 수 있음은 이해되어야 할 것이다.

- [0025] 도 2는 본 개시의 예시적 실시예에 따른 비휘발성 메모리 장치를 나타내는 블록도이다. 도 1과 중복되는 내용은 생략한다.

- [0026] 도 2를 참조하면, 비휘발성 메모리 장치(10)는 메모리 셀 어레이(110), 제어 로직(120), 리커버리 모드 매니저 (130), 전압 생성부(140), 로우 디코더(150) 및 입출력 회로(160)를 포함할 수 있다.

- [0027] 제어 로직(120)은 메모리 컨트롤러(도 1의 20)로부터 수신한 각종 커맨드(CMD\_w/CMD\_r/CMD\_spd/CMD\_rsm) 및 어드레스(ADDR)를 기초로 하여, 메모리 셀 어레이(110)에 데이터를 기입하거나 메모리 셀 어레이(110)로부터 데이터를 독출하기 위한 각종 제어 신호를 출력할 수 있다. 또한, 비휘발성 메모리 장치(10)가 서스팬드 커맨드(CMD\_spd)를 수신하면, 리커버리 모드 매니저(130)는 이에 대응하여 리커버리 모드(RM)를 결정하고 결정된 리커버리 모드(RM)를 제어 로직(120)에 출력할 수 있다. 리커버리 모드(RM)는 서스팬드 커맨드(CMD\_spd)를 수신한 직후에 리커버리 동작을 수행하는 캔슬 모드(CM) 및 수행중인 프로그램 루프에 대응한 프로그램 동작을 완료한후 리커버리를 수행하는 루프 모드(LM)를 포함할 수 있다. 제어 로직(120)은 리커버리 모드(RM)에 기초하여 메모리 셀 어레이(110)에 리커버리 동작을 수행하기 위한 각종 제어 신호를 출력할 수 있다. 캔슬 모드(CM) 및 루프 모드(LM)에 대해서는 도 9에서 후술한다.

- [0028] 전압 생성부(140)는 전압 제어 신호(CTRL\_vol)를 기초로 하여 메모리 셀 어레이(110)에 대한 기입, 독출 및 소

거 동작을 수행하기 위한 다양한 종류의 전압들을 생성할 수 있다. 구체적으로, 전압 생성부(140)는 워드 라인 전압(WL), 예를 들어, 프로그램 전압(또는 기입 전압), 독출 전압, 패스 전압(또는 워드 라인 비선택 전압), 검증 전압 또는 리커버리 전압 등을 생성할 수 있다.

- [0029] 로우 디코더(150)는 로우 어드레스(X-ADDR)에 응답하여 워드 라인들(WL) 중 일부 워드 라인을 선택할 수 있다. 로우 디코더(150)는 워드 라인에 워드 라인 전압을 전달한다. 프로그램 동작시, 로우 디코더(150)는 선택 워드 라인에 프로그램 전압과 검증 전압을, 비선택 워드 라인에는 프로그램 인히빗 전압을 인가할 수 있다. 독출 동작시, 로우 디코더(150)는 선택 워드 라인에는 독출 전압을, 비선택된 워드 라인에는 독출 인히빗 전압을 인가할 수 있다. 리커버리 동작시, 로우 디코더(150)는 선택 워드라인에 리커버리 전압을 인가할 수 있다. 또한, 로우 디코더(150)는 로우 어드레스(X-ADDR)에 응답하여 스트링 선택 라인들 중 일부 스트링 선택 라인 또는 그라운드 선택 라인들 중 일부 그라운드 선택 라인을 선택할 수 있다.

- [0030] 입출력 회로(160)는 외부로부터(예를 들어, 메모리 콘트롤러) 데이터를 입력 받고, 입력된 데이터를 메모리 셀어레이(110)에 저장한다. 또한, 입출력 회로(160)는 메모리 셀어레이(110)로부터 데이터를 읽고, 독출된 데이터를 외부로 출력할 수 있다. 입출력 회로(160)는 비트 라인들(BL)에 대응하는 페이지 퍼버들(미도시)을 포함할수 있다. 페이지 버퍼는 비트 라인들(BL)을 통해 메모리 셀어레이(110)에 연결될 수 있고, 제어 로직(120)으로부터 수신한 칼럼 어드레스(Y-ADDR)에 응답하여 비트 라인들(BL) 중 일부 비트 라인을 선택할 수 있다. 프로그램 동작 시 페이지 버퍼는 기입 드라이버로 동작하여 메모리 셀어레이(110)에 저장하고자 하는 데이터(DATA)를 프로그램할 수 있다.

- [0031] 도 3은 본 개시의 예시적 실시예에 따른 비휘발성 메모리 장치의 동작을 나타내는 순서도이다.

- [0032] 도 2 및 도 3을 참조하면, 비휘발성 메모리 장치(10)는 복수의 프로그램 루프들 중 제1 프로그램 루프에 대응하는 프로그램 동작을 수행할 수 있다(S110). 비휘발성 메모리 장치(10)는 제1 프로그램 루프 도중 메모리 컨트롤러(20)로부터 긴급 독출을 위한 서스팬드 커맨드(CMD\_spd)를 수신할 수 있다(S120). 비휘발성 메모리 장치(10)는 서스팬드 커맨드(CMD\_spd)를 기초로 리커버리 모드(RM)를 결정할 수 있다(S130). 결정된 리커버리 모드(RM)가 캔슬 모드(CM)인 경우(S140), 비휘발성 메모리 장치(10)는 캔슬 모드로 리커버리 동작을 수행할 수 있다(S150). 결정된 리커버리 모드(RM)가 캔슬 모드(CM)가 아닌 경우(S140), 비휘발성 메모리 장치(10)는 루프 모드(LM)로 리커버리 동작을 수행할 수 있다(S160). 도 3에서는 캔슬 모드(CM)인지 여부를 결정하는 실시예가 도시되어 있으나, 루프 모드(LM)인지 여부를 결정하는 실시예에도 본 개시의 기술적 사상이 적용될 수 있음은 당연하다.

- [0033] 도 4a는 본 개시의 예시적 실시예에 따른 비휘발성 메모리 장치의 동작을 나타내는 순서도이다. 자세하게는, 도 4a는 도 3의 S150에 따라서 캔슬 모드로 리커버리를 수행하는 비휘발성 메모리 장치의 동작을 나타내는 순서도 이다.

- [0034] 도 2 및 도 4a를 참조하면, 비휘발성 메모리 장치(10)는 리커버리 모드(RM)로서 캔슬 모드(CM)를 결정하고, 이에 대응하여 바로 선택 워드라인에 리커버리 전압을 인가함으로서 리커버리 동작을 수행할 수 있다(S151). 즉, 비휘발성 메모리 장치(10)는 캔슬 모드(CM)에서 서스팬드 커맨드(CMD\_spd) 수신에 대응하여 바로 리커버리 동작을 수행할 수 있다. 비휘발성 메모리 장치(10)는 리커버리 동작 완료 후 독출 커맨드(CMD\_r)에 응답하여 긴급 독출 동작을 수행할 수 있다(S152). 도시되지는 않았지만 일 실시예에서, 비휘발성 메모리 장치(10)는 리커버리 동작 완료 후 레디/비지 신호(RnB)로서 레디 신호를 출력하고, 메모리 컨트롤러(도 1, 20)는 이에 대응하여 독출 커맨드(CMD\_r)를 출력할 수 있다.

- [0035] 비휘발성 메모리 장치(10)는 긴급 독출 동작 완료 후 리쥼 커맨드(CMD\_rsm)를 수신할 수 있다(S153). 도시되지는 않았지만 일 실시예에서, 비휘발성 메모리 장치(10)는 긴급 독출 동작 완료 후 레디/비지 신호(RnB)로서 레디 신호를 출력하고, 메모리 컨트롤러(도 1, 20)는 이에 대응하여 리쥼 커맨드(CMD\_rsm)를 출력할 수 있다. 비휘발성 메모리 장치(10)는 리쥼 커맨드(CMD\_rsm)에 대응하여 제1 프로그램 루프에 대응하는 프로그램 동작을 다시 수행할 수 있다(S154).

- [0036] 도 4b는 본 개시의 예시적 실시예에 따른 비휘발성 메모리 장치의 동작을 나타내는 순서도이다. 자세하게는, 도 4b는 도 3의 S150에 따라서 루프 모드로 리커버리를 수행하는 비휘발성 메모리 장치의 동작을 나타내는 순서도이다.

- [0037] 도 2 및 도 4b를 참조하면, 비휘발성 메모리 장치(10)는 리커버리 모드(RM)로서 루프 모드(LM)를 결정하고, 이에 대응하여 제1 프로그램 루프에 대응하는 프로그램 동작을 수행할 수 있다(S161). 즉, 비휘발성 메모리 장치

(10)는 루프 모드(LM)에서 서스팬드 커맨드(CMD\_spd)의 수신에도 불구하고 수행하던 제1 프로그램 루프에 대응하는 프로그램 동작을 계속 수행할 수 있다. 일 실시예에서, 제1 프로그램 루프에 대응하는 프로그램 동작에는 검증 동작이 포함될 수 있다. 제1 프로그램 루프에 대응하는 프로그램 동작 완료 후 비휘발성 메모리 장치(10)는 선택 워드라인에 리커버리 전압을 인가함으로서 리커버리 동작을 수행할 수 있다(S162).

- [0038] 비휘발성 메모리 장치(10)는 리커버리 동작 완료 후 독출 커맨드(CMD\_r)에 응답하여 긴급 독출 동작을 수행할 수 있다(S162). 도시되지는 않았지만 일 실시예에서, 비휘발성 메모리 장치(10)는 리커버리 동작 완료 후 레디/비지 신호(RnB)로서 레디 신호를 출력하고, 메모리 컨트롤러(도 1, 20)는 이에 대응하여 독출 커맨드(CMD\_r)를 출력할 수 있다. 비휘발성 메모리 장치(10)는 긴급 독출 동작 완료 후 리쥼 커맨드(CMD\_rsm)를 수신할 수 있다 (S163). 도시되지는 않았지만 일 실시예에서, 비휘발성 메모리 장치(10)는 긴급 독출 동작 완료 후 레디/비지신호(RnB)로서 레디 신호를 출력하고, 메모리 컨트롤러(도 1, 20)는 이에 대응하여 리쥼 커맨드(CMD\_rsm)를 출력할 수 있다. 제1 프로그램 루프에 대한 프로그램 동작이 완료되었기 때문에, 비휘발성 메모리 장치(10)는 리쥼 커맨드(CMD\_rsm)에 대응하여 제1 프로그램 루프의 다음 루프에 해당하는 제2 프로그램 루프에 대응하는 프로그램 동작을 수행할 수 있다(S164).

- [0039] 도 5는 본 개시의 예시적 실시예에 따른 메모리 셀 어레이에 포함된 메모리 블록을 나타내는 회로도이다.

- [0040] 도 5를 참조하면, 메모리 셀 어레이(예를 들어, 도 2의 110)는 수평 낸드 플래시 메모리의 메모리 셀 어레이일 수 있고, 복수의 메모리 블록들을 포함할 수 있다. 각 메모리 블록(BLKa)은 비트 라인(BL0 ~ BLn-1) 방향으로, 다수 개의 메모리 셀(MC)들이 직렬로 연결되는 n(n는 2 이상의 정수)개의 셀 스트링(STR)들을 포함할 수 있다. 일 예로서, 도 5에는 각각의 셀 스트링(STR)이 8 개의 메모리 셀들을 포함하는 예가 도시된다.

- [0041] 도 5와 같은 구조를 갖는 낸드 플래시 메모리 장치는 블록 단위로 소거가 수행되고, 각 워드 라인(WL0 ~ WL7)에 대응되는 페이지 단위로 프로그램을 수행한다. 도 5는 하나의 블록에 n개의 워드 라인들(WL1 ~ WLn)에 대한 n개의 페이지들이 구비되는 예를 도시한다. 또한, 도 1 및 도 2의 비휘발성 메모리 장치(10)는 이상에서 설명된 메모리 셀 어레이(110)와 동일한 구조로 동일한 동작을 수행하는 복수의 메모리 셀 어레이들을 포함할 수도 있다.

- [0042] 도 6는 본 개시의 예시적 실시예들에 따른 메모리 셀 어레이에 포함된 메모리 블록의 다른 예를 나타내는 회로 도이다.

- [0043] 도 6를 참조하면, 메모리 셀 어레이(예를 들어, 도 2의 110)는 수직 낸드 플래시 메모리의 메모리 셀 어레이일수 있고, 복수의 메모리 블록들을 포함할수 있다. 각 메모리 블록(BLKO)은 복수의 낸드 셀 스트링들(NS11 ~ NS33), 복수의 워드 라인들(WL1 ~ WL8), 복수의 비트 라인들(BL1 ~ BL3), 복수의 그라운드 선택 라인들(GSL1 ~ GSL3), 복수의 셀 스트링 선택 라인들(SSL1 ~ SSL3) 및 공통 소스 라인(CSL)을 포함할수 있다. 여기서, 낸드셀 스트링들의 개수, 워드 라인들의 개수, 비트 라인들의 개수, 그라운드 선택 라인의 개수 및 셀 스트링 선택라인들의 개수는 실시예에 따라 다양하게 변경될수 있다.

- [0044] 제1 비트 라인(BL1)과 공통 소스 라인(CSL) 사이에 낸드 셀 스트링들(NS11, NS21, NS31)이 제공되고, 제2 비트라인(BL2)과 공통 소스 라인(CSL) 사이에 낸드 셀 스트링들(NS12, NS22, NS32)이 제공되고 제3 비트라인(BL3)과 공통 소스 라인(CSL) 사이에 낸드 셀 스트링들(NS13, NS23, NS33)이 제공된다. 각 낸드 셀 스트링(예를 들면, NS11)은 직렬로 연결된 셀 스트링 선택 트랜지스터(SST), 복수의 메모리 셀들(MC1 내지 MC8) 및 그라운드선택 트랜지스터(GST)를 포함할 수 있다.

- [0045] 하나의 비트 라인에 공통으로 연결된 셀 스트링들은 하나의 칼럼을 구성한다. 예를 들어, 제1 비트 라인(BL1)에 공통으로 연결된 셀 스트링들(NS11, NS21, NS31)은 제1 칼럼에 대응되고, 제2 비트 라인(BL2)에 공통으로 연결된 셀 스트링들(NS12, NS22, NS32)은 제2 칼럼에 대응되며, 제3 비트 라인(BL3)에 공통으로 연결된 셀 스트링들 (NS13, NS23, NS33)은 제3 칼럼에 대응될 수 있다.

- [0046] 하나의 셀 스트링 선택 라인에 연결되는 셀 스트링들은 하나의 로우를 구성한다. 예를 들어, 제1 셀 스트링 선택 라인(SSL1)에 연결된 셀 스트링들(NS11, NS12, NS13)은 제1 로우에 대응되고, 제2 셀 스트링 선택 라인(SSL2)에 연결된 셀 스트링들(NS21, NS22, NS23)은 제2 로우에 대응되며, 제3 셀 스트링 선택 라인(SSL3)에 연결된 셀 스트링들(NS31, NS32, NS33)은 제3 로우에 대응될 수 있다.

- [0047] 셀 스트링 선택 트랜지스터(SST)는 대응하는 셀 스트링 선택 라인(SSL1 ~ SSL3)에 연결된다. 복수의 메모리 셀 들(MC1 ~ MC8)은 각각 대응하는 워드 라인(WL1 내지 WL8)에 연결된다. 그라운드 선택 트랜지스터(GST)는 대응하는 그라운드 선택 라인(GSL1 ~ GSL3)에 연결된다. 셀 스트링 선택 트랜지스터(SST)는 대응하는 비트 라인(BL1 ~

BL3)에 연결되고, 그라운드 선택 트랜지스터(GST)는 공통 소스 라인(CSL)에 연결된다.

- [0048] 동일 높이의 워드 라인(예를 들면, WL1)은 서로 공통으로 연결되어 있고, 셀 스트링 선택 라인들(SSL1 ~ SSL3)은 서로 분리되어 있고, 그라운드 선택 라인들(GSL1 ~ GSL3)도 서로 분리되어 있다. 예를 들어, 제 1 워드 라인 (WL1)에 연결되어 있고 셀 스트링(NS11, NS12, NS13)에 속해 있는 메모리 셀들을 프로그램하는 경우에는, 제1 워드 라인(WL1)과 제1 셀 스트링 선택 라인(SSL1)이 선택된다. 그라운드 선택 라인들(GSL1 ~ GSL3)은 서로 공통으로 연결될 수도 있다.

- [0049] 도 7은 도 6의 메모리 블록(BLKO)을 나타내는 사시도이다.

- [0050] 도 7를 참조하면, 메모리 셀 어레이(예를 들어, 도 2의 110)에 포함된 각 메모리 블록은 기판(SUB)에 대해 수직 방향으로 형성되어 있다. 도 6에서는, 메모리 블록이 2개의 선택 라인들(GSL, SSL), 8개의 워드 라인들(WL1 ~ WL8), 그리고 3개의 비트 라인들(BL1 ~ BL3)을 포함하는 것으로 도시되어 있으나, 실제로는 이것들보다 더 많거나 적을 수 있다.

- [0051] 기판(SUB)은 제1 도전형(예를 들어, p 타입)을 가지며, 기판(SUB) 상에 제1 방향(예를 들어, Y 방향)을 따라 신장되고, 제2 도전형(예를 들어, n 타입)의 불순물들이 도핑된 공통 소스 라인(CSL)이 제공된다. 인접한 두 공통소스 라인(CSL) 사이의 기판(SUB)의 영역 상에, 제1 방향을 따라 신장되는 복수의 절연막들(IL)이 제3 방향(예를 들어, Z 방향)을 따라 순차적으로 제공되며, 복수의 절연막들(IL)은 제3 방향을 따라 특정 거리만큼 이격된다. 예를 들어, 복수의 절연막들(IL)은 실리콘 산화물과 같은 절연 물질을 포함할 수 있다.

- [0052] 인접한 두 공통 소스 라인들(CSL) 사이의 기판(SUB)의 영역 상에, 제1 방향을 따라 순차적으로 배치되며, 제3 방향을 따라 복수의 절연막들(IL)을 관통하는 복수의 필라들(pillars)(P)이 제공된다. 예를 들어, 복수의 필라들(P)은 복수의 절연막들(IL)을 관통하여 기판(SUB)과 컨택할 것이다. 구체적으로, 각 필라(P)의 표면층 (surface layer)(S)은 제1 타입을 갖는 실리콘 물질을 포함할 수 있고, 채널 영역으로 기능할 수 있다. 한편, 각 필라(P)의 내부층(I)은 실리콘 산화물과 같은 절연 물질 또는 에어 갭(air gap)을 포함할 수 있다.

- [0053] 인접한 두 공통 소스 라인들(CSL) 사이의 영역에서, 절연막들(IL), 필라들(P) 및 기판(SUB)의 노출된 표면을 따라 전하 저장층(charge storage layer, CS)이 제공된다. 전하 저장층(CS)은 게이트 절연층(또는 '터널링 절연층'이라고 지칭함), 전하 트랩층 및 블로킹 절연층을 포함할 수 있다. 예를 들어, 전하 저장층(CS)은 ONO(oxide-nitride-oxide) 구조를 가질 수 있다. 또한, 인접한 두 공통 소스 라인들(CSL) 사이의 영역에서, 전하 저장층(CS)의 노출된 표면 상에, 선택 라인들(GSL, SSL) 및 워드 라인들(WL1 ~ WL8)과 같은 게이트 전극(GE)이 제공된다.

- [0054] 복수의 필라들(P) 상에는 드레인들 또는 드레인 컨택들(DR)이 각각 제공된다. 예를 들어, 드레인들 또는 드레인 컨택들(DR)은 제2 도전형을 갖는 불순물들이 도핑된 실리콘 물질을 포함할 수 있다. 드레인들(DR) 상에, 제2 방향(예를 들어, X 방향)으로 신장되고 제1 방향을 따라 특정 거리만큼 이격되어 배치된 비트 라인들(BL1 내지 BL3)이 제공된다.

- [0055] 도 8는 본 개시의 예시적 실시예에 따른 비휘발성 메모리 장치의 프로그램 동작을 나타내는 그래프이다. 도 8에 도시된 그래프의 x축은 시간을 가리키고, y축은 전압 레벨을 가리킨다. 간결한 설명을 위하여 비휘발성 메모리 장치(도 1, 10)는 페이지(page) 단위로 프로그램 동작을 수행하는 것으로 가정한다. 그러나, 본 발명의 범위가이에 한정되는 것은 아니며, 비휘발성 메모리 장치(도 1, 10)의 프로그램 방식는 다양하게 변경되어 적용될 수 있다.

- [0056] 도 2 및 도 8을 참조하면, 비휘발성 메모리 장치(10)는 ISPP(Incremental Step Pulse Program) 방식을 기반으로 프로그램 동작을 수행할 수 있다. 즉, 비휘발성 메모리 장치(10)는 복수의 프로그램 루프들(Program loop 1~Program Loop n)을 통해 프로그램 동작을 수행할 수 있다. 복수의 프로그램 루프들(Program loop 1~Program Loop n)에 대응하는 프로그램 동작 각각은 프로그램 전압들(Vpgm\_1~Vpgm\_n)이 인가되는 프로그램 전압 인가 동작 및 검증 전압(Vvfy)이 검증 동작으로 구성될 수 있다. 프로그램 루프가 증가할수록 인가되는 프로그램 전압 (Vpgm)은 프로그램 전압 증가폭(△Vpgm)만큼 증가할 수 있다. 검증 동작에서 프로그램 패스된 메모리 셀들은 다음 프로그램 루프에서 프로그램 금지될 수 있다.

- [0057] 도 9는 본 개시의 예시적 실시예에 따른 비휘발성 메모리 장치의 선택 워드라인의 전압 레벨을 나타내는 그래프이다. 자세하게는, 도 9는 도 8의 (a) 구간의 제1 프로그램 루프를 확대시킨 그래프이다. 도 9에 도시된 그래프의 x축은 시간을 가리키고, y축은 전압 레벨을 가리킨다.

- [0058] 도 1 및 도 9를 참조하면, 비휘발성 메모리 장치(10)의 프로그램 대상이 되는 선택 워드라인의 전압 레벨은 제1 프로그램 전압(Vpgm1)에 도달할 때까지 서서히 증가할 수 있다. 비휘발성 메모리 장치(10)는 제1 시점(ta)에서 서스팬드 커맨드(CMD\_spd)를 수신할 수 있다. 캔슬 모드(CM)에서 비휘발성 메모리 장치(10)는 서스팬드 커맨드(CMD\_spd)를 수신한 제1 시점(ta)에서 선택 워드라인에 리커버리 전압을 인가함으로서 바로 리커버리 동작을 수 행할 수 있다. 이에 따라서, 선택 워드라인의 전압 레벨은 제1 시점(ta)에서 리커버리 전압까지 하락할 수 있다. 비휘발성 메모리 장치(10)는 긴급 독출 동작 수행 후 제1 리쥼 커맨드(CMD\_rsm1)에 대응하여 중단했던 제1 프로그램 루프를 수행할 수 있다.

- [0059] 루프 모드(LM)에서 비휘발성 메모리 장치(10)는 서스팬드 커맨드(CMD\_spd)의 수신에도 불구하고 제1 프로그램 루프에 대응한 프로그램 동작를 수행할 수 있다. 도시되지는 않았지만, 일 실시예에서, 비휘발성 메모리 장치(10)는 제1 프로그램 루프에 포함되는 검증 동작도 같이 수행될 수 있다. 제1 프로그램 루프가 완료되는 제2 시점(tb)에서 비휘발성 메모리 장치(10)는 선택 워드라인에 리커버리 전압을 인가함으로서 리커버리 동작을 수행할 수 있다. 이에 따라서, 선택 워드라인의 전압 레벨은 제2 시점(tb)에서 리커버리 전압까지 하락할 수 있다. 비휘발성 메모리 장치(10)는 긴급 독출 동작 수행 후 제2 리쥼 커맨드(CMD\_rsm2)에 대응하여 제1 프로그램 루프의 다음 순서인 제2 프로그램 루프를 수행할 수 있다.

- [0060] 캔슬 모드(CM)는 서스팬드 커맨드(CMD\_spd)를 수신한 제1 시점(ta)에서 바로 리커버리를 수행하기 때문에 프로그램 동작은 지연되어 (a) 구간 이후에 제1 프로그램 루프에 대응하는 프로그램 동작이 완료될 수 있으나 긴급 독출 요청에 대해서 바로 대응할 수 있다. 루프 모드(LM)는 프로그램 동작을 우선 완료하고 서스팬드 커맨드 (CMD\_spd)에 대응한 긴급 독출 요청에 대해서 대응하기 때문에 프로그램 동작이 지연되지 않지만, 긴급 독출 요청에 대한 대응이 늦어질 수 있다. 본 개시의 기술적 사상에 따르면, 서스팬드 커맨드(CMD\_spd)에 기초하여 리커버리 모드를 서로 다르게 결정함으로서 프로그램 요청이 지연되는 기입 지연 현상(Write Starvation)이 방지되고, 효율적인 긴급 독출 동작이 수행될 수 있다.

- [0061] 도 10은 본 개시의 예시적 실시예에 따른 리커버리 모드 매니저를 나타내는 블록도이다. 도 1과 중복되는 내용은 생략한다.

- [0062] 도 10을 참조하면, 리커버리 모드 매니저(130)는 서스팬드 커맨드 카운팅부(131), 공급 전압 판단부(132), 워드라인 전압 레벨 판단부(133) 및 소요시간 카운팅부(134)를 포함할 수 있다. 도 1에서 상술한 바와 같이, 리커버리 모드 매니저(130)는 메모리 컨트롤러(도 1, 20)로부터 수신한 서스팬트 커맨드(CMD\_spd)를 기초로 리커버리 모드(RM)를 결정하고, 결정된 리커버리 모드(RM)를 제어 로직(도 1, 120)에 출력할 수 있다.

- [0063] 서스팬드 커맨드 카운팅부(131)는 메모리 컨트롤러(도 1, 20)로부터 수신한 서스팬드 커맨드(CMD\_spd)를 카운팅하고, 그 결과로 생성된 서스팬드 커맨드 카운트와 기준 카운트를 비교함으로서 리커버리 모드(RM)를 결정할 수있다. 일 실시예에서, 기준 카운트는 미리 결정되어 있을 수 있다. 일 실시예에서, 서스팬드 커맨드 카운팅부(131)는 서스팬드 커맨드 카운트가 기준 카운트보다 작은 경우 리커버리 모드(RM)로 캔슬 모드(CM)를 결정하고, 서스팬드 커맨드 카운트가 기준 카운트보다 크거나 같은 경우 리커버리 모드(RM)로 루프 모드(LM)를 결정할 수있다. 일 실시예에서, 서스팬드 커맨드 카운팅부(131)는 서스팬드 커맨드 카운트를 카운팅하기 위한 적어도 하나의 카운터 또는 플립-플랍(Flip-Flop)을 포함할 수 있다. 이에 관해서는 도 11a 및 도 11b에 후술한다.

- [0064] 공급 전압 판단부(132)는 제어 로직(도 1, 120)로부터 서스팬드 커맨드(CMD\_spd)를 수신하는 순간의 선택 워드라인에 공급되는 공급 전압의 공급 전압 레벨에 대한 정보를 수신하고, 수신한 공급 전압 레벨을 기준 전압과 비교함으로서 리커버리 모드(RM)를 결정할 수 있다. 비휘발성 메모리 장치(도 1, 10)는 프로그램 동작에서 선택워드라인의 전압 레벨을 높이기 위해 단계적으로 높은 전압 레벨을 갖는 공급 전압을 선택워드라인에 인가할수 있다. 일 실시예에서, 기준 전압은 미리 결정될수 있다. 일 실시예에서, 공급 전압 판단부(132)는 공급 전압 레벨이 기준 전압 레벨보다 작은 경우 리커버리 모드(RM)로 캔슬 모드(CM)를 결정하고, 공급 전압 레벨이 기준 전압 레벨보다 크거나 같은 경우 리커버리 모드(RM)로 루프 모드(LM)를 결정할수 있다. 이에 관해서는 도 12a 및 도 12b에 후술한다.

- [0065] 일 실시예에서, 비휘발성 메모리 장치(도 1, 10)는 복수의 단계 별로 서로 다른 공급 전압을 선택 워드라인에 인가할 수 있다. 본 실시예에서 제어 로직(도 1, 120)은 공급 전압 레벨에 따른 단계 정보를 생성할 수 있고, 공급 전압 판단부(132)는 제어 로직(도 1, 120)으로부터 수신한 단계 정보에 기초하여 리커버리 모드(RM)를 결정할 수 있다.

- [0066] 워드라인 전압 레벨 판단부(133)는 메모리 셀 어레이(도 1, 110)로부터 서스팬드 커맨드(CMD\_spd)를 수신하는

순간의 선택 워드라인의 전압 레벨에 대한 정보를 수신하고, 수신한 선택 워드라인 전압 레벨을 기준 전압과 비교함으로서 리커버리 모드(RM)를 결정할 수 있다. 일 실시예에서, 기준 전압은 미리 결정될 수 있다. 일 실시예에서, 워드라인 전압 레벨 판단부(133)는 선택 워드라인 전압 레벨이 기준 전압 레벨보다 작은 경우 리커버리모드(RM)로 캔슬 모드(CM)를 결정하고, 선택 워드라인 전압 레벨이 기준 전압 레벨보다 크거나 같은 경우 리커버리모드(RM)로 루프 모드(LM)를 결정할 수 있다. 이에 관해서는 도 13a 및 도 13b에 후술한다.

- [0067] 소요시간 카운팅부(134)는 비휘발성 메모리 장치(도 1, 10)가 프로그램 동작을 위해 선택 워드라인의 전압 레벨을 높이기 시작하는 순간부터 서스팬드 커맨드(CMD\_spd)를 수신한 순간까지의 소요시간을 카운팅하고, 카운팅한 소요시간과 기준 시간을 비교함으로서 리커버리 모드(RM)를 결정할 수 있다. 일 실시예에서, 기준 시간은 미리 결정될 수 있다. 일 실시예에서, 소요시간 카운팅부(134)는 소요시간이 기준 시간보다 작은 경우 리커버리 모드(RM)로 캔슬 모드(CM)를 결정하고, 소요시간이 기준 시간보다 크거나 같은 경우 리커버리 모드(RM)로 루프 모드(LM)를 결정할 수 있다. 이에 관해서는 도 14a 및 도 14b에서 후술한다.

- [0068] 도 10에서 리커버리 모드 매니저(130)는 서스팬드 커맨드 카운팅부(131), 공급 전압 판단부(132), 워드라인 전압 레벨 판단부(133) 및 소요시간 카운팅부(134)를 모두 포함하고 있으나 이는 일 실시예 일뿐이고, 리커버리모드 매니저(130)는 서스팬드 커맨드 카운팅부(131), 공급 전압 판단부(132), 워드라인 전압 레벨 판단부(133)및 소요시간 카운팅부(134)중 적어도 하나를 포함하고, 포함된 구성을 이용하여 리커버리모드(RM)를 결정할수 있다.

- [0069] 도 11a는 본 개시의 예시적 실시예에 따른 리커버리 모드 매니저의 동작을 나타내는 순서도이다. 자세하게는, 도 11a는 리커버리 모드 매니저가 서스팬드 커맨드 카운팅부를 이용하여 리커버리 모드를 결정하는 실시예를 나타낸다.

- [0070] 도 2 및 도 11a를 참조하면, 리커버리 모드 매니저(130)는 메모리 컨트롤러(도 1, 20)로부터 긴급 독출을 위한 서스팬드 커맨드(CMD\_spd)를 수신할 수 있다(S211). 리커버리 모드 매니저(130)는 복수의 프로그램 루프 중 제1 프로그램 루프 동안 수신한 서스팬드 커맨드(CMD\_spd)를 카운팅함으로서 서스팬드 커맨드 카운트(Nspd)를 생성할 수 있다(S212). 리커버리 모드 매니저(130)는 서스팬드 커맨드 카운트(Nspd)와 기준 카운트(Nth)를 비교할수 있다(S213). 서스팬드 커맨드 카운트(Nspd)가 기준 카운트(Nth)보다 작은 경우, 리커버리 모드 매니저(130)는 제어 로직(120)에 리커버리 모드(RM)로서 캔슬 모드(CM)를 출력할 수 있다(S214). 서스팬드 커맨드 카운트(Nspd)가 기준 카운트(Nth)보다 작지 않은 경우, 리커버리 모드 매니저(130)는 제어 로직(120)에 리커버리 모드(RM)로서 루프 모드(LM)를 출력할 수 있다(S215).

- [0071] 도 11b는 본 개시의 예시적 실시예에 따른 리커버리 모드 매니저의 동작을 나타내는 그래프이다. 자세하게는, 도 11b는 리커버리 모드 매니저가 서스팬드 커맨드 카운팅부를 이용하여 리커버리 모드를 결정하는 실시예를 나타낸다. 또한, 도 11b는 기준 카운트가 '4'인 예시를 나타낸다.

- [0072] 도 2, 도 11a 및 도 11b를 참조하면, 비휘발성 메모리 장치(10)가 제1 프로그램 루프를 수행하는 동안, 리커버리 모드 매니저(130)는 제1 시점(t1)에서 제1 서스팬드 커맨드(CMD\_spd1)를 수신하고 이에 대응하여 서스팬드 커맨드 카운트(Nspd)를 '1'로 카운팅할 수 있다. 서스팬드 커맨드 카운트(Nspd) '1'은 기준 카운트(Nth) '4'보다 작기 때문에, 리커버리 모드 매니저(130)는 제어 로직(120)에 리커버리 모드(RM)로서 캔슬 모드(CM)를 출력할 수 있다. 제어 로직(120)은 캔슬 모드(CM)의 수신에 대응하여 리커버리 전압(Vrcv)까지 선택 워드라인의 전압 레벨을 낮춤으로서 바로 리커버리 동작을 수행할 수 있다. 도시되진 않았지만, 리커버리 동작 완료 후 제1 시점(t1)부터 제2 시점(t2) 사이에서 비휘발성 메모리 장치(10)는 긴급 독출 동작을 수행할 수 있다. 긴급 독출 동작 완료 후 비휘발성 메모리 장치(10)는 제2 시점(t2)에서 리쥼 커맨드(CMD\_rsm)에 대응하여 다시 제1 프로그램 루프를 수행할 수 있다.

- [0073] 리커버리 모드 매니저(130)는 제3 시점(t3)에서 제2 서스팬드 커맨드(CMD\_spd2)를 수신하고 이에 대응하여 서스팬드 커맨드 카운트(Nspd)를 '2'로 카운팅할 수 있다. 서스팬드 커맨드 카운트(Nspd) '2'는 기준 카운트 (Nth) '4'보다 작기 때문에, 리커버리 모드 매니저(130)는 제어 로직(120)에 리커버리 모드(RM)로서 캔슬 모드(CM)를 출력할 수 있다. 제어 로직(120)은 캔슬 모드(CM)의 수신에 대응하여 리커버리 전압(Vrcv)까지 선택워드라인의 전압 레벨을 낮춤으로서 바로 리커버리 동작을 수행할 수 있다. 도시되진 않았지만, 리커버리 동작완료 후 제3 시점(t3)부터 제4 시점(t4) 사이에서 비휘발성 메모리 장치(10)는 긴급 독출 동작을 수행할 수 있다. 긴급 독출 동작 완료 후 비휘발성 메모리 장치(10)는 제4 시점(t4)에서 리쥼 커맨드(CMD\_rsm)에 대응하여다시 제1 프로그램 루프를 수행할 수 있다.

- [0074] 리커버리 모드 매니저(130)는 제5 시점(t5)에서 제3 서스팬드 커맨드(CMD\_spd3)를 수신하고 이에 대응하여 서스팬드 커맨드 카운트(Nspd)를 '3'로 카운팅할 수 있다. 서스팬드 커맨드 카운트(Nspd) '3'은 기준 카운트 (Nth) '4'보다 작기 때문에, 리커버리 모드 매니저(130)는 제어 로직(120)에 리커버리 모드(RM)로서 캔슬 모드(CM)를 출력할 수 있다. 제어 로직(120)은 캔슬 모드(CM)의 수신에 대응하여 리커버리 전압(Vrcv)까지 선택워드라인의 전압 레벨을 낮춤으로서 바로 리커버리 동작을 수행할 수 있다. 도시되진 않았지만, 리커버리 동작완료 후 제5 시점(t5)부터 제6 시점(t6) 사이에서 비휘발성 메모리 장치(10)는 긴급 독출 동작을 수행할 수 있다. 긴급 독출 동작 완료 후 비휘발성 메모리 장치(10)는 제6 시점(t6)에서 리쥼 커맨드(CMD\_rsm)에 대응하여다시 제1 프로그램 루프를 수행할 수 있다.

- [0075] 리커버리 모드 매니저(130)는 제7 시점(t7)에서 제4 서스팬드 커맨드(CMD\_spd4)를 수신하고 이에 대응하여 서스팬드 커맨드 카운트(Nspd)를 '4'로 카운팅할 수 있다. 서스팬드 커맨드 카운트(Nspd) '4'는 기준 카운트 (Nth) '4'보다 작지 않기 때문에, 리커버리 모드 매니저(130)는 제어 로직(120)에 리커버리 모드(RM)로서 루프 모드(LM)를 출력할 수 있다. 제어 로직(120)은 루프 모드(LM)의 수신에 대응하여 바로 리커버리 동작을 수행하지 않고 선택 워드라인의 전압 레벨을 제1 프로그램 전압(Vpgm1)으로 높임으로서 제1 프로그램 루프를 완료할수 있다. 비휘발성 메모리 장치(10)는 제1 프로그램 루프를 완료한 제8 시점(t8)에서 리커버리 동작을 수행할수 있다. 도시되진 않았지만, 리커버리 동작 완료 후 제8 시점(t8)부터 제9 시점(t9) 사이에서 비휘발성 메모리 장치(10)는 긴급 독출 동작을 수행할수 있다. 긴급 독출 동작 완료 후 비휘발성 메모리 장치(10)는 제9 시점(t9)에서 리쥼 커맨드(CMD\_rsm)에 대응하여 제1 프로그램 루프 다음 순서인 제2 프로그램 루프를 수행할수 있다.

- [0076] 도 12a는 본 개시의 예시적 실시예에 따른 리커버리 모드 매니저의 동작을 나타내는 순서도이다. 자세하게는, 도 12a는 리커버리 모드 매니저가 공급 전압 판단부를 이용하여 리커버리 모드를 결정하는 실시예를 나타낸다.

- [0077] 도 2 및 도 12a를 참조하면, 리커버리 모드 매니저(130)는 메모리 컨트롤러(도 1, 20)로부터 긴급 독출을 위한 서스팬드 커맨드(CMD\_spd)를 수신할 수 있다(S221). 리커버리 모드 매니저(130)는 제어 로직(120)으로부터 서스팬드 커맨드(CMD\_spd) 수신 시점의 공급 전압 정보를 수신할 수 있다(S222). 리커버리 모드 매니저(130)는 공급전압(Vspl)과 기준 전압(Vth)을 비교할 수 있다(S223). 공급전압(Vspl)이 기준 전압(Vth)보다 작은 경우, 리커버리 모드 매니저(130)는 제어 로직(120)에 리커버리 모드(RM)로서 캔슬 모드(CM)를 출력할 수 있다(S224). 공급전압(Vspl)이 기준 전압(Vth)보다 작지 않은 경우, 리커버리 모드 매니저(130)는 제어 로직(120)에 리커버리모드(RM)로서 루프 모드(LM)를 출력할 수 있다(S225).

- [0078] 도 10에서 상술한 바와 같이, 다른 실시예에서 리커버리 모드 매니저(130)는 제어 로직(120)으로부터 공급 전압 레벨에 따른 단계 정보를 기초로 리커버리 모드(RM)를 결정할 수 있다. 일 실시예에서, 리커버리 모드 매니저 (130)는 단계 정보가 기준 단계 이전인 경우 제어 로직(120)에 리커버리 모드(RM)로서 캔슬 모드(CM)를 출력하고, 단계 정보가 기준 단계 이전이 아닌 경우 제어 로직(120)에 리커버리 모드(RM)로서 루프 모드(LM)를 출력할수 있다.

- [0079] 도 12b는 본 개시의 예시적 실시예에 따른 리커버리 모드 매니저의 동작을 나타내는 그래프이다. 자세하게는, 도 12b는 리커버리 모드 매니저가 공급 전압 판단부를 이용하여 리커버리 모드를 결정하는 실시예를 나타낸다.

- [0080] 도 2, 도 12a 및 도 12b를 참조하면, 비휘발성 메모리 장치(10)는 선택 워드라인의 전압 레벨을 제1 프로그램 전압(Vpgm1)까지 높이기 위해 제1 단계(Step1)에서 제1 공급 전압(Vspl1)을 공급하고, 제2 단계(Step2)에서 제2 공급 전압(Vspl2)을 공급하고, 제3 단계(Step3)에서 제3 공급 전압(Vspl3)을 공급하고, 제4 단계에서 제1 프로그램 전압(Vpgm1)을 공급할 수 있다. 도 12b의 실시예에서 기준 전압(Vth)의 전압 레벨은 제2 공급 전압(Vspl2)보다 크고 제3 공급 전압(Vspl3)보다 작을 수 있다.

- [0081] (a)의 예시에서 비휘발성 메모리 장치(10)가 제1 프로그램 루프를 수행하는 동안, 리커버리 모드 매니저(130)는 제1 시점(t1)에서 제1 서스팬드 커맨드(CMD\_spd1)를 수신할 수 있다. 또한, 리커버리 모드 매니저(130)는 제어 로직(120)으로부터 제1 시점(t1)에서 공급 전압인 제2 공급 전압(Vsp12)에 대한 정보를 수신할 수 있다. 제2 공급 전압(Vsp12)은 기준 전압(Vth)보다 작기 때문에, 리커버리 모드 매니저(130)는 제어 로직(120)에 리커버리 모드(RM)로서 캔슬 모드(CM)를 출력할 수 있다. 제어 로직(120)은 캔슬 모드(CM)의 수신에 대응하여 리커버리 전압(Vrcv)까지 선택 워드라인의 전압 레벨을 낮춤으로서 바로 리커버리 동작을 수행할 수 있다. 도시되진 않았지만, 리커버리 동작 완료 후 비휘발성 메모리 장치(10)는 긴급 독출 동작을 수행할 수 있다. 또한, 긴급 독출 동작 완료 후 비휘발성 메모리 장치(10)는 리쥼 커맨드(CMD\_rsm)에 대응하여 제1 프로그램 루프를 다시 수행할

수 있다.

- [0082] (b)의 예시에서 비휘발성 메모리 장치(10)가 제1 프로그램 루프를 수행하는 동안, 리커버리 모드 매니저(130)는 제2 시점(t2)에서 제2 서스팬드 커맨드(CMD\_spd2)를 수신할 수 있다. 또한, 리커버리 모드 매니저(130)는 제어 로직(120)으로부터 제2 시점(t2)에서 공급 전압인 제3 공급 전압(Vsp13)에 대한 정보를 수신할 수 있다. 제3 공급 전압(Vsp13)은 기준 전압(Vth)보다 작지 않기 때문에, 리커버리 모드 매니저(130)는 제어 로직(120)에 리커버리 모드(RM)로서 루프 모드(LM)를 출력할 수 있다. 제어 로직(120)은 루프 모드(LM)의 수신에 대응하여 바로리커버리 동작을 수행하지 않고 선택 워드라인의 전압 레벨을 제1 프로그램 전압(Vpgm1)으로 높임으로서 제1 프로그램 루프를 완료할 수 있다. 비휘발성 메모리 장치(10)는 제1 프로그램 루프를 완료한 제3 시점(t3)에서 리커버리 동작을 수행할 수 있다. 도시되진 않았지만, 리커버리 동작 완료 후 비휘발성 메모리 장치(10)는 긴급독출 동작을 수행할 수 있다. 또한, 긴급 독출 동작 완료 후 비휘발성 메모리 장치(10)는 리쥼 커맨드(CMD\_rsm)에 대응하여 제1 프로그램 루프 다음 순서인 제2 프로그램 루프를 수행할 수 있다.

- [0083] 리커버리 모드 매니저(130)는 기준 단계를 이용하여 리커버리 모드(RM)를 결정할 수 있다. 기준 단계가 제3 단계(Step3)인 실시예에서 리커버리 모드 매니저(130)는 제1 시점(t1)에서 제어 로직(120)으로부터 공급 전압 레벨에 따른 단계인 제2 단계(Step2)에 대한 정보를 수신할 수 있다. 제2 단계(Step2)는 기준 단계인 'Step3'보다 이전이기 때문에 리커버리 모드 매니저(130)는 리커버리 모드(RM)로서 캔슬 모드(CM)를 제어 로직(120)에 출력할 수 있다. 반면, 리커버리 모드 매니저(130)는 제2 시점(t2)에서 제어 로직(120)으로부터 공급 전압 레벨에 따른 단계인 제3 단계(Step3)에 대한 정보를 수신할 수 있다. 제3 단계(Step3)는 기준 단계 'Step3'보다 이전이 아니기 때문에 리커버리 모드 매니저(130)는 리커버리 모드(RM)로서 루프 모드(LM)를 제어 로직(120)에 출력할 수 있다.

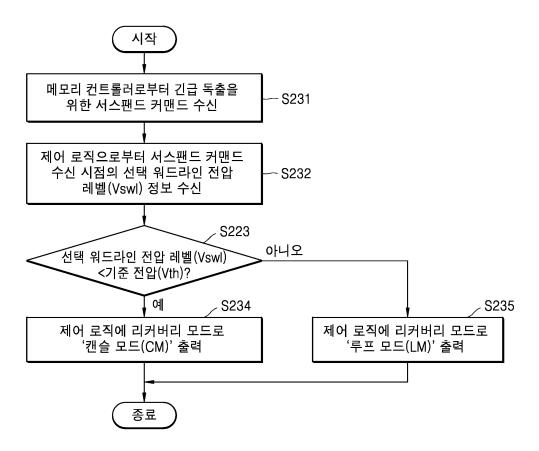

- [0084] 도 13a는 본 개시의 예시적 실시예에 따른 리커버리 모드 매니저의 동작을 나타내는 순서도이다. 자세하게는, 도 13a는 리커버리 모드 매니저가 워드라인 전압 레벨 판단부를 이용하여 리커버리 모드를 결정하는 실시예를 나타낸다.

- [0085] 도 2 및 도 13a를 참조하면, 리커버리 모드 매니저(130)는 메모리 컨트롤러(도 1, 20)로부터 긴급 독출을 위한 서스팬드 커맨드(CMD\_spd)를 수신할 수 있다(S231). 리커버리 모드 매니저(130)는 제어 로직(120)또는 메모리 셀 어레이(110)로부터 서스팬드 커맨드(CMD\_spd) 수신 시점의 선택 워드라인의 전압 레벨(Vswl)에 대한 정보를 수신할 수 있다(S232). 리커버리 모드 매니저(130)는 선택 워드라인 전압 레벨(Vswl)과 기준 전압(Vth)을 비교할 수 있다(S233). 선택 워드라인 전압 레벨(Vswl)이 기준 전압(Vth)보다 작은 경우, 리커버리 모드 매니저(130)는 제어 로직(120)에 리커버리 모드(RM)로서 캔슬 모드(CM)를 출력할 수 있다(S234). 선택 워드라인 전압 레벨(Vswl)이 기준 전압(Vth)보다 작지 않은 경우, 리커버리 모드 매니저(130)는 제어 로직(120)에 리커버리 모드(RM)로서 루프 모드(LM)를 출력할 수 있다(S235).

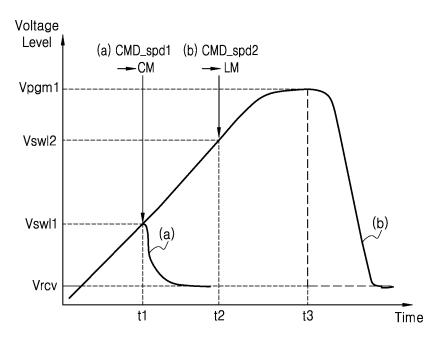

- [0086] 도 13b는 본 개시의 예시적 실시예에 따른 리커버리 모드 매니저의 동작을 나타내는 그래프이다. 자세하게는, 도 13b는 리커버리 모드 매니저가 선택 워드라인 전압 레벨 판단부를 이용하여 리커버리 모드를 결정하는 실시 예를 나타낸다.

- [0087] 도 2, 도 13a 및 도 13b를 참조하면, (a)의 예시에서 비휘발성 메모리 장치(10)가 제1 프로그램 루프를 수행하는 동안, 리커버리 모드 매니저(130)는 제1 시점(t1)에서 제1 서스팬드 커맨드(CMD\_spd1)를 수신할 수 있다. 제1 시점(t1)에서 제1 선택 워드라인 전압 레벨(Vswl1)은 기준 전압(Vth)보다 작기 때문에, 리커버리 모드 매니저(130)는 제어 로직(120)에 리커버리 모드(RM)로서 캔슬 모드(CM)를 출력할 수 있다. 제어 로직(120)은 캔슬 모드(CM)의 수신에 대응하여 리커버리 전압(Vrcv)까지 선택 워드라인의 전압 레벨을 낮춤으로서 바로 리커버리 동작을 수행할 수 있다. 도시되진 않았지만, 리커버리 동작 완료 후 비휘발성 메모리 장치(10)는 긴급 독출 동작을 수행할 수 있다. 또한, 긴급 독출 동작 완료 후 비휘발성 메모리 장치(10)는 리쥼 커맨드(CMD\_rsm)에 대응하여 제1 프로그램 루프를 다시 수행할 수 있다.

- [0088] (b)의 예시에서 비휘발성 메모리 장치(10)가 제1 프로그램 루프를 수행하는 동안, 리커버리 모드 매니저(130)는 제2 시점(t2)에서 제2 서스팬드 커맨드(CMD\_spd2)를 수신할 수 있다. 제2 시점(t2)에서 제2 선택 워드라인 전압 레벨(Vswl2)은 기준 전압(Vth)보다 작지 않기 때문에, 리커버리 모드 매니저(130)는 제어 로직(120)에 리커버리 모드(RM)로서 루프 모드(LM)를 출력할 수 있다. 제어 로직(120)은 루프 모드(LM)의 수신에 대응하여 바로 리커버리 동작을 수행하지 않고 선택 워드라인의 전압 레벨을 제1 프로그램 전압(Vpgm1)으로 높임으로서 제1 프로그램 루프를 완료할 수 있다. 비휘발성 메모리 장치(10)는 제1 프로그램 루프를 완료한 제3 시점(t3)에서 리커버리 동작을 수행할 수 있다. 도시되진 않았지만, 리커버리 동작 완료 후 비휘발성 메모리 장치(10)는 긴급 독출

동작을 수행할 수 있다. 또한, 긴급 독출 동작 완료 후 비휘발성 메모리 장치(10)는 리쥼 커맨드(CMD\_rsm)에 대응하여 제1 프로그램 루프 다음 순서인 제2 프로그램 루프를 수행할 수 있다.

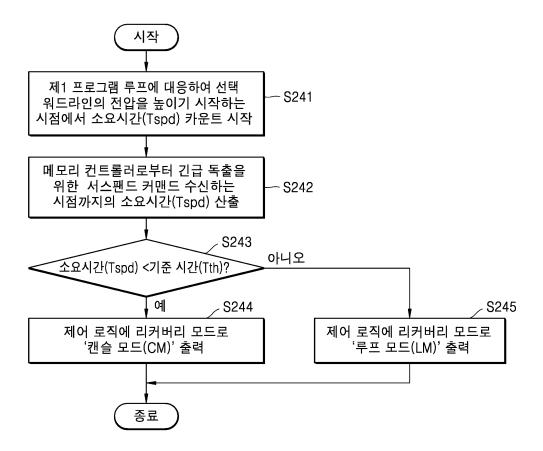

- [0089] 도 14a는 본 개시의 예시적 실시예에 따른 리커버리 모드 매니저의 동작을 나타내는 순서도이다. 자세하게는, 도 14a는 리커버리 모드 매니저가 소요시간 카운팅부를 이용하여 리커버리 모드를 결정하는 실시예를 나타낸다.

- [0090] 도 2 및 도 14a를 참조하면, 리커버리 모드 매니저(130)는 제1 프로그램 루프에 대응하여 선택 워드라인의 전압 레벨이 높아지기 시작하는 시점에서 소요시간(Tspd) 카운팅을 시작할 수 있다(S241). 리커버리 모드 매니저 (130)는 메모리 컨트롤러(도 1, 20)로부터 긴급 독출을 위한 서스팬드 커맨드(CMD\_spd)를 수신하고, 선택 워드라인의 전압 레벨이 높아지는 시점에서 서스팬드 커맨드(CMD\_spd)를 수신한 시점까지의 소요시간(Tspd)을 산출할 수 있다(S242). 리커버리 모드 매니저(130)는 소요시간(Tspd)과 기준 시간(Tth)을 비교할 수 있다(S243). 소요시간(Tspd)이 기준 시간(Tth)보다 작은 경우, 리커버리 모드 매니저(130)는 제어 로직(120)에 리커버리 모드 (RM)로서 캔슬 모드(CM)를 출력할 수 있다(S244). 소요시간(Tspd)이 기준 시간(Tth)보다 작지 않은 경우, 리커버리 모드 매니저(130)는 제어 로직(120)에 리커버리 모드(RM)로서 루프 모드(LM)를 출력할 수 있다(S245).

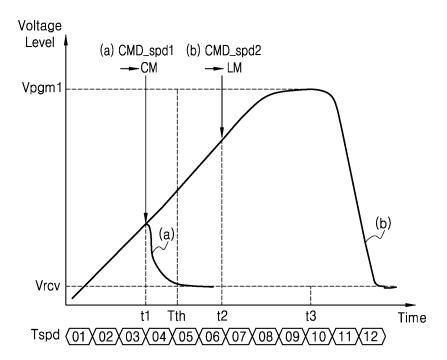

- [0091] 도 14b는 본 개시의 예시적 실시예에 따른 리커버리 모드 매니저의 동작을 나타내는 그래프이다. 자세하게는, 도 14b는 리커버리 모드 매니저가 소요시간 카운팅부를 이용하여 리커버리 모드를 결정하는 실시예를 나타낸다. 또한, 도 15b는 기준 시간(Tth)이 '04'인 실시예를 나타낸다.

- [0092] 도 2, 도 14a 및 도 14b를 참조하면, 리커버리 모드 매니저(130)는 선택 워드라인의 전압 레벨이 높아지는 시점 부터 소요시간(Tspd)의 카운팅을 시작할 수 있다. (a)의 예시에서 비휘발성 메모리 장치(10)가 제1 프로그램 루프를 수행하는 동안, 리커버리 모드 매니저(130)는 제1 시점(t1)에서 제1 서스팬드 커맨드(CMD\_spd1)를 수신할 수 있다. 리커버리 모드 매니저(130)는 제1 시점(t1)에서 소요시간(Tspd)로 '03'을 생성할 수 있고, 생성한 소요시간(Tspd)은 기준 시간(Tth) '04'보다 작기 때문에, 리커버리 모드 매니저(130)는 제어 로직(120)에 리커버리 모드(RM)로서 캔슬 모드(CM)를 출력할 수 있다. 제어 로직(120)은 캔슬 모드(CM)의 수신에 대응하여 리커버리 전압(Vrcv)까지 선택 워드라인의 전압 레벨을 낮춤으로서 바로 리커버리 동작을 수행할 수 있다. 도시되진 않았지만, 리커버리 동작 완료 후 비휘발성 메모리 장치(10)는 긴급 독출 동작을 수행할 수 있다. 또한, 긴급 독출 동작 완료 후 비휘발성 메모리 장치(10)는 리쥼 커맨드(CMD\_rsm)에 대응하여 제1 프로그램 루프를 다시수행할 수 있다.

- [0093] (b)의 예시에서 비휘발성 메모리 장치(10)가 제1 프로그램 루프를 수행하는 동안, 리커버리 모드 매니저(130)는 제2 시점(t2)에서 제2 서스팬드 커맨드(CMD\_spd2)를 수신할 수 있다. 리커버리 모드 매니저(130)는 제2 시점(t2)에서 소요시간(Tspd)로 '06'을 생성할 수 있고, 생성한 소요시간(Tspd)은 기준 시간(Tth) '04'보다 작지 않기 때문에, 리커버리 모드 매니저(130)는 제어 로직(120)에 리커버리 모드(RM)로서 루프 모드(LM)를 출력할 수 있다. 제어 로직(120)은 루프 모드(LM)의 수신에 대응하여 바로 리커버리 동작을 수행하지 않고 선택 워드라인의 전압 레벨을 제1 프로그램 전압(Vpgm1)으로 높임으로서 제1 프로그램 루프를 완료할 수 있다. 비휘발성 메모리 장치(10)는 제1 프로그램 루프를 완료한 제3 시점(t3)에서 리커버리 동작을 수행할 수 있다. 도시되진 않았지만, 리커버리 동작 완료 후 비휘발성 메모리 장치(10)는 긴급 독출 동작을 수행할 수 있다. 또한, 긴급 독출 동작 완료 후 비휘발성 메모리 장치(10)는 리쥼 커맨드(CMD\_rsm)에 대응하여 제1 프로그램 루프 다음 순서인 제2 프로그램 루프를 수행할 수 있다.

- [0094] 도 15는 본 개시의 예시적 실시예에 따른 리커버리 모드 매니저의 동작을 나타내는 순서도이다.

- [0095] 도 2, 도 10 및 도 15를 참조하면, 리커버리 모드 매니저(130)는 서스팬드 커맨드 카운팅부(131), 공급 전압 판단부(132), 워드라인 전압 레벨 판단부(133) 및 소요시간 카운팅부(134) 중 두 개 이상의 조건을 이용하여 리커버리 모드를 결정할 수 있다.

- [0096] 리커버리 모드 매니저(130)는 메모리 컨트롤러(도 1, 20)로부터 긴급 독출을 위한 서스팬드 커맨드(CMD\_spd)를 수신할 수 있다(S251). 리커버리 모드 매니저(130)는 복수의 프로그램 루프 중 제1 프로그램 루프 동안 수신한 서스팬드 커맨드(CMD\_spd)를 카운팅함으로서 서스팬드 커맨드 카운트(Nspd)를 생성할 수 있다(S252). 리커버리 모드 매니저(130)는 서스팬드 커맨드 카운트(Nspd)와 기준 카운트(Nth)를 비교할 수 있다(S253). 서스팬드 커맨드 카운트(Nspd)가 기준 카운트(Nth)보다 작지 않은 경우, 리커버리 모드 매니저(130)는 제어 로직(120)에 리커 버리 모드(RM)로서 루프 모드(LM)를 출력할 수 있다(S256). 서스팬드 커맨드 카운트(Nspd)가 기준 카운트(Nth)보다 작은 경우, 리커버리 모드 매니저(130)는 제어 로직(120)으로부터 수신한 공급 전압(Vspl) 기준 전압(Vth)을 비교할 수 있다(S254). 공급 전압(Vspl)이 기준 전압(Vth)보다 작은 경우, 리커버리 모드 매니저(130)는

제어 로직(120)에 리커버리 모드(RM)로서 캔슬 모드(CM)를 출력할 수 있다(S255). 공급 전압(Vspl)이 기준 전압 (Vth)보다 작지 않은 경우, 리커버리 모드 매니저(130)는 제어 로직(120)에 리커버리 모드(RM)로서 루프 모드 (LM)를 출력할 수 있다(S256).

- [0097] 도 15는 리커버리 모드 매니저(130)가 서스팬드 커맨드 카운팅부(131) 및 공급 전압 판단부(132)를 이용하여 리커버리 모드를 결정하는 실시예에 대해서 도시되어 있으나, 본 개시의 기술적 사상은 이에 한정되지 않고 서로다른 두 개 이상의 조건을 사용하여 리커버리 모드를 결정하는 실시예에 유추 적용될 수 있음은 이해되어야 할것이다.

- [0098] 도 16은 본 개시의 예시적 실시예에 따른 비휘발성 메모리 장치를 SSD 시스템에 적용한 예를 나타내는 블록도이다

- [0099] 도 16를 참조하면, SSD 시스템(1000)은 호스트(1100) 및 SSD(1200)를 포함할 수 있다. SSD(1200)는 신호 커넥터(signal connector)를 통해 호스트(1100)와 신호를 주고 받으며, 전원 커넥터(power connector)를 통해 전원을 입력 받는다. SSD(1200)는 SSD 컨트롤러(1210), 보조 전원 장치(1220) 및 복수의 플래시 메모리 장치들 (1230, 1240, 1250)을 포함할 수 있다. 이때, SSD(1200)는 도 1 내지 도 15에 도시된 실시예들을 이용하여 구현될 수 있다.

- [0100] 구체적으로, 도 2의 비휘발성 메모리 장치(10)가 플래시 메모리 장치들(1230 내지 1250) 중 적어도 하나에 적용될 수 있다. 이에 따라 플래시 메모리 장치들(1230 내지 1250) 중 적어도 하나는 프로그램 수행하는 도중 긴급독출을 위한 서스팬드 커맨드를 수신하면, 서스팬드 커맨드에 기초하여 리커버리 모드를 결정하고, 결정된 리커버리 모드에 따라 서로 다른 시점에서 리커버리 동작을 수행할 수 있다. 이에 따라, 프로그램 요청이 지연되는 기입 지연 현상(Write Starvation)이 방지되고, 효율적인 긴급 독출 동작이 수행될 수 있다.

- [0101] 본 개시의 실시예에 따른 비휘발성 메모리 장치는 SSD(1200) 뿐만 아니라, 메모리 카드 시스템, 컴퓨팅 시스템, UFS 등에 탑재되거나 적용될 수 있다. 또한 본 개시의 실시예에 다른 비휘발성 메모리 장치의 동작 방법은 비휘발성 메모리가 탑재되는 다양한 종류의 전자 시스템에 적용될 수 있다.

- [0102] 이상에서와 같이 도면과 명세서에서 예시적인 실시예들이 개시되었다. 본 명세서에서 특정한 용어를 사용하여 실시예들을 설명되었으나, 이는 단지 본 개시의 기술적 사상을 설명하기 위한 목적에서 사용된 것이지 의미 한 정이나 특허청구범위에 기재된 본 개시의 범위를 제한하기 위하여 사용된 것은 아니다. 그러므로 본 기술분야의 통상의 지식을 가진 자라면 이로부터 다양한 변형 및 균등한 타 실시예가 가능하다는 점을 이해할 것이다. 따라서, 본 개시의 진정한 기술적 보호범위는 첨부된 특허청구범위의 기술적 사상에 의해 정해져야 할 것이다.

#### 도면

#### 도면4a

#### 도면4b

#### 도면11a

# 도면11b

#### 도면12a

#### 도면12b

#### 도면13a

### 도면13b

#### 도면14a

### 도면14b

【심사관 직권보정사항】

【직권보정 1】

【보정항목】청구범위

【보정세부항목】청구항 10

#### 【변경전】

프로그램 커맨드에 대응하여 제1 내지 제N 공급 전압(N은 1이상의 정수)을 순차적으로 인가함으로서 프로그램 대상이 되는 선택 워드라인의 전압 레벨을 증가시키는 단계;

긴급 독출 동작을 위한 서스팬드 커맨드를 수신하는 단계;

상기 제1 프로그램 루프에 대응하는 프로그램 동작 수행 중 수신하는 상기 서스팬드 커맨드를 카운팅하여 서스 팬드 카운트를 생성하는 단계;

상기 서스팬드 커맨드에 기초하여 리커버리 시점에 따른 리커버리 모드를 결정하는 단계;

결정된 상기 리커버리 모드에 따라서 리커버리를 수행하는 단계; 및

독출 커맨드에 대응하여 긴급 독출 동작을 수행하는 단계;를 포함하고,

상기 리커버리 모드는 상기 서스팬드 커맨드 수신 직후에 리커버리를 수행하는 캔슬 모드 및 상기 선택 워드라 인의 전압 레벨을 목표 전압까지 도달 시킨 후 리커버리를 수행하는 루프 모드 중 어느 하나이고,

상기 리커버리를 수행하는 단계는,

상기 서스팬드 카운트가 기준 카운트 이상인 경우 상기 리커버리 시점을 상기 제2 시점으로 결정하는 단계를 포함하는 비휘발성 메모리 장치의 동작 방법.

#### 【변경후】

프로그램 커맨드에 대응하여 제1 내지 제N 공급 전압(N은 1이상의 정수)을 순차적으로 인가함으로서 프로그램 대상이 되는 선택 워드라인의 전압 레벨을 증가시키는 단계;

긴급 독출 동작을 위한 서스팬드 커맨드를 수신하는 단계;

제1 프로그램 루프에 대응하는 프로그램 동작 수행 중 수신하는 상기 서스팬드 커맨드를 카운팅하여 서스팬드

카운트를 생성하는 단계;

상기 서스팬드 커맨드에 기초하여 리커버리 시점에 따른 리커버리 모드를 결정하는 단계;

결정된 상기 리커버리 모드에 따라서 리커버리를 수행하는 단계; 및

독출 커맨드에 대응하여 긴급 독출 동작을 수행하는 단계;를 포함하고,

상기 리커버리 모드는 상기 서스팬드 커맨드 수신 직후에 리커버리를 수행하는 캔슬 모드 및 상기 선택 워드라 인의 전압 레벨을 목표 전압까지 도달 시킨 후 리커버리를 수행하는 루프 모드 중 어느 하나이고,

상기 리커버리를 수행하는 단계는,

상기 서스팬드 카운트가 기준 카운트 이상인 경우 상기 리커버리 시점을 제2 시점으로 결정하는 단계를 포함하는 비휘발성 메모리 장치의 동작 방법.