## (19) 대한민국특허청(KR)

## (12) 등록특허공보(B1)

(51) 국제특허분류(Int. Cl.) **GO2F 1/136** (2006.01)

10-2008-0034348 (21) 출원번호

(22) 출워일자 2008년04월14일 심사청구일자 2013년03월26일

(65) 공개번호 10-2009-0108976 (43) 공개일자 2009년10월19일

(56) 선행기술조사문헌 US5671026 A US20070268637 A1 (11) 등록번호

10-1448002 (24) 등록일자 2014년09월30일

(73) 특허권자

(45) 공고일자

### 삼성디스플레이 주식회사

경기도 용인시 기흥구 삼성2로 95 (농서동)

2014년10월08일

(72) 발명자

#### 윤영수

경기도 수원시 영통구 청명남로12번길 5-20, 203 호 (영통동)

#### 채종철

서울특별시 마포구 독막로42길 2, LG자이아파트 106동 1902호 (염리동)

#### 고준철

경기 화성시 반송동 나루마을우림루미아트아파트 603동 1804호

(74) 대리인

팬코리아특허법인

전체 청구항 수 : 총 16 항

심사관 : 신창우

### (54) 발명의 명칭 박막 트랜지스터 표시판 및 그 제조 방법

#### (57) 요 약

본 발명은 박막 트랜지스터 표시판 및 그 제조 방법에 관한 것이다. 본 발명의 한 실시예에 따른 박막 트랜지스 터 표시판은 기판, 상기 기판 위에 형성되어 있는 제1 및 제2 신호선, 상기 제1 및 제2 신호선과 연결되어 있으 며 제1 절연막을 포함하는 스위칭 박막 트랜지스터, 상기 스위칭 박막 트랜지스터와 연결되어 있으며 제2 절연막 을 포함하는 구동 박막 트랜지스터, 그리고 상기 제1 및 제2 신호선과 연결되어 있고 상기 제1 절연막 및 상기 제2 절연막을 포함하는 방전 박막 트랜지스터를 포함한다.

## 대 표 도 - 도4

### 특허청구의 범위

#### 청구항 1

기판.

상기 기판 위에 형성되어 있는 제1 및 제2 신호선,

상기 제1 신호선과 연결되어 있는 제1전극 및 상기 제2 신호선과 연결되어 있는 제2전극을 포함하는 스위칭 박막 트랜지스터.

상기 스위칭 박막 트랜지스터와 연결되어 있는 제3전극 및 상기 제3전극과 분리되어 있는 제4전극을 포함하는 구동 박막 트랜지스터, 그리고

상기 제1 신호선 또는 상기 제2 신호선과 연결되어 있는 제5전극, 그리고 상기 제5전극과 다른 층에 위치하는 제6전극을 포함하는 방전 박막 트랜지스터

를 포함하고,

상기 스위칭 박막 트랜지스터는 상기 제1전극과 상기 제2전극 사이에 위치하는 제1 절연막을 포함하고.

상기 구동 박막 트랜지스터는 상기 제3전극과 상기 제4전극 사이에 위치하며 상기 제1 절연막과 다른 층에 위치하는 제2 절연막을 포함하고,

상기 제1 절연막과 상기 제2 절연막은 상기 방전 박막 트랜지스터의 상기 제5전극과 상기 제6전극 사이에 위치하는

박막 트랜지스터 표시판.

### 청구항 2

제1항에서,

상기 스위칭 박막 트랜지스터는

상기 제2전극과 마주하며 상기 구동 박막 트랜지스터의 상기 제3전극과 연결되어 있는 제1 출력 전극, 그리고

상기 제1전극과 상기 제2전극 및 상기 제1 출력 전극 사이에 위치하는 제1 반도체

를 더 포함하며,

상기 제1 절연막은 상기 제1전극과 상기 제1 반도체 사이에 위치하는

박막 트랜지스터 표시판.

#### 청구항 3

제2항에서,

상기 구동 박막 트랜지스터의 상기 제3전극은 상기 제1 출력 전극과 연결되어 있고,

상기 구동 박막 트랜지스터의 상기 제4전극은 상기 제3전극과 일부분 중첩하고,

상기 구동 박막 트랜지스터는

상기 제4전극과 마주하는 제2 출력 전극, 그리고

상기 제3전극과 상기 제4전극 및 상기 제2 출력 전극 사이에 위치하는 제2 반도체

를 더 포함하며,

상기 제2 절연막은 상기 제3전극과 상기 제2 반도체 사이에 위치하는

박막 트랜지스터 표시판.

### 청구항 4

제3항에서,

상기 제2 절연막은 상기 제1 절연막 하부에 위치하는 박막 트랜지스터 표시판.

#### 청구항 5

제3항에서.

상기 제1 신호선 또는 상기 제2 신호선과 절연되어 교차하는 구동 전압선을 더 포함하고, 상기 제4전극은 상기 구동 전압선과 연결되어 있는 박막 트랜지스터 표시판.

#### 청구항 6

제3항에서,

표시 영역,

상기 표시 영역 주변에 형성되어 있는 주변 영역, 그리고

상기 주변 영역에 형성되어 있는 단락선

을 더 포함하는 박막 트랜지스터 표시판.

### 청구항 7

제6항에서,

상기 방전 박막 트랜지스터는

상기 제5전극과 마주하는 방전 출력 전극, 그리고

상기 제5전극과 상기 제6전극 사이에 위치하는 방전 반도체를 더 포함하며,

상기 제1 절연막 및 상기 제2 절연막은 상기 제6전극과 상기 방전 반도체 사이에 위치하는 박막 트랜지스터 표시판.

## 청구항 8

제7항에서,

상기 방전 출력 전극은 상기 단락선과 연결되어 있는

박막 트랜지스터 표시판.

#### 청구항 9

제7항에서,

상기 제6전극 및 상기 방전 출력 전극은 상기 단락선과 연결되어 있는

박막 트랜지스터 표시판.

### 청구항 10

제7항에서,

상기 제1 반도체 및 상기 방전 반도체는 비정질 반도체를 포함하고, 상기 제2 반도체는 결정질 반도체를 포함하는 박막 트랜지스터 표시판.

### 청구항 11

제7항에서,

상기 제6전극과 상기 제3전극은 하나의 마스크로 동시에 형성되는 박막 트랜지스터 표시판.

### 청구항 12

제7항에서,

상기 제1전극, 상기 제4전극 및 상기 제2 출력 전극은 하나의 마스크로 동시에 형성되는 박막 트랜지스터 표시 판.

#### 청구항 13

제7항에서,

상기 제1 반도체와 상기 방전 반도체는 하나의 마스크로 동시에 형성되고,

상기 제2전극, 상기 제1 출력 전극, 상기 제5전극 및 상기 방전 출력 전극도 하나의 마스크로 동시에 형성되는 박막 트랜지스터 표시판.

### 청구항 14

기판 위에 구동 제어 전극 및 방전 제어 전극을 형성하는 단계,

상기 구동 제어 전극 및 상기 방전 제어 전극을 형성한 다음 상기 구동 제어 전극 및 상기 방전 제어 전극 위에 제1 절연막을 형성하는 단계,

상기 제1 절연막을 형성한 다음 상기 제1 절연막 위에 구동 반도체를 형성하는 단계,

상기 구동 반도체를 형성한 다음 상기 제1 게이트 절연막 및 상기 구동 반도체 위에 도전층을 적충하고 사진 식 각하여 스위칭 제어 전극, 구동 전압선 및 구동 출력 전극을 형성하는 단계,

상기 스위칭 제어 전극, 상기 구동 전압선 및 상기 구동 출력 전극을 형성한 다음 상기 스위칭 제어 전극, 상기 구동 전압선, 상기 구동 출력 전극 및 상기 제1 절연막 위에 제2 절연막을 형성하는 단계,

상기 제2 절연막을 형성한 다음 상기 제2 절연막 위에 스위칭 반도체 및 방전 반도체를 형성하는 단계,

상기 스위칭 반도체 및 상기 방전 반도체를 형성한 다음 상기 제2 절연막, 상기 스위칭 반도체 및 상기 방전 반도체 위에 스위칭 입력 전극을 포함하는 데이터선, 스위칭 출력 전극, 방전 입력 전극 및 방전 출력 전극을 형성하는 단계,

상기 데이터선, 상기 스위칭 출력 전극, 상기 방전 입력 전극 및 상기 방전 출력 전극을 형성한 다음 상기 구동 출력 전극과 연결되어 있는 화소 전극을 형성하는 단계,

상기 화소 전극을 형성한 다음 상기 화소 전극 위에 발광 부재를 형성하는 단계, 그리고

상기 발광 부재를 형성한 다음 상기 발광 부재 위에 공통 전극을 형성하는 단계

를 포함하는

박막 트랜지스터 표시판의 제조 방법.

#### 청구항 15

제14항에서,

상기 구동 반도체를 형성하는 단계는 결정질 반도체를 중착하는 단계를 포함하는 박막 트랜지스터 표시판의 제조 방법.

#### 청구항 16

제14항에서,

상기 구동 반도체를 형성하는 단계는

비정질 반도체를 형성하는 단계, 그리고

상기 비정질 반도체를 형성한 다음 상기 비정질 반도체를 결정화하는 단계

를 포함하는 박막 트랜지스터 표시판의 제조 방법.

### 명 세 서

### 발명의 상세한 설명

### 기술분야

[0001] 본 발명은 박막 트랜지스터 표시판 및 그 제조 방법에 관한 것이다.

#### 배경기술

- [0002] 박막 트랜지스터 표시판은 액정 표시 장치(liquid crystal display)나 유기 발광 표시 장치(organic light emitting diode display) 등에서 각 화소를 독립적으로 구동하기 위한 회로 기판으로서 사용된다.

- [0003] 유기 발광 표시 장치는 두 개의 전극과 그 사이에 위치하는 발광층을 포함하며, 하나의 전극으로부터 주입된 전 자(electron)와 다른 전극으로부터 주입된 정공(hole)이 발광층에서 결합하여 여기자(exciton)를 형성하고, 여기자가 에너지를 방출하면서 발광한다.

- [0004] 이를 위해 유기 발광 표시 장치의 박막 트랜지스터 표시판은 신호선에 연결되어 데이터 전압을 제어하는 스위칭 박막 트랜지스터(switching thin film transistor) 및 이로부터 전달받은 데이터 전압을 게이트 전압으로 인가 하여 발광 소자에 전류를 흘리는 구동 박막 트랜지스터(driving thin film transistor)를 포함한다.

- [0005] 한편, 박막 트랜지스터 표시판 주변 영역에는 게이트선 또는 데이터선에 연결되어 유입된 정전기를 분산시켜 정전 전압을 떨어뜨리거나 축전기에 정전하를 충전하고 과전압시 먼저 터짐으로써 박막 트랜지스터 표시판의 주된 회로를 보호하는 정전기 방전 방지 회로(electrostatic discharge protection circuit)가 구비된다. 정전기 방전 방지 회로도 문턱 전압(turn-on voltage) 이상의 전압이 인가되면 턴 온되는 방전 박막 트랜지스터를 포함한다.

### 발명의 내용

### 해결 하고자하는 과제

[0006] 정전기 방전 방지 회로의 문턱 전압이 낮을 경우 누설 전류가 생겨 게이트 온 전압 또는 데이터 전압에 손실을 가져올 수 있다. 따라서 본 발명이 이루고자 하는 기술적 과제는 유기 발광 표시 장치 등의 표시 장치에 있어서 정전기 방전 방지 회로에 쓰이는 방전 박막 트랜지스터의 문턱 전압을 높여 누설 전류를 방지하는 것이다.

### 과제 해결수단

- [0007] 본 발명의 한 실시예에 따른 박막 트랜지스터 표시판은 기판, 상기 기판 위에 형성되어 있는 제1 및 제2 신호선, 상기 제1 및 제2 신호선과 연결되어 있으며 제1 절연막을 포함하는 스위칭 박막 트랜지스터, 상기 스위칭 박막 트랜지스터와 연결되어 있으며 제2 절연막을 포함하는 구동 박막 트랜지스터, 그리고 상기 제1 및 제2 신호선과 연결되어 있고 상기 제1 절연막 및 상기 제2 절연막을 포함하는 방전 박막 트랜지스터를 포함한다.

- [0008] 상기 스위칭 박막 트랜지스터는 상기 제1 신호선과 연결되어 있는 제1 제어 전극, 상기 제2 신호선과 연결되어 있는 제1 입력 전극, 상기 제1 입력 전극과 마주하며 상기 구동 박막 트랜지스터와 연결되어 있는 제1 출력 전극, 그리고 상기 제1 제어 전극과 상기 제1 입력 전극 및 상기 제1 출력 전극 사이에 위치하는 제1 반도체를 더 포함하며, 상기 제1 절연막은 상기 제1 제어 전극과 상기 제1 반도체 사이에 위치할 수 있다.

- [0009] 상기 구동 박막 트랜지스터는 상기 제1 출력 전극과 연결되어 있는 제2 제어 전극, 상기 제2 제어 전극과 일부분 중첩하는 제2 입력 전극, 상기 제2 입력 전극과 마주하는 제2 출력 전극, 그리고 상기 제2 제어 전극과 상기 제2 입력 전극 및 상기 제2 출력 전극 사이에 위치하는 제2 반도체를 더 포함하며, 상기 제2 절연막은 상기 제2 제어 전극과 상기 제2 반도체 사이에 위치할 수 있다.

- [0010] 상기 제2 절연막은 상기 제1 절연막 상부에 위치할 수 있다.

- [0011] 상기 제1 신호선 또는 상기 제2 신호선과 절연되어 교차하는 구동 전압선을 더 포함하고, 상기 제2 입력 전극은 상기 구동 전압선과 연결되어 있을 수 있다.

- [0012] 표시 영역, 상기 표시 영역 주변에 형성되어 있는 주변 영역, 상기 주변 영역에 형성되어 있는 단락선을 더 포

함할 수 있다.

- [0013] 상기 방전 박막 트랜지스터는 상기 제1 신호선 또는 상기 제2 신호선과 연결되어 있는 방전 제어 전극 및 방전 입력 전극, 상기 단락선과 연결되어 있는 방전 출력 전극, 그리고 상기 방전 제어 전극과 상기 방전 입력 전극 및 상기 방전 출력 전극 사이에 위치하는 방전 반도체를 더 포함하며, 상기 제1 절연막 및 상기 제2 절연막은 상기 방전 제어 전극과 상기 방전 반도체 사이에 위치할 수 있다.

- [0014] 상기 방전 박막 트랜지스터는 상기 단락선과 연결되어 있는 방전 제어 전극 및 방전 입력 전극, 상기 제1 신호 선과 또는 상기 제2 신호선과 연결되어 있는 방전 출력 전극, 그리고 상기 방전 제어 전극과 상기 방전 입력 전 극 및 상기 방전 출력 전극 사이에 위치하는 방전 반도체를 더 포함하며, 상기 제1 절연막 및 상기 제2 절연막 은 상기 방전 제어 전극과 상기 방전 반도체 사이에 위치할 수 있다.

- [0015] 상기 제1 반도체 및 방전 반도체는 비정질 반도체를 포함하고, 상기 제2 반도체는 결정질 반도체를 포함할 수 있다.

- [0016] 상기 방전 제어 전극과 상기 제2 제어 전극은 하나의 마스크로 동시에 형성될 수 있다.

- [0017] 상기 제1 제어 전극, 상기 제2 입력 전극 및 상기 제2 출력 전극은 하나의 마스크로 동시에 형성될 수 있다.

- [0018] 상기 제1 반도체와 상기 방전 반도체는 하나의 마스크로 동시에 형성되고, 상기 제1 입력 전극, 상기 제1 출력 전극, 상기 방전 입력 전극 및 상기 방전 출력 전극도 다른 하나의 마스크로 동시에 형성될 수 있다.

- [0019] 본 발명의 한 실시예에 따른 박막 트랜지스터 표시판의 제조 방법은 기판 위에 구동 제어 전극 및 방전 제어 전 극을 형성하는 단계, 상기 구동 제어 전극 및 상기 방전 제어 전극 위에 제1 절연막을 형성하는 단계, 상기 제1 절연막 위에 구동 반도체를 형성하는 단계, 상기 제1 게이트 절연막 및 상기 구동 반도체 위에 도전층을 적층하고 사진 식각하여 스위칭 제어 전극, 구동 전압선 및 구동 출력 전극을 형성하는 단계, 상기 스위칭 제어 전극, 상기 구동 전압선, 상기 구동 출력 전극 및 상기 제1 절연막 위에 제2 절연막을 형성하는 단계, 상기 제2 절연막 위에 스위칭 반도체 및 방전 반도체를 형성하는 단계, 상기 제2 절연막, 상기 스위칭 반도체 및 상기 방전 반도체 위에 스위칭 입력 전극을 포함하는 데이터선, 스위칭 출력 전극, 방전 입력 전극 및 방전 출력 전극을 형성하는 단계, 상기 구동 출력 전극과 연결되어 있는 화소 전극을 형성하는 단계, 상기 화소 전극 위에 발광 부재를 형성하는 단계, 그리고 상기 발광 부재 위에 공통 전극을 형성하는 단계를 포함한다.

- [0020] 상기 구동 반도체를 형성하는 단계는 결정질 반도체를 증착하는 단계를 포함할 수 있다..

- [0021] 상기 구동 반도체를 형성하는 단계는 비정질 반도체를 형성하는 단계, 그리고 상기 비정질 반도체를 결정화하는 단계를 포함할 수 있다.

#### 直 과

[0022] 본 발명에 따르면 정전기 방전 방지 회로의 트랜지스터의 문턱 전압을 높여 트랜지스터를 통한 누설 전류를 막 아 데이터 전압 및 게이트 온 전압의 손실을 방지할 수 있다.

### 발명의 실시를 위한 구체적인 내용

- [0023] 그러면 첨부한 도면을 참고로 하여 본 발명의 실시예에 대하여 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자가 용이하게 실시할 수 있도록 상세히 설명한다. 그러나 본 발명은 여러 가지 상이한 형태로 구현될 수 있으며 여기에서 설명하는 실시예에 한정되지 않는다.

- [0024] 도면에서 여러 층 및 영역을 명확하게 표현하기 위하여 두께를 확대하여 나타내었다. 명세서 전체를 통하여 유사한 부분에 대해서는 동일한 도면 부호를 붙였다. 층, 막, 영역, 판 등의 부분이 다른 부분 "위에" 있다고 할때, 이는 다른 부분 "바로 위에" 있는 경우 뿐만 아니라 그 중간에 또 다른 부분이 있는 경우도 포함한다. 반대로 어떤 부분이 다른 부분 "바로 위에" 있다고 할때에는 중간에 다른 부분이 없는 것을 뜻한다.

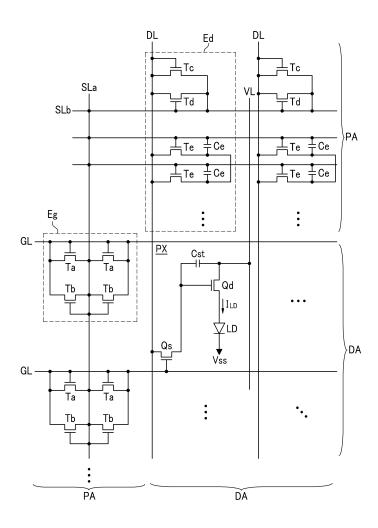

- [0025] 도 1은 본 발명의 한 실시예에 따른 표시 장치용 박막 트랜지스터 표시판의 등가 회로도이다.

- [0026] 도 1을 참고하면, 본 실시예에 따른 박막 트랜지스터 표시판은 화면을 이루는 표시 영역(DA)과 그 주변 영역 (PA)을 포함한다.

- [0027] 표시 영역(DA)은 복수의 신호선(GL, DL, VL)과 이들에 연결되어 있으며 대략 행렬(matrix)의 형태로 배열된 복수의 화소(PX)를 포함한다.

- [0028] 신호선(GL, DL, VL)은 주사 신호를 전달하는 복수의 주사 신호선(scanning line)(GL), 데이터 전압을 전달하는 복수의 데이터선(data line)(DL) 및 구동 전압(Vdd)을 전달하는 복수의 구동 전압선(driving voltage line)(VL)을 포함한다. 주사 신호선(GL)은 대략 행 방향으로 뻗어 있으며 서로가 거의 평행하고 데이터선(DL)과 구동 전압선(VL)은 대략 열 방향으로 뻗어 있으며 서로가 거의 평행하다.

- [0029] 각 화소(PX)는 스위칭 트랜지스터(switching transistor)(Qs), 구동 트랜지스터(driving transistor)(Qd), 유 지 축전기(storage capacitor)(Cst) 및 유기 발광 소자(organic light emitting element)(LD)를 포함한다.

- [0030] 스위칭 트랜지스터(Qs) 및 구동 트랜지스터(Qd)는 각각 제어 단자(control terminal), 입력 단자(input terminal) 및 출력 단자(output terminal)를 가진다.

- [0031] 스위칭 트랜지스터(Qs)의 제어 단자는 주사 신호선(GL)과 연결되어 있고, 입력 단자는 데이터선(DL)과 연결되어 있으며, 출력 단자는 구동 트랜지스터(Qd)와 연결되어 있다. 스위칭 트랜지스터(Qs)는 주사 신호선(GL)에 인가되는 주사 신호에 응답하여 데이터선(DL)에 인가되는 데이터 전압을 구동 트랜지스터(Qd)에 전달한다.

- [0032] 구동 트랜지스터(Qd)의 제어 단자는 스위칭 트랜지스터(Qs)와 연결되어 있고, 입력 단자는 구동 전압선(VL)과 연결되어 있으며, 출력 단자는 유기 발광 소자(LD)와 연결되어 있다. 구동 트랜지스터(Qd)는 제어 단자와 출력 단자 사이에 걸리는 전압에 따라 그 크기가 달라지는 출력 전류(I<sub>LD</sub>)를 흘린다.

- [0033] 유지 축전기(Cst)는 구동 트랜지스터(Qd)의 제어 단자와 입력 단자 사이에 연결되어 있다. 유지 축전기(Cst)는 구동 트랜지스터(Qd)의 제어 단자에 인가되는 데이터 전압을 충전하고 스위칭 트랜지스터(Qs)가 턴 오프된 뒤에 도 이를 유지한다.

- [0034] 유기 발광 소자(LD)는 유기 발광 다이오드(organic light emitting diode, OLED)일 수 있으며, 구동 트랜지스 터(Qd)의 출력 단자에 연결되어 있는 애노드(anode)와 공통 전압(Vss)에 연결되어 있는 캐소드(cathode)를 가진다. 유기 발광 소자(LD)는 구동 트랜지스터(Qd)의 출력 전류(I<sub>LD</sub>)에 따라 세기를 달리하여 발광함으로써 영상을 표시한다.

- [0035] 스위칭 트랜지스터(Qs) 및 구동 트랜지스터(Qd)는 비정질 규소 또는 다결정 규소로 만들어진 n-채널 전계 효과 트랜지스터(field effect transistor, FET)이다. 그러나 스위칭 트랜지스터(Qs)와 구동 트랜지스터(Qd) 중 적어도 하나는 p-채널 전계 효과 트랜지스터일 수 있다. 또한, 트랜지스터(Qs, Qd), 축전기(Cst) 및 유기 발광소자(LD)의 연결 관계가 바뀔 수 있다.

- [0036] 주변 영역(PA)은 복수의 가로 단락선(SLb), 세로 단락선(SLa), 주사 신호선(GL) 및 세로 단락선(SLa)에 연결되어 있는 복수의 제1 정전기 방전 방지 회로(Eg), 그리고 데이터선(DL) 및 가로 단락선(SLb)에 연결되어 있는 복수의 제2 정전기 방전 방지 회로(Ed)를 포함한다.

- [0037] 가로 단락선(SLb)은 대략 행 방향으로 뻗어 있으며 서로가 거의 평행하고, 세로 단락선(SLa)은 대략 열 방향으로 뻗어 있으며 가로 단락선(SLb)과 전기적으로 연결되어 있다.

- [0038] 제1 정전기 방전 방지 회로(Eg)는 한 쌍의 제1 상부 방전 트랜지스터(Ta)와 한 쌍의 제1 하부 방전 트랜지스터 (Tb)를 포함하며, 제1 상부 및 하부 방전 트랜지스터(Ta, Tb)는 각각 제어 단자, 입력 단자 및 출력 단자를 포함한다.

- [0039] 제1 상부 방전 트랜지스터(Ta)의 제어 단자 및 입력 단자는 주사 신호선(GL)에 연결되어 있고, 출력 단자는 세로 단락선(SLa)에 연결되어 있다. 제1 하부 방전 트랜지스터(Tb)의 제어 단자 및 입력 단자는 세로 단락선 (SLa)에 연결되어 있고, 출력 단자는 주사 신호선(GL)에 연결되어 있다. 한 주사 신호선(GL)으로 문턱 전압 이상의 정전기가 유입되면 제1 상부 방전 트랜지스터(Ta)가 턴 온되고 정전기는 제1 상부 방전 트랜지스터(Ta)를 통해 세로 단락선(SLa)으로 전달된다. 그러면 세로 단락선(SLa)으로 전달된 정전기에 의해 다른 주사 신호선 (GL)에 연결된 제1 정전기 방전 방지 회로(Eg)의 제1 하부 방전 트랜지스터(Tb)가 턴 온되고 정전기는 제1 하부 방전 트랜지스터(Tb)를 통해 다른 주사 신호선(GL)으로 분산된다.

- [0040] 제2 정전기 방전 방지 회로(Ed)는 제2 상부 방전 트랜지스터(Tc), 제2 하부 방전 트랜지스터(Td), 제3 방전 트랜지스터(Te) 및 방전 축전기(Ce)를 포함한다.

- [0041] 제2 상부 방전 트랜지스터(Tc)의 제어 단자 및 입력 단자는 데이터선(DL)에 연결되어 있고, 출력 단자는 가로 단락선(SLb)에 연결되어 있다. 또한 제2 하부 트랜지스터(Td)의 제어 단자 및 입력 단자는 가로 단락선(SLb)에 연결되어 있고, 출력 단자는 데이터선(DL)에 연결되어 있다. 한 데이터선(DL)으로 문턱 전압 이상의 정전기가

유입되면 제2 상부 방전 트랜지스터(Tc)가 턴 온되고 정전기는 제2 상부 방전 트랜지스터(Tc)를 통해 가로 단락선(SLb)으로 전달된다. 그러면 가로 단락선(SLb)으로 전달된 정전기에 의해 다른 데이터선(DL)에 연결된 제2 정전기 방전 방지 회로(Ed)의 제2 하부 방전 트랜지스터(Td)가 턴 온되고 정전기는 제2 하부 방전 트랜지스터(Td)를 통해 다른 데이터선(DL)으로 분산된다. 한편 데이터선(DL)에 유입된 정전기는 제3 방전 트랜지스터(Te)를 통해 방전 축전기(Ce)에 충전되었다가 과전압시 표시 영역(DA) 내의 트랜지스터(Qs, Qd)를 대신해 먼저 터짐으로써 표시 영역(DA)의 회로를 보호한다.

- [0042] 이제 도 1에 도시한 박막 트랜지스터 표시판의 상세 구조에 대하여 도 2 내지 도 4를 참고하여 상세하게 설명한다.

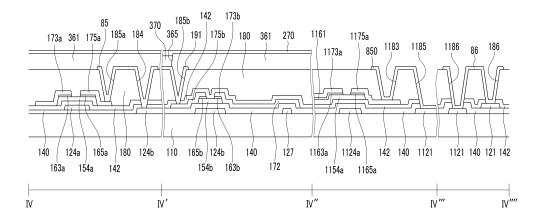

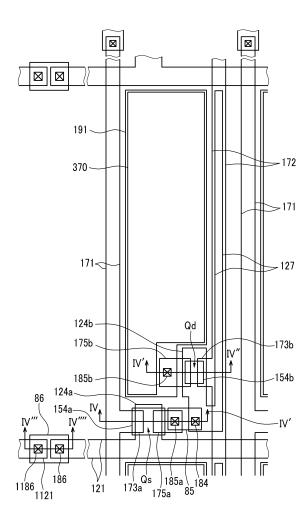

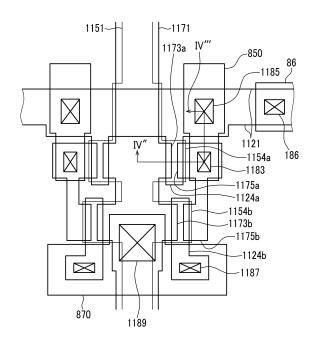

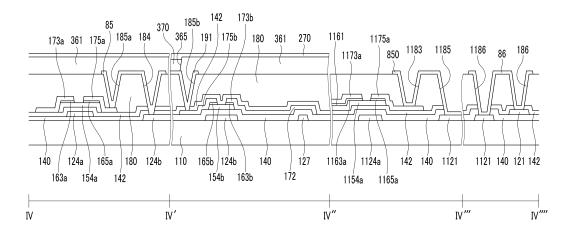

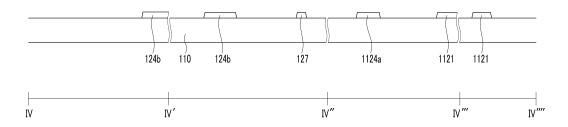

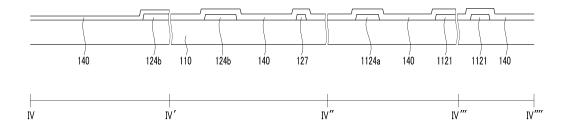

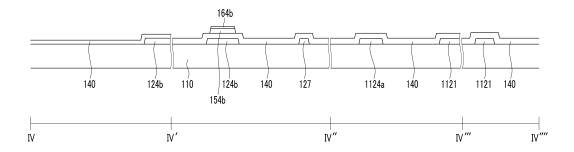

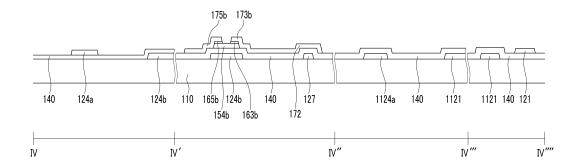

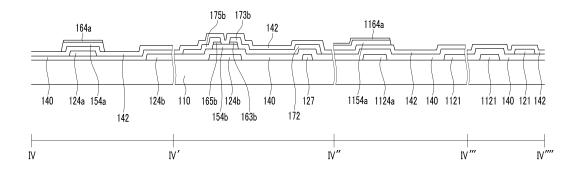

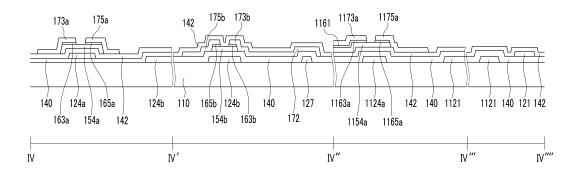

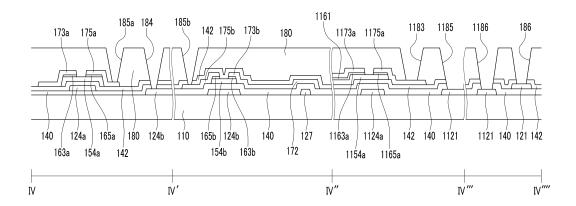

- [0043] 도 2는 본 발명의 한 실시예에 따른 표시 장치용 박막 트랜지스터 표시판의 한 화소에 대한 배치도이고, 도 3은 본 발명의 한 실시예에 따른 표시 장치용 박막 트랜지스터 표시판의 정전기 방전 방지 회로의 배치도이고, 도 4는 도 2의 박막 트랜지스터 표시판을 IV-IV'선, IV'-IV''선 및 IV'''-IV'''선을 따라 자르고 도 3의 정전기 방전 방지 회로를 IV''-IV''' 선을 따라 잘라 함께 도시한 단면도이다.

- [0044] 절연 기판(110) 위에 복수의 구동 제어 전극(driving control electrode)(124b), 복수의 방전 주사 신호선 (1121) 및 복수 쌍의 하부 방전 제어 전극(1124b)을 포함하는 복수의 게이트 도전체(gate conductor)가 형성되어 있다. 방전 주사 신호선(1121) 및 하부 방전 제어 전극(1124b)은 박막 트랜지스터 표시판의 주변 영역에 형성되어 있다.

- [0045] 구동 제어 전극(124b)은 섬형이며, 세로 방향으로 길게 뻗은 유지 전극(storage electrode)(127)을 포함한다.

- [0046] 방전 주사 신호선(1121)은 주사 신호를 전달하며 주로 가로 방향으로 뻗어 있고 아래로 돌출한 한 쌍의 상부 방전 제어 전극(1124a)을 포함한다.

- [0047] 하부 방전 제어 전극(1124b)은 섬형이며 상부 방전 제어 전극(1124a) 아래에 하나씩 위치한다. 하부 방전 제어 전극(1124b)는 세로 방향으로 짧게 뻗어 있는 부분과 다른 층과의 접속을 위한 면적이 넓은 부분을 포함한다.

- [0048] 게이트 도전체(124b, 1121, 1124b) 위에는 질화규소 또는 산화규소 따위로 만들어진 하부 게이트 절연막(gate insulating layer)(140)이 형성되어 있다.

- [0049] 하부 게이트 절연막(140) 위에는 복수의 구동 반도체(154b)가 형성되어 있다. 구동 반도체(154b)는 구동 제어 전극(124b) 위에 위치하며 결정질 규소(crystalline silicon)로 만들어질 수 있다.

- [0050] 구동 반도체(154b) 위에는 복수 쌍의 저항성 접촉 부재(ohmic contact)(163b, 165b)가 형성되어 있다. 저항성 접촉 부재(163b, 165b)는 섬형이며, 인(P) 따위의 n형 불순물이 고농도로 도핑되어 있는 결정질 또는 비정질 규소 등의 물질로 만들어질 수 있다.

- [0051] 저항성 접촉 부재(163b, 165b) 및 하부 게이트 절연막(140) 위에는 스위칭 제어 전극(switching control electrode)(124a)을 포함하는 복수의 주사 신호선(121), 구동 입력 전극(driving input electrode)(173b)을 포함하는 복수의 구동 전압선(172) 및 복수의 구동 출력 전극(175b)을 포함하는 복수의 제1 데이터 도전체(data conductor)가 형성되어 있다.

- [0052] 주사 신호선(121)은 주사 신호를 전달하고 주로 가로 방향으로 뻗어 있으며, 스위칭 제어 전극(124a)은 주사 신호선(121)으로부터 위로 뻗어 있다.

- [0053] 구동 전압선(172)은 구동 전압을 전달하며 주로 세로 방향으로 뻗어 주사 신호선(121)과 교차한다. 각 구동 전압선(172)은 구동 제어 전극(124b)을 향하여 뻗은 복수의 구동 입력 전극(173b)을 포함하며 유지 전극(127)과 중첩한다.

- [0054] 구동 출력 전극(175b)은 주사 신호선(121), 데이터선(171) 및 구동 전압선(172)과 분리되어 있다. 구동 입력 전극(173b)과 구동 출력 전극(175b)은 구동 반도체(154b) 위에서 서로 마주한다.

- [0055] 제1 데이터 도전체(121, 172, 175b)는 게이트 도전체(124b, 1121, 1124b)와 동일한 재료로 만들어질 수 있다.

- [0056] 주사 신호선(121), 구동 전압선(172) 및 구동 출력 전극(175b) 위에는 질화규소 또는 산화규소 따위로 만들어진 상부 게이트 절연막(142)이 형성되어 있다.

- [0057] 상부 게이트 절연막(142) 위에는 복수의 스위칭 반도체(154a) 및 박막 트랜지스터 표시판의 주변 영역에 위치하는 선형 방전 반도체(1151)가 형성되어 있다.

- [0058] 스위칭 반도체(154a)는 스위칭 제어 전극(124a) 위에 위치하고, 방전 반도체(1151)는 선형이며 주로 세로로 뻗어 있다. 또한 방전 반도체(1151)는 상부 및 하부 방전 제어 전극(1124a, 1124b)을 향하여 좌우로 각각 뻗은 상부 및 하부 돌출부(1154a, 1154b)를 포함한다. 스위칭 반도체(154a) 및 방전 반도체(1151)는 수소화 비정질 규소(hydrogenated amorphous silicon)로 만들어질 수 있다

- [0059] 스위칭 반도체(154a) 위에는 복수 쌍의 섬형 저항성 접촉 부재(ohmic contact)(163a, 165a)가 형성되어 있으며, 방전 반도체(1151) 위에는 선형 저항성 접촉 부재(1161) 및 복수의 섬형 저항성 접촉 부재(1165a)가 형성되어 있다. 선형 저항성 접촉 부재(1161)는 방전 반도체(1151)의 상부 및 하부 돌출부(1154a, 1154b) 위에 위치하며 일부분 중첩하는 돌출부(1163a)를 포함한다. 저항성 접촉 부재(163a, 165a, 1161, 1165a)는 인(P) 따위의 불순물이 고농도로 도핑되어 있는 n+ 수소화 비정질 규소 따위로 만들어질 수 있다.

- [0060] 저항성 접촉 부재(163a, 165a, 1161, 1165a) 및 상부 게이트 절연막(142) 위에는 복수의 데이터선(171), 복수의 스위칭 출력 전극(175a), 세로 단락선(1171) 및 복수의 상부 및 하부 방전 출력 전극(1175a, 1175b)을 포함하는 제2 데이터 도전체가 형성되어 있다. 세로 단락선(1171)과 상부 및 하부 방전 출력 전극(1175a, 1175b)은 박막 트랜지스터 표시판의 주변 영역에 형성되어 있다.

- [0061] 데이터선(171)은 데이터 신호를 전달하며 주로 세로 방향으로 뻗어 주사 신호선(121)과 교차한다. 각 데이터선 (171)은 스위칭 제어 전극(124a)을 향하여 뻗은 복수의 스위칭 입력 전극(switching input electrode)(173a)을 포함한다.

- [0062] 스위칭 출력 전극(175a)은 데이터선(171)과 분리되어 있다. 스위칭 입력 전극(173a) 및 스위칭 출력 전극 (175a)은 스위칭 반도체(154a)를 중심으로 서로 마주한다.

- [0063] 세로 단락선(1171)은 주로 세로 방향으로 뻗어 방전 주사 신호선(1121)과 교차하며, 상부 및 하부 방전 제어 전 극(1124a, 1124b)을 향하여 좌우로 각각 뻗은 복수의 상부 및 하부 방전 입력 전극(1173a, 1173b)을 포함한다.

- [0064] 상/하부 방전 출력 전극(1175a/1175b)은 상/하부 방전 제어 전극(1124a/1124b)을 중심으로 상/하부 방전 입력 전극(1173a/1173b)과 마주하며, 상부 및 하부 방전 출력 전극(1175a, 1175b)은 상하로 연결되어 있다.

- [0065] 제2 데이터 도전체(171, 175a, 1171, 1175a, 1175b)는 게이트 도전체(124b, 1121, 1124b)와 동일한 재료로 만들어질 수 있다.

- [0066] 제2 데이터 도전체(171, 175a, 1171, 1175a, 1175b) 위에는 보호막(passivation layer)(180)이 형성되어 있다.

- [0067] 보호막(180)에는 스위칭 출력 전극(175a)을 드러내는 복수의 접촉 구멍(contact hole)(185a), 상부 방전 출력 전극(1175a)을 드러내는 복수의 접촉 구멍(1183), 그리고 세로 단락선(1171)의 일부를 드러내는 접촉 구멍(1189)이 형성되어 있다. 보호막(180) 및 상부 게이트 절연막(142)에는 구동 출력 전극(175b)을 드러내는 복수의 접촉 구멍(185b) 및 주사 신호선(121)의 끝 부분을 드러내는 복수의 접촉 구멍(186)이 형성되어 있다. 보호막(180), 상부 게이트 절연막(142) 및 하부 게이트 절연막(140)에는 구동 제어 전극(124b)을 드러내는 복수의 접촉 구멍(184), 방전 주사 신호선(1121)을 드러내는 복수의 접촉 구멍(1185, 1186), 그리고 하부 방전 제어 전극(1124b)을 드러내는 복수의 접촉 구멍(1187)이 형성되어 있다.

- [0068] 보호막(180) 위에는 복수의 화소 전극(pixel electrode)(191) 및 복수의 연결 부재(85, 86, 850, 870)가 형성되어 있다.

- [0069] 화소 전극(191)은 접촉 구멍(185b)을 통하여 구동 출력 전극(175b)과 전기적으로 연결되어 있다.

- [0070] 연결 부재(85)는 접촉 구멍(184, 185a)을 통하여 스위칭 출력 전극(175a) 및 구동 제어 전극(124b)과 연결되어 있고, 연결 부재(86)는 접촉 구멍(186, 1186)을 통하여 주사 신호선(121) 및 방전 주사 신호선(1121)과 연결되어 있다. 연결 부재(850)는 접촉 구멍(1183, 1185)을 통하여 상부 방전 출력 전극(1175a) 및 방전 주사 신호선 (1121)과 연결되어 있고, 연결 부재(870)는 접촉 구멍(1187, 1189)을 통하여 하부 방전 제어 전극(1124b) 및 세로 단락선(1171)과 연결되어 있다.

- [0071] 화소 전극(191) 및 연결 부재(85, 86, 850, 870)는 ITO 또는 IZO 따위의 투명 도전체로 만들어질 수 있다.

- [0072] 보호막(180), 화소 전극(191) 및 연결 부재(85, 86, 850, 870) 위에는 격벽(partition)(361)이 형성되어 있다. 격벽(361)은 화소 전극(191) 가장자리 주변을 둑(bank)처럼 둘러싸서 개구부(opening)(365)를 정의하며 유기 절 연물 또는 무기 절연물로 만들어진다. 격벽(361)은 또한 검정색 안료를 포함하는 감광재로 만들어질 수

있는데, 이 경우 격벽(361)은 차광 부재의 역할을 하며 그 형성 공정이 간단하다.

- [0073] 격벽(361)이 정의하는 화소 전극(191) 위의 개구부(365)에는 유기 발광 부재(organic light emitting member)(370)가 형성되어 있다. 유기 발광 부재(370)는 적색, 녹색, 청색의 삼원색 등 기본색(primary color) 중 어느 하나 또는 하나 이상의 빛을 고유하게 내는 유기 물질로 만들어진다. 유기 발광 표시 장치는 유기 발광 부재(370)들이 내는 기본색 색광의 공간적인 합으로 원하는 영상을 표시한다.

- [0074] 유기 발광 부재(370) 위에는 공통 전극(common electrode)(270)이 형성되어 있다. 공통 전극(270)은 기판의 전면(全面)에 형성되어 있으며, 화소 전극(191)과 쌍을 이루어 유기 발광 부재(370)에 전류를 흘려 보낸다.

- [0075] 이러한 박막 트랜지스터 표시판의 표시 영역(DA)에서, 스위칭/구동 제어 전극(124a/124b), 스위칭/구동 입력 전극(173a/173b) 및 스위칭/구동 출력 전극(175a/175b)은 스위칭/구동 반도체(154a/154b)와 함께 스위칭/구동 트랜지스터(Qs/Qd)를 이루며, 스위칭/구동 트랜지스터(Qs/Qd)의 채널(channel)은 스위칭/구동 입력 전극(173a/173b)과 스위칭/구동 출력 전극(175a/175b) 사이의 스위칭/구동 반도체(154a/154b)에 형성된다.

- [0076] 또한 박막 트랜지스터 표시판의 주변 영역(PA)에서는 상/하부 방전 제어 전극(1124a/1124b), 상/하부 방전 입력 전극(1173a/1173b) 및 상/하부 방전 출력 전극(1175a/1175b)은 방전 반도체(1151)의 상/하부 돌출부 (1154a/1154b)와 함께 상/하부 방전 트랜지스터(Ta/Tb)를 이루며, 상/하부 방전 트랜지스터(Ta/Tb)의 채널 (channel)은 상/하부 방전 입력 전극(1173a/1173b)과 상/하부 방전 출력 전극(1175a/1175b) 사이의 상/하부 방 전 반도체(1154a/1154b)에 형성된다.

- [0077] 이와 같이, 본 발명의 실시예에 따르면 방전 트랜지스터(Ta, Tb)의 방전 제어 전극(1124 a, 1124b)과 방전 반도체(1154a, 1154b) 사이에 하부 및 상부 게이트 절연막(140, 142)의 이중의 절연막이 형성되어 있으므로 단일의절연막이 있는 경우에 비해 방전 트랜지스터(Ta, Tb)를 턴 온시킬 수 있는 문턱 전압이 높아진다. 따라서 주사신호선(121)에 인가되는 게이트 온 전압에 의한 누설 전류를 막아 게이트 온 전압의 손실을 방지할 수 있다.

- [0078] 또한, 스위칭 반도체(154a) 및 방전 반도체(1151)는 비정질 반도체로 만들고 구동 반도체(154b)는 결정질 반도체로 만들면 구동 트랜지스터의 채널은 결정질 반도체에 형성함으로써 높은 전하 이동도(carrier mobility) 및 안정성(stability)을 가질 수 있고 스위칭 트랜지스터의 채널은 오프 전류가 작은 비정질 반도체에 형성함으로써 데이터 전압의 감소 및 크로스 토크를 방지할 수 있다.

- [0079] 화소 전극(191), 유기 발광 부재(370) 및 공통 전극(270)은 유기 발광 다이오드(LD)를 이루며, 화소 전극(191) 이 애노드(anode), 공통 전극(270)이 캐소드(cathode)가 되거나 반대로 화소 전극(191)이 캐소드, 공통 전극(270)이 애노드가 된다. 또한 서로 중첩하는 유지 전극(127)과 구동 전압선(172)은 유지 축전기(storage capacitor)(Cst)를 이룬다.

- [0080] 그러면 도 2 내지 도 4에 도시한 박막 트랜지스터 표시판을 제조하는 방법에 대하여 도 5 내지 도 13을 참조하여 상세하게 설명한다.

- [0081] 도 5 내지 도 13은 도 2 내지 도 4의 표시 장치용 박막 트랜지스터 표시판을 본 발명의 한 실시예에 따라 제조 하는 방법을 차례로 도시한 배치도이다.

- [0082] 도 5에 도시한 바와 같이, 사진 식각 공정으로 기판(110) 위에 유지 전극(127)을 포함하는 복수의 구동 제어 전극(124b), 한 쌍의 상부 방전 제어 전극(1124a)을 포함하는 복수의 방전 주사 신호선(1121), 그리고 복수 쌍의 하부 방전 제어 전극(1124b)을 포함하는 복수의 게이트 도전체를 형성한다.

- [0083] 다음, 도 6에 도시한 바와 같이, 게이트 도전체(124b, 1121, 1124b) 위에 하부 게이트 절연막(140)을 형성하고, 도 7에 도시한 바와 같이 하부 게이트 절연막(140) 위에 결정질 규소층 및 불순물 비정질 규소층을 연속하여 적 층한 후 사진 식각하여 구동 반도체(154b) 및 저항성 접촉층(164b)을 형성한다.

- [0084] 또는, 구동 제어 전극(124b) 위에 하부 게이트 절연막(140), 비정질 규소층 및 불순물 비정질 규소층을 연속하여 적층한 후 결정화할 수 있다. 이 때 결정화는 고상 결정화(solid phase crystallization, SPC), 급속 열처리(rapid thermal annealing, RTA), 액상 결정화(liquid phase recrystallization, LPR), 엑시머 레이저 열처리(excimer laser annealing, ELA) 등의 방법으로 수행할 수 있으며, 이 중에서 고상 결정화 방법이바람직하다.

- [0085] 다음, 도 8에 도시한 바와 같이, 하부 게이트 절연막(140) 및 저항성 접촉충(164b) 위에 금속충을 적충하고 사진 식각하여 스위칭 제어 전극(124a)을 포함하는 복수의 주사 신호선(121), 구동 입력 전극(173b)을 포함하는

복수의 구동 전압선(172) 및 복수의 구동 출력 전극(175b)을 포함하는 제1 데이터 도전체를 형성한다.

- [0086] 이어서, 구동 전압선(172) 및 구동 출력 전극(175b)을 마스크로 하여 저항성 접촉층(164b)을 식각하여 한 쌍의 저항성 접촉 부재(163b, 165b)를 형성한다.

- [0087] 다음, 도 9에 도시한 바와 같이, 제1 데이터 도전체(121, 172, 175b) 위에 상부 게이트 절연막(142), 진성 비정 질 규소층 및 불순물 비정질 규소층을 연속하여 적층한 후 사진 식각하여 스위칭 반도체(154a), 돌출부(1154a, 1154b)를 포함하는 선형 방전 반도체(1151), 저항성 접촉층(164a) 및 저항성 접촉층(1164a)을 형성한다.

- [0088] 다음, 도 10에 도시한 바와 같이, 상부 게이트 절연막(142) 및 저항성 접촉층(164a, 1164a) 위에 금속층을 적층하고 사진 식각하여 스위칭 입력 전극(173a)을 포함하는 복수의 데이터선(171), 복수의 스위칭 출력 전극(175a), 상부 및 하부 방전 입력 전극(1173a, 1173b)을 포함하는 세로 단락선(1171) 및 복수의 상부 및 하부 방전 출력 전극(1175a, 1175b)을 포함하는 제2 데이터 도전체를 형성한다.

- [0089] 이어서, 데이터선(171), 스위칭 출력 전극(175a), 세로 단락선(1171), 그리고 상부 및 하부 방전 출력 전극 (1175a, 1175b)을 마스크로 하여 저항성 접촉층(164a, 1164a)을 식각하여 복수 쌍의 저항성 접촉 부재(163a, 165a), 돌출부(1163a)를 포함하는 저항성 접촉 부재(1161) 및 복수의 저항성 접촉 부재(1165a)를 형성한다.

- [0090] 다음, 도 11에 도시한 바와 같이, 기판 전면에 보호막(180)을 적충하고 사진 식각하여 복수의 접촉 구멍(184, 185a, 185b, 186, 1183, 1185, 1186, 1187, 1189)을 형성한다.

- [0091] 다음, 도 12에 도시한 바와 같이, 보호막(180) 위에 ITO를 증착한 후 사진 식각하여 복수의 화소 전극(191) 및 연결 부재(85, 86, 850, 870)를 형성한다.

- [0092] 다음, 도 13 및 도 2 내지 도 4에 도시한 바와 같이, 화소 전극(191)과 연결 부재(85, 86, 850, 870) 및 보호 막(180) 위에 감광성 유기막을 도포한 후 노광 및 현상하여 복수의 개구부(365)를 가지는 격벽(361)을 형성한다.

- [0093] 이어서, 개구부(365)에 발광 부재(370)를 형성한다. 발광 부재(370)는 잉크젯 인쇄(inkjet printing) 방법 등 의 용액 방법(solution process) 또는 증착(deposition)으로 형성할 수 있다.

- [0094] 마지막으로, 도 2 내지 도 4에 도시한 바와 같이 격벽(361) 및 발광 부재(370) 위에 공통 전극(270)을 형성한다.

- [0095] 도 2 내지 도 13에 도시한 실시예에서는 도 1의 제1 정전기 방전 방지 회로(Eg)를 예로 하여 설명하였지만, 제2 정전기 방전 방지 회로(Ed)의 제2 상부 및 하부 방전 트랜지스터(Tc, Td)와 제3 방전 트랜지스터(Te)의 경우도 제1 정전기 방전 방지 회로(Eg)의 방전 트랜지스터(Ta, Tb)와 같이 구성할 수 있다. 즉, 구동 트랜지스터(Qd)의 구동 제어 전극(124b)과 같은 층에 방전 트랜지스터(Tc, Td, Te)의 방전 제어 전극을 형성하고, 스위칭 트랜지스터(Qs)의 스위칭 반도체(154a)와 같은 층에 방전 반도체를 형성하여 상부 및 하부 게이트 절연막을 방전 제어 전극과 방전 반도체 사이에 둘 수 있다. 이렇게 함으로써 방전 트랜지스터(Tc, Td, Te)의 문턱 전압을 높일수 있고, 데이터선(171)으로부터 방전 트랜지스터(Tc, Td, Te)를 통해 흐르는 누설 전류를 막아 데이터 전압의 손실을 방지할 수 있다.

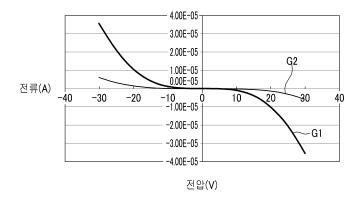

- [0096] 도 14는 본 발명의 한 실시예에 따른 표시 장치용 박막 트랜지스터 표시판의 정전기 방전 방지 회로의 전압-전 류 특성을 나타낸 그래프이다.

- [0097] 도 14를 참고하면, G1은 방전 트랜지스터(Ta-Te)의 절연막이 한 층인 경우의 전압-전류 특성이고, G2는 방전 트랜지스터(Ta-Te)의 절연막이 두 층인 경우의 전압-전류 특성이다. 방전 트랜지스터(Ta-Te)의 방전 제어 전극과 방전 반도체 사이에 절연막이 한 층인 경우(G1), 정전기 전압이 10V 이상이면 방전 트랜지스터(Ta-Te)에서 누설 전류가 생기지만, 본 발명의 실시예와 같이 두 층의 절연막을 포함할 경우(G2) 누설 전류가 생기는 문턱 전압이 20V로 높아져 데이터 전압 또는 게이트 온 전압의 손실을 방지할 수 있다.

- [0098] 이상에서 본 발명의 바람직한 실시예에 대하여 상세하게 설명하였지만 본 발명의 권리범위는 이에 한정되는 것은 아니고 다음의 청구범위에서 정의하고 있는 본 발명의 기본 개념을 이용한 당업자의 여러 변형 및 개량 형태 또한 본 발명의 권리범위에 속하는 것이다.

#### 도면의 간단한 설명

[0099] 도 1은 본 발명의 한 실시예에 따른 표시 장치용 박막 트랜지스터 표시판의 등가 회로도이고,

| [0100] | 도 2는 본 발명의 | l 청 시치세세 r | 때로 교기 자기요 | 바마 트레키스디 | 교기 파이 의 | 청소세 미청 베ㅋ   | 1 にんコ |

|--------|------------|------------|-----------|----------|---------|-------------|-------|

| 10100  | 도 2는 돈 말썽의 | l 안 걸시때에 i | 따른 표시 장시품 | 막막 느댄시스다 | 품시판의 안  | ' 와오에 내안 매스 | 네노이끄. |

| [0101] | 도 3은 본 발명의 한 실시예에 따른 표시 장치용 박막 트랜지스터 표시판의 정전기 방전 방지 회로의 배치도이 |

|--------|--------------------------------------------------------------|

|        | 7                                                            |

[0102] 도 4는 도 2의 박막 트랜지스터 표시판을 IV-IV' 선, IV'-IV'' 선 및 IV'''-IV''' 선을 따라 자르고 도 3의 정전기 방전 방지 회로를 IV''-IV'''선을 따라 잘라 함께 도시한 단면도이고,

[0103] 도 5 내지 도 13은 도 2 내지 도 4의 표시 장치용 박막 트랜지스터 표시판을 본 발명의 한 실시예에 따라 제조하는 방법을 차례로 도시한 배치도이고,

[0104] 도 14는 본 발명의 한 실시예에 따른 표시 장치용 박막 트랜지스터 표시판의 정전기 방전 방지 회로의 전압-전 류 특성을 나타낸 그래프이다.

<도면의 주요 부분에 대한 부호의 설명>

110: 절연 기판 121: 주사 신호선

[0107] 124a: 스위칭 제어 전극 124b: 구동 제어 전극

[0108] 127: 유지 전극 140: 게이트 절연막

[0109] 154a, 154b: 반도체 171: 데이터선

[0110] 172: 구동 전압선 85: 연결 부재

[0111] 173a: 스위칭 입력 전극 173b: 구동 입력 전극

[0112] 175a: 스위칭 출력 전극 175b: 구동 출력 전극

[0113] 191: 화소 전극 184, 185a, 185b: 접촉 구멍

270: 공통 전극 361: 격벽

370: 유기 발광 부재 850, 870: 방전 연결 부재

[0116] 1121: 방전 주사 신호선 1124a, 1124b: 방전 제어 전극

[0117] 1171: 세로 단락선

[0105]

[0106]

[0114]

[0115]

[0118]

1183, 1185, 1186, 1187, 1189: 접촉 구멍

[0119] Qs: 스위칭 트랜지스터 Qd: 구동 트랜지스터

[0120] LD: 유기 발광 소자

# *도면5*

## 도면8

## 도면9

## 도면12