## (19) **日本国特許庁(JP)**

# (12)公表特許公報(A)

(11)特許出願公表番号

特表2007-527091 (P2007-527091A)

(43) 公表日 平成19年9月20日(2007.9.20)

テーマコード (参考) FI(51) Int.C1.

G 1 1 C 29/50 (2006, 01) G 1 1 C 29/00 671M5L106 G 1 1 C 11/401 (2006.01) G 1 1 C 11/34 371A5MO24

#### 審查請求 未請求 予備審查請求 未請求 (全 15 百)

(21) 出願番号 特願2007-501438 (P2007-501438) (86) (22) 出願日 平成17年3月3日(2005.3.3) (85) 翻訳文提出日 平成18年7月27日 (2006.7.27) (86) 国際出願番号 PCT/1B2005/050800 (87) 国際公開番号 W02005/088644 (87) 国際公開日 平成17年9月22日 (2005.9.22) (31) 優先権主張番号 60/550, 416

(32) 優先日 平成16年3月5日(2004.3.5)

(33) 優先権主張国 米国(US) (31) 優先権主張番号 60/590, 402

(32) 優先日 平成16年7月21日 (2004.7.21)

(33) 優先権主張国 米国(US) (71) 出願人 590000248

コーニンクレッカ フィリップス エレク

トロニクス エヌ ヴィ

オランダ国 5621 ベーアー アイン ドーフェン フルーネヴァウツウェッハ

(74) 代理人 100087789

弁理士 津軽 進

(74)代理人 100114753

弁理士 宮崎 昭彦

(74)代理人 100122769

弁理士 笛田 秀仙

最終頁に続く

#### (54) 【発明の名称】遅延障害を検出するためのセルフタイミング型メモリを強化するDFT技術

## (57)【要約】

本発明は、クロックモニタ(152)とセルフタイミ ング型メモリの内部メモリブロック(125)との間に 挿入されるテストシステム(100)に関する。例示の 実施例において、テストシステム(100)は、クロッ クモニタ(152)からの内部クロック信号(104) と、外部クロック信号(CL)と、制御信号(CS)と を受信する。テストシステムのマルチプレクサ(110 )は、制御信号(CS)に応じて、セルフタイミング型 メモリの動作のノーマルモードにおいて内部メモリブロ ック(125)に内部クロック信号(104)を供給し 、セルフタイミング型メモリのテストモード(108) において外部クロック信号(CL)を内部メモリブロッ ク(125)に供給する。テストシステム(100)は 、テストモードにおいて外部クロック信号(CL)を直 接供給することにより、内部メモリブロック(125) のクロックサイクルの制御を可能とする。したがって、 内部メモリブロックは、小さな遅延障害の検出を可能と するよう適正に強化される。

#### 【特許請求の範囲】

### 【請求項1】

外部クロック信号をセルフタイミング型メモリの内部メモリブロックに供給する方法であって、前記セルフタイミング型メモリのクロックモニタから内部クロック信号を受信すること、外部クロック信号を受信すること、制御信号を受信すること、及び前記制御信号に応じて前記セルフタイミング型メモリの動作のノーマルモードにおいて前記内部クロック信号を前記内部メモリブロックに前記セルフタイミング型メモリのテストモードにおいて前記外部クロック信号を前記内部メモリブロックに供給することを含む方法。

#### 【請求項2】

請求項1に記載の外部クロック信号をセルフタイミング型メモリの内部メモリブロックに供給する方法であって、前記テストモードにおいて受信される前記外部クロック信号は、所定のテストパターンに応じて発生される、方法。

#### 【請求項3】

請求項2に記載の外部クロック信号をセルフタイミング型メモリの内部メモリブロックに供給する方法であって、前記テストモードにおいて受信される前記外部クロック信号は、前記内部メモリブロックの50%デューティサイクルよりも小さなデューティサイクルを有する、方法。

#### 【請求項4】

請求項2に記載の外部クロック信号をセルフタイミング型メモリの内部メモリブロックに供給する方法であって、前記テストモードにおいて受信される前記外部クロック信号は、前記内部メモリブロックの50%デューティサイクルよりも大きなデューティサイクルを有する、方法。

### 【請求項5】

請求項1に記載の外部クロック信号をセルフタイミング型メモリの内部メモリブロックに供給する方法であって、前記内部クロック信号は、制御信号のないときに前記内部メモリブロックに供給される、方法。

### 【請求項6】

請求項1に記載の外部クロック信号をセルフタイミング型メモリの内部メモリブロックに供給する方法であって、前記テストモードの開始を示す制御信号が供給される、方法。

#### 【請求項7】

請求項 6 に記載の外部クロック信号をセルフタイミング型メモリの内部メモリブロックに供給する方法であって、前記テストモードの終了を示す制御信号が供給される、方法。

### 【請求項8】

請求項7に記載の外部クロック信号をセルフタイミング型メモリの内部メモリブロックに供給する方法であって、前記テストモードにおいて少なくとも1つの制御信号が供給される、方法。

#### 【請求項9】

内部メモリブロックと、

外部クロック信号を受信しこれに基づいて内部クロック信号を前記内部メモリブロック に供給するクロックモニタと、

前記クロックモニタと前記内部メモリブロックとの間に介在するテストシステムと、 を有するセルフタイミング型メモリであって、

前記テストシステムは、前記内部クロック信号を受信するために前記クロックモニタとの信号伝送をなす内部クロック信号入力ポートと、前記外部クロック信号を受信するための外部クロック信号入力ポートと、制御信号を受信するための制御信号入力ポートと、前記内部メモリブロックとの信号伝送のための出力ポートと、前記内部クロック信号入力ポート、前記制御信号入力ポート及び前記出力ポートとの信号伝送のためのマルチプレクサとを有し、

当該制御回路は、前記内部クロック信号、前記外部クロック信号及び前記制御信号を受信し、前記制御信号に基づいて前記セルフタイミング型メモリの動作のノーマルモードに

10

20

30

40

おいて前記出力ポートを介して前記内部クロック信号を前記内部メモリブロックに供給し 前記セルフタイミング型メモリのテストモードにおいて前記外部クロック信号を前記内部 メモリブロックに供給する、

メモリ。

### 【請求項10】

請求項9に記載のセルフタイミング型メモリであって、前記クロックモニタは、前記外部クロック信号を受信する入力ポートを有し、前記入力ポートは、前記テストシステムの前記外部クロック信号入力ポートに接続される、メモリ。

#### 【請求項11】

請求項10に記載のセルフタイミング型メモリであって、前記テストシステムとの信号伝送のためのテスト回路を有し、前記テスト回路は、前記テストシステムに制御信号を供給し、テストモードにおいて前記テストシステムに前記外部クロック信号を供給する、メモリ。

### 【請求項12】

請求項9に記載のセルフタイミング型メモリであって、前記内部メモリブロックは、アドレスデコーダを有する、メモリ。

### 【請求項13】

請求項9に記載のセルフタイミング型メモリであって、前記内部メモリブロックは、センス増幅器を有する、メモリ。

#### 【請求項14】

請求項9に記載のセルフタイミング型メモリであって、前記内部メモリブロックは、カラム及びバンクデコーダを有する、メモリ。

#### 【請求項15】

請求項9に記載のセルフタイミング型メモリであって、前記内部メモリブロックは、プリチャージ及びディスチャージ回路を有する、メモリ。

#### 【請求項16】

請求項9に記載のセルフタイミング型メモリであって、前記内部メモリブロックは、入力/出力ラッチを有する、メモリ。

### 【請求項17】

少なくとも1つの内部メモリブロックと、

外部クロック信号を受信しこれに基づいて内部クロック信号を前記少なくとも1つの内部メモリブロックに供給するクロックモニタと、

前記クロックモニタと前記少なくとも 1 つの内部メモリブロックとの間に介在するテストシステムと、

を有するセルフタイミング型メモリであって、

前記テストシステムは、少なくとも1つの内部クロック信号を受信するために前記クロックモニタとの信号伝送をなすための少なくとも1つの内部クロック信号入力ポートと、前記外部クロック信号を受信するための外部クロック信号入力ポートと、制御信号を受信するための制御信号入力ポートと、少なくとも1つの内部メモリブロックとの信号伝送のための少なくとも1つの出力ポートと、前記少なくとも1つの内部クロック信号入力ポート、前記外部クロック信号入力ポート、前記制御信号入力ポート及び前記少なくとも1つの出力ポートとの信号伝送のための制御回路とを有し、

前記制御回路は、前記少なくとも1つの内部クロック信号、前記外部クロック信号及び前記制御信号を受信し、前記制御信号に基づいて前記セルフタイミング型メモリの動作のノーマルモードにおいて前記少なくとも1つの出力ポートを介して前記少なくとも1つの内部クロック信号を前記少なくとも1つの内部メモリブロックに供給し前記セルフタイミング型メモリのテストモードにおいて前記外部クロック信号を前記少なくとも1つの内部メモリブロックのうちの少なくとも1つに供給する、メモリ。

### 【請求項18】

50

30

10

20

20

30

40

50

請求項17に記載のセルフタイミング型メモリであって、前記制御回路は、マルチプレクサを有する、メモリ。

#### 【請求項19】

請求項18に記載のセルフタイミング型メモリであって、前記少なくとも1つの内部メモリブロックは、アドレスデコーダを有する、メモリ。

#### 【請求項20】

請求項19に記載のセルフタイミング型メモリであって、前記少なくとも1つの内部メモリブロックは、センス増幅器を有する、メモリ。

### 【請求項21】

請求項20に記載のセルフタイミング型メモリであって、前記少なくとも1つの内部メモリブロックは、カラム及びバンクデコーダを有する、メモリ。

#### 【請求項22】

請求項21に記載のセルフタイミング型メモリであって、前記少なくとも1つの内部メモリブロックは、プリチャージ及びディスチャージ回路を有する、メモリ。

### 【請求項23】

請求項22に記載のセルフタイミング型メモリであって、前記少なくとも1つの内部メモリブロックは、入力/出力ラッチを有する、メモリ。

#### 【請求項24】

請求項23に記載のセルフタイミング型メモリであって、前記テストシステムとの信号 伝送のためのテスト回路を有し、このテスト回路は、制御信号を前記テストシステムに供 給し、テストモードにおいて前記テストシステムに前記外部クロック信号を供給する、メ モリ。

### 【発明の詳細な説明】

### 【技術分野】

#### [0001]

この出願は、2004年3月5日に出願の"DFT Technique for Stressing Self-Timed Semiconductor Memories to Detect Delay Faults"と題された仮出願(通し番号60/550,416)の優先権を主張するものであり、その全部が参照により編入される。

### [0002]

本発明は、半導体メモリのテストの分野に関し、特に、半導体メモリの遅延障害を検出するためのテスト(DFT)方法のデザインに関する。

### 【背景技術】

#### [0003]

集積回路の体系化され自動化されたテストは、益々重要になっている。集積回路の新しい出現の度に、構成要素密度、システム機能の数及びクロック速度が相当に大きくなっている。集積回路は、最も精緻で高価な従来のテスト方法を用いても処理欠陥がもはや検出できないような複雑さ及び速度に達している。しかしながら、需要者は、実際の使用においてそれらの隠れた欠陥が現われこれにより例えば生命維持システム又は航空機制御システムが信頼性のないものとなるような製品を受け付けるものではない。

#### [0004]

セルフタイミング型の半導体メモリは、当業界においてはよく知られており、高速用途に用いられるのが好ましい。このセルフタイミング型のメモリにおける読出及び書込サイクルは、クロック信号の正又は負のエッジにより起動される。このメモリサイクルは、その完了まで、当該クロックエッジとは無関係に継続する。50%から外れるデューティサイクルの供給は、遅延障害の検出に影響を及ぼす。50%を下回るデューティサイクルは、メモリアドレスデコーダにおいて緩慢な立ち上がりの作用を生じる遅延障害の検出を可能とする。50%を超えるデューティサイクルは、メモリアドレスデコーダにおいて緩慢な立ち上がりの作用を生じる遅延障害の検出を可能とする。さらに、クロックデューティサイクルは、センス増幅器、ビットライン、プリチャージ回路及びディスチャージ回路を強化し、十分に遅延障害検出を向上させる。この分野では、適正なテストパターンが実現され

たときに「急速な」テストが遅延障害を強化することが知られている。しかしながら、高周波数のビルトインセルフテスト(BIST)の実施には、BISTのための領域をかなり増大させ、多くの用途において許容されない。但し、外部クロックのデューティサイクルを変えることは、セルフタイミング型の半導体メモリの遅延障害の検出に影響を与えない。何故なら、外部クロックの正又は負のエッジは、当該クロックサイクルの端部を制御しないからである。セルフタイミング型メモリにおいては、ダミーブロックに応じて読取/書込動作の終了が内部的に定められる。したがって、緩慢な立ち上がり及び緩慢な立下りの遅延を検出するためにメモリテストを難しいタスクにする外部クロックのデューティサイクルを増大又は減少させることにより、高感度化動作を制御することはできない。

【発明の開示】

【発明が解決しようとする課題】

[0005]

セルフタイミング型の半導体メモリにおいて緩慢な立ち上がり及び緩慢な立下り遅延を 検出するための高速テストの欠点を克服する方策を提供する必要性がある。

【課題を解決するための手段】

[0006]

本発明は、高速テスト以外のセルフタイミング型の半導体メモリにおける緩慢立ち上がり及び緩慢立下り遅延を検出するのに有益であることが判明した。本発明は、デューティサイクルが緩慢立ち上がり及び緩慢立下り遅延を検出するためのパラメータになるようなセルフタイミング型半導体メモリの内部ブロックの制御性を向上させる技術を提供するものである。

[0007]

本発明による一実施例によれば、外部クロック信号をセルフタイミング型メモリの内部メモリブロックに供給する方法が提供される。本方法は、前記セルフタイミング型メモリのクロックモニタから内部クロック信号を受信すること、外部クロック信号を受信すること、及び制御信号を受信することを含む。前記制御信号に応じて、前記セルフタイミング型メモリの動作のノーマルモードにおいて前記内部クロック信号を前記内部メモリブロックに、前記セルフタイミング型メモリのテストモードにおいて前記外部クロック信号を前記内部メモリブロックに供給する。

[00008]

本発明による他の実施例では、内部メモリブロックを有するセルフタイミング型メモリが設けられる。外部クロック信号を受信し、これに基づいて内部クロック信号を内部メモリブロックに供給するクロックモニタが設けられる。クロックモニタと内部メモリブロックに供給するクロックモニタが設けられる。クロックモニタと内部メモリブロック信号入力ポートと、前記外部クロック信号入力ポートと、制御信号を受信するための制御信号入力ポートと、前記内部メモリブロック信号入力ポート、前記制御信号入力ポート及び前記出力ポートとの信号伝送のためのマルチプレクサとを有し、御信号入力ポート及び前記出力ポートとの信号伝送のためのマルチプレクサとを有し、

[0009]

当該制御回路は、前記内部クロック信号、前記外部クロック信号及び前記制御信号を受信し、前記制御信号に基づいて前記セルフタイミング型メモリの動作のノーマルモードにおいて前記出力ポートを介して前記内部クロック信号を前記内部メモリブロック信号を前記内部メモリブロックに供給し、カードにおいて前記外部クロック信号を前記内部メモリブロックに供給する。

[0010]

本発明による他の実施例によれば、少なくとも1つの内部メモリブロックと、外部クロック信号を受信しこれに基づいて内部クロック信号を前記少なくとも1つの内部メモリブロックに供給するクロックモニタと、前記クロックモニタと前記少なくとも1つの内部メモリブロックとの間に介在するテストシステムと、を有するセルフタイミング型メモリが

10

20

30

40

20

30

40

50

[0011]

本発明の上記要約は、本発明の開示される各実施例又は全ての態様を表すことを意図したものではない。他の態様及び例示の実施例は、図面及び以下の詳細な説明において提供される。

[0012]

本発明は、添付図面に関連して本発明の様々な実施例の次の詳細な説明を考慮してより深く理解することができるものである。

【発明を実施するための最良の形態】

[ 0 0 1 3 ]

本発明は、様々な変更や代替形態に適用できるが、その特定のものは、図面に例示として示されており、以下に詳細に説明する。但し、その意図は、本発明を説明した特定の実施例に限定するものではないことを理解されたい。これとは対照的に、添付の請求項によって規定されるような本発明の主旨及び範囲内にある全ての変更例、等価概念及び代替例をカバーする意図である。

[0014]

セルフタイミング型半導体メモリにおいては、セルフタイミング動作によりデューティサイクル作用が消失する。読取 / 書込動作の終了は、内部で定められる。したがって、メモリテストを緩慢立ち上がり及び緩慢立下り遅延の検出のために困難なタスクとするセルフタイミング機能メモリの内部メモリブロックにおける動作の始まり又は終わりを制御することは不可能である。

[0015]

セルフタイミング型メモリのこの欠点は、本発明によるセルフタイミング型メモリをテストするためのテストシステムを組み入れることにより克服される。このテストシステムは、デューティサイクルが緩慢立ち上がり及び緩慢立下り遅延を検出するためのパラメータとなるように内部メモリブロックの制御を可能とするデザイン・フォア・テスト(DFT;Design For Test)技術に基づいている。本発明によるテストシステムを用いてセルフタイミング型メモリの内部機能の始まりと終わりの外部制御を可能とすることにより、遅延障害を検出するために当該デューティサイクルを増大又は減少させることが可能となる。好ましくは、このテストシステムは、遅延障害の検出にかなりのインパクトを呈する内部メモリブロックのデューティサイクルを変更するために実現される。例えば、アドレスデコーダを制御することによって、脆弱な抵抗性開口欠陥によるメモリのワードラインにおける小さな遅延障害を検出することができる。

[0016]

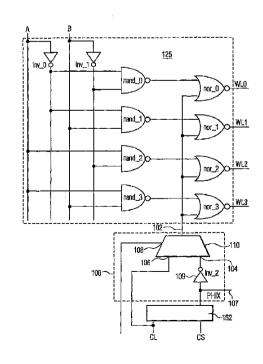

図1を参照すると、内部クロック信号 P H I X により制御される 2 - 4 アドレスデコーダ 1 2 5 が示される。アドレスデコーダ 1 5 0 の制御ロジックたるクロックモニタ 1 5 2 は、外部クロック信号 C L の正又は負のエッジに基づいて始動させられる。そして制御ロジック 1 5 2 は、内部クロック信号 P H I X を発生する。ワードラインのアクティブ化及

び非アクティブ化は、内部クロック信号PHIXの正又は負のエッジに基づいて制御される。したがって、当該ワードラインのアクティブ化及び非アクティブ化は、外部クロック信号CLに応じたものとなる。これにより、緩慢立ち上がり及び緩慢立下り遅延障害の検出は、内部クロック信号PHIXのデューティサイクルに依存し、外部クロック信号CLには依存しないものとなる。チップセレクトCSは、メモリの動作をアクティブにする信号である。一例のメモリでは、CSが論理「1」であるとき、読出又は書込動作のためにメモリがアクティブとされる。他の例のメモリでは、CSが論理「0」であるとき、読出又は書込動作のためにメモリがアクティブとされる。したがって、メモリのデザインに応じて、inv\_2(109)をバッファと置き換えることができる。

#### [0017]

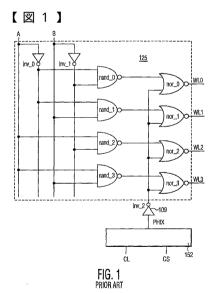

図2を参照すると、2-4アドレスデコーダ125に接続される本発明によるテストシ ステム100が示される。テストシステム100は、クロックモニタ152からの内部ク ロック信号PHIXと外部クロック信号CLとをそれぞれ受信するクロック信号入力ポー ト 1 0 4 及び 1 0 6 を含む。制御入力ポート 1 0 8 で受信された制御信号に応じて、マル チプレクサ 1 1 0 は、出力ポート 1 0 2 を介して内部クロック信号 1 0 7 ( P H I X ) 又 は 外 部 ク ロ ッ ク 信 号 C L を ア ド レ ス デ コ ー ダ 1 2 5 に 供 給 す る 。 受 信 し た 制 御 信 号 に 応 じ て、マルチプレクサ110は、ノーマルモードでは内部クロック信号PHIXをアドレス デコーダ125に、或いはテストモードでは外部クロック信号CLを供給する。クロック モニタ152とアドレスデコーダ125との間にテストシステム100を挿入することに よって、テストモードにおいて外部クロック信号CLをアドレスデコーダ125に直接供 給 することにより、アドレスデコーダ125のクロックサイクルの制御が可能となる。し た が っ て 、 ワ ー ド ラ イ ン の ア ク テ ィ ブ 化 及 び 非 ア ク テ ィ ブ 化 の 開 始 及 び 終 了 は 、 遅 延 障 害 の検出を可能とする外部クロック信号CLにより簡単に制御される。ここで分かるように 当該テストシステムは、センス増幅器、列(カラム)及びバンクデコーダ、プリチャー ジ 及 び デ ィ ス チ ャ ー ジ 回 路 、 並 び に 入 力 / 出 力 ラ ッ チ な ど の 内 部 メ モ リ ク ロ ッ ク に よ り 制 御される複数の内部メモリブロックをカバーするよう簡単に拡張される。

### [ 0 0 1 8 ]

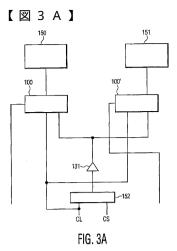

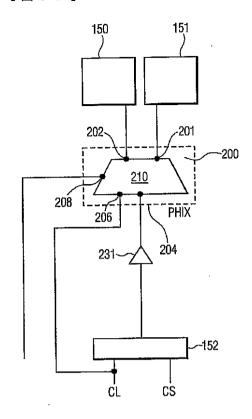

図3 A ないし図3 C を参照すると、本発明によるテストシステムの3 つの実施例は、2 つの内部メモリブロック150及び151にそれぞれ結合される形で示される。単に簡単に示すため、図3 A ないし図3 C における描写は、2 つの内部メモリブロックに限定している。これから分かるように、実施例は、2 つを超える数の内部メモリブロックに拡張することができる。

#### [0019]

図3 A に示される実現形態では、2 つのテストシステム100,100 ′がクロックモニタ152 と内部メモリブロック150及び151の各々との間に挿入される。すなわち、1 つのテストシステムは、1 つの内部メモリブロック150及び151をそれぞれ制御するために用いられる。バッファ131は、クロックモニタ152をテストシステム100,100 ′の入力に結合する。

### [0020]

或いは、図3Bに示されるように、2つの出力ポート201及び202をそれぞれ有する1つのテストシステム200は、クロックモニタ152と内部メモリブロック150及び151の各々との間に挿入される。制御入力ポート208で受信された制御信号に応じて、マルチプレクサ210は、出力ポート201及び202を介して、入力ポート204で受信した内部クロック信号PHIXを、或いは入力ポート206で受信した外部クロック信号CLを、内部メモリブロック150及び151にそれぞれ供給する。この受信した制御信号に応じて、テストシステム200は、ノーマルモードにおいては内部クロック信号PHIXを内部メモリブロック150及び151に、或いはテストモードにおいては外部クロック信号CLを供給する。バッファ231は、クロックモニタ152の1つの出力をテストシステム200の入力に結合する。

### [0021]

50

10

20

30

10

20

30

40

50

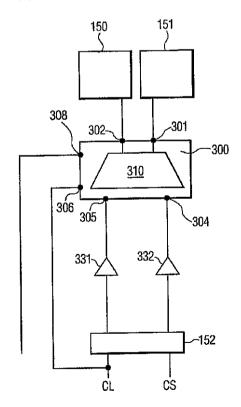

図3 C に示される例示の実施例では、テストシステム300は、入力ポート304及び305を介して内部メモリブロック150及び151それぞれのための2つの内部クロック信号を受信する。制御入力ポート308で受信した制御信号に応じて、マルチプレクサ310は、出力ポート301及び302を介して、入力ポート304及び305で受信した内部クロック信号を、或いは、入力ポート306で受信した外部クロック信号 C L を、内部メモリブロック150及び151にそれぞれ供給する。バッファ331,332は、クロックモニタ152の出力をテストシステム300の入力304,305と結合する。

[0022]

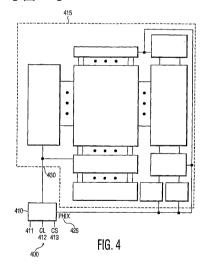

図 4 を参照する。本発明の実施例によるテストシステム 4 1 0 は、セルフタイミング型メモリ 4 1 5 に結合される。テストシステム 4 1 0 は、アドレスデコーダのためのクロック 4 3 0 とメモリ 4 1 5 の他のブロックを制御するための内部クロック 4 2 5 ( P H I X ) とを発生する。テストシステム 4 1 0 は、テストモード入力 4 1 1、外部クロック信号入力 4 1 2 及びチップセレクト 4 1 3 を有する。

[0023]

他の例示の実施例においては、制御信号入力ポート及び外部クロック信号入力ポートがメモリのものと同じチップ上に実現されるテスト回路に接続される。このテストードを開始されるを力がある。のからは、テストモードを開始されるの動作のモードを制御する。例えば、テストモードやにおいて、テストモードや中において、テストモードを終了させるための制御信号を供給する。1つの例示実施例では、テストモード中においたがは、制御信号が何ら受信されないときにノーマルモードで動作する。テストモード中の制御信号の供給により、例えば、所定のテストパターンに応じて異なる内部メモリブロックに外部クロック信号の供給を切り換えることにより1つのテストシステムを用いて複数の内部メモリブロックのテストが可能となる。テスト回路は、例えば内部メモリブロックのテストが可能となる。テスト回路は、例えば内部メモリブロックののまりのがデューティサイクルよりも小さいか又は大きなデューティサイクルを有する、遅延障害検出用の所定テストパターンに応じた外部クロック信号を発生し、それをテストモード中にテストシステムに供給する。

[ 0 0 2 4 ]

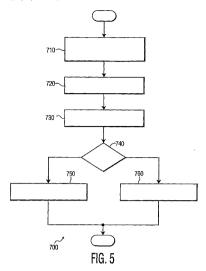

本発明によるテストシステムは、セルフタイミング型メモリにおける遅延障害を検出する能力を格段に向上させるテストモードにおいて外部クロック信号により内部メモリで接近で開いたセルフタイミング型半導体メモリの現行の設計に容易に統合される。さらにののテストシステムは、そのテスト能力を相当に向上させるとともに、その実現のためのセスを、図5に示すことができる。方法700は、外部クロック信号をセルフタイミング型とものの内部メモリブロックに供給する。内部クロック信号は、セルフタイミング型メモリの内部メモリブロックに供給する。内部クロック信号は、セルフタイミング型メモリの動信号は、セルフタイミング型メモリの動作のノーマルモードの間に内部メモリプロックに供給可能となり(750)、外部クロック信号は、セルフタイミング型メモリの動作のノーマルモードの間に内部メモリのテストモードの間内部メモリブロックに供給可能となる(760)。

[0025]

当業者であれば、本発明の他の沢山の実施例を添付の請求項に規定されるような本発明の主旨及び範囲から逸脱することなく見出すことができる。

【図面の簡単な説明】

[0026]

【図1】内部クロック信号を発生するためのクロックモニタを伴うアドレスデコーダを概略的に示す簡略化されたブロック図(先行技術)。

【図2】本発明によるテストシステムを伴う図1に示されるアドレスデコーダを概略的に示す簡略化されたブロック図(先行技術)。

【図3A】本発明によるテストシステムの一実施例を概略的に示す簡略化されたブロック

図。

【図3B】本発明によるテストシステムの他の実施例を概略的に示す簡略化されたブロック図。

【図3C】本発明によるテストシステムのさらに他の実施例を概略的に示す簡略化されたプロック図。

【図4】本発明の実施例によるテストシステムに結合された詳細なセルフタイミング型メモリブロック図。

【図5】本発明による実施例を実現する際のステップのフローチャート。

| 125 | 125 | 125 | 125 | 125 | 126 | 126 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127 | 127

【図3B】

FIG. 3B

【図3C】

FIG. 3C

【図4】

【図5】

INTERNATIONAL SEARCH REPORT

pal Application No

#### 【国際調査報告】

# PCT/IB2005/050800 a. classification of subject matter IPC 7 G11C29/00 According to International Patent Classification (IPC) or to both national classification and IPC B. FIELDS SEARCHED Minimum documentation searched (classification system followed by classification symbols) IPC 7 G11C Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched Electronic data base consulted during the international search (name of data base and, where practical, search terms used) EPO-Internal, PAJ C. DOCUMENTS CONSIDERED TO BE RELEVANT Citation of document, with indication, where appropriate, of the relevant passages Relevant to daim No. Category \* 1-24 P.X AZIMANE M ET AL: "New test methodology for resistive open defect detection in memory address decoders" VLSI TEST SYMPOSIUM, 2004. PROCEEDINGS. 22ND IEEE NAPA VALLEY, CA, USA 25-29 APRIL 2004, PISCATAWAY, NJ, USA, IEEE, 25 April 2004 (2004-04-25), pages 123-128, XP010705929 ISBN: 0-7695-2134-7 Items 4.2 - 4.3. figures 5-8 1-24 US 6 115 836 A (CHURCHILL ET AL) χ 5 September 2000 (2000-09-05) column 16, line 47 - column 19, line 10: figure 9 -/--Patent family members are listed in annex. Further documents are listed in the continuation of box C. Special categories of cited documents: "I" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the \*A' document defining the general state of the art which is not considered to be of particular relevance \*E' earlier document but published on or after the international filling date invention "X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone \*L\* document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified) "Y' document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art. \*O\* document referring to an oral disclosure, use, exhibition or "P" document published prior to the international filing date but later than the priority date claimed "&" document member of the same patent family Daté of mailing of the international search report Date of the actual completion of the international search 19 July 2005 28/07/2005 Name and mailing address of the ISA Authorized officer European Patent Office, P.B. 5818 Patentlaan 2 NL - 2280 HV Fijiswijk Tel. (+31-70) 340-2040, Tx. 31 651 epo nl, Fax: (+31-70) 340-3016 Ríos Báez, A

Form PCT/ISA/210 (second sheet) (January 2004)

# INTERNATIONAL SEARCH REPORT

Internation No PCT/1B2005/050800

| Continue   | uation) DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                                                  |  |                       |  |  |  |  |  |  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-----------------------|--|--|--|--|--|--|

| Category * | Citation of document, with indication, where appropriate, of the relevant passages                                                                                           |  | Relevant to claim No. |  |  |  |  |  |  |

|            |                                                                                                                                                                              |  |                       |  |  |  |  |  |  |

| Х          | US 2003/117881 A1 (JOHNSON BRIAN ET AL)<br>26 June 2003 (2003-06-26)                                                                                                         |  | 1,2,5-24              |  |  |  |  |  |  |

| Y          | abstract; figure 2<br>paragraph '0043!<br>                                                                                                                                   |  | 3,4                   |  |  |  |  |  |  |

| Y          | EP 0 867 887 A (TEXAS INSTRUMENTS<br>INCORPORATED)<br>30 September 1998 (1998-09-30)                                                                                         |  | 3                     |  |  |  |  |  |  |

| Ą          | abstract; figures 7a-7c<br>column 5, line 52 - line 58                                                                                                                       |  | 1,2,4-24              |  |  |  |  |  |  |

| Y          | WO 02/103706 A (ARTISAN COMPONENTS, INC)<br>27 December 2002 (2002-12-27)                                                                                                    |  | 4                     |  |  |  |  |  |  |

| A          | abstract; figures 3,4 page 13, line 10 - line 27 page 15, line 12 - line 25                                                                                                  |  | 1-3,5-24              |  |  |  |  |  |  |

| X          | PATENT ABSTRACTS OF JAPAN vol. 2002, no. 03, 3 April 2002 (2002-04-03) & JP 2001 332099 A (HITACHI LTD; HITACHI ULSI SYSTEMS CO LTD), 30 November 2001 (2001-11-30) abstract |  | 1,2,5-8               |  |  |  |  |  |  |

| A          |                                                                                                                                                                              |  | 3,4,9-24              |  |  |  |  |  |  |

|            | ·                                                                                                                                                                            |  |                       |  |  |  |  |  |  |

|            |                                                                                                                                                                              |  |                       |  |  |  |  |  |  |

|            |                                                                                                                                                                              |  |                       |  |  |  |  |  |  |

|            |                                                                                                                                                                              |  |                       |  |  |  |  |  |  |

|            |                                                                                                                                                                              |  |                       |  |  |  |  |  |  |

|            |                                                                                                                                                                              |  |                       |  |  |  |  |  |  |

|            |                                                                                                                                                                              |  |                       |  |  |  |  |  |  |

|            |                                                                                                                                                                              |  |                       |  |  |  |  |  |  |

|            |                                                                                                                                                                              |  |                       |  |  |  |  |  |  |

|            |                                                                                                                                                                              |  |                       |  |  |  |  |  |  |

|            |                                                                                                                                                                              |  |                       |  |  |  |  |  |  |

|            |                                                                                                                                                                              |  |                       |  |  |  |  |  |  |

Form PCT/ISA/210 (continuation of second sheet) (January 2004)

# **INTERNATIONAL SEARCH REPORT**

mation on patent family members

Internation No PCT/IB2005/050800

| Patent document<br>dted in search report |      | Publication date | Patent family<br>member(s) |            | Publication date |            |

|------------------------------------------|------|------------------|----------------------------|------------|------------------|------------|

| US 6115836                               | A    | 05-09-2000       | NONE                       | ·          |                  |            |

| US 200311788                             | L A1 | 26-06-2003       | AU                         | 2002361761 | A1               | 24-07-2003 |

|                                          |      |                  | EΡ                         | 1459323    | A1               | 22-09-2004 |

|                                          |      |                  | JΡ                         | 2005514721 | Ţ                | 19-05-2005 |

|                                          |      |                  | ΤW                         | 222068     | В                | 11-10-2004 |

|                                          |      |                  | US                         | 2005094432 | Ā1               | 05-05-2005 |

|                                          |      |                  | WO                         | 03058630   |                  | 17-07-2003 |

|                                          |      |                  | ÜS                         | 2004090821 |                  | 13-05-2004 |

| EP 0867887                               | A    | 30-09-1998       | EP                         | 0867887    | A2               | 30-09-1998 |

| EI 000/00/                               | ^    | 30 09 1390       | ĴΡ                         | 10255498   |                  | 25-09-1998 |

|                                          |      |                  | US                         | 6266749    |                  | 24-07-2001 |

|                                          |      |                  |                            | 0200743    |                  |            |

| WO 02103706                              | Α    | 27-12-2002       | US                         | 2004004872 | A1               | 08-01-2004 |

|                                          |      |                  | TW                         | 559823     | В                | 01-11-2003 |

|                                          |      |                  | WO                         | 02103706   | A2               | 27-12-2002 |

|                                          |      |                  | US                         | 2004062095 | A1               | 01-04-2004 |

| JP 200133209                             | 9 A  | 30-11-2001       | NONE                       |            |                  |            |

Form PCT/ISA/210 (patent family annex) (January 2004)

### フロントページの続き

(81)指定国 AP(BW,GH,GM,KE,LS,MW,MZ,NA,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM), EP(AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HU,IE,IS,IT,LT,LU,MC,NL,PL,PT,RO,SE,SI,SK,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AT,AU,AZ,BA,BB,BG,BR,BW,BY,BZ,CA,CH,CN,CO,CR,CU,CZ,DE,DK,DM,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,HR,HU,ID,IL,IN,IS,JP,KE,KG,KP,KR,KZ,LC,LK,LR,LS,LT,LU,LV,MA,MD,MG,MK,MN,MW,MX,MZ,NA,NI,NO,NZ,OM,PG,PH,PL,PT,RO,RU,SC,SD,SE,SG,SK,SL,SM,SY,TJ,TM,TN,TR,TT,TZ,UA,UG,US,UZ,VC,VN,YU,ZA,ZM,ZW

(72)発明者 アジマネ モハメド

オランダ国 5621 ベーアー アインドーフェン フルーネヴァウツウェッハ 1

(72)発明者 マジヒ アナンタ

オランダ国 5621 ベーアー アインドーフェン フルーネヴァウツウェッハ 1

Fターム(参考) 5L106 AA01 DD11 DD32 DD37 GG03

5M024 AA90 BB27 BB28 BB40 DD82 DD83 JJ36 MM04 MM10 PP01 PP02 PP10