## (19)**日本国特許庁(JP)**

# (12)特許公報(B2)

(11)特許番号 特許第7183061号 (P7183061)

(45)発行日 令和4年12月5日(2022.12.5)

(24)登録日 令和4年11月25日(2022.11.25)

| (51)国際特許分                                           | ·<br>類                                                                                                       | FΙ                                                  |                                                |                                                                                                                                         |

|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| H 0 1 L<br>H 0 1 L<br>G 0 9 F<br>G 0 2 F            | 29/786 (2006.01)<br>21/336 (2006.01)<br>9/30 (2006.01)<br>1/167(2019.01)                                     | H 0 1 L<br>H 0 1 L<br>H 0 1 L<br>H 0 1 L<br>G 0 9 F | 29/78<br>29/78<br>29/78<br>29/78<br>9/30<br>請求 | 6 1 6 T<br>6 1 7 N<br>6 1 2 A<br>6 1 2 B<br>3 3 8<br>試項の数 4 (全17頁) 最終頁に続く                                                               |

| (21)出願番号<br>(22)出願日<br>(65)公開番号<br>(43)公開日<br>審査請求日 | 特願2019-15774(P20<br>平成31年1月31日(20 <sup>2</sup><br>特開2020-123696(P2<br>A)<br>令和2年8月13日(2020<br>令和3年9月21日(2021 | 19.1.31)<br>2020-123696<br>0.8.13)                  | (73)特許権者 (74)代理人 (72)発明者 審査官                   | 502356528<br>株式会社ジャパンディスプレイ<br>東京都港区西新橋三丁目7番1号<br>110001737弁理士法人スズエ国際特許<br>事務所<br>尾関 芳孝<br>東京都港区西新橋三丁目7番1号 株式<br>会社ジャパンディスプレイ内<br>脇水 佳弘 |

|                                                     |                                                                                                              |                                                     |                                                | 最終頁に続く                                                                                                                                  |

## (54)【発明の名称】 表示装置及びトランジスタ

# (57)【特許請求の範囲】

### 【請求項1】

複数の画素が配置される画素部と、当該画素部の周辺に設けられる周辺部とを有する表示パネルと、

前記周辺部に設けられ、前記画素を駆動する駆動回路と

を具備し、

前記画素部または前記周辺部にはトランジスタが設けられており、該トランジスタは、第 1 端部及び第 2 端部を有する半導体層と、当該第 1 端部寄りの位置で当該半導体層と重置する第 1 ゲート電極と、該第 1 ゲート電極と前記第 2 端部との間で当該半導体層と重置する第 2 ゲート電極と、前記第 1 端部に接続されるソース電極と、前記第 2 端部に接続されるドレイン電極とを備え、

前記第1及び第2ゲート電極は、第1層に配置されており、

前記ソース電極及び前記ドレイン電極は、前記第1層とは異なる第2層に配置されており、

前記ソース電極は、平面視において、少なくとも前記第1ゲート電極と半導体層の重畳 領域である第1チャネル領域を覆って形成されており、

前記ドレイン電極は、平面視において、少なくとも前記第2ゲート電極と半導体層の重 畳領域である第2チャネル領域を覆って形成されて<u>おり、</u>

\_ 前記周辺部は、保護回路を含み、

<u>前記保護回路は、前記第1ゲート電極及び前記第2ゲート電極の順に並べて配置される</u>

第1ゲート電極部と、前記第2ゲート電極及び前記第1ゲート電極が並べて配置される第 <u>2 ゲート電極部とが交互に配置されるように構成されており、</u>

前記ソース電極及び前記ドレイン電極は、当該ソース電極が前記第1ゲート電極と重畳 する位置に配置され、当該ドレイン電極が前記第2ゲート電極と重畳する位置に配置され るように、互いに噛み合う 歯型の形状に形成され口る表示装置。

## 【請求項2】

前記第1チャネル領域と第2チャネル領域の形状及び面積は同一であり、

前記第1チャネル領域と前記ソース電極とが重畳する部分の面積は、前記第2チャネル 領域と前記ドレイン電極とが重畳する部分の面積と同一である

請求項1記載の表示装置。

## 【請求項3】

前記トランジスタは、基材と前記半導体層の間に前記第1及び第2ゲート電極が配置さ れるボトムゲート型のトランジスタである請求項1記載の表示装置。

#### 【請求項4】

前記トランジスタは、前記半導体層と前記ソース電極及び前記ドレイン電極との間に前 記第1及び第2ゲート電極が配置されるトップゲート型のトランジスタである請求項1記 載の表示装置。

【発明の詳細な説明】

#### 【技術分野】

#### [0001]

本発明の実施形態は、表示装置及びトランジスタに関する。

#### 【背景技術】

#### [0002]

一般に、素子基板と対向基板との間に電気泳動素子を挟持した電気泳動表示装置(EP D: Electrophoretic Display)が知られている。

## [0003]

この電気泳動表示装置によれば、当該電気泳動表示装置に配列されている各画素に含ま れる画素トランジスタを駆動することによって、当該各画素において例えば白色または黒 色等を表示することができる。

# [0004]

ところで、電気泳動表示装置は駆動電圧が大きく、上記した画素トランジスタにも高電 圧が印加される。

#### [0005]

このため、電気泳動表示装置においては、画素トランジスタに印加される高電圧に起因 する発熱により、特性異常または動作異常が生じる可能性がある。

【先行技術文献】

# 【特許文献】

#### [0006]

【文献】特開2009-049080号公報

## 【発明の概要】

【発明が解決しようとする課題】

## [0007]

そこで、本発明が解決しようとする課題は、発熱による異常を抑制することが可能な表 示装置及びトランジスタを提供することにある。

【課題を解決するための手段】

### [00008]

実施形態によれば、複数の画素が配置される画素部と、当該画素部の周辺に設けられる 周辺部とを有する表示パネルと、前記周辺部に設けられ、前記画素を駆動する駆動回路と を具備する表示装置が提供される。前記画素部または前記周辺部にはトランジスタが設け られており、該トランジスタは、第1端部及び第2端部を有する半導体層と、当該第1端 10

20

30

50

部寄りの位置で半導体層と重畳する第1ゲート電極と、該第1ゲート電極と前記第2端部との間で当該半導体層と重畳する第2ゲート電極と、前記第1端部に接続されるソース電極と、前記第2端部に接続されるドレイン電極とを備える。前記第1及び第2ゲート電極は、第1層に配置されている。前記ソース電極及び前記ドレイン電極は、前記第1層とは異なる第2層に配置されている。前記ソース電極は、平面視において、少なくとも前記第1ゲート電極と半導体層の重畳領域である第1チャネル領域を覆って形成されている。前記ドレイン電極は、平面視において、少なくとも前記第2ゲート電極と半導体層の重畳領域である第2チャネル領域を覆って形成されている。前記周辺部は、保護回路を含む。前記保護回路は、前記第1ゲート電極及び前記第2ゲート電極の順に並べて配置される第1ゲート電極部と、前記第2ゲート電極及び前記第1ゲート電極が並べて配置される第1ゲート電極部とが交互に配置されるように構成されている。前記ソース電極及び前記ドレイン電極は、当該ソース電極が前記第1ゲート電極と重畳する位置に配置され、当該ドレイン電極が前記第2ゲート電極と重畳する位置に配置され、当該ドレイン電極が前記第2ゲート電極と重畳する位置に配置され、当該ドレイン電極が前記第2ゲート電極と重畳する位置に配置され、当該ドレイン電極が前記第2ゲート電極と重畳する位置に配置され、当該ドレイン電極が前記第2ゲート電極と重畳する位置に配置されるように、互いに噛み合う 歯型の形状に形成されている。

【図面の簡単な説明】

#### [0009]

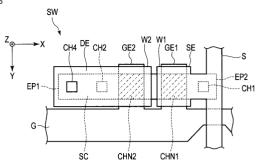

- 【図1】第1実施形態に係る表示装置の構成の一例を示す平面図。

- 【図2】画素の第1方向に沿った断面の一例を示す図。

- 【図3】画素トランジスタの一例を示す平面図。

- 【図4】本実施形態の比較例における画素の第1方向に沿った断面の一例を示す図。

- 【図5】本実施形態の比較例における画素トランジスタの一例を示す平面図。

- 【図6】ソース電極及びドレイン電極の構成の一例について説明するための図。

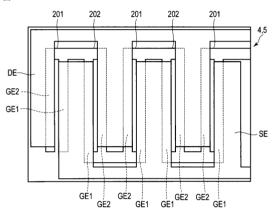

- 【図7】保護ダイオードの構成の一例について説明するための図。

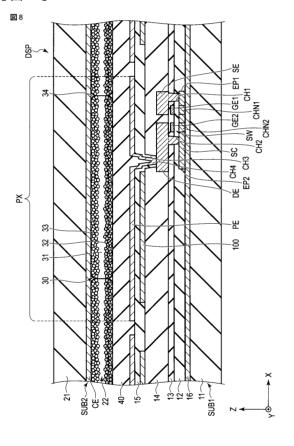

- 【図8】トップゲート型の画素トランジスタの一例を示す図。

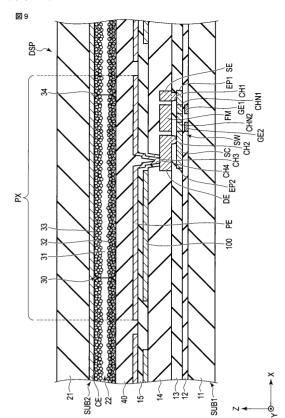

- 【図9】第2実施形態における画素の第1方向に沿った断面の一例を示す図。

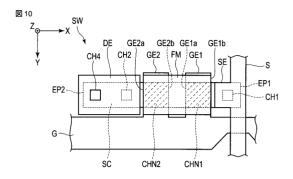

- 【図10】本実施形態における画素トランジスタの一例を示す平面図。

- 【図11】本実施形態における画素トランジスタの他の例を示す平面図。

- 【図12】トップゲート型の画素トランジスタの一例を示す図。

【発明を実施するための形態】

## [0010]

以下、本実施形態について、図面を参照しながら説明する。なお、開示はあくまで一例に過ぎず、当業者において、発明の主旨を保っての適宜変更について容易に想到し得るものについては、当然に本発明の範囲に含有されるものである。また、図面は、説明をより明確にするため、実際の態様に比べて、各部の幅、厚さ、形状等について模式的に表される場合があるが、あくまで一例であって、本発明の解釈を限定するものではない。また、本明細書と各図において、既出の図に関して前述したものと同一または類似した機能を発揮する構成要素には同一の参照符号を付し、重複する詳細な説明を適宜省略することがある。

### [0011]

## (第1実施形態)

図1は、第1実施形態に係る表示装置の構成の一例を示す平面図である。図1に示す例では、第1方向X、第2方向Y及び第3方向Zは、互いに直交しているが、互いに90度以外の角度で交差していてもよい。第1方向X及び第2方向Yは、表示装置DSPを構成する基板の主面と平行な方向に相当し、第3方向Zは、表示装置DSPの厚さ方向に相当する。本実施形態において、第3方向Zを示す矢印の先端側の位置を上方(または単に上)と称し、矢印の後端側の位置を下方(または単に下)と称する。また、第3方向Zを示す矢印の先端側に表示装置DSPを観察する観察位置があるものとし、この観察位置から、第1方向X及び第2方向Yで規定されるX-Y平面に向かって見ることを平面視という。

# [0012]

図1に示す表示装置DSPは、第1基板SUB1及び第2基板SUB2を含む表示パネ

10

20

30

40

ル1を備える。表示パネル1は、画素部としての表示領域DAと、当該画素部の周辺に設けられる周辺部としての非表示領域NDAとを有する。

#### [0013]

表示領域DAは、平面視で第1基板SUB1及び第2基板SUB2が重畳する領域に位置している。表示領域DA(画素部)においては、第1方向X及び第2方向Yにマトリクス状に複数の画素PXが配置されている。

## [0014]

非表示領域NDAは、額縁状に形成されている。ゲートドライバGD1及びGD2とソースドライバSDとを含む駆動回路(表示パネル1を駆動する駆動回路)は、非表示領域NDAに位置し、第1基板SUB1に設けられている。

#### [0015]

フレキシブル配線基板2は、第1基板SUB1に接続されている。ICチップ3は、フレキシブル配線基板2に接続されている。なお、ICチップ3は、第1基板SUB1に接続されてもよい。また、上記したゲートドライバGD1及びGD2とソースドライバSDとは、例えばICチップ3に内蔵されていてもよい。

#### [0016]

更に、本実施形態に係る表示装置DSPにおいては、第1基板SUB1上に保護ダイオード4及び5が設けられていてもよい。保護ダイオード4はフレキシブル配線基板2とソースドライバSDとの間に配置されており、当該保護ダイオード4を経て供給される信号がソースドライバSDに入力される。保護ダイオード5はゲートドライバGD1及びGD2の各々に対応する位置に配置されており、当該保護ダイオード5を経て供給される信号がゲートドライバGD1及びGD2に入力される。

#### [0017]

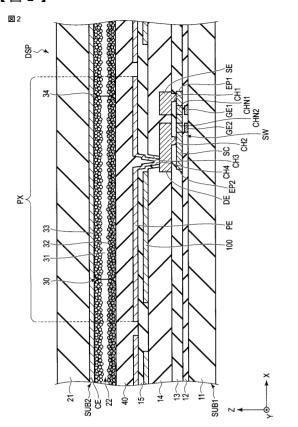

図2は、画素部に設けられる画素PXの第1方向Xに沿った断面の一例を示す。図2に示すように、第1基板SUB1は、基材11及び絶縁膜12~15を備える。

## [0018]

基材 1 1 は、絶縁性のガラスやポリイミド樹脂等の樹脂によって形成された絶縁基板である。基材 1 1 は、第 2 基板 S U B 2 に対して観察位置の反対側に位置しているため、例えば不透明な基材であるが、透明な基材であってもよい。

#### [0019]

ここで、上記した画素 P X (画素回路)はスイッチング素子である画素トランジスタ (薄膜トランジスタ) S W を含むが、本実施形態において、当該画素トランジスタ S W は、ダブルゲート構造を有する。すなわち、画素トランジスタ S W は、半導体層 S C と、2 つのゲート電極 G E 1 及び G E 2 と、1 つのソース電極 S E と、1 つのドレイン電極 D E とを有する。

# [0020]

ゲート電極GE1及びGE2は、基材11の上に位置し、絶縁膜(ゲート絶縁膜)12によって覆われている。ゲート電極GE1及びGE2は、アルミニウム(A1)、チタン(Ti)、銀(Ag)、モリブデン(Mo)、タングステン(W)、銅(Cu)、クロム(Cr)等の金属材料や、これらの金属材料を組み合わせた合金等によって形成される。また、ゲート電極GE1及びGE2は、単層構造であってもよいし、積層構造であってもよい。

## [0021]

半導体層SCは、絶縁膜12の上に位置し、絶縁膜13によって覆われている。半導体層SCは、平面視において、上記したゲート電極GE1及びGE2と重畳する位置に配置されている。半導体層SCは、例えば多結晶シリコン(例えば、低温ポリシリコン)によって形成されているが、アモルファスシリコンや酸化物半導体によって形成されていてもよい。

# [0022]

なお、図2に示す例において、画素トランジスタSWは、基材11と半導体層SCとの

10

20

30

40

間に(つまり、半導体層SCの下に)ゲート電極GE1及びGE2が配置されるボトムゲート型のトランジスタである。

## [0023]

ソース電極SE及びドレイン電極DEは、絶縁膜13の上に位置し、絶縁膜14によって覆われている。ソース電極SE及びドレイン電極DEは、同一材料によって形成され、例えば上記の金属材料を用いて形成されている。

## [0024]

ソース電極 S E は、絶縁膜 1 3 を貫通する貫通孔 C H 1 において、半導体層 S C にコンタクトしている(接続されている)。ドレイン電極 D E は、絶縁膜 1 3 を貫通する貫通孔 C H 2 において、半導体層 S C にコンタクトしている(接続されている)。

## [0025]

すなわち、トランジスタSWは、半導体層SCと、当該半導体層SCの一方の端部(第1端部)EP1寄りの位置で半導体層SCと重畳するゲート電極GE1と、当該ゲート電極GE1と他方の端部(第2端部)EP2との間で半導体層SCと重畳するゲート電極GE2と、半導体層SCの端部EP1に接続されるソース電極SEと、当該半導体層SCの端部EP2に接続されるドレイン電極DEとを備えている。

### [0026]

なお、ゲート電極GE1及びGE2は走査線に接続され、ソース電極SEは信号線に接続されているが、図2においては、当該走査線及び信号線は省略されている。

## [0027]

容量電極100は、絶縁膜14の上に位置し、絶縁膜(容量絶縁膜)15によって覆われている。容量電極100は、例えばインジウムスズ酸化物(ITO)またはインジウム 亜鉛酸化物(IZO)等の透明導電材料によって形成された透明電極である。容量電極100は、透明でない金属材料(非透明導電材料)によって形成されていてもよい。なお、図2においては省略されているが、容量電極100は、例えば給電線等にコンタクトしていてもよい。

## [0028]

画素電極PEは、絶縁膜15の上に位置している。画素電極PEは、表示領域DAに配置されている複数の画素PXの各々に対して1つずつ設けられている。

#### [0029]

画素電極PEは、絶縁膜14を貫通する貫通孔CH3及び絶縁膜15を貫通する貫通孔CH4において、ドレイン電極DEにコンタクトしている。画素電極PEは、上記したITOまたはIZO等の透明導電材料によって形成された透明電極である。画素電極PEは、光反射性を有する金属材料(非透明導電材料)によって形成されていてもよい。画素電極PEは、絶縁膜15を介して容量電極100と重畳し、画素PXの容量を形成する。

## [0030]

絶縁膜12、13及び15は、シリコン酸化物(SiO)、シリコン窒化物(SiN)、シリコン酸窒化物(SiON)等の無機材料によって形成された無機絶縁膜に相当する。これらの絶縁膜12、13及び15は、それぞれが単層構造であってもよいし、積層構造であってもよい。

# [0031]

絶縁膜14は、アクリル樹脂等の有機材料によって形成された有機絶縁膜(有機平坦化膜)に相当する。絶縁膜14は、上記の無機絶縁膜(絶縁膜12、13及び15)よりも厚く形成されている。当該有機絶縁膜を所定の厚さで形成することにより、当該有機絶縁膜より下方の凹凸が吸収され、有機絶縁膜上は平坦なものとなる。これにより、当該有機絶縁膜上に形成される容量電極や画素電極の凹凸は抑制される。

## [0032]

ここで、本実施形態に係る表示装置 DSP は、例えば電気泳動表示装置 (EPD: Elect rophoretic Display) であるものとする。この場合、第2基板 SUB2は、基材21、 共通電極 CE 及び電気泳動素子22を備えている。 10

20

30

#### [0033]

基材 2 1 は、絶縁性のガラスまたはポリイミド樹脂等の樹脂によって形成されている。 基材 2 1 は、第 1 基板 S U B 1 に対して観察位置側に位置しているため、透明な基材である。

## [0034]

共通電極 C E は、基材 2 1 と電気泳動素子 2 2 との間に位置している。共通電極 C E は、 I T O や I Z O 等の透明導電材料によって形成された透明電極である。なお、共通電極 C E は、上記した容量電極 1 0 0 と同電位である。

#### [0035]

電気泳動素子22は、画素電極PEと共通電極CEとの間に位置している。電気泳動素子22は、X-Y平面内においてほとんど隙間なく配列された複数のマイクロカプセル30によって形成されている。

## [0036]

マイクロカプセル30は、例えば20µm~70µm程度の粒径を有している。なお、例えば1辺の長さが百~数百µm程度の矩形状または多角形上の画素電極PEの上には、1個~10個程度のマイクロカプセル30が配置されている。

### [0037]

マイクロカプセル30は、分散媒31と、複数の黒色粒子32と、複数の白色粒子33とを備えている。マイクロカプセル30の外殻34は、例えばアクリル樹脂等の透明な樹脂によって形成されている。

### [0038]

分散媒31は、マイクロカプセル30内において、黒色粒子32及び白色粒子33を分散させる液体である。

## [0039]

黒色粒子32及び白色粒子33は、例えば電気泳動粒子と称され、互いに逆極性の電荷を有している。例えば黒色粒子32は正に帯電し、白色粒子33は負に帯電している。

# [0040]

なお、マイクロカプセル30は、黒色粒子32及び白色粒子33の他に、赤、緑、青、イエロー、シアン、マゼンタ等の他の色の電気泳動粒子を備えていてもよい。また、上記の他の色の電気泳動粒子は、黒色粒子32及び白色粒子33の少なくとも一方と置換されてもよい。

## [0041]

上記構成の電気泳動素子22において画素PXが黒を表示する場合、画素電極PEが共通電極CEよりも相対的に高電位に保持される。すなわち、共通電極CEの電位を基準電位としたとき、画素電極PEが正極性に保持される。これにより、正に帯電した黒色粒子32が共通電極CEに引き寄せられる一方で、負に帯電した白色粒子33が画素電極PEに引き寄せられる。その結果、第2基板SUB2の上方(つまり、観察位置)から画素PXを観察すると、黒色が視認される。

## [0042]

一方、画素PXが白を表示する場合、画素電極PEが共通電極CEよりも相対的に低電位に保持される。すなわち、共通電極CEの電位を基準電位としたとき、画素電極PEが負極性に保持される。これにより、負に帯電した白色粒子33が共通電極CE側へ引き寄せられる一方で、正に帯電した黒色粒子32が画素電極PEに引き寄せられる。その結果、第2基板SUB2の上方(つまり、観察位置)から画素PXを観察すると白色が視認される。

# [0043]

なお、上記した第1基板SUB1及び第2基板SUB2は、粘着層40によって貼合されている。図2に示す例では、粘着層40は、画素電極PEと電気泳動素子22との間に位置している。

## [0044]

10

20

30

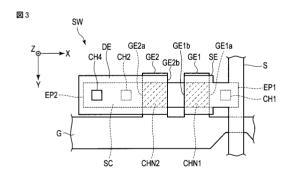

図3は、本実施形態における画素トランジスタSWの一例を示す平面図である。なお、上記したように画素トランジスタSWは、2つのゲート電極(つまり、ゲート電極GE1 及びGE2)を備えるダブルゲート構造を有する。

#### [0045]

図3に示すように、ゲート電極GE1及びGE2は、走査線Gと同層に形成されており、当該走査線Gと接続されている。走査線Gは、第1方向Xに沿って延出し、図1に示すゲートドライバGD1及びGD2の一方に接続されている。ソース電極SEは、ソース電極SE及びドレイン電極DEと同層に形成されている信号線Sと接続されている。信号線Sは、第2方向Yに沿って延出し、図1に示すソースドライバSDに接続されている。画素トランジスタSWは、走査線Gと信号線Sとの交差部に位置している。

[0046]

ゲート電極 G E 1 及び G E 2 は、第 1 方向 X に間隔を置いて並べて配置される。また、ゲート電極 G E 1 及び G E 2 は、半導体層 S C と重畳する位置に配置される。

## [0047]

なお、ゲート電極 G E 1 及び G E 2 は、平面視において同一の形状及び同一の大きさ(面積)に形成されている。

### [0048]

ソース電極SEは、貫通孔CH1において半導体層SCと電気的に接続されている。ドレイン電極DEは、貫通孔CH2において半導体層SCと電気的に接続されている。なお、画素電極PEは、貫通孔CH4においてドレイン電極DEと電気的に接続されている。この場合、ドレイン電極DEは、画素電極PEとコンタクトするコンタクト部の台座としても機能する。

# [0049]

ここで、ゲート電極 G E 1 は、信号線 S に沿う第 1 端部 G E 1 a と、該第 1 端部 G E 1 a とゲート電極 G E 2 との間に設けられる第 2 端部 G E 1 b とを備えている。かかるゲート電極 G E 1 に対し、ソース電極 S E はゲート線 G に沿って延在しており、平面視において、第 1 端部 G E 1 a 及び第 2 端部 G E 1 b の両方と重畳する。

#### [0050]

また、ゲート電極GE2は、ゲート線Gと交差する(例えば、直行する)方向に沿う第3端部GE2aと、当該第3端部GE2aとゲート電極GE1との間に設けられる第4端部GE2bとを備えている。かかるゲート電極GE2に対し、ドレイン電極DEはゲート線Gに沿って延在しており、平面視において、第3端部GE2a及び第4端部GE2bの両方と重畳する。

# [0051]

すなわち、本実施形態において、ソース電極SEは第1方向Xにおいてゲート電極GE 1(ゲート電極GE1に対応するチャネル領域の上部)を全て覆って形成されており、ドレイン電極DEはゲート電極GE2(ゲート電極GE2に対応するチャネル領域の上部)を全て覆って形成されている。チャネル領域とは、半導体層のうち、ゲート電極GE1を正投影して当該ゲート電極GE1に重なる領域CHN1及びゲート電極GE2を正投影して当該ゲート電極GE2に重なる領域CHN2をいう。

# [0052]

なお、図3に示す例では平面視においてソース電極SEのドレイン電極DE側の端部がゲート電極GE1の端部GE1bと一致しているが、ソース電極SEは第1方向Xにおいてゲート電極GE1の全てを覆っていればよい。このため、ソース電極SEのドレイン電極DE側の端部は、ゲート電極GE1のゲート電極GE2側の端部GE1bを越えて、更に延伸していてもよい。

#### [0053]

同様に、ドレイン電極 D E のソース電極 S E 側の端部は、ゲート電極 G E 2 の端部 G E 2 b を越えて、更に延伸していてもよい。

## [0054]

10

20

30

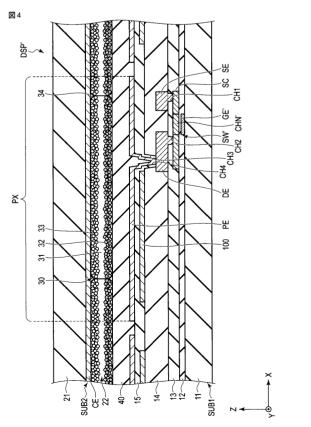

以下、本実施形態に係る表示装置DSPの作用について説明する。ここで、図4は、本実施形態の比較例における画素PXの第1方向Xに沿った断面を示す図である。また、図5は、本実施形態の比較例における画素トランジスタSW´の平面図である。

#### [0055]

なお、図4及び図5において上記した図2及び図3と同様の部分には、当該図2及び図3と同一参照符号が付されている。ここでは、図2及び図3と同様の部分についての説明を省略する。以下の説明についても同様である。

## [0056]

本実施形態の比較例において、画素トランジスタSW´は、シングルゲート構造を有する。すなわち、画素トランジスタSW´は、ゲート電極GE´、ソース電極SE及びドレイン電極DEをそれぞれ1つずつ有している。

#### [0057]

また、本実施形態の比較例において、ソース電極SEは、平面視においてゲート電極GE´と重畳していないものとする。また、ドレイン電極DEは、平面視においてゲート電極GE´のドレイン電極DE側の一部のみと重畳しているものとする。

#### [0058]

すなわち、本実施形態の比較例は、画素トランジスタSW´がシングルゲート構造を有し、かつ、ゲート電極GE´の全てがソース電極SE及びドレイン電極DEで覆われていない点で本実施形態とは異なる。

#### [0059]

ここで、上記した本実施形態の比較例に係る表示装置 D S P ′ において画像を表示する場合を想定する。この場合、画素トランジスタ S W ′ には、当該画素トランジスタ S W ′ のスイッチング駆動に伴って例えば 4 0 V 以上の高電圧が印加される。このため、画素トランジスタ S W ′ のチャネル領域 C H N ′ においては強電界が生じ、ホットキャリアが加速される。

## [0060]

この結果、当該のチャネル領域 C H N ´ (ゲート電極 G E ´ と重畳する半導体層 S C の領域)で局所的にホットキャリアの発生に伴う高熱が発生し、画素トランジスタ S W ´ の上部に形成されている有機絶縁膜(絶縁膜14)が焼損する可能性がある。

## [0061]

このような有機絶縁膜の焼損は、画素トランジスタSW´の閾値特性(Vth特性)に 影響を及ぼすため、画素トランジスタSW´の特性異常及び動作異常の原因となる。

#### [0062]

なお、図4及び図5に示す例ではドレイン電極DEがゲート電極GE´の一部と重畳しているが、このように一部と重畳するのみでは、電気泳動表示装置において印加される高電圧下における上記した有機絶縁膜の焼損を防止することはできない。

## [0063]

ここで、上記した有機絶縁膜の焼損を防止するために、本実施形態の比較例において、 ゲート電極GE´の全てを例えばドレイン電極DE(ドレインメタル)で覆う(オーバー ラップさせる)構成が考えられる。

# [0064]

一方で、かかる構成はドレイン電極DEの電圧状態によって発生する電界がチャネル領域CHN´に影響し、トランジスタ特性に変化を及ぼすことが考えられる。すなわち、回路設計的に画素トランジスタ(ソース電極SE及びドレイン電極DE含む)全体が非対称な構成となり、ソース電極SE 正印加及びドレイン電極DE - 負印加とした場合と、これらを逆転させた場合とでトランジスタ特性が変化する(対称とならない)ことが考えられる。このため、良好なトランジスタ特性が損なわれる場合がある。

# [0065]

これに対して、本実施形態においては、画素トランジスタSWがダブルゲート構造を有し、当該ダブルゲート構造における一方のゲート電極GE1(当該ゲート電極GE1に対

10

20

30

応するチャネル領域)を覆うソース電極SEを形成するとともに、他方のゲート電極GE 2(当該ゲート電極GE2に対応するチャネル領域)を覆うドレイン電極DEを形成する。

[0066]

これによれば、ゲート電極GE1に対応するチャネル領域で発生する熱はソース電極SEで分散され、ゲート電極GE2に対応するチャネル領域で発生する熱はドレイン電極DEで分散される。

[0067]

上記したように本実施形態において、画素トランジスタSWは、第1端部EP1及び第2端部EP2を有する半導体層SCと、半導体層SCの第1端部EP1寄りの位置で当該半導体層SCと重畳するゲート電極(第1ゲート電極)GE1と、当該ゲート電極GE1と半導体層SCの第2端部EP2との間で当該半導体層SCと重畳するゲート電極(第2ゲート電極)GE2と、半導体層SCの第1端部EP1に接続されるソース電極SEと、半導体層SCの第2端部EP2に接続されるドレイン電極DEとを備える。なお、本実施形態において、ゲート電極GE1及びGE2とソース電極SE及びドレイン電極DEとは異なる層に配置されている。

[0068]

また、本実施形態において、ソース電極SEは、平面視において、ゲート電極GE1の端部GE1a及びGE1bと重畳している。更に、ドレイン電極DEは、平面視において、ゲート電極GE2の端部GE2a及びGE2bと重畳している。

[0069]

すなわち、本実施形態においては、画素トランジスタSWをダブルゲート構造とした上で、ソース電極SE及びドレイン電極DEをそれぞれ延伸してゲート電極GE1及びGE2と重畳させる(中間ノードまで当該ソース電極SE及びドレイン電極DEで覆う)。これより、高電圧下での表示装置DSP(例えば、電気泳動表示装置)の駆動に起因する画素トランジスタの発熱を当該ソース電極SE及びドレイン電極DEで分散(放熱)させることが可能となる。これによれば、有機絶縁膜への局所的な伝熱を抑制し、当該有機絶縁膜が焼損することを防止する(つまり、許容耐圧を向上する)ことができるため、発熱による異常を抑制することが可能となる。

[0070]

なお、本実施形態において、平面視におけるゲート電極GE1及びGE2の形状及び面積(大きさ)は同一であり、ゲート電極GE1とソース電極SEとが重畳する部分の面積は、ゲート電極GE2とドレイン電極DEとが重畳する部分の面積と同一である。

[0071]

すなわち、本実施形態においては、ゲート電極GE1に対応するチャネル領域(第1チャネル領域)CHN1と重畳するソース電極SEの幅及びゲート電極GE2に対応するチャネル領域(第2チャネル領域)CHN2と重畳するドレイン電極DEの幅(つまり、メタル幅)を同一とすることにより、S-D逆転時のトランジスタ特性(Vth、ON電流)が対称となり、駆動設計観点でマージンを確保しやすい良好なトランジスタ特性を得ることができる。

[0072]

ここで、本実施形態において、ソース電極SEは少なくとも当該ソース電極SEの端部が当該ゲート電極GE1に対応するチャネル領域CHN1の端部と一致する位置まで延在していればよい(つまり、ソース電極SEがゲート電極GE1の第1端部GE1aに対応するチャネル領域CHN1の端部及び第2端部GE1bに対応するチャネル領域CHN1の端部と重畳していればよい)が、当該ソース電極SEは、当該ソース電極SEの端部がゲート電極GE1に対応するチャネル領域CHN1の端部を越える位置まで延在していてもよい。換言すれば、本実施形態においてソース電極SEは、平面視において、少なくともゲート電極GE1に対応するチャネル領域CHN1を覆って形成されている。

[0073]

同様に、本実施形態において、ドレイン電極DEは少なくとも当該ドレイン電極DEの

10

20

30

40

端部が当該ゲート電極GE2に対応するチャネル領域CHN2の端部と一致する位置まで延在していればよい(つまり、ドレイン電極DEがゲート電極GE2の第3端部GE2aに対応するチャネル領域CHN2の端部及び第4端部GE2bに対応するチャネル領域CHN2の端部と重畳していればよい)が、当該ドレイン電極DEは、当該ドレイン電極DEの端部がゲート電極GE2に対応するチャネル領域CHN2の端部を越える位置まで延在していてもよい。換言すれば、本実施形態においてドレイン電極DEは、平面視において、少なくともゲート電極GE2に対応するチャネル領域CHN2を覆って形成されている。

#### [0074]

この場合、上記発熱における放熱の効率を高めるためには、ソース電極SEとドレイン電極DEの面積がいずれも大きい方が好ましい。この結果としてゲート電極GE1の第2端部GE1bを越えるソース電極SEの端部と、ゲート電極GE2の第2端部GE2bを越えるドレイン電極DEの端部とがゲート電極間で互いに近接することが考えられるが、過剰に近接するとソース電極SEとドレイン電極DEとが電気的に接続され、ショートする可能性がある。このため、ソース電極SEの端部とドレイン電極DEの端部とはショートしない程度に近接しているものとする。なお、ソース電極SE及びドレイン電極DEとがショートすることを防止するために、例えばソース電極SEのドレイン電極DE側の角部(端部)及びドレイン電極DEのソース電極SE側の角部(端部)が面取り加工されていてもよい。

#### [0075]

更に、ソース電極SEは、比較的面積の大きい信号線Sと接続されている(一体に形成されている)ため、ゲート電極GE1に対応するチャネル領域で熱が発生したとしても、当該熱を信号線S側に放熱しやすい(逃がしやすい)。他方、ドレイン電極DEは島状に形成されており、ソース電極SEに比べると熱を逃がしにくい。このため、図6に示すように、例えばソース電極SEがゲート電極GE1を越えて延在する幅W1(第1幅)を、ドレイン電極DEがゲート電極GE2を越えて延在する幅W2(第2幅)よりも小さく形成する。

#### [0076]

このような構成によれば、ドレイン電極DEを大きく形成することができ、ゲート電極GE2に対応するチャネル領域CHN2における発熱に対する分散効果を向上させることができる。

# [0077]

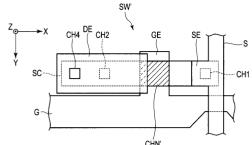

なお、本実施形態においては画素部(表示領域 DA)に含まれる画素トランジスタ SW について主に説明したが、本実施形態は、周辺部(非表示領域 NDA)に含まれる例えば保護ダイオード(保護回路)等に対して適用されても構わない。

# [0078]

ここで、図7を参照して、保護ダイオードの構成の一例について簡単に説明する。本実施形態においては、上記した図1に示す保護ダイオード4及び5のうちの少なくとも一方が図7に示す構成を有していればよい。

## [0079]

保護ダイオード4、5は具体的にはダイオード接続された薄膜トランジスタを含み、例えば画素PXに含まれる画素トランジスタよりも保護ダイオード4、5の閾値電圧を高くする。このような保護ダイオード4、5によれば、サージ電流が侵入した場合に画素トランジスタ(画素回路)を保護することができる。

#### [0800]

図 7 に示すように、保護ダイオード 4 、 5 において、ゲート電極は、ゲート電極 G E 1 及び G E 2 の順に並べて配置されるゲート電極部(第 1 ゲート電極部) 2 0 1 と、ゲート電極 G E 2 及び G E 1 の順に並べて配置されるゲート電極部(第 2 ゲート電極部) 2 0 2 とが交互に配置される構成を有する。

## [0081]

10

20

30

このようなゲート電極に対して、ソース電極SE及びドレイン電極DEは、それぞれ 歯状に形成され、平面視で互いに噛み合って配置されている。これによれば、ソース電極 SEはゲート電極GE1と重畳する位置に配置され、ドレイン電極DEはゲート電極GE 2と重畳する位置に配置される。

## [0082]

図7に示すような保護ダイオード4、5においては、上記した画素トランジスタSWと同様に、ゲート電極GE1がソース電極SEで覆われるとともに、ゲート電極GE2がドレイン電極DEで覆われる構成であるため、トランジスタのチャネル領域で発生した熱を分散させることが可能となる。なお、図7においては、半導体層SCは省略されている。

#### [0083]

ここでは保護ダイオード 4、5について説明したが、周辺部に含まれる他のトランジスタであっても同様に、ダブルゲート構造とし、2つのゲート電極の各々と重畳するソース電極及びドレイン電極を形成することによって、トランジスタのチャネル領域で発生した熱を分散させることが可能である。

#### [0084]

なお、本実施形態においては画素トランジスタSWがボトムゲート型のトランジスタである場合について説明したが、本実施形態は、図8に示すようにソース電極SE及びドレイン電極DEの各々と半導体層SCの間(つまり、半導体層SCの上に)ゲート電極GE1及びGE2が配置されるトップゲート型のトランジスタに適用されても構わない。

### [0085]

図8に示す例では、第1基板SUB1は、ボトムゲート型の場合と同様に基材11及び 絶縁膜12~15を備えるが、基材11と半導体層SCとの間にはアンダーコート層16 が更に設けられている。なお、アンダーコート層16は、無機材料によって形成された無 機絶縁膜に相当する。なお、図2等と同様の部分については、ここではその詳しい説明を 省略する。

## [0086]

また、本実施形態においては表示装置DSPが電気泳動表示装置であるものとして主に説明したが、本実施形態において説明したトランジスタは、電気泳動表示装置以外の表示装置(例えば、液晶表示装置)に適用されても構わない。更に、本実施形態において説明したトランジスタは、表示装置以外の電子機器等に適用されても構わない。以下の実施形態についても同様である。

## [0087]

## (第2実施形態)

次に、第2実施形態について説明する。なお、本実施形態に係る表示装置の構成については、前述した第1実施形態と同様であるため、適宜、図1を用いて説明する。

# [0088]

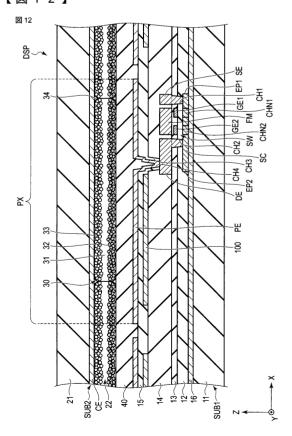

図9は、本実施形態における画素PXの第1方向Xに沿った断面の一例を示す図である。なお、前述した図2と同様の部分には同一参照符号を付してその詳しい説明を省略する。ここでは、図2と異なる部分について主に述べる。

## [0089]

前述した第1実施形態においてはソース電極SEがゲート電極GE1と重畳し、ドレイン電極DEがゲート電極GE2と重畳するものとして説明したが、本実施形態は、ゲート電極GE1及びGE2と重畳する位置にフローティングメタル(メタル部材)を配置する点で当該第1実施形態とは異なる。

#### [0090]

図9に示すように、フローティングメタルFMは、絶縁膜13の上に位置し、絶縁膜14によって覆われている。また、フローティングメタルFMは、ソース電極SE及びドレイン電極DEと同じ層であって、当該ソース電極SE及びドレイン電極DEに挟まれる位置に配置される。なお、フローティングメタルFMは、前述した金属材料を用いて形成される。

10

20

30

30

#### [0091]

なお、図 9 に示す例において、画素トランジスタ S W は、ボトムゲート型のトランジスタである。

#### [0092]

図10は、本実施形態における画素トランジスタSWの平面図である。なお、前述した図3と同様の部分には同一参照符号を付してその詳しい説明を省略する。ここでは、図3と異なる部分について主に述べる。

### [0093]

本実施形態における画素トランジスタSWは、前述した第1実施形態と同様に、ダブル ゲート構造を有する。

#### [0094]

ソース電極 S E は、貫通孔 C H 1 において半導体層 S C と電気的に接続されている。ドレイン電極 D E は、貫通孔 C H 2 において半導体層 S C と電気的に接続されている。

## [0095]

なお、本実施形態において、ソース電極SEは、平面視においてゲート電極GE1及びGE2とは重畳しない。同様に、ドレイン電極DEは、平面視においてゲート電極GE1及びGE2とは重畳しない。

#### [0096]

ここで、本実施形態においては、上記したようにソース電極SEとドレイン電極DEとに挟まれる位置にフローティングメタルFMが形成されている。

#### [0097]

フローティングメタルFMは、ゲート電極GE1の端部GE1a及びGE1bとゲート 電極GE2の端部GE2a及びGE2bとの全てと重畳している。

## [0098]

この場合、フローティングメタルFMは、当該フローティングメタルFMのソース電極SE側の端部とゲート電極GE1の端部GE1aとが平面視において少なくとも一致する位置まで延在し、当該フローティングメタルFMのドレイン電極DE側の端部とゲート電極GE2の端部GE2aとが平面視において少なくとも一致する位置まで延在している。

# [0099]

すなわち、本実施形態においては、第1方向 X においてゲート電極 G E 1 及び G E 2 (ゲート電極 G E 1 及び G E 2 の各々に対応するチャネル領域 C H N 1 及び C H N 2 の上部)を全て覆うフローティングメタル F M が形成されている。

#### [0100]

図10に示す例では平面視においてフローティングメタルFMの第1方向Xの両端部がゲート電極GE1の端部GE1a及びゲート電極GE2の端部GE2aとそれぞれ一致しているが、フローティングメタルFMはゲート電極GE1及びGE2を覆っていればよい。このため、フローティングメタルFMの両端部は、ソース電極SE側及びドレイン電極DE側の双方に更に延伸していてもよいし、当該ソース電極SE側及びドレイン電極DE側の一方にのみ更に延伸していてもよい。

# [0101]

上記したように本実施形態においては、画素トランジスタSWをダブルゲート構造とした上で、ゲート電極GE1(当該ゲート電極GE1に対応するチャネル領域CHN1)及びゲート電極GE2(当該ゲート電極GE2に対応するチャネル領域CHN2)と重畳する位置にフローティングメタルFM(メタル部材)が配置される。

#### [0102]

これによれば、ゲート電極GE1に対応するチャネル領域CHN1で発生した熱及びゲート電極GE2に対応するチャネル領域CHN2で発生した熱はフローティングメタルFMで分散される。

## [0103]

したがって、本実施形態においては、有機絶縁膜への伝熱を抑制し、当該有機絶縁膜が

10

20

30

焼損することを防止することができるため、発熱による異常を抑制することが可能となる。 【 0 1 0 4 】

なお、上記した図10に示す例では平面視におけるフローティングメタルFMの第2方向Yの幅はゲート電極GE1及びGE2の第2方向Yの幅よりも狭いが、当該フローティングメタルFMの第2方向Yの幅を当該第2方向Yに更に延伸してもよい。これによれば、フローティングメタルFMの面積を大きくし、ゲート電極GE1及びGE2を確実に覆うことが可能となるため、上記した画素トランジスタSWのチャネル領域における発熱に対する分散効果を更に向上させることが可能となる。

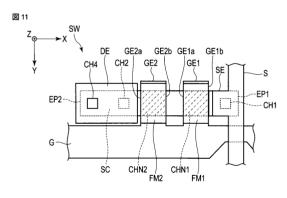

## [0105]

また、図10においてはゲート電極GE1(に対応するチャネル領域CHN1)及びゲート電極GE2(に対応するチャネル領域CHN2)を重畳する1つのフローティングメタルFMが形成されるものとして説明したが、図11に示すように、ゲート電極GE1に重畳する第1フローティングメタルFM1及びゲート電極GE2に重畳する第2フローティングメタルFM2が形成される構成としても構わない。

#### [0106]

図11に示す第1フローティングメタルFM1及び第2フローティングメタルFM2が 形成される構成であっても、ゲート電極GE1に対応するチャネル領域CHN1で発生した熱を第1フローティングメタルFM1で分散し、ゲート電極GE2に対応するチャネル 領域CHN2で発生した熱を第2フローティングメタルFM2で分散することができるため、発熱による異常を抑制することが可能となる。

#### [0107]

なお、本実施形態においては画素部に含まれる画素トランジスタSWについて主に説明 したが、本実施形態は、第1実施形態において説明したように周辺部に含まれるトランジ スタに対して適用されても構わない。

#### [0108]

また、本実施形態においては画素トランジスタSWがボトムゲート型のトランジスタである場合について説明したが、本実施形態は、図11に示すようにトップゲート型のトランジスタに適用されても構わない。なお、ソース電極SE及びドレイン電極DEの間にフローティングメタルFMが配置されている点以外は、前述した図8と同様であるため、ここではその詳しい説明を省略する。

## [0109]

以上に述べた少なくとも 1 つの実施形態によれば、チャネル領域における発熱による異常を抑制することが可能な表示装置及びトランジスタを提供することにある。

# [0110]

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれると同様に、特許請求の範囲に記載された発明とその均等の範囲に含まれるものである。

# 【符号の説明】

## [0111]

1 …表示パネル、2 … フレキシブル配線基板、3 … I C チップ、1 1 , 2 1 …基材、1 2 ~ 1 6 … 絶縁膜、2 2 … 電気泳動素子、3 0 …マイクロカプセル、3 1 …分散媒、3 2 … 黒色粒子、3 3 …白色粒子、1 0 0 …容量電極、2 0 1 …第 1 ゲート電極部、2 0 2 … 第 2 ゲート電極部、D S P …表示装置、S U B 1 …第 1 基板、S U B 2 …第 2 基板、G D 1 ,G D 2 …ゲートドライバ、S D … ソースドライバ、D A …表示領域(画素部)、N D A …非表示領域(周辺部)、S C …半導体層、G E 1 ,G E 2 …ゲート電極、S E … ソース電極、D E …ドレイン電極、S W … 画素トランジスタ、P X … 画素、P E … 画素電極、F M … フローティングメタル(メタル部材)。

10

20

30

40

-GD2

NDA

SUB1

# 【図面】

# 【図1】

Z DA DSP

Y DA SUB2

SD

# 【図2】

【図3】

# 【図4】

40

10

20

30

# 【図5】

図 5

# 【図6】

図 6

10

# 【図7】

図 7

# 【図8】

20

30

# 【図9】

# 【図10】

10

20

30

# 【図11】

# 【図12】

# フロントページの続き

(51)国際特許分類

FΙ

G 0 2 F 1/167

(56)参考文献 特開2000-036599(JP,A)

特開平11-186561(JP,A) 特開2002-189427(JP,A)

特開2003-308027(JP,A)

(58)調査した分野 (Int.Cl., DB名)

H01L 29/786 H01L 21/336 G09F 9/30 G02F 1/167