## (19) 대한민국특허청(KR)

## (12) 등록특허공보(B1)

(51) 국제특허분류(Int. Cl.)

H01L 23/495 (2006.01) H01L 21/48 (2006.01) H01L 21/56 (2006.01) H01L 21/77 (2017.01) H01L 23/00 (2006.01)

(52) CPC특허분류 *H01L 23/495* (2013.01) *H01L 21/4821* (2013.01)

(21) 출원번호 10-2015-7008983

(22) 출원일자(국제) **2013년09월05일** 심사청구일자 **2018년08월17일**

(85) 번역문제출일자 **2015년04월07일**

(65) 공개번호 **10-2015-0079592**

(43) 공개일자2015년07월08일

(86) 국제출원번호 PCT/IB2013/002685

(87) 국제공개번호 **WO 2014/037815** 국제공개일자 **2014년03월13일**

(30) 우선권주장

61/698,199 2012년09월07일 미국(US)

(56) 선행기술조사문헌

JP2010056441 A\*

KR100437436 B1\*

KR1020070007151 A\*

US07405468 B2\*

\*는 심사관에 의하여 인용된 문헌

(45) 공고일자 2020년06월23일

(11) 등록번호 10-2126009

(24) 등록일자 2020년06월17일

(73) 특허권자

#### 이오플렉스 리미티드

중국 홍콩 노스 포인트 일렉트릭 로드 148 9/ 에프. 유닛 902

(72) 발명자

#### 로그렌 필립 이.

미국 95134 캘리포니아주 샌 호제 엔. 퍼스트 스 트릿 2950

(74) 대리인

유미특허법인

전체 청구항 수 : 총 22 항

심사관 : 정구원

## (54) 발명의 명칭 **인쇄 형태의 단자 패드를 갖는 리드 캐리어**

#### (57) 요 약

리드 캐리어는 집적회로칩을 포함하고 있는 패키지로서 제조하는 동안 이러한 집적회로칩 및 관련 리드를 위한 지지를 제공한다. 리드 캐리어는 복수의 패키지 사이트를 갖는 임시 지지 부재를 포함한다. 각각의 패키지 사이트는 다이 부착 영역을 둘러싸는 복수의 단자 패드를 포함한다. 패드는 소결된 전기 도전성 재료로 형성된다. 칩은 다이 부착 영역에 배치되고, 와이어 본드가 칩에서부터 단자 패드까지 연장한다. 패드, 칩 및 와이어 본드모두가 몰드 컴파운드 내에 인캡슐레이션된다. 임시 지지 부재는 박리될 수 있고, 그리고나서 개별 패키지 사이트는 전자 시스템 기판 내의 탑재를 위한 복수의 표면 마운트 조인트를 포함하는 완성된 패키지를 제공하기 위해 서로 고립될 수 있다. 패드의 에지는 패드로 하여금 패키지 내의 패드를 안전하게 유지하기 위해 몰드 컴파운드와 결합하도록 하기 위한 윤곽으로 된다.

#### 대 표 도 - 도9

## (52) CPC특허분류

**H01L 21/568** (2013.01)

**H01L 21/77** (2013.01)

**H01L 23/49541** (2013.01)

**H01L 23/49548** (2013.01)

**H01L 24/97** (2013.01)

H01L 2224/48091 (2013.01)

H01L 2224/48247 (2013.01)

H01L 2924/18165 (2013.01)

### 명세서

## 청구범위

#### 청구항 1

전기 도전성 재료로 형성되며, 각각의 단자 패드가 하면 반대쪽의 상면을 갖고 상기 상면과 상기 하면 사이에에지를 가지며, 상기 단자 패드의 하면은 하부 평면을 포함하고, 각각의 단자 패드는 전기 도전성 재료의 소결구조물(sintered structure)인, 복수의 단자 패드;

상부 표면 반대쪽에 베이스를 갖는 반도체; 및

하나 이상의 상기 단자 패드와 상기 반도체 사이의 와이어 본드

를 포함하며,

상기 단자 패드, 상기 반도체, 및 상기 와이어 본드가 전기적 비도전성 재료 내에서 적어도 부분적으로 인캡슐레이션되며,

상기 각각의 단자 패드의 상기 하부 평면 전체와 상기 반도체의 상기 베이스는 각각 공통 평면 내에 위치되는, 리드 캐리어와 반도체 조합.

#### 청구항 2

제1항에 있어서,

상기 복수의 단자 패드의 하나 이상은, 적어도 일부분이 상기 전기적 비도전성 재료에 대해 상기 패드를 유지하기 위한 윤곽으로 되는 윤곽 형성된 에지(contoured edge)를 갖는, 리드 캐리어와 반도체 조합.

## 청구항 3

제2항에 있어서,

상기 윤곽 형성된 에지는 하부 연장부(lower extent) 반대쪽의 상부 연장부(upper extent)를 가지며, 상기 하부 연장부로부터 이격된 상기 윤곽 형성된 에지의 적어도 제1 부분이 상기 제1 부분보다 상기 하부 연장부에 더 가까운 상기 에지의 제2 부분보다 더 큰 측면 패드 폭을 형성하며, 이로써 상기 제1 부분이 상기 제2 부분을 돌출 (overhang)하는, 리드 캐리어와 반도체 조합.

#### 청구항 4

제3항에 있어서,

상기 윤곽 형성된 에지는 계단형 윤곽(stepped contour)을 가지며, 상기 계단 위에 있고 상기 에지의 상기 상부 연장부에 더 근접한 부분이 상기 계단 아래에 있고 상기 윤곽 형성된 에지의 상기 하부 연장부에 더 근접한 상 기 에지의 부분에 대하여 오버행을 형성하는, 리드 캐리어와 반도체 조합.

#### 청구항 5

제3항에 있어서,

상기 윤곽 형성된 에지는, 상기 하부 연장부로부터 가장 먼 상기 윤곽 형성된 에지의 부분이 상기 하부 연장부에 더 근접한 상기 윤곽 형성된 에지의 부분을 돌출하는, 테이퍼(taper)를 보이고 있는, 리드 캐리어와 반도체조합.

## 청구항 6

제1항에 있어서.

상기 반도체 및 상기 복수의 단자 패드는, 상기 반도체의 상기 베이스와 상기 단자 패드의 상기 하면을 제외하

고는, 상기 전기적 비도전성 재료 내에 각각 전체적으로 인캡슐레이션되는, 리드 캐리어와 반도체 조합.

#### 청구항 7

제1항에 있어서,

상기 복수의 단자 패드, 상기 반도체, 및 상기 와이어 본드는 패키지를 형성하며, 상기 패키지는 공통의 상기 전기적 비도전성 재료 내에 인캡슐레이션된 복수의 패키지 중의 하나인, 리드 캐리어와 반도체 조합.

#### 청구항 8

제7항에 있어서,

상기 복수의 패키지는 상기 단자 패드를 형성하는 상기 전기 도전성 재료의 소결 온도보다 높은 용융점을 갖는 공통의 가요성 지지 층 상에 각각 위치되는, 리드 캐리어와 반도체 조합.

### 청구항 9

제8항에 있어서,

상기 반도체의 상기 베이스와 상기 공통의 가요성 지지 층 사이에 접착제가 위치되는, 리드 캐리어와 반도체 조합.

## 청구항 10

복수의 입력, 복수의 출력, 또는 복수의 입력과 복수의 출력을 갖는 전자 소자를 지지하기 위한 리드 캐리어에 있어서,

서로 이격되어 있고 다이 부착 영역에 인접해 있는 복수의 전기 도전성 단자 패드를 포함하고,

상기 단자 패드는 소결된 전기 도전성 재료로 형성되고, 각각의 단자 패드는 하부 평면 반대쪽의 상면을 가지며, 상기 단자 패드는 상기 단자 패드를 형성하는 상기 재료의 소결 온도보다 높은 용융점을 갖는 임시 층 상에 위치되고, 상기 임시 층은 각각의 단자 패드의 상기 하부 평면 전체와 반도체의 베이스가 각각 공통 평면 내에 위치되도록 상기 반도체를 상기 임시 층 위에 부착하도록 구성되는.

리드 캐리어.

## 청구항 11

제10항에 있어서,

상기 단자 패드는 상기 다이 부착 영역 중의 하나를 둘러싸는, 리드 캐리어.

#### 청구항 12

제10항에 있어서,

상기 복수의 전기 도전성 단자 패드의 하나 이상은 하부 연장부 반대쪽의 상부 연장부를 갖는 에지를 가지며, 상기 하부 연장부가 상기 임시 층에 인접하며, 상기 하부 연장부로부터 이격된 상기 에지의 적어도 제1 부분이 상기 제1 부분보다 상기 에지의 상기 하부 연장부에 더 가까운 상기 에지의 제2 부분보다 더 큰 측면 패드 폭을 형성하며, 이로써 상기 제1 부분이 상기 제2 부분을 돌출하는, 리드 캐리어.

### 청구항 13

제12항에 있어서,

상기 에지는 계단형 윤곽을 가지며, 상기 계단 위에 있고 상기 에지의 상기 상부 연장부에 더 근접한 부분이 상기 계단 아래에 있고 상기 에지의 상기 하부 연장부에 더 근접한 상기 에지의 부분에 대하여 오버행을 형성하는, 리드 캐리어.

## 청구항 14

제12항에 있어서,

상기 에지는, 상기 하부 연장부로부터 가장 먼 상기 에지의 부분이 상기 하부 연장부에 더 근접한 상기 에지의 부분을 돌출하는, 테이퍼(taper)를 보이고 있는, 리드 캐리어.

#### 청구항 15

제10항에 있어서,

상기 반도체는, 상기 반도체로부터 상기 다이 부착 영역에 인접한 복수의 상기 전기 도전성 단자 패드까지 연장되는 복수의 와이어 본드로 상기 다이 부착 영역 각각에 위치되며,

상기 단자 패드, 상기 와이어 본드, 및 상기 반도체는 전기적 비도전성 재료로 적어도 부분적으로 인캡슐레이션 되는, 리드 캐리어.

#### 청구항 16

제15항에 있어서,

상기 전기적 비도전성 재료의 층은, 상기 임시 층을 바라보고 있는 상기 반도체 및 상기 단자 패드의 일부분 이외의, 그 모든 측면 상의 상기 복수의 전기 도전성 단자 패드 및 상기 반도체를 인캡슐레이션하는, 리드캐리어.

#### 청구항 17

제16항에 있어서,

상기 임시 층은 상기 단자 패드, 상기 반도체의 상기 베이스, 및 인캡슐레이션하고 있는 상기 비도전성 재료층 으로부터의 박리 제거(peeling removal)를 허용하기에 충분하게 가요성을 갖는, 리드 캐리어.

### 청구항 18

복수의 집적회로칩을 포함하는 패키지를 형성하는 방법에 있어서,

상면을 갖는 임시 층을 제공하는 단계;

상기 임시 층의 상면 상에 전기 도전성 단자 패드들을 배치하는 단계 - 각각의 단자 패드는 하면 반대쪽의 상면을 가지고 상기 하면은 하부 평면을 포함함-;

상면 반대쪽에 베이스를 갖는 집적회로를 상기 상면 상에 위치시키는 단계;

상기 단자 패드와 각각의 상기 집적회로 사이에 와이어 본드를 부착하는 단계;

상기 단자 패드, 상기 와이어 본드, 및 상기 집적회로를 전기적 비도전성 재료 내에 인캡슐레이션하는 단계; 및 상기 임시 층을 제거하여, 상기 단자 패드의 하부 평면들 전체와 상기 집적회로의 베이스가 공통 평면에 노출되 게 하는 단계를 포함하고,

상기 배치하는 단계는, 상기 임시 층의 상면 상에 임시 형태 재료(temporary form material)를 배치하는 단계, 상기 임시 형태 재료에 보이드를 제공하는 단계, 상기 보이드를 전기 도전성 금속 파우더 및 바인딩 액체 (binding liquid)를 포함하는 유동성 재료(flowable material)로 채우는 단계, 상기 유동성 재료를 상기 바인 당 액체가 휘발되고 제거되게 하는 온도로 가열하는 단계, 상기 임시 형태 재료를 휘발되고 가열되게 하는 단계, 및 상기 임시 층의 용융점 아래로 유지하면서 상기 금속 파우더를 단자 패드로 소결하는 단계를 더 포함하는,

복수의 집적회로칩을 포함하는 패키지를 형성하는 방법.

## 청구항 19

제18항에 있어서,

상기 위치시키는 단계는, 상기 집적회로의 베이스와 상기 임시 층의 상면 사이에 접착제를 입히는 단계를 포함하는, 복수의 집적회로칩을 포함하는 패키지를 형성하는 방법.

## 청구항 20

제18항에 있어서,

복수의 집적회로를 포함하는 패키지를 개별 패키지로 싱귤레이션하는 단계를 더 포함하며, 각각의 패키지가 하나 이상의 집적회로칩, 복수의 단자 패드, 및 상기 단자 패드로부터 상기 집적회로칩까지 연장하는 와이어 본드를 가지며, 상기 와이어 본드와, 상기 집적회로 및 상기 단자 패드의 일부분이 전기적 비도전성 재료 내에 인캡슐레이션되는, 복수의 집적회로칩을 포함하는 패키지를 형성하는 방법.

#### 청구항 21

복수의 집적회로칩을 포함하는 패키지를 형성하는 방법에 있어서,

상면을 갖는 임시 층을 제공하는 단계;

상기 임시 층의 상면 상에 전기 도전성 단자 패드를 배치하는 단계;

상면 반대쪽에 베이스를 갖는 집적회로를 상기 상면 상에 위치시키는 단계;

상기 단자 패드와 각각의 상기 집적회로 사이에 와이어 본드를 부착하는 단계;

상기 단자 패드, 상기 와이어 본드, 및 상기 집적회로를 전기적 비도전성 재료 내에 인캡슐레이션하는 단계;

상기 임시 층을 제거하여, 상기 단자 패드의 하부 평면들 전체와 상기 집적회로의 베이스가 공통 평면에 노출되 게 하는 단계; 및

상기 배치하는 단계 후와 상기 부착하는 단계 전에, 상기 전기 도전성 단자 패드의 전기적 성능을 테스트하는 단계를 포함하는, 복수의 집적회로칩을 포함하는 패키지를 형성하는 방법.

### 청구항 22

복수의 집적회로칩을 포함하는 패키지를 형성하는 방법에 있어서,

상면을 갖는 임시 층을 제공하는 단계;

상기 임시 층의 상면 상에 전기 도전성 단자 패드를 배치하는 단계;

상면 반대쪽에 베이스를 갖는 집적회로를 상기 상면 상에 위치시키는 단계;

상기 단자 패드와 각각의 상기 집적회로 사이에 와이어 본드를 부착하는 단계;

상기 단자 패드, 상기 와이어 본드, 및 상기 집적회로를 전기적 비도전성 재료 내에 인캡슐레이션하는 단계;

상기 임시 층을 제거하여, 상기 단자 패드의 하부 평면들 전체와 상기 집적회로의 베이스가 공통 평면에 노출되 게 하는 단계; 및

상기 복수의 패키지를 개별 패키지로 싱귤레이션하기 전에, 상기 복수의 집적회로칩을 포함하는 패키지의 전기 적 성능을 테스트하는 단계를 포함하는, 복수의 집적회로칩을 포함하는 패키지를 형성하는 방법.

#### 청구항 23

삭제

## 발명의 설명

## 기술분야

[0001] 본 발명은 전기 시스템에서의 집접회로칩의 효과적인 상호접속을 위해 집적회로칩과 함께 사용하기 위한 리드 캐리어 기반의 패키지에 관한 것이다. 보다 구체적으로, 본 발명은 집적회로와의 조합, 와이어 본드의 부착, 및 비도전성 재료 내의 인캡슐레이션의 이전에 및 그 동안에, 인쇄회로 기판과 같은 전자 시스템 기판 상에서의 사용을 위한 개별 패키지로의 아이솔레이션 전에, 공통 어셈블리 내에서 복수의 패키지 사이트(package site)의 어레이로서 제조되는 리드 프레임 및 기타 리드 캐리어에 관한 것이다.

## 배경기술

[0002] 더 작고 더 성능이 좋은 휴대용 전자 시스템에 대한 요구는, 오늘날의 반도체에서의 증가된 집적 레벨과 조합되

어, 더 많은 개수의 입력/출력 단자를 갖는 더 작은 반도체 패키지에 대한 필요성을 야기하고 있다. 이와 동시에, 소비자 전자 시스템의 부품 모두의 비용을 감소시키려는 끊임없는 압박이 있다. 쿼드 플랫 노 리드(quad flat no lead, QFN) 반도체 패키지군은 그 중에서도 모든 반도체 패키징 타입 중 가장 작고 가장 비용 효율적이지만, 종래의 기술 및 재료로 제조될 때에는 커다란 한계를 갖는다. 예컨대, QFN 기술로는, 이 기술이 지원할수 있는 I/O 단자의 개수 및 전기적 성능이 제한된다.

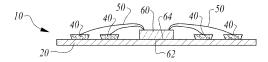

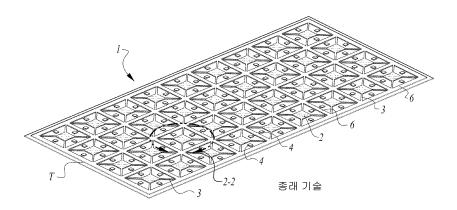

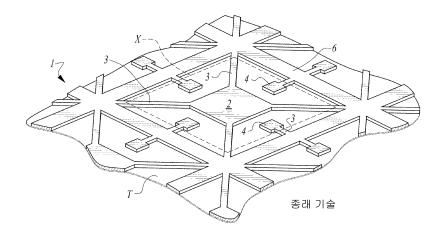

- [0003] QFN 패키지 P(도 5 내지 도 7)는 종래에는 구리 시트로부터 에칭된 영역 어레이 리드 프레임(1)(도 1 및 도 2) 상에 조립된다. 리드 프레임(1)은 수십 내지 수천개의 패키지 사이트를 포함할 수 있으며, 각각의 패키지 사이트는 와이어 본드 패드(4)(도 2, 도 5-7)의 하나 이상의 행(row)에 의해 둘러싸인 다이 부착 패드(2)(도 1, 도 2, 도 5-7)로 이루어진다. 이들 패키지 P 콤포넌트의 전부는, 본딩 및 솔더링 표면의 도금(plating)을 용이하게 하기 위해, 리드 프레임(1)의 나머지에 대한 패키지 P 콤포넌트의 위치를 유지하고 콤포넌트의 전부에 대한 전기 접속을 제공하기 위해 구리 피스(piece of copper)에 의해 공통 프레임(1)에 부착된다.

- [0004] 타이 바(tie bar)(3)로서 흔히 알려진(도 1, 도 2, 도 5-7) 이들 연결된 구조물들은 리드 프레임(1)의 부품 전부를 함께 단락시킨다. 따라서, 이들 타이 바(3)는 개별 패키지 P의 싱귤레이션 동안 각각의 패키지 P를 둘러싸는 공통 단락 구조물(6)(도 1 및 도 2)로부터 접속해제될 수 있도록 설계되어야 하며, 이로써 각각의 다이 부착 패드(2)와 와이어 본드 패드(4)를 전기적으로 고립되게 한다. 통상적으로, 리드 프레임(1)에 대한 타이 바(3)의 전기 접속을 끊는 것을 용이하게 하기 위한 설계는 최종 패키지 P 풋프린트의 바로 외측의 각각의 패키지 P 싸이트를 둘러싸는 구리 단락 구조물(6)(도 1 및 도 2)에 타이 바(3)를 연결하는 것을 포함한다. 이 단락 구조물(6)은 싱귤레이션 프로세스 동안 소잉(sawing)되어, 타이 바(3)가 패키지 P의 에지에서 노출되게 된다.

- [0005] QFN 리드 프레임(1)은 패키지 P 내의 집적회로칩(7)(도 5-7)과 같은 반도체 다이를 고정하는 것을 용이하게 하는 패키지 P의 부분과, 와이어 본드(8)(도 5, 도 6)를 통해 집적회로(7)에 연결될 수 있는 단자를 제공한다. 와이어 본드 패드(4) 형태의 단자 또한 와이어 본드(8) 표면의 반대 표면 상의 솔더 조인트(5)(도 5-7)를 통해 전자 시스템 기판(인쇄회로 기판과 같은)에 연결하는 수단을 제공한다.

- [0006] 패키지 P 콤포넌트의 전부가 금속 구조물에 의해 리드 프레임(1)에 연결되어야 하는 조건은 임의의 소정의 패키지 P 아웃라인에서 구현될 수 있는 리드의 개수를 크게 제한한다. 예컨대, 와이어 본드 패드(4)가 다이 부착 패드(2)를 둘러싸는 복수의 행으로 제공될 수 있고, 각각의 행이 다이 부착 패드(2)로부터 상이한 거리로 떨어져 있다. 와이어 본드 패드(4)의 최외각 행 내부의 임의의 와이어 본드 패드(4)에 대해, 구조물들을 연결하는 타이 바(3)는 외측 행의 패드(4)들 사이에 라우트(route)되어야 하고, 이로써 이러한 타이 바(3)가 패키지 P 아이솔레이션의 바깥쪽의 공통 단락 구조물(6)까지 연장할 수 있게 된다. 이들 타이 바(3)의 최소 스케일은 단지하나가 2개의 인접 패드(4)들 사이에 라우팅될 수 있도록 된다. 그러므로, 패드(4)들의 단지 2개의 행이 표준 QFN 리드 프레임(1)에서 구현될 수 있다. 다이 크기와 리드 카운트 간의 현재의 관계 때문에, 표준 QFN 패키지는 대략 100개의 단자로 제한되고, 패키지 P의 대부분이 겨우 대략 60개의 단자를 갖는다. 이러한 제한은 더작은 크기 및 더 낮은 비용의 QFN 기술로부터 이득을 얻을 다수의 타입의 다이에 의한 QFN 패키징의 사용을 배제한다.

- [0007] 종래의 QFN 기술이 매우 비용이 저렴하지만, 아직도 비용을 추가로 감소시킬 기회는 있다. 집적회로칩(7)이 와이 본드(8)로 외부 리드 와이어 본드 패드(4)에 부착되고 연결된 후, 복수의 패키지 P의 조립된 리드 프레임(1)은 트랜스퍼 몰딩 프로세스(transfer molding process)에서와 같이 에폭시 몰드 컴파운드(9)(도 6, 도 7)로 완전히 인캡슐레이션된다. 리드 프레임(1)이 대체로 앞에서 뒤로(front to back) 개방되기 때문에, 몰딩 동안 각각의 패키지 P의 배면(back plane)을 규정하기 위해 조립 공정 전에 리드 프레임(1)의 뒤쪽에 고온 테이프(T)의 층이 가해진다. 이 테이프(T)가 고온 프로세스로부터의 부작용 없이 고온 본딩 및 몰딩 프로세스를 견뎌 약만 하기 때문에, 테이프는 비교적 고가이다. 테이프 T를 적용하고, 테이프(T)를 제거하고, 접착제 잔여물을 제거하는 프로세스는 각각의 리드 프레임(1)을 처리하는데 비용을 크게 증가시킬 수 있다.

- [0008] 리드 프레임(1)으로부터의 개별 패키지 P의 싱귤레이션의 가장 보편적인 방법은 소잉(sawing)(도 2의 라인 X를 따른)에 의한 것이다. 에폭시 몰드 컴파운드(9)를 절단하는 것에 부가하여, 소잉이 패키지 P 아웃라인 바로 외측의 단락 구조물(6)의 전부를 제거하여야 하기 때문에, 이 프로세는 상당히 느려지고, 몰드 컴파운드(9)만이 절단되는 경우에도 블레이드 수명을 현저하게 단축시킨다. 단락 구조물(6)이 싱귤레이션 프로세스까지는 제거되지 않기 때문에, 이것은 다이가 싱귤레이션이 이루어진 때까지는 테스트될 수 없다는 것을 의미한다. 아주작은 수천의 패키지 P를 핸들링하고 각각이 정확한 배향으로 테스터에 제공되도록 하는 것은 알려진 사이트에 있는 각각의 패키지 P를 갖는 전체 스트립을 테스트하는 것보다 훨씬 더 많은 비용이 든다.

- [0009] 편치 싱귤레이션(punch singulation)으로서 알려진 리드 프레임(1) 기반 프로세스는 소우 싱귤레이션(saw singulation)과 연관된 문제점을 어느 정도까지는 해소하고, 리드 프레임(1) 스트립에서의 테스팅을 허용하지만, 실질적으로는 리드 프레임(1)의 절단 이용에 의한 비용을 소우 싱귤레이션된 리드 프레임(1)의 비용의 50퍼센트 미만까지로 증가시킨다. 편치 싱귤레이션은 또한 모든 기본 리드 프레임 설계에 대해 전용의 몰드 툴링의 조건을 부과한다. 소우 싱귤레이션을 위해 설계된 표준 리드 프레임(1)은 동일한 치수의 모든 리드 프레임(1)에 대해 단일의 몰드 캡을 이용한다.

- [0010] 소우 싱귤레이션된 패키지 P와 편치 싱귤레이션된 패키지 P 둘 모두에서, 타이 바(3)는 완성된 패키지에 남겨지 게 되고, 제거될 수 없는 용량성 및 유도성 기생 성분(capacitive and inductive parasitic elements) 둘 모두를 나타낸다. 이제는 불필요한 이들 피스의 금속(these now superfluous pieces of metal)은 완성된 패키지 P의 성능에 크게 영향주어, 다수의 고성능 집적회로칩(7) 및 어플리케이션을 위한 QFN 패키지 P의 사용을 불가능하게 한다. 더욱이, 이러한 잠재적으로 보다 가치가 있는 불필요한 금속의 비용은 상당할 수 있으며, QFN 프로세스에 의해 낭비된다.

- [0011] 에칭된 리드 프레임의 제한을 제거하는 QFN 타입 기판을 위해 여러 가지의 개념이 진전을 보였다. 이들 중의하나는 전기도금에 의해 희생 캐리어(sacrificial carrier) 상에 패키지 콤포넌트의 어레이를 침적하는 프로세스이다. 캐리어는 먼저 도금 레지스트로 패터닝되며, 대개는 스테인레스강인 캐리어는 접착력(adhesion)을 증 강시키기 위해 약하게 에칭된다. 그리고나서, 스트립이 접착/배리어 층을 생성하기 위해 금 및 팔라듐으로 도금되고, 그리고나서 대략 60 미크론 두께로 Ni로 도금된다. Ni 범프의 상단부는 와이어 본딩을 용이하게 하기위해 전기도금된 Ag의 층으로 마무리된다. 스트립이 조립되고 몰딩된 후, 캐리어 스트립은 시트로 테스트되고 종래의 리드 프레임보다 높은 속도 및 수율로 싱귤레이션될 수 있는 패키징된 다이의 시트를 남기도록 박리된다 (peeled away). 이 전기도금 방법은 패키지 내의 연결 금속 구조물(connective metal structure)에 연관된 문제점의 전부를 제거하고, 매우 미세한 특징부를 가능하게 한다. 그러나, 도금 프로세스는 표준 에칭 리드 프레임에 비하여 매우 비용이 많이드는 스트립을 발생한다.

- [0012] 또 다른 방법은 에칭된 리드 프레임 프로세스를 수정한 것이며, 여기서 전면측 패턴은 리드 프레임의 두께의 약절반으로 에칭되고, 리드 프레임 스트립의 배면은 몰딩 프로세스가 완료된 후까지는 온전한 상태로 남겨지게 된다. 몰딩이 완료된 때에, 배면 패턴이 인쇄되고, 리드 프레임은 와이어 본드 패드 및 다이 패들(die paddle)의 배면 일부분을 제외한 금속의 전부를 제거하기 위해 에칭된다. 이 이중 에칭 프로세스는 패키지 내의 연결 금속 구조물과 연관된 모든 문제점을 제거한다. 이중 에칭된 리드 프레임의 가격은 전기도금된 버전보다 적지만, 표준 에칭된 리드 프레임보다는 여전히 고가이며, 에칭 및 도금 프로세스가 환경적인 면에서 바람직하지 않다. 리드 프레임 패키징된 집적회로의 한 가지 고장 모드는, 특히 패키지에 의해 충격 부하(shock load)를 경험하게 되는 때에(그 안에 패키지를 통합하고 있는 전자 디바이스가 떨어져서 단단한 표면에 부딪히는 때와 같은), 와이어 본드 패드(4)가 와이어 본드 패드에 연결된 와이어 본드(8)와 연결해제되는 것이다. 와이어 본드 패드(4)는 주변의 에폭시 몰드 컴파운드로부터 약간 분리되면서 인쇄회로 기판 또는 기타 전자 시스템 기판에 탑재된 채로 유지될 수 있으며, 이것은 와이어 본드(8)가 와이어 본드 패드(4)로부터 끊어지게 한다. 이에 따라서, 특히 충격 부하를 경험하게 되는 때에 전체 패키지 내의 와이어 본드 패드(4)를 더 우수하게 유지하는 리드 캐리어 패키지에 대한 추가의 필요성이 존재한다.

### 발명의 내용

### 해결하려는 과제

- [0013] 본 발명의 목적은 다양한 상이한 제조 단계에서의 테스트를 용이하게 하고 재료 낭비의 방지를 용이하게 하기 위해 임의의 2개의 패드들 간의 전기 접속이 없는 상태로 패드를 갖는 복수의 반도체 패키지의 연속적인 스트립을 발생하기 위하여 몰딩 후에 박리될 수 있는 희생 캐리어 상에 배열된 반도체 패키지의 전기적 인터커넥트 부품을 제공하는 시스템 및 방법을 제공하는 것이다.

- [0014] 본 발명의 다른 목적은 전자 시스템의 시스템 기판에 대한 반도체 다이의 전기 접속을 용이하게 하기 위해 그 안에서 최소량의 금속을 사용하면서 더 높은 전기적 성능을 가능하게 하는 방식으로 반도체 패키지의 전기적 인터커넥트 부품을 제공하는 것이다.

- [0015] 본 발명의 또 다른 목적은 표준 QFN 조립 공정의 단계들을 간략화하고 제거함으로써 패키지의 조립 비용을 낮추는 반도체 패키지의 전기적 인터커넥트 부품을 제공하는 것이다.

- [0016] 본 발명의 또 다른 목적은 종래 기술의 리드 프레임 기반 QFN 패키지로 실시되는 것보다 수배의 입력/출력 단자의 개수 및 입력/출력 단자의 2개 이상의 행의 포함을 허용하는 반도체 패키지의 전기적 인터커넥트 부품을 제공하는 것이다.

- [0017] 본 발명의 또 다른 목적은 리드 프레임 기반 QFN 기술에 비교할 때 복수의 전원 및 그라운드 구조물 및 복수의 다이 부착 영역과 같은 특징부를 통합하기 위한 더 큰 설계 가요성을 허용하는 반도체 패키지의 전기적 인터커 넥트 부품을 제공하는 것이다.

- [0018] 본 발명의 또 다른 목적은 저비용의 고품질 방식으로 제조될 수 있는 복수의 집적회로 탑재 패키지 사이트를 갖는 리드 캐리어를 제공하는 것이다.

- [0019] 본 발명의 또 다른 목적은 반도체 패키지에 대한 충격 부하에 연관된 손상에 대해 커다란 저항성을 나타내는 인 접한 부품에의 전기적 상호접속을 위한 반도체 패키지를 제공하는 것이다.

- [0020] 본 발명의 또 다른 목적은 과잉의 전도 부분을 최소화함으로써 전기적으로 높은 성능을 나타내는 복수의 집적회로 탑재 패키지 사이트를 갖는 리드 캐리어를 제공하는 것이다.

- [0021] 본 발명의 또 다른 목적은 간략하고 자동화된 양상으로 제조 공정에서의 복수의 단계에서 테스트될 수 있는 패키지 사이트를 갖는 리드 캐리어를 제공하는 것이다.

- [0022] 본 발명의 또 다른 목적은 반도체 조립 공정 동안 반도체 소자를 탑재하고 유지하기 위한 별도의 구조물을 요구하지 않는 QFN 또는 랜드 그리드 어레이 타입 패키지를 제조하기 위한 수단(vehicle)을 제공하는 것이다.

- [0023] 산업상 이용가능성을 입증하는 본 발명의 다른 추가의 목적은 본 명세서에 포함된 상세한 설명의 면밀한 이해, 첨부된 도면의 검토, 및 본 명세서에 포함된 청구항의 검토로부터 명백하게 될 것이다.

#### 과제의 해결 수단

- [0024] 본 발명에서는, 멀티-패키지 리드 캐리어의 형태로 별도의 패키지 사이트의 어레이를 갖는 리드 캐리어가 제공된다. 통상적으로 실버 파우더로서 시작되는 소결 재료(sintered material)가 스테인레스강과 같은 고온 저항성 재료로 형성된 임시 층(temporary layer) 상에 위치된다. 임시 층을 형성하는 스테인레스강 또는 기타 재료는 소결 온도로 가열되는 동안 소결 재료를 지지한다.

- [0025] 소결 재료는 바람직하게는 단자 패드의 형태로 서로 전기적으로 고립된(임시 층을 통해서가 아닌) 별도의 구조물에서 임시 층 상에 위치된다. 본 발명은 반도체 소자가 임시로 임시 층에 배치되거나 또는 고착(접차제를 이용하는 등으로)될 수 있기 때문에 특히 반도체 소자를 수용하고 유지하기 위한 목적으로 구조물이 임시 층 상에 제공되어야 하는 조건을 방지한다. 따라서, 본 발명은 다이 부착 패드가 아닌 다이 부착 영역을 제공하도록 설계된다. 각각의 다이 부착 영역에 하나 이상의 단자 패드가 연관된다. 각각의 다이 부착 영역은 집적회로 또는 기타 반도체 소자가 그 위에 지지되도록 구성된다. 와이어 본드는 다이 부착 영역 상의 집적회로에서부터 각각의 다이 부착 영역을 둘러싸는 별도의 단자 패드까지 라우팅될 수 있다. 그리고나서, 집적회로, 단자 패드 및 와이어 본드를 인캡슐레이션하는 몰드 컴파운드가 가해질 수 있다. 집적회로 및 단자 패드의 일부분 아래에 형성되어 있는 표면 마운트 조인트는 임시 층에 인접하여 있기 때문에 이들만이 인캡슐레이션되지 않은 채로 유지된다.

- [0026] 몰드 컴파운드가 경화된 때에, 임시 층이 리드 캐리어의 나머지 부분으로부터 박리될 수 있으며, 이로써 개별 다이 부착 영역 및 관련된 집적회로와, 단자 패드와, 와이어 본드 모두가 공통의 몰드 컴파운드 내에 임베디드되는 복수의 패키지가 남겨지게 된다. 그리고나서, 개별 패키지 사이트는 패키지 사이트들 사이의 경계와 표면마운트 조인트를 통해 전자 시스템 기판 또는 기타 지지체에 탑재된 표면을 따라 절단함으로써 서로 절단될 수 있다.

- [0027] 패키지 사이트 및 패키지 사이트 내의 개별 패드가 임시 충을 통해서가 아니라 각각 서로 전기적으로 고립되어 있기 때문에, 이들 개별 패드는 집적회로의 탑재 이전 또는 몰드 컴파운드 내의 인캡슐레이션 및 임시 충의 제거 후이지만 별도의 패키지로의 싱귤레이션 이전과 같은 다양한 상이한 시간에 전기적 연속성(electrical continuity) 및 기타 전기적 성능 특성에 대해 테스트될 수 있다. 이러한 테스팅은 패드의 어레이가 임시 충상에 지지되고 있는 동안 또는 임시 충으로부터 제거된 후에 발생할 수 있다. 더욱이, 이러한 패키지는 QFN 패키지와 함께 이용되는 공지의 테스팅 장치 또는 기타 테스팅 장치를 이용하여 리드 캐리어 상의 인접한 패키지로부터의 고립 후에 테스팅될 수 있다.

[0028] 이에 부가하여, 각각의 패드는 어느 정도는 몰드 컴파운드와 기계적으로 결합하도록 구성되는 에지를 각각의 패드의 둘레부(periphery) 주위에 갖는 것이 바람직하다. 구체적으로, 이들 에지는 오버행잉 모양(overhanging fashion)으로 테이퍼되거나, 오버행잉 모양으로 계단형으로 되거나(be stepped in an overhanging fashion), 또는 바닥부로부터 이격된 각각의 에지의 부분이 각각의 에지의 바닥부에 더 근접한 각각의 에지의 부분보다 더 측방으로 연장하도록 구성될 수 있다. 그러므로, 몰드 컴파운드는, 경화된 후에, 패드를 몰드 컴파운드 내에 확고하게 고정(lock)한다. 이러한 방식으로, 패드는 와이어 본드로부터의 이탈에 대해 저항력을 갖게 되고, 그 렇지 않은 경우에는 몰드 컴파운드로부터 이탈되게 되며, 전체 패키지를 하나의 단일체 패키지(single unitary package)로서 유지한다.

## 도면의 간단한 설명

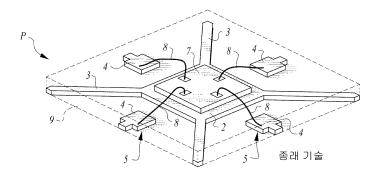

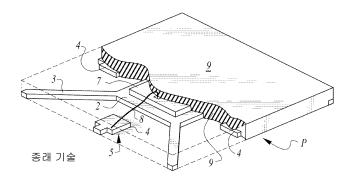

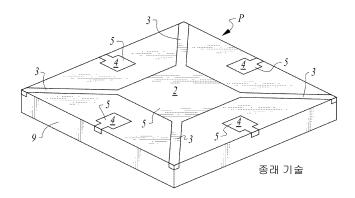

[0029] 도 1은 종래의 리드 프레임 기술을 예시하는 간략화된 다양한 구성의 QFN 리드 프레임의 사시도이다.

도 2는 리드 프레임으로부터 개별 패키지 사이트를 분리하기 위해 절단 라인이 따라야 하는 곳을 파선으로 나타내고 있는 도 1에 도시되어 있는 리드 프레임의 상세를 보여주는 사시도이다.

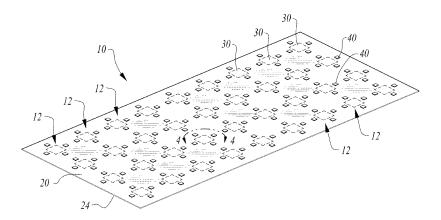

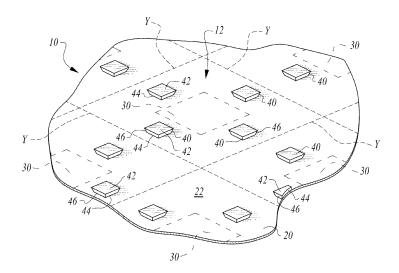

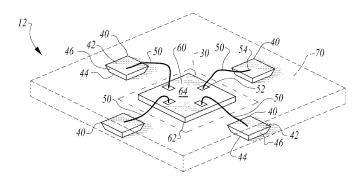

도 3은 그 위에 복수의 별도의 패키지 사이트를 갖고 임시 지지 부재 상에 탑재되는 본 발명에 따른 리드 캐리어의 사시도이다.

도 4는 도 3에 되시되어 있는 리드 캐리어의 일부분의 상세를 보여주는 사시도로, 집적회로칩의 탑재, 와이어 본드의 부착, 및 몰드 컴파운드 내에의 인캡슐레이션 전의 각각의 패키지 사이트의 상세를 예시하고 있다.

도 5는 집적회로칩 및 와이어 본드의 배치를 보여주고 인캡슐레이션 재료를 패키지 내의 다른 도전성 구조물에 관련하여 위치시키는 방법을 파선으로 예시하는 종래 기술의 QFN 패키지의 사시도이다.

도 6은 도 5에 도시되어 있는 것과 유사하지만 인캡슐레이팅 몰드 컴파운드가 제위치에 있고 패키지의 내부 구조물을 드러내기 위해 인캡슐레이팅 몰드 컴파운드의 일부분이 절단되어 있는 사시도이다.

도 7은 도 6에 도시되어 있는 것과 유사하지만 전자 시스템 기판 상에의 패키지의 표면 탑재에 이용할 수 있는 솔더 조인트 및 전기 시스템 내의 기타 인터페이스를 예시하기 위해 아래에서 본 사시도이다.

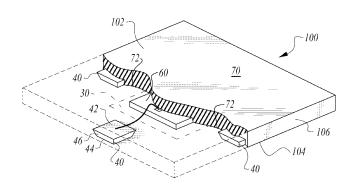

도 8은 집적회로칩 및 와이어 본드의 배치 후의 본 발명의 리드 캐리어 상의 개별 패키지 사이트를 보여주고 몰 드 컴파운드의 위치를 파선으로 예시하는 사시도이다.

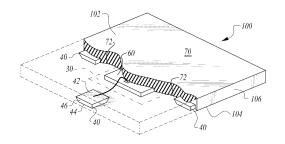

도 9는 도 8과 유사하지만 패키지 내의 도전성 구조물을 인캡슐레이션하는 몰드 컴파운드를 제위치에 도시하고 있고 몰드 컴파운드의 일부분이 패키지의 내부 상세를 보여주기 위해 절단되어 있는 사시도이다.

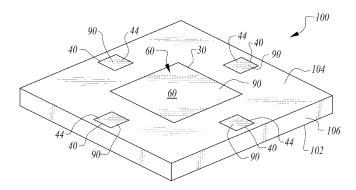

도 10은 본 발명에 따른 패키지를 아래로부터 본 도면으로, 패키지의 표면 마운트 조인트를 예시하는 사시도이다.

도 11 내지 도 17은 본 발명에 따른 반도체 지지 패키지를 제조하는 공정 동안의 임시 지지 부재 및 리드 캐리어의 전체적인 단면도이다.

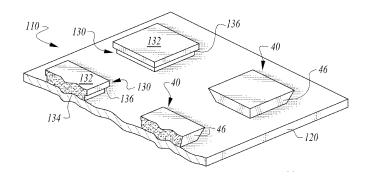

도 18은 둘러싸고 있는 인캡슐레이팅 몰드 컴파운드와의 상이한 결합 특성을 나타내기 위해 상이한 에지 윤곽을 갖는 것으로 예시된 대안의 패드를 갖는 대안의 리드 캐리어의 사시도이다.

### 발명을 실시하기 위한 구체적인 내용

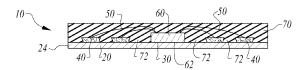

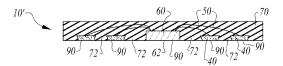

[0030] 동일한 도면 부호가 여러 도면에 걸쳐 동일한 부분을 나타내고 있는 도면을 참조하면, 도면 부호 10은 집적회로 칩(60)을 포함하고 집적회로칩(60)에 다수의 입력 및 출력을 제공하기 위한 복수의 패키지(100)(도 9, 도 10)를 제조하기 위한 임시 지지 부재(20) 상에서 그 위에 복수의 패키지 사이트(12)를 지지할 수 있는 리드 캐리어(도 3, 도 4)를 나타낸다. 본 발명은 또한 개별 패키지(100)의 제조 및 리드 캐리어(10)의 공통의 임시 지지 부재(20)로부터 패키지(100)의 제거 후의 복수의 패키지 사이트(12) 및 리드 캐리어(10')(도 17)로부터 고립된 복수의 결과 패키지(100)에 관한 것이다.

[0031] 본질적으로 그리고 도 3, 도 4, 도 8 및 도 9를 구체적으로 참조하여, 본 발명의 바람직한 실시예에 따른 리드 캐리어(10) 및 패키지(100)의 기본적인 상세를 설명한다. 리드 캐리어(10)는 스테인레스강과 같은 얇은 평면형의 고온 저항성 재료의 임시 지지 부재(20)를 포함한다. 패키지 사이트(12)에서의 임시 지지 부재(20) 상에 복수의 다이 부착 영역(30) 및 단자 패드(40)가 배열되며, 각각의 다이 부착 영역(30)을 복수의 단자 패드(40)가

둘러싸고 있다.

- [0032] 집적회로칩(60)은 다이 부착 영역(30)에 위치된다(도 8, 도 9). 와이어 본드(50)는 칩(60) 상의 입력 출력 단자와 단자 패드(40) 사이에 연결된다. 단자 패드(40), 와이어 본드(50) 및 칩(60)을 포함한 전체 패키지(100)가 패키지(100)의 하면(underside)을 형성하는 표면 마운트 조인트(90) 부분(도 10) 외에는 몰드 컴파운드(70)내에 인캡슐레이션된다. 몰드 컴파운드(70)는 통상적으로 각각의 패키지 사이트(12)를 둘러싸도록 리드 캐리어(10)에 가해진다. 각각의 패키지(100)의 추후의 고립은 원래의 리드 캐리어(10)로부터 복수의 패키지(100)를 제공하기 위해 몰드 컴파운드(70)의 절단에 의해 발생한다.

- [0033] 도 1 및 도 2를 참조하면, 본 발명의 리드 캐리어(10)의 상세와의 비교 및 대비를 위하여 다양한 "쿼드 플랫 노리드(QFN)"의 종래 기술의 리드 프레임(1)의 상세가 도시되어 있다. 도시된 실시예에서, QFN 리드 프레임(1)은 에칭된 도전성 재료의 평면형 구조물이다. 이 에칭된 도전성 재료는 별개의 다이 부착 패드(2) 및 와이어 본드 패드(4) 내로 에칭되고, 이들은 각각의 타이 바(3)를 통해 공통의 단락 구조물(6)에 연결된다. 이 전체 에칭된 QFN 리드 프레임(1)은 에폭시 몰드 컴파운드(9)가 리드 프레임(1)에 가해질 수 있고 패드(2, 4)를 인캡슐레이션 하도록 몰딩 테이프(T) 상에 탑재된다(도 5-7).

- [0034] 이러한 인캡슐레이션 전에, 칩(7)의 통합체가 다이 부착 패드(2) 상에 탑재된다. 와이어 본드 패드(4)와 칩(7) 상의 입력/출력 단자 사이에는 와이어 본드(8)가 위치된다. 몰드 컴파운드(9)는 그리고나서 칩(7) 및 와이어 본드(8)뿐만 아니라 패드(2, 4)를 전체적으로 인캡슐레이션할 수 있다. 몰드 컴파운드는 테이프(T)에 의해 패드(2, 4)의 하면을 인캡슐레이션하는 것이 방지된다. 몰드 컴파운드(9)가 경화된 후, 테이프(T)는 솔더 조인트(5)(도 7)가 리드 프레임(1)의 하면 상에 나타나도록 박리될 수 있다. 최종적으로, 별도의 QFN 패키지 P는 전체 리드 프레임(1)으로부터 각각의 패키지 P를 고립시키기 위해 절단(도 2의 절단 라인 X를 따른)에 의해 격리된다.

- [0035] 특히, 다이 부착 패드(2) 및 와이어 본드 패드(4)로부터 연장하는 타이 바(3)의 일부분이 패키지 P 내에 유지된다는 것에 유의하기 바란다. 이들 타이 바(3)의 몇몇 부분은 실제로 패키지 P의 에지이 외측으로 연장한다(도 6, 도 7). 더욱이, 공통의 단락 구조물(6)(도 1, 도 2)은 어떠한 패키지 P의 부분도 아니다. 그러므로, 공통단락 구조물(6)은 통상적으로 낭비된다. 더욱이, 각각의 패키지 P 내의 타이 바(3)의 나머지 부분은 어떠한 이로운 용도도 제공하지 못하며, 그러므로 역시 패키지 P 내에서 낭비된다. 이러한 타이 바(3) 잔류물은 또한 패키지 P 및 패키지 P 내의 칩(7)의 성능에 대한 악영향을 가질 수 있다. 예컨대, 패키지 P의 몰드 컴파운드(9)의 에지의 바깥으로 연장하는 타이 바(3)의 부분은 바람직하지 않은 단락 또는 전자기 간섭 및 "노이즈"의 가능성을 제공하며, 이로써 어떠한 전자 응용기기는 종래 기술의 QFN 패키지 P에 의해 원활하게 제공되지 않게된다. 이러한 종래 기술의 QFN 패키지가 적절한 때에도, 패키지 P 내에 임베디드된 공통의 단락 구조물(6) 및타이 바(3)에 연관된 낭비는 바람직하지 않다. 더욱이, 테이프(T)는 재사용 가능하지 않으며, 공지의 종래 기술의 QFN 리드 프레임(1) 및 패키지 P 기술을 이용하는 또 다른 낭비 비용이 된다.

- [0036] 도 3 및 도 4를 참조하면, 일례의 실시예에 따른, 임지 지지 부재(20)와 같은 임시 층 및 패드(40)뿐만 아니라 본 발명의 리드 캐리어(10)의 구체적인 세부구성이 설명되어 있다. 이 일례의 실시예는 각각의 패키지 사이트 (12)가 단지 각각의 다이 부착 영역(30)을 둘러싸는 4개의 단자 패드(40)를 보여주고 있다는 점에서 전형적인 바람직한 실시예에 비하여 상당히 간략화되어 있다. 전형적으로, 이러한 단자 패드(40)는 각각의 다이 부착 영역(30)을 둘러싸는 수십개 또는 가능하게는 수천개로 제공될 것이다. 이러한 단자 패드(40)는 전형적으로 다이 부착 영역(30)에 가장 근접한 최내측 행과, 다이 부착 영역(30)으로부터 가장 떨어져 있는 단자 패드(40)의 최외곽 행과, 단자 패드(40)의 최내측 행과 최외곽 행 사이의 복수의 중간 행을 포함한 복수의 행으로 제공될 것이다.

- [0037] 리드 캐리어(10)는, 복수의 패키지 사이트(12)를 포함하고, 이들의 제조 동안과 테스트 동안과 복수의 패키지 (100)(도 9, 도 10)의 최종적인 생산을 용이하게 하기 위해 집적회로칩(60)(또는 다이오드 또는 트랜지스터와 같은 기타 반도체 소자) 및 와이어 본드(50)(도 8, 도 9)와의 집적 동안 이들 패키지 사이트(12)를 지지하도록 제조되는 평면형 구조물이다. 리드 캐리어(10)는 임시 지지 부재(20)를 포함한다. 이 임시 지지 부재(20)는 가장 바람직하게는 스테인레스강인 고온 저항성 재료의 얇은 평면형 시트이다. 이 부재(20)는 리드 캐리어(10)의 다른 부분이 그 위에서 제조되는 상면(22)을 포함한다. 임지 지지 부재(20)의 에지는 임시 지지 부재(20)의 둘레를 형성한다. 이 일례의 실시예에서, 이 에지(24)는 전반적으로 직사각이다.

- [0038] 임시 지지 부재(20)는 어느 정도 가요성을 나타내고 패키지 사이트(12) 및 리드 캐리어(10)(도 8-10, 도 17)에 서의 패키지(100)의 완전한 제조 후에 리드 캐리어(10)로부터의 임지 지지 부재(20)의 박리 제거(peeling

removal)(또는 그 반대로의)를 용이하게 할 수 있도록 충분히 얇은 것이 바람직하다. 리드 캐리어(10')(도 17)는 임시 지지 부재(20)를 제거한 후의 리드 캐리어를 지칭한다.

- [0039] 임시 지지 부재(20)의 상면(22)은 그 위에 복수의 패키지 사이트(12)를 지지하며, 각각의 패키지 사이트(12)가 하나 이상의 다이 부착 영역(30) 및 각각의 다이 부착 영역(30)에 연관된 복수의 단자 패드(40)를 포함한다. 절단 라인 Y는 일반적으로 각각의 패키지 사이트(12)(도 4)의 경계를 형성한다.

- [0040] 단자 패드(40)는 상이한 지오메트리 및 위치를 나타낼 수도 있지만, 유사한 재료로 형성되는 것이 바람직하다. 구체적으로, 이들 패드(40)는 소결된 재료로 형성되는 것이 바람직하다. 바람직한 실시예에 따라, 이들 패드 (40)는 서스펜션 성분(suspension component)과 혼합된, 바람직하게는 실버와 같은, 전기 도전성 재료의 파우더로서 시작된다. 서스펜션 성분은 일반적으로 실버 파우더가 최상으로 핸들링될 수 있고 패드(40)의 요구된 지오메트리를 나타내기 위해 처리될 수 있도록 실버 파우더에게 페이스트 또는 기타 유동성 재료 특성(flowable material characteristic)의 농도(consistency)를 제공하기 위해 바인딩 액체(binding liquid)로서 작용한다.

- [0041] 이 서스펜션 성분과 실버 파우더 또는 기타 전기 도전성 금속 파우더의 혼합물은 금속 파우더를 위한 소결 온도로 가열된다. 서스펜션 성분은 끓어지게 되어서(또는 휘발되어) 가스로 되고, 리드 캐리어(10)로부터 증발된다. 금속 파우더가 단자 패드(40)를 위해 요구된 형상을 갖는 단일체 덩어리(unitary mass)로 소결된다.

- [0042] 임시 지지 부재(20)는 패드(40)를 형성하는 전기 도전성 재료를 위한 이 소결 온도까지 가요성 및 요구된 정도 의 세기 및 기타 특성을 유지하도록 하는 열특성을 갖도록 구성된다. 전형적으로, 이 소결 온도는 패드(40)로 소결되는 금속 파우더를 위한 용융점에 접근한다.

- [0043] 도 11-14를 참조하면, 리드 캐리어(10)에 대한 설명이 패드(40)의 형성을 위한 순차적인 단계로 제공되어 있다. 도 12로부터, 임시 지지 부재(20) 상에 먼저 임시 형태 재료(temporary form material)(80)가 위치되는 것을 알 수 있다. 이 임시 형태 재료(80)는 임시 지지 부재(20)의 상면(22) 상에 인쇄될 수 있거나, 또는 임시 지지 부재(20) 상에 사전에 위치되는 연속적인 재료 내로 에칭될 수 있거나, 또는 이와 다르게 형성될 수 있다. 임지 형태 재료(80)의 측면(82)은 임시 형태 재료(80)의 영역들 사이에 보이드(84)의 에지를 형성한다. 이들 보이드(84)는 금속 파우더와 서스펜션 성분의 혼합물을 이들 보이드(84) 내로 흘러들어가게 함으로써 이 혼합물로 채워진다. 소결 공정이 발생하고, 임시 형태 재료(80), 금속 파우더와 서스펜션 혼합물뿐만 아니라 임시 지지 부재(20)가 가열되는 때에, 금속 파우더가 소결되고 서스펜션 성분이 휘발되고 제거되는뿐만 아니라, 임시 형태 재료(80)가 휘발되고 리드 캐리어(10) 상의 패키지 사이트(12)로부터 제거된다. 그러므로, 소결 후에는, 소결된 재료의 패드(40)만이 임시 지지 부재(20) 상에 잔류된다(도 14).

- [0044] 단자 패드(40)는 다양한 상이한 크기 및 지오메트리를 가질 수 있다. 가장 바람직하게는, 단자 패드(40)는 임시 지지 부재(20)의 상면(22) 위에 위치하는 실질적으로 바닥면 반대쪽의 실질적으로 평면형의 상면(42)을 포함할 것이다. 단자 패드(40)의 에지(46)는 단자 패드(40)의 둘레 형상을 형성한다. 이 에지(46)는 임시 지지 부재(20)에 수직한 평면으로 지향되지 않고, 테이퍼를 갖거나, 또는 각각의 에지(46)의 상부 연장부(upper extent)가 각각의 에지(46)의 하부 연장부(lower extent)를 돌출하는 형태로 적어도 부분적인 오버행이 존재하도록 하는 윤곽이 되도록 구성되는 것이 바람직하다. 이 테이퍼는 임시 형태 재료(80)(도 12-14)의 측면(82)의 베벨링(beveling)에 의해 제공되는 것이 바람직하다.

- [0045] 이 오버행 관계는 도시된 바와 같이 에지(46)를 테이퍼링함으로써와 같이 연속적인 것일 수 있다. 대안의 형태 (도 18)에서, 에지(46)는 계단형 윤곽과 같은 다른 윤곽을 갖고, 여전히 몇몇 형태의 오버행을 제공할 수 있다. 다른 형태에서, 에지(46)의 적어도 몇몇 부분이 에지(46)의 하부 연장부에 더 가까운 에지(46)의 일부분을 돌출하는 한, 오버행의 형태가 제공된다. 도 16 및 도 17에서 알 수 있는 바와 같이, 몰드 컴파운드(70)가 패드 (40)를 인캡슐레이션한 후, 단자 패드(40)의 에지(46)에서의 이 오버행은, 특히 임시 지지 부재(20)의 제거 동안, 단자 패드(40)로 하여금 몰드 컴파운드(70) 내에 유지되도록 한다.

- [0046] 도 3 및 도 4에 도시된 일례의 실시예에서는 각각의 다이 부착 영역(30) 주위에 단지 4개의 단자 패드(40)가 도시되어 있지만, 바람직하게는 각각의 다이 부착 영역(30)을 둘러싸는 단자 패드(40)의 수는 각각의 다이 부착 영역(30)을 둘러싸는 수십 또는 수백의 단자(40)의 정도일 것이다. 또한, 전형적으로, 단자 패드(40)는 각각의 다이 부착 영역(30)을 둘러싸는 행으로 배열될 것이다. 단자 패드(40)는 이 일례의 실시예에서 설명된 바와 같이 다이 부착 영역(30)에 비하여 더 작거나 또는 더 클 수 있다. 단자 패드(40)의 에지가 각각 오버행일 윤곽을 갖는 것으로 도시되어 있지만, 각각의 단자 패드(40)의 에지(46) 중의 몇몇만이 이러한 오버행잉 윤곽을 갖고, 여저힌 본 발명의 이 특징에 따른 몇몇 이점을 제공할 것이라는 것을 상정할 수 있다.

- [0047] 바람직하게는, 각각의 단자 패드(40)의 상면(42)은 공통 평면이다. 그러나, 상면(42)은 상이한 높이를 가질 수있고, 이들 상면(42)은 완전하게 평면형 이외의 형태로 될 수 있고, 여전히 본 발명에 따른 이점의 몇몇을 제공할 것이라는 것을 상정할 수 있다. 바닥면(44)은 제조 공정의 완료 후에 각각의 패키지(100) 내의 표면 마운트조인트(90)를 형성한다(도 10).

- [0048] 도 8-10을 참조하면, 이 일레의 실시예에 따라, 다양한 패키지 사이트(12)에서의 리드 캐리어(10) 상의 추가의 제조 후의 각각의 패키지(100)의 상세가 설명된다. 집적회로칩(60)은 다이 부착 영역(30)에 탑재된다. 이러한 탑재는 다이 부착 영역(30)에서의 임시 지지 부재(20) 상에 집적회로칩(60)을 위치시키는 것과 같은 단순한 것일 수 있다(도 4, 도 14, 도 15). 임시 지지 부재(20) 상에 집적회로칩(60)을 유지하기 위해 접착제가 사용될 수 있거나, 또는 정적 흡인(static attraction), 자기 흡인(magnetic attraction), 석션(suction) 또는 패스너 (fastener)와 같은 다른 형태의 부착이 채용될 수 있다.

- [0049] 필요한 경우, 집적회로칩(60)의 하면이 다이 부착 영역(30)에 전기적으로 결합될 수 있다. 이러한 전기 결합은 집적회로칩(60)을 위한 "그라운드"에 공통될 수 있거나, 또는 집적회로칩(60)을 위한 몇몇 다른 기준에 공통될 수 있거나, 또는 패키지(100)가 이용되는 전체적인 전기 시스템 내에서의 다른 몇몇 전기적 상태를 가질 수 있다. 전기 결합은 처음에는 임시 지지 부재(20)와 이루어질 수 있으며, 그리고나서 임시 지지 부재(20)로부터의 제거 후의 공통 리드 캐리어(10')에 있는 동안의 패키지(100)를 테스트하도록 구성된 테스트 구조물의 단자에 대한 전기 결합과 이루어질 수 있다. 집적회로칩(60)은 다이 부착 영역(30)과 실질적으로 공통 평면을 이루는 하부를 형성하는 베이스(62)를 포함한다. 집적회로칩(60)의 상부 표면(64)은 베이스(62)의 반대쪽에 제공된다. 이 상부 표면(64)은 와이어 본드(50) 중의 한쪽 단부에 종단될 수 있는 복수의 입력 출력 접합부(input output junction)를 갖는다(도 8, 도 9).

- [0050] 하나의 와이어 본드(50)가 집적회로칩(60) 상의 각각의 입력 출력 접합부와 주변 단자 패드(40) 사이에 종단되는 것이 바람직하다. 그러므로, 각각의 와이어 본드(50)는 단자 단부 반대쪽에 칩 단부를 갖는다. 또 다른 대안으로서, 예컨대, 하나의 패키지(100)가 2개 이상의 특정한 설계를 포괄하게 되도록 설계되고, 이러한 설계 중의 하나가 다른 설계보다 더 많은 단자 패드(40)를 요구하는 때에는, 하나 이상의 단자 패드(40)가 와이어 본드(50) 없이 잔류될 수 있다. 또한, 와이어 본드(50)는 단자 패드(40)의 세트들 사이에 제공될 수 있으며, 여기서 이러한 전기적 상호접속은 회로 설계에 의해 요청된다. QFN 리드 프레임과 함께 사용되는 것과 같은 공지의와이어 본드(50) 종단 기술을 이용하면, 이들 와이어 본드(50)는 집적회로칩(60)과 단자 패드(40) 사이 또는 단자 패드(40)의 세트들의 사이에 결합된다.

- [0051] 패키지(100) 형성 공정을 완료하기 위해, 몰드 컴파운드(70)가 리드 캐리어(10)에 걸쳐 흐르게 되고, 단자 패드 (40), 와이어 본드(50) 및 집적회로칩(60)의 각각을 완전하게 인캡슐레이션하는 방식으로 경화하도록 허용된다. 이 몰드 컴파운드(70)는 임시 지지 부재(20)의 상면(22)에 대해 몰딩할 수 있다. 그러므로, 각각의 패드(40)와 각각의 칩(60)의 베이스(62)의 표면 마운트 조인트(90)는 임시 지지 부재(20)의 제거 후에 노출된 상태로 유지된다(도 10). 몰드 컴파운드(70)는 전형적으로 제1 온도에서는 유체 형태이지만 제2 온도로 조정되는 때에는 경화될 수 있는 다양한 것이어도 된다.

- [0052] 몰드 컴파운드(70)는 패드(40)와 집적회로칩(60)의 베이스(62)가 서로 전기적으로 고립되도록 실질적으로 비도 전성 재료로 형성된다. 몰드 컴파운드(70)는 패드(40)와 칩(60)을 전체 패키지(100) 내에서 몰드 컴파운드(70)와 함께 유지하는 경향이 있는 인터로크(72)(도 16, 도 17)를 제공하기 위해 패드(40) 사이에 흐른다. 이러한 인터로크(72)는 단자 패드(40)가 와이어 본드(50)로부터 이탈되는 것을 방지한다. 이러한 이탈 경향은 먼저임시 지지 부재(20)가 리드 캐리어(10)로부터 제거되는 때에 저항을 받게 되고, 또한 이롭게는 패키지(100)가 사용되고 있고 패키지(100)로부터 단자 패드(40)를 이탈시킬 수도 있는 충격 부하를 경험할 수도 있을 때에 저항을 받게 된다. 이들 인터로크(72)는 패드(40)의 에지(46)에 연관되고 원래에는 임시 형태 재료(80)(도 12,도 13)의 측면(82)의 윤곽을 기반으로 하는 전술한 바와 같은 다양한 형상을 가질 수 있다.

- [0053] 몰드 컴파운드(70)의 경화 후에, 바닥부(104) 반대쪽의 상단부(102)(도 9, 도 10)를 포함하고 둘레 측면(106)을 갖는 패키지(100)가 리드 캐리어(10) 상에 어레이로 제공된다. 둘레 측면(106)은 그로부터 연장하는 어떠한 전기 도전성 재료를 반드시 가져야 하는 종래 기술의 QFN 패키지 P(도 6, 도 7)와는 달리 이러한 전기 도전성 재료를 갖도록 요구되지 않는 이점이 있다.

- [0054] 도 18을 참조하여, 대안의 리드 캐리어(110)의 상세를 설명한다. 이 대안의 리드 캐리어(110)에서, 임시 지지부재(120)는 그 위에 놓여지는 대안의 패드(130)를 갖는다. 이들 대안의 패드(130)는 바닥면(134) 반대쪽의 상면(132)을 포함하고 바닥면 위에 계단형 에지(136)를 갖는다. 이 계단형 에지(136)는 전술한 단자 패드(40) 상

에 제공된 에지의 대안의 에지이다. 이러한 계단형 에지(136)는 전체 패키지(100) 내의 패드(40)를 이롭게 유지하는 몰드 컴파운드(70)와 인터로킹하는 형태를 여전히 제공한다.

[0055] 본 개시내용은 본 발명의 바람직한 실시예 및 본 발명을 실시하기 위한 최상의 모드를 보여주기 위해 제공된 것이다. 본 발명을 이러한 방식으로 설명하였지만, 본 발명의 개시내용의 범위 및 사상으로부터 벗어나지 않고서도 바람직한 실시예에 대하여 다양한 상이한 수정이 이루어질 수 있다는 것을 이해하여야 한다. 구조물이 기능을 수행하기 위한 수단으로서 식별되는 때에는, 이러한 식별은 지정된 기능을 수행할 수 있는 모든 구조물을 포함하도록 의도된다. 본 발명의 구조물이 함께 결합되는 것으로서 식별되는 때에는, 이러한 언어 표현은 직접적으로 함께 결합되거나 또는 매개 구조물을 통해 함께 결합되는 구조물을 포함하는 것으로 폭넓게 해석되어야 한다. 일한 결합은 영구적일 수도 또는 일시적인 것일 수도 있으며, 구체적으로 제한되지 않는다면 견고한 양상으로 이루어지거나 또는 몇몇 형태의 부착을 제공하면서 피봇, 슬라이딩 또는 기타 상대적 움직임을 허용하는 양상으로 이루어질 수도 있다.

[0056] 본 발명은 QFN 패키징된 반도체 다이를 보다 용이하게 생산하기 위해 간략화된 QFN 프로세스의 구현을 가능하게 하는 반도체 패키지의 전기적 인터커넥트 부품을 제공하기 위한 시스템을 제공한다.

### 도면

### 도면1

# 도면4

## 도면7

## 도면8

## 도면11

## 도면12

## 도면13

## 도면14

## 도면15