# UK Patent Application (19) GB (11) 2 244 863(13)A

(43) Date of A publication 11.12.1991

- (21) Application No 9110088.3

- (22) Date of filing 10.05.1991

- (30) Priority data (31) 906731

- (32) 11.05.1990

- (33) KR

(71) Applicant

Gold Star Electron Co., Ltd

(Incorporated in the Republic of Korea)

50 Hyangjeong-Dong, Cheongju-Si, Chungcheongbuk-Do, Republic of Korea

- (72) Inventor Sung Min Lee

- (74) Agent and/or Address for Service Urquhart-Dykes & Lord 91 Wimpole Street, London, W1M 8AH, United Kingdom

- (51) INT CL5 H01L 27/148

- (52) UK CL (Edition K) H1K KECC K1CC9 K1EB K4C14 K9B1 K9D1 H4F FCC FD30E FD30K FD30X FD54 FD83B U1S S2222

- (56) Documents cited None

- (58) Field of search UK CL (Edition K) H1K KECC INT CL5 H01L, H04N

#### (54) CCD image sensor

(57) A CCD image sensor comprises odd and even rows of photodetectors coupled by transfer gates to an array of VCCD regions operable as scanners, wherein the photodetectors in each row are operatively associated alternately with the left and the right sides of successive said VCCD regions across the array, and the photodetectors in each pair of adjacent said photodetectors not having a VCCD region therebetween are spaced apart by a channel stop region. A four phase clock signal consisting of four fields is used to operate the sensor. The sensor provides an increased area ratio of photodetectors to VCCD regions, thereby improving resolution.

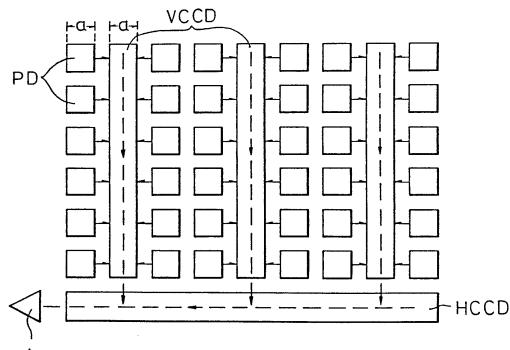

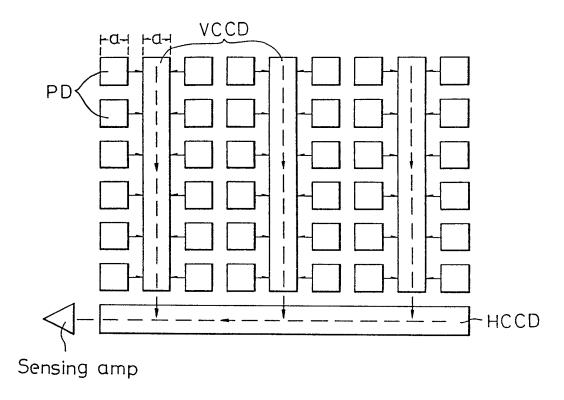

F 1 G. 4a

Sensing amp

I/8

F I G. 1a

PRIOR ART

F I G. 1b PRIOR ART

2/8

F I G. 2a

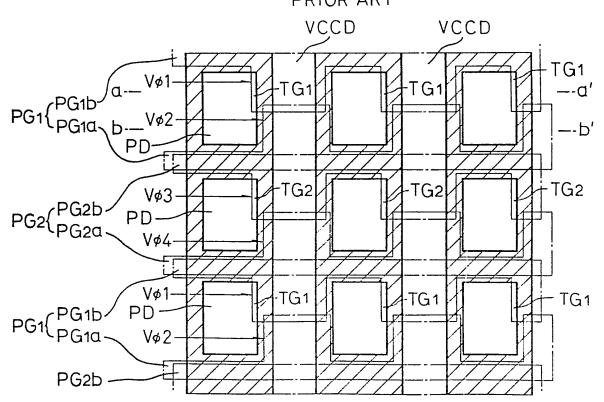

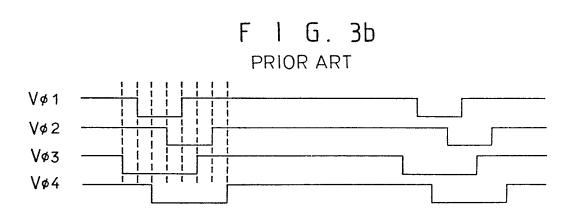

PRIOR ART

VCCD V

F I G. 2b PRIOR ART

F I G. 2c PRIOR ART

F I G. 2d PRIOR ART

4/8

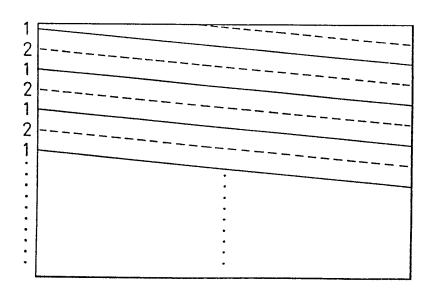

F I G. 3c PRIOR ART

| 1 | 1 | 1 | 1 | 1 | 1 | 1 |

|---|---|---|---|---|---|---|

| 2 | 2 | 2 | 2 | 2 | 2 | 2 |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 2 | 2 | 2 | 2 | 2 | 2 | 2 |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 2 | 2 | 2 | 2 | 2 | 2 | 2 |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 |

5/8 F I G. 4a

F I G. 4b

F 1 G. 4c

F I G. 4d

F 1 G. 5a

F I G. 5b

8/8

F 1 G. 5c

| 1 | 3 | 1  | 3 | 1 | 3 |

|---|---|----|---|---|---|

| 4 | 2 | 4  | 2 | 4 | 2 |

| 1 | 3 | 1  | 3 | 1 | 3 |

| 4 | 2 | 4  | 2 | 4 | 2 |

| 1 | 3 | 1. | 3 | 1 | 3 |

| 4 | 2 | 4  | 2 | 4 | 2 |

## F I G. 5d

| 1 | $\frac{1+3}{2}$ | 3 | 1 | 1+3                 | 3 | 1 | 1+3        | 3 |

|---|-----------------|---|---|---------------------|---|---|------------|---|

| 4 | 4+2             | 2 | 4 | 4+2                 | 2 | 4 | 4+2        | 2 |

| 1 | 1+3             | 3 | 1 | 1+3<br>2            | 3 | 1 | 1+3        | 3 |

| 4 | 4+2             | 2 | 4 | <del>4+2</del><br>2 | 2 | 4 | 4+2        | 2 |

| 1 | <u>1+3</u>      | 3 | 1 | 1+3<br>2            | 3 | 1 | 1+3        | 3 |

| 4 | 4+2             | 2 | 4 | <u>4+2</u><br>2     | 2 | 4 | <u>4+2</u> | 2 |

| 1 | 1+3             | 3 | 1 | 1+3<br>2            | 3 | 1 | 1+3        | 3 |

| 4 | 4+2             | 2 | 4 | <u>4+2</u><br>2     | 2 | 4 | 4+2        | 2 |

| 1 | <u>1+3</u><br>2 | 3 | 1 | <u>1+3</u><br>2     | 3 | 1 | 1+3<br>2   | 3 |

#### CCD IMAGE SENSOR

### Background of the Invention

The present invention relates to a CCD image sensor, and more particularly, to a CCD image sensor which provides an improved resolution of picture.

CCD, 1.e., charge coupled device is mainly used for fabricating solid state image sensor or CCD image sensor.

Solid state image sensor is a semiconductor such as silicon onto which a plurality of photodetector and scanner are disposed and can, with a proper photodetector, provide an image sansing from visible region to infrared region.

As a scanner for solid state image sensor, metal oxide semiconductor(MOS) switch or CCD has been principally used.

The MOS switch has a problem that it cannot be used for detecting weak signals in which high signal to noise ratio is required, since the spike noise occurred during the operation thereof results in a lowering of signal to noise ratio.

Thus, they are hardly used now.

The CCD allows a use of any type of photoconductor as the MOS switch does.

In case that the CCD is employed as a scanner, it is preferrable to design the CCD part, particularly vertical charge coupled device(VCCD) in such a way that its surface is as small as possible so that more effective surface of photodetector may be available. This is more important when an interlace manner is adopted, in which CCD is disposed between photodetectors.

As photodetectors, PN junction, metal insulator semiconductor(MIS) structure, Schottky junction and the like are commonly used.

The scanning manner using CCD as a scanner include interlace and non-interlace manners.

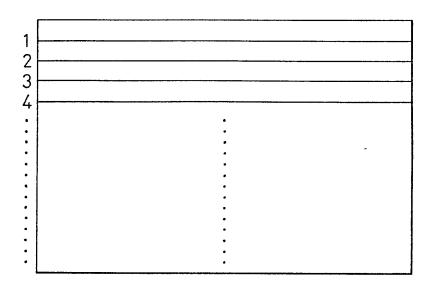

In non-interlace manner, one frame consists of a plurality of field and the data of input field are scanned to the screen in an order that they are input-ted as shown in Fig. 1(a).

The figures 1, 2, 3.... in Fig. 1(a) represent that the scanned fields are displayed according to their input order.

In interlace manner, one frame consists of even and odd fields and data of the odd fields and then data of the even fields are scanned to the screen in turn.

In Fig. 1(b), figure 1 and 2 represent odd and even fields, respectively.

The non-interlace manner can acquire the accurate actual image of moving subject due to rapid scanning speed, so that it is used for military equipments, for example, missile.

Its defect is that the video is vibrated.

The interlace manner can provide a stable video because the scanning speed is low compared to the non-interlace manner. However, rapidly moving subject is displayed in two images. Therefore, it is not proper for military equipments but used for TV broadcasting of NTSC or PAL manner.

The structure of the above conventional CCD image sensor for interlace manner will be described with reference to the accompanying Fig. 2(a) to (e).

Hereinafter, the odd-numbered horizontal line in which photo diodes (PD) are disposed is referred to as odd horizontal line and the even-numbered horizontal line is referred to as even horizontal line.

Fig. 2(a) shows a block diagram of CCD image sensor in the conventional interlace manner. Each photo diode(PD) is connected consecutively to corresponding VCCD region(VCCD) and each photo diode(PD) is connected to VCCD region (VCCD) in such a way that output video signal charge may be transferred to VCCD in only one direction while each VCD region (VCCD) is connected to HCCD region

(HCCD) so that signal charges coming out of each photo diode(PD) may be transferred to HCCD region(HCCD) through the first to fourth VCCD clock signals( $V\phi_1-V\phi_4$ ) consisting of 4 phases.

Fig. 2(b) shows a layout diagram of CCD image sensor according to a structure of Fig. 2(a). Channel stop region(ST) is formed between VCCD region (VCCD) and photo diode(PD). Odd gate electrode(PG<sub>1</sub>) to which the first and second VCCD clock signals(V $\phi_1$ , V $\phi_2$ ) are applied is formed over from VCCD region (VCCD) to channel stop region(ST) so that said odd gate electrode(PG<sub>1</sub>) may be connected to corresponding transfer gate(TG<sub>1</sub>) of photo diode(PD) disposed in the odd horizontal line while even gate electrode(PG<sub>2</sub>) to which the third and fourth VCCD clock signals(V $\phi_3$ -V $\phi_4$ ) is applied are formed over from channel stop region(ST), VCCD region(VCCD) to photo diode(PD) so that said even gate electrode (PG<sub>2</sub>) may be connected to corresponding transfer gate(TG<sub>2</sub>) of photo diode(PD) disposed in the even horizontal line.

The desired numbers of the odd gate(PG<sub>1</sub>) and even gate(PG<sub>2</sub>) may be formed consecutively in the same form. Thery are separated from each other by an insulating material which is not shown in Fig.

As a material for transfr gates  $(TG_1, TG_2)$ , and odd and even gate electrodes  $(PG_1, PG_2)$ , poly silicon was used.

The odd gate electrode(PG<sub>1</sub>) consists of the first odd gate electrode(PG<sub>1</sub>a) which is formed under the photo diode(PD) in the odd horizontal line and to which the second VCCD clock signal(V $\phi_2$ ) is applied and the second odd gate electrode (PG<sub>1</sub>b)which is formed in the upper region of the photo diode(PD) in the odd horizontal line, to which the first VCCD clock signal(V $\phi_1$ ) is applied and which is connected to the transfer gate(TG<sub>1</sub>) of the photo diode(PD) formed in the odd horizontal line.

The even gate electrode(PG<sub>2</sub>) consists of the first even gate electrode (PG<sub>2</sub>) which is formed under the photo diode(PD) in the even horizontal line and to which the fourth VCCD clock signal(V $\phi_4$ ) is applied and the second even gate electrode(PG<sub>2</sub>b) which is formed in the upper region of the photo diode (PD) in the even horizontal line, to which the third VCCD clock signal(V $\phi_3$ ) is applied and which is connected to the transfer gate(TG<sub>2</sub>) of the photo diode(PD) formed in the even horizontal line.

The first to fourth VCCD clock signals  $(V\phi_1-V\phi_4)$ , which are of four phases, consist of even and odd field. The clocking of the VCCD will be hereinafter described in more detail.

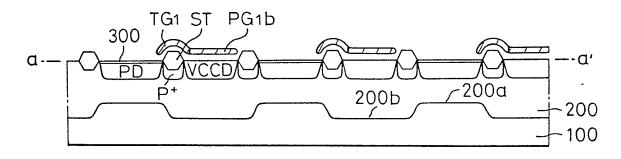

Fig. 2(c) shows a cross sectional view taken along the a-a' line of Fig. 2(b). A p-type well(200) is formed on the n-type substrate(100), an n-type photo diode(PD) and n-type VCCD region(VCCD), which are formed in the even horizontal line, are disposed consecutively aparting from each other by a distance of channel stop region(ST), a transfer gate(TG<sub>2</sub>) for connecting the photo diode(PD) and the VCCD region (VCCD) is formed in the upper region of the space by which the photo diode(PD) and the VCCD region (VCCD) are separated from each other and, in the upper region of surface of the VCCD region (VCCD), the second even gate electrode(PG<sub>2b</sub>) of even gate electrode(PG<sub>2</sub>), to which the third VCCD clock signal(V $\phi$ 3) is applied, is connected to the corresponding transfer gate(TG<sub>2</sub>) of the photo diode(PD) in even horizontal line.

The p-type well(200) consists of shallow(200a) and deep(200b) p-type wells in order to control the over flow drain (OFD) voltage.

On the surface of photo diode(PD), a p+-type thin film(300) is usually formed to apply the initial vias. The figure p+ under the channel stop region

(ST) represents channel stop ion.

Fig. 2(d) shows a cross sectional view taken along the c-c' line of Fig. 2(b). In Fig. 2(d), a p-type well(200) is formed on an n-type substrate (100), and n-type photo diode(PD) and n-type VCCD region(VCCD) in the even horizontal line are disposed consecutively aparting from each other by a distance of channel stop region and the first even gate electrode(PG<sub>2a</sub>) of the even gate electrode(PG<sub>2</sub>) to which the fourth VCCD clock signal(V $\phi_4$ ) is applied, is formed in the upper region of the surface of the VCCD region(VCCD).

In Fig. 2(d), like Fig. 2(c), conventional p+-type thin film(300) is formed on the surface of photo diode(PD) and the figure p+ shown under the channel stop region(ST) represents p+-type ion for stopping channel. The p-type well(200) consists of shallow(200a) and deep(200b) p-type wells in order to control the OFD voltage.

Accordingly, the transfer gate(TG<sub>1</sub>) of the photo diode(PD) formed in the odd horizontal line can be drived only be the first VCCD clock signal(V $\phi_1$ ) which is applied to the second odd gate electrode(PG<sub>1</sub> $_b$ ) of the odd gate electrode(PG<sub>1</sub> $_b$ ). Further, the transfer gate(TG<sub>2</sub>) of the photo diode(PD) formed in the even horizontal line can be drived only by the third VCCD clock signal (V $\phi_3$ ) which is applied to the second even gate electrode(PG<sub>2</sub> $_b$ ) of the even gate electrode(PG<sub>2</sub> $_b$ ).

The second VCCD clock signal( $V\phi_2$ ) which is applied to the first odd gate electrode( $PG_{1a}$ ) of the odd gate electrode( $PG_{1}$ ) and the fourth VCCD clock signal( $V\phi_4$ ) which is applied to the first even gate electrode( $PG_{2a}$ ) of the even gate electrode( $PG_{2a}$ ) have a function of shifting the image signal charge coming out of the photo diodes (PD) formed in the odd and even horizontal lines to a HCCD(Horizontal Charge Coupled Device).

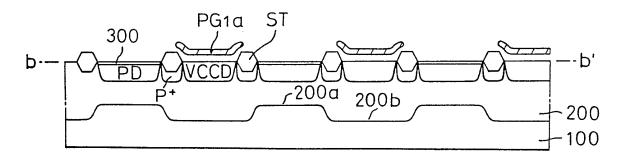

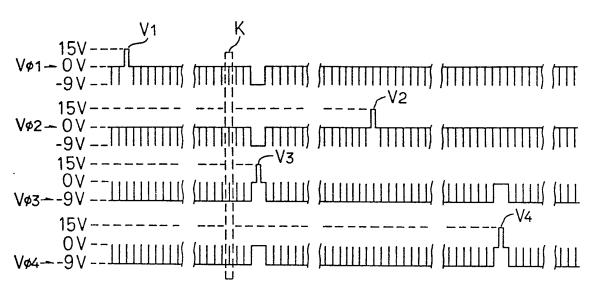

Hereinafter, operation of the conventional CCD image sensor will be described with reference to the accompanying Fig. 3(a) which shows a timing diagram of the first to fourth VCCD clock signals  $(V\phi_1-V\phi_4)$  which are of 4 phases.

Each clock signal consists of two fields, i.e., one odd field and one even field.

In the odd field, a transfer gate driving voltage( $V_1$ ) of high level state (15V) is involved in the first VCCD clock signal( $V\phi_1$ ) which is applied to the second odd gate electrode( $PG_{1\,b}$ ) of the odd gate electrode( $PG_{1\,b}$ ).

In the even field, a transfer gate driving voltage( $V_2$ ) of high level state (15V) is involved in the third VCCD clock signal( $V\phi_3$ ) which is applied to the second even gate electrode( $PG_{2b}$ ) of the even gate electrode( $PG_2$ ).

First, when in the odd field, the first to fourth VCCD clock signals  $(V\phi_1 - V\phi_4)$  are applied simultaneously, the transfer gates(TG<sub>1</sub>) of the photo diodes (PD) formed in each odd horizontal line are turned on simultaneously by the transfer gate driving voltage  $(V_1)$  involved in the first VCCD clock signal( $V\phi_1$ ).

Accordingly, an image signal charge generated at the photo diode(PD) is transferred to the VCCD region from which it is moved again to the HCCD region by the clocking operatin of VCCD.

Fig. 3(b) shows a pulse waveform diagram of the applied first to fourth clock signals  $(V\phi_1 - V\phi_4)$  in the unit section(K) of Fig. 3(a).

The image signal charge coming out of the photo diode(PD) by serial clocking operations as shown in Fig 3(b) is moved in a vertical direction to the HCCD region(HCCD).

The second VCCD clock signal( $V\phi_2$ ) which is applied through the first odd gate electrode( $PG_{1a}$ ) of the odd gate electrode( $PG_1$ ) formed under the odd horizo-

ntal line has a function of shifting the image signal charge coming out of the photo diode(PD) in the odd horizontal line by said first VCCD clock signal(V $\phi_1$ ) to the HCCD region(HCCD) by aid of said first VCCD clock signal(V $\phi_1$ ).

In the even field of fig. 3(a), when the first to fourth clock signals  $(V\phi_1-V\phi_4)$  are applied simultaneously, the transfer gates(TG<sub>2</sub>) of the photo diodes(PD) formed in each even horizontal line are turned on by the transfer gate driving voltage(V<sub>2</sub>) involved in the third VCCD clock signal(V $\phi_3$ ).

Accordingly, an image signal charge generated at the photo diode(PD) in the even horizontal line is moved in a vertical direction to the HCCD region by the clocking operation, like in Fig. 3(b) for odd field.

The fourth VCCD clock signal( $V\phi_4$ ) which is applied through the first even gate electrode( $PG_{2a}$ ) of the even gate electrode( $PG_{2b}$ ) formed under the even horizontal line has a function of, together with the third VCCD clock signal( $V\phi_3$ ), shifting the image signal charge coming out of the photo diode(PD) in the even horizontal line by said third VCCD clock signal( $V\phi_3$ ).

Use of VCCD clock signals of 4 phases makes it possible to transfer more amount of image signal charge than VCCD clock signals of 2 phases.

According to the above description of operation, first, the image signal charges of the photo diodes(PD) disposed in the odd horizontal line are scanned to the screen in due turn by the first to fourth VCCD clock signals( $V\phi_1-V\phi_4$ ) which are of 4 phases through the VCCD region(VCCD) and HCCD region (HCCD). Then, the image signal charges of the photo diodes(PD) disposed in the even horizontal line are scanned to the screen in due turn through the VCCD region(VCCD) and HCCD region(HCCD).

The above explained scanning manner is called interlace manner.

As shown in Fig. 2(a), when the signal charge of the photo diode(PD) disposed in the odd horizontal line is referred to as 1 and the signal charge of the photo diode(PD) disposed in the even horizontal line is referred to as 2, a state of the screen(the frame) consisting of Pixels which are displayed by said image signal charges 1 and 2 may be shown as Fig. 3(c).

However, such a CCD image sensor of the prior art has problems that, although said CCD image sensor of interlace manner is widely used for TV broadcasting of NTSC or PAL manner, VCCD region which does not participate in receiving the image signal is too broad in view of the total chip surface of said CCD image sensor since the VCCD is disposed between photodetectors.

Consequently, it is hard to obtain a high resolution video due to restriction in increasing the photodetectors for improving resolution with defined chip size.

## Summary of the Invention

An object of the invention is to provide a CCD image sensor which has no disadvantage of the prior art and, thus, can be used for systems requiring high resolution by making it possible to decrease CCD region and to increase photodetectors receiving light of image signal in the same chip size.

This object is accomplished by an improved CCD image sensor according to the invention which contains a plurality of photodetector and uses a CCD as a scanner for reading image signal an improvement characterized in that photo diodes are connected consecutively to both left and right sides of VCCD region and, in the parts without VCCD region, are disposed repeatedly parallel to each other at an interval of channel stop region.

The CCD image sensor according to the invention is operated by a 4

phase clock signal cossisting of 4 fields.

The CCD image sensor is also provided with four gate electrodes formed through over channel stop region, photodetector and VCCD region, to which the 4 phase clock signal is apllied, so that transfer gates of the photodetectors formed in the left upper and lower regions and in the right upper and lower regions with reference to the reference point which is a center of both odd and even horizontal lines in which said photodetectors are disposed may be turned on in different fields respectively by said 4 phase clock signal.

#### Brief Description of the Drawings

- Fig. 1(a) is a reference diagram to explain the non-interlace manner;

- Fig. 1(b) is a reference diagram to explain the interlace manner;

- Fig. 2(a) is a block diagram of the CCD image sensor in the conventional manner:

- Fig. 2(b) is a layout diagram of Fig. 2(a);

- Fig. 2(c) is a cross sectional view taken along the a-a' line of Fig. 2 (b).

- Fig. 2(d) is a cross sectional view taken along the b-b' line of Fig. 2 (b).

- Fig. 3(a) is a timing diagram of VCCD clock signal in the conventional interlace manner;

- Fig. 3(b) is a pulse waveform diagram of unit section of fig. 3(a).

- Fig. 3(c) is a Pixel block diagram of a frame according to the conventional interlace manner;

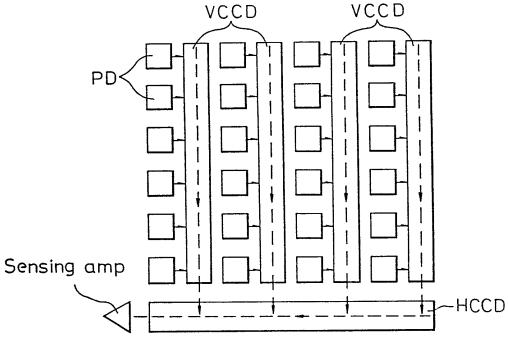

- Fig. 4(a) is a block diagram of CCD image sensor according to the

#### invention :

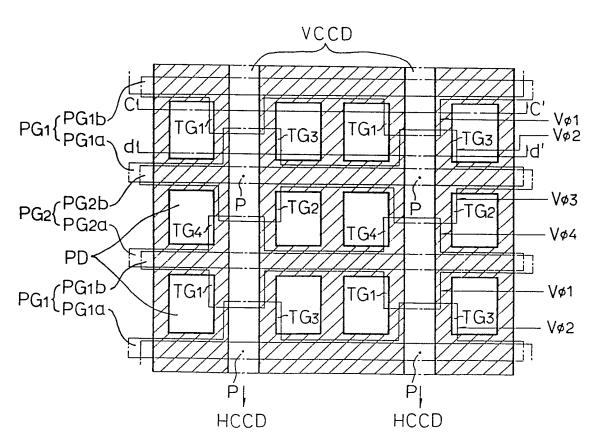

- Fig. 4(b) is a layout diagram of Fig. 4(a);

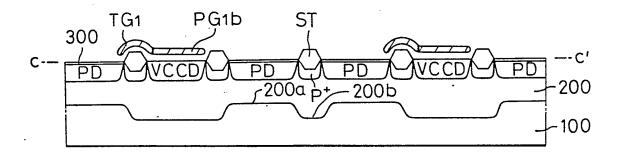

- Fig. 4(c) is a cross sectional view taken along c-c' line of Fig. 4(b);

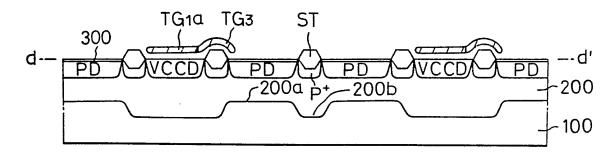

- Fig. 4(d) is a cross sectional view taken along d-d'line of Fig. 4(b);

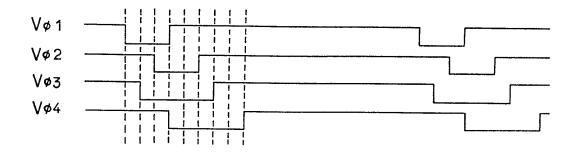

- Fig. 5(a) is a timing diagram of VCCD clock signal of the present invention;

- Fig. 5(b) is a pulse waveform diagram of unit section of Fig. 5(a);

- Fig. 5(c) is a Pixel block diagram of a frame according to the invention; and

- Fig. 5(d) is an another Pixel block diagram of a frame according to the invention.

## Detailed Description of the Preferred Embodiment

An embodiment of the present invention will be described in more detail with reference to the accompanying Fig. 4(a) to Fig. 4(d).

Fig. 4(a) is a block diagram of the CCD image sensor according to the present invention. As shown in Fig. 4(a), photo diodes(PD) are connected consecutively to both the left and right sides of VCCD region (VCCD) and are disposed parallel to each other at an interval of channel stop region (ST) in the parts without VCCD regions, and HCCD region (HCCD) is formed under the VCCD region(VCCD).

Fig. 4(b) is a layout diagram of the CCD image sensor according to the present. As shown in Fig. 4(b), two photo diodes(PD), which are insulated from each other by channel stop region(ST), are disposed consecutively parallel to each other between VCCD regions(VCCD), and in an odd horizontal line in which photo diodes(PD) are disposed an odd gate electrode(PG<sub>1</sub>) for

applying VCCD clock signals( $V\phi_1-V\phi_2$ ) is formed through over photo diode(PD), channel stop region (ST) and VCCD region(VCCD), while, in an even horizontal line in which photo diodes(PD) are disposed, an even gate electrode(PG<sub>2</sub>) for applying VCCD clock signals( $V\phi_3$ ,  $V\phi_4$ ) is formed through over photo diode (PD), channel stop region(ST) and VCCD region(VCCD).

Said odd gate electrode(PG<sub>1</sub>) consists of a first odd gate electrode(PG<sub>1a</sub>) which is formed under the photo diode(PD) disposed in the odd horizontal line, which is connected to a transfer gate(TG<sub>3</sub>) of the photo diode(PD) formed in the right side of the VCCD region(VCCD) and to which the second VCCD clock signal(V $\phi_2$ ) is applied and a second odd gate electrode(PG<sub>1b</sub>) which is formed in upper region of the photo diode(PD) disposed in the odd horizontal line, which is connected to a transfer gate(TG<sub>1</sub>) of the photo diode(PD) formed in the left side of the VCCD region (VCCD) and to which the first VCCD clock signal(V $\phi_1$ ) is applied.

Further, said even gate electrode(PG<sub>2</sub>) consists of a first even gate electrode(PG<sub>2</sub>a) which is formed under the photo diode(PD) disposed in the even horizontal line, which is connected to a transfer gate(TG<sub>4</sub>) of the photo diode (PD) formed in the left side of the VCCD region(VCCD) and to which the fourth VCCD clock signal(V $\phi_4$ ) is applied and a second even gate electrode(PG<sub>2</sub>b) which is formed in upper region of the photo diode(PD) disposed in the even horizontal line, which is connected to transfer gate(TG<sub>2</sub>) of the photo diode (PD) formed in the right side of the VCCD region (VCCD) and to which the third VCCD clock signal(V $\phi_3$ ) is applied.

Said odd gate electrode and even gate electrode are electrically insulated from each other by a insulating membrane which is not shown in Fig.

Fig. 4(c) shows a cross sectional view taken along c-c'line of Fig. 4

(b). As shown in Fig. 4(c), a p-type well(200) is formed on an n-type substrate(100), an n-type photo diode(PD) and n-type VCCD region(VCCD) are consecutively formed on the surface of said p-type well(200) at a distance of channel stop region(ST), a transfer gate(TG<sub>1</sub>) for connecting the photo diode (PD) formed at the left side of the VCCD region(VCCD) and the VCCD region(VCCD) is formed in the upper region of space between of them and a second odd gate electrode (PG<sub>1b</sub>) of the odd gate electrode(PG<sub>1</sub>) for applying the first VCCD clock signal(V $\phi_1$ ) is formed in the upper region of the VCCD region(VCCD).

The p-type well(200) consists of a shallow p-type well(200a) and a deep p-type well(200b) in order to control OFD voltage.

Fig. 4(d) shows a cross sectional view taken along d-d'line of Fig. 4(b), of which constitution is the same as in Fig. 4(c). As shown in Fig. 4 (d), a transfer gate(TG<sub>3</sub>) for connecting the VCCD region(VCCD) and the photo diode(PD) formed in the right side of the the VCCD region(VCCD) is formed in the upper region of space between them and a first odd gate electrode(PG<sub>1a</sub>) of the odd gate electrode(PG<sub>1</sub>) to which the second VCCD clock signal(V $\phi_2$ ) is applied is formed in the upper region of the VCCD region(VCCD) instead of the transfer gate(TG<sub>1</sub>) and the second odd gate electrode(PG<sub>1b</sub>) in Fig. 4(c).

Operation of the above structure will be described in detail with reference to Fig. 5(a) and 5(b).

Fig. 5(a) shows a timing diagram of the first to fourth VCCD clock signals  $(V\phi_1-V\phi_4)$  used in the invention, in which all the clock signals consist of 4 fields.

As shown in Fig. 5(a), the first VCCD clock signal( $V\phi_1$ ) has a transfer gate driving voltage( $V_1$ ) of 15V in the first field, the second VCCD clock signal( $V\phi_2$ ) has a transfer gate driving voltage( $V_2$ ) of 15V in the third field, and the third VCCD clock signal( $V\phi_3$ ) has a transfer gate driving voltage( $V_3$ )

of 15V in the second field while the fourth VCCD clock signal( $V\phi_4$ ) has a transfer gate driving voltage( $V_4$ ) of 15V in the fourth field.

Fig. 5(b) shows a pulse waveform diagram of said first to fourth clock signals  $(V\phi_1-V\phi_4)$  generated at a unit section(K).

Image signal coming out of the photo diode(PD) with such a pulse waveform is shifted vertically toward the HCCD region(HCCD) shown in Fig. 4(a) and 4(b).

First, in the first field section of Fig. 5(a), when the first to fourth VCCD clock signals  $(V\phi_1-V\phi_4)$  are applied to the odd gate electrode(PG<sub>1</sub>) and even gate electrode(PG<sub>2</sub>) simultaneously, the transfer gate(TG<sub>1</sub>) of the photo diode(PD) which is formed in the left upper region of reference point(P) of Fig. 4(b) is turned on by the transfer gate driving voltage(V<sub>1</sub>) involved in the first VCCD clock signal(V $\phi_1$ ) which is applied through the second odd gate electrode(PG<sub>1b</sub>) of the odd gate electrode(PG<sub>1</sub>).

Consequently, an image signal charge generated at the photo diode(PD) is shifted to the VCCD region(VCCD), where it is vertically moved toward the HCCD region by clocking operation of the first to fourth VCCD clock signals( $V\phi_1 - V\phi_4$ ) shown in Fig. 5(b).

Next, in the second field section of Fig. 5(a), when the first to fourth VCCD clock signals  $(V\phi_1-V\phi_4)$  are applied to the odd gate electrode(PG<sub>1</sub>) and even gate electrode(PG<sub>2</sub>) simultaneously, the transfer gate(TG<sub>2</sub>) of the photo diode(PD) which is formed in the right lower region of reference point(P) of Fig. 4(b) is turned on by the transfer gate driving voltage(V<sub>3</sub>) involved in the third VCCD clock signal(V $\phi_3$ ) which is applied through the second even gate electrode(PG<sub>2b</sub>) of the even gate electrode(PG<sub>2</sub>).

Consequently, an image signal charge generated at the photo diode(PD) is shifted to the VCCD region(VCCD), where it is vertically moved toward the HCCD

region by clocking operation of the first to fourth VCCD clock signals  $(V\phi_1-V\phi_4)$  shown in Fig. 5(b).

Then, in the third field section of Fig. 5(a), when the first to fourth VCCD clock signals  $(V\phi_1-V\phi_4)$  are applied simultaneously, the transfer gate(TG<sub>3</sub>) of the photo diode(PD) which is formed in the right upper region of reference point(P) of Fig. 4(b) is turned on by the transfer gate driving vlotage  $(V_2)$  involved in the second VCCD clock signal( $V\phi_2$ ) which is applied through the first odd gate electrode(PG<sub>1a</sub>) of the odd gate electrode(PG<sub>1</sub>).

Consequently, an image signal charge generated at the photo diode(PD) is shifted to the VCCD region(VCCD), where it is moved to the HCCD region(HCCD) by clocking operation of the first to fourth VCCD clock signals( $V\phi_1-V\phi_4$ ) shown in Fig. 5(b).

Finally, in the fourth field section of Fig. 5(a), when the first to fourth VCCD clock signals  $(V\phi_1-V\phi_4)$  are applied to the odd gate electrode(PG<sub>1</sub>) and even gate electrode(PG<sub>2</sub>) simultaneously, the transfer gate(TG<sub>4</sub>) of the photo diode(PD) which is formed in the left lower region of reference point(P) of Fig. 4(b) is turned on by the transfer gate driving voltage(V<sub>4</sub>) involved in the fourth VCCD clock signal(V $\phi_4$ ) which is applied through the first even gate electrode(PG<sub>2</sub>a) of the even gate electrode(PG<sub>2</sub>).

Consequently, an image signal charge generated at the photo diode(PD) is shifted to each VCCD region(VCCD), where it is moved vertically toward the HCCD region(HCCD) by clocking operation of the first to fourth VCCD clock signals( $V\phi_1-V\phi_4$ ) shown in Fig. 5(b).

Herein, the reference point(P) of Fig. 4(b) indicates a point located at the center of both odd and even horizontal lines, in the VCCD region(VCCD).

Fig. 5(c) shows a state of a screen(i.e., a frame) dispalyed by the

above operations.

In Fig. 5(c), the figure 1 represents a state that the image signal charge generated at the photo diode(PD) located in the left upper region of the reference point(P) in Fig. 4(b) is displayed as a Pixel, the figure 2 represents a state that the image signal charge generated at the photo diode (PD) located in the right lower region of the reference point(P) in Fig. 4(b) is displayed a Pixel and the figure 3 represents a state that the image signal charge generated at the photo diode(PD) located in the right upper region of the reference point(P) in Fig. 4(b) is displayed as a Pixel while the figure 4 represents a state that the image signal charge generated at the photo diode(PD) located in the left lower region of the reference point(P) in Fig. 4(b) is displayed as a Pixel.

Fig. 5(d) shows a state of screen displayed according to the above operation, considering each VCCD region (VCCD) as an imaginary photo diode region.

In Fig. 5(d), the figure 1+3/2 represents a state in which a value obtained by adding image signal charges generated at two photo diodes(PD) located in the left upper and the right upper regions respectively together and dividing it by 2 using a computing mean, which is not described herein, is displayed as a Pixel. The figure 2+4/2 represents a state in which a value obtained bu adding image signal charges generated at two photo diodes(PD) located in the left lower and right lower regions respectively together and dividing it by 2 is displayed as a Pixel.

The CCD image sensor according to the invention can improve resolution of the video by reducing its VCCD area and, thus, increasing the photodetector's area, sequently, the number of fill factor.

The CCD image sensor according to the invention can improve resolution of

the video although the scanning speed is low since it is operated by 4 phase clock signal consisting of 4 fields, so that it may be applied to camcorder or still camera which requires high resolution.

$\mathbf{s} = (\mathbf{t} - \mathbf{t})^{-1}$

#### CLAIMS:

- A CCD image sensor comprising a plurality of 1. photodetectors in rows a coupled by transfer gates to an array of VCCD regions operable as scanners to read signals from the photodetectors, wherein the photodetectors in a row are operatively associated alternately with the left and the right sides of successive said VCCD regions across the array, and each pair adjacent photodetectors of the in photodetectors not having a said VCCD region therebetween are spaced apart by a channel stop region.

- 2. A CCD image sensor according to claim 1 wherein a plurality of sets of first to fourth gate electrodes for applying VCCD clock signals are formed on said VCCD regions, said gate electrodes being electrically separated from each other by an insulating membrane.

- A CCD image sensor according to claim 2 wherein said 3. first to fourth of said photodetectors are formed in the left upper and lower regions and in the right upper and lower regions with reference to a reference point which lies between adjacent odd and even rows in which said photodetectors are disposed, and said first to fourth gate electrodes for in operative applying VCCD clock signals are formed association with first to fourth said transfer corresponding to said first to fourth photodetectors, whereby said transfer gates are turned on in due turn by the applied VCCD clock signals so that a signal charge corresponding to a pixel of the sensed image is transferred to one said VCCD region including said reference point.

- 4. A CCD image sensor according to claim 3 wherein said first to fourth gate electrodes are formed over successive said VCCD regions across the array and over successive said photodetectors and channel stop regions along the rows so that, when the VCCD clock signal consists of first to fourth fields, the transfer gate of the first photodector is turned on by a clock signal of the first field, the transfer gate of

the second photodetector is turned on by a clock signal of the second field, the transfer gate of the third photodetector is turned on by a clock signal of the third field, and the transfer gate of the fourth photodetector is turned on by a clock signal of the fourth field.

- 5. A CCD image sensor according to any one of claims 2 to 4 wherein said gate electrodes are formed of poly silicon.

- 6. A CCD image sensor according to any one of claims 1 to 5 wherein said photodetectors comprise photo diodes having PN junctions.

- 7. A CCD image sensor according to any one of claims 1 to 6 wherein said transfer gates of the photodetectors are formed of poly silicon.

- 8. A CCD image sensor according to any one of claims 1 to 7 wherein the widths of the photodetectors and of the VCCD regions are the same as each other across the array.

- 9. A CCD image sensor substantially as described herein with reference to Figures 4a to 5d of the accompanying drawings.