#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

# (19) World Intellectual Property Organization

International Bureau

(10) International Publication Number WO 2013/180016 A1

(43) International Publication Date 5 December 2013 (05.12.2013)

(51) International Patent Classification: **G06F 1/30** (2006.01) G08B 17/06 (2006.01) G06F 1/32 (2006.01) H01L 29/786 (2006.01)

(21) International Application Number:

PCT/JP2013/064426

(22) International Filing Date:

17 May 2013 (17.05.2013)

(25) Filing Language:

(26) Publication Language:

English

(30) Priority Data:

2012-126365 1 June 2012 (01.06.2012) 2012-159898 18 July 2012 (18.07.2012)

JP

JP

- (71) Applicant: SEMICONDUCTOR ENERGY LABORAT-ORY CO., LTD. [JP/JP]; 398, Hase, Atsugi-shi, Kanagawa, 2430036 (JP).

- (72) Inventors: KOYAMA, Jun; c/o SEMICONDUCTOR Published: ENERGY LABORATORY CO., LTD., 398, Hase, Atsugishi, Kanagawa, 2430036 (JP). YAMAZAKI, Shunpei.

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM,

AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW. GH. GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

with international search report (Art. 21(3))

# (54) Title: SEMICONDUCTOR DEVICE AND ALARM DEVICE

(57) Abstract: In the microcomputer in the alarm device, supply of power to a sensor portion or a CPU in a sensor is allowed or stopped by a power gate controlled by a power gate controller. In addition, a volatile memory portion and a nonvolatile memory portion are provided in the CPU, data of the volatile memory portion is stored in the nonvolatile memory portion before supply of power to the CPU is stopped, and the data of the nonvolatile memory portion is restored to the volatile memory portion after the supply of power to the CPU is resumed. Thus, during an interval between measurement periods, supply of power to the sensor portion and the CPU can be stopped, so that low power consumption can be achieved compared with the case where power is continuously supplied.

#### DESCRIPTION

#### SEMICONDUCTOR DEVICE AND ALARM DEVICE

### 5 TECHNICAL FIELD

[0001]

The disclosed invention relates to a semiconductor device. The disclosed invention relates to an alarm device which generates a signal related to an alarm by sensing a physical quantity relating to an abnormal situation as an example of the semiconductor device. In particular, the disclosed invention relates to an alarm device functioning as a fire alarm.

[0002]

10

15

In this specification, an alarm device refers to any device which senses a physical quantity relating to an abnormal situation and transmits a signal related to an alarm, and for example, a fire alarm device (hereinafter also referred to as a fire alarm), a gas alarm device, a burglar alarm device, and a security alarm device are included in its category.

### **BACKGROUND ART**

20 [0003]

There are a variety of kinds of alarm devices such as fire alarm devices, gas alarm devices, burglar alarm devices, and security alarm devices. In these alarm devices, in accordance with an abnormal situation related to an alarm, a physical quantity such as the amount of light or temperature is measured selectively, and a variety of sensors are used for an alarm device in accordance with the usage.

[0004]

25

30

For example, there are a variety of systems of a fire alarm device, that is a fire alarm, as a fire detection system such as a smoke detection system and a heat detection system. A typical smoke-detection fire alarm is a photoelectric one utilizing light scattering caused by smoke.

[0005]

A photoelectric smoke detector has a structure in which a light-emitting

element which emits light having high directivity in a circular container and a light-receiving element such as a photodiode are provided (for example, see Patent Document 1). In addition, a circuit board which controls the light-emitting element and the light-receiving element, performs arithmetic processing of measurement data, and transmits an electric signal is provided in a space isolated from a space in which smoke in the container is detected.

[0006]

5

10

In the fire alarm, the light-emitting element and the light-receiving element are arranged so that light emitted from the light-emitting element does not enter the light-receiving element when no fire exists in the container. However, when smoke exists in the container, light emitted from the light-emitting element can be scattered by smoke and enter the light-receiving element. Light from the light-emitting element enters the light-receiving element, whereby the fire alarm detects a fire.

[Reference]

15 [Patent Document]

[0007]

[Patent Document 1] Japanese Published Patent Application No. H5-73785

## DISCLOSURE OF INVENTION

20 [0008]

25

An alarm device is a device which measures a physical quantity such as the amount of light or temperature and raises an alarm when detecting an abnormal situation. In other words, the alarm device needs to raise an alarm immediately in the case where an abnormal situation occurs; however, in the case where an abnormal situation is not detected, a physical quantity such as the amount of light or temperature does not need to be measured continuously but it is only necessary to perform measurement regularly for preparing for an abnormal situation.

[0009]

However, for example, a general fire alarm measures the amount of light or temperature continuously and prepares for occurrence of smoke or heat due to a fire. Accordingly, a control microcomputer, a sensor, an amplifier, and the like provided in the fire alarm consume power continuously.

[0100]

Since the fire alarms are supplied with power only from batteries in many cases, when power is consumed continuously and the batteries are drained early, an alternate battery or maintenance such as replacement of a battery is required many times. In particular, since the fire alarm is generally placed on a high place such as a ceiling, a specialist is required for maintenance in some cases. Therefore, to maintain the fire alarm, not only power consumption and battery cost but also maintenance fee such as employment cost is increased.

[0011]

5

10

15

20

25

30

Against such a problem, regular measurement is performed in a fire alarm and supply of power to a circuit element in the fire alarm is stopped during an interval between measurement periods, which enables low power consumption. For example, an emission interval of a light-emitting element is made longer in a photoelectric smoke detector described in Patent Document 1, so that power consumption is reduced. However, a control circuit, an arithmetic processing circuit, and the like, such as a light-emission control circuit and a counter circuit, continuously consumes power. [0012]

In view of the above problems, in one embodiment of the disclosed invention, an object is to provide an alarm device in which low power consumption is achieved. In particular, an object is to provide an alarm device in which low power consumption of a microcomputer is achieved.

[0013]

In the disclosed invention, in a microcomputer in an alarm device, supply of power to a sensor portion provided with a sensor or a CPU is allowed or stopped by a power gate controlled by a power gate controller. Accordingly, supply of power to the sensor portion or the CPU is performed in a period during which a physical quantity relating to an abnormal situation is measured and the supply of power to the sensor portion or the CPU is stopped during an interval between the measurement periods, so that power consumption can be reduced compared with the case where power is supplied continuously.

[0014]

In addition, a volatile memory portion and a nonvolatile memory portion are

WO 2013/180016 PCT/JP2013/064426

4

provided in a CPU, data of the volatile memory portion is stored in the nonvolatile memory portion before the supply of power to the CPU is stopped, and the data of the nonvolatile memory portion is restored to the volatile memory portion after the supply of power to the CPU is resumed. Thus, arithmetic processing related to the measurement can be started immediately after the supply of power is resumed. [0015]

5

10

15

20

25

30

One embodiment of the disclosed invention is an alarm device including a microcomputer. The microcomputer includes a power gate controller electrically connected to a power supply line, a power gate electrically connected to the power supply line and the power gate controller, a CPU electrically connected to the power gate, and a sensor portion electrically connected to the power gate and the CPU. The power gate controller includes a timer and controls the power gate with the use of the timer. The power gate allows or stops supply of power from the power supply line to the CPU and the sensor portion, in accordance with control by the power gate controller. The sensor portion measures a physical quantity and transmits a measurement value to

the CPU. The CPU performs arithmetic processing on the measurement value and transmits a signal based on the arithmetic result. The CPU includes a volatile memory portion and a nonvolatile memory portion, stores data of the volatile memory portion in the nonvolatile memory portion before the power gate stops the supply of power, and restores the data of the nonvolatile memory portion to the volatile memory portion after the power gate allows to resume the supply of power.

[0016]

Another embodiment of the present invention is an alarm device including a housing provided with an inlet and a microcomputer provided in the housing. The microcomputer includes a power gate controller electrically connected to a power supply line, a power gate electrically connected to the power supply line and the power gate controller, a CPU electrically connected to the power gate, and a sensor portion electrically connected to the power gate and the CPU. The power gate controller includes a timer and controls the power gate with the use of the timer. The power gate allows or stops supply of power from the power supply line to the CPU and the sensor portion, in accordance with control by the power gate controller. The sensor portion measures a physical quantity relating to a fire and transmits a measurement value to the

CPU. The CPU performs arithmetic processing on the measurement value and transmits a signal based on the arithmetic result. The CPU includes a volatile memory portion and a nonvolatile memory portion, stores data of the volatile memory portion in the nonvolatile memory portion before the power gate stops the supply of power, and restores the data of the nonvolatile memory portion to the volatile memory portion after the power gate allows to resume the supply of power.

[0017]

In the above, a transistor including an oxide semiconductor film is preferably provided in the nonvolatile memory portion.

10 [0018]

5

15

20

25

30

In the above, it is preferable that the alarm device further include a light-emitting element in the housing and have a structure in which the sensor portion includes a photo sensor which measures the amount of light as a physical quantity relating to a fire and the light-emitting element and the photo sensor operate when the power gate allows supply of power to the sensor portion. Further, it is preferable that light emitted from the light-emitting element be scattered by smoke entering the housing and then sensed by the photo sensor. A transistor including an oxide semiconductor film may be provided in the photo sensor.

[0019]

In the above, it is preferable that the sensor portion include a temperature sensor which measures a temperature as a physical quantity relating to a fire and the temperature sensor measure the temperature when the power gate allows supply of power to the sensor portion. A semiconductor element including an oxide semiconductor and a semiconductor element including a silicon semiconductor may be provided in the temperature sensor.

[0020]

Power may be supplied to the power supply line from a battery. [0021]

Note that in this specification and the like, the term "high potential H" means a potential high enough to turn on an n-channel transistor provided in a processor and turn off a p-channel transistor when the potential is supplied to gate electrodes. Further, in this specification and the like, the term "low potential L" means a potential low enough

to turn off an n-channel transistor provided in a processor and turn on a p-channel transistor when the potential is supplied to gate electrodes.

[0022]

5

10

Note that in this specification and the like, the term "over" or "below" does not necessarily mean that a component is placed directly on or directly under another component. For example, the expression "a gate electrode over a gate insulating layer" does not exclude the case where another component is placed between the gate insulating layer and the gate electrode.

[0023]

In this specification and the like, the term "electrode" or "wiring" does not limit the function of a component. For example, an electrode can be used as part of a wiring, and the wiring can be used as part of the electrode. The term "electrode" or "wiring" can also mean a combination of a plurality of electrodes or wirings, for example.

15 [0024]

Functions of a "source" and a "drain" are sometimes replaced with each other when a transistor of opposite polarity is used or when the direction of current flowing is changed in circuit operation, for example. Thus, in this specification and the like, the terms "source" and "drain" can be replaced with each other.

20 [0025]

Note that in this specification and the like, the expression "electrically connected" includes the case where components are connected to each other through an "object having any electric function". Here, there is no particular limitation on an "object having any electric function" as long as electric signals can be transmitted and received between components that are connected to each other.

[0026]

25

Examples of an "object having any electric function" include an electrode, a wiring, a switching element such as a transistor, a resistor, an inductor, a capacitor, and an element with a variety of functions.

30 [0027]

According to one embodiment of the disclosed invention, an alarm device in which low power consumption is achieved can be provided. In particular, an alarm

device in which low power consumption of a microcomputer is achieved can be provided.

### **BRIEF DESCRIPTION OF DRAWINGS**

5 [0028]

15

20

25

30

In the accompanying drawings:

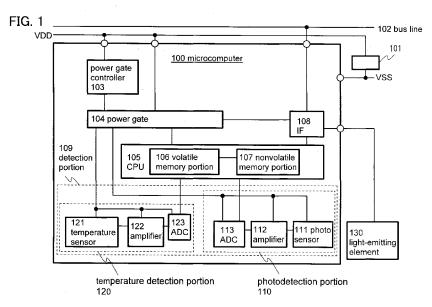

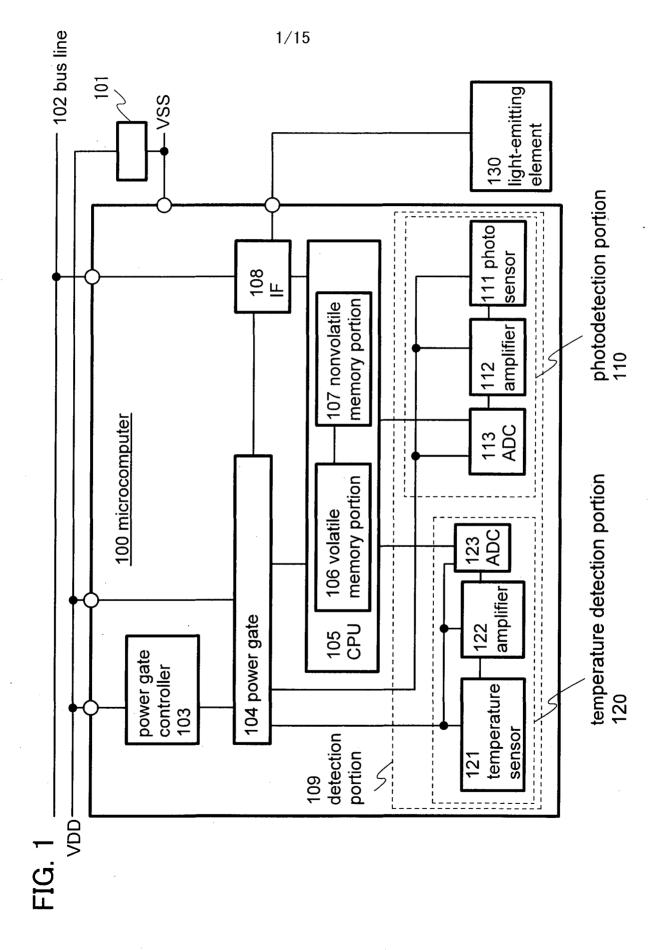

- FIG. 1 is a block diagram of an alarm device according to one embodiment of the disclosed invention;

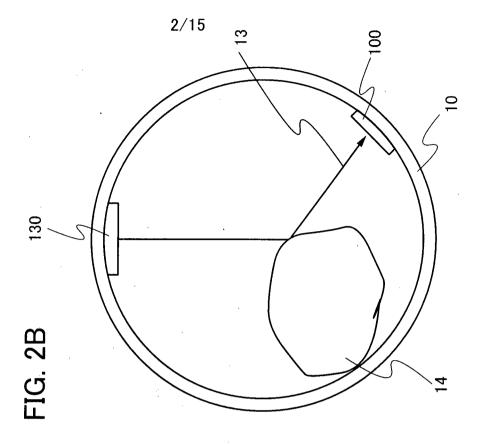

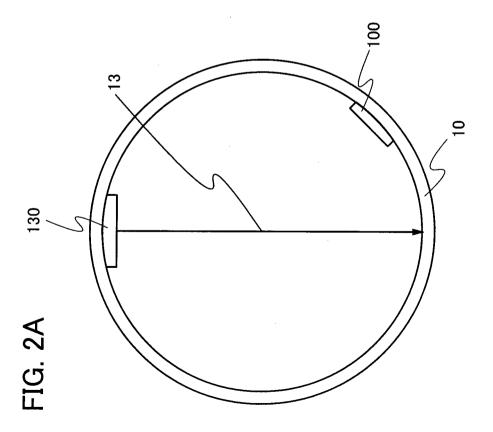

- FIGS. 2A and 2B are plan views of an alarm device according to one embodiment of the disclosed invention;

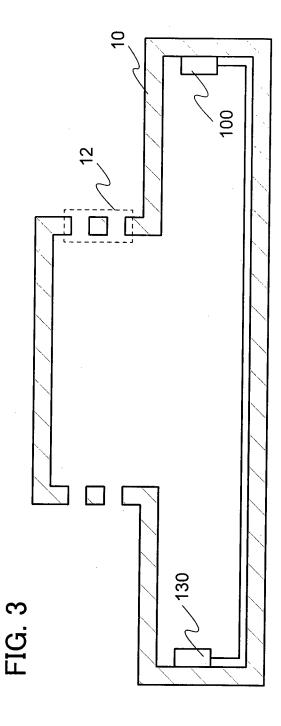

- FIG. 3 is a cross-sectional view of an alarm device according to one embodiment of the disclosed invention;

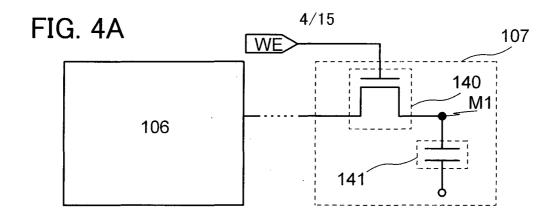

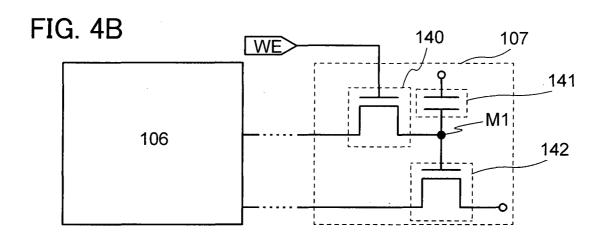

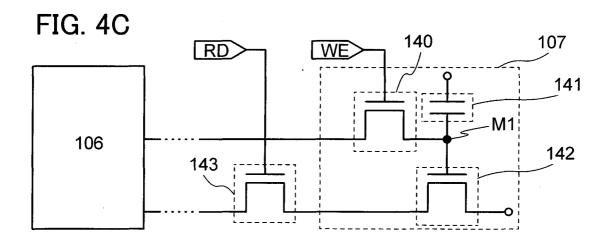

- FIGS. 4A to 4C each are an equivalent circuit diagram of part of an alarm device according to one embodiment of the disclosed invention;

- FIG. 5 is an equivalent circuit diagram of part of an alarm device according to one embodiment of the disclosed invention;

- FIG. 6 is a diagram showing operation of an alarm device according to one embodiment of the disclosed invention;

- FIG. 7 is an equivalent circuit diagram of part of an alarm device according to one embodiment of the disclosed invention;

- FIG. 8 is an equivalent circuit diagram of part of an alarm device according to one embodiment of the disclosed invention;

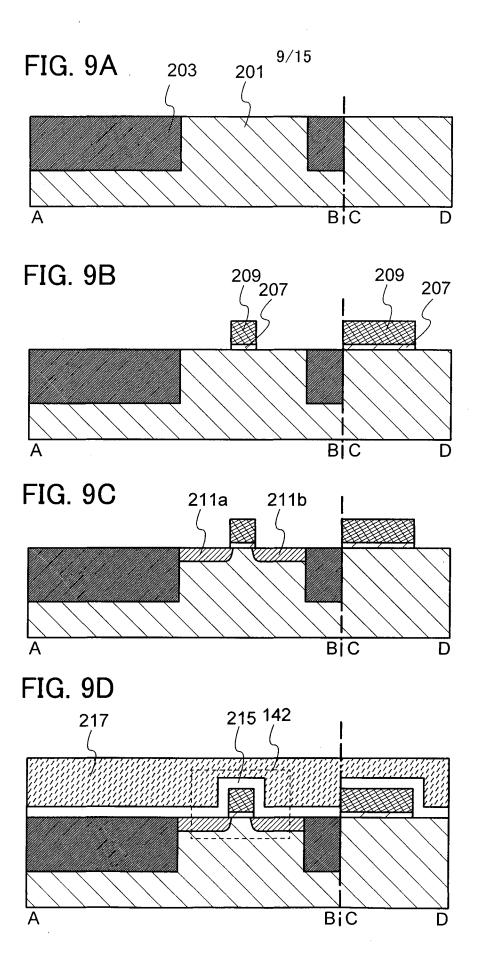

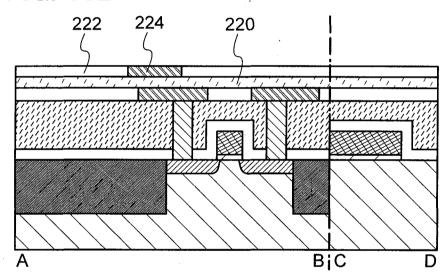

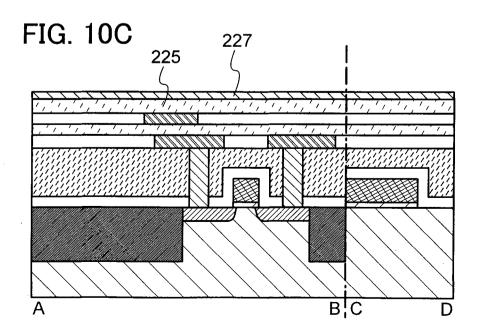

- FIGS. 9A to 9D are cross-sectional views illustrating some of steps of manufacturing an alarm device according to one embodiment of the disclosed invention;

- FIGS. 10A to 10C are cross-sectional views illustrating some of steps of manufacturing an alarm device according to one embodiment of the disclosed invention;

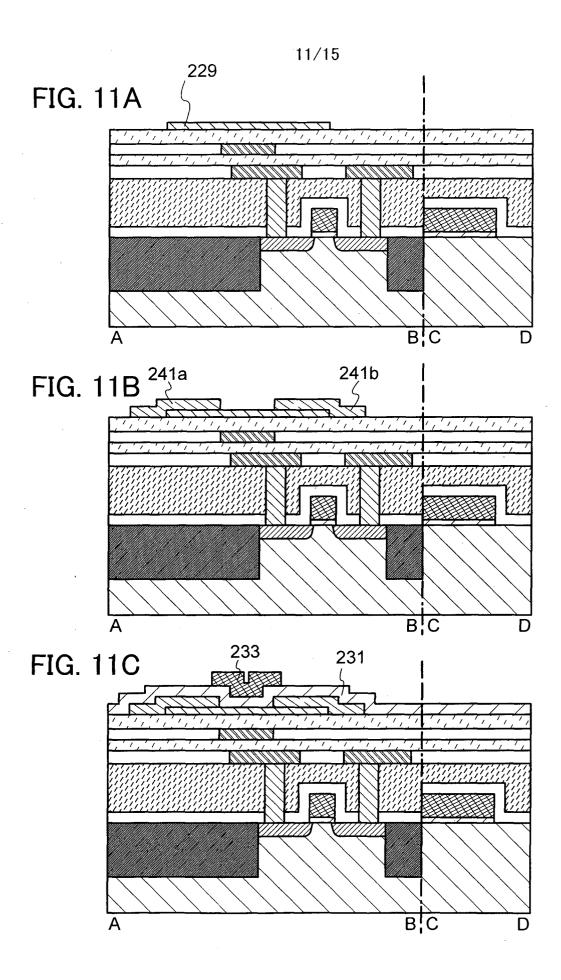

- FIGS. 11A to 11C are cross-sectional views illustrating some of steps of manufacturing an alarm device according to one embodiment of the disclosed invention;

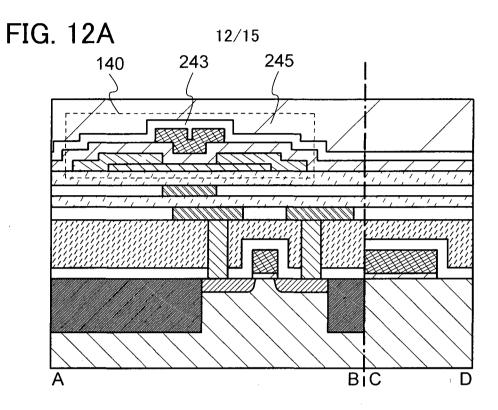

- FIGS. 12A and 12B are cross-sectional views illustrating some of steps of manufacturing an alarm device according to one embodiment of the disclosed invention;

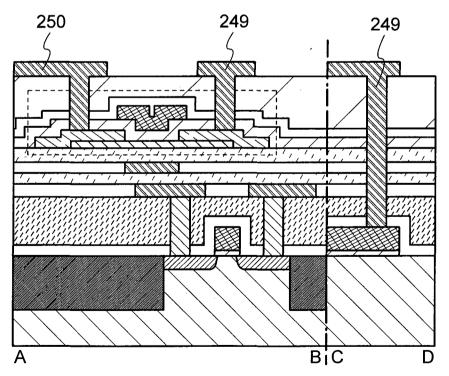

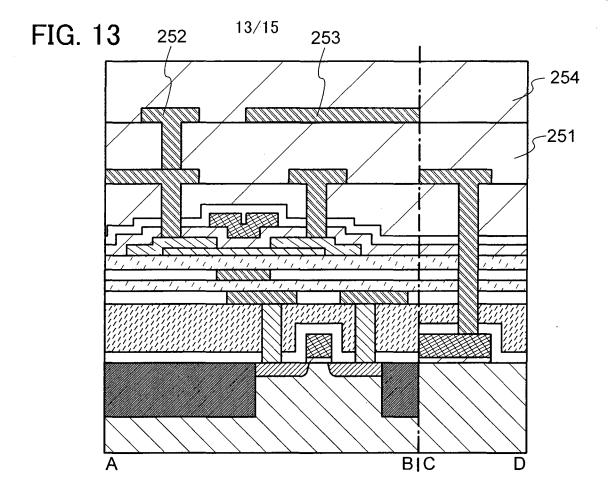

- FIG. 13 is a cross-sectional view illustrating some of steps of manufacturing an alarm device according to one embodiment of the disclosed invention;

FIG. 14 is a cross-sectional view illustrating some of steps of manufacturing an alarm device according to one embodiment of the disclosed invention; and

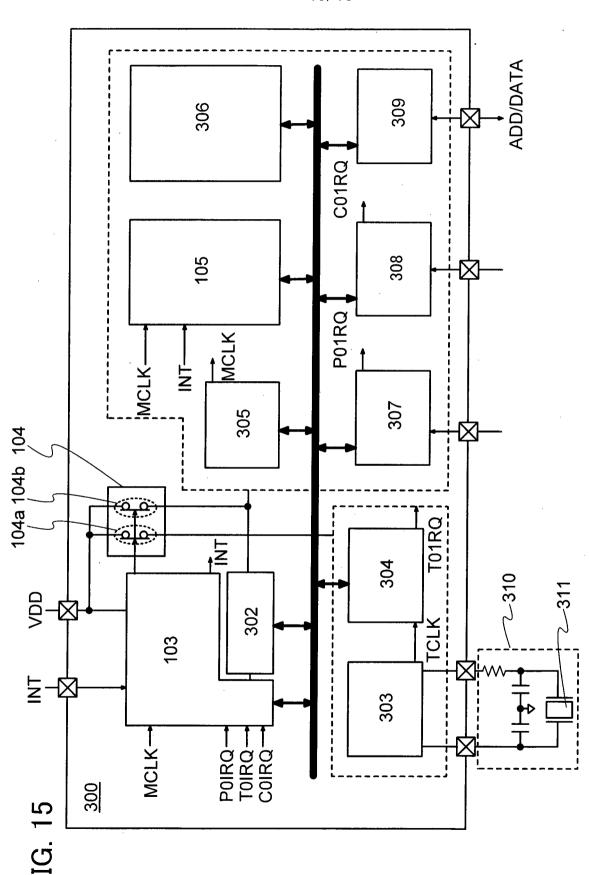

FIG. 15 is a block diagram illustrating a structure of a microcomputer included in an alarm device according to one embodiment of the disclosed invention.

5

10

# BEST MODE FOR CARRYING OUT THE INVENTION [0029]

Examples of embodiments of the present invention will be described below with reference to the drawings. Note that the present invention is not limited to the following description. It will be readily appreciated by those skilled in the art that modes and details of the present invention can be changed in various ways without departing from the spirit and scope of the present invention. The present invention therefore should not be construed as being limited to the following description of the embodiments.

15 [0030]

Note that the position, size, range, or the like of each component illustrated in drawings and the like is not accurately represented in some cases for easy understanding. The disclosed invention is therefore not necessarily limited to the position, size, range, or the like disclosed in the drawings and the like.

20 [0031]

Note that in this specification and the like, ordinal numbers such as "first", "second", and "third" are used in order to avoid confusion among components and do not limit the number.

[0032]

# 25 (Embodiment 1)

In this embodiment, a structure and operation of an alarm device according to one embodiment of the disclosed invention are described. As an example of the alarm device, a structure and operation of a fire alarm are described with reference to FIG. 1, FIGS. 2A and 2B, FIG. 3, FIGS. 4A to 4C, FIG. 5, and FIG. 6.

30 [0033]

A fire alarm in this specification refers to any device which raises an alarm over fire occurrence instantly, and for example, a residential fire alarm, an automatic fire alarm system, and a fire detector used for the automatic fire alarm system are included in its category.

[0034]

The structure of the alarm device according to one embodiment of the disclosed invention is illustrated in a block diagram of FIG. 1. FIGS. 2A and 2B are plan views of the alarm device, and FIG. 3 is a cross-sectional view thereof. The plan view in FIG. 2A illustrates the alarm device in a state where smoke does not enter a housing 10, and the plan view in FIG. 2B illustrates the alarm device in a state where smoke enters the housing 10.

10 [0035]

5

15

20

30

As illustrated in FIG. 1, the alarm device includes at least a microcomputer 100. Here, the microcomputer 100 is provided in the housing 10 including an inlet 12. The microcomputer 100 includes a power gate controller 103 electrically connected to a high potential power supply line VDD, a power gate 104 electrically connected to the high potential power supply line VDD and the power gate controller 103, a CPU 105 electrically connected to the power gate 104, and a sensor portion 109 electrically connected to the power gate 104 and the CPU 105. Further, the CPU 105 includes a volatile memory portion 106 and a nonvolatile memory portion 107.

The CPU 105 is electrically connected to a bus line 102 through an interface 108. The interface 108 is also electrically connected to the power gate 104, similarly to the CPU 105. As a bus standard of the interface 108, an I<sup>2</sup>C bus can be used, for example. A light-emitting element 130 electrically connected to the power gate 104 through the interface 108 is provided in the alarm device described in this embodiment.

25 [0037]

The light-emitting element 130 is preferably an element which emits light with high directivity, and for example, an organic EL element, an inorganic EL element, or a light-emitting diode (LED) can be used.

[0038]

The power gate controller 103 includes a timer and controls the power gate 104 with the use of the timer. The power gate 104 allows or stops supply of power from the high potential power supply line VDD to the CPU 105, the sensor portion 109, and

WO 2013/180016 PCT/JP2013/064426

10

the interface 108, in accordance with the control by the power gate controller 103. Here, as an example of the power gate 104, a switching element such as a transistor can be given.

[0039]

5

10

15

20

25

With the use of the power gate controller 103 and the power gate 104, power is supplied to the sensor portion 109, the CPU 105, and the interface 108 in a period during which the amount of light, temperature, or the like is measured, and supply of power to the sensor portion 109, the CPU 105, and the interface 108 can be stopped during an interval between measurement periods. The alarm device operates in such a manner, whereby power consumption can be reduced compared with the case where power is continuously supplied to the above structures.

In the case where a transistor is used as the power gate 104, it is preferable to use a transistor which has extremely low off-state current and is used for the nonvolatile memory portion 107 to be described later, for example, a transistor including an oxide semiconductor. With the use of such a transistor, leakage current can be reduced when supply of power is stopped by the power gate 104, so that power consumption can be reduced.

[0041]

A direct-current power source 101 may be provided in the alarm device described in this embodiment so that power is supplied from the direct-current power source 101 to the high potential power supply line VDD. An electrode of the direct-current power source 101 on a high potential side is electrically connected to the high potential power supply line VDD, and an electrode of the direct-current power source 101 on a low potential side is electrically connected to a low potential power supply line VSS. The low potential power supply line VSS is electrically connected to the microcomputer 100. Here, the high potential power supply line VDD is supplied with a high potential H. Further, the low potential power supply line VSS is supplied with a low potential L, e.g., a ground potential (GND).

30 [0042]

In the case where a battery is used as the direct-current power source 101, for example, a battery case including an electrode electrically connected to the high

potential power supply line VDD, an electrode electrically connected to the low potential power supply line VSS, and a housing which can hold the battery, is provided in the housing 10. Note that the alarm device described in this embodiment does not necessarily include the direct-current power source 101 and may have, for example, a structure in which power is supplied from an alternate-current power source provided outside the alarm device through a wiring.

[0043]

5

10

15

20

25

30

As the above battery, a secondary battery such as a lithium ion secondary battery (also called a lithium ion storage battery or simply a lithium ion battery) can be used. Further, a solar battery is preferably provided to charge the secondary battery.

[0044]

The sensor portion 109 measures a physical quantity relating to an abnormal situation and transmits a measurement value to the CPU 105. A physical quantity relating to an abnormal situation depends on the usage of the alarm device, and in an alarm device functioning as a fire alarm, a physical quantity relating to a fire is measured. Accordingly, the sensor portion 109 includes a photosensor portion 110 which measures the amount of light as a physical quantity relating to a fire and senses smoke and a temperature sensor portion 120 which measures a temperature as a physical quantity relating to a fire and senses heat. That is, an alarm device including the photosensor portion 110 and the temperature sensor portion 120 functions as a smoke-sensing and heat-sensing fire alarm.

[0045]

The photosensor portion 110 includes a photo sensor 111 electrically connected to the power gate 104, an amplifier 112 electrically connected to the power gate 104, and an AD converter 113 electrically connected to the power gate 104 and the CPU 105. The photo sensor 111, the amplifier 112, and the AD converter 113 which are provided in the photosensor portion 110 and the light-emitting element 130 operate when the power gate 104 allows supply of power to the photosensor portion 110. Here, as the photo sensor 111, one provided with a photoelectric conversion element such as a photodiode can be used, for example.

[0046]

Here, how the alarm device functioning as a fire alarm detects smoke is

WO 2013/180016 PCT/JP2013/064426

described with reference to FIGS. 2A and 2B and FIG. 3. As illustrated in FIGS. 2A and 2B and FIG. 3, the alarm device functioning as a fire alarm includes the housing 10 in which central axes align on one surface of a first cylindrical portion and a second cylindrical portion having a radius smaller than that of the first cylindrical portion is provided. The inlet 12 is provided on a side surface of the second cylindrical portion of the housing 10, and the microcomputer 100 and the light-emitting element 130 are provided in contact with an inner wall of the first cylindrical portion of the housing 10. Note that the microcomputer 100 and the light-emitting element 130 are provided so as not to face each other with respect to the center point of the bottom surface of the first cylindrical portion. Note that the housing 10 of the alarm device according to this embodiment is not limited to this structure and can be changed as appropriate depending on the usage of the alarm device, an installation requirement, or the like.

5

10

15

20

25

30

In FIGS. 2A and 2B, a solid arrow denotes light. As illustrated in FIG. 2A, although the light-emitting element 130 emits light 13 with high directivity, the light-emitting element 130 and the microcomputer 100 are not provided to face each other; thus, light 13 emitted from the light-emitting element 130 is emitted in a direction different from the direction toward the microcomputer 100. In other words, when there is no smoke in the housing 10, light 13 emitted from the light-emitting element 130 does not enter the photo sensor 111 in the microcomputer 100.

However, as illustrated in FIG. 2B, when smoke 14 enters the inside of the housing 10 through the inlet 12, light 13 emitted from the light-emitting element 130 is scattered by the smoke 14, so that the light 13 enters the photo sensor 111 in the microcomputer 100. When the light 13 enters the photo sensor 111, a potential in accordance with the amount of received light 13 is input from the photo sensor 111 to the amplifier 112, a potential amplified by the amplifier 112 is input to the AD converter 113, and a potential converted from an analog signal to a digital signal in the AD converter 113 is transmitted to the CPU 105. In such a manner, the alarm device including the photosensor portion 110 detects smoke relating to a fire.

Further the temperature sensor portion 120 includes a temperature sensor 121

electrically connected to the power gate 104, an amplifier 122 electrically connected to the power gate 104, and an AD converter 123 electrically connected to the power gate 104 and the CPU 105. The temperature sensor 121, the amplifier 122, and the AD converter 123 which are provided in the temperature sensor portion 120 operate when the power gate 104 allows supply of power to the temperature sensor portion 120. Here, for example, a thermistor (resistive element of which resistance varies depending on temperature) or an IC temperature sensor (which uses a temperature characteristics of a base-emitter voltage of an NPN transistor) can be used as the temperature sensor 121. The temperature sensor 121 can be formed using two or more kinds of semiconductor elements with different temperature characteristics.

[0050]

5

10

15

20

25

30

When a temperature value is input to the temperature sensor 121, a potential in accordance with the input temperature value is input to the amplifier 122, a potential amplified by the amplifier 122 is input to the AD converter 123, and a potential converted from an analog signal to a digital signal in the AD converter 123 is transmitted to the CPU 105. In such a manner, the alarm device including the temperature sensor portion 120 detects heat relating to a fire.

As described above, when the photosensor portion 110 which detects smoke and the temperature sensor portion 120 which detects heat are provided in the sensor portion 109, the accuracy of detection of a fire can be increased.

[0052]

Note that in the alarm device described in this embodiment, the photosensor portion 110 and the temperature sensor portion 120 are not necessarily provided as the sensor portion 109. For example, either the photosensor portion 110 or the temperature sensor portion 120 may be provided. Alternatively, neither the photosensor portion 110 nor the temperature sensor portion 120 is necessary to be provided in sensor portion 109. In this case, a sensor which measures a physical quantity, not the amount of light and temperature, is provided as the sensor portion 109, and a sensor which measures an ultraviolet ray, an infrared ray, carbon monoxide, or the like can be provided. For example, in the case where an infrared ray is sensed, a photoelectric conversion element using germanium having a light absorption

wavelength different from that of silicon can be used. [0053]

Note that in the case where the photosensor portion 110 is not provided, the light-emitting element 130 does not need to be provided.

5 [0054]

10

15

25

30

WO 2013/180016

The alarm device according to this embodiment is not limited to a fire alarm and can be used as various alarm devices, for example, a gas alarm device, a burglar alarm device, and a security alarm device. In the case where the alarm device described in this embodiment is used as an alarm device which is not a fire alarm, a sensor which can measure a physical quantity in accordance with an abnormal situation to be checked by the alarm device is provided in the sensor portion 109.

Further, the alarm device according to this embodiment has a structure in which the sensor portion 109 including the temperature sensor portion 120 and the photosensor portion 110 is provided in the microcomputer 100; however, the alarm device according to the present invention is not limited thereto. A structure in which the sensor portion 109 is provided outside the microcomputer 100 and the sensor portion 109 and the microcomputer 100 are electrically connected to each other through a wiring or the like may be employed.

20 [0056]

Alternatively, only part of the sensor portion 109 may be provided outside the microcomputer 100. For example, the microcomputer 100 according to this embodiment may have a structure in which the AD converter 113 in the photosensor portion 110 and the AD converter 123 in the temperature sensor portion 120 are provided inside the microcomputer 100, and the photo sensor 111 and the amplifier 112 in the photosensor portion 110 and the temperature sensor 121 and the amplifier 122 in the temperature sensor portion 120 are provided outside the microcomputer 100. [0057]

The CPU 105 performs arithmetic processing on a measurement value and transmits a signal based on the arithmetic result. The signal transmitted from the CPU 105 is output to the bus line 102 through the interface 108. In the case where the alarm device according to this embodiment is used as a fire detector of an automatic fire alarm

system, the signal is transmitted to a receiver of the automatic fire alarm system and the receiver raises an alarm. Further, in the case where the alarm device according to this embodiment is used as a residential fire alarm, the signal is transmitted to the alarm device electrically connected to the CPU 105 instead of the bus line 102 and an alarm is raised. Here, as a way of raising an alarm by the alarm device, voice, beep sound, light emission, smell, or the like can be used.

[0058]

5

10

15

20

25

30

Further, transmission of a signal to the above receiver or alarm device is not necessarily performed through a wire and may be performed wirelessly. For example, the alarm device may be provided with a wireless chip.

[0059]

Further, the CPU 105 includes the volatile memory portion 106 and the nonvolatile memory portion 107. Before the power gate 104 stops supply of power, data of the volatile memory portion 106 is stored in the nonvolatile memory portion 107, and after the power gate 104 allows the supply of power, the data of the nonvolatile memory portion 107 is restored to the volatile memory portion 106.

The volatile memory portion 106 includes a plurality of volatile memory elements and also includes a circuit relating to control thereof and the like. Note that access speed of the volatile memory element included in the volatile memory portion 106 is higher than at least that of a nonvolatile memory element included in the nonvolatile memory portion 107 to be described later.

[0061]

A semiconductor material used for a transistor included in the volatile memory element is not particularly limited. However, the semiconductor material preferably has a band gap width different from that of a semiconductor material used for a transistor with low off-state current in the nonvolatile memory element to be described later. Such a semiconductor material can be, for example, silicon, germanium, silicon germanium, or gallium arsenide and is preferably single crystal. In order to increase the speed of processing data, it is preferable to use, for example, a transistor with high switching speed, such as a transistor formed using single crystal silicon.

WO 2013/180016 PCT/JP2013/064426

16

The nonvolatile memory portion 107 includes a plurality of nonvolatile memory elements and also includes a circuit relating to control thereof and the like. The nonvolatile memory element is electrically connected to a node holding electric charge corresponding to data of the volatile memory element and is used for storing data from the volatile memory element in a period during which power is not supplied. Accordingly, the nonvolatile memory element included in the nonvolatile memory portion 107 has a longer data holding time than at least the volatile memory element to which power is not supplied.

[0063]

5

10

15

20

25

30

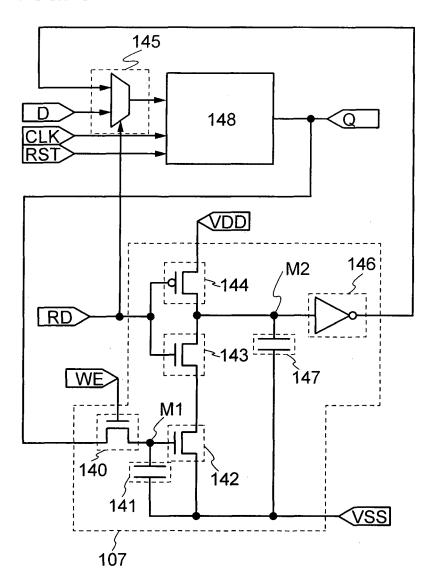

Here, examples of a structure of the nonvolatile memory element in the nonvolatile memory portion 107 are described using circuit diagrams in FIGS. 4A to 4C.

[0064]

The nonvolatile memory portion 107 in FIG. 4A includes a transistor 140 and a capacitor 141 and is electrically connected to the volatile memory portion 106 through the transistor 140. Note that in this embodiment, the transistor 140 is an n-channel transistor; however, a p-channel transistor may be used as appropriate. In such a case, a potential supplied to a gate electrode is inverted as appropriate.

[0065]

Specifically, a source electrode (or a drain electrode) of the transistor 140 is electrically connected to a node holding electric charge corresponding to data of the volatile memory portion 106. The drain electrode (or the source electrode) of the transistor 140 is electrically connected to one electrode of the capacitor 141 (hereinafter the drain electrode of the transistor 140 is referred to as a node M1 in some cases). A write control signal WE is supplied to the gate electrode of the transistor 140, and the transistor 140 is turned on or off in accordance with the potential of the write control signal WE. A predetermined potential is supplied to the other electrode of the capacitor 141. Here, the predetermined potential is, for example, a ground potential (GND). By providing the capacitor 141 in this manner, much electric charge can be held in the node M1, so that data holding characteristics can be improved.

The transistor 140 is preferably a transistor with extremely low off-state current.

WO 2013/180016 PCT/JP2013/064426

The transistor with extremely low off-state current preferably includes, in a channel formation region, a wide band gap semiconductor having a wider band gap and lower intrinsic carrier density than single crystal silicon. For example, the band gap of the wide band gap semiconductor is more than 1.1 eV, preferably 2.5 eV or more and 4 eV or less, more preferably 3 eV or more and 3.8 eV or less. For example, as the wide band gap semiconductor, a compound semiconductor such as silicon carbide (SiC) or gallium nitride (GaN), an oxide semiconductor formed using metal oxide such as an In-Ga-Zn-O-based oxide semiconductor, or the like can be used. Alternatively, since a transistor including amorphous silicon, microcrystalline silicon, or the like can have lower off-state current than a transistor including single crystal silicon, the transistor 140 may employ amorphous silicon, microcrystalline silicon, or the like.

5

10

15

20

25

30

Here, the band gap of single crystal silicon is approximately 1.1 eV, and even in a state where there is no carrier caused by a donor or an acceptor (i.e., even in the case of an intrinsic semiconductor), the concentration of thermally excited carriers is approximately  $1 \times 10^{11}$  cm<sup>-3</sup>. The band gap of the In-Ga-Zn-O-based oxide semiconductor which is the wide band gap semiconductor is approximately 3.2 eV and the concentration of thermally excited carriers is approximately  $1 \times 10^{-7}$  cm<sup>-3</sup>. The off-state resistance (resistance between a source and a drain of a transistor in an off state) of a transistor is inversely proportional to the concentration of thermally excited carriers in the channel formation region. Accordingly, the resistivity of the In-Ga-Zn-O-based oxide semiconductor at the time when the transistor is off is 18 orders of magnitude higher than that of silicon.

By using such a wide band gap semiconductor for the transistor 140, for example, off-state current (per unit channel width (1  $\mu$ m), here) at room temperature (25 °C) is 100 zA (1 zA (zeptoampere) is  $1 \times 10^{-21}$  A) or lower, preferably 10 zA or lower. [0069]

For example, when the off-state current of the transistor 140 at room temperature (25 °C) (per unit channel width (1  $\mu$ m), here) is 10 zA or lower, data can be held for 10<sup>4</sup> seconds or longer. Needless to say, the holding time depends on the

characteristics of the transistor 140, a capacitance value of a capacitor in the electrode of the transistor 140 and the like.

[0070]

In this embodiment, a transistor including an oxide semiconductor whose off-state current is extremely low is used as the transistor 140.

[0071]

5

10

15

20

30

When data is stored from the volatile memory portion 106, by turning on the transistor 140 by supply of the high potential H as the write control signal WE, the potential of the node holding electric charge corresponding to data of the volatile memory portion 106 is supplied to the node M1. After that, by turning off the transistor 140 by supply of the low potential L as the write control signal WE, electric charge supplied to the node M1 is held. Here, since the off-state current of the transistor 140 is extremely low, electric charge in the node M1 is held for a long time. [0072]

When data is restored to the volatile memory portion 106, by turning on the transistor 140 by supply of the high potential H as the write control signal WE, the potential of the node M1 is supplied to the node holding electric charge corresponding to data of the volatile memory portion 106.

[0073]

By using a wide band gap semiconductor or the like for the transistor 140, the off-state current of the transistor 140 can be extremely low. Thus, by turning off the transistor 140, the potential of the node M1 can be held for an extremely long time. With such a structure, the nonvolatile memory portion 107 can be used as a nonvolatile memory element capable of holding data without supply of power.

25 [0074]

As illustrated in FIG. 4B, the nonvolatile memory portion 107 may include a transistor 142 in addition to the components in FIG. 4A. A gate electrode of the transistor 142 is electrically connected to the node M1. A drain electrode (or a source electrode) of the transistor 142 is electrically connected to the node holding electric charge corresponding to data of the volatile memory portion 106. A predetermined potential is supplied to the source electrode (or the drain electrode) of the transistor 142. [0075]

In the nonvolatile memory portion 107 in FIG. 4B, the state of the transistor 142 depends on a potential held in the node M1 in the storage of data. In other words, the transistor 142 is turned on when the high potential H is supplied in the storage of data, and the transistor 142 is turned off when the low potential L is supplied in the storage of data.

[0076]

5

10

In restorage of data, the potential of the drain electrode of the transistor 142 is supplied to the node holding electric charge corresponding to data of the volatile memory portion 106. In other words, when the high potential H is supplied to the node M1 in the storage of data, the transistor 142 is on, and the potential of the source electrode of the transistor 142 is supplied to the volatile memory portion 106. Further, when the low potential L is supplied to the node M1 in the storage of data, the transistor 142 is off, and the potential of the source electrode of the transistor 142 is not supplied to the volatile memory portion 106.

15 [0077]

In order to increase the speed of reading data, it is preferable to use a transistor that is similar to the transistor used for the volatile memory element as the transistor 142.

[0078]

20

25

30

Note that the source electrode of the transistor 142 and the other electrode of the capacitor 141 may have the same potential or different potentials. The source electrode of the transistor 142 and the other electrode of the capacitor 141 may be electrically connected to each other. Further, the capacitor 141 is not necessarily provided. For example, in the case where the parasitic capacitance of the transistor 142 is high, the parasitic capacitance can be used instead of the capacitor 141.

Here, the drain electrode of the transistor 140 and the gate electrode of the transistor 142 (i.e., the node M1) have the same effect as a floating gate of a floating-gate transistor used as a nonvolatile memory element. However, since data can be directly rewritten by turning on or off the transistor 140, injection of electric charge into a floating gate and extraction of electric charge from the floating gate with the use of high voltage are not necessary. In other words, in the nonvolatile memory

portion 107, high voltage needed for writing or erasing data in a conventional floating gate transistor is not necessary. Thus, by using the nonvolatile memory portion 107 in this embodiment, power consumption needed for storage of data can be reduced. [0080]

For similar reasons, a decrease in operation speed due to data writing or data erasing can be reduced; thus, the nonvolatile memory portion 107 can operate at high speed. Further, for similar reasons, the problem of deterioration of a gate insulating film (a tunnel insulating film) that is pointed out in a conventional floating gate transistor does not exist. In other words, unlike in a conventional floating gate transistor, the nonvolatile memory portion 107 described in this embodiment has no limitation on the number of writings in principle. From the above, the nonvolatile memory portion 107 can be adequately used as a memory device that needs many rewritings and high-speed operation, such as a register.

[0081]

5

10

15

20

25

30

As illustrated in FIG. 4C, the nonvolatile memory portion 107 may include a transistor 143 in addition to the components in FIG. 4B. A read control signal RD is supplied to a gate electrode of the transistor 143. A drain electrode (or a source electrode) of the transistor 143 is electrically connected to the node holding electric charge corresponding to data of the volatile memory portion 106. The source electrode (or the drain electrode) of the transistor 143 is electrically connected to the drain electrode of the transistor 142.

[0082]

Here, the read control signal RD is a signal for supplying the high potential H to the gate electrode of the transistor 143 at the time of the restorage of data. In this case, the transistor 143 can be turned on. Accordingly, at the time of the restorage of data, a potential based on the on state or off state of the transistor 142 can be supplied to the node holding electric charge corresponding to data of the volatile memory portion 106.

[0083]

Note that in order to increase the speed of reading data, it is preferable to use a transistor that is similar to the transistor used for the volatile memory element in the volatile memory portion 106 as the transistor 143.

[0084]

FIG. 5 shows an example of a circuit configuration of a nonvolatile register which can hold 1-bit data and includes the nonvolatile memory portion 107 in FIG. 4C. Note that in FIG. 5, the same reference numerals are used for the same components as those in FIG. 4C.

[0085]

5

The register in FIG. 5 includes a flip-flop 148, the nonvolatile memory portion 107, and a selector 145. In the register in FIG. 5, the flip-flop 148 is provided as the volatile memory portion 106 in FIG. 4C.

10 [0086]

The flip-flop 148 is supplied with a reset signal RST, a clock signal CLK, and a data signal. The flip-flop 148 has a function of holding data of a data signal D that is input in accordance with the clock signal CLK and outputting the data as a data signal Q.

15 [0087]

20

25

30

The nonvolatile memory portion 107 is supplied with the write control signal WE, the read control signal RD, and the data signal Q. [0088]

The nonvolatile memory portion 107 has a function of storing data of an inputted data signal Q in accordance with the write control signal WE and outputting the stored data as the data signal Q in accordance with the read control signal RD.

[0089]

The selector 145 selects the data signal D or the data signal Q output from the nonvolatile memory portion 107 and inputs the selected signal to the flip-flop 148 in accordance with the read control signal RD.

[0090]

Further, as illustrated in FIG. 5, the transistor 140 and the capacitor 141 are provided in the nonvolatile memory portion 107.

[0091]

The transistor 140 is an n-channel transistor. One of a source electrode and a drain electrode of the transistor 140 is electrically connected to an output terminal of the flip-flop 148. The transistor 140 has a function of controlling holding a data signal

output from the flip-flop 148 in accordance with the write control signal WE. [0092]

The transistor 140 can be a transistor which includes an oxide semiconductor and has low off-state current, as in the structure in FIG. 4C.

5 [0093]

10

15

One of a pair of electrodes of the capacitor 141 is electrically connected to the other of the source electrode and the drain electrode of the transistor 140 (hereinafter the node is referred to as a node M1 in some cases). The low potential L is supplied to the other of the pair of electrodes of the capacitor 141. The capacitor 141 has a function of holding electric charge based on data of the stored data signal D in the node M1. Since the off-state current of the transistor 140 is extremely low, the electric charge in the node M1 is held and thus the data is held even when supply of the power supply voltage is stopped.

[0094]

A transistor 144 is a p-channel transistor. One of a source electrode and a drain electrode of the transistor 144 is supplied with the high potential H. A gate electrode of the transistor 144 is supplied with the read control signal RD. The difference between the high potential H and the low potential L is a power supply voltage.

20 [0095]

The transistor 143 is an n-channel transistor. One of the source electrode and the drain electrode of the transistor 143 is electrically connected to the other of the source electrode and the drain electrode of the transistor 144 (hereinafter the node is referred to as the node M2 in some cases). The gate electrode of the transistor 143 is supplied with the read control signal RD.

[0096]

25

30

The transistor 142 is an n-channel transistor. One of the source electrode and the drain electrode of the transistor 142 is electrically connected to the other of the source electrode and the drain electrode of the transistor 143, and the other thereof is supplied with the low potential L.

[0097]

An input terminal of an inverter 146 is electrically connected to the one of the

WO 2013/180016 PCT/JP2013/064426

source electrode and the drain electrode of the transistor 144. An output terminal of the inverter 146 is electrically connected to an input terminal of the selector 145. [0098]

One of a pair of electrodes of a capacitor 147 is electrically connected to the input terminal of the inverter 146, and the other thereof is supplied with the low potential L. The capacitor 147 has a function of holding electric charge based on data of a data signal input to the inverter 146.

[0099]

In the register having the above-described structure in FIG. 5, when data is stored from the flip-flop 148, the transistor 140 is turned on by supply of the high potential H as the write control signal WE, so that electric charge based on data of the data signal Q in the flip-flop 148 is supplied to the node M1. After that, by turning off the transistor 140 by supply of the low potential L as the potential of the write control signal WE, electric charge supplied to the node M1 is held. While the low potential L is supplied as the potential of the read control signal RD, the transistor 143 is turned off and the transistor 144 is turned on, so that the potential of the node M2 becomes the high potential H.

[0100]

5

10

15

20

25

When data is restored from the flip-flop 148, by supply of the high potential H as the read control signal RD, the transistor 144 is turned off and the transistor 143 is turned on, so that a potential based on the electric charge held in the node M1 is supplied to the node M2. In the case where electric charge corresponding to the high potential H of the data signal Q is held in the node M1, the transistor 142 is turned on, the low potential L is supplied to the node M2, and the high potential H is restored to the flip-flop 148 through the inverter 146. Alternatively, in the case where electric charge corresponding to the low potential L of the data signal Q is held in the node M1, the transistor 142 is turned off, the high potential H in the node M2 when the low potential L is supplied is held as the potential of the read control signal RD, and the low potential L is restored to the flip-flop 148 through the inverter 146.

30 [0101]

By provision of the volatile memory portion 106 and the nonvolatile memory portion 107 in the CPU 105 as described above, data can be stored from the volatile

memory portion 106 in the nonvolatile memory portion 107 before supply of power to the CPU 105 is stopped and data can be quickly restored from the nonvolatile memory portion 107 to the volatile memory portion 106 when the supply of power to the CPU 105 is resumed.

5 [0102]

By storing and restoring data in such a manner, the CPU 105 does not need to be started up from a state where the volatile memory portion 106 is initialized every time the supply of power is stopped; thus, after the supply of power is resumed, the CPU 105 can start arithmetic processing relating to measurement immediately.

10 [0103]

In the above, the structure of the nonvolatile memory portion 107 is not limited to the structures in FIGS. 4A to 4C and FIG. 5. For example, a phase change memory (PCM), a resistance random access memory (ReRAM), a magnetoresistive random access memory (MRAM), a ferroelectric random access memory (FeRAM), or a flash memory can be used.

[0104]

15

20

25

30

A plurality of volatile memory elements in the volatile memory portion 106 can be included in, for example, a register such as a buffer register or a general-purpose register. A cache memory including a static random access memory (SRAM) or the like can also be provided in the volatile memory portion 106. The register and cache memory can store data in the nonvolatile memory portion 107.

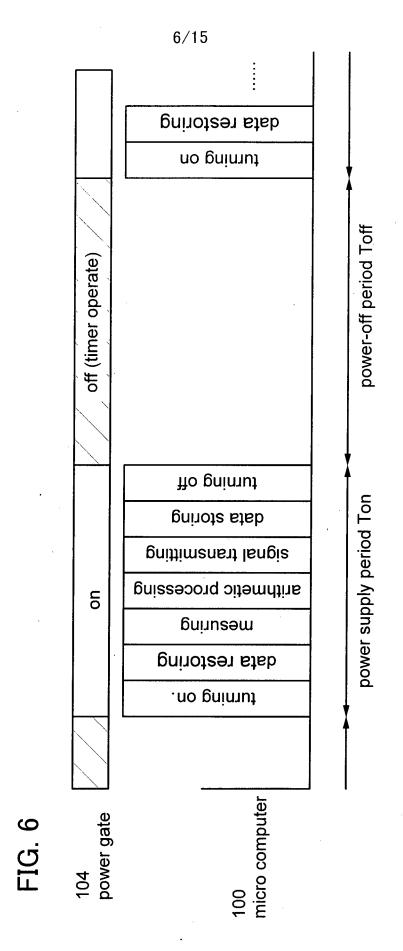

Next, operation of the alarm device according to this embodiment is described with reference to FIG. 6. FIG. 6 is a diagram showing the state of the power gate 104 and the operation of the microcomputer 100 in a power supply period Ton and a power-off period Toff.

[0106]

The alarm device according to this embodiment operates in the following divided periods: the power supply period Ton during which the power gate 104 is in an on state and power is supplied to the CPU 105, the sensor portion 109, and the interface 108; and the power-off period Toff during which the power gate 104 is in an off state and supply of power to the CPU 105, the sensor portion 109, and the interface 108 is

stopped.

[0107]

5

10

15

20

25

30

The operation of the microcomputer 100 in the power supply period Ton during which the power gate 104 is in an on state is described. First, by control by the power gate controller 103, the power gate 104 is turned on and power is on. At this time, supply of power to the CPU 105, the sensor portion 109, and the interface 108 from the high potential power supply line VDD is started through the power gate 104. In the case where the photosensor portion 110 is provided in the sensor portion 109, supply of power to the photo sensor 111, the amplifier 112, the AD converter 113, and the light-emitting element 130 is also started. Further, in the case where the temperature sensor portion 120 is provided in the sensor portion 109, supply of power to the temperature sensor 121, the amplifier 122, and the AD converter 123 is also started. [0108]

Note that power is not necessarily supplied to the CPU 105, the sensor portion 109, and the interface 108 at the same time. For example, at the timing of the use of the CPU 105, the photosensor portion 110, the temperature sensor portion 120, and the interface 108, power can be supplied at different timings.

[0109]

Next, in the CPU 105, data is restored from the nonvolatile memory portion 107 to the volatile memory portion 106. The above description of FIGS. 4A to 4C and FIG. 5 can be referred to for details of the storage of data. By performing the restorage of data in the CPU 105 in such a manner, the CPU 105 does not need to be started up from the state where the volatile memory portion 106 is initialized every time the power supply period Ton begins; thus, after the supply of power is resumed, the CPU 105 can start arithmetic processing immediately.

[0110]

Next, in the sensor portion 109, a physical quantity relating to an abnormal situation is measured. In the alarm device functioning as a fire alarm, in the photosensor portion 110, light from the light-emitting element 130 is received by the photo sensor 111, a potential in accordance with the amount of received light is input from the photo sensor 111 to the amplifier 112, and a potential amplified by the amplifier 112 is input to the AD converter 113. A potential converted from an analog

signal to a digital signal in the AD converter 113 is transmitted to the CPU 105 as a measurement value obtained by the photosensor portion 110.

[0111]

5

10

WO 2013/180016

Further, in the temperature sensor portion 120, a potential in accordance with a temperature is input from the temperature sensor 121 to the amplifier 122 and a potential amplified by the amplifier 122 is input to the AD converter 123. A potential converted from an analog signal to a digital signal in the AD converter 123 is transmitted to the CPU 105.

[0112]

Next, in the CPU 105, arithmetic processing is performed on the measurement value transmitted from the sensor portion 109. For example, in the arithmetic processing, whether a fire occurs or not is determined based on the measurement value transmitted from the sensor portion 109 and a fire occurrence signal or a no fire signal is transmitted.

15 [0113]

Next, a signal based on the arithmetic result is transmitted from the CPU 105 to the bus line 102 through the interface 108. In the case where the alarm device according to this embodiment is used as a fire detector of an automatic fire alarm system, the signal is transmitted to a receiver of the automatic fire alarm system, and when the signal is a fire occurrence signal, the receiver raises an alarm.

[0114]

20

25

Further, in the case where the alarm device according to this embodiment is used as a residential fire alarm, the signal is transmitted to the alarm device electrically connected to the CPU 105 instead of the bus line 102, and when the signal is a fire occurrence signal, the alarm device raises an alarm.

[0115]

Next, in the CPU 105, data is stored from the volatile memory portion 106 to the nonvolatile memory portion 107. The above description of FIGS. 4A to 4C and FIG. 5 can be referred to for details of the storage of data.

30 [0116]

Next, by control by the power gate controller 103, the power gate 104 is turned off and power is off. At this time, supply of power to the CPU 105, the sensor portion

WO 2013/180016 PCT/JP2013/064426

109, and the interface 108 from the high potential power supply line VDD is stopped through the power gate 104. In the case where the photosensor portion 110 is provided in the sensor portion 109, supply of power to the photo sensor 111, the amplifier 112, the AD converter 113, and the light-emitting element 130 is also stopped. Further, in the case where the temperature sensor portion 120 is provided in the sensor portion 109, supply of power to the temperature sensor 121, the amplifier 122, and the AD converter 123 is also stopped.

[0117]

5

10

15

20

25

Note that supply of power to the CPU 105, the sensor portion 109, and the interface 108 is not necessarily stopped at the same time. For example, at the timing of the end of the use of the CPU 105, the photosensor portion 110, the temperature sensor portion 120, and the interface 108, supply of power can be stopped at different timings.

[0118]

When the power supply period Ton ends as described above, the power-off period Toff begins. Here, the power gate controller 103 makes its timer operate and starts measuring time when the power gate 104 is turned off. After passage of a certain period of time is measured by the timer, the power gate controller 103 turns on the power gate 104 again, and the power supply period Ton is resumed. Note that the period measured by the timer may be changed with software.

[0119]

The alarm device operates in the power supply period Ton and the power-off period Toff with the use of the power gate controller 103 and the power gate 104 in such a manner, whereby power consumption can be reduced compared with the case where power is continuously supplied. For example, it is sufficient that measurement for fire detection is performed every 30 seconds, and the power supply period Ton takes 0.1 second or less; thus, the power-off period Toff takes 29.9 seconds. Since the power-off period Toff can be longer than the power supply period Ton in this manner, power consumption can be sufficiently reduced.

30 [0120]

In the alarm device to which power is supplied only with a battery, battery drain is reduced by achieving sufficient reduction in power consumption, so that an

alternate battery or maintenance such as battery replacement can be reduced. In particular, since the fire alarm is generally placed on a high place such as a ceiling, a specialist is required for maintenance in some cases; however, by suppressing power drain, maintenance fee such as employment cost can also be reduced.

5 [0121]

10

15

20

25

30

In addition, by provision of the volatile memory portion 106 and the nonvolatile memory portion 107 in the CPU 105, data can be stored from the volatile memory portion 106 in the nonvolatile memory portion 107 before supply of power to the CPU 105 is stopped and data can be quickly restored from the nonvolatile memory portion 107 to the volatile memory portion 106 when the supply of power to the CPU 105 is resumed. Thus, after the supply of power is resumed, the CPU 105 can start arithmetic processing immediately.

[0122]

By provision of the volatile memory portion 106 and the nonvolatile memory portion 107 which can store and restore data in this manner, even when power consumption of the CPU 105 is reduced by providing the power supply period Ton and the power-off period Toff, the alarm device operate without a large increase in time required for start up of the CPU 105.

[0123]

The methods, structures, and the like described in this embodiment can be combined as appropriate with any of the methods, structures, and the like described in the other embodiments.

[0124]

(Embodiment 2)

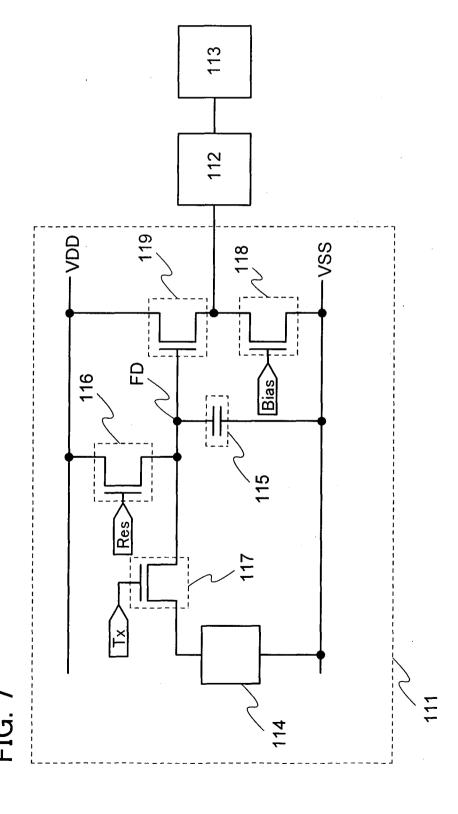

In this embodiment, an example of a configuration of the photosensor portion described in the above embodiment, particularly the photo sensor 111, is described with reference to FIG. 7.

[0125]

FIG. 7 shows an example of a circuit configuration of a photosensor portion of an alarm device, according to one embodiment of the disclosed invention. Note that in FIG. 7, the same reference numerals are used for the same components as those in FIG. 1.

[0126]

The photosensor portion in FIG. 7 includes the photo sensor 111, the amplifier 112, and the AD converter 113. The photo sensor 111 includes a photoelectric conversion element 114, a capacitor 115, a transistor 116, a transistor 117, a transistor 118, and a transistor 119. As the photoelectric conversion element 114, a photodiode or the like can be used here, for example.

[0127]

5

10

15

20

25

30

One of terminals of the photoelectric conversion element 114 is electrically connected to the low potential power supply line VSS, and the other of the terminals thereof is electrically connected to one of a source electrode and a drain electrode of the transistor 117. A gate electrode of the transistor 117 is supplied with an electric charge accumulation control Tx, and the other of the source electrode and the drain electrode thereof is electrically connected to one of a pair of electrodes of the capacitor 115, one of a source electrode and a drain electrode of the transistor 116, and a gate electrode of the transistor 119 (hereinafter the node is referred to as a node FD in some cases). The other of the pair of electrodes of the capacitor 115 is electrically connected to the low potential power supply line VSS. A gate electrode of the transistor 116 is supplied with a reset signal Res, and the other of the source electrode and the drain electrode thereof is electrically connected to the high potential power supply line VDD. One of a source electrode and a drain electrode of the transistor 119 is electrically connected to one of a source electrode and a drain electrode of the transistor 118 and the amplifier 112. The other of the source electrode and the drain electrode of the transistor 119 is electrically connected to the high potential power supply line VDD. A gate electrode of the transistor 118 is supplied with a bias signal Bias, and the other of the source electrode and the drain electrode thereof is electrically connected to the low potential power supply line VSS.

[0128]

The photo sensor 111 operates in the following manner. First, a potential at which the transistor 116 is turned on is supplied as the reset signal Res, so that the transistor 116 is turned on. Accordingly, the high potential H of the high potential power supply line VDD is supplied to the node FD, so that the photo sensor 111 is reset. [0129]

WO 2013/180016

5

10

15

20

25

30

Next, the transistor 116 is turned off and the transistor 117 is supplied with a potential at which the transistor 117 is turned on as the electric charge accumulation control signal Tx. Thus, when the light 13 from the light-emitting element 130 described in the above embodiment enters the photoelectric conversion element 114, photocurrent flows to the photoelectric conversion element 114 in accordance with the amount of received light 13, and the capacitor 115 performs discharging in accordance with the photocurrent. Consequently, a potential of the node FD is decreased in accordance with the photocurrent. Note that in the case where light from the light-emitting element 130 does not enter the photoelectric conversion element 114, the amount of flowing photocurrent is smaller than that in the case where light 13 from the light-emitting element 130 enters the photoelectric conversion element 114; therefore, a decrease in the potential of the node FD is also small.

When the transistor 117 is turned off after a certain period, the discharge of the capacitor 115 is stopped and the potential of the node FD is determined. The potential of the node FD is output to the amplifier 112 from the transistor 118 and the transistor 119 included in a source follower circuit. A potential amplified by the amplifier 112 is input to the AD converter 113, and a potential converted from an analog signal to a digital signal in the AD converter 113 is transmitted, as a measurement value obtained by the photosensor portion, to the CPU 105 described in the above embodiment.

The above-described photosensor portion can be used for the alarm device described in Embodiment 1 in which low power consumption is achieved.

[0132]

Since the photosensor portion described in this embodiment can be incorporated into the microcomputer 100 described in the above embodiment, the number of components can be reduced and the size of the housing 10 can be reduced.

[0133]

Note that the capacitor 115 is not necessarily provided. For example, in the case where parasitic capacitance of the transistor 119 or the like is sufficiently large, a structure without the capacitor 115 may be employed. Further, as each of the transistors 116 and 117, the transistor with extremely low off-state current which is

described in the above embodiment is preferably used. As the transistor with extremely low off-state current, a transistor including an oxide semiconductor is preferably is used as described in the above embodiment. With such a structure, the potential of the node FD can be held for a long time.

5 [0134]

The configuration of the photosensor portion described in this embodiment is merely an example and can be modified as appropriate depending on conditions of the alarm device or the like.

[0135]

10

15

20

25

30

The methods, structures, and the like described in this embodiment can be combined as appropriate with any of the methods, structures, and the like described in the other embodiments.

[0136]

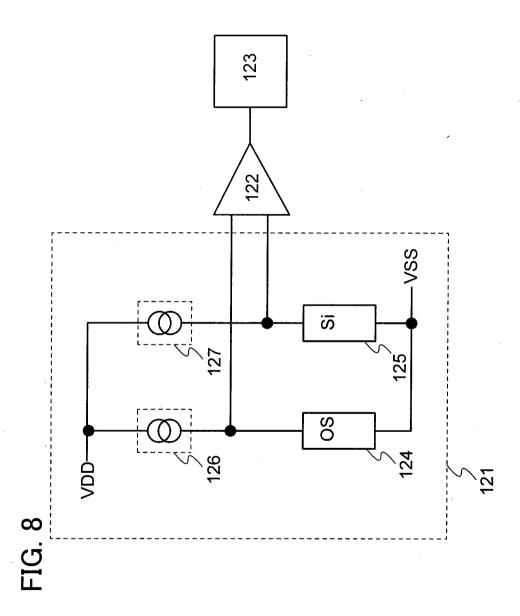

(Embodiment 3)

In this embodiment, an example of a configuration of the temperature sensor portion described in the above embodiment, particularly the temperature sensor 121, is described with reference to FIG. 8.

[0137]

FIG. 8 shows an example of a circuit configuration of a temperature sensor portion of an alarm device, according to one embodiment of the disclosed invention. Note that in FIG. 8, the same reference numerals are used for the same components as those in FIG. 1.

[0138]

The temperature sensor portion in FIG. 8 includes the temperature sensor 121, the amplifier 122, and the AD converter 123. The temperature sensor 121 includes a semiconductor element 124 including an oxide semiconductor, a semiconductor element 125 including a semiconductor whose temperature dependency is higher than that of an oxide semiconductor, a constant current circuit 126, and a constant current circuit 127. [0139]

One of terminals of the semiconductor element 124 is electrically connected to the low potential power supply line VSS, and the other of the terminals thereof is electrically connected to one of terminals of the constant current circuit 126 and one of

PCT/JP2013/064426

terminals of the amplifier 122. The other of the terminals of the constant current circuit 126 is electrically connected to the high potential power supply line VDD. One of terminals of the semiconductor element 125 is electrically connected to the low potential power supply line VSS, and the other of the terminals thereof is electrically connected to one of terminals of the constant current circuit 127 and the other of the terminals of the amplifier 122. The other of the terminals of the constant current circuit 127 is electrically connected to the high potential power supply line VDD. [0140]

As an oxide semiconductor used for the semiconductor element 124, for example, it is possible to use the oxide semiconductor which is used for the transistor with extremely low off-state current in the above embodiment. The semiconductor element 124 can be formed by short-circuiting a gate electrode and a drain electrode of a transistor. Further, the semiconductor element 125 includes a semiconductor whose temperature dependency is higher than that of an oxide semiconductor, such as single crystal silicon, polycrystalline silicon, microcrystalline silicon, or amorphous silicon; however, one embodiment of the present invention is not limited thereto. The semiconductor element 125 may be formed, for example, by short-circuiting a gate electrode and a drain electrode of a transistor or using a simple PN junction.

When constant current flows from the constant current circuit 126 and the constant current circuit 127, voltage is generated between both ends of each of the semiconductor elements 124 and 125. Here, in the semiconductor element 124 including an oxide semiconductor, a change in electrical characteristics due to temperature is small, whereas in the oxide element 125, a change in electrical characteristics due to temperature is large. Accordingly, voltage generated between the both ends of the semiconductor element 124 is hardly affected by temperature, and voltage generated between the both ends of the semiconductor element 125 is significantly affected by temperature.

[0142]

5

10

15

20

25

30

When the voltage generated between the both ends of the semiconductor element 124 and the voltage generated between the both ends of the semiconductor element 125 are input to the amplifier 122 functioning as a differential amplifier circuit

and amplified, a potential in accordance with the temperature can be obtained. The potential amplified by the amplifier 122 is input to the AD converter 123, and a potential converted from an analog signal to a digital signal in the AD converter 123 is transmitted, as a measurement value obtained by the temperature sensor portion, to the CPU 105 described in the above embodiment.

[0143]

5

10

15

25

Note that in the CPU 105, a look-up table may be provided in which a collection of data of an output potential of the AD converter 123 related to temperature information of an object to be sensed is saved. Further, data in accordance with temperature can be obtained by performing arithmetic processing with reference to the data stored in the look-up table.

[0144]

The above-described temperature sensor portion can be used for the alarm device described in the above embodiment in which low power consumption is achieved.

[0145]

Since the temperature sensor portion described in this embodiment can be incorporated into the microcomputer 100 described in Embodiment 1, the number of components can be reduced and the size of the housing 10 can be reduced.

20 [0146]

The configuration of the temperature sensor portion described in this embodiment is merely an example and can be modified as appropriate depending on conditions of the alarm device or the like.

[0147]

The methods, structures, and the like described in this embodiment can be combined as appropriate with any of the methods, structures, and the like described in the other embodiments.

[0148]

(Embodiment 4)

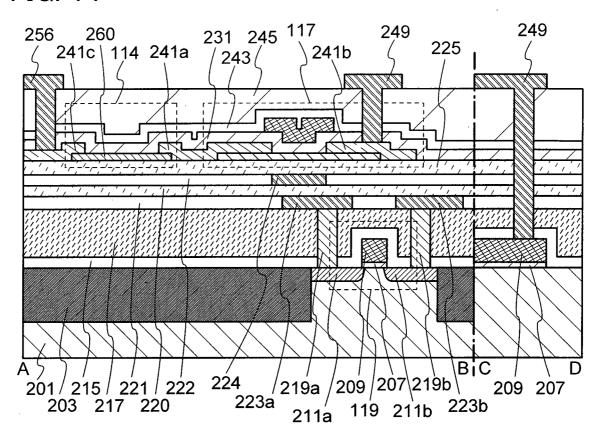

In this embodiment, an example of a method for manufacturing the microcomputer 100 which is provided in the alarm device described in the above embodiment is described with reference to FIGS. 9A to 9D, FIGS. 10A to 10C, FIGS.

11A to 11C, FIGS. 12A and 12B, and FIG. 13. A method for manufacturing the transistor 140 and the transistor 142 in the nonvolatile memory portion 107 in FIG. 4B is described. Note that in FIGS. 9A to 9D, FIGS. 10A to 10C, FIGS. 11A to 11C, and FIGS. 12A and 12B, a cross-sectional view taken along line A-B corresponds to a cross-sectional view of a region where the transistor 140 including an oxide semiconductor as a wide band gap semiconductor and the n-channel transistor 142 are formed, and a cross-sectional view taken along line C-D corresponds to a cross-sectional view of the node M1 at which the drain electrode (or the source electrode) of the transistor 140 including an oxide semiconductor film is connected to the gate electrode of the n-channel transistor 142.

[0149]

5

10

15

20

25

30

Note that the transistor included in the volatile memory portion or the like and formed using silicon or the like, which is described in the above embodiment, can be formed using a material and a method that are similar to those of the transistor 142. Further, the transistor included in the nonvolatile memory portion or the like and formed using an oxide semiconductor or the like, which is described in the above embodiment, can be formed using a material and a method that are similar to those of the transistor 140.

[0150]

First, as illustrated in FIG. 9A, element isolation regions 203 are formed in a p-type semiconductor substrate 201.

[0151]

As the p-type semiconductor substrate 201, a single crystal silicon substrate (a silicon wafer) having p-type conductivity, or a compound semiconductor substrate (e.g., a SiC substrate or a GaN substrate) can be used.

[0152]

Instead of the p-type semiconductor substrate 201, the following substrate may be used as a silicon on insulator (SOI) substrate: a so-called separation by implanted oxygen (SIMOX) substrate which is formed in such a manner that after an oxygen ion is implanted into a mirror-polished wafer, an oxide layer is formed at a certain depth from a surface and defects generated in a surface layer are eliminated by high-temperature heating; or an SOI substrate formed by a technique called a Smart-Cut method in which

a semiconductor substrate is cleaved by utilizing the thermally induced growth of a minute void formed by implantation of a hydrogen ion, an epitaxial layer transfer (ELTRAN: a registered trademark of Canon Inc.) method, or the like.

The element isolation region 203 can be formed by a local oxidation of silicon (LOCOS) method, a shallow trench isolation (STI) method, or the like.

[0154]

In the case where a p-channel transistor is formed over the same substrate, an n-well region may be formed in part of the p-type semiconductor substrate 201. The n-well region is formed by addition of an impurity element imparting n-type conductivity, such as phosphorus or arsenic.

[0155]

[0153]

5

10

15

20

25

30

Although the p-type semiconductor substrate is used here, a p-channel transistor may be formed using an n-type semiconductor substrate. In that case, a p-well region to which an impurity element imparting p-type conductivity, such as boron, is added may be formed in the n-type semiconductor substrate and an n-channel transistor may be formed over the same substrate.

[0156]

Next, as illustrated in FIG. 9B, a gate insulating film 207 and a gate electrode 209 are formed over the semiconductor substrate 201.

[0157]