(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第6620889号 (P6620889)

(45) 発行日 令和1年12月18日(2019, 12, 18)

(24) 登録日 令和1年11月29日(2019.11.29)

(51) Int.Cl. F 1

HO 1 L

21/336

(2006.01)

HO 1 L

29/78

3 O 1 V

HO 1 L

29/78

(2006.01)

HO 1 L

29/78

3 O 1 X

HO 1 L

29/78

3 O 1 D

請求項の数 8 (全 19 頁)

(21) 出願番号 特願2018-533350 (P2018-533350)

(86) (22) 出願日 平成28年8月10日 (2016.8.10)

(86) 国際出願番号 PCT/JP2016/073525

(87) 国際公開番号 W02018/029796 (87) 国際公開日 平成30年2月15日 (2018, 2, 15)

(87) 国際公開日 平成30年2月15日 (2018. 2. 15 審査請求日 平成31年3月6日 (2019. 3. 6) ||(73)特許権者 000003997

日産自動車株式会社

神奈川県横浜市神奈川区宝町2番地

|(74)代理人 100083806

弁理士 三好 秀和

||(74)代理人 100101247

弁理士 高橋 俊一

(74)代理人 100095500

弁理士 伊藤 正和

(74) 代理人 100098327

弁理士 高松 俊雄

(72) 発明者 田中 亮太

神奈川県横浜市神奈川区宝町2番地 日産

自動車株式会社内

最終頁に続く

### (54) 【発明の名称】半導体装置

### (57)【特許請求の範囲】

## 【請求項1】

基板と、

前記基板の第1主面に設けられ、前記基板よりも高不純物濃度の第1導電型のドリフト 領域と、

前記ドリフト領域の前記第1主面と反対側の第2主面から、前記第2主面の垂直方向に 形成されたソース電極溝と、

前記ソース電極溝の側面に接して、少なくとも一部が前記ドリフト領域内に形成された 第 2 導電型のウェル領域と、

前記ソース電極溝の側面に接して、前記ウェル領域内に形成された第1導電型のソース 領域と、

前記ソース領域と電気的に接続されたソース電極と、

前記ドリフト領域、前記ウェル領域及び前記ソース領域と接するように、前記第2主面から前記垂直方向に形成されたゲート電極溝と、

前記ゲート電極溝の表面に形成されたゲート絶縁膜と、

前記ゲート絶縁膜の表面に形成されたゲート電極と、

前記ドリフト領域内に、前記ウェル領域から離れて形成された第1導電型のドレイン領域と、

前記ドレイン領域と電気的に接続されたドレイン電極とを備える半導体装置において、 前記ゲート電極溝は、前記ソース電極溝に接するように形成され、

20

前記ソース電極と電気的に絶縁され、前記ソース電極溝内に前記ゲート電極に接して形成されたゲート配線を有することを特徴とする半導体装置。

#### 【請求項2】

前記ソース電極溝は、前記ゲート電極溝よりも深く形成されることを特徴とする請求項1に記載の半導体装置。

### 【請求項3】

前記ゲート配線は、絶縁膜を介して前記基板に接するように形成されることを特徴とする請求項1又は2に記載の半導体装置。

#### 【請求項4】

前記第2主面に形成された層間絶縁膜と、

前記ソース電極と電気的に接続されるソース配線と、

前記ドレイン電極と電気的に接続されるドレイン配線と、を更に備え、

前記ソース配線及び前記ドレイン配線は、前記層間絶縁膜の前記第2主面と反対側かつ 平行な主面に形成されることを特徴とする請求項1乃至3の何れか1項に記載の半導体装置。

### 【請求項5】

前記基板は、絶縁体又は半絶縁体からなることを特徴とする請求項1乃至4の何れか1項に記載の半導体装置。

#### 【請求項6】

前記ゲート電極及び前記ゲート配線は、互いに同じ材料で形成されることを特徴とする 請求項1万至5の何れか1項に記載の半導体装置。

#### 【請求項7】

前記ゲート配線は、シリコンから形成され、表面に形成されたシリコン酸化膜により前記ソース電極と電気的に絶縁されることを特徴とする請求項1乃至6の何れか1項に記載の半導体装置。

### 【請求項8】

前記ドリフト領域は、ワイドバンドギャップ半導体からなることを特徴とする請求項 1 乃至 7 の何れか 1 項に記載の半導体装置。

### 【発明の詳細な説明】

### 【技術分野】

[0001]

本発明は、半導体装置に関する。

#### 【背景技術】

### [0002]

特許文献1は、チャネルを形成するベース層と、エミッタ層及びコレクタ層とが、ドリフト層の表層部に形成された半導体装置を開示する。この半導体装置は、ドリフト層の裏面に絶縁膜を有し、トレンチに形成されたゲート電極が絶縁膜に達することにより、トレンチ端部の電界集中を低減し、耐圧性を向上する。

## 【先行技術文献】

### 【特許文献】

40

10

20

30

50

## [0003]

【特許文献 1 】特開 2 0 1 3 - 1 8 3 0 7 1 号公報

### 【発明の概要】

【発明が解決しようとする課題】

### [0004]

しかしながら、特許文献1に記載の半導体装置は、ゲート電極に接続するゲート配線が、ドリフト層の表面側に形成され、チャネルを形成するベース層付近に位置するため、チャネルがゲート配線の電位に影響され、しきい値電圧が変動する可能性がある。

#### [0005]

上記問題点を鑑み、本発明は、しきい値電圧の変動を低減することができる半導体装置

を提供することを目的とする。

【課題を解決するための手段】

[0006]

本発明の一態様に係る半導体装置は、ドリフト領域、ウェル領域及びソース領域と接するように形成されたゲート電極溝と、ゲート電極溝の表面に絶縁膜を介して形成されたゲート電極と、ゲート電極溝に接するソース電極溝と、ソース領域に電気的に接続されたソース電極と、ソース電極と電気的に絶縁され、ソース電極溝内にゲート電極に接して形成されたゲート配線とを備える。

【発明の効果】

[0007]

本発明の一態様によれば、しきい値電圧の変動を低減することができる半導体装置を提供することができる。

【図面の簡単な説明】

[0008]

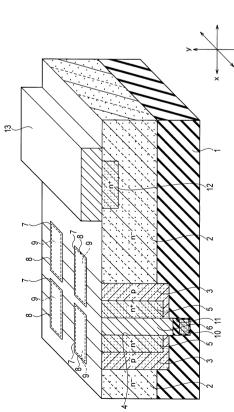

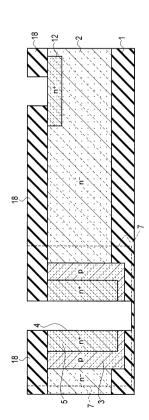

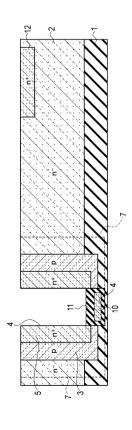

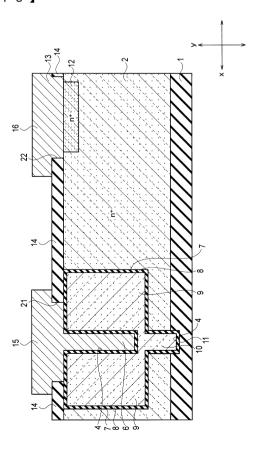

- 【図1】図1は、本発明の第1実施形態に係る半導体装置を説明する斜視図である。

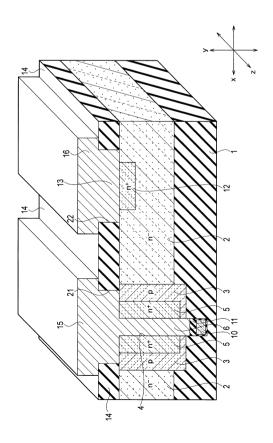

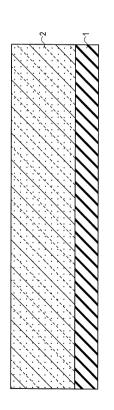

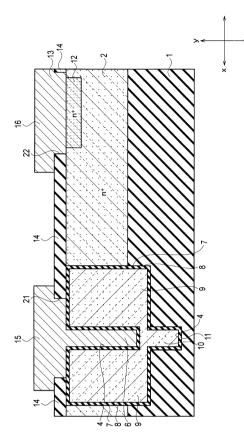

- 【図2】図2は、本発明の第1実施形態に係る半導体装置を説明する斜視図である。

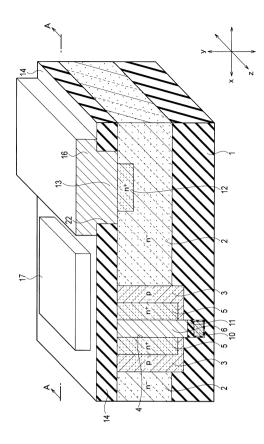

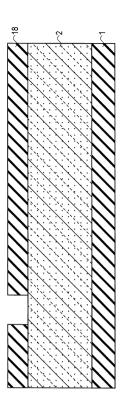

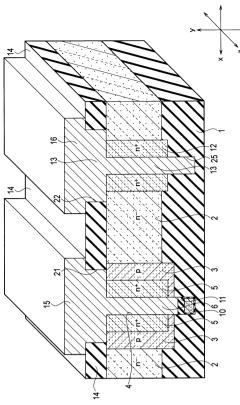

- 【図3】図3は、本発明の第1実施形態に係る半導体装置を説明する斜視図である。

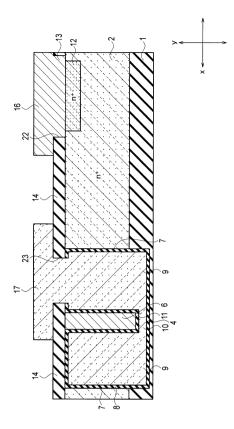

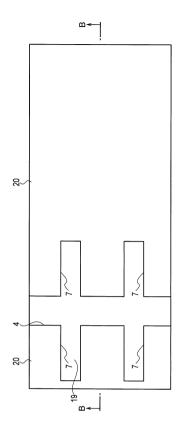

- 【図4】図4は、図3のA-A方向から見た断面図である。

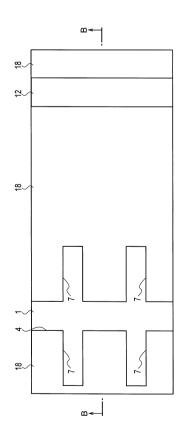

- 【図5】図5は、本発明の第1実施形態に係る半導体装置の製造方法を説明する平面図である。

【図6】図6は、図5のB-B方向から見た断面図である。

- 【図7】図7は、本発明の第1実施形態に係る半導体装置の製造方法を説明する平面図である。

- 【図8】図8は、図7のB-B方向から見た断面図である。

- 【図9】図9は、本発明の第1実施形態に係る半導体装置の製造方法を説明する平面図である。

- 【図10】図10は、図9のB-B方向から見た断面図である。

- 【図11】図11は、本発明の第1実施形態に係る半導体装置の製造方法を説明する平面図である。

- 【図12】図12は、図11のB-B方向から見た断面図である。

- 【図13】図13は、本発明の第1実施形態に係る半導体装置の製造方法を説明する平面図である。

- 【図14】図14は、図13のB-B方向から見た断面図である。

- 【図15】図15は、本発明の第1実施形態に係る半導体装置の製造方法を説明する平面図である。

- 【図16】図16は、図15のB-B方向から見た断面図である。

- 【図17】図17は、本発明の第2実施形態に係る半導体装置を説明する断面図である。

- 【図18】図18は、本発明の第2実施形態の変形例に係る半導体装置を説明する断面図である。

- 【図19】図19は、本発明の第3実施形態に係る半導体装置を説明する断面図である。

- 【図20】図20は、本発明の第4実施形態に係る半導体装置を説明する断面図である。

【発明を実施するための形態】

[0009]

以下、図面を参照して、本発明の第1乃至第4実施形態を説明する。図面の記載において、同一又は類似の部分には同一又は類似の符号を付し、重複する説明を省略する。但し、図面は模式的なものであり、各寸法の関係や比率などは実際のものとは異なる場合がある。また、図面相互間においても互いの寸法の関係や比率が異なる部分が含まれる。また、以下に示す実施形態は、本発明の技術的思想を具体化するための装置や方法を例示するものであって、本発明の技術的思想は、構成部品の材質、形状、構造、配置等を下記のものに特定するものでない。

10

20

30

40

#### [ 0 0 1 0 ]

また、以下の実施形態において、「第1導電型」と「第2導電型」とは互いに反対導電型である。即ち、第1導電型が n 型であれば、第2導電型は p 型であり、第1導電型が p 型であれば、第2導電型は n 型である。以下の説明では第1導電型が n 型、第2導電型が p 型の場合を説明するが、第1導電型が p 型、第2導電型が n 型でもあっても良い。 n 型と p 型を入れ替える場合には、印加電圧の極性も逆転する。

#### [0011]

### (第1実施形態)

図1は、本発明の第1実施形態に係る半導体装置の構成を模式的に示す斜視図である。 第1実施形態では、複数の半導体素子として金属酸化膜半導体電界効果トランジスタ(MOSFET)を有する半導体装置を例示的に説明する。半導体素子は、平面における2軸方向(X軸方向及びZ軸方向)それぞれに更に多数配列され得る。なお、図1では分かり易くするため、電極の一部及び配線は図示を省略している。

#### [0012]

第1実施形態に係る半導体装置は、図1に示すように、基板1と、ドリフト領域2と、ウェル領域3と、ソース電極溝4と、ソース領域5と、ソース電極6と、ゲート電極溝7と、ゲート絶縁膜8と、ゲート電極9と、ゲート配線10と、シリコン酸化膜11と、ドレイン領域12と、ドレイン電極13とを備える。

### [0013]

基板 1 は、例えば、半絶縁体又は絶縁体からなる平板である。ここで、絶縁体とは、シート抵抗が数 k / 以上の材料を意味し、半絶縁体とは、シート抵抗が数十 / 以上の材料を意味する。基板 1 の材料となる絶縁体としては、例えばポリタイプ 4 H の炭化ケイ素 ( S i C ) が採用可能である。基板 1 は、半導体装置の機械的強度を確保するため、例えば、数十 $\mu$  m ~ 数百 $\mu$  m 程度の厚さを有する。

#### [0014]

ドリフト領域 2 は、基板 1 の片側の主面(以下「第 1 主面」という)に形成された n 型の領域である。ドリフト領域 2 の不純物濃度は基板 1 よりも高く、例えば  $1\times10^{14}$  c m  $^{-3}$  ~  $1\times10^{18}$  c m  $^{-3}$  程度である。ドリフト領域 2 は、基板 1 と同じ材料から形成され得る。例えば、基板 1 がポリタイプ 4 H の S i C からなる場合、ドリフト領域 2 は、ポリタイプ 4 H の S i C からなるエピタキシャル成長層である。ドリフト領域 2 は、例えば、数  $\mu$  m ~ 数 +  $\mu$  m 程度の厚さを有する。

## [0015]

ソース電極溝 4 は、ドリフト領域 2 の、基板 1 と接する主面(以下「第 1 主面」という)の反対側の主面(以下「第 2 主面」という)から基板 1 内まで、ドリフト領域 2 の第 2 主面に対して垂直方向(y 軸方向)に形成された溝である。すなわち、ソース電極溝 4 の深さは、ドリフト領域 2 の厚さより大きい。ソース電極溝 4 の寸法は、半導体装置の集積度、プロセス上の精度等の設計条件に基づいて決定される。ソース電極溝 4 の幅は、例えば 2 μ m である。ソース電極溝 4 は、ドリフト領域 2 の第 2 主面に対して平行な一方向(z 軸方向)に延伸する。

### [0016]

ウェル領域 3 は、ソース電極溝 4 の側面に接して、少なくとも一部がドリフト領域 2 内に形成された p 型の領域である。ウェル領域 3 は、ドリフト領域 2 の第 2 主面から基板 1 内まで、ドリフト領域 2 の第 2 主面に対して垂直方向( y 軸方向)に形成される。ウェル領域 3 の深さは、ソース電極溝 4 の深さより小さい。ウェル領域 3 は、ソース電極溝 4 の延伸方向( z 軸方向)に延伸する。ウェル領域 3 の不純物濃度は、例えば、 1 × 1 0  $^{15}$  c m  $^{-3}$  ~ 1 × 1 0  $^{19}$  c m  $^{-3}$  程度である。

### [0017]

ソース領域 5 は、ソース電極溝 4 の側面に接して、ウェル領域 3 内に形成された n <sup>+</sup>型の領域である。ソース領域 5 は、ドリフト領域 2 の第 2 主面から基板 1 内まで、ドリフト領域 2 の第 2 主面に対して垂直方向( y 軸方向)に形成される。ソース領域 5 の深さは、

10

20

30

40

10

20

30

40

50

ウェル領域 3 の深さより小さい。ソース領域 5 は、ソース電極溝 4 の延伸方向 (z 軸方向) に延伸する。ソース領域 5 の不純物濃度は、ドリフト領域 2 よりも高く、例えば、 1 × 1 0  $^{18}$  c m  $^{-3}$  ~ 1 × 1 0  $^{21}$  c m  $^{-3}$  程度である。

### [0018]

ソース電極 6 は、ソース領域 5 に電気的に接続される。ソース電極 6 は、ソース電極溝 4 内に形成されることにより、ソース領域 5 にオーミック接続する。ソース領域 5 及びウェル領域 3 は、ソース電極 6 と同電位をとる。ソース電極 6 の材料としては、例えば、ニッケルシリサイド(NiSi)、チタン(Ti)又はモリブデン(Mo)等の金属材料を含む導電体が使用可能である。ソース電極 6 は、ソース領域 5 とオーミック接続する金属材料と、アルミニウム(Al)、銅(Cu)、金(Au)、ニッケル(Ni)、銀(Ag)等の金属材料との多層構造を有してもよい。

#### [0019]

ゲート電極溝7は、ドリフト領域2の第2主面から基板1内まで、ドリフト領域2の第2主面に対して垂直方向(y軸方向)に形成された溝である。ゲート電極溝7は、ドリフト領域2の第2主面に平行であり、ソース電極溝4の延伸方向に直交する方向(x軸方向)において、ソース電極溝4、ドリフト領域2、ウェル領域3及びソース領域5に接するように延伸する。ゲート電極溝7は、ウェル領域3及びソース領域5を貫通する。ゲート電極溝7の深さは、ソース電極溝4の深さに等しい。ゲート電極溝7は、ドリフト領域2の第2主面に平行且つ延伸方向に直交する方向(z軸方向)に複数配列される。

### [0020]

ゲート絶縁膜8は、ゲート電極溝7の表面に形成される。ゲート絶縁膜8の材料は、例えば酸化ケイ素(SiO₂)等の絶縁体である。ゲート電極9は、ゲート絶縁膜8の表面に形成される。すなわち、ゲート電極9は、ゲート絶縁膜8を介して、ゲート電極溝7の表面に接するように形成される。ゲート電極9の材料は、例えば多結晶シリコンである。ゲート電極9は、表面がゲート絶縁膜8に被覆された状態でゲート電極溝7内に配置される。ゲート電極9は、ドリフト領域2の第2主面におけるゲート電極溝7の開口部においてもゲート絶縁膜8に被覆される。

#### [0021]

ゲート配線10は、ソース電極6と電気的に絶縁され、ソース電極6内にゲート電極9に接して形成される。ゲート配線10は、表面に絶縁膜であるシリコン酸化膜11が形成された状態で、ソース電極溝4の下部に位置する。シリコン酸化膜11は、ゲート配線10とソース電極6とを互いに絶縁させる。ソース電極溝4内のゲート配線10及びシリコン酸化膜11を除く空間は、ソース電極6で充填される。ゲート配線10の表面において、ゲート電極9と接する領域は、シリコン酸化膜11が形成されない。同様に、ゲート電極9の表面において、ゲート配線10と接する領域は、ゲート絶縁膜8が形成されない。

#### [0022]

ドレイン領域 1 2 は、ドリフト領域 2 内に、ウェル領域 3 から離れて形成された  $n^{+}$ 型の領域である。ドレイン領域 1 2 は、ドリフト領域 2 の第 2 主面から、ドリフト領域 2 の第 2 主面から、ドリフト領域 2 の第 2 主面に対して垂直方向(y 軸方向)に形成される。ドレイン領域 1 2 の深さは、ドリフト領域 2 の厚さより小さい。ドレイン領域 1 2 は、ソース電極溝 4 の延伸方向(z 軸方向)に延伸する。ドレイン領域 1 2 は、ドリフト領域 2 と同じ導電型である。ドレイン領域 1 2 の不純物濃度は、ドリフト領域 2 よりも高く且つソース領域 5 と同程度であり、例えば、 1 × 1  $0^{18}$  c  $m^{-3}$  ~ 1 × 1  $0^{21}$  c  $m^{-3}$  程度である。

## [0023]

ドレイン電極13は、ドレイン領域12と電気的に接続される。ドレイン電極13は、 ドリフト領域2の第2主面に形成され、第2主面において露出された<u>ドレイン領域12</u>に 接する。ドレイン電極13は、例えばソース電極6と同様の材料から構成可能である。

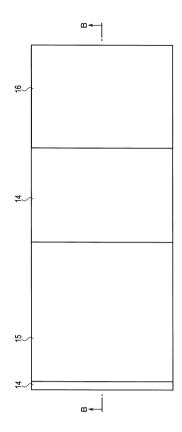

#### [0024]

図2は、第1実施形態に係る半導体装置の、図1において図示を省略した構成を説明する図である。図2に示すように、第1実施形態に係る半導体装置は、層間絶縁膜14と、

ソース配線15と、ドレイン配線16とを更に備える。

### [0025]

層間絶縁膜 14 は、ドリフト領域 2 の第 2 主面に形成される。層間絶縁膜 14 は、酸化ケイ素(S i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i O i

[0026]

ソース配線15は、溝21において露出したソース電極6を被覆するように、層間絶縁膜14の上面に形成される。層間絶縁膜14の上面は、ドリフト領域2の第2主面と反対側の主面であり、ドリフト領域2の第2主面に対して平行である。ソース配線15は、溝21の延伸方向に延伸する。ドレイン配線16は、溝22において露出したドレイン電極13を被覆するように、層間絶縁膜14の上面に形成される。ドレイン配線16は、溝22の延伸方向に延伸する。ソース配線15及びドレイン配線16は、互いに離れ、平行に形成される。

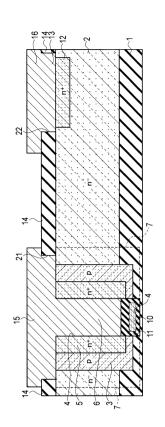

[0027]

図3は、第1実施形態に係る半導体装置において、ゲート電極9及びゲート配線10の電位に接続する構成の一例を説明する図である。図4は、図3のA-A方向から見た断面図である。図3及び図4は、第1実施形態に係る半導体装置のうち、図1又は図2に示す範囲と異なる範囲であり、z軸方向における一部を選択的に示す図である。

[0028]

第1実施形態に係る半導体装置は、層間絶縁膜14上の一部に形成されたゲートパッド17を更に備える。図4に示すように、層間絶縁膜14は、複数のゲート電極9のうち、少なくとも1つのゲート電極9の上方に形成された貫通孔23を有する。貫通孔23の下方に位置するゲート電極9の上面に形成されたゲート絶縁膜8は、貫通孔23に対応する範囲において除去される。ゲートパッド17は、貫通孔23を介して下方のゲート電極9と、ゲート配線10とに電気的に接続される。複数のゲート電極9は、全てゲート配線10と電気的に接続されているため、ゲートパッド17の電位を調整することにより、全てのゲート電極9の電位が調整可能である。

[0029]

次に、図 5 ~図 1 6 を参照し、第 1 実施形態に係る半導体装置の製造方法の一例を説明する。

[0030]

まず、図5及び図6に示すように、上面(第1主面)にドリフト領域2が形成された基板1を用意する。基板1は、ノンドープのSiCからなる絶縁性基板である。ドリフト領域2は、基板1にエピタキシャル成長により形成されたn 型の領域である。

[0031]

次に、図7及び図8に示すように、ドリフト領域2の上面(第2主面)にマスク材18を形成する。化学気相成長(CVD)法によりドリフト領域2の上面にSiO₂を堆積してシリコン酸化膜を形成し、シリコン酸化膜をパターニングすることによりマスク材18が形成される。シリコン酸化膜は、フォトリソグラフィ法及びドライエッチング法によりパターニングされる。すなわち、シリコン酸化膜の上面にレジストを塗布し、ソース電極溝4及びゲート電極溝7を形成する予定の領域のみを選択的に除去する。残されたレジストをマスクとする反応性イオンエッチング(RIE)等のドライエッチング法により、シリコン酸化膜をパターニングすることにより、ソース電極溝4及びゲート電極溝7を形成するためのマスク材18が形成される。なお、不要になったレジストは酸素プラズマや硫酸等により適宜除去される。その後、マスク材18をマスクとするドライエッチング法に

10

20

30

40

より、ソース電極溝4及びゲート電極溝7が形成される。

## [0032]

次に、図9及び図10に示すように、p型のウェル領域3と、n \*型のソース領域5及びドレイン領域12とを形成する。フォトリソグラフィ法により、基板1及びドリフト領域2の露出された表面にレジストを塗布し、ソース電極溝4に対応する領域を除去する。残されたレジストをマスクとして、イオン注入法により、ホウ素(B)等のp型不純物を、ゲート電極溝7の延伸方向に直交(x - y平面に平行)且つドリフト領域2の第2主面に対して所定角度を有する方向に注入する。所定角度は、例えば10°~20°である。【0033】

そして、フォトリソグラフィ法により、マスク材18上にレジストを塗布し、ドレイン領域12を形成する予定の領域に対応する領域のみを選択的に除去する。残されたレジストをマスクとして、ドライエッチング法により、マスク材18をパターニングする。パターニングされたマスク材18及びホウ素の注入に用いられたレジストをマスクとして、イオン注入法により、n型不純物を所定方向に注入する。n型不純物は、例えばリン(P)であり、注入方向は、p型不純物の注入方向と同様である。但し、ソース領域5がウェル領域3内に形成されるように、n型不純物の注入エネルギーは、p型不純物の注入エネルギーより小さい。

### [0034]

その後、ウェットエッチング法により、マスク材18を全て除去する。また、熱処理(アニール)することでイオン注入した不純物を活性化する。活性化によって、ウェル領域3、ソース領域5及びドレイン領域12が形成される。また、熱酸化法により、露出された全ての表面に、薄いシリコン酸化膜20を形成する。シリコン酸化膜20の厚さは、例えば数十mm程度である。

#### [0035]

次に、図11及び図12に示すように、CVD法により、ソース電極溝4及びゲート電極溝7に、ゲート電極9及びゲート配線10の材料である多結晶シリコン19を堆積する。CVD法により多結晶シリコンを堆積する場合、面の向きに関わらず露出された表面から多結晶シリコン層が成長する。この為、ソース電極溝4及びゲート電極溝7の幅がそれぞれ2μmであれば、堆積する厚さを1μmとすることにより、ソース電極溝4及びゲート電極溝7が多結晶シリコン19により充填される。その後、ドライエッチング法により、多結晶シリコン19を1μmエッチングすることで、ソース電極溝4及びゲート電極溝7に堆積された多結晶シリコン19を残して、ドリフト領域2の第2主面より上に堆積された多結晶シリコン19が選択的に除去される。

### [0036]

その後、フォトリソグラフィ法により、シリコン酸化膜20及び多結晶シリコン19の上面にレジストを塗布し、ソース電極溝4の領域のみを選択的に除去する。残されたレジストをマスクとして、ドライエッチング法により、ソース電極溝4内に堆積された多結晶シリコン19を、底面から数μmの領域を残して除去する。ソース電極溝4の底部に残された多結晶シリコン19は、ゲート配線10として機能する。また、犠牲酸化法により、ソース電極溝4の側面に形成されたシリコン酸化膜20を除去する。

## [0037]

次に、図13及び図14に示すように、ゲート電極9の表面を被覆するゲート絶縁膜8及びゲート配線10を被覆するシリコン酸化膜11を形成する。熱酸化法により、露出されたすべての表面にシリコン酸化膜を形成する。このとき、多結晶シリコンはSiCより酸化速度が大きいため、ゲート電極9及びゲート配線10の表面には、SiCから構成される他の面に比べて厚いシリコン酸化膜が形成される。ウェットエッチング法により、SiCから構成される面に形成されたシリコン酸化膜のみが全て除去され、多結晶シリコン19の表面に形成されたシリコン酸化膜のみが全て除去され、多結晶シリコン19の表面に形成されたシリコン酸化膜が残されるような処理時間でシリコン酸化膜を選択的に除去する。これにより、ゲート電極9の表面にゲート絶縁膜8が形成され、ゲート配線10の表面にシリコン酸化膜11が形成される。

10

20

30

40

#### [0038]

次に、図15及び図16に示すように、ソース電極6、ソース配線15、ドレイン電極13及びドレイン配線16を形成する。スパッタリング法により、ソース電極溝4内及びドリフト領域2の第2主面に、ソース電極6及びドレイン電極13の材料である金属材料を堆積する。フォトリソグラフィ法により、金属材料の表面にレジストを塗布し、ドリフト領域2の第2主面より上の領域における、ソース電極6及びドレイン電極13を形成する予定の領域を除く領域のレジストを選択的に除去する。残されたレジストをマスクとして、スパッタエッチング法により、ドリフト領域2の第2主面に位置する金属材料を選択的に除去することにより、ソース電極6及びドレイン電極13が形成される。

#### [0039]

その後、CVD法により、ドリフト領域2の第2主面及び残された金属材料の上面にSiO2を堆積して層間絶縁膜14を形成する。フォトリソグラフィ法により、層間絶縁膜14の上面にレジストを塗布し、ソース電極6及びドレイン電極13の領域を選択的に除去する。残されたレジストをマスクとして、ドライエッチング法により、層間絶縁膜14をパターニングする。これにより、ソース電極6が挿入される溝21及びドレイン電極13が挿入される溝22のそれぞれ上端が開口する。

### [0040]

更に、スパッタリング法により、ソース配線15及びドレイン配線16の材料である金属材料を堆積する。フォトリソグラフィ法により、金属材料の上面にレジストを塗布し、ソース配線15及びドレイン配線16を形成する予定の領域を除く領域のレジストを選択的に除去する。残されたレジストをマスクとして、スパッタエッチング法により、金属材料を選択的に除去することにより、ソース配線15及びドレイン配線16が形成される。以上の工程を経て、図2に示す半導体装置が完成する。

### [0041]

なお、図1に示す例においては、ゲート電極9の一部がソース電極溝4に入り込んでいるが、ソース電極溝4に堆積された多結晶シリコン19をエッチングする際のマスクパターンを調整することにより、ゲート電極9は形状が変更され得る。

#### [0042]

次に、第1実施形態に係る半導体装置の基本的な動作について説明する。

### [0043]

第1実施形態に係る半導体装置は、ソース電極6の電位を基準として、ドレイン電極13に正の電位を印加した状態でゲート電極9の電位を制御することにより、トランジスタとして機能する。すなわち、ゲート電極9とソース電極6間の電圧を所定の閾値以上にすると、ゲート電極9側面に位置するウェル領域3にチャネルとなる反転層が形成されてオン状態となり、ドレイン電極13からソース電極6へ電流が流れる。具体的には、電子がソース電極6からソース領域5に流れ、ソース領域5からチャネルを介してドリフト領域2に流れ込む。電子は更に、ドリフト領域2からドレイン領域12に流れ、最後にドレイン電極13に流れる。

### [0044]

一方、ゲート電極 9 とソース電極 6 間の電圧を所定の閾値<u>よりも小さく</u>すると、ウェル 領域 3 の反転層が消滅してオフ状態となり、ドレイン電極 1 3 及びソース電極 6 間の電流 が遮断される。この際、ドレイン・ソース間には数百 V ~数千 V の高電圧が印加され得る

## [0045]

一般に、ゲート電極に接続するゲート配線は、ウェル領域の近くに配置される。この場合、ゲート配線の電位が反転層の形成に影響を及ぼし、しきい値が変動してしまう可能性がある。しきい値が変動すると、誤ターンオンなど意図しない動作が生じ得るため、装置の信頼性が低下する可能性がある。

#### [0046]

第1実施形態に係る半導体装置によれば、ゲート配線10がソース電極溝4内に形成さ

10

20

30

40

れるため、ウェル領域 3 から離れた箇所に位置する。よって、ウェル領域 3 に形成されるチャネルがゲート配線 1 0 から受ける影響が低減されるため、しきい値の変動を低減することができる。

#### [0047]

また、第1実施形態に係る半導体装置によれば、ゲート電極9がソース電極溝4内に形成されたゲート配線10に接するため、ゲート電極9の上面側において金属配線及びコンタクトホールが不要である。よって、ゲート電極9の幅を削減することができ、半導体装置の集積度を向上することができる。これにより、ゲート電極9の数を増加させることができるため、チャネル幅が増加され、オン抵抗を低減することができる。

#### [0048]

また、第1実施形態に係る半導体装置によれば、ゲート配線10が、ソース電極溝4内に形成されるため、層間絶縁膜14の上面に形成されたソース配線15及びドレイン配線16の幅を制限することがない。よって、ソース配線15及びドレイン配線16の抵抗の増大によるオン抵抗及びスイッチング損失の悪化を抑制することができる。

#### [0049]

第1実施形態に係る半導体装置によれば、ゲート配線10がシリコン酸化膜11を介して基板1に接するため、ドリフト領域2から基板1内まで形成可能である。よって、ゲート配線10の断面積を増加させることができため、ゲート配線10の抵抗及びスイッチング損失を低減することができる。

## [0050]

また、第1実施形態に係る半導体装置によれば、ソース配線15及びドレイン配線16が層間絶縁膜14の上面にそれぞれ形成されるため、両配線を多層構造とする場合に比べて、平坦性を向上することができる。よって、配線間の絶縁膜の局部における電界集中による耐圧性の悪化を回避することができる。

#### [0051]

また、第1実施形態に係る半導体装置によれば、基板1が絶縁体又は半絶縁体からなるため、ウェル領域3、ゲート電極9及びゲート配線10の少なくともいずれかの端部が基板1内に位置する場合、端部における電界集中を低減することができる。よって、耐圧性を向上することができる。

## [0052]

また、第1実施形態に係る半導体装置によれば、ゲート電極9及びゲート配線10が互いに同じ材料からなるため、同じ工程により形成可能であり、更に、互いを電気的に接続するための工程が不要である。よって、製造工数を低減することができ、製造コストを低減することができる。また、ゲート電極9とゲート配線10との界面における抵抗が生じることを回避することができる。

### [0053]

また、第1実施形態に係る半導体装置によれば、多結晶シリコンからなるゲート配線10が、表面に形成されたシリコン酸化膜11によりソース電極6と絶縁される。よって、熱酸化法によりゲート配線10を被覆するシリコン酸化膜11を用意に形成することができる。更に、ドリフト領域2がSi〇 $_2$ より酸化速度が遅いSiC等の材料からなるため、等方性エッチング法により、ゲート配線10の表面に選択的にシリコン酸化膜11を形成できる。よって、窒化ケイ素など酸化しない材料から形成されるマスクを用いて、ゲート配線10に選択的に酸化膜を形成する場合に比べて、製造工数を低減することができ、製造コストを低減することができる。

#### [0054]

また、第1実施形態に係る半導体装置によれば、ドリフト領域2がSiC等のワイドバンドギャップ半導体からなるため、絶縁破壊強度を向上することができる。このため、仮にドレイン電極13とソース電極6との間が狭く、急峻な電界分布が生じても耐圧性を確保しつつ集積度を向上することができる。

## [0055]

50

10

20

30

また、第1実施形態に係る半導体装置によれば、ゲート配線10が、ドリフト領域2から離れて形成されるため、ゲート-ドレイン間の容量の増加を抑制することができる。仮に、ゲート配線がドリフト領域付近に形成される場合、ドリフト領域の電位はドレイン電極とほぼ等しいため、ゲート-ドレイン間の容量が増加してしまう。一方、第1実施形態に係る半導体装置では、ゲート-ドレイン間の容量の増加が抑制されるため、スイッチング損失を低減することができる。

#### [0056]

また、第1実施形態に係る半導体装置によれば、基板1とドリフト領域2とが互いに同じ材料から形成されるため、応力による反りが生じる可能性を低減し、素子の信頼性を向上することができる。

10

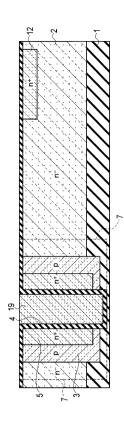

### [0057]

#### (第2実施形態)

図17は、本発明の第2実施形態に係る半導体装置を説明する断面図である。なお、図17は、第2実施形態に係る半導体装置を、ゲート電極9を通る×・y平面で切断した断面図である。第2実施形態に係る半導体装置は、ソース電極溝4がゲート電極溝7よりも深く形成される点等で上述の第1実施形態と異なる。第2実施形態において説明しない構成、作用及び効果は、第1実施形態と実質的に同様であり重複するため省略する。

#### [0058]

第2実施形態において、ソース電極溝4の深さは、ドリフト領域2の厚さより小さいため、ソース電極溝4は、基板1に接しない。また、ゲート電極溝7の深さは、ソース電極溝4の深さより浅い。

20

#### [0059]

ソース電極溝4及びゲート電極溝7を形成する際のマスクは、ドライエッチング法により薄くなり、強度が低下してしまう。第2実施形態に係る半導体装置では、ソース電極溝4及びゲート電極溝7の深さがドリフト領域2の厚さより小さい。このため、製造工程において、ソース電極溝4及びゲート電極溝7を形成する際のマスクとなるシリコン酸化膜は、第1実施形態におけるマスク材18よりも薄くすることができる。なお、溝を掘るドライエッチング法において、ソース電極溝4の幅をゲート電極溝7の幅より大きく設計することにより、ソース電極溝4をゲート電極溝7よりも深く形成することができる。

[0060]

30

第2実施形態に係る半導体装置によれば、ソース電極溝4がゲート電極溝7よりも深く 形成されるため、ゲート配線10をより深く形成することができ、ゲート配線10の<u>断面</u> <u>積</u>を増加させることができる。よって、ゲート配線10の抵抗を低減し、スイッチング損 失を低減することができる。

### [0061]

また、第2実施形態に係る半導体装置によれば、ゲート電極溝7がドリフト領域2の厚さよりも浅く形成されるため、ウェル領域3の、ゲート電極溝7の底面側においてもチャネルが形成される。よって、チャネル幅を増加させることができ、オン抵抗を低減させることができる。

[0062]

40

## (変形例)

図18は、本発明の第2実施形態の変形例に係る半導体装置を説明する断面図である。 第2実施形態の変形例に係る半導体装置は、ソース電極溝4の底部が基板1内に位置する 点で上述の第2実施形態と異なる。第2実施形態の変形例において説明しない構成、作用 及び効果は、上述の第2実施形態と実質的に同様であり重複するため省略する。

## [0063]

第2実施形態の変形例では、ソース電極溝4がゲート電極溝7よりも深く、基板1に接するように形成される。ソース電極溝4の底部において、ゲート配線10は、シリコン酸化膜11を介して基板1に接する。すなわち、ゲート配線10の端部は、基板1内に位置する。ここで端部とは、ドリフト領域2の第2主面に垂直な面と、ドリフト領域2の第2

主面に対向する端面とが交わる部分を意味する。なお、製造工程において、ソース電極溝4及びゲート電極溝7を形成する際のマスクとなるシリコン酸化膜を、第1実施形態におけるマスク材18よりも厚くすることにより、溝の深さを深くすることができる。また、ソース電極溝4及びゲート電極溝7の幅の比を調整することにより、ソース電極溝4及びゲート電極溝7の深さの比を調整することができる。

#### [0064]

第2実施形態の変形例に係る半導体装置によれば、ソース電極溝4がドリフト領域2の厚さよりも深く形成されるため、ゲート配線10を更に深く形成することができ、ゲート配線10の断面積を増加させることができる。よって、ゲート配線10の抵抗を低減し、スイッチング損失を低減することができる。

[0065]

また、第2実施形態の変形例に係る半導体装置によれば、ソース電極溝4の底部が基板1を接するため、ソース電極溝4の端部における電界集中を低減し、耐圧性を向上することができる。

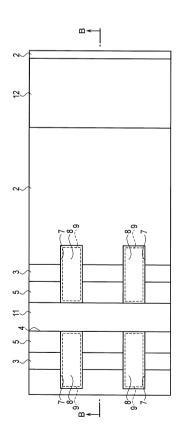

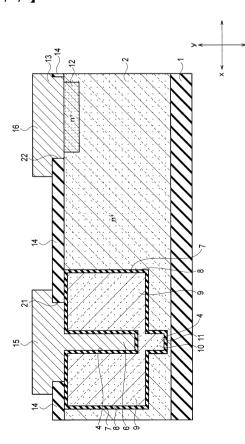

### [0066]

(第3実施形態)

図19は、本発明の第3実施形態に係る半導体装置を説明する断面図である。第3実施 形態に係る半導体装置は、ゲート電極溝7の底部が基板1に接する点で第2実施形態と異 なる。第3実施形態において説明しない構成、作用及び効果は、第1及び第2実施形態と 実質的に同様であり重複するため省略する。

[0067]

第3実施形態において、ソース電極溝4がゲート電極溝7よりも深く、ソース電極溝4及びゲート電極溝7は基板1に接するように形成される。ソース電極溝4の底部において、ゲート配線10は、シリコン酸化膜11を介して基板1に接する。ゲート電極9は、ゲート絶縁膜8を介してなお、基板1に接する。製造工程において、ソース電極溝4及びゲート電極溝7を形成する際のマスクとなるシリコン酸化膜を、第2実施形態におけるマスクよりも厚くすることにより、溝の深さを深くすることができる。また、ソース電極溝4及びゲート電極溝7の幅の比を調整することにより、ソース電極溝4及びゲート電極溝7の深さの比を調整することができる。

[0068]

第3実施形態に係る半導体装置によれば、ゲート電極溝7の端部が基板1に接するため、ゲート電極溝7の端部における電界集中が低減され、ゲート絶縁膜8の絶縁破壊を抑制して、耐圧性を向上することができる。

### [0069]

(第4実施形態)

図20は、本発明の第4実施形態に係る半導体装置を説明する断面図である。第4実施 形態に係る半導体装置は、ドレイン電極13が形成されるドレイン電極溝25を備える点 等で第1万至第3実施形態と異なる。第4実施形態において説明しない構成、作用及び効 果は、第1万至第3実施形態と実質的に同様であり重複するため省略する。

[0070]

ドレイン電極溝25は<u>ド</u>リフト領域2内に、ウェル領域3から離れて形成される。ドレイン電極溝25は、ドリフト領域2の第2主面から基板1内まで、ドリフト領域2の第2主面に対して<u>垂直</u>(y軸方向)に形成される。ドレイン領域12は、ドレイン電極溝25の側面に接する。第4実施形態において、ドレイン領域12は、ドリフト領域2の第2主面から基板1内まで、ドリフト領域2の第2主面に対して<u>垂直</u>(y軸方向)に形成される。ドレイン電極溝25の深さは、ドレイン領域12の深さより深い。

#### [0071]

ドレイン電極溝25は、第1実施形態に係る半導体装置の製造方法において、マスク材18となるシリコン酸化膜を、ドレイン電極溝25を形成する予定の領域も選択的に除去することにより形成可能である。このマスク材18をマスクとして、ドライエッチング法

10

20

40

30

により、ソース電極溝 4 、ゲート電極溝 7 及びドレイン電極溝 2 5 を同時に形成することができる。

#### [0072]

また、ドレイン電極溝25が形成されることにより、ドレイン領域12の製造工程において、第1実施形態と比べて高い注入エネルギーで不純物を注入する必要なく、深い位置までドレイン領域12を形成することができる。

#### [ 0 0 7 3 ]

第4実施形態に係る半導体装置によれば、ドレイン電極溝25がドリフト領域2より深く形成されるため、ドリフト領域2の深さ方向(y軸方向)における電界分布を低減することができる。よって、電界集中が低減され、耐圧性を向上することができる。

### [0074]

また、第4実施形態に係る半導体装置によれば、ドリフト領域2よりも高不純物濃度のドレイン領域12が、ドリフト領域2より深く形成されるため、電流経路をドリフト領域2からドレイン領域12に置き換えることができる。よって、オン抵抗を低減することができる。

### [0075]

### (その他の実施形態)

上記のように、本発明を上記の実施形態によって記載したが、この開示の一部をなす論述及び図面は本発明を限定するものであると理解すべきではない。この開示から当業者には様々な代替実施形態、実施例及び運用技術が明らかとなろう。

#### [0076]

例えば、第1乃至第4実施形態において、SiCからなる基板1及びドリフト領域2に 半導体装置を製造する場合を説明したが、材料としてはSiCに限定されない。例えば、 基板1及びドリフト領域2の材料となるワイドバンドギャップ半導体として、例えば窒化 ガリウム(GaN)、ダイヤモンド、酸化亜鉛(ZnO)、窒化アルミニウムガリウム( A1GaN)等が挙げられる。

#### [0077]

また、第1乃至第4実施形態において、ドリフト領域2をエピタキシャル成長により形成する場合を説明したが、SiC等の絶縁性基板にn型不純物を注入することにより形成するようにしてもよい。

### [0078]

また、第1乃至第4実施形態において、基板1は、ドリフト領域2より不純物濃度が低いn型半導体からなるようにしてもよい。これにより、半導体装置のオン状態時に、電流が基板1内を流れることになり、電流経路が増加するため、電流が増加する。仮に基板1がp型半導体である場合、ドリフト領域2内に電流経路を狭めるように空乏層が広がるため、電流が低減する。即ち、基板1がドリフト領域2と同じ導電型である場合、電流が増加して損失が低減される。

# [0079]

また、第1乃至第4実施形態において、ゲート電極溝7及びソース電極溝4の底面は、 ドリフト領域2の第1主面よりも高くても低くてもよく、第1主面に一致していてもよい 。また、ソース電極溝4内におけるゲート配線10の位置は、ゲート電極溝7の底面より も高くてもよい。

### [0800]

また、第1乃至第4実施形態において、半導体装置の一例としてMOSFETを説明したが、本発明実施形態に係る半導体装置は、絶縁ゲート型バイポーラトランジスタ(IGBT)やサイリスタにも適用できるのは勿論である。

# [0081]

また、第1乃至第4実施形態において、「平行」、「垂直」、「直交」等の表現は、完全なトポロジーを意味するものではなく、フォトリソグラフィやその他のプロセス上の理由から、不完全なトポロジーをも許容するものである。

10

20

30

40

### [0082]

その他、上記の各構成を相互に応用した構成等、本発明はここでは記載していない様々 な実施形態等を含むことは勿論である。したがって、本発明の技術的範囲は上記の説明か ら妥当な特許請求の範囲に係る発明特定事項によってのみ定められるものである。

## 【符号の説明】

## [0083]

- 1 基板

- 2 ドリフト領域

- 3 ウェル領域

- 4 ソース電極溝

- 5 ソース領域

- 6 ソース電極

- ゲート電極溝

- 8 ゲート絶縁膜

- 9 ゲート電極

- 10 ゲート配線

- 1 1 シリコン酸化膜

- 1 2 ドレイン領域

- 13 ドレイン電極

- 14 層間絶縁膜

- 15 ソース配線

- 16 ドレイン配線

【図1】 【図2】

10

【図3】 【図4】

【図5】 【図6】

【図7】 【図8】

【図9】 【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図17】

【図18】

【図19】

【図20】

### フロントページの続き

(72)発明者 林 哲也

神奈川県横浜市神奈川区宝町2番地 日産自動車株式会社内

(72)発明者 倪 威

神奈川県横浜市神奈川区宝町2番地 日産自動車株式会社内

(72)発明者 早見 泰明

神奈川県横浜市神奈川区宝町2番地 日産自動車株式会社内

審査官 市川 武宜

(56)参考文献 国際公開第2015/008550(WO,A1)

特表2002-504267(JP,A)

国際公開第2014/054375(WO,A1)

特開2011-171420(JP,A)

特開平2-271637(JP,A)

特開平10-261635(JP,A)

(58)調査した分野(Int.CI., DB名)

H01L 21/336

H01L 29/78