## (19) 中华人民共和国国家知识产权局

# (12) 发明专利

(10) 授权公告号 CN 106206592 B (45) 授权公告日 2020. 10. 30

(21)申请号 201510334494.1

(22)申请日 2015.06.16

(65) 同一申请的已公布的文献号 申请公布号 CN 106206592 A

(43) 申请公布日 2016.12.07

(30) 优先权数据 10-2014-0161183 2014.11.18 KR

(73) **专利权人** 爱思开海力士有限公司 地址 韩国京畿道

(72) 发明人 宋贤旻

(74) 专利代理机构 北京弘权知识产权代理事务 所(普通合伙) 11363

代理人 俞波 毋二省

(51) Int.CI.

*H01L* 27/112 (2006.01) *G11C* 17/16 (2006.01)

(56) 对比文件

US 8471355 B2,2013.06.25

US 8067288 B2,2011.11.29

CN 101055876 A, 2007.10.17

US 8471355 B2,2013.06.25

审查员 徐晓雷

权利要求书2页 说明书37页 附图43页

#### (54) 发明名称

反熔丝式单次可编程存储器单元阵列及其 操作方法

#### (57) 摘要

一种反熔丝式单次可编程(OTP)存储器单元 阵列包括多个单位单元,其分别位于多个行与多 个列的交叉点;阱区,其被所述多个单位单元所 共享;多个反熔丝栅极,其分别被设置在所述多 个列以与所述阱区相交;多个源极/漏极区,其分 别被设置在所述阱区的介于所述多个反熔丝栅 极之间的部分中;以及多个漏极区,其分别被设 置在所述阱区的位于被排列于最后一列的所述 反熔丝栅极的与排列在第一列的所述反熔丝栅 极相对的一侧的部分中。所述单位单元的每一个 包括反熔丝晶体管,无选择晶体管,所述反熔丝 晶体管具有MOS晶体管结构。

1.一种反熔丝式单次可编程OTP存储器单元阵列,其包括分别位于多个行与多个列的交叉点的多个单位单元,反熔丝式OTP存储器单元阵列包括:

多个阱区,其分别被设置在所述多个行,其中每个阱区被同一行中的单位单元共享;

多个有源区,所述多个有源区之中的每个有源区设置在每个阱区中;

多个反熔丝栅极,其分别被设置在所述多个列以与所述多个阱区相交;

多个源极/漏极区,其分别被设置在所述有源区的介于所述多个反熔丝栅极之间的部分中;以及

多个漏极区,其分别被设置在位于被设置在最后一列的最后反熔丝栅极的一侧的所述 有源区中,所述最后反熔丝栅极的所述一侧与被设置在第一列的第一反熔丝栅极相对,

其中每一个所述单位单元包括一个反熔丝晶体管,无选择晶体管,所述反熔丝晶体管具有金属氧化物半导体MOS晶体管结构,

其中,通过向选中的单位单元的反熔丝栅极施加第一编程电压、向位于设置在同一行中最后一列的最后反熔丝栅极的一侧的漏极区施加接地电压、向所述选中的单位单元所设置在的行的阱区施加接地电压、向所述选中的单位单元未耦接的反熔丝栅极和所述选中的单位单元未设置在的行的阱区施加第二编程电压,所述选中的单位单元被编程。

- 2.如权利要求1所述的反熔丝式0TP存储器单元阵列,其中所述多个阱区的导电类型是与所述多个源极/漏极区和所述多个漏极区的导电类型相反的。

- 3. 如权利要求2所述的反熔丝式0TP存储器单元阵列,

其中所述多个阱区是P型:以及

其中所述多个源极/漏极区和所述多个漏极区是N型。

4. 如权利要求2所述的反熔丝式0TP存储器单元阵列,其进一步包括:

深阱区,其包围所述多个阱区的侧壁及底表面。

- 5. 如权利要求4所述的反熔丝式0TP存储器单元阵列,其中所述深阱区的导电类型是与 所述多个阱区的所述导电类型相反的。

- 6. 如权利要求1所述的反熔丝式0TP存储器单元阵列,

其中被设置在所述第一列的所述反熔丝晶体管的每一个具有半MOS晶体管结构;以及

其中,被设置在所述第一列的所述第一反熔丝栅极包括第一侧壁,所述第一侧壁与在 所述第一反熔丝栅极与被设置在第二列的第二反熔丝栅极之间的所述源极/漏极区的一个 侧壁垂直地对齐;以及第二侧壁,其位于所述阱区之上。

- 7. 如权利要求1所述的反熔丝式0TP存储器单元阵列,其进一步包括:

- 多个字线,其分别电连接至所述多个反熔丝栅极;

- 多个阱偏置线,其分别电连接至所述多个阱区;以及

- 多个位线,其分别电连接至所述多个漏极区。

- 8. 如权利要求1所述的反熔丝式0TP存储器单元阵列,其进一步包括:

- 多个沟道区,其被设置在所述阱区的与所述反熔丝栅极重叠的上部区域中。

- 9. 如权利要求1所述的反熔丝式0TP存储器单元阵列,其中,所述源极/漏极区的每一个 具有两个相对的侧壁,所述两个相对的侧壁与两个相邻的反熔丝栅极部分重叠;并且所述 漏极区的每一个具有与相邻于所述漏极区的所述反熔丝栅极部分重叠的侧壁。

- 10.一种反熔丝式单次可编程OTP存储器单元阵列,其包括:

多个单位单元,其分别位于多个行与多个列的交叉点,所述单位单元的每一个包括反熔丝晶体管,所述反熔丝晶体管具有金属氧化物半导体MOS晶体管结构:

多个字线,其分别被设置在所述多个列,排列在每个列的所述反熔丝晶体管共享所述 多个字线的任一个:

多个阱偏置线,其分别被设置在所述多个行,排列在每个行的所述反熔丝晶体管共享 所述多个阱偏置线的任一个;以及

多个位线,其分别连接至排列在所述多个列的最后一列的所述反熔丝晶体管的漏极端 子,

其中,通过向与选中的单位单元耦接的字线施加第一编程电压、向所述选中的单位单元所设置在的行的位线施加接地电压、向所述选中的单位单元所设置在的行的阱偏置线施加接地电压、向未耦接所述选中的单位单元的字线和所述选中的单位单元未设置在的行的阱偏置线施加第二编程电压,所述选中的单位单元被编程。

- 11.如权利要求10所述的反熔丝式0TP存储器单元阵列,其中排列在每个行的所述反熔 丝晶体管是串联连接的。

- 12. 如权利要求11所述的反熔丝式0TP存储器单元阵列,其进一步包括:

- 多个PN二极管,其设置在所述反熔丝晶体管的漏极端子与所述阱偏置线之间。

- 13.如权利要求12所述的反熔丝式0TP存储器单元阵列,其中,所述PN二极管的阳极连接至所述阱偏置线,并且所述PN二极管的阴极连接至所述反熔丝晶体管的所述漏极端子。

- 14. 如权利要求13所述的反熔丝式0TP存储器单元阵列,其进一步包括:

深阱偏置线:以及

多个深阱PN二极管,其耦接在所述深阱偏置线与所述阱偏置线之间。

- 15. 如权利要求14所述的反熔丝式0TP存储器单元阵列,其中,所述深阱PN二极管的阳极连接至所述阱偏置线,并且所述深阱PN二极管的阴极连接至所述深阱偏置线。

- 16.如权利要求10所述的反熔丝式0TP存储器单元阵列,其中,排列在所述多个列的第一列的所述反熔丝晶体管的所有的源极端子电浮置。

# 反熔丝式单次可编程存储器单元阵列及其操作方法

[0001] 相关申请的交叉引用

[0002] 本申请是要求2014年11月18日向韩国知识产权局申请的韩国专利申请10-2014-0161183的优先权,其整体内容通过引用合并于此。

## 技术领域

[0003] 本公开内容的各种实施例涉及一种非易失性 (nonvolatile) 存储器件,并且更具体而言涉及一种反熔丝式单次可编程 (0TP) 存储器单元阵列及其操作方法。

## 背景技术

[0004] 非易失性存储器件即使在其电源供应中断时也能保持所储存的数据。非易失性存储器件包括只读存储器(ROM)件、OTP存储器件和可重写存储器件。非易失性存储器件一般是利用互补金属氧化物半导体(CMOS)工艺来加以制造。

[0005] 单次可编程的存储器件可以被分类为熔丝式或是反熔丝式OTP存储器件。被包括在熔丝式OTP存储器件中的所有存储器单元在其被编程之前都是短路的,并且接着在编程之后形成开路。相反地,在反熔丝式OTP存储器件中的所有存储器单元在编程之前都可以具有开路,并且可以在编程之后被短路。考虑到MOS晶体管的特性,所述CMOS工艺可能最适合用于制造反熔丝式OTP存储器件。

## 发明内容

[0006] 各种的实施例是针对于一种反熔丝式0TP存储器单元阵列及其操作方法。

[0007] 根据一实施例,其提供有一种反熔丝式0TP存储器单元阵列,其包括分别位于多个行与多个列的交叉点的多个单位单元。所述反熔丝式0TP存储器单元阵列包括多个阱区,其分别被设置在所述多个行;多个反熔丝栅极,其分别被设置在所述多个列以与所述多个阱区相交;多个源极/漏极区,其分别被设置在所述阱区的介于所述多个反熔丝栅极之间的部分中;以及多个漏极区,其分别被设置在位于被设置在最后一列的最后反熔丝栅极的与被设置在第一列的第一反熔丝栅极相对的一侧的所述阱区中。所述单位单元的每一个由具有金属氧化物半导体(MOS)晶体管结构的反熔丝晶体管所构成,无任何选择晶体管。

[0008] 根据另一实施例,一种反熔丝式OTP存储器单元阵列包括多个单位单元,其分别位于多个行与多个列的交叉点。所述单位单元的每一个是由反熔丝晶体管所构成的,其具有金属氧化物半导体(MOS)晶体管结构。多个字线分别被设置在所述多个列。排列在每个列的所述反熔丝晶体管共享所述多个字线的任一个。多个阱偏置线分别被设置在所述多个行。排列在每个行的所述反熔丝晶体管共享所述多个阱偏置线的任一个。多个位线分别连接至排列在所述多个列的最后一列的所述反熔丝晶体管的漏极端子。

[0009] 根据另一实施例,提供有一种反熔丝式0TP存储器单元阵列,其包括多个分别位于多个行与多个列的交叉点的单位单元。所述反熔丝式0TP存储器单元阵列包括阱区,其被所述多个单位单元所共享;多个反熔丝栅极,其分别被设置在所述多个行与所述多个列的交

叉点以构成所述多个单位单元;多个源极/漏极区,其分别被设置在所述阱区的介于排列在 所述多个行的每一个中的所述多个反熔丝栅极之间的部分中;以及多个漏极区,其分别被 设置在所述阱区的位于排列在所述多个列的最后一列的所述反熔丝栅极的与排列在所述 多个列的第一列的所述反熔丝栅极相对的一侧的部分中。所述单位单元的每一个是由具有 金属氧化物半导体(MOS)晶体管结构的反熔丝晶体管所构成的,无任何选择晶体管。

[0010] 根据另一实施例,一种反熔丝式0TP存储器单元阵列包括多个单位单元,其分别位于多个行与多个列的交叉点。所述单位单元的每一个是由反熔丝晶体管所构成的,其具有一种金属氧化物半导体 (MOS) 晶体管结构。多个字线分别连接至所述反熔丝晶体管。所述反熔丝晶体管彼此共享阱偏置线。多个位线分别连接至排列在所述多个列的最后一列的所述反熔丝晶体管的漏极端子。

[0011] 根据另一实施例,提供有一种操作反熔丝式0TP存储器单元阵列的方法,所述反熔 丝式0TP存储器单元阵列包括分别位于多个行与多个列的交叉点的多个单位单元;多个字 线,其分别被设置在所述多个列;多个阱区,其分别被设置在所述多个行;多个阱偏置线,其分别连接至所述多个阱区;多个位线,其分别连接至排列在所述多个列的最后一列的所述 单位单元的漏极端子;以及多个PN二极管,其耦接在所述多个阱偏置线与所述多个单位单元的所述漏极端子之间。所述方法包括选择所述多个行的行;以及依序地编程排列在选中的行的所述单位单元。所述多个单位单元的每一个是由具有金属氧化物半导体(MOS)晶体管结构反熔丝晶体管所构成的,无任何选择晶体管。

[0012] 根据另一实施例,提供有一种操作反熔丝式0TP存储器单元阵列的方法,所述反熔 丝式0TP存储器单元阵列包括分别位于多个行与多个列的交叉点的多个单位单元;多个字 线,其分别被设置在所述多个列;多个阱区,其分别被设置在所述多个行;多个阱偏置线,其分别连接至所述多个阱区;多个位线,其分别连接至排列在所述多个列的最后一列的所述 单位单元的漏极端子;以及多个PN二极管,其耦接在所述多个阱偏置线与所述多个单位单元的所述漏极端子之间。所述方法包括选择所述多个列的列;以及同时编程排列在选中的列的所述单位单元中的至少一个。所述多个单位单元的每一个是由具有金属氧化物半导体 (MOS) 晶体管结构的反熔丝晶体管所构成的,无任何选择晶体管。

[0013] 根据另一实施例,提供有一种操作反熔丝式0TP存储器单元阵列的方法,所述反熔丝式0TP存储器单元阵列包括分别位于多个行与多个列的交叉点的多个单位单元;多个字线,其分别连接至所述多个单位单元;阱区,其被所述多个单位单元所共享;阱偏置线,其连接至所述阱区;多个位线,其分别连接至排列在所述多个列的最后一列的所述单位单元的漏极端子;以及多个PN二极管,其耦接在所述阱偏置线与所述多个单位单元的所述漏极端子之间。所述方法包括选择所述多个行的行;以及依序地编程排列在选中的行的所述单位单元。所述多个单位单元的每一个是由具有金属氧化物半导体(MOS)晶体管结构的反熔丝晶体管所构成的,无任何选择晶体管。

[0014] 根据另一实施例,提供有一种操作反熔丝式0TP存储器单元阵列的方法,所述反熔 丝式0TP存储器单元阵列包括分别位于多个行和多个列的交叉点的多个单位单元;多个字 线,其分别连接至所述多个单位单元;阱区,其被所述多个单位单元所共享;阱偏置线,其连接至所述阱区;多个位线,其分别连接至排列在所述多个列的最后一列的所述单位单元的漏极端子;以及多个PN二极管,其耦接在所述阱偏置线与所述多个单位单元的所述漏极端

子之间。所述方法包括选择所述多个列的列;以及同时编程排列在选中的列的所述单位单元中的至少一个。所述多个单位单元的每一个是由具有金属氧化物半导体 (MOS) 晶体管结构的反熔丝晶体管所构成的,无选择晶体管。

## 附图说明

[0015] 本公开内容的各种实施例在考虑到所附的附图和所附的详细说明下将会变得更明显,其中:

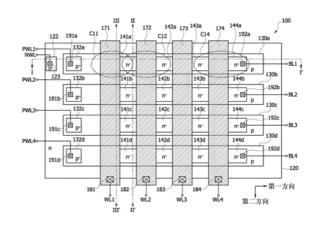

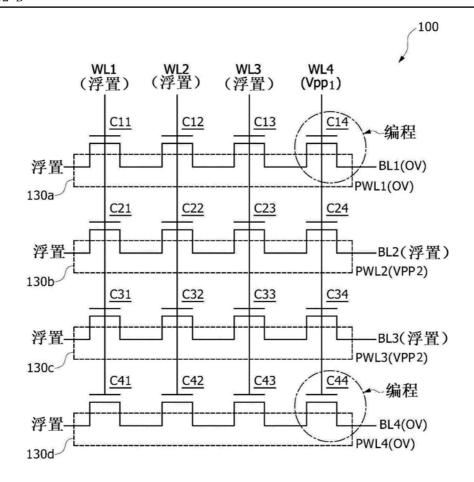

[0016] 图1是描绘根据一实施例的反熔丝式0TP存储器单元阵列的布局图;

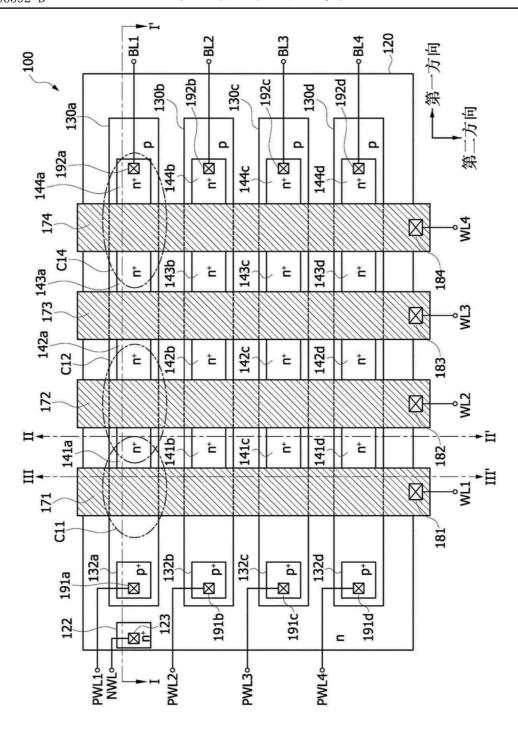

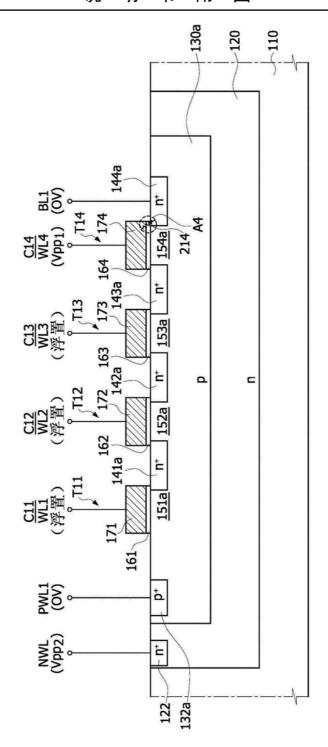

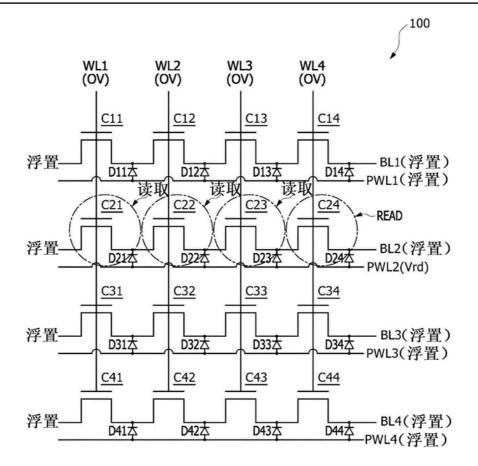

[0017] 图2是沿着图1的线I-I'所取的横截面图;

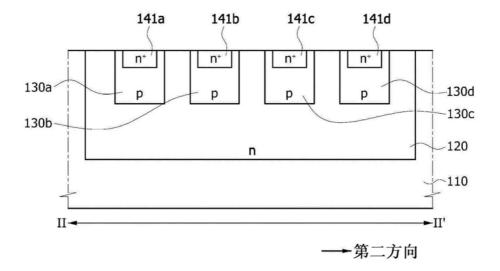

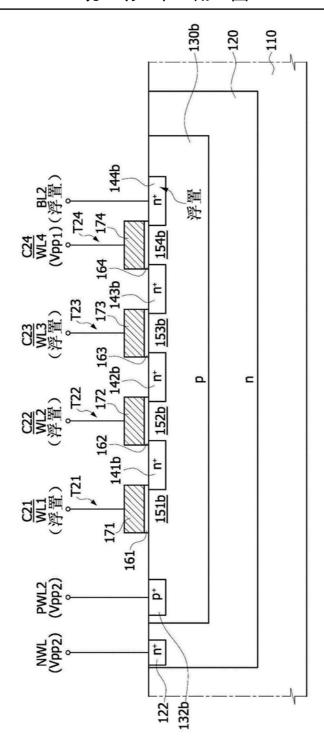

[0018] 图3是沿着图1的线Ⅱ-Ⅱ'所取的横截面图;

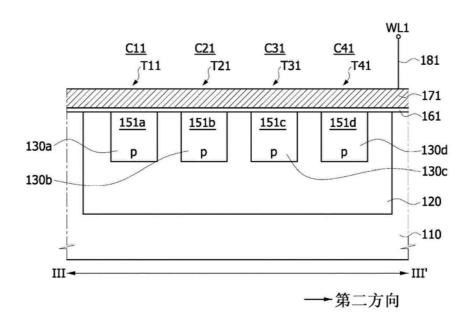

[0019] 图4是沿着图1的线Ⅲ-Ⅲ'所取的横截面图;

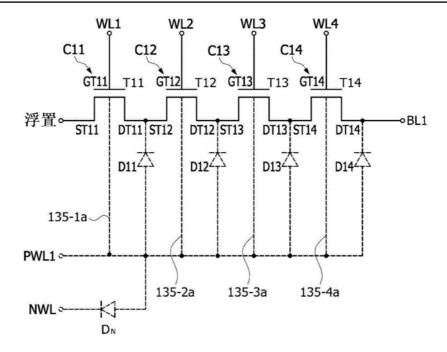

[0020] 图5是描绘在图2中所示的横截面图的等效电路图;

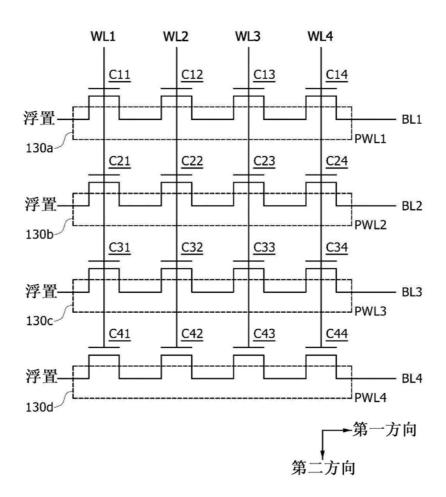

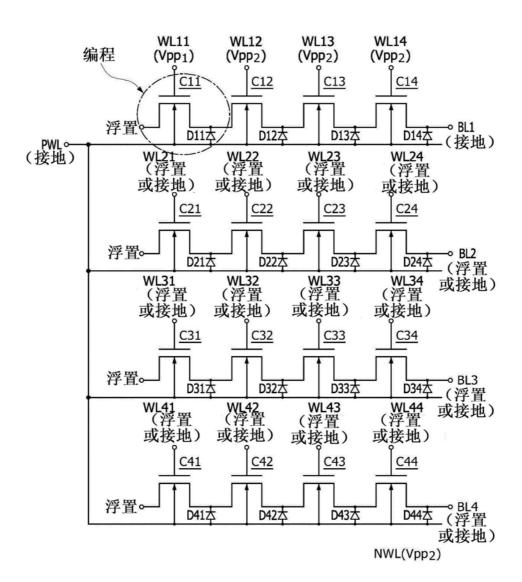

[0021] 图6是描绘在图1中所示的反熔丝式0TP存储器单元阵列的等效电路图;

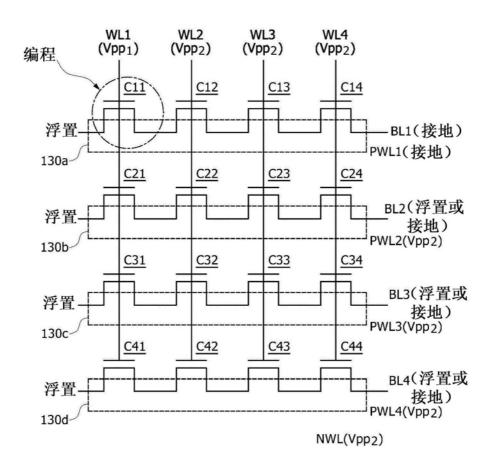

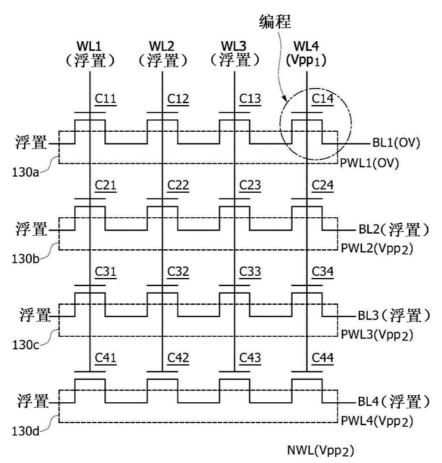

[0022] 图7至20是描绘在图6中所示的反熔丝式0TP存储器单元阵列的编程操作的示意图;

[0023] 图21至24是描绘在图6中所示的反熔丝式0TP存储器单元阵列的其它编程操作的示意图:

[0024] 图25至27是描绘在图6中所示的反熔丝式0TP存储器单元阵列的读取操作的示意图:

[0025] 图28是描绘根据另一实施例的反熔丝式OTP存储器单元阵列的布局图:

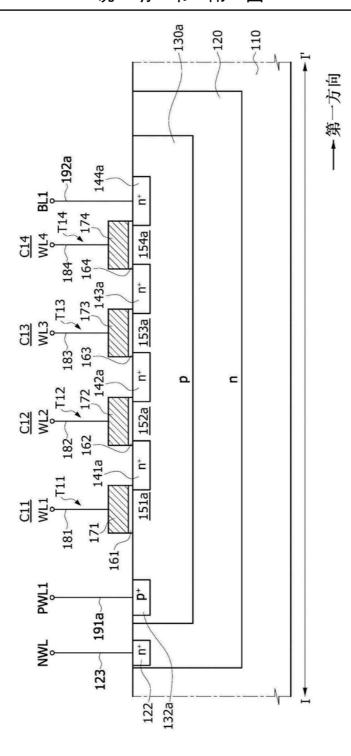

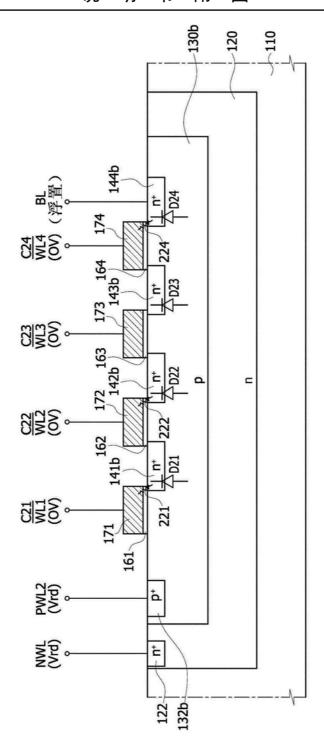

[0026] 图29是沿着图28的线IV-IV'所取的横截面图;

[0027] 图30是描绘在图29中所示的横截面图的等效电路图:

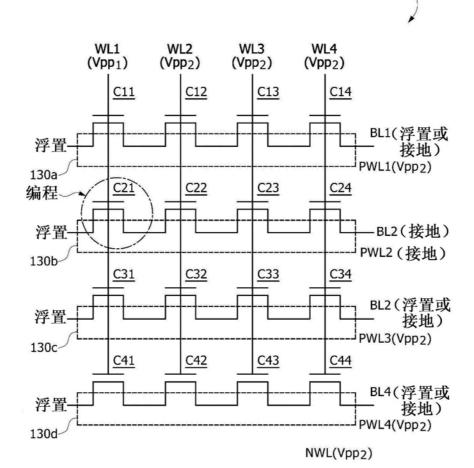

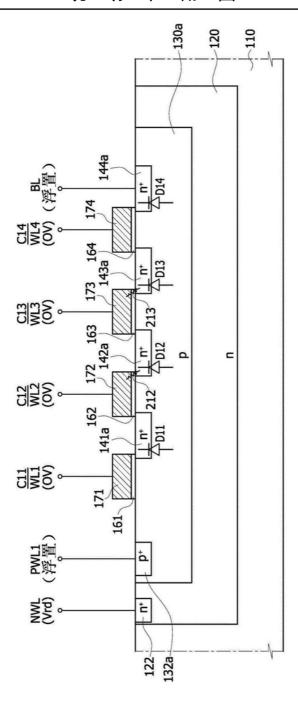

[0028] 图31是描绘在图28中所示的反熔丝式0TP存储器单元阵列的等效电路图:

[0029] 图32至41是描绘在图31中所示的反熔丝式0TP存储器单元阵列的编程操作的示意图;

[0030] 图42及43是描绘在图31中所示的反熔丝式0TP存储器单元阵列的其它编程操作的示意图:以及

[0031] 图44是描绘在图31中所示的反熔丝式0TP存储器单元阵列的读取操作的示意图。

## 具体实施方式

[0032] 反熔丝元件可以被形成为最初具有绝缘状态,亦即电开路状态,并且在等于或大于阈值电压的电压被施加至其时,可以被编程以具有导电状态,亦即电短路状态。因而,可编程的反熔丝元件可以被采用在构成一种反熔丝式0TP存储器单元阵列的多个单位单元的每一个中。可编程的反熔丝元件可以被实现以具有一种金属氧化物半导体(MOS)晶体管结构。构成反熔丝式0TP存储器单元阵列的单位单元中的每一个可以包括至少一个反熔丝晶体管和至少一个选择晶体管。选择晶体管可以在编程操作或是读取操作期间被用来选择单位单元中的至少一个。然而,根据以下的实施例,构成反熔丝式0TP存储器单元阵列的单位单元中的每一个可以被配置以只包括单一反熔丝晶体管,而无选择晶体管。换言之,根据实施例,一个或多个特定的单位单元甚至可以在无任何选择晶体管的情况下被选择性地编程

及读出。因此,一种反熔丝式OTP存储器单元阵列所占用的平面面积可以被减小,以增大包括反熔丝式OTP存储器单元阵列的半导体存储器件的集成密度。

[0033] 将会了解到的是,尽管第一、第二、第三等等的术语可能在此被使用来描述各种的元件,但是这些元件不应该受限于这些术语。这些术语只是被用来区别一元件与另一元件。因此,在某些实施例中的第一元件可能在其它实施例中被称为第二元件,而不脱离本公开内容的教导。

[0034] 同样将会理解到的是,当一元件被称为位于另一元件"上"、"之上"、"上方"、"下"、"之下"或是"下方"时,其可以直接接触另一元件、或是至少一中间元件可以存在于两者之间。因而,在此所用的例如是"上"、"之上"、"上方"、"下"、"之下"、"下方"与类似者的术语只是为了描述特定实施例的目的而已,因而并不欲限制本公开内容的范围。

[0035] 进一步将会理解到的是,当一元件被称为"连接"或"耦接"至另一元件时,其可以直接连接或耦接至另一元件、或是介于中间的元件可以存在。相对地,当一元件被称为"直接连接"或"直接耦接"至另一元件时,并没有介于中间的元件存在。

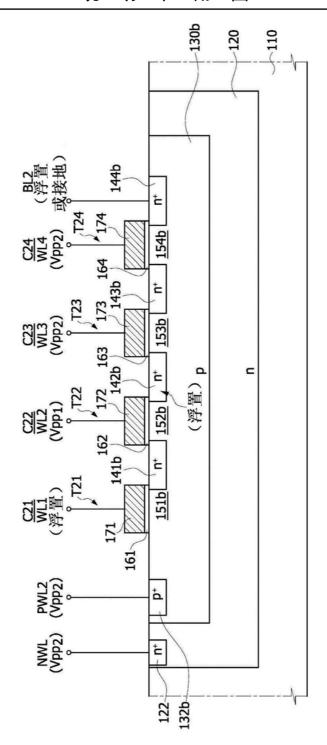

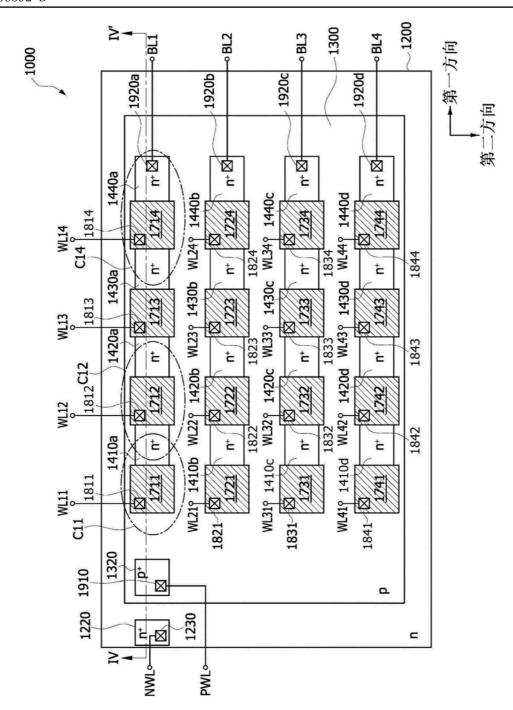

[0036] 图1是描绘根据一实施例的一种反熔丝式OTP存储器单元阵列100的布局图。

[0037] 参照图1,反熔丝式0TP存储器单元阵列100可以包括多个阱区130a、130b、130c及130d。阱区130a、130b、130c及130d的侧壁和底表面可以被深阱区120包围。深阱区120可以具有第一导电类型,并且阱区130a、130b、130c及130d可以具有与第一导电类型相反的第二导电类型。在本实施例中,深阱区120可以是N型,并且阱区130a、130b、130c及130d可以是N型。深阱区120可以是P型,并且阱区130a、130b、130c及130d可以是N型。深阱区120可以通过执行利用掩模图案的离子注入工艺和扩散工艺来被形成。类似地,阱区130a、130b、130c及130d亦可以通过执行利用掩模图案的离子注入工艺和扩散工艺来被形成。类似地,阱区130a、130b、130c及130d亦可以通过执行利用掩模图案的离子注入工艺和扩散工艺来被形成。阱区130a、130b、130c及130d的每一个可以被设置以具有在第一方向(例如是在图1中的水平方向)上延伸的条带或线形。阱区130a、130b、130c及130d可以沿第二方向(例如是在图1中是垂直的方向)排列,并且可以在第二方向上彼此间隔开一定距离。阱区130a、130b、130c及130d分别可以被设置在多个行。例如,第一阱区130a可以被设置在第一行,第二阱区130b可以被设置在第二行,第三阱区130c可以被设置在第三行,并且第四阱区130d可以被设置在第四行。如在图1中所绘,第二方向可以是垂直于第一方向。然而,在某些实施例中,第二方向可以用非直角的角度与第一方向相交。

[0038] 多个反熔丝栅极171、172、173及174可以被设置在深阱区120之上,以与阱区130a、130b、130c及130d相交。反熔丝栅极171、172、173及174的每一个可以具有在第二方向上延伸的条带或线形。反熔丝栅极171、172、173及174可以沿第一方向排列,并且可以在第一方向上彼此间隔开一定距离。尽管未显示在图1中,反熔丝绝缘层可以被设置在反熔丝栅极171、172、173及174与阱区130a、130b、130c及130d之间。反熔丝绝缘层可以延伸以被设置在反熔丝栅极171、172、173及174与深阱区120之间。换言之,反熔丝栅极171、172、173及174可以藉由反熔丝绝缘层而与深阱区120和阱区130a、130b、130c及130d电绝缘。反熔丝栅极171、172、173及174分别可以被设置在多个列中。例如,第一反熔丝栅极171可以被设置在第一列,第二反熔丝栅极172可以被设置在第二列,第三反熔丝栅极173可以被设置在第二列,第三反熔丝栅极174可以被设置在第四列。因而,分别被设置在第一至第四列的反熔丝栅极171、172、173及174可以相交于分别被设置在第一至第四行的阱区130a、130b、130c及

130d,以提供其多个交叉点。

[0039] 反熔丝式0TP存储器单元阵列100的多个单位单元可以分别位于第一至第四阱区130a、130b、130c及130d与第一至第四反熔丝栅极171、172、173及174的交叉点。因而,反熔丝式0TP存储器单元阵列100可以包括十六个单位单元,其被排列以具有'4×4'矩阵形式。反熔丝式0TP存储器单元阵列100的单位单元的每一个可以通过阱区130a、130b、130c及130d被设置所在的行的一行、和反熔丝栅极171、172、173及174被设置所在的列的一列来加以限定。例如,位于第一行与第一列的交叉点的单位单元可以对应于被设置在第一阱区130a和第一反熔丝栅极171的交叉点的单位单元C11。类似地,位于第一行与第二列的交叉点的单位单元可以对应于被设置在第一阱区130a和第二反熔丝栅极172的交叉点的单位单元C12。因此,其余的单位单元亦可以通过所述行的一行和所述列的一列来加以限定。

[0040] 多个第一源极/漏极区141a、142a及143a和第一漏极区144a可以被设置在位于第一行的第一阱区130a中。尽管未显示在图1中,第一源极/漏极区141a、142a及143a和第一漏极区144a的侧壁及底表面可以被第一阱区130a包围。第一源极/漏极区141a、142a及143a和第一漏极区144a可以沿第一方向排列,并且可以彼此间隔开。第一漏极区144a可以被设置在第四反熔丝栅极174的与第三反熔丝栅极173相对的一侧,并且可以在第一阱区130a的顶表面被露出。第一源极/漏极区141a在平面图中可以位于第一反熔丝栅极与第二反熔丝栅极5第二反熔丝栅极5第二反熔丝栅极与第二反熔丝栅极与第三反熔丝栅极5第三反熔丝栅极5第三反熔丝栅极5第三反熔丝栅极5第三反熔丝栅极5第三反熔丝栅极5第三反熔丝栅极5第三反熔丝栅极5第四反熔丝栅极173与174之间并且被露出。第一源极/漏极区143a在平面图中可以位于第三反熔丝栅极与第四反熔丝栅极173与174之间并且被露出。第一源极/漏极区141a、142a及143a可以与第一、第二、第三及第四反熔丝栅极171、172、173及174自对准。尽管未显示在图1中,第一源极/漏极区141a、142a及143a的每一个都可以具有两个相对的侧壁,所述侧壁与相邻的第一至第四反熔丝栅极171、172、173及174中的两个重叠。第一漏极区144a可以具有与第四反熔丝栅极174部分重叠的侧壁。当第一阱区130a是P型时,第一源极/漏极区141a、142a及143a和第一漏极区144a可以是N型。

[0041] 多个第二源极/漏极区141b、142b及143b和第二漏极区144b可以被设置在位于第二行的第二阱区130b中。尽管未显示在图1中,第二源极/漏极区141b、142b及143b和第二漏极区144b的侧壁及底表面可以被第二阱区130b包围。第二源极/漏极区141b、142b及143b和第二漏极区144b可以沿第一方向排列,并且可以彼此间隔开。第二漏极区144b可以被设置在第四反熔丝栅极174的与第三反熔丝栅极173相对的一侧,并且可以在第二阱区130b的顶表面被露出。第二源极/漏极区141b在平面图中可以位于第一反熔丝栅极与第二反熔丝栅极171与172之间并且被露出。第二源极/漏极区142b在平面图中可以位于第二反熔丝栅极与第三反熔丝栅极与第三反熔丝栅极173与174之间并且被露出。第二源极/漏极区143b在平面图中可以位于第三反熔丝栅极与第四反熔丝栅极173与174之间并且被露出。第二源极/漏极区141b、142b及143b可以与第一、第二、第三及第四反熔丝栅极171、172、173及174自对准。尽管未显示在图1中,第二源极/漏极区141b、142b及143b的每一个都可以具有两个相对的侧壁,所述侧壁与相邻的第一至第四反熔丝栅极171、172、173及174中的两个重叠。第二漏极区144b可以具有与第四反熔丝栅极174部分重叠的侧壁。当第二阱区130b是P型时,第二源极/漏极区141b、142b及143b和第二漏极区144b可以是N型。

[0042] 多个第三源极/漏极区141c、142c及143c和第三漏极区144c可以被设置在位于第

三行的第三阱区130c中。尽管未显示在图1中,第三源极/漏极区141c、142c及143c和第三漏极区144c的侧壁及底表面可以被第三阱区130c包围。第三源极/漏极区141c、142c及143c和第三漏极区144c可以沿第一方向排列,并且可以彼此间隔开。第三漏极区144c可以被设置在第四反熔丝栅极174的与第三反熔丝栅极173相对的一侧,并且可以在第三阱区130c的顶表面被露出。第三源极/漏极区141c在平面图中可以位于第一反熔丝栅极与第二反熔丝栅极171与172之间并且被露出。第三源极/漏极区142c在平面图中可以位于第二反熔丝栅极与第三反熔丝栅极与第三反熔丝栅极与第三反熔丝栅极与第三反熔丝栅极与第三反熔丝栅极与第四反熔丝栅极173与174之间并且被露出。第三源极/漏极区143c在平面图中可以位于第三反熔丝栅极与第四反熔丝栅极173与174之间并且被露出。第三源极/漏极区141c、142c及143c可以与第一、第二、第三及第四反熔丝栅极171、172、173及174自对准。尽管未显示在图1中,第三源极/漏极区141c、142c及143c的每一个都可以具有两个相对的侧壁,侧壁与相邻的第一至第四反熔丝栅极171、172、173及174中的两个重叠。第三漏极区144c可以具有与第四反熔丝栅极174部分重叠的侧壁。当第三阱区130c是P型时,第三源极/漏极区141c、142c及143c和第三漏极区144c可以是N型。

[0043] 多个第四源极/漏极区141d、142d及143d和第四漏极区144d可以被设置在位于第四行的第四阱区130d中。尽管未显示在图1中,第四源极/漏极区141d、142d及143d和第四漏极区144d的侧壁及底表面可以被第四阱区130d包围。第四源极/漏极区141d、142d及143d和第四漏极区144d可以沿第一方向排列,并且可以彼此间隔开。第四漏极区144d可以被设置在第四反熔丝栅极174的与第三反熔丝栅极173相对的一侧,并且可以在第四阱区130d的顶表面被露出。第四源极/漏极区141d在平面图中可以位于第一反熔丝栅极与第二反熔丝栅极5第二反熔丝栅极5第二反熔丝栅极与第二反熔丝栅极与第三反熔丝栅极5第四原熔丝栅极5第四原熔丝栅极5第四反熔丝栅极5第四反熔丝栅极173与174之间并且被露出。第四源极/漏极区143d在平面图中可以位于第三反熔丝栅极与第四反熔丝栅极173与174之间并且被露出。第四源极/漏极区141d、142d及143d可以与第一、第二、第三及第四反熔丝栅极171、172、173及174自对准。尽管未显示在图1中,第四源极/漏极区141d、142d及143d的每一个都可以具有两个相对的侧壁,侧壁与相邻的第一至第四反熔丝栅极171、172、173及174中的两个重叠。第四漏极区144d可以具有与第四反熔丝栅极174部分重叠的侧壁。当第四阱区130d是P型时,第四源极/漏极区141d、142d及143d和第四漏极区144d可以是N型。

[0044] 源极/漏极区的任一个都可以被设置在介于位于第一列的第一反熔丝栅极171与位于第二列的第二反熔丝栅极172之间的每个行。换言之,第一源极/漏极区141a可以被设置在介于第一反熔丝栅极与第二反熔丝栅极171与172之间的位于第一行的第一阱区130a中,并且第二源极/漏极区141b可以被设置在介于第一反熔丝栅极与第二反熔丝栅极171与172之间的位于第二行的第二阱区130b中。类似地,第三源极/漏极区141c可以被设置在介于第一反熔丝栅极与第二反熔丝栅极171与172之间的位于第三行的第三阱区130c中,并且第四源极/漏极区141d可以被设置在介于第一反熔丝栅极与第二反熔丝栅极171与172之间的位于第四行的第四阱区130d中。第一、第二、第三及第四源极/漏极区141a、141b、141c及141d可以用作构成排列在第一列的单位单元的单元晶体管的漏极区,并且亦可以用作构成排列在第二列的单位单元的单元晶体管的源极区。

[0045] 源极/漏极区的任一个都可以被设置在介于位于第二列的第二反熔丝栅极172与位于第三列的第三反熔丝栅极173之间的每个行。换言之,第一源极/漏极区142a可以被设

置在介于第二反熔丝栅极与第三反熔丝栅极172与173之间的位于第一行的第一阱区130a中,并且第二源极/漏极区142b可以被设置在介于第二反熔丝栅极与第三反熔丝栅极172与173之间的位于第二行的第二阱区130b中。类似地,第三源极/漏极区142c可以被设置在介于第二反熔丝栅极与第三反熔丝栅极172与173之间的位于第三行的第三阱区130c中,并且第四源极/漏极区142d可以被设置在介于第二反熔丝栅极与第三反熔丝栅极172与173之间的位于第四行的第四阱区130d中。第一、第二、第三及第四源极/漏极区142a、142b、142c及142d可以用作构成排列在第二列的单位单元的单元晶体管的漏极区,并且亦可以用作构成排列在第三列的单位单元的单元晶体管的源极区。

[0046] 源极/漏极区的任一个都可以被设置在介于位于第三列的第三反熔丝栅极173与位于第四列的第四反熔丝栅极174之间的每个行。换言之,第一源极/漏极区143a可以被设置在介于第三反熔丝栅极与第四反熔丝栅极173与174之间的位于第一行的第一阱区130a中,并且第二源极/漏极区143b可以被设置在介于第三反熔丝栅极与第四反熔丝栅极173与174之间的位于第二行的第二阱区130b中。类似地,第三源极/漏极区143c可以被设置在介于第三反熔丝栅极与第四反熔丝栅极173与174之间的位于第三行的第三阱区130c中,并且第四源极/漏极区143d可以被设置在介于第三反熔丝栅极与第四反熔丝栅极173与174之间的位于第四行的第四阱区130d中。第一、第二、第三及第四源极/漏极区143a、143b、143c及143d可以用作构成排列在第三列的单位单元的单元晶体管的源极区,并且亦可以用作构成排列在第四列的单位单元的单元晶体管的源极区。

[0047] 反熔丝式0TP存储器单元阵列100的单位单元可以被配置以具有单个MOS晶体管结构。例如,位于第一行与第二列的交叉点的单位单元C12可以是MOS晶体管,其包括第一阱区130a、第一源极/漏极区141a及142a、和第二反熔丝栅极172。第一源极/漏极区141a可以用作单位单元C12的源极区,并且第一源极/漏极区142a可以用作单位单元C12的漏极区。如上所述,反熔丝绝缘层(亦即,第二反熔丝绝缘层)可以被设置在第一阱区130a与第二反熔丝栅极172之间。除了第一列和最后一列(亦即,第四列)之外,其它排列在第二及第三列的单位单元的每一个亦可以具有与单位单元C12相同的结构。

[0048] 排列在最后一列(亦即,第四列)中的单位单元的每一个亦可以具有单个MOS晶体管结构。例如,位于第一行与第四列的交叉点的单位单元C14可以是MOS晶体管,其包括第一阱区130a、第一源极/漏极区143a、第一漏极区144a和第四反熔丝栅极174。第一源极/漏极区143a可以用作单位单元C14的源极区,并且第一漏极区144a可以用作单位单元C14的漏极区。排列在最后一列(亦即,第四列)中的其余的单位单元的每一个亦可以具有与单位单元C14相同的结构。

[0049] 相对地,排列在第一列的单位单元的每一个可以具有半MOS晶体管结构。例如,位于第一行与第一列的交叉点的单位单元C11可以是半MOS晶体管,其包括第一阱区130a、第一源极/漏极区141a和第一反熔丝栅极171。第一源极/漏极区141a可以用作单位单元C11的漏极区,而且没有源极区被设置在单位单元C11中。排列在第一列的其余的单位单元的每一个亦可以具有与单位单元C11相同的结构。

[0050] 深阱接触区122可以被设置在深阱区120中。深阱接触区122可以与第一至第四阱区130a、130b、130c及130d间隔开。深阱接触区122可以具有与深阱区120相同的导电类型(例如是第一导电类型),并且可以具有杂质浓度高于深阱区120的杂质浓度。深阱接触区

122可以通过深阱偏置线接触123来电连接至深阱偏置线NWL。尽管图1是描绘了一个其中单一深阱接触区122被设置在深阱区120中的例子,但是本公开内容并不限于此。例如,在某些实施例中,多个深阱接触区可以被设置在深阱区120中。在此情况下,多个深阱接触区可以连接至深阱偏置线NWL。

[0051] 第一阱接触区132a、第二阱接触区132b、第三阱接触区132c和第四阱接触区132d分别可以被设置在第一至第四阱区130a、130b、130c及130d中。第一至第四阱接触区132a、132b、132c及132d可以具有与第一至第四阱区130a、130b、130c及130d相同的导电类型(例如是第二导电类型)。此外,第一至第四阱接触区132a、132b、132c及132d可以具有杂质浓度高于第一至第四阱区130a、130b、130c及130d的杂质浓度。

[0052] 第一反熔丝栅极171可以通过第一字线接触181来电连接至第一字线WL1,并且第二反熔丝栅极172可以通过第二字线接触182来电连接至第二字线WL2。类似地,第三反熔丝栅极173可以通过第三字线接触183来电连接至第三字线WL3,并且第四反熔丝栅极174可以通过第四字线接触184来电连接至第四字线WL4。第一阱接触区132a可以通过第一阱偏置线接触191a来电连接至第一阱偏置线PWL1,并且第二阱接触区132b可以通过第二阱偏置线接触191b来电连接至第二阱偏置线PWL2。类似地,第三阱接触区132c可以通过第三阱偏置线接触191c来电连接至第三阱偏置线PWL3,并且第四阱接触区132d可以通过第四阱偏置线接触191d来电连接至第三阱偏置线PWL3,并且第四阱接触区132d可以通过第四阱偏置线接触191d来电连接至第四阱偏置线PWL4。在第一阱区130a中的第一漏极区144a可以通过第一位线接触192a来电连接至第一位线BL1,并且在第二阱区130b中的第二漏极区144b可以通过第二位线接触192b来电连接至第二位线BL2。类似地,在第三阱区130c中的第三漏极区144c可以通过第三位线接触192c来电连接至第三位线BL3,并且在第四阱区130d中的第四漏极区144d可以通过第四位线接触192d来电连接至第四位线BL4。

[0053] 尽管图1描绘了一个其中反熔丝式0TP存储器单元阵列100包括十六个单位单元的例子,其中所述十六个单位单元以通过第一至第四阱区130a、130b、130c及130d和第一至第四反熔丝栅极171、172、173及174所限定的'4×4'矩阵形式排列,但是本公开内容并不限于此。例如,在某些实施例中,反熔丝式0TP存储器单元阵列100可以包括以通过一、二、三、五或更多个阱区和一、二、三、五或更多个反熔丝栅极所限定的另一种矩阵形式排列的多个单位单元。在某些其它实施例中,阱区的数目可以是不同于反熔丝栅极的数目。不论在任何情形中,根据本公开内容的反熔丝式0TP存储器单元阵列可以是基于参考图1所述的配置。

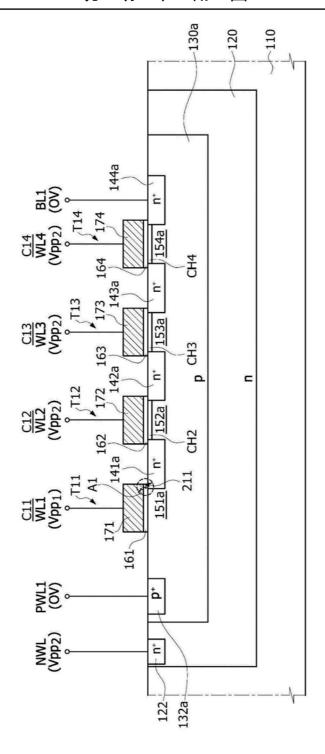

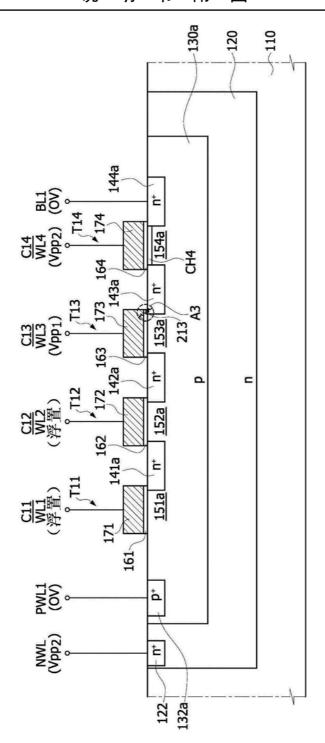

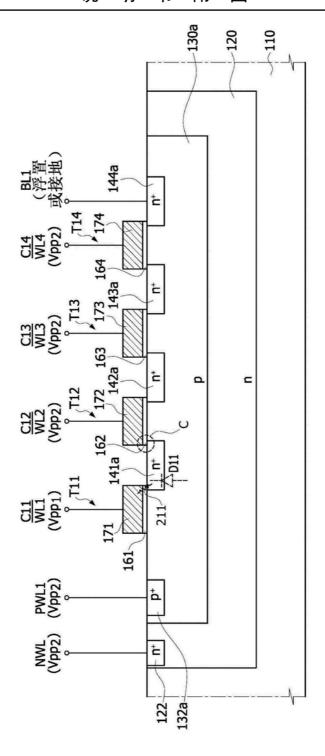

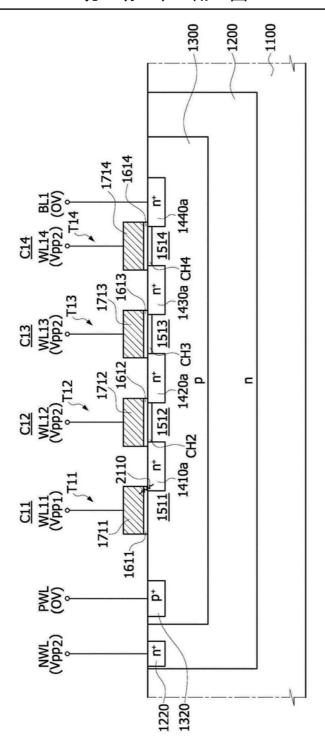

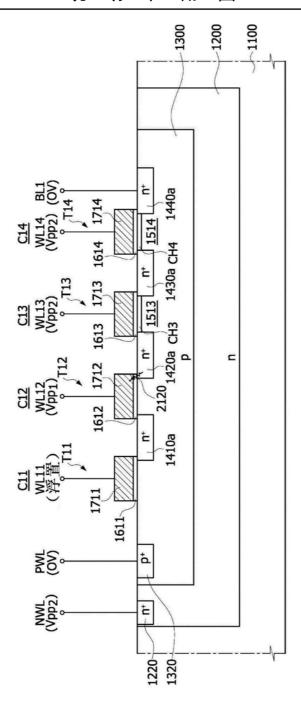

[0054] 图2是沿着图1的线I-I'所取的横截面图。图2描绘了与在图1中分别被设置在第一行与第一至第四列的交叉点的单位单元C11、C12、C13及C14相对应的第一晶体管T11、T12、T13及T14的横截面图。沿着第二、第三及第四行所取的横截面图的每一个可以与在图2中所描绘的横截面图实质相同。在图1及2中,相同的附图标记表示相同的元件。

[0055] 参照图1及图2,具有第一导电类型的深阱区120(例如,N型深阱区)可以被设置在 村底110的上部区域中。深阱接触区122和第一阱区130a可以被设置在深阱区120的上部区域中。因而,深阱接触区122的侧壁及底表面和第一阱区130a的侧壁及底表面可以被深阱区120包围。如参考图1所述的,被设置在深阱区120中的深阱接触区122的数目可以是等于或大于1。深阱接触区122可以具有与深阱区120相同的导电类型。然而,深阱接触区122的杂质浓度可以高于深阱区120的杂质浓度。

[0056] 第一阱接触区132a、多个第一源极/漏极区141a、142a及143a、和第一漏极区144a

可以依序地排列在第一阱区130a的上部区域中,以在第一方向上彼此间隔开。第一阱接触区132a可以具有与第一阱区130a相同的导电类型。然而,第一阱接触区132a的杂质浓度可以高于第一阱区130a的杂质浓度。第一源极/漏极区141a、142a及143a和第一漏极区144a全部都可以是N型。在第一列的第一沟道区151a可以被设置在第一源极/漏极区141a的与第一漏极区144a相对的一侧。在第二列的第一沟道区152a可以被设置在第一源极/漏极区141a与第一源极/漏极区142a之间。在第三列的第一沟道区153a可以被设置在第一源极/漏极区141a与第一源极/漏极区143a之间。再者,在第四列的第一沟道区154a可以被设置在第一源极/漏极区143a与第一源极区144a之间。

[0057] 第一反熔丝绝缘层161和第一反熔丝栅极171可以依序地被层叠在第一列的第一沟道区151a上。第一反熔丝绝缘层161和第一反熔丝栅极171的一侧壁可以与第一源极/漏极区141a的第一侧壁垂直地对齐。第二反熔丝绝缘层162和第二反熔丝栅极172可以依序地被层叠在第二列的第一沟道区152a上。第二反熔丝绝缘层162和第二反熔丝栅极172的一侧壁可以与第一源极/漏极区141a的第二侧壁垂直地对齐,并且第二反熔丝绝缘层162和第二反熔丝栅极172的第二侧壁可以与第一源极/漏极区142a的第一侧壁垂直地对齐。第三反熔丝绝缘层163和第三反熔丝栅极173可以依序地被层叠在第三列的第一沟道区153a上。第三反熔丝绝缘层163和第三反熔丝栅极173的一侧壁可以与第一源极/漏极区142a的第二侧壁垂直地对齐,并且第三反熔丝绝缘层163和第三反熔丝栅极173的第二侧壁可以与第一源极/漏极区143a的第一侧壁垂直地对齐。第四反熔丝绝缘层164和第四反熔丝栅极174可以依序地被层叠在第四列的第一沟道区154a上。第四反熔丝绝缘层164和第四反熔丝栅极174的一侧壁可以与第一源极/漏极区143a的第二侧壁垂直地对齐,并且第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四反熔丝绝缘层164和第四处容处处容k

[0058] 在被排列于第一行的第一晶体管T11、T12、T13及T14中的在第一列的第一晶体管T11可以具有半MOS晶体管结构。在第一行的其余的第一晶体管T12、T13及T14的每一个都可以具有完整的MOS晶体管结构。

[0059] 第一至第四反熔丝栅极171、172、173及174可以分别通过第一至第四字线接触181、182、183及184来电连接至第一至第四字线WL1、WL2、WL3及WL4。深阱接触区122可以通过深阱偏置线接触123来电连接至深阱偏置线NWL。第一阱接触区132a可以通过第一阱偏置线接触191a来电连接至第一阱偏置线PWL1。第一漏极区144a可以通过第一位线接触192a来电连接至第一位线BL1。

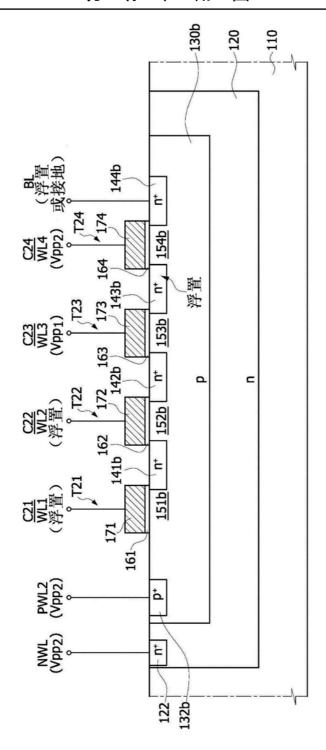

[0060] 图3是沿着图1的线 II - II,所取的横截面图。在图1、2及3中,相同的附图标记表示相同的元件。

[0061] 参照图1及3,被掺杂P型杂质的第一至第四阱区130a、130b、130c及130d可以依序地排列在N型深阱区120的上部区域中,以在第二方向上彼此间隔开。被掺杂N型杂质的第一源极/漏极区141a、141b、141c及141d分别可以被设置在第一至第四阱区130a、130b、130c及130d的上部区域中。

[0062] 由于被掺杂P型杂质的第一至第四阱区130a、130b、130c及130d的侧壁及底表面是被N型深阱区120包围,因此第一至第四阱区130a、130b、130c及130d可以通过N型深阱区120来彼此电隔离。明确地说,当第一至第四阱区的个(例如是第一阱区130a)任一接地、而且正偏置电压被施加至深阱区120时,在第一阱区130a与深阱区120之间的PN结可以被反向偏

置,以将第一阱区130a与其它阱区(亦即,第二、第三及第四阱区130b、130c及130d)电隔离开。换言之,当正电压被施加至深阱区120,而且接地电压被施加至特定的阱区时,在特定的阱区中执行的电操作不会影响到其它阱区。即使相同的偏置电压被施加至第一阱区130a和深阱区120两者,第一阱区130a仍然可以与第二、第三及第四阱区130b、130c及130d电隔离开,因为内建的电位存在于第一阱区130a与深阱区120之间的PN结中。

[0063] 图4是沿着图1的线Ⅲ-Ⅲ'所取的横截面图。图4描绘了与分别被设置在图1中的第一列与第一至第四行的交叉点的单位单元C11、C21、C31及C41相对应的晶体管T11、T21、T31及T41的沟道区的横截面图。沿着第二、第三及第四列所取的横截面图的每一个可以与在图4中描绘的横截面图实质相同的。在图1、2、3及4中,相同的附图标记表示相同的元件。

[0064] 参照图1及4,被掺杂P型杂质的第一至第四阱区130a、130b、130c及130d可以如参考图3所述的,依序地排列在N型深阱区120的上部区域中,以在第二方向上彼此间隔开。位于第一行与第一列的交叉点的第一沟道区151a可以被设置在第一阱区130a的与第一反熔丝绝缘层161和第一反熔丝栅极171重叠的上部区域中。位于第二行与第一列的交叉点的第二沟道区151b可以被设置在第二阱区130b的与第一反熔丝绝缘层161和第一反熔丝栅极171重叠的上部区域中。位于第三行与第一列的交叉点的第三沟道区151c可以被设置在第三阱区130c的与第一反熔丝绝缘层161和第一反熔丝栅极171重叠的上部区域中。位于第四行与第一列的交叉点的第四沟道区151d可以被设置在第四阱区130d的与第一反熔丝绝缘层161和第一反熔丝栅极171重叠的上部区域中。当第一至第四阱区130a、130b、130c及130d接地、而且大于阈值电压的正栅极电压被施加至第一反熔丝栅极171时,反转沟道(inversion channel)可以被形成在第一至第四沟道区151a、151b、151c及151d中,以在相邻的源极/漏极区之间、或是在源极/漏极区与漏极区之间提供导电的路径。

[0065] 图5是描绘在图2中所示的横截面图的等效电路图。尽管图5只有描绘了排列在第一行的单位单元C11、C12、C13及C14的等效电路图,但是对应于沿着其它行(亦即,第二、第三及第四行)所取的横截面图的等效电路图的每一个亦可以与在图5中所示的等效电路图实质相同的。

[0066] 参照图1、2及5,在第一行的单位单元C11可以对应于具有半MOS晶体管结构的晶体管T11,并且排列在第一行的其余的单位单元C12、C13及C14可以对应于晶体管T12、T13及T14,其分别具有完整的MOS晶体管结构。换言之,反熔丝式OTP存储器单元阵列100并不包括任何用于在被排列于第一行的单位单元C11、C12、C13及C14中选择特定的单位单元的选择晶体管。晶体管T11、T12、T13及T14可以依序地串联连接。换言之,位于第一行与第一列的交叉点的晶体管T12的源极端子ST12;位于第一行与第二列的交叉点的晶体管T12的源极端子ST12;位于第一行与第二列的交叉点的晶体管T12的漏极端子DT12可以电连接至位于第一行与第三列的交叉点的晶体管T13的源极端子ST13;并且位于第一行与第三列的交叉点的晶体管T13的源极端子ST13;并且位于第一行与第三列的交叉点的晶体管T14的源极端子ST11。位于第一行与第一列的交叉点的晶体管T11的源极端子ST11可以电连接至位于第一行与第二列的交叉点的晶体管T14的源极端子ST11可以是电浮置的,并且位于第一行与第四列的交叉点的晶体管T14的漏极端子DT14可以电连接至第一位线BL1。

[0067] 位于第一行与第一列的交叉点的晶体管T11的栅极端子GT11可以电连接至第一字线WL1。位于第一行与第二列的交叉点的晶体管T12的栅极端子GT12可以电连接至第二字线

WL2。位于第一行与第三列的交叉点的晶体管T13的栅极端子GT13可以电连接至第三字线WL3。位于第一行与第四列的交叉点的晶体管T14的栅极端子GT14可以电连接至第四字线WL4。晶体管T11的漏极端子DT11和晶体管T12的源极端子ST12可以电连接至位于第一行与第一列的交叉点的第一二极管D11的阴极;并且晶体管T12的漏极端子DT12和晶体管T13的源极端子ST13可以电连接至位于第一行与第二列的交叉点的第一二极管D12的阴极。类似地,晶体管T13的漏极端子DT13和晶体管T14的源极端子ST14可以电连接至位于第一行与第三列的交叉点的第一二极管D13的阴极;并且晶体管T14的漏极端子DT14可以电连接至位于第一行与第三列的交叉点的第一二极管D13的阴极;并且晶体管T14的漏极端子DT14可以电连接至位于第一行与第二列的交叉点的第一二极管D13的阴极。第一二极管D11、D12、D13及D14的阳极可以电连接至第一件偏置线PWL1。第一二极管D11、D12、D13及D14的阳极亦可以电连接至深阱二极管D10的阳极。深阱二极管D10阳极可以电连接至深阱偏置线NWL。

[0068] 构成位于第一行与第一列的交叉点的单位单元C11的晶体管T11的栅极端子GT11和漏极端子DT11可以分别对应于参考图1及2所述的第一反熔丝栅极171和第一源极/漏极区141a。没有对应于晶体管T11的浮置的源极端子ST11的扩散区可以存在于衬底110中。构成位于第一行与第二列的交叉点的单位单元C12的晶体管T12的栅极端子GT12、源极端子ST12和漏极端子DT12可以分别对应于第二反熔丝栅极172、第一源极/漏极区141a和第一源极/漏极区142a。第一源极/漏极区141a可以用作晶体管T11的漏极端子DT11和晶体管T12的源极端子ST12。构成位于第一行与第三列的交叉点的单位单元C13的晶体管T13的栅极端子GT13、源极端子ST13和漏极端子DT13可以分别对应于第三反熔丝栅极173、第一源极/漏极区142a和第一源极/漏极区143a。第一源极/漏极区142a可以用作晶体管T12的漏极端子DT12和晶体管T13的源极端子ST13。构成位于第一行与第四列的交叉点的单位单元C14的晶体管T14的栅极端子GT14、源极端子ST14和漏极端子DT14可以分别对应于第四反熔丝栅极174、第一源极/漏极区143a和第一漏极区144a。第一源极/漏极区143a可以用作晶体管T13的漏极端子DT13和晶体管T14的源极端子ST14。

[0069] 第一二极管D11可以对应于由第一阱区130a和第一源极/漏极区141a所构成的寄生二极管组件,并且第一二极管D12可以对应于由第一阱区130a和第一源极/漏极区142a所构成的寄生二极管组件。再者,第一二极管D13可以对应于由第一阱区130a和第一源极/漏极区143a所构成的寄生二极管组件,并且第一二极管D14可以对应于由第一阱区130a和第一漏极区144a所构成的寄生二极管组件。此外,深阱二极管DN可以对应于由第一阱区130a和深阱区120所构成的寄生二极管组件。

[0070] 第一阱区130a可以用作排列在第一行的晶体管T11、T12、T13及T14的共用体 (bulk)区。因此,晶体管T11的第一沟道区151a可以通过线135-1a来电连接至第一阱偏置线 PWL1,并且晶体管T12的第一沟道区152a可以通过线135-2a来电连接至第一阱偏置线PWL1。 类似地,晶体管T13的第一沟道区153a可以通过线135-3a来电连接至第一阱偏置线PWL1,并且晶体管T14的第一沟道区154a可以通过线135-4a来电连接至第一阱偏置线PWL1。

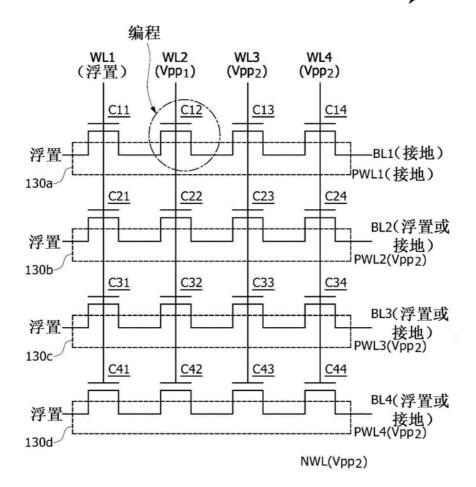

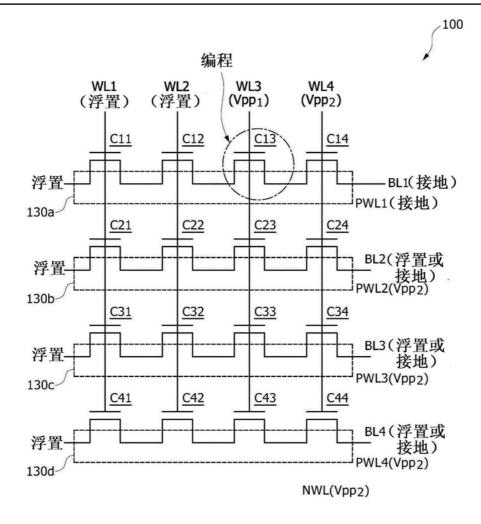

[0071] 图6是描绘在图1中所示的反熔丝式0TP存储器单元阵列100的等效电路图。图6的 反熔丝式0TP存储器单元阵列100可以对应于多个行的等效电路图,其中每一行都具有与参考图5所述的第一行实质相同的配置。图6描绘了无图5中所示的寄生二极管D11、D12、D13、D14及DN的反熔丝式0TP存储器单元阵列100的等效电路图。此外,图6将阱区130a、130b、130c及130d描绘为通过虚线绘制的矩形方块。

[0072] 参照图6,多个字线WL1、WL2、WL3及WL4可以沿第一方向排列,并且多个阱区130a、130b、130c及130d可以沿第二方向排列。如参考图1所述的,第一至第四阱区130a、130b、130c及130d可以分别电连接至第一至第四阱偏置线PWL1、PWL2、PWL3及PWL4。因而,多个字线WL1、WL2、WL3及WL4可以被设置为与列平行,并且多个阱偏置线PWL1、PWL2、PWL3及PWL4可以被设置为与行平行。字线WL1、WL2、WL3及WL4和阱偏置线PWL1、PWL2、PWL3及PWL4的此种配置仅仅是许多适合的布局图中的一个例子而已。因而,在某些实施例中,多个字线WL1、WL2、WL3及WL4可以被设置为与行平行,并且多个阱偏置线PWL1、PWL2、PWL3及PWL4可以被设置为与列平行。

[0073] 排列在第一行的单位单元C11、C12、C13及C14可以串联连接在第一方向(亦即,行方向)上,并且可以彼此共享第一阱偏置线PWL1。被排列于第一行的单位单元C11、C12、C13及C14之中的单位单元C11的源极端子可以浮置,并且单位单元C14的漏极端子可以电连接至第一位线BL1。排列在第二行的单位单元C21、C22、C23及C24亦可以是串联连接在第一方向上,并且可以彼此共享第二阱偏置线PWL2。被排列于第二行的单位单元C21、C22、C23及C24之中的单位单元C21的源极端子可以浮置,并且单位单元C24的漏极端子可以电连接至第二位线BL2。排列在第三行的单位单元C31、C32、C33及C34亦可以是串联连接在第一方向上,并且可以彼此共享第三阱偏置线PWL3。被排列于第三行的单位单元C31、C32、C33及C34之中的单位单元C31的源极端子可以浮置,并且单位单元C34的漏极端子可以电连接至第三位线BL3。排列在第四行的单位单元C41、C42、C43及C44亦可以是串联连接在第一方向上,并且可以彼此共享第四阱偏置线PWL4。被排列于第四行的单位单元C41、C42、C43及C44之中的单位单元C41的源极端子可以浮置,并且单位单元C44的漏极端子可以电连接至第四位线BL4。

[0074] 排列在第一列的单位单元C11、C21、C31及C41可以彼此共享第一字线WL1,并且排列在第二列的单位单元C12、C22、C32及C42可以彼此共享第二字线WL2。类似地,排列在第三列的单位单元C13、C23、C33及C43可以彼此共享第三字线WL3,并且排列在第四列的单位单元C14、C24、C34及C44可以彼此共享第四字线WL4。

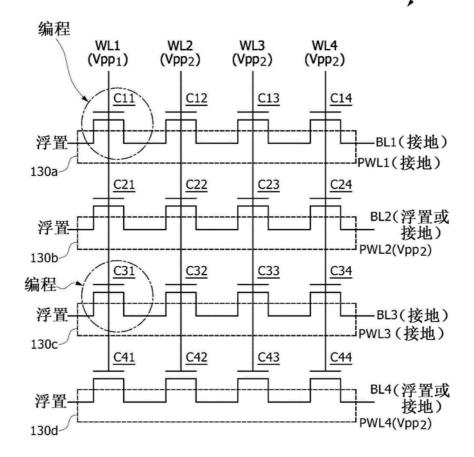

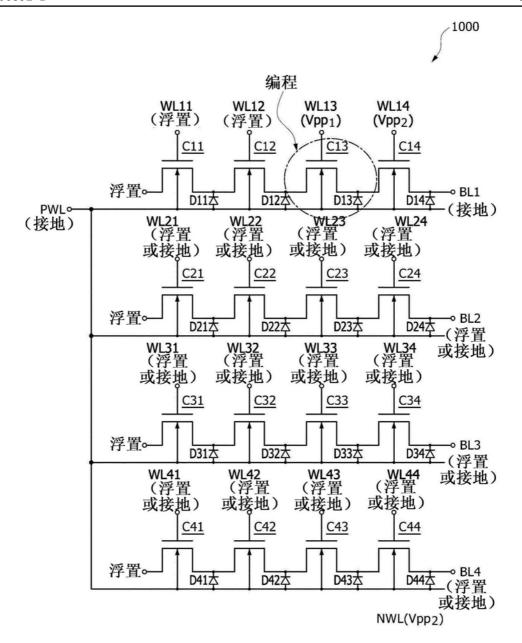

[0075] 图7至20是描绘在图6中所示的反熔丝式0TP存储器单元阵列100的编程操作的示意图。在图7至20中,与在图1至6中所用的相同的附图标记表示相同的元件。

[0076] 反熔丝式0TP存储器单元阵列100的编程操作可以包括依序地编程排列在所述行的任一行的多个单位单元。例如,反熔丝式0TP存储器单元阵列100的编程操作可以包括依序地编程排列在第一行的多个单位单元C11、C12、C13及C14。换言之,根据反熔丝式0TP存储器单元阵列100的编程操作,位于第一行与第一列的交叉点的单位单元C11可以被编程,并且位于第一行与第二列的交叉点的单位单元C12接着可以被编程。随后,位于第一行与第三列的交叉点的单位单元C13可以被编程,并且位于第一行与第四列的交叉点的单位单元C14接着可以被编程。此外,在被排列于第一行的所有的单位单元C11、C12、C13及C14都依序地被编程之后,未编程行(例如是第二行)中的任一行可以被选中,因而排列在第二行的单位单元C21、C22、C23及C24可以利用与在编程单位单元C11、C12、C13及C14中所用的相同的方法来依序地被编程。再者,在被排列于第二行的所有的单位单元C21、C22、C23及C24都依序地被编程之后,未编程行(例如是第三行)中的任一行可以被选中,因而排列在第三行的单位单元C31、C32、C33及C34可以利用与在编程单位单元C11、C12、C13及C14中所用的相同的位单元C31、C32、C33及C34可以利用与在编程单位单元C11、C12、C13及C14中所用的相同的

方法来依序地被编程。最后,在被排列于第三行的所有的单位单元C31、C32、C33及C34都依 序地被编程之后,例如是第四行的其余的未编程行可以被选中,因而排列在第四行的单位 单元C41、C42、C43及C44可以利用与在编程单位单元C11、C12、C13及C14中所用的相同的方 法来依序地被编程。在某些实施例中,在编程操作期间可以用随机顺序来选择行。在下文 中,用于依序地编程排列在第一行的单位单元C11、C12、C13及C14的编程操作将会被描述。 首先,参照图7,被排列于第一行的单位单元C11、C12、C13及C14之中的单位单元 C11可以被编程。为了选择性地编程单位单元C11,第一编程电压Vpp1可以被施加至连接到 选中的单位单元C11的第一字线WL1。第一编程电压Vpp1可以被设定以具有能够使得选中的 单位单元C11的反熔丝绝缘层(图2的161)破裂以形成电阻性路径的电压电平。在某些实施 例中,第一编程电压Vpp1可以具有约10V到约20V的电压电平。此外,第二编程电压Vpp2可以 被施加至分别连接到未选中的单位单元C12、C13及C14的第二、第三及第四字线WL2、WL3及 WL4。第二编程电压Vpp2可以被设定以具有大于构成未选中的单位单元C12、C13及C14的晶 体管的阈值电压而且能够防止未选中的单位单元C12、C13及C14的反熔丝绝缘层(图2的 162、163及164) 破裂的电压电平。此外,在第一与第二编程电压Vpp1与Vpp2之间的电压差可 以被设定以防止未选中的单位单元C12、C13及C14的反熔丝绝缘层(图2的162、163和164)破 裂。在某些实施例中,第二编程电压Vpp2可以具有约2V到约5V的电压电平。再者,在排列在 第一行的单位单元C11、C12、C13及C14被编程的同时,第一位线BL1和第一阱偏置线PWL1可 以是接地的。再者,第二编程电压Vpp2亦可以被施加至深阱偏置线NWL、第二阱偏置线PWL2、 第三阱偏置线PWL3、以及第四阱偏置线PWL4。其它的位线,亦即第二、第三及第四位线BL2、 BL3及BL4可以是浮置或接地的。

[0078] 图8描绘了选中的单位单元C11在以上的偏置条件下的编程机制。

[0079] 如在图8中所绘,因为大于未选中的单位单元C12、C13及C14的阈值电压的第二编程电压Vpp2被施加至所有连接到未选中的单位单元C12、C13及C14的第二、第三及第四字线WL2、WL3及WL4,因此构成未选中的单位单元C12、C13及C14的晶体管T12、T13及T14可以被导通。因此,反转沟道CH2、CH3及CH4可以分别被形成在晶体管T12、T13及T14的第一沟道区152a、153a及154a中。在以上的偏置条件下,反转沟道亦可以被形成在构成选中的单位单元C11的晶体管T11的第一沟道区151a中。然而,被形成在晶体管T11的第一沟道区151a中的反转沟道不会影响到选中的单位单元C11的编程操作。因此,如在图8中所绘,在晶体管T11的第一沟道区151a中并未绘出反转沟道。

[0080] 被施加至第一位线BL1的接地电压通过第一漏极区144a、反转沟道CH4、第一源极/漏极区143a、反转沟道CH3、第一源极/漏极区142a、反转沟道CH2、以及第一源极/漏极区141a而可以最终被传送至在第一反熔丝栅极171之下的反转沟道。因此,在第一编程电压Vpp1与接地电压之间的电压差(亦即第一编程电压Vpp1)可以被施加在第一反熔丝栅极171与第一源极/漏极区141a之间、以及在第一反熔丝栅极171与第一反熔丝栅极171与第一反熔丝栅极171与第一反熔丝栅极171与第一反熔丝栅极171与第一反熔丝栅极171与第一反熔丝栅极171与第一反熔丝栅极171与第一反熔丝栅极171与第一反熔丝栅极171与第一反熔丝栅极171与第一反熔丝栅极171与第一反熔丝栅极171与第一反熔丝栅极171与第一反熔丝栅极171与第一反熔丝栅极171与第一反熔丝栅极171与第一反熔丝栅极171与第一反熔丝栅极171与第一反熔丝栅极171与第一反熔丝栅极171与第一反熔丝栅极171与第一反熔丝栅极171与第一反熔丝地极171与第一反熔丝地极171与第一级上,在第一反熔丝栅极171与第一级增加速至141。因此,在第一反熔丝地极171与第一级增加速至141。因此,在第一反熔丝地缘层161可以因第一编程电压Vpp1而破积,以形成电流流过的电阻性路径211,即如通过图8的部分,A1,所指出的。因此,选中的单位单元C11可以被编程。

[0081] 在与选中的单位单元C11共享第一阱偏置线PWL1的未选中的单位单元C12中,第二编程电压Vpp2可以被施加在第二反熔丝栅极172与第一源极/漏极区142a之间。由于第二编程电压Vpp2是具有不足以使得第二反熔丝绝缘层162破裂的电压电平,因此没有电阻性路径被形成在介于第二反熔丝栅极172与第一源极/漏极区142a之间的第二反熔丝绝缘层162中。未选中的单位单元C12的此种编程禁止机制可以等同地被应用到与选中的单位单元C11共享第一阱偏置线PWL1的其余的未选中的单位单元C13及C14。再者,未选中的单位单元C12的编程禁止机制亦可以被应用到与未选中的单位单元C12共享第二字线WL2的其余的未选中的单位单元C22、C32及C42、与未选中的单位单元C13共享第三字线WL3的其余的未选中的单位单元C23、C33及C43、以及与未选中的单位单元C14共享第四字线WL4的其余的未选中的单位单元C24、C34及C44。

[0082] 再次参照图7,与选中的单位单元C11共享第一字线WL1的未选中的单位单元C21、C31及C41不会被编程,因为没有反转沟道被形成在构成未选中的单位单元C22、C23、C24、C32、C33、C34、C42、C43及C44的晶体管中。

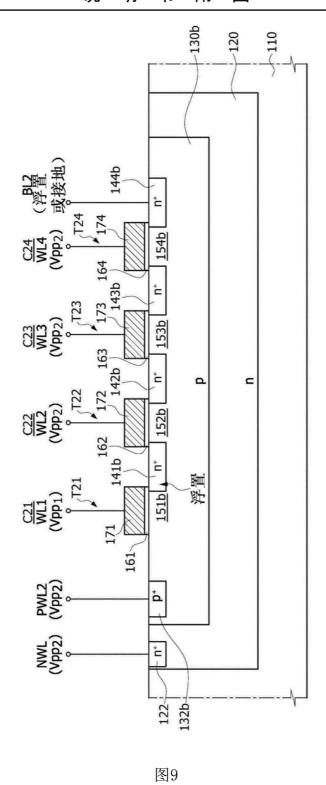

[0083] 图9描绘了在以上的偏置条件下的未选中的单位单元的编程禁止机制。尤其,图9描绘了沿着在以上的偏置条件下的第二行所取的横截面图。

[0084] 为了编程未选中的单位单元C21,在被施加至第一反熔丝栅极171的第一编程电压 Vpp1与在第二源极/漏极区141b之处感生的电压之间的电压差必须是大到足以使得第一反熔丝绝缘层161破裂。然而,由于第二编程电压Vpp2可以被施加至第二、第三反熔丝栅极与第四反熔丝栅极172、173及174和第二阱区130b,因此在第二阱区130b与反熔丝栅极172、173及174之间可以没有电压差。因而,没有反转沟道被形成在被排列于第二行的晶体管T22、T23及T24的第二沟道区152b、153b及154b的每一个中。因此,即使接地电压被施加至第二位线BL2,接地电压也无法被传送至第二源极/漏极区141b。因此,第二源极/漏极区141b可以是浮置的。即使第二位线BL2是浮置的,第二源极/漏极区141b仍然可以是浮置的,而不论被施加至第二、第三反熔丝栅极与第四反熔丝栅极172、173及174的电压电平为何。

[0085] 此外,如上所述,在被施加至第一反熔丝栅极171的第一编程电压Vpp1与被施加至第二阱区130b的第二编程电压Vpp2之间的电压差可以具有不足以使得反熔丝绝缘层161、162、163及164破裂的电压电平。因而,在以上的偏置条件下,没有电阻性路径被形成在未选中的单位单元C21、C31及C41的第一反熔丝绝缘层161中。因此,未选中的单位单元C21、C31及C41不会被编程。

[0086] 参照图10,被排列于第一行的单位单元C11、C12、C13及C14之中的单位单元C11被编程之后,用于选择性地编程位于第二列的单位单元C12的编程操作可以被执行。明确地说,在一种其中连接至已编程单位单元C11的第一字线WL1是浮置的状态中,第一编程电压Vpp1可以被施加至连接到选中的单位单元C12的第二字线WL2,并且第二编程电压Vpp2可以被施加至连接到未编程单位单元之中的未选中的单位单元C13及C14的第三及第四字线WL3及WL4。此外,接地电压可以被施加至连接到选中的单位单元C12的第一位线BL1和第一阱偏置线PWL1,并且其余的位线BL2、BL3及BL4可以是浮置或接地的。再者,第二编程电压Vpp2亦可以被施加至其余的阱偏置线,例如是第二、第三及第四阱偏置线PWL2、PWL3及PWL4。第二编程电压Vpp2亦可以被施加至深阱偏置线NWL。

[0087] 图11是描绘在以上的偏置条件下的选中的单位单元C12的编程机制。

[0088] 如在图11中所绘,由于连接至已编程单位单元C11的第一字线WL1是浮置的,因此不论单位单元C11是否具有已编程状态,用于编程选中的单位单元C12的编程操作都不会影响到单位单元C11。因为大于未选中的单位单元C13及C14的阈值电压的第二编程电压Vpp2被施加至连接到未选中的单位单元C13及C14的第三及第四字线WL3及WL4,因此构成未选中的单位单元C13及C14的晶体管T13及T14可以被导通。因此,反转沟道CH3及CH4可以分别被形成在晶体管T13及T14的第一沟道区153a及154a中。反转沟道CH2亦可以被形成在构成选中的单位单元C12的晶体管T12的第一沟道区152a中。

[0089] 被施加至第一位线BL1的接地电压可以通过第一漏极区144a、反转沟道CH4、第一源极/漏极区143a、反转沟道CH3、以及第一源极/漏极区142a而被传送至第一源极/漏极区141a。因此,第一编程电压Vpp1与接地电压之间的电压差(亦即,第一编程电压Vpp1)可以被施加在第二反熔丝栅极172与第一源极/漏极区142a之间。因而,在第二反熔丝栅极172与第一源极/漏极区142a之间的第一反熔丝绝缘层162可以因第一编程电压Vpp1而破裂,以形成电流流过的电阻性路径212,即如通过图11的部分'A2'所指出的。因此,选中的单位单元C12可以被编程。

[0090] 在与选中的单位单元C12共享第一阱偏置线PWL1的未选中的单位单元C13中,第二编程电压Vpp2可以被施加在第三反熔丝栅极173与第一源极/漏极区143a之间。由于第二编程电压Vpp2具有不足以使得第三反熔丝绝缘层163破裂的电压电平,因此没有电阻性路径被形成在介于第三反熔丝栅极173与第一源极/漏极区143a之间的第三反熔丝绝缘层163中。未选中的单位单元C13的此种编程禁止机制可以等同地被应用到与选中的单位单元C12共享第一阱偏置线PWL1的其余的未选中的单位单元C14。再者,未选中的单位单元C13的编程禁止机制亦可以被应用到与未选中的单位单元C13共享第三字线WL3的其余的未选中的单位单元C23、C33及C43、以及与未选中的单位单元C14共享第四字线WL4的其余的未选中的单位单元C24、C34及C44。

[0091] 再次参照图10,与已编程单位单元C11共享第一字线WL1的未选中的单位单元C21、C31及C41不会受到选中的单位单元C12的编程操作的影响,因为第一字线WL1是浮置的。此外,与选中的单位单元C12共享第二字线WL2的未选中的单位单元C22、C32及C42不会被编程,因为没有反转沟道被形成在构成未选中的单位单元C23、C24、C33、C34、C43及C44的晶体管的每一个中。

[0092] 图12描绘了在以上的偏置条件下的未选中的单位单元的编程禁止机制。尤其,图 12描绘了沿着在以上的偏置条件下的第二行所取的横截面图。

[0093] 为了编程未选中的单位单元C22,在被施加至第二反熔丝栅极172的第一编程电压 Vpp1与在第二源极/漏极区142b之处感生的电压之间的电压差必须是大到足以使得第二反熔丝绝缘层162破裂。然而,由于第二编程电压Vpp2可以被施加至第三反熔丝栅极与第四反熔丝栅极173与174和第二阱区130b,因此第二阱区130b与反熔丝栅极173与174之间的电压差可以是零伏特。因而,没有反转沟道被形成在被排列于第二行的晶体管T23及T24的第二沟道区153b及154b的每一个中。因此,即使接地电压被施加至第二位线BL2,接地电压也无法被传送至第二源极/漏极区142b。因此,由于第二源极/漏极区142b是浮置的,因此未选中的单位单元C22的第二反熔丝绝缘层162不会破裂。因此,没有电阻性路径被形成在未选中的单位单元C22的第二反熔丝绝缘层162中。当第二位线BL2是浮置时,第二源极/漏极区

142b仍然可以是浮置的,而不论被施加至第三反熔丝栅极与第四反熔丝栅极173及174的电压电平为何。

[0094] 同时,如上所述,被施加至第二反熔丝栅极172的第一编程电压Vpp1与被施加至第二阱区130b的第二编程电压Vpp2之间的电压差可以具有不足以使得反熔丝绝缘层161、162、163及164破裂的电压电平。因而,在以上的偏置条件下,没有电阻性路径被形成在未选中的单位单元C22、C32及C42的第二反熔丝绝缘层162中。因此,未选中的单位单元C22、C32及C42不会被编程。

[0095] 参照图13,被排列于第一行的单位单元C11、C12、C13及C14之中的单位单元C11及C12被编程之后,用于选择性地编程位于第三列的单位单元C13的编程操作可以被执行。明确地说,在一种其中连接至已编程单位单元C11及C12的第一及第二字线WL1及WL2是浮置的状态中,第一编程电压Vpp1可以被施加至连接到选中的单位单元C13的第三字线WL3,并且第二编程电压Vpp2可以被施加至连接到未编程单位单元之中的未选中的单位单元C14的第四字线WL4。此外,接地电压可以被施加至连接到选中的单位单元C13的第一位线BL1和第一阱偏置线PWL1,并且其余的位线BL2、BL3及BL4可以是浮置或接地的。再者,第二编程电压Vpp2亦可以被施加至其余的阱偏置线,例如第二、第三及第四阱偏置线PWL2、PWL3及PWL4。第二编程电压Vpp2亦可以被施加至深阱偏置线NWL。

[0096] 图14描绘了在以上的偏置条件下的选中的单位单元C13的编程机制。

[0097] 如在图14中所绘,由于连接至已编程单位单元C11及C12的第一及第二字线WL1及WL2是浮置的,因此不论单位单元C11及C12是否具有已编程状态,用于编程选中的单位单元C13的编程操作都不会影响到单位单元C11及C12。因为大于未选中的单位单元C14的阈值电压的第二编程电压Vpp2被施加至第四字线WL4,并且接地电压被施加至第一阱偏置线PWL1,因此构成未选中的单位单元C14的晶体管T14可以被导通。因而,反转沟道CH4可以被形成在晶体管T14的第一沟道区154a中。在以上的偏置条件下,反转沟道(未显示)亦可以被形成在构成选中的单位单元C13的晶体管T13的第一沟道区153a中。然而,被形成在晶体管T13的第一沟道区153a中的反转沟道不会影响到选中的单位单元C13的编程操作。

[0098] 被施加至第一位线BL1的接地电压可以通过第一漏极区144a和反转沟道CH4而被传送至第一源极/漏极区143a。因此,第一编程电压Vpp1与接地电压之间的电压差(亦即,第一编程电压Vpp1)可以被施加在第三反熔丝栅极173与第一源极/漏极区143a之间。因而,在第三反熔丝栅极173与第一源极/漏极区143a之间的第三反熔丝绝缘层163可以因第一编程电压Vpp1而破裂,以形成电流流过的电阻性路径213,即如通过图14的部分,A3,所指出的。因此,选中的单位单元C13可以被编程。

[0099] 在与选中的单位单元C13共享第一阱偏置线PWL1的未选中的单位单元C14中,第二编程电压Vpp2可以被施加在第四反熔丝栅极174与第一漏极区144a之间。由于第二编程电压Vpp2具有不足以使得第四反熔丝绝缘层164破裂的电压电平,因此没有电阻性路径被形成在介于第四反熔丝栅极174与第一漏极区144a之间的第四反熔丝绝缘层164中。未选中的单位单元C14的此种编程禁止机制可以等同地被应用到与未选中的单位单元C14共享第四字线WL4的其余的未选中的单位单元C24、C34及C44。

[0100] 再次参照图13,与已编程单位单元C11共享第一字线WL1的未选中的单位单元C21、C31及C41以及与已编程单位单元C12共享第二字线WL2的未选中的单位单元C22、C32及C42

不会受到选中的单位单元C13的编程操作的影响,因为第一及第二字线WL1及WL2是浮置的。此外,与选中的单位单元C13共享第三字线WL3的未选中的单位单元C23、C33及C43不会被编程,因为没有反转沟道被形成在构成未选中的单位单元C24、C34及C44的晶体管的每一个中。

[0101] 图15描绘了在以上的偏置条件下的未选中的单位单元的编程禁止机制。尤其,图 15描绘了沿着在以上的偏置条件下的第二行所取的横截面图。

[0102] 为了编程未选中的单位单元C23,在被施加至第三反熔丝栅极173的第一编程电压 Vpp1与在第二源极/漏极区143b之处感生的电压之间的电压差必须是大到足以使得第三反熔丝绝缘层163破裂。然而,由于第二编程电压Vpp2可以被施加至第四反熔丝栅极174和第二阱区130b,因此第二阱区130b与反熔丝栅极174之间的电压差可以实际是零伏特。因而,没有反转沟道被形成在被排列于第二行的晶体管T24的第二沟道区154b的每一个中。因此,即使接地电压被施加至第二位线BL2,接地电压也无法被传送至第二源极/漏极区143b。因此,由于第二源极/漏极区143b是浮置的,因而未选中的单位单元C23的第三反熔丝绝缘层163不会破裂。因此,没有电阻性路径被形成在未选中的单位单元C23的第三反熔丝绝缘层163中。在其中第二位线BL2是浮置的情形中,第二源极/漏极区143b仍然可以是浮置的,而不论被施加至第四反熔丝栅极174的电压电平为何。

[0103] 同时,如上所述,被施加至第三反熔丝栅极173的第一编程电压Vpp1与被施加至第二阱区130b的第二编程电压Vpp2之间的电压差可以具有不足以使得反熔丝绝缘层161、162、163及164破裂的电压电平。因而,在以上的偏置条件下,没有电阻性路径被形成在未选中的单位单元C23、C33及C43的第三反熔丝绝缘层163中。因此,未选中的单位单元C23、C33及C43不会被编程。

[0104] 参照图16,被排列于第一行的单位单元C11、C12、C13及C14之中的单位单元C11、C12及C13被编程之后,用于选择性地编程位于最后一列(亦即,第四列)的单位单元C14的编程操作可以被执行。明确地说,在一种其中连接至已编程单位单元C11、C12及C13的第一、第二及第三字线WL1、WL2及WL3可以是浮置的状态中,第一编程电压Vpp1可以被施加至连接到选中的单位单元C14的第四字线WL4。此外,接地电压可以被施加至连接到选中的单位单元C14的第一位线BL1和第一阱偏置线PWL1。在先前的用于编程单位单元C11、C12及C13的编程操作中,其余的位线,例如第二、第三及第四位线BL2、BL3及BL4是浮置或接地的。然而,为了选择性地编程排列在最后一列的单位单元(亦即,排列在第四列的单位单元C14),未选中的位线,例如第二、第三及第四位线BL2、BL3及BL4并非接地的,而是浮置的。再者,第二编程电压Vpp2可以被施加至其余的阱偏置线,例如第二、第三及第四阱偏置线PWL2、PWL3及PWL4。第二编程电压Vpp2亦可以被施加至深阱偏置线NWL。

[0105] 图17描绘了在以上的偏置条件下的选中的单位单元C14的编程机制。

[0106] 如在图17中所绘,由于连接至已编程单位单元C11、C12及C13的第一、第二及第三字线WL1、WL2及WL3是浮置的,因此不论单位单元C11、C12及C13是否具有已编程状态,用于编程选中的单位单元C14的编程操作都不会影响到单位单元C11、C12及C13。被施加至第一位线BL1的接地电压可以直接被传送至第一漏极区144a。因此,第一编程电压Vpp1与接地电压之间的电压差(亦即,第一编程电压Vpp1)可以被施加在第四反熔丝栅极174与第一漏极区144a之间的第四反熔丝绝缘层164

可以因第一编程电压Vpp1而破裂,以形成电流流过的电阻性路径214,即如通过图17的部分'A4'所指出的。因此,选中的单位单元C14可以被编程。

[0107] 再次参照图16,与已编程单位单元C11共享第一字线WL1的未选中的单位单元C21、C31及C41、与已编程单位单元C12共享第二字线WL2的未选中的单位单元C22、C32及C42、以及与已编程单位单元C13共享第三字线WL3的未选中的单位单元C23、C33及C43不会受到选中的单位单元C14的编程操作的影响。此可以是因为第一、第二及第三字线WL1、WL2及WL3是浮置的。此外,与选中的单位单元C14共享第四字线WL4的未选中的单位单元C24、C34及C44不会被编程,因为位线BL2、BL3及BL4是浮置的。

[0108] 图18描绘了在以上的偏置条件下的未选中的单位单元的编程禁止机制。尤其,图 18描绘了沿着在以上的偏置条件下的第二行所取的横截面图。

[0109] 为了编程未选中的单位单元C24,在被施加至第四反熔丝栅极174的第一编程电压 Vpp1与在第二漏极区144b之处感生的电压之间的电压差必须是大到足以使得第四反熔丝绝缘层164破裂。然而,即使第一编程电压Vpp1被施加至第四反熔丝栅极174,第二漏极区144b可以被浮置,以防止未选中的单位单元C24的第四反熔丝绝缘层164破裂。因此,没有电阻性路径被形成在未选中的单位单元C24的第四反熔丝绝缘层164中。未选中的单位单元C24的此种编程禁止机制可以等同地被应用到与选中的单位单元C14共享第四字线WL4的未选中的单位单元C34及C44。

[0110] 参照图19,被排列于第一行的所有的单位单元C11、C12、C13及C14都被编程之后,排列在第二行的单位单元C21、C22、C23及C24可以被编程。明确地说,用于选择性地编程被排列于第二行的单位单元C21、C22、C23及C24之中的单位单元C21的编程操作可以首先被执行,并且用于编程在第二列的单位单元C22和在第三列的单位单元C23的编程操作可以依序地被执行。最后,用于选择性地编程在最后一列(亦即,第四列)中的单位单元C24的编程操作可以被执行。这些编程操作可以与参考图7至18所描述的用于编程单位单元C11、C12、C13及C14的编程操作实质相同的。

[0111] 在某些实施例中,在用于编程排列在第二行的单位单元C21、C22、C23及C24的编程操作被执行之前,单位单元C11、C12、C13及C14中的至少一个可以具有未编程状态、或是所有的单位单元C11、C12、C13及C14可以具有已编程状态。当单位单元C11、C12、C13及C14的任一个具有未编程状态时,在单位单元C11、C12、C13及C14之中的未编程单位单元的反熔丝栅极和漏极区中的至少一个在被排列于第二行的单位单元C21、C22、C23及C24被编程时可以是浮置的、或是被施加至在第一行的未编程单位单元的反熔丝绝缘层的电压可以被设定为不足以使得反熔丝绝缘层破裂的电压电平。因此,当在第二行的单位单元C21、C22、C23及C24被编程时,在第一行的未编程单位单元不会被编程。换言之,即使排列在第一行的单位单元C11、C12、C13及C14中的至少一个具有未编程状态,在第一行的未编程单位单元也不会受到用于编程排列在第二行的单位单元C21、C22、C23及C24的编程操作的影响。

[0112] 图20描绘了:在用于选择性地编程位于第二行与第一列的交叉点的单位单元C21的编程操作期间,被施加至具有电阻性路径211的单位单元C11的偏置条件。

[0113] 如在图20中所绘,第一编程电压Vpp1可以被施加至单位单元C11和选中的单位单元C21所共享的第一字线WL1,并且第二编程电压Vpp2可以被施加至第二、第三及第四字线WL2、WL3及WL4。第一位线BL1可以是浮置或接地的,并且第二编程电压Vpp2亦可以被施加至

深阱偏置线NWL。

[0114] 单位单元C11可以具有带有电阻性路径211的已编程状态。因此,第一反熔丝栅极171可以通过电阻性路径211来电连接至第一源极/漏极区141a。在此情况下,当第一编程电压Vpp1被施加至单位单元C11和选中的单位单元C21所共享的第一字线WL1时,通过从第一编程电压Vpp1减去电阻性路径211的电压降所获得的电压可以被施加至第一源极/漏极区141a。由于电阻性路径211的电阻值可以小到可以忽略,因此可以假设第一编程电压Vpp1被施加至第一源极/漏极区141a。由于第二编程电压Vpp2被施加至第一阱偏置线PWL1,因此第二编程电压Vpp2亦可以被施加至第一阱区130a。因此,由被掺杂P型杂质的第一阱区130a和被掺杂N型杂质的第一源极/漏极区141a所构成的第一寄生二极管D11可以被反向偏置。因而,因为没有电流流过第一寄生二极管D11,因此第一寄生二极管D11可以在第一阱区130a与第一源极/漏极区141a之间提供开路。因此,已编程单位单元C11不会受到在第一阱区130a的电位波动的影响。

[0115] 第二编程电压Vpp2可以被施加至所有的第二至第四字线WL2、WL3及WL4和第一阱偏置线PWL1。因此,没有反转沟道可以被形成在构成排列在第一行的单位单元C12、C13及C14的晶体管T12、T13及T14的每一个中。因而,第一源极/漏极区142a及143a可以是电浮置的,而不论第一位线BL1的电压电平为何。因此,已编程单位单元C11不会受到被施加至第一位线BL1的电压的影响。

[0116] 第一编程电压Vpp1可以被施加至单位单元C11和选中的单位单元C21所共享的第一字线WL1,并且第二编程电压Vpp2可以被施加至相邻于第一字线WL1的第二字线WL2。因此,第一与第二编程电压Vpp1与Vpp2之间的电压差可以被施加在第二反熔丝栅极172与第一源极/漏极区141a之间。然而,第一与第二编程电压Vpp1与Vpp2之间的电压差可以不足以使得在图20的部分'C'中的第二反熔丝绝缘层162破裂。因此,由于没有电阻性路径被形成在部分'C'中的第二反熔丝绝缘层162中,因此第一源极/漏极区141a仍然可以是浮置的。

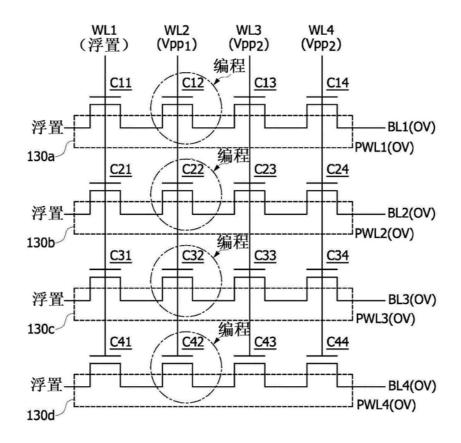

[0117] 图21至24是描绘在图6中所示的反熔丝式0TP存储器单元阵列100的其它编程操作的示意图。

[0118] 根据本实施例,编程操作可以以列为单位来被执行。换言之,用于选择性地编程被排列于第一列的单位单元C11、C21、C31及C41之中的至少一个目标单位单元的编程操作可以被执行,并且用于选择性地编程被排列于第二列的单位单元C12、C22、C32及C42之中的至少一个目标单位单元的编程操作接着可以被执行。接着,用于选择性地编程被排列于第三列的单位单元C13、C23、C33及C43之中的至少一个目标单位单元的编程操作可以被执行,并且用于选择性地编程被排列于最后一列(亦即,第四列)之中的单位单元C14、C24、C34及C44的至少一个目标单位单元的编程操作可以最后来被执行。因而,被排列于每个列的多个单位单元之中的至少一个目标单位单元可以同时被编程,以减少编程操作的数目。换言之,根据本实施例,反熔丝式0TP存储器单元阵列100可以通过反复地执行与反熔丝式0TP存储器单元阵列100的列的数目相同次数的编程操作来被编程。

[0119] 参照图21,一个其中在被排列于第一列的单位单元C11、C21、C31及C41之中的单位单元C11和单位单元C31同时被编程的例子将会首先被叙述。明确地说,第一编程电压Vpp1可以被施加至共同连接到选中的单位单元C11及C31两者的第一字线WL1,并且第二编程电压Vpp2可以被施加至其余的字线WL2、WL3及WL4。第一及第二编程电压Vpp1及Vpp2可以具有

与如参考图7至20所述的相同的电压电平。此外,接地电压可以分别被施加至连接到选中的单位单元C11及C31的第一位线BL1和第三位线BL3。分别连接至未选中的单位单元C21及C41的第二位线BL2和第四位线BL4可以是浮置或接地的。再者,接地电压可以被施加至分别连接到选中的单位单元C11及C31的第一阱偏置线PWL1和第三阱偏置线PWL3,并且第二编程电压Vpp2可以被施加至分别连接到未选中的单位单元C21及C41的第二阱偏置线PWL2和第四阱偏置线PWL4。尽管未显示在图21中,第二编程电压Vpp2亦可以被施加至深阱偏置线NWL。

[0120] 在以上的偏置条件下,选中的单位单元C11及C31可以同时被编程。换言之,电阻性路径可以被形成在选中的单位单元C11及C31的每一个的第一反熔丝绝缘层161中。选中的单位单元C11及C31可以通过与参考图8所述的相同的机制来被编程。通过与参考图9所述的相同的编程禁止机制,在被排列于第一列的单位单元C11、C21、C31及C41之中的单位单元C21及C41不会被编程。换言之,由于没有反转沟道可以被形成在构成与单位单元C21共享第二阱偏置线PWL2的未选中的单位单元C22、C23及C24的晶体管的每一个中,因此被施加至第二位线BL2的接地电压无法被传送至单位单元C21的源极/漏极区。因此,没有电阻性路径可以被形成在单位单元C21的第一反熔丝绝缘层中。类似地,由于没有反转沟道可以被形成在构成与单位单元C41共享第四阱偏置线PWL4的未选中的单位单元C42、C43及C44的晶体管的每一个中,因此被施加至第四位线BL4的接地电压无法被传送至单位单元C41的源极/漏极区。因此,没有电阻性路径可以被形成在单位单元C41的第一反熔丝绝缘层中。

[0121] 与选中的单位单元C11共享第一阱偏置线PWL1的未选中的单位单元C12、C13及C14不会被编程,因为横跨未选中的单位单元C12、C13及C14的反熔丝绝缘层所形成的电场是不足以在反熔丝绝缘层的每一个中形成电阻性路径。此种编程禁止机制亦可以相同地应用到与选中的单位单元C31共享第三阱偏置线PWL3的未选中的单位单元C32、C33及C34。

[0122] 参照图22,在被排列于第一列的单位单元的编程操作被执行之后,排列在第二列的单位单元的编程操作可以被执行。如在图22中所绘,为了选择性地编程排列在第二列的所有的单位单元C12、C22、C32及C42,在一种其中被设置在包括已编程单位单元的第一列的第一字线WL1是浮置的状态中,第一编程电压Vpp1可以被施加至设置在待被编程的第二列的第二字线WL2,并且第二编程电压Vpp2可以被施加至其余的字线WL3及WL4。此外,接地电压可以被施加至分别连接到选中的单位单元C12、C22、C32及C42的第一至第四位线BL1、BL2、BL3及BL4。再者,接地电压亦可以被施加至分别连接到选中的单位单元C12、C22、C32及C42的第一至第四阱偏置线PWL1、PWL2、PWL3及PWL4。尽管未显示在图22中,第二编程电压Vpp2亦可以被施加至深阱偏置线NWL。

[0123] 在以上的偏置条件下,选中的单位单元C12、C22、C32及C42可以同时被编程。换言之,电阻性路径可以被形成在选中的单位单元C12、C22、C32及C42的每一个的第二反熔丝绝缘层162中。选中的单位单元C12、C22、C32及C42可以通过与参考图11所述的相同的机制来被编程。排列在第一列的未选中的单位单元C11、C21、C31及C41不会受到编程选中的单位单元C12、C22、C32及C42的影响,因为第一字线WL1是浮置的。排列在第三及第四列的单位单元C13、C14、C23、C24、C33、C34、C43及C44不会被编程,因为如参考图11所述的,被施加至第三及第四字线WL3及WL4的第二编程电压Vpp2具有不足以使得被设置在第三及第四列的第三及第四反熔丝绝缘层破裂的电压电平。

[0124] 参照图23,在被排列于第一及第二列的单位单元的编程操作被执行之后,排列在

第三列的单位单元的编程操作可以被执行。如在图23中所绘,一个其中在被排列于第三列的单位单元C13、C23、C33及C43之中的单位单元C13、C23及C33同时被编程的例子将会被描述。明确地说,当第一及第二字线WL1及WL2是浮置时,第一编程电压Vpp1可以被施加至第三字线WL3,并且第二编程电压Vpp2可以被施加至其余的字线WL4。此外,接地电压可以被施加至分别连接到选中的单位单元C13、C23及C33的第一、第二及第三位线BL1、BL2及BL3。连接至单位单元C43的第四位线BL4可以是浮置或接地的。再者,接地电压可以被施加至分别连接到选中的单位单元C13、C23及C33的第一、第二及第三阱偏置线PWL1、PWL2及PWL3。第二编程电压Vpp2亦可以被施加至其余的阱偏置线,亦即第四阱偏置线PWL4。尽管未显示在图23中,第二编程电压Vpp2亦可以被施加至深阱偏置线NWL。

[0125] 在以上的偏置条件下,选中的单位单元C13、C23及C33可以同时被编程。换言之,电阻性路径可以被形成在选中的单位单元C13、C23及C33的每一个的第三反熔丝绝缘层163中。选中的单位单元C13、C23及C33可以通过与参考图14所述的相同的机制来被编程。排列在第一列的未选中的单位单元C11、C21、C31及C41不会受到用于编程选中的单位单元C13、C23及C33的编程操作的影响,因为第一字线WL1是浮置的。类似地,排列在第二列的未选中的单位单元C12、C22、C32及C42不会受到用于编程选中的单位单元C13、C23及C33的编程操作的影响,因为第二字线WL2是浮置的。排列在第四列的单位单元C14、C24、C34及C44不会被编程,因为如参考图14所述的,被施加至第四字线WL4的第二编程电压Vpp2具有电压电平是不足以使得被设置在第四列的第四反熔丝绝缘层破裂。通过与参考图15所述的相同的编程禁止机制,排列在第三列的单位单元C43不会被编程。

[0126] 参照图24,在被排列于第一、第二及第三列的单位单元的编程操作被执行之后,排列在最后一列(亦即,第四列)中的单位单元的编程操作可以被执行。如在图24中所绘,一个其中在被排列于第四列的单位单元C14、C24、C34及C44之中的单位单元C14及C44同时被编程的例子将会被描述。明确地说,在一种其中第一、第二及第三字线WL1、WL2及WL3可以是浮置的状态中,第一编程电压Vpp1可以被施加至第四字线WL4。此外,接地电压可以被施加至分别连接到选中的单位单元C14及C44的第一及第四位线BL1及BL4。其余的位线,亦即第二及第三位线BL2及BL3可以是浮置的。再者,接地电压可以被施加至分别连接到选中的单位单元C14及C44的第一及第四阱偏置线PWL1及PWL4,并且第二编程电压Vpp2可以被施加至其余的阱偏置线,亦即第二及第三阱偏置线PWL2及PWL3。尽管未显示在图24中,第二编程电压Vpp2亦可以被施加至深阱偏置线NWL。

[0127] 在以上的偏置条件下,选中的单位单元C14及C44可以同时被编程。换言之,电阻性路径可以被形成在选中的单位单元C14及C44的每一个的第四反熔丝绝缘层164中。选中的单位单元C14及C44可以通过与参考图17所述的相同的机制来被编程。排列在第一列的未选中的单位单元C11、C21、C31及C41不会受到用于编程选中的单位单元C14及C44的编程操作的影响,因为第一字线WL1是浮置的。排列在第二列的未选中的单位单元C12、C22、C32及C42不会受到编程选中的单位单元C14及C44的影响,因为第二字线WL2是浮置的。排列在第三列的未选中的单位单元C13、C23、C33及C43不会受到编程选中的单位单元C14及C44的影响,因为第三字线WL3是浮置的。通过与参考图18所述的相同的编程禁止机制,排列在第四列的单位单元C24及C34不会被编程。

[0128] 图25及27是描绘在图6中所示的反熔丝式0TP存储器单元阵列100的读取操作的示

意图。

[0129] 根据本实施例的读取操作可以以行为单位来执行。因此,储存在反熔丝式0TP存储器单元阵列100中的所有的数据可以通过将读取操作执行与行的数目相同的次数来被读出。为了选择性地读出储存在被排列于选中的行的单位单元中的数据,读取电压Vrd可以被施加至被设置在选中的行的阱偏置线。此外,所有的字线都可以是接地的,并且所有的位线都可以是浮置的。再者,被设置在除了选中的行之外的未选中的行的其余的阱偏置线可以是浮置的。

[0130] 图25描绘了一个其中排列在第二行的单位单元C21、C22、C23及C24的数据被读出的例子。

[0131] 参照图25,为了读出排列在第二行的单位单元C21、C22、C23及C24的数据,读取电压Vrd可以被施加至共同连接到单位单元C21、C22、C23及C24的第二阱偏置线PWL2。读取电压Vrd可以具有大于一个一般的PN二极管的导通电压的电压电平。在某些实施例中,读取电压Vrd可以是在约1V到约3V的范围内。其余的阱偏置线,亦即第一、第三及第四阱偏置线PWL1、PWL3及PWL4可以是浮置的。所有的字线WL1、WL2、WL3及WL4可以是接地的,并且所有的位线BL1、BL2、BL3及BL4可以是浮置的。尽管未显示在图25中,读取电压Vrd或是大于读取电压Vrd的电压可以被施加至深阱偏置线NWL。

[0132] 图26是描绘排列在第二行的单位单元C21、C22、C23及C24的横截面图。

[0133] 如在图26中所绘,在被排列于第二行的单位单元C21、C22、C23及C24之中的单位单元C21、C22及C24可以具有例如是已编程状态的第一状态,其分别具有电阻性路径221、222及224。相对地,在被排列于第二行的单位单元C21、C22、C23及C24之中的单位单元C23可以具有例如是擦除状态的第二状态,其不具有电阻性路径。位于第二行与第一列的交叉点的单位单元C21可以包括由第二阱区130b和第二源极/漏极区141b所构成的寄生PN二极管D21,并且位于第二行与第二列的交叉点的单位单元C22可以包括由第二阱区130b和第二源极/漏极区142b所构成的寄生PN二极管D22。此外,位于第二行与第三列的交叉点的单位单元C23可以包括由第二阱区130b和第二源极/漏极区143b所构成的寄生PN二极管D23,并且位于第二行与第四列的交叉点的单位单元C24可以包括由第二阱区130b和第二漏极区144b所构成的寄生PN二极管D24。

[0134] 读取电压Vrd可以通过第二阱偏置线PWL2而被施加至第二阱区130b。所有的寄生PN二极管D21、D22、D23及D24都可以被正向偏置,以具有导通的状态。即使寄生PN二极管D21、D22、D23及D24具有导通的状态,流过寄生PN二极管D21、D22、D23及D24的每一个的电流仍然可以是依据单位单元C21、C22、C23及C24的每一个是否已编程而定。明确地说,因为单位单元C21具有带有电阻性路径221的已编程状态,因此第二源极/漏极区141b可以通过电阻性路径221来电连接至第一字线WL1。若忽略在寄生PN二极管D21中的电压降,则读取电压Vrd可以被施加至第二源极/漏极区141b。因此,电流可以从第二阱偏置线PWL2,通过寄生PN二极管D21而流向接地的第一字线WL1。因此,当检测到流过第一字线WL1的电流时,连接至第一字线WL1的单位单元C21可以被识别为已编程。单位单元C21的此读取操作可以等同地被应用到其它具有已编程状态的选中的单位单元C22及C24。

[0135] 同时,因为单位单元C23具有不带有电阻性路径的擦除状态,因此第三字线WL3可以通过第三反熔丝绝缘层163而与第二源极/漏极区142b及143b电隔离或绝缘。因此,即使

寄生PN二极管D22及D23被正向偏置使得读取电压Vrd被施加至第二源极/漏极区142b及143b,也没有电流可以从第二阱偏置线PWL2流向接地的第三字线WL3,因为第三反熔丝绝缘层163用作为电阻障层。因而,当未检测到流过第三字线WL3的电流时,连接至第三字线WL3的单位单元C23可以被识别为擦除的。

[0136] 图27是描绘排列在第一行的单位单元C11、C12、C13及C14在用于读出排列在第二行的单位单元C21、C22、C23及C24的数据的读取操作期间的偏置条件的横截面图。

[0137] 排列在第一行的单位单元C11、C12、C13及C14可以与其上分别被执行读取操作的单位单元C21、C22、C23及C24共享第一、第二、第三及第四字线WL1、WL2、WL3及WL4。因此,当用于读出排列在第二行的单位单元C21、C22、C23及C24的数据的读取操作被执行时,电流不可以流过排列在第一行的单位单元C11、C12、C13及C14,以便于正确地读出排列在第二行的单位单元C21、C22、C23及C24的数据。

[0138] 当被排列于第一行的单位单元C11、C12、C13及C14之中的单位单元C11及C14具有擦除状态时,寄生PN二极管D11及D14不会被正向偏置,因为第一阱偏置线PWL1是浮置的。此外,因为在单位单元C11及C14的第一及第四反熔丝绝缘层161及164中没有电阻性路径,因此不论寄生PN二极管D11及D14的偏置条件为何,都没有电流会流过单位单元C11及C14。在单位单元C12及C13中的寄生PN二极管D12及D13不会被正向偏置,因为第一阱偏置线PWL1是浮置的。因此,即使单位单元C12及C13具有已编程状态,其中电阻性路径212被形成在第二字线WL2与第一源极/漏极区142a之间,并且电阻性路径213被形成在第三字线WL3与第一源极/漏极区143a之间,也没有电流会流过单位单元C12及C13。类似地,在用于读出排列在第二行的单位单元C21、C22、C23及C24的数据的读取操作期间,没有电流会流过排列在第三行的单位单元C31、C32、C33及C34和排列在第四行的单位单元C41、C42、C43及C44。换言之,当用于选择性地读出排列在第二行的单位单元C21、C22、C23及C24的数据的读取操作被执行时,排列在第一、第三及第四行的未选中的单位单元C11、C12、C13、C14、C31、C32、C33、C34、C41、C42、C43及C44不会影响到读取操作。

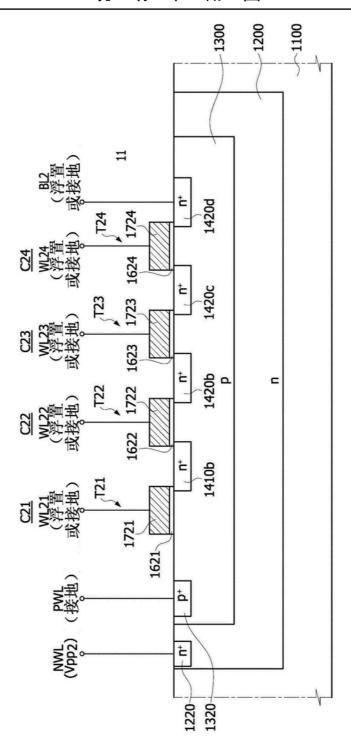

[0139] 图28是描绘根据另一实施例的一种反熔丝式OTP存储器单元阵列1000的布局图。

[0140] 参照图28,反熔丝式0TP存储器单元阵列1000可以包括阱区1300。阱区1300的侧壁和底表面可以被深阱区1200包围。深阱区1200可以具有第一导电类型,并且阱区1300可以具有一种与第一导电类型相反的第二导电类型。在某些实施例中,深阱区1200可以是N型,并且阱区1300可以是P型。深阱区1200可以通过执行利用掩模图案的离子注入工艺和扩散工艺来被形成。类似地,阱区亦可以通过执行利用掩模图案的离子注入工艺和扩散工艺来被形成。

[0141] 多个反熔丝栅极1711至1714、1721至1724、1731至1734和1741至1744可以被设置在阱区1200上。反熔丝栅极1711至1714、1721至1724、1731至1734以及1741至1744可以二维地排列,以彼此在第一方向和第二方向上间隔开。在某些实施例中,第一方向和第二方向可以是彼此垂直的。尽管未显示在图28中,反熔丝绝缘层可以被设置在每个反熔丝栅极与阱区1300之间。反熔丝栅极1711至1714、1721至1724、1731至1734以及1741至1744的每一个可以通过其中一行和其中一列来限定。换言之,反熔丝栅极1711至1714可以依序地位于第一行与第一至第四列的交叉点,并且反熔丝栅极1721至1724可以依序地位于第二行与第一至第四列的交叉点。此外,反熔丝栅极1731至1734可以依序地位于第三行与第一至第四列的

交叉点,并且反熔丝栅极1741至1744可以依序地位于第四行与第一至第四列的交叉点。因此,反熔丝栅极1711至1714、1721至1724、1731至1734和1741至1744可以被排列成具有'4×4'矩阵形式。

[0142] 第一源极/漏极区1410a、1420a及1430a可以依序地被设置在阱区1300的介于排列在第一行的反熔丝栅极1711至1714之间的部分中。第一漏极区1440a可以被设置在阱区1300的相邻于反熔丝栅极1714的一侧的一部分中,所述一侧与在反熔丝栅极1713与反熔丝栅极1714之间的第一源极/漏极区1430a相对。第二源极/漏极区1410b、1420b及1430b可以依序地被设置在阱区1300的介于排列在第二行的反熔丝栅极1721至1724之间的部分中。第二漏极区1440b可以被设置在阱区1300的相邻于反熔丝栅极1721至1724之间的部分中。第二漏极区1440b可以被设置在阱区1300的相邻于反熔丝栅极1724的与在反熔丝栅极1723与反熔丝栅极1724之间的第二源极/漏极区1430b相对的一侧的部分中。第三源极/漏极区1410c、1420c及1430c可以依序地被设置在阱区1300的介于排列在第三行的反熔丝栅极1734之间的部分中。第三漏极区1440c可以被设置在阱区1300的相邻于反熔丝栅极1734的与在反熔丝栅极1733与反熔丝栅极1734之间的第三源极/漏极区1430c相对的一侧的部分中。第四源极/漏极区1410d、1420d和1430d可以依序地被设置在阱区1300的介于排列在第四行的反熔丝栅极1741至1744之间的部分中。第四漏极区1440d可以被设置在阱区1300的相邻于反熔丝栅极1744的与在反熔丝栅极1743与反熔丝栅极1744之间的第四源极/漏极区1430d相对的一侧的部分中。

[0143] 因此,一对源极/漏极区可以被设置于排列在第二列的反熔丝栅极1712至1742、排列在第三列的反熔丝栅极1713至1743、以及排列在第四列的反熔丝栅极1714至1744的每一个反熔丝栅极的两侧。例如,第一源极/漏极区1410a可以被设置在位于第一行与第一列的交叉点的反熔丝栅极1711和位于第一行与第二列的交叉点的反熔丝栅极1712之间,并且第一源极/漏极区1420a可以被设置在位于第一行与第二列的交叉点的反熔丝栅极1712和位于第一行与第三列的交叉点的反熔丝栅极1713之间。再者,第一源极/漏极区1430a可以被设置在位于第一行与第三列的交叉点的反熔丝栅极1713和位于第一行与第四列的交叉点的反熔丝栅极1714之间。第一源极/漏极区1410a、1420a及1430a、第二源极/漏极区1410b、1420b及1430b、第三源极/漏极区1410c、1420c及1430c、第四源极/漏极区1410d、1420d及1430d、第一漏极区1440a、第二漏极区1440b、第三漏极区1440c以及第四漏极区1440d可以具有第一导电类型(亦即N型),其与阱区1300的第二导电类型(亦即P型)相反。

[0144] 根据反熔丝式0TP存储器单元阵列1000,单一单位单元可以被设置在反熔丝栅极1711至1714、1721至1724、1731至1734以及1741至1744被设置之处的交叉点的每一个中。因此,反熔丝式0TP存储器单元阵列1000可以包括十六个单位单元,其被排列成具有'4×4'矩阵形式。换言之,单位单元的每一个可以通过一行和一列来被限定。单位单元的每一个可以被配置以具有单MOS晶体管结构。例如,位于第一行与第二列的交叉点的单位单元C12可以是MOS晶体管,其是由阱区1300、第一源极/漏极区1410a及1420a、以及反熔丝栅极1712所构成的。在此情况下,第一源极/漏极区1410a可以用作单位单元C12的源极区,并且第一源极/漏极区1420a可以用作单位单元C12的漏极区。如上所述,反熔丝绝缘层(未显示)可以被设置在阱区1300与反熔丝栅极1712之间。除了第一列和最后一列(亦即,第四列)之外,排列在第二及第三列的其它单位单元的每一个亦可以具有与单位单元C12相同的结构。

[0145] 相对地,排列在第一列的单位单元的每一个可以具有半MOS晶体管结构。例如,位

于第一行与第一列的交叉点的单位单元C11可以是半MOS晶体管,其是由阱区1300、第一源极/漏极区1410a和反熔丝栅极1711所构成的。在此情况下,第一源极/漏极区1410a可以用作单位单元C11的漏极区,并且没有源极区被设置在单位单元C11中。排列在第一列的其余的单位单元的每一个亦可以具有与单位单元C11相同的结构。

[0146] 排列在最后一列(亦即,第四列)中的单位单元的每一个亦可以具有单MOS晶体管结构。例如,位于第一行与第四列的交叉点的单位单元C14可以是MOS晶体管,其是由阱区1300、第一源极/漏极区1430a、第一漏极1440a和反熔丝栅极1714所构成的。在此情况下,第一源极/漏极区1430a可以用作单位单元C14的源极区。排列在最后一列(亦即,第四列)中的其余的单位单元的每一个亦可以具有与单位单元C14相同的结构。

[0147] 深阱接触区1220可以被设置在深阱区1200中。深阱接触区1220可以与阱区1300间隔开。深阱接触区1220可以具有与深阱区1200相同的导电类型(例如是第一导电类型),并且可以具有杂质浓度高于深阱区1200的杂质浓度。深阱接触区1220可以通过深阱偏置线接触1230来电连接至深阱偏置线NWL。尽管图28描绘了一个其中单一深阱接触区1220被设置在深阱区1200中的例子,但是本公开内容并不限于此。例如,在某些实施例中,多个深阱接触区可以被设置在深阱区1200中。多个深阱接触区可以连接至深阱偏置线NWL。

[0148] 阱接触区1320可以被设置在阱区1300中。阱接触区1320可以具有与阱区1300相同的导电类型(例如是第二导电类型)。此外,阱接触区1320可以具有杂质浓度高于阱区1300的杂质浓度。尽管图28描绘了一个其中单一阱接触区1320被设置在阱区1300中的例子,但是本公开内容并不限于此。例如,在某些实施例中,多个阱接触区可以被设置在阱区1300中。

[0149] 反熔丝栅极1711至1714、1721至1724、1731至1734以及1741至1744可以分别通过字线接触1811至1814、1821至1824、1831至1834以及1841至1844来电连接至字线WL11至WL14、WL21至WL24、WL31至WL34以及WL41至WL44。阱接触区1320可以通过阱偏置线接触1910来电连接至阱偏置线PWL。第一漏极区1440a可以通过第一位线接触1920a来电连接至第一位线BL1,并且第二漏极区1440b可以通过第二位线接触1920b来电连接至第二位线BL2。类似地,第三漏极区1440c可以通过第三位线接触1920c来电连接至第三位线BL3,并且第四漏极区1440d可以通过第四位线接触1920d来电连接至第四位线BL4。

[0150] 尽管图28描绘了一个其中反熔丝式0TP存储器单元阵列1000包括用'4×4'矩阵形式排列的十六个反熔丝栅极1711至1714、1721至1724、1731至1734以及1741至1744的例子,但是本公开内容并不限于此。换言之,可以有任意数目个反熔丝栅极。

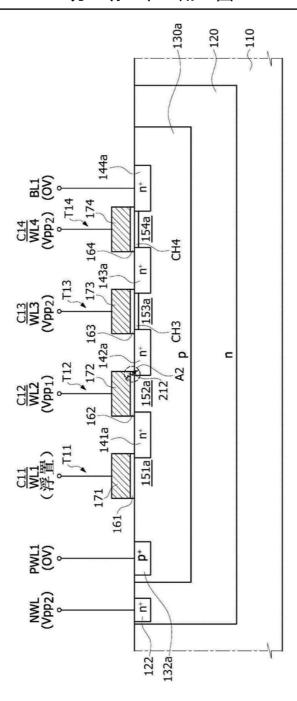

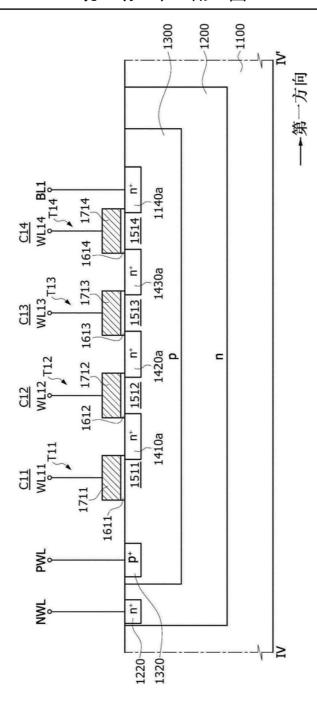

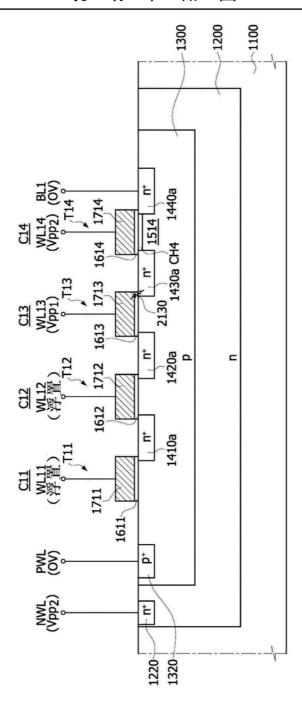

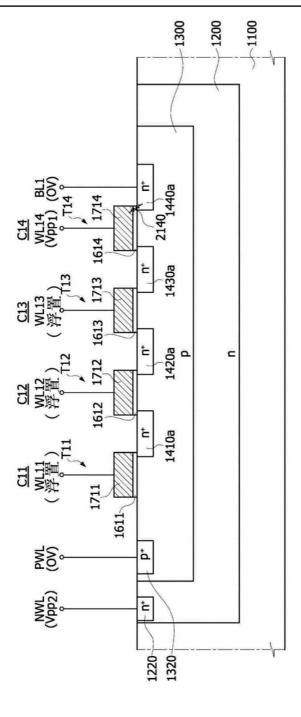

[0151] 图29是沿着图28的线IV-IV'所取的横截面图。换言之,图29描绘了与图28中分别被设置在第一行与第一至第四列的交叉点的单位单元C11、C12、C13及C14对应的第一晶体管T11、T12、T13及T14的横截面图。沿着第二、第三及第四行所取的横截面图的每一个可以与在图29中描绘的横截面图实质相同的。在图29中,和在图28中所用的相同的附图标记表示相同的元件。

[0152] 参照图28及29,具有第一导电类型的深阱区1200(例如,N型深阱区)可以被设置在村底1100的上部区域中。深阱接触区1220和阱区1300可以被设置在深阱区1200的上部区域中。因而,深阱接触区1220的侧壁及底表面和阱区1300的侧壁及底表面可以被深阱区1200包围。尽管未显示在图29中,如参考图28所述的,排列在第二、第三及第四行的单位单元可

以与排列在第一行的单位单元C11、C12、C13及C14共享阱区1300。深阱接触区1220可以具有与深阱区1200相同的导电类型,并且具有杂质浓度高于深阱区1200的杂质浓度。

[0153] 阱接触区1320、多个第一源极/漏极区1410a、1420a及1430a、以及第一漏极区1440a可以依序地排列在阱区1300的上部区域中,以在第一方向上彼此间隔开。阱接触区1320可以具有与阱区1300相同的导电类型。然而,阱接触区1320的杂质浓度可以高于阱区1300的杂质浓度。所有的第一源极/漏极区1410a、1420a及1430a以及第一漏极区1440a可以是N型。在第一列的第一沟道区1511可以被设置在第一源极/漏极区1410a的与第一漏极区1440a相对的一侧。在第二列的第一沟道区1512可以被设置在第一源极/漏极区1410a与1420a之间。在第三列的第一沟道区1513可以被设置在第一源极/漏极区1420a与1430a之间。再者,在第四列的第一沟道区1514可以被设置在第一源极/漏极区1430a与第一漏极区1440a之间。

[0154] 反熔丝绝缘层1611和反熔丝栅极1711可以依序地被层叠在位于第一行与第一列的交叉点的第一沟道区1511上。反熔丝绝缘层1611和反熔丝栅极1711的一侧壁可以与第一源极/漏极区1410a的第一侧壁垂直地对齐。反熔丝绝缘层1612和反熔丝栅极1712可以依序地被层叠在位于第一行与第二列的交叉点的第一沟道区1512上。反熔丝绝缘层1612和反熔丝栅极1712的一侧壁可以与第一源极/漏极区1410a的第二侧壁垂直地对齐,并且反熔丝绝缘层1612和反熔丝栅极1712的第二侧壁可以与第一源极/漏极区1420a的第一侧壁垂直地对齐。反熔丝绝缘层1613和反熔丝栅极1713可以依序地被层叠在位于第一行与第三列的交叉点的第一沟道区1513上。反熔丝绝缘层1613和反熔丝栅极1713的一侧壁可以与第一源极/漏极区1420a的第二侧壁垂直地对齐,并且反熔丝绝缘层1613和反熔丝栅极1713的第二侧壁可以与第一源极/漏极区1430a的第一侧壁垂直地对齐。反熔丝绝缘层1614和反熔丝栅极1714可以依序地被层叠在位于第一行与第四列的交叉点的第一沟道区1514上。反熔丝绝缘层1614和反熔丝栅极1714的一侧壁可以与第一源极/漏极区1430a的第二侧壁垂直地对齐,并且反熔丝绝缘层1614和反熔丝栅极1714的第二侧壁可以与第一漏极区1440a的第一侧壁垂直地对齐。

[0155] 在被排列于第一行的第一晶体管T11、T12、T13及T14中的在第一列的第一晶体管T11可以具有半MOS晶体管结构。在第一行的其余的第一晶体管T12、T13及T14的每一个可以具有完整的MOS晶体管结构。

[0156] 排列在第一行的反熔丝栅极1711、1712、1713及1714可以分别电连接至位于第一行与第一至第四列的交叉点的字线WL11、WL12、WL13及WL14。深阱接触区1220可以电连接至深阱偏置线NWL。阱接触区1320可以电连接至阱偏置线PWL。第一漏极区1440a可以电连接至第一位线BL1。

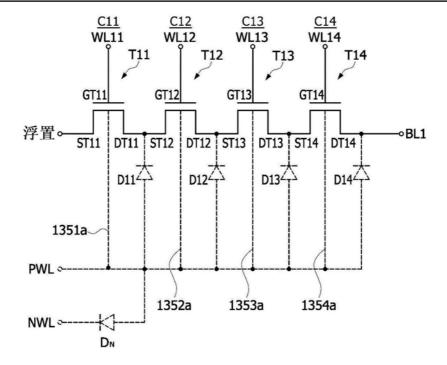

[0157] 图30是描绘在图29中所示的横截面图的等效电路图。尽管图30只描绘了排列在第一行的单位单元C11、C12、C13及C14的等效电路图,但是与沿着其它行(亦即第二、第三及第四行)所取的横截面图相对应的等效电路图的每一个亦可以与在图30中所示的等效电路图实质相同的。

[0158] 参照图28、29及30,在第一行的单位单元C11可以对应于具有半MOS晶体管结构的晶体管T11,并且排列在第一行的其余的单位单元C12、C13及C14可以对应于晶体管T12、T13及T14,其分别具有完整的MOS晶体管结构。换言之,反熔丝式OTP存储器单元阵列1000并不

包括用于在被排列于第一行的单位单元C11、C12、C13及C14之中选择特定的单位单元的选择晶体管。晶体管T11、T12、T13及T14可以依序地串联连接。换言之,位于第一行与第一列的交叉点的晶体管T11的漏极端子DT11可以电连接至位于第一行与第二列的交叉点的晶体管T12的源极端子ST12;位于第一行与第二列的交叉点的晶体管T12的漏极端子DT12可以电连接至位于第一行与第三列的交叉点的晶体管T13的源极端子ST13;并且位于第一行与第三列的交叉点的晶体管T13的漏极端子DT13可以电连接至位于第一行与第四列的交叉点的晶体管T14的源极端子ST14。位于第一行与第一列的交叉点的晶体管T11的源极端子ST11可以是电浮置的,并且位于第一行与第四列的交叉点的晶体管T14的漏极端子DT14可以电连接至第一位线BL1。

[0159] 位于第一行与第一列的交叉点的晶体管T11的栅极端子GT11可以电连接至字线WL11。位于第一行与第二列的交叉点的晶体管T12的栅极端子GT12可以电连接至字线WL12。位于第一行与第三列的交叉点的晶体管T13的栅极端子GT13可以电连接至字线WL13。位于第一行与第四列的交叉点的晶体管T14的栅极端子GT14可以电连接至字线WL14。晶体管T11的漏极端子DT11和晶体管T12的源极端子ST12可以电连接至位于第一行与第一列的交叉点的第一二极管D11的阴极,并且晶体管T12的漏极端子DT12和晶体管T13的源极端子ST13可以电连接至位于第一行与第二列的交叉点的第一二极管D12的阴极。类似地,晶体管T13的漏极端子DT13和晶体管T14的源极端子ST14可以电连接至位于第一行与第三列的交叉点的第一二极管D13的阴极,并且晶体管T14的漏极端子DT14可以电连接至位于第一行与第四列的交叉点的第一二极管D13的阴极,并且晶体管T14的漏极端子DT14可以电连接至位于第一行与第四列的交叉点的第一二极管D11、D12、D13及D14的阳极可以电连接至阱偏置线PWL。第一二极管D11、D12、D13及D14的阳极亦可以是电连接至深阱二极管D的阳极。深阱二极管D的阳极可以电连接至深阱偏置线NWL。

[0160] 构成位于第一行与第一列的交叉点的单位单元C11的晶体管T11的栅极端子GT11和漏极端子DT11可以分别对应于参考图28及29所述的反熔丝栅极1711和第一源极/漏极区1410a。没有对应于晶体管T11的浮置的源极端子ST11的扩散区可以被设置在衬底1100中。构成位于第一行与第二列的交叉点的单位单元C12的晶体管T12的栅极端子GT12、源极端子ST12和漏极端子DT12可以分别对应于反熔丝栅极1712、第一源极/漏极区1410a和第一源极/漏极区1420a。第一源极/漏极区1410a可以用作晶体管T11的漏极端子DT11和晶体管T12的源极端子ST12。构成位于第一行与第三列的交叉点的单位单元C13的晶体管T13的栅极端子GT13、源极端子ST13和漏极端子DT13可以分别对应于反熔丝栅极1713、第一源极/漏极区1420a和第一源极/漏极区1430a。第一源极/漏极区1420a可以用作晶体管T12的漏极端子DT12和晶体管T13的源极端子ST13。构成位于第一行与第四列的交叉点的单位单元C14的晶体管T14的栅极端子GT14、源极端子ST14和漏极端子DT14可以分别对应于反熔丝栅极1714、第一源极/漏极区1430a和第一漏极区1440a。第一源极/漏极区1430a可以用作晶体管T13的漏极端子DT13和晶体管T14的源极端子ST14。

[0161] 第一二极管D11可以对应于由阱区1300与第一源极/漏极区1410a所构成的寄生二极管组件,并且第一二极管D12可以对应于由阱区1300与第一源极/漏极区1420a所构成的寄生二极管组件。再者,第一二极管D13可以对应于由阱区1300与第一源极/漏极区1430a所构成的寄生二极管组件,并且第一二极管D14可以对应于由阱区1300与第一漏极区1440a所构成的寄生二极管组件。此外,深阱二极管DN可以对应于由阱区1300与深阱区1200所构成

的寄生二极管组件。

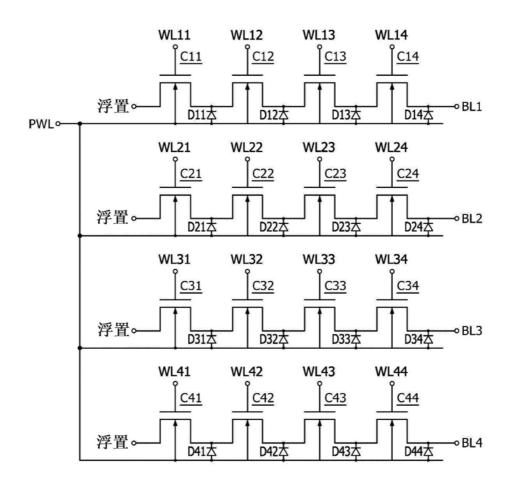

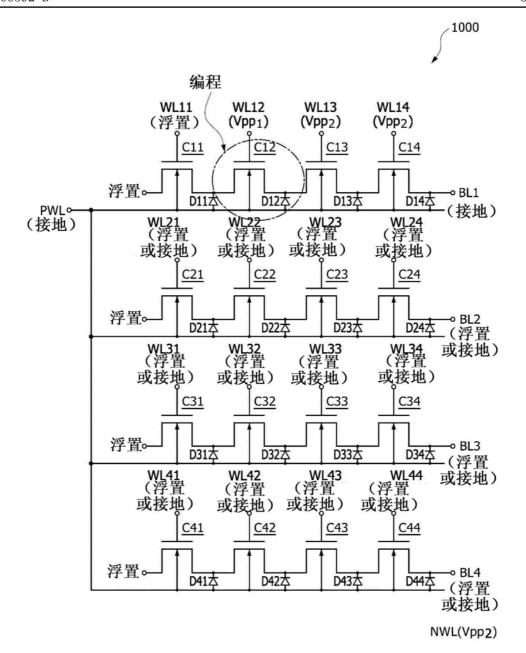

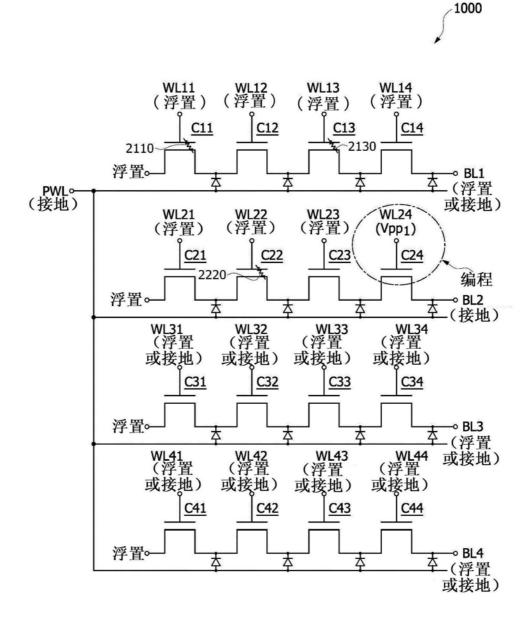

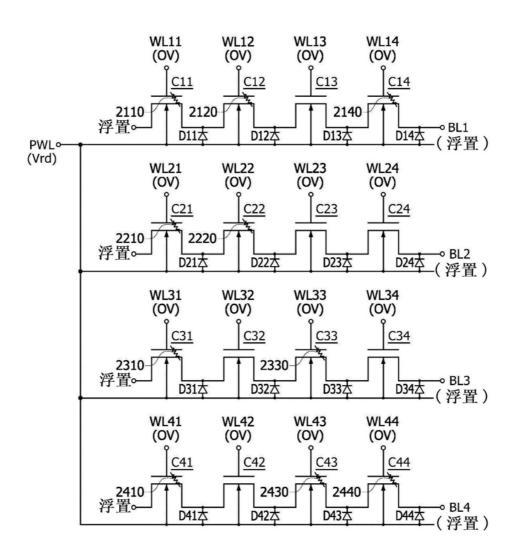

[0163] 图31是描绘在图28中所示的反熔丝式0TP存储器单元阵列1000的等效电路图。图 31的反熔丝式0TP存储器单元阵列1000可以对应于多个行的等效电路图,每一行都具有与参考图30所述的第一行实质相同的配置。

[0164] 参照图31,多个字线WL11至WL14、WL21至WL24、WL31至WL34和WL41至WL44可以连接至构成分别位于行和列的交叉点的单位单元的晶体管的栅极端子。如参考图30所述的,所有位于所述行与所述行列的交叉点的单位单元都可以连接至阱偏置线PWL。

排列在第一行的单位单元C11、C12、C13及C14可以在第一方向(亦即,行方向)上串 联连接。被排列于第一行的单位单元C11、C12、C13及C14之中的单位单元C11的源极端子可 以是浮置的,并且单位单元C14的漏极端子可以电连接至第一位线BL1。排列在第二行的单 位单元C21、C22、C23及C24亦可以串联连接在第一方向上。在被排列于第二行的单位单元 C21、C22、C23及C24之中的单位单元C21的源极端子可以是浮置的,并且单位单元C24的漏极 端子可以电连接至第二位线BL2。排列在第三行的单位单元C31、C32、C33及C34亦可以串联 连接在第一方向上。在被排列于第三行的单位单元C31、C32、C33及C34之中的单位单元C31 的源极端子可以是浮置的,并且单位单元C34的漏极端子可以电连接至第三位线BL3。排列 在第四行的单位单元C41、C42、C43及C44亦可以串联连接在第一方向上。在被排列于第四行 的单位单元C41、C42、C43及C44之中的单位单元C41的源极端子可以是浮置的,并且单位单 元C44的漏极端子可以电连接至第四位线BL4。寄生PN二极管D11至D14、D21至D24、D31至D34 以及D41至D44可以被设置在阱偏置线PWL与构成单位单元C11至C14、C21至C24、C31至C34以 及C41至C44的晶体管(在以下被称为"单元晶体管")的漏极端子之间。寄生PN二极管D11至 D14、D21至D24、D31至D34和D41至D44的阳极可以电连接至阱偏置线PWL,并且寄生PN二极管 D11至D14、D21至D24、D31至D34以及D41至D44的阴极可以电连接至单元晶体管的漏极端子。 图32至41是描绘在图31中所示的反熔丝式0TP存储器单元阵列1000的编程操作的

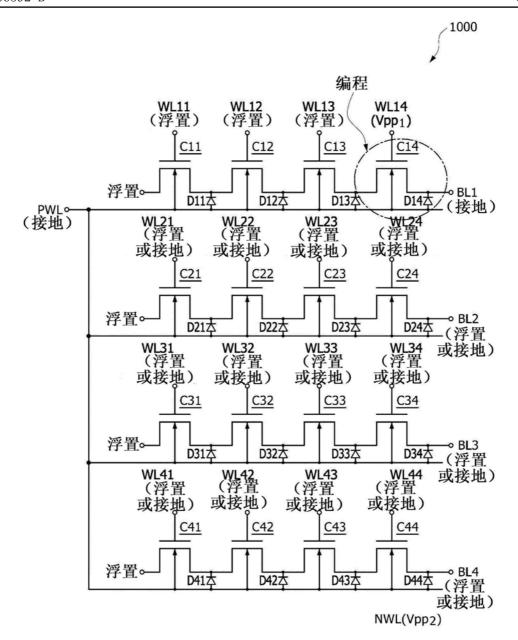

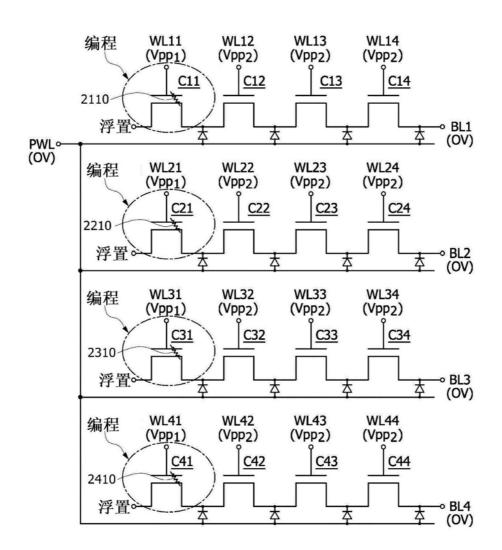

[0167] 反熔丝式0TP存储器单元阵列1000可以逐行地被编程。换言之,编程操作可以以行为单位来反复地被执行。此外,排列在每个行的单位单元可以从位于第一列的第一个单位单元起到位于最后一列的最后一个单位单元依序地被编程。

示意图。在图32至41中,和在图28至31中所用的相同的附图标记表示相同的元件。

[0168] 如在图32中所绘,位于第一行与第一列的交叉点的单位单元C11可以首先被编程,以便于编程排列在第一行的单位单元C11、C12、C13及C14。为了选择性地编程单位单元C11,第一编程电压Vpp1可以被施加至连接到选中的单位单元C11的字线WL11。第一编程电压Vpp1可以被设定以具有能够使得选中的单位单元C11的反熔丝绝缘层(图29的1611)破裂的电压电平,以形成电阻性路径。在某些实施例中,第一编程电压Vpp1可以具有约10V到约20V的电压电平。此外,第二编程电压Vpp2可以被施加至分别连接到排列在第一行的其余的未选中的单位单元C12、C13及C14的字线WL12、WL13及WL14。第二编程电压Vpp2可以被设定以

具有大于构成未选中的单位单元C12、C13及C14的晶体管的阈值电压并且能够防止未选中的单位单元C12、C13及C14的反熔丝绝缘层(图29的1612、1613及1614)破裂的电压电平。在某些实施例中,第二编程电压Vpp2可以具有约2V到约5V的电压电平。再者,在排列在第一行的单位单元C11、C12、C13及C14被编程的同时,第一位线BL1和阱偏置线PWL可以是接地的。再者,第二编程电压Vpp2亦可以被施加至深阱偏置线NWL。其它的位线,亦即第二、第三及第四位线BL2、BL3及BL4可以是浮置或接地的。其它的字线,亦即排列在第二行的字线WL21至WL24、排列在第三行的字线WL31至WL34、以及排列在第四行的字线WL41至WL44亦可以是浮置或接地的。

[0169] 图33是排列在第一行的单位单元C11、C12、C13及C14的横截面图,以描绘在以上的偏置条件下的选中的单位单元C11的编程机制。

[0170] 如在图33中所绘,因为大于未选中的单位单元C12、C13及C14的阈值电压的第二编程电压Vpp2被施加至连接到未选中的单位单元C12、C13及C14的所有字线WL12、WL13及WL14,因此构成未选中的单位单元C12、C13及C14的晶体管T12、T13及T14可以被导通。因此,反转沟道CH2、CH3及CH4分别可以被形成在晶体管T12、T13及T14的第一沟道区1512、1513及1514中。

[0171] 被施加至第一位线BL1的接地电压可以通过第一漏极区1440a、反转沟道CH4、第一源极/漏极区1430a、反转沟道CH3、第一源极/漏极区1420a、以及反转沟道CH2而被传送至第一源极/漏极区1410a。因此,在第一编程电压Vpp1与接地电压之间的电压差(亦即,第一编程电压Vpp1)可以被施加在第一反熔丝栅极1711与第一源极/漏极区1410a之间。因而,在第一反熔丝栅极1711与第一源极/漏极区1410a之间的反熔丝绝缘层1611可以因第一编程电压Vpp1而破裂,以形成电流流过的电阻性路径2110。因此,选中的单位单元C11可以被编程。[0172] 在被排列于第一行的未选中的单位单元C12中,第二编程电压Vpp2可以被施加在反熔丝栅极1712与第一源极/漏极区1420a之间。由于第二编程电压Vpp2具有不足以使得反熔丝绝缘层1612破裂的电压电平,因此没有电阻性路径被形成在介于第二反熔丝栅极1712与第一源极/漏极区1420a之间的反熔丝绝缘层1612中。未选中的单位单元C12的此种编程禁止机制可以等同地被应用到排列在第一行的其余的未选中的单位单元C13及C14。

[0173] 图34是描绘在用于选择性地编程单位单元C11的编程操作期间被施加至排列在第二行的单位单元C21、C22、C23及C24的偏置条件的横截面图。

[0174] 如在图34中所绘,连接至排列在第二行的未选中的单位单元C21、C22、C23及C24的字线WL21至WL24可以是浮置或接地的。连接至未选中的单位单元C24的第二位线BL2亦可以是浮置或接地的。

[0175] 当字线WL21至WL24浮置时,被包括在未选中的单位单元C21、C22、C23及C24中的反熔丝绝缘层1621、1622、1623及1624并不会破裂,而不论被施加至第二位线BL2的电压电平为何。因此,没有电阻性路径被形成在反熔丝绝缘层1621、1622、1623及1624的每一个中。

[0176] 当字线WL21至WL24是接地的、并且第二位线BL2是浮置时,所有的第二源极/漏极区1410b、1420b及1430b和第二漏极区1440b可以是浮置的。因此,即使字线WL21至WL24是接地的,被包括在未选中的单位单元C21、C22、C23及C24中的反熔丝绝缘层1621、1622、1623及1624也不会破裂。因此,在反熔丝绝缘层1621、1622、1623及1624的每一个中并没有形成电阻性路径。

[0177] 当字线WL21至WL24接地、并且第二位线BL2接地时,所有的第二源极/漏极区1410b、1420b及1430b可以是浮置的,因为没有反转沟道被形成在晶体管T22、T23及T24的每一个中,并且第二漏极区1440b可以是接地的。因此,即使字线WL21至WL24是接地的,被包括在未选中的单位单元C21、C22、C23及C24中的反熔丝绝缘层1621、1622、1623及1624也不会破裂。因而,在第二行的未选中的单位单元C21、C22及C23不会被编程。在未选中的单位单元C24中,在反熔丝栅极1724与第二漏极1440b之间的电压差可以是约为零。因此,未选中的单位单元C24不会被编程。未选中的单位单元C21、C22、C23及C24的此种编程禁止机制可以等同地被应用到排列在第三行的其余的未选中的单位单元C31、C32、C33及C34和排列在第四行的其余的未选中的单位单元C41、C42、C43及C44。

[0178] 参照图35,被排列于第一行的单位单元C11、C12、C13及C14之中的单位单元C11被编程之后,用于选择性地编程位于第二列的单位单元C12的编程操作可以被执行。明确地说,当连接至已编程单位单元C11的字线WL11浮置时,第一编程电压Vpp1可以被施加至连接到选中的单位单元C12的字线WL12,并且第二编程电压Vpp2可以被施加至连接到未编程单位单元之中的未选中的单位单元C13及C14的字线WL13及WL14。此外,接地电压可以被施加至第一位线BL1和阱偏置线PWL,并且其余的位线BL2、BL3及BL4可以是浮置或接地的。其它的字线,亦即排列在第二行的字线WL21至WL24、排列在第三行的字线WL31至WL34、和排列在第四行的字线WL41至WL44亦可以是浮置或接地的。再者,第二编程电压Vpp2亦可以被施加至深阱偏置线NWL。

[0179] 图36是描绘在用于选择性地编程单位单元C12的编程操作期间,被施加至排列在第一行的单位单元C11、C12、C13及C14的偏置条件的横截面图。

[0180] 如在图36中所绘,由于连接至已编程单位单元C11的字线WL11是浮置的,因此不论第一源极/漏极区1410a的电压电平为何,用于编程选中的单位单元C12的编程操作都不会影响到已编程单位单元C11。

[0181] 因为大于未选中的单位单元C13及C14的阈值电压的第二编程电压Vpp2被施加至连接到未选中的单位单元C13及C14的字线WL13及WL14,因此构成未选中的单位单元C13及C14的晶体管T13及T14可以被导通。因此,反转沟道CH3及CH4分别可以被形成在晶体管T13及T14的沟道区1513及1514中。被施加至第一位线BL1的接地电压可以通过第一漏极区1440a、反转沟道CH4、第一源极/漏极区1430a以及反转沟道CH3而被传送至第一源极/漏极区1420a。因此,第一编程电压Vpp1与接地电压之间的电压差(亦即,第一编程电压Vpp1)可以被施加在反熔丝栅极1712与第一源极/漏极区1420a之间。因而,在反熔丝栅极1712与第一源极/漏极区1420a之间的反熔丝绝缘层1612可以因第一编程电压Vpp1而破裂,以形成电流流过的电阻性路径2120。因此,选中的单位单元C12可以被编程。

[0182] 在与选中的单位单元C12一起排列在第一行的未选中的单位单元C13中,第二编程电压Vpp2可以被施加在反熔丝栅极1713与第一源极/漏极区1430a之间。由于第二编程电压Vpp2具有不足以使得反熔丝绝缘层1613破裂的电压电平,因此没有电阻性路径被形成在介于反熔丝栅极1713与第一源极/漏极区1430a之间的反熔丝绝缘层1613中。未选中的单位单元C13的此种编程禁止机制可以等同地被应用到位于第一行与第四列的交叉点的其余的未选中的单位单元C14。再者,在用于选择性地编程单位单元C12的编程操作期间,排列在第二、第三及第四行的未选中的单位单元C21至C24、C31至C34以及C41至C44通过与参考图34

所述的相同的编程禁止机制而不会被编程。

[0183] 参照图37,被排列于第一行的单位单元C11、C12、C13及C14之中的单位单元C11及C12被编程之后,用于选择性地编程位于第三列的单位单元C13的编程操作可以被执行。明确地说,在一种其中连接至已编程单位单元C11及C12的字线WL11及WL12可以是浮置的状态中,第一编程电压Vpp1可以被施加至连接到选中的单位单元C13的字线WL13,并且第二编程电压Vpp2可以被施加至连接到未编程单位单元之中的未选中的单位单元C14的字线WL14。此外,接地电压可以被施加至第一位线BL1和阱偏置线PWL,并且其余的位线BL2、BL3及BL4可以是浮置或接地的。其它的字线,亦即排列在第二行的字线WL21至WL24、排列在第三行的字线WL31至WL34、以及排列在第四行的字线WL41至WL44亦可以是浮置或接地的。再者,第二编程电压Vpp2亦可以被施加至深阱偏置线NWL。

[0184] 图38是描绘在用于选择性地编程单位单元C13的编程操作期间被施加至排列在第一行的单位单元C11、C12、C13及C14的偏置条件的横截面图。

[0185] 如在图38中所绘,由于连接至已编程单位单元C11及C12的字线WL11及WL12是浮置的,因此不论第一源极/漏极区1410a及1420a的电压电平为何,用于编程选中的单位单元C13的编程操作都不会影响到单位单元C11及C12。

[0186] 因为大于未选中的单位单元C14的阈值电压的第二编程电压Vpp2被施加至字线WL14,因此构成未选中的单位单元C14的晶体管T14可以被导通。因而,反转沟道CH4可以被形成在晶体管T14的沟道区1514中。被施加至第一位线BL1的接地电压可以通过第一漏极区1440a和反转沟道CH4而被传送至第一源极/漏极区1430a。因此,第一编程电压Vpp1与接地电压之间的电压差(亦即,第一编程电压Vpp1)可以被施加在反熔丝栅极1713与第一源极/漏极区1430a之间。因而,在反熔丝栅极1713与第一源极/漏极区1430a之间的第三反熔丝绝缘层1613可以因第一编程电压Vpp1而破裂,以形成电流流过的电阻性路径2130。因此,选中的单位单元C13可以被编程。

[0187] 在与选中的单位单元C13一起排列在第一行的未选中的单位单元C14中,第二编程电压Vpp2可以被施加在反熔丝栅极1714与第一漏极区1440a之间。由于第二编程电压Vpp2具有不足以使得第四反熔丝绝缘层1614破裂的电压电平,因此没有电阻性路径被形成在介于反熔丝栅极1714与第一漏极区1440a之间的第四反熔丝绝缘层1614中。在用于选择性地编程单位单元C13的编程操作期间,排列在第二、第三及第四行的未选中的单位单元C21至C24、C31至C34和C41至C44通过与参考图34所述的相同的编程禁止机制而不会被编程。

[0188] 参照图39,被排列于第一行的单位单元C11、C12、C13及C14之中的单位单元C11、C12及C13被编程之后,用于选择性地编程位于最后一列(亦即,第四列)中的单位单元C14的编程操作可以被执行。明确地说,在一种其中连接至已编程单位单元C11、C12及C13的字线WL11、WL12及WL13可以是浮置的状态中,第一编程电压Vpp1可以被施加至连接到选中的单位单元C14的字线WL14。此外,接地电压可以被施加至第一位线BL1和阱偏置线PWL。其余的位线,例如是第二、第三及第四位线BL2、BL3及BL4可以是浮置或接地的。其它的字线,亦即排列在第二行的字线WL21至WL24、排列在第三行的字线WL31至WL34、和排列在第四行的字线WL41至WL44亦可以是浮置或接地的。再者,第二编程电压Vpp2亦可以被施加至深阱偏置线NWL。

[0189] 图40是描绘在用于选择性地编程单位单元C14的编程操作期间被施加至排列在第

一行的单位单元C11、C12、C13及C14的偏置条件的横截面图。

[0190] 如在图40中所绘,由于连接至已编程单位单元C11、C12及C13的字线WL11、WL12及WL13是浮置的,因此不论第一源极/漏极区1410a、1420a及1430a的电压电平为何,用于编程选中的单位单元C14的编程操作都不会影响到单位单元C11、C12及C13。

[0191] 被施加至第一位线BL1的接地电压可以直接被传送至第一漏极区1440a。因此,第一编程电压Vpp1与接地电压之间的电压差(亦即,第一编程电压Vpp1)可以被施加在反熔丝栅极1714与第一漏极区1440a之间。因而,在反熔丝栅极1714与第一漏极区1440a之间的反熔丝绝缘层1614可以因第一编程电压Vpp1而破裂,以形成电流流过的电阻性路径2140。因此,选中的单位单元C14可以被编程。在用于选择性地编程单位单元C14的编程操作期间,排列在第二、第三及第四行的未选中的单位单元C21至C24、C31至C34以及C41至C44通过与参考图34所述的相同的编程禁止机制而不会被编程。

[0192] 参照图41,在编程操作被施加至排列在第一行的所有的单位单元C11、C12、C13及C14和排列在第二行的单位单元C21、C22及C23之后,排列在第二行的单位单元C24可以被编程。在某些实施例中,被施加编程操作的单位单元C11、C12、C13、C14、C21、C22及C23可以具有一种带有电阻性路径的第一状态、或是一种不带有电阻性路径的第二状态。在本实施例中,可以假设单位单元C11、C13及C22具有分别带有电阻性路径2110、2130及2220的第一状态,并且单位单元C12、C14、C21及C23具有不带有电阻性路径的第二状态。排列在第三及第四行的单位单元C31至C34和C41至C44将会在后续的步骤中被编程。

[0193] 如在图41中所绘,阱偏置线PWL和第二位线BL2可以是接地的,以选择性地编程单位单元C24。其余的第一、第三及第四位线BL1、BL3及BL4可以是浮置或接地的。此外,连接至单位单元C11至C14、C21、C22及C23的字线WL11至WL14、WL21、WL22及WL23可以是浮置的,并且连接至单位单元C31至C34和C41至C44的字线WL31至WL34和WL41至WL44可以是浮置或接地的。再者,第一编程电压Vpp1可以被施加至连接到选中的单位单元C24的字线WL24。尽管未显示在图41中,第二编程电压Vpp2可以被施加至深阱偏置线NWL。

[0194] 在以上的偏置条件下,选中的单位单元C24可以通过与参考图39及40所描述的单位单元C14的编程机制相同的机制来被编程。在用于编程选中的单位单元C24的编程操作期间,单位单元C31至C34和C41至C44通过与参考图34所述的相同的编程禁止机制而不会被编程。单位单元C11至C14、C21、C22及C23不会受到用于编程选中的单位单元C24的编程操作的影响,因为连接至单位单元C11至C14、C21、C22及C23的字线是浮置的。因此,即使用于编程选中的单位单元C24的编程操作被执行,单位单元C11至C14、C21、C22及C23的每一个仍然可以维持其状态(亦即第一状态或第二状态)。

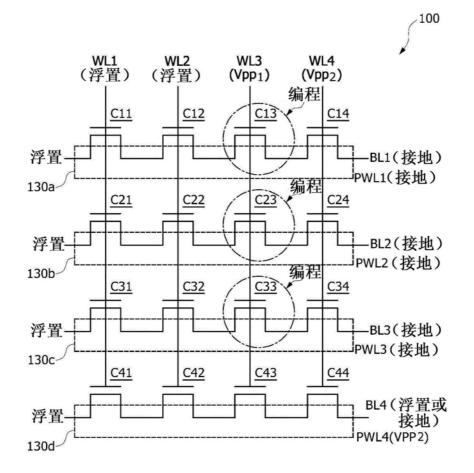

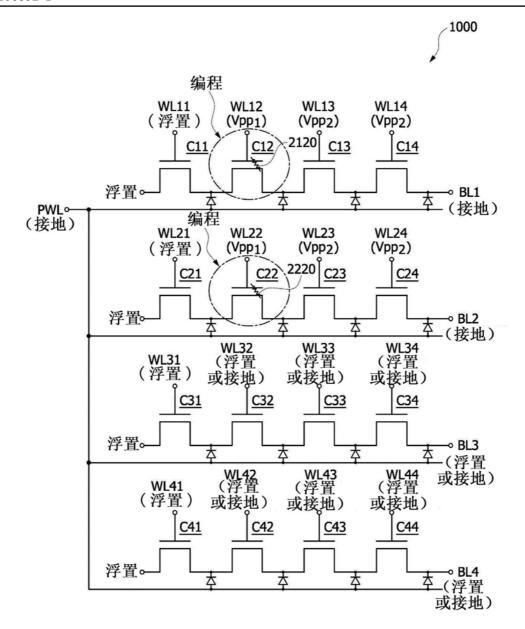

[0195] 图42及43是描绘在图31中所示的反熔丝式0TP存储器单元阵列1000的其它编程操作的等效电路图。

[0196] 根据本实施例,编程操作可以以列为单位来执行。换言之,用于选择性地编程被排列于第一列的单位单元C11、C21、C31及C41之中的至少一个目标单位单元的编程操作可以被执行,并且用于选择性地编程被排列于第二列的单位单元C12、C22、C32及C42之中的至少一个目标单位单元的编程操作接着可以被执行。接着,用于选择性地编程被排列于第三列的单位单元C13、C23、C33及C43之中的至少一个目标单位单元的编程操作可以被执行,并且用于选择性地编程被排列于最后一列(亦即,第四列)中的单位单元C14、C24、C34及C44的至

少一目标单位单元的编程操作可以最后来被执行。因而,在被排列于每个列的多个单位单元之中的至少一个目标单位单元可以被编程,以减少编程操作的数目。换言之,根据本实施例,反熔丝式0TP存储器单元阵列1000可以通过反复地执行与反熔丝式0TP存储器单元阵列1000的列的数目相同次数的编程操作来被编程。

[0197] 参照图42,一个其中排列在第一列的所有的单位单元C11、C21、C31及C41选择性且同时地被编程的例子将会被描述。明确地说,第一编程电压Vpp1可以被施加至连接到选中的单位单元C11、C21、C31及C41的字线WL11、WL21、WL31及WL41,并且第二编程电压Vpp2可以被施加至其余的字线WL12至WL14、WL22至WL24、WL32至WL34和WL42至WL44。阱偏置线PWL和第一至第四位线BL1至BL4可以是接地的。尽管未显示在图42中,第二编程电压Vpp2亦可以被施加至深阱偏置线NWL。

[0198] 在以上的偏置条件下,排列在第一列的选中的单位单元C11至C41可以通过与参考图33所描述的单位单元C11的编程机制相同的机制来同时被编程。因此,电阻性路径2110、2210、2310及2410分别可以被形成在选中的单位单元C11至C41的反熔丝绝缘层中。其余的未选中的单位单元C12至C14、C22至C24、C32至C34以及C42至C44通过与参考图33所描述的单位单元C12、C13及C14的编程禁止机制相同的机制而不会被编程。

参照图43,在被排列于第一列的单位单元C11至C41的编程操作被执行之后,排列 在第二列的单位单元C12至C42的编程操作可以被执行。如在图43中所绘,一个其中在被排 列于第二列的单位单元C12至C42中只有单位单元C12及C22选择性且同时地被编程的例子 将会被描述。为了选择性地编程单位单元C12及C22,连接至已编程单位单元C11至C41的字 线WL11至WL41可以是浮置的,并且第一编程电压Vpp1可以被施加至连接到选中的单位单元 C12及C22的字线WL12及WL22。连接至在被排列于第二列的单位单元C12至C42中的未选中的 单位单元C32及C42的字线WL32及WL42可以是浮置或接地的。第二编程电压Vpp2可以被施加 至连接到未选中的单位单元C13及C14的字线WL13及WL14,未选中的单位单元C13及C14排列 在与选中的单位单元C12相同的行,并且在后续的步骤中被编程。类似地,第二编程电压 Vpp2亦可以被施加至连接到未选中的单位单元C23及C24的字线WL23及WL24,未选中的单位 单元C23及C24排列在与选中的单位单元C22相同的行,并且在后续的步骤中被编程。连接至 未选中的单位单元C33、C34、C43及C44的字线WL33、WL34、WL43及WL44可以是浮置或接地的, 未选中的单位单元C33、C34、C43及C44排列在与未选中的单位单元C32及42相同的行并且在 后续的步骤中被编程。此外,接地电压可以被施加至分别连接到选中的单位单元C12及C22 的第一及第二位线BL1及BL2,并且其余的第三及第四位线BL3及BL4可以是浮置或接地的。 再者,阱偏置线PWL可以是接地的。尽管未显示在图43中,第二编程电压Vpp2亦可以被施加 至深阱偏置线NWL。

[0200] 在以上的偏置条件下,选中的单位单元C12及C22可以通过与参考图35及36所描述的单位单元C12的编程机制相同的机制来同时被编程。因此,电阻性路径2120及2220分别可以被形成在选中的单位单元C12及C22的反熔丝绝缘层中。如参考图36所述的单位单元C11,排列在第一列的未选中的单位单元C11、C21、C31及C41不会受到用于编程选中的单位单元C12及C22的编程操作的影响,因为字线WL11、WL21、WL31及WL41是浮置的。排列在第二、第三及第四列的其余的单位单元C13、C14、C23、C24、C32、C33、C34、C42、C43及C44通过与参考图35及36所述的相同的编程禁止机制而不会被编程。

[0201] 在用于编程排列在第二列的单位单元C12及C22的编程操作被执行之后,用于编程排列在第三列的单位单元中的至少一个的编程操作、以及用于编程排列在第四列的单位单元中的至少一个的编程操作可以被执行。用于编程排列在第三及第四列的单位单元的编程操作可以利用与用于编程排列在第一及第二列的单位单元的编程操作相同的方法来执行。 [0202] 图44是描绘在图31中所示的反熔丝式0TP存储器单元阵列1000的读取操作的偏置条件的等效电路图。

[0203] 根据本实施例的读取操作可以被执行,以同时读出构成反熔丝式OTP存储器单元阵列1000的所有的单位单元的数据。参照图44,读取电压Vrd可以被施加至阱偏置线PWL。尽管未显示在图44中,读取电压Vrd或是大于读取电压Vrd的电压可以被施加至深阱偏置线NWL,以电隔离反熔丝式OTP存储器单元阵列1000。所有的字线WL11至WL14、WL21至WL24、WL31至WL34和WL41至WL44可以是接地的,并且所有的位线BL1、BL2、BL3及BL4可以是浮置的。在某些实施例中,读取电压Vrd可以是在约1V到约3V的范围内。

[0204] 在本实施例中,可以假设排列在第一行的单位单元C11、C12及C14、排列在第二行的单位单元C21及C22、排列在第三行的单位单元C31及C33、以及排列在第四行的单位单元C41、C43及C44具有分别带有电阻性路径2110、2120、2140、2210、2220、2310、2330、2410、2430及2440的已编程状态。因此,电流可以从阱偏置线PWL起分别通过单位单元C11、C12及C14的寄生PN二极管D11、D12及D14和电阻性路径2110、2120及2140而流向字线WL11、WL12及WL14。换言之,当检测到流过字线WL11、WL12及WL14的电流时,连接至字线WL11、WL12及WL14的单位单元C11、C12及C14可以被识别为具有已编程状态。相对地,没有电流可以从阱偏置线PWL流向字线WL13,而不论寄生PN二极管D13的偏置条件为何,因为单位单元C13在其反熔丝绝缘层中并不具有任何电阻性路径。因此,连接至字线WL13的单位单元C13可以被识别为具有擦除状态,因为并未检测到流过字线WL13的电流。

[0205] 在被排列于第二行的单位单元C21至C24中,电流可以从阱偏置线PWL起分别通过单位单元C21及C22的寄生PN二极管D21及D22和电阻性路径2210及2220而流向字线WL21及WL22。换言之,当检测到流过字线WL21及WL22的电流时,连接至字线WL21及WL22的单位单元C21及C22可以被识别为具有已编程状态。相对地,没有电流可以从阱偏置线PWL流向字线WL23及WL24,而不论寄生PN二极管D23及D24的偏置条件为何,因为单位单元C23及C24的每一个在其反熔丝绝缘层中并不具有任何电阻性路径。因此,连接至字线WL23及WL24的单位单元C23及C24可以被识别为具有擦除状态,因为并未检测到流过字线WL23及WL24的电流。

[0206] 在被排列于第三行的单位单元C31至C34中,电流可以从阱偏置线PWL起分别通过单位单元C31及C33的寄生PN二极管D31及D33和电阻性路径2310及2330而流向字线WL31及WL33。换言之,当检测到流过字线WL31及WL33的电流时,连接至字线WL31及WL33的单位单元C31及C33可以被识别为具有已编程状态。相对地,没有电流可以从阱偏置线PWL流向字线WL32及WL34,而不论寄生PN二极管D32及D34的偏置条件为何,因为单位单元C32及C34的每一个在其反熔丝绝缘层中并不具有电阻性路径。因此,连接至字线WL32及WL34的单位单元C32及C34可以被识别为具有擦除状态,因为并未检测到流过字线WL32及WL34的电流。

[0207] 在被排列于第四行的单位单元C41至C44中,电流可以从阱偏置线PWL起分别通过单位单元C41、C43及C44的寄生PN二极管D41、D43及D44和电阻性路径2410、2430及2440而流向字线WL41、WL43及WL44。换言之,当检测到流过字线WL41、WL43及WL44的电流时,连接至字

线WL41、WL43及WL44的单位单元C41、C43及C44可以被识别为具有已编程状态。相对地,没有电流可以从阱偏置线PWL流向字线WL42,而不论寄生PN二极管D42的偏置条件为何,因为单位单元C42在其反熔丝绝缘层中并不具有电阻性路径。因此,连接至字线WL42的单位单元C42可以被识别为具有擦除状态,因为并未检测到流过字线WL42的电流。

[0208] 本公开内容的实施例已经在以上为了举例说明的目的而被公开。本领域技术人员将会体认到各种的修改、添加及替代都是可能的,而不脱离如在所附的权利要求中所公开的本公开内容的范围和精神。

[0209] 通过以上实施例可以看出,本申请提供了以下的技术方案。

[0210] 技术方案1.一种反熔丝式单次可编程0TP存储器单元阵列,其包括分别位于多个行与多个列的交叉点的多个单位单元,所述反熔丝式0TP存储器单元阵列包括:

[0211] 多个阱区,其分别被设置在所述多个行;

[0212] 多个反熔丝栅极,其分别被设置在所述多个列以与所述多个阱区相交;

[0213] 多个源极/漏极区,其分别被设置在所述阱区的介于所述多个反熔丝栅极之间的部分中:以及

[0214] 多个漏极区,其分别被设置在位于被设置在最后一列的最后反熔丝栅极的一侧的 所述阱区中,所述最后反熔丝栅极的所述一侧与被设置在第一列的第一反熔丝栅极相对,

[0215] 其中所述单位单元的每一个包括一个反熔丝晶体管,无选择晶体管,所述反熔丝晶体管具有金属氧化物半导体MOS晶体管结构。

[0216] 技术方案2. 如技术方案1所述的反熔丝式0TP存储器单元阵列,其中所述多个阱区的导电类型是与所述多个源极/漏极区和所述多个漏极区的导电类型相反的。

[0217] 技术方案3. 如技术方案2所述的反熔丝式0TP存储器单元阵列,

[0218] 其中所述多个阱区是P型:以及

[0219] 其中所述多个源极/漏极区和所述多个漏极区是N型。

[0220] 技术方案4. 如技术方案2所述的反熔丝式0TP存储器单元阵列, 其进一步包括:

[0221] 深阱区,其包围所述多个阱区的侧壁及底表面。

[0222] 技术方案5. 如技术方案4所述的反熔丝式0TP存储器单元阵列,其中所述深阱区的导电类型是与所述多个阱区的所述导电类型相反的。

[0223] 技术方案6. 如技术方案1所述的反熔丝式0TP存储器单元阵列,

[0224] 其中被设置在所述第一列的所述反熔丝晶体管的每一个具有半MOS晶体管结构; 以及

[0225] 其中,被设置在所述第一列的所述第一反熔丝栅极包括第一侧壁,所述一侧壁与在所述第一反熔丝栅极与被设置在第二列的第二反熔丝栅极之间的所述源极/漏极区的一个侧壁垂直地对齐;以及第二侧壁,其位于所述阱区之上。

[0226] 技术方案7. 如技术方案1所述的反熔丝式0TP存储器单元阵列,其进一步包括:

[0227] 多个字线,其分别电连接至所述多个反熔丝栅极;

[0228] 多个阱偏置线,其分别电连接至所述多个阱区;以及

[0229] 多个位线,其分别电连接至所述多个漏极区。

[0230] 技术方案8.如技术方案1所述的反熔丝式0TP存储器单元阵列,其进一步包括:

[0231] 多个沟道区,其被设置在所述阱区的与所述反熔丝栅极重叠的上部区域中。

[0232] 技术方案9. 如技术方案1所述的反熔丝式0TP存储器单元阵列,其中,所述源极/漏极区的每一个具有两个相对的侧壁,所述两个相对的侧壁与两个相邻的反熔丝栅极部分重叠;并且所述漏极区的每一个具有与相邻于所述漏极区的所述反熔丝栅极部分重叠的侧壁。

[0233] 技术方案10.一种反熔丝式单次可编程0TP存储器单元阵列,其包括:

[0234] 多个单位单元,其分别位于多个行与多个列的交叉点,所述单位单元的每一个包括反熔丝晶体管,所述反熔丝晶体管具有金属氧化物半导体MOS晶体管结构;

[0235] 多个字线,其分别被设置在所述多个列,排列在每个列的所述反熔丝晶体管共享 所述多个字线的任一个:

[0236] 多个阱偏置线,其分别被设置在所述多个行,排列在每个行的所述反熔丝晶体管共享所述多个阱偏置线的任一个;以及

[0237] 多个位线,其分别连接至排列在所述多个列的最后一列的所述反熔丝晶体管的漏极端子。

[0238] 技术方案11.如技术方案10所述的反熔丝式0TP存储器单元阵列,其中排列在每个行的所述反熔丝晶体管是串联连接的。

[0239] 技术方案12. 如技术方案11所述的反熔丝式0TP存储器单元阵列,其进一步包括:

[0240] 多个PN二极管,其设置在所述反熔丝晶体管的漏极端子与所述阱偏置线之间。

[0241] 技术方案13.如技术方案12所述的反熔丝式0TP存储器单元阵列,其中,所述PN二极管的阳极连接至所述阱偏置线,并且所述PN二极管的阴极连接至所述反熔丝晶体管的所述漏极端子。

[0242] 技术方案14. 如技术方案13所述的反熔丝式0TP存储器单元阵列,其进一步包括:

[0243] 深阱偏置线:以及

[0244] 多个深阱PN二极管,其耦接在所述深阱偏置线与所述阱偏置线之间。

[0245] 技术方案15.如技术方案14所述的反熔丝式0TP存储器单元阵列,其中,所述深阱PN二极管的阳极连接至所述阱偏置线,并且所述深阱PN二极管的阴极连接至所述深阱偏置线。

[0246] 技术方案16.如技术方案10所述的反熔丝式0TP存储器单元阵列,其中,排列在所述多个列的第一列的所述反熔丝晶体管的所有的源极端子电浮置。

[0247] 技术方案17.一种反熔丝式单次可编程0TP存储器单元阵列,其包括分别位于多个行与多个列的交叉点的多个单位单元,所述反熔丝式0TP存储器单元阵列包括:

[0248] 阱区,其被所述多个单位单元所共享:

[0249] 多个反熔丝栅极,其分别被设置在所述多个行与所述多个列的交叉点以构成所述 多个单位单元;

[0250] 多个源极/漏极区,其分别被设置在所述阱区的介于排列在所述多个行的每一个中的所述多个反熔丝栅极之间的部分中;以及

[0251] 多个漏极区,其分别被设置在所述阱区的位于排列在所述多个列的最后一列的所述反熔丝栅极的一侧的部分中,所述反熔丝栅极的所述一侧与排列在所述多个列的第一列的所述反熔丝栅极相对,

[0252] 其中,所述单位单元的每一个包括一个反熔丝晶体管,无选择晶体管,所述反熔丝

晶体管具有金属氧化物半导体MOS晶体管结构。

[0253] 技术方案18.一种反熔丝式单次可编程0TP存储器单元阵列,其包括:

[0254] 多个单位单元,其分别位于多个行与多个列的交叉点,所述单位单元的每一个包括反熔丝晶体管,所述反熔丝晶体管具有金属氧化物半导体MOS晶体管结构;

[0255] 多个字线,其分别连接至所述反熔丝晶体管;

[0256] 阱偏置线,其被所述反熔丝晶体管所共享;以及

[0257] 多个位线,其分别连接至排列在所述多个列的最后一列的所述反熔丝晶体管的漏极端子。

[0258] 技术方案19. 如技术方案18所述的反熔丝式0TP存储器单元阵列,其中排列在每个行的所述反熔丝晶体管是串联连接的。

[0259] 技术方案20. 如技术方案18所述的反熔丝式0TP存储器单元阵列,其进一步包括:

[0260] 多个PN二极管,其被设置在所述反熔丝晶体管的漏极端子与所述阱偏置线之间。

图1

图2

图3

图4

图5

图6

图7

图8

48

图10

图11

图12

图13

图14

图15

图16

图17

图18

100

图19

图20

图21

图22

图23

图24

图25

图26

图27

图28

图29

图30

图31

图32

图33

图34

图35

图36

图37

图38

图39

图40

图41

图42

图43

图44