(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第4680888号 (P4680888)

(45) 発行日 平成23年5月11日(2011.5.11)

(24) 登録日 平成23年2月10日(2011.2.10)

(51) Int . Cl .

HO 1 L 25/065 (2006.01)

HO1L 25/08

FL

$\mathbf{z}$

HO1L 25/07 (2006.01) HO1L 25/18 (2006.01)

請求項の数 5 (全 9 頁)

(21) 出願番号 特願2006-503297 (P2006-503297)

(86) (22) 出願日 平成16年2月4日 (2004.2.4)

(65) 公表番号 特表2006-520531 (P2006-520531A)

(43)公表日 平成18年9月7日 (2006.9.7) (86) 国際出願番号 PCT/US2004/003099

(87) 国際公開番号 W02004/077896

(87) 国際公開日 平成16年9月10日 (2004.9.10) 審査請求日 平成19年2月1日 (2007.2.1)

(31) 優先権主張番号 10/371,089

(32) 優先日 平成15年2月21日 (2003. 2. 21)

(33) 優先権主張国 米国(US)

|(73)特許権者 504199127

フリースケール セミコンダクター イン

コーポレイテッド

アメリカ合衆国 78735 テキサス州 オースティン ウィリアム キャノン

ドライブ ウエスト 6501

(74)代理人 100116322

弁理士 桑垣 衛

|(72)発明者 ガーバー、マーク エイ.

アメリカ合衆国 78745 テキサス州 オースティン ウエスト ドーマン ド

ライブ 15808

最終頁に続く

(54) 【発明の名称】マルチダイ半導体パッケージ及びその形成方法

## (57)【特許請求の範囲】

### 【請求項1】

半導体パッケージであって、

頂部面及び底面を有する平坦な上部電気コンタクトレベルと<u>頂部面及び底面を有する平</u> 坦な下部電気コンタクトレベルとを有する電気相互接続フレーム<u>であって</u>、前記<u>上部</u>電気 コンタクトレベルは前記<u>下部</u>電気コンタクトレベルとほぼ平行かつオフセットの状態にあ る、電気相互接続フレームと、

前記上部電気コンタクトレベルの頂部面に取付けられる第一の集積回路ダイと、

前記上部電気コンタクトレベルの底面に取付けられる第二の集積回路ダイと、

前記第二の集積回路ダイ上のパッドに接続される第一の端部<u>と前</u>記<u>上部</u>電気コンタクトレベルの底面に接続される第二の端部とを有する第二のワイヤと、

前記第一の集積回路ダイ上のパッドに接続される第一の端部<u>と前</u>記<u>下部</u>電気コンタクトレベルの頂部面に接続される第二の端部とを有する第一のワイヤと、

からなる半導体パッケージ。

#### 【請求項2】

前記電気相互接続フレームは更に差込構造体を含み、前記差込構造体は前記<u>上部</u>電気コンタクトレベルに配置される頂部と、前記<u>下部</u>電気コンタクトレベルに配置される底部とを含み、前記<u>第二のワイヤ</u>の第二の端部は、前記<u>差込構造体の</u>頂部の底面に接続されている請求項1に記載の半導体パッケージ。

【請求項3】

20

半導体パッケージであって、

複数の第一のパッドを有す<u>る平</u>坦な<u>上部</u>電気コンタクトレベル<u>と複</u>数の第二のパッドを有す<u>る平</u>坦な<u>下部</u>電気コンタクトレベルとを含む金属性の電気相互接続フレームと、前記 上部電気コンタクトレベルは、前記<u>下部</u>電気コンタクトレベルとほぼ平行かつオフセット の状態にあることと、前記<u>上部</u>電気コンタクトレベル及び前記<u>下部</u>電気コンタクトレベル のいずれも頂部面及び底面を有することと、

頂部面及び底面を備えた第一の集積回路ダイと、前記第一の集積回路ダイの底面は前記上部電気コンタクトレベルの頂部面に取付けられることと、前記第一の集積回路ダイの頂部面は前記複数の第二のパッドにワイヤ接続される複数のパッドを有することと、

頂部面及び底面を備えた第二の集積回路ダイと、前記第二の集積回路ダイの底面は前記上部電気コンタクトレベルの底面に取付けられることと、前記第二の集積回路ダイの頂部面は前記複数の第一のパッドにワイヤ接続される複数のパッドを有することと、からなる半導体パッケージ。

## 【請求項4】

前記<u>電気相互接続フレームは、各々が前記上部電気コンタクトレベルに配置される頂部と</u>前記下部電気コンタクトレベルに配置される底部とを有する複数の差込構造体を含み、

前記<u>上部電気コンタクトレベルの</u>複数の第一のパッドの各々は前記複数の<u>差込構</u>造体のうちの一つの差込構造体の一部である請求項3に記載の半導体パッケージ。

#### 【請求項5】

半導体パッケージを形成する方法において、

電気相互接続フレームを形成するために<u>使用される</u>金属シートを準備する工程<u>(a)</u>と

前記金属シートの少なくとも一部を所定のパターンにエッチング処理する工程<u>(b)</u>と

前記工程(b)においてエッチング処理された金属シートを変形して、パッドを有する 平坦な上部電気コンタクトレベルと、パッドを有する平坦な下部電気コンタクトレベルと、を含む電気相互接続フレームを形成する工程であって、前記上部電気コンタクトレベルは、前記下部電気コンタクトレベルとオフセット状態、かつほぼ平行となるように構成される、前記電気相互接続フレームを形成する工程(c)と、

前記工程(c)において形成された前記電気相互接続フレームの前記上部電気コンタクトレベルの底面に第二の集積回路ダイを取付ける工程(d)と、

<u>前記工程(d)により取付けられた前記第二の集積回路ダイと</u>前記上部電気コンタクトレベルのパッドの底面とをワイヤにより電気的に接続する工程(e)と、

<u>前記工程(e)の後に、</u>前記上部電気コンタクトレベルの頂部面に第一の集積回路ダイを取付ける工程(f)と、

<u>前記工程(f)により取付けられた前記第一の集積回路ダイと</u>前記下部電気コンタクトレベルのパッド<u>とを</u>ワイヤ結合させる工程<u>(g)</u>と、

【発明の詳細な説明】

#### 【先奶の計画なる 【技術分野】

[0001]

からなる方法。

本発明は半導体パッケージに関し、より詳細には、マルチダイ半導体パッケージに関する。

## 【背景技術】

[0002]

マルチダイ(multi-die)半導体パッケージは複数の集積回路(IC)ダイを含む。幾らかのパッケージにおいて、パッケージ内の一つのダイの動作は、パッケージ内の他のダイの性能を干渉するかもしれない。例えば、内臓メモリを含むデジタル集積回路を備えたダイと、ラジオ周波数RF集積回路を備えたダイとを有するパッケージにおいて、内臓メモリはRF集積回路を備えたダイに近接した範囲内にホットスポットを発生する

10

20

30

•

40

かもしれない。これらのホットスポットは、RF集積回路のインダクタの性能を干渉し、 それによりRF集積回路の性能全体を低減することになるかもしれない。

#### 【発明の開示】

【発明が解決しようとする課題】

#### [0003]

マルチダイ半導体パッケージに対する改良された形態が必要とされている。

#### 【課題を解決するための手段】

#### [0004]

本発明の一態様において、半導体パッケージは<u>頂部面及び底面を有する平坦な上部</u>電気コンタクトレベル及び<u>頂部面及び底面を有する平坦な下部</u>電気コンタクトレベルを有する電気相互接続フレームを含む。<u>上部</u>電気コンタクトレベルは<u>下部</u>電気コンタクトレベルに平行、かつ該<u>下部</u>電気コンタクトレベルからオフセット状態にある。半導体パッケージはまた、<u>上部</u>電気コンタクトレベルの頂部面に取付けられる第一の集積回路ダイと、<u>上部電気コンタクトレベルの底面に取付けられる第二の集積回路ダイとを含む。半導体パッケージはまた、第二の集積回路ダイのパッドに接続される第一の端部と、<u>上部</u>電気コンタクトレベルの構造体の底面に接続される第二の端部とを有する第二の端部と、<u>下部</u>電気コンタクトレベルの頂部面に接続される第二の端部とを有する第一のワイヤを含む。</u>

#### [0005]

本発明の別の態様において、半導体パッケージは複数の第一のパッドを有するほぼ平坦な上部電気コンタクトレベルと、複数の第二のパッドを有するほぼ平坦な下部電気コンタクトレベルは下部電気コンタクトレベルに平行、かつ該下部電気コンタクトレベルからオフセット状態にある。上部及び下部電気コンタクトレベルのいずれも頂部面と底面の両方を備える。半導体パッケージはまた、頂部面および底面を備えた第一の集積回路ダイを含む。第一の集積回路ダイの底面は、上部電気コンタクトレベルの頂部面に取付けられる。第一の集積の頂部面は複数の第二のパッドにワイヤ接続される複数のパッドを有する。半導体パッケージはまた、頂部面および底面を備えた第二の集積回路ダイを含む。第二の集積回路ダイの底面は、上部電気コンタクトレベルの底面に取付けられる。第二の集積回路ダイの底面は、上部電気コンタクトレベルの底面に取付けられる。第二の集積回路ダイの頂部面は複数の第一のパッドにワイヤ接続される複数のパッドを有する。

## [0006]

本発明の別の態様において、半導体パッケージを形成する方法は、電気相互接続フレームを形成するために使用される金属シートを準備する工程(a)と、該金属シートの少なくとも一部を所定のパターンにエッチング処理する工程(b)とを含む。該方法はまた、工程(b)においてエッチング処理された金属シートを変形して、パッドを有する平坦な下部電気コンタクトレベルとを含む電気相互接続フレームを形成する工程(c)を含む。上部電気コンタクトレベルは、下部電気コンタクトレベルは、下部電気コンタクトレベルは、下部電気コンタクトレベルは、下部電気コンタクトレベルは、下部電気コンタクトレベルの底面に第二の集積回路ダイを取付ける工程(d)と、上部電気コンタクトレベルのパッドの底面と工程(d)により取付けられた第二の集積回路ダイとをワイヤにより電気的に接続する工程(e)を含む。該方法は更に、工程(e)の後に、該上部電気コンタクトレベルの頂部面に第一の集積回路ダイを取付ける工程(f)と、下部電気コンタクトレベルのパッドと工程(f)により取付けられた第一の集積回路ダイとをワイヤ結合させる工程(g)とを含む。

#### 【発明を実施するための最良の形態】

## [0007]

本発明は、添付した図面を参照してより理解され、かつその種々の目的、特徴及び利点は当業者に明らかにされるであろう。

#### [00008]

明記されていない限り、異なる図面における同一の符号の使用は、同一の部材を示す。

10

20

30

40

本発明を実施するための形態の詳細な説明を以下に記載する。詳細な説明は本発明を例示することを意図しており、本発明を制限するものと解釈されるべきではない。

#### [0009]

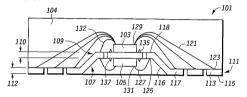

図1は、本発明に従うマルチダイ半導体パッケージの側方断面図である。パッケージ101は、非導電性の封入材料104中に封入される集積回路(IC)ダイ103及びICダイ105を含む。パッケージ101は、集積回路のダイ103及び105の間に導電性を提供し、かつパッケージ101の外側に導電構造体を提供するための電気相互接続フレーム107を含む。図示された実施形態において、パッケージ101は、マルチダイ、パーシャルアレイ、鉛フリーのパッケージである。

### [0010]

フレーム107は上部コンタクトレベル(contact 1 eve1)109及び下部コンタクトレベル111を含み、上部コンタクトレベル109は下部コンタクトレベル111を含み、上部コンタクトレベル109は面110内にほぼ配置されており、下部コンタクトレベル111は面112内にほぼ配置されている。フレーム107は複数の導電構造体を含み、一実施形態において該構造体は銅から形成されている。幾らかの実施形態において、フレーム107の一部は、例えばニッケル、銀、金又はパラジウムのような第二の金属でメッキされ得る。フレーム107は下部コンタクトレベル111の一部を構成する複数のパッド(例えば、113)を含む。これらのパッドの各々は、ダイ103又は105の信号又は出力パッドと、パッケージ101が取付けられている装置(例えば、プリント基板(図示しない))の外部導電構造体とを接続するための接触子として機能する。

#### [0011]

ダイ103は上部コンタクトレベル109の頂部面に取付けられ、かつダイ105は上部コンタクトレベル109の底面に取付けられる。例えば、121のようなワイヤは、ダイ103の頂部面に配置されたワイヤ結合パッド(例えば、129)に結合されるとともに下部コンタクトレベル111のパッド(例えば、113)の頂部面123に結合され、ダイ103のダイ結合パッドを下部コンタクトレベル111のパッドと電気的に接続する

### [0012]

フレーム107は差込構造体(例えば、116)を含み、各差込構造体は上部コンタクトレベル109に配置された上側部(例えば、118)と、下部コンタクトレベル111に配置された下側部(例えば、117)とを含む。ダイ105は上部コンタクトレベル109の底面に取付けられている。上側部(例えば、118)はダイ105の底面に配置されたダイ結合パッド(例えば、131)に結合されるワイヤ(例えば、127)を結合するための結合パッドとして機能する。差込構造体(例えば、116)の下側部(例えば、117)は、ダイ105の信号又は出力ダイパッド(例えば、131)をパッケージ101の外側の導電構造体と接続するためのパッケージ結合パッドとして機能する。図示された実施形態において、ダイ103の幾つかのダイ結合パッドは、ワイヤ(例えば、132)を介して差込構造体の上側部(例えば、118)に接続される。

#### [0013]

一実施形態において、ダイ103は、例えばベースバンドプロセッサ又はメモリのようなデジタルICを含む。ダイ105は携帯電話のトランスミッタ又はレシーバのようなRFICを含む。その他の実施形態において、ダイ105は他のタイプのアナログICを含み得るか、或いは、デジタルICを含み得る。フレーム107はダイ103及び105の間にRF遮蔽を提供する。

## [0014]

上部及び下部コンタクトレベルを備えた電気相互接続フレームを提供することにより、図1の実施形態に示されるように、ダイを(例えば、遮蔽の目的にて)フレームの反対側に配置することを可能にする一方で、フレームの一部が両方のダイに対して外部出力及び信号パッドとして機能することを可能にする。更に、上部及び下部コンタクトレベルを使

10

20

30

40

10

20

30

40

50

用することにより、マルチダイパッケージの高さを低減することも可能になる。また、上部及び下部コンタクトレベルを提供することにより、頂部ダイに連結されたワイヤと底部ダイに連結されたワイヤとが平行に進行する可能性が低く、かつ互いに近接した状態であるパッケージのワイヤ間の交差接続を低減することを助ける。

### [0015]

パッケージ101は、ダイ103を上部コンタクトレベル109の頂部面に取付けるために使用される接着剤を含む接着剤流出制御リング135を、該上部コンタクトレベル109の頂部面に含む。パッケージ101はまた、ダイ105を上部コンタクトレベル109の底面に取付けるために使用される接着剤を含む、第二の接着剤流出制御リング137を含む。その他の実施形態において、ダイは、ある種のダイ取付接着フィルムを用いることにより、又は上部コンタクトレベルに取付けられた別の型の介在構造体にダイを取付けることにより、上部コンタクトレベル109に取付けられ得る。

### [0016]

幾らかの実施形態において、ダイ103の頂部面からダイ105の底面までの距離は、各ダイの集積回路からの干渉を低減するように、0.5mm以下である。二つのコンタクトレベルを備えたフレームの相対向する側にダイを配置することにより、パッケージの高さを顕著に増大させることなく頂部ダイ103と底部ダイ105との活性面(図1の実施形態において、ダイのダイ結合パッドを備える面)の間の距離の増大を可能にする。

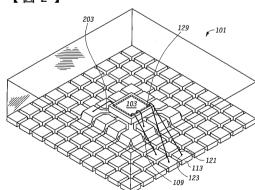

#### [0017]

図2は、パッケージ101の外側の線を備え、かつフレーム107の詳細を示すとともにダイ103がフレーム107に取付けられた位置を示すために透視して示されたパッケージ101の斜視図を示す。上部コンタクトレベル109はXフラッグ(X-flag)203を含み、ダイ103はXフラッグに取付けられている。図示された実施形態において、ダイ103及び105の接地用ダイパッドはXフラッグ203に連結されている。その他の実施形態において、上部コンタクトレベルは、例えばダイが固形のフラッグ等に取付けられているようなその他の形態及び/又は構造体を含み得る。

#### [0018]

図2に示されるように、下部コンタクトレベル111の周縁部の外側2列のパッド(例えば、113)は、それらの列のその他のパッドから電気的に絶縁されている。その他の実施形態において、これらの列のパッドの幾らかはこれらの列のその他のパッドと電気的に接続されている。ワイヤ121は、ダイ103の頂部面のダイ結合パッド129と、下部コンタクトレベル111のパッド113の頂部面123とに接続された状態にて示されている。簡略化するために、ダイ103の頂部面のダイ結合パッドと下部コンタクトレベル111のその他のパッドとを接続するためのその他のワイヤは図2においては示されていない。

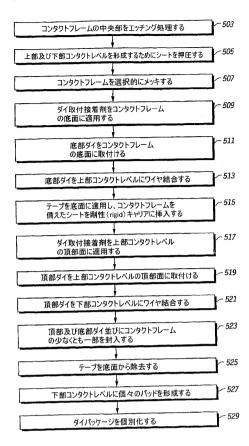

### [0019]

図5は、本発明に従うマルチダイ半導体パッケージを製造するための段階を記載するフローチャートである。図3及び4はそれぞれ、製造工程の異なる段階のパッケージ101を示す。図5の実施形態において、複数のパッケージのフレームは一枚の金属シートから形成される(図示しない)。幾らかの実施形態において、該シートは銅から形成されるとともに127乃至254µm(5乃至10ミル)の厚みを有する。パッケージを製造するための工程は、図5には示されていないその他の従来からの段階(例えば、洗浄段階)を含むこともできる。

## [0020]

503において、金属シートは各電気相互接続フレームの上部コンタクトレベル(例えば、109)の構造を定義するために、該フレームの中心部分に対応する位置がエッチング処理される。505において、上部コンタクトレベル及び下部コンタクトレベルを形成するために該シートが押圧される。押圧動作時に、該シートの一部が変形され、上側部(例えば、118)及び下側部(例えば、117)の間にオフセットを備えた差込構造体(例えば、116)が提供される。507において、ワイヤが結合されるフレームの一部(

10

20

30

40

50

例えば、107)は第二の金属(例えば、銀、金、ニッケル又はパラジウム)にて選択的にメッキされる。その他の実施形態において、シート全体がメッキされ得る。

#### [0021]

509において、接着剤が上部コンタクトレベル(例えば、109)の底面のダイ取付領域に適用され、511においてダイ取付領域に底部ダイ(例えば、105)が取付けられる。

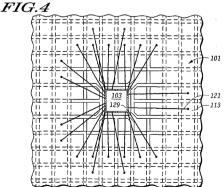

#### [0022]

513において、ワイヤ(例えば、127)は、底部ダイ(例えば、105)のダイ結合パッドに結合され、かつ差込構造体(例えば、116)の上側部(例えば、118)の底面に結合される。一実施形態において、これらのワイヤ(例えば、127)は、該ワイヤのループ高さを低減するために、底部ダイ(例えば、105)の結合パッド及び差込構造体(例えば、116)の上側部(例えば、118)に返し縫い(reversed stitch)にて結合される。図3は、パッケージ101が形成されるシートの一部を示す底面図である。

#### [0023]

5 1 5 において、テープ(図示しない)は、下部コンタクトレベル(例えば、1 1 1 )の底部側においてシートの底部を横切って適用される。テープは上部コンタクトレベル(例えば、1 0 9 )の底面、底部ダイ(例えば、1 0 5 )の底面又は底部ダイ(例えば、1 3 1 )に結合されるワイヤと接触しない。テープは、5 2 3 において、成形部の一部を封入するために提供される。幾らかの実施形態において、台(図示しない)がテープと底部ダイ(1 0 5 )の頂部面(ダイ結合パッド(例えば、1 3 1 )を備えたダイ1 0 5 の表面)との間に配置される。また、5 1 5 において、底部ダイ(例えば、1 0 5 )を支持するとともに底部ダイに結合されるワイヤ(例えば、1 2 7 )を保護するために、シートは隆起部を備えたキャリア(図示しない)に挿入される。

#### [0024]

5 1 7 において、接着剤は、上部コンタクトレベル(例えば、109)の頂部面のダイ取付領域に適用され、5 1 9 において、頂部ダイ(例えば、103)をダイ取付領域に取付ける。5 2 1 において、ワイヤ(例えば、121)は頂部ダイ(例えば、103)のダイ結合パッド(例えば、129)及び下部コンタクトレベル(例えば、111)のパッド(例えば、113)の頂部面に結合される。幾らかの実施形態において、頂部ダイのダイ結合パッドに結合されるワイヤは差込構造体(例えば、116)の上側部(例えば、118)の頂部面に結合され得る。図4は段階521における、パッケージ101が形成されるシートの部分の上面図である。下部コンタクトレベル111における点線は、段階527において除去されるパッド間の空間を示す。

## [0025]

5 2 3 において、第一および第二のダイ及びフレームの少なくとも一部は封入される。 5 2 5 において、テープがフレームの底部側から除去される。

527において、下部コンタクト層の一部は、下部コンタクトレベル(例えば、111)の個々のパッド(例えば、113)を形成するために除去される。図4を参照すると、一実施形態において、下部コンタクトレベル(例えば、111)のパッド(例えば、113)を形成するために点線の間に示されるシートの部分を除去するために該シートはエッチング処理される。その他の実施形態において、下部コンタクトレベルのパッド間の材料は、特定の深さにおいて、点線に沿ってフレームをソーで切断することにより除去され得る。529において、パッケージは、例えばソーにて切断する等により、互いに封入体を介して個別化(singulate)される。

## [0026]

その他の実施形態において、フリップ・チップ形態を備えたダイは上部コンタクトレベルの底面に取付けられ得る。これらの実施形態において、フリップ・チップ形態を備えたダイのソルダボール(sold ball)は差込構造体(例えば、116)の上側部(例えば、118)の底部側にはんだ付けされる。これらの実施形態において、差込構造体

(例えば、116)の上側部(例えば、118)は、図1に示される図面に対して、ダイ105の上に配置されるべく拡大される。

#### [0027]

別の実施形態において、電気相互接続フレームはその他の形態を備え得る、及び / 又はフレームのパッドは、その他の形状を備え得る、及び / 又はその他の方向に配置され得る。例えば、下部コンタクトレベルのパッドは斜めに配置され得る。また、その他の実施形態において、本明細書に示され、又は図示されるフレームはその他のタイプのパッケージにおいても使用され得る。

#### [0028]

本発明の特殊な実施形態を示すとともに記載してきたが、本明細書の示唆に基づいて、本発明及びそのより広い態様から逸脱することなく更なる変更及び修正がなされることは当業者に認識されるであろう。従って、添付された請求の範囲は、その範囲を包含するものであり、そのような変更及び修正の全ては、本発明の真の精神及び範囲内にある。

【図面の簡単な説明】

### [0029]

【図1】本発明に従うマルチダイ半導体パッケージの一実施形態の一部側方断面図である

【図2】本発明に従う頂部集積回路ダイ及び電気相互接続フレームを示すマルチダイ半導体パッケージの一実施形態の斜視図である。

【図3】マルチダイ半導体パッケージが本発明に従って形成されているシートの一実施形態の一部底面図である。

【図4】マルチダイ半導体パッケージが本発明に従って形成されているシートの一実施形 態の一部上面図である。

【図5】本発明に従うマルチダイ半導体パッケージを製造するための段階の一実施形態を記載するフローチャートである。

## 【図1】

FIG.1

【図2】

FIG.2

## 【図3】

FIG.3

# 【図4】

10

## 【図5】

## フロントページの続き

(72)発明者 ホン、デ ワイ.

アメリカ合衆国 78745 テキサス州 オースティン リトル テキサス レーン 401 ナンバー2131

(72)発明者 サファイ、ソラブ

アメリカ合衆国 78681 テキサス州 ラウンド ロック グレン キャニオン ドライブ 8315

審査官 今井 拓也

(56)参考文献 特開2001-127186(JP,A)

特開2002-026243(JP,A)

特開2002-353403(JP,A)

(58)調査した分野(Int.CI., DB名)

H01L 25/065

H01L 25/07

H01L 25/18