# (19) 대한민국특허청(KR)

# (12) 등록특허공보(B1)

(51) 국제특허분류(Int. Cl.)

**G06F 9/46** (2006.01) **G06F 12/02** (2018.01)

(52) CPC특허분류

**G06F 9/466** (2013.01) **G06F 12/0246** (2013.01)

(21) 출원번호 **10-2015-0076165**

(22) 출원일자 2015년05월29일

심사청구일자 2019년11월28일

(65) 공개번호 10-2016-0140061

(43) 공개일자 2016년12월07일

(56) 선행기술조사문헌

KR1020110067656 A\*

US04993029 A\*

US20080205145 A1\*

US20150095274 A1\*

\*는 심사관에 의하여 인용된 문헌

(45) 공고일자 2021년08월05일

(11) 등록번호 10-2285940

(24) 등록일자 2021년07월29일

(73) 특허권자

## 에스케이하이닉스 주식회사

경기도 이천시 부발읍 경충대로 2091

(72) 발명자

#### 조경래

경기도 화성시 동탄반석로 96 솔빛마을경남아너스 빌아파트 405동 1804호

(74) 대리인

김성남

전체 청구항 수 : 총 3 항

심사관 : 최정권

## (54) 발명의 명칭 데이터 처리 회로, 데이터 처리 회로를 포함하는 데이터 저장 장치 및 그것의 동작 방법

## (57) 요 약

데이터 처리 회로는 복수의 입력 비트 그룹들을 복수의 출력 비트 그룹들로 병렬적으로 각각 변환하도록 구성된 복수의 변환부들을 포함하되, 상기 변환부들 각각은 대응하는 입력 비트 그룹을 자신이 생성한 랜덤 패턴을 이용하여 대응하는 출력 비트 그룹으로 변환한다.

#### 대 표 도 - 도1

(52) CPC특허분류 *G06F 2207/581* (2013.01)

## 명 세 서

## 청구범위

#### 청구항 1

복수의 입력 비트 그룹들을 복수의 출력 비트 그룹들로 병렬적으로 각각 변환하도록 구성된 복수의 변환부들을 포함하되,

상기 변환부들 각각은 시드에 기반하여 랜덤 패턴을 생성하고, 대응하는 입력 비트 그룹을 상기 랜덤 패턴을 이용하여 대응하는 출력 비트 그룹으로 변환하고,

상기 시드는 상기 출력 비트 그룹들이 저장될 메모리 영역의 어드레스 오프셋에 대응하는 데이터 처리 회로.

### 청구항 2

◈청구항 2은(는) 설정등록료 납부시 포기되었습니다.◈

제1항에 있어서,

상기 입력 비트 그룹들은 복수의 입력 비트들을 포함하고,

상기 입력 비트들은 상기 변환부들로 병렬적으로 입력되는 데이터 처리 회로.

#### 청구항 3

◈청구항 3은(는) 설정등록료 납부시 포기되었습니다.◈

제1항에 있어서.

상기 출력 비트 그룹들은 복수의 출력 비트들을 포함하고,

상기 변환부들은 상기 출력 비트들을 병렬적으로 출력하는 데이터 처리 회로.

#### 청구항 4

◈청구항 4은(는) 설정등록료 납부시 포기되었습니다.◈

제1항에 있어서,

상기 변환부들 각각은 상기 랜덤 패턴을 생성하도록 선형 되먹임 시프트 레지스터(이하, LFSR; Linear feedback shift register)를 포함하고,

상기 변환부들에 포함된 LFSR들은 적어도 두 개의 특성 다항식들에 대응하는 데이터 처리 회로.

#### 청구항 5

◈청구항 5은(는) 설정등록료 납부시 포기되었습니다.◈

제1항에 있어서,

상기 변환부들 각각은 상기 랜덤 패턴을 생성하도록 구성된 LFSR를 포함하고,

상기 LFSR은 직렬 연결된 N개의 레지스터들로 구성되고  $2^{N}-1$ 의 주기를 가지는 시퀀스를 출력하는 데이터 처리회로.

## 청구항 6

◈청구항 6은(는) 설정등록료 납부시 포기되었습니다.◈

제1항에 있어서,

상기 변환부들 각각은 상기 랜덤 패턴을 생성하도록 구성된 LFSR를 포함하고,

상기 LFSR은 직렬 연결된 N개의 레지스터들로 구성되고, 상기 N은 상기 변환부들 각각으로 입력되는 비트 수의 배수인 데이터 처리 회로.

#### 청구항 7

◈청구항 7은(는) 설정등록료 납부시 포기되었습니다.◈

제1항에 있어서.

상기 변환부들 각각은,

상기 시드에 응답하여 상기 랜덤 패턴을 생성하도록 구성된 랜덤 패턴 생성부; 및

상기 대응하는 입력 비트 그룹과 상기 랜덤 패턴을 논리 연산하여, 상기 대응하는 출력 비트 그룹을 생성하도록 구성된 연산부를 포함하는 데이터 처리 회로.

#### 청구항 8

복수의 라이트 비트 그룹들을 복수의 변환 라이트 비트 그룹들로 병렬적으로 각각 변환하고, 상기 변환 라이트 비트 그룹들을 병렬적으로 각각 출력하는 복수의 변환부들; 및

상기 변환 라이트 비트 그룹들을 입력받고, 메모리 영역에 저장하도록 구성된 불휘발성 메모리 장치를 포함하되.

상기 변환부들 각각은 상기 메모리 영역의 어드레스 오프셋에 대응하는 시드에 기반하여 랜덤 패턴을 생성하고, 상기 랜덤 패턴에 근거하여 대응하는 라이트 비트 그룹을 대응하는 변환 라이트 비트 그룹으로 변환하는 데이터 저장 장치.

#### 청구항 9

◈청구항 9은(는) 설정등록료 납부시 포기되었습니다.◈

제8항에 있어서,

상기 라이트 비트 그룹들은 복수의 라이트 비트들을 포함하고,

상기 라이트 비트들은 상기 변환부들로 병렬적으로 입력되는 데이터 저장 장치.

## 청구항 10

◈청구항 10은(는) 설정등록료 납부시 포기되었습니다.◈

제8항에 있어서,

상기 변환 라이트 비트 그룹들은 복수의 변환 라이트 비트들을 포함하고,

상기 변환부들은 상기 변환 라이트 비트들을 병렬적으로 출력하는 데이터 저장 장치.

## 청구항 11

◈청구항 11은(는) 설정등록료 납부시 포기되었습니다.◈

제8항에 있어서,

상기 변환부들 각각은,

상기 시드에 응답하여 랜덤 패턴을 생성하도록 구성된 랜덤 패턴 생성부; 및

자신에게 대응하는 라이트 비트 그룹과 상기 랜덤 패턴을 논리 연산하여, 자신에게 대응하는 변환 라이트 비트 그룹을 생성하도록 구성된 연산부를 포함하는 데이터 저장 장치.

## 청구항 12

◈청구항 12은(는) 설정등록료 납부시 포기되었습니다.◈

제11항에 있어서,

상기 랜덤 패턴 생성부는 상기 랜덤 패턴을 생성하도록 구성된 LFSR를 포함하고,

상기 변환부들에 포함된 LFSR들은 적어도 두 개의 특성 다항식들에 대응하는 데이터 저장 장치.

#### 청구항 13

◈청구항 13은(는) 설정등록료 납부시 포기되었습니다.◈

제11항에 있어서,

상기 랜덤 패턴 생성부는 상기 랜덤 패턴을 생성하도록 구성된 LFSR를 포함하고

상기 LFSR은 직렬 연결된 N개의 레지스터들로 구성되고,  $2^{N}$ -1의 주기를 가지는 시퀀스를 출력하는 데이터 저장 장치.

## 청구항 14

◈청구항 14은(는) 설정등록료 납부시 포기되었습니다.◈

제11항에 있어서,

상기 랜덤 패턴 생성부는 상기 랜덤 패턴을 생성하도록 구성된 LFSR를 포함하고

상기 LFSR은 직렬 연결된 N개의 레지스터들로 구성되고, 상기 N은 상기 변환부들 각각으로 입력되는 비트 수의 배수인 데이터 저장 장치.

#### 청구항 15

◈청구항 15은(는) 설정등록료 납부시 포기되었습니다.◈

제8항에 있어서,

상기 불휘발성 메모리 장치는 저장된 변환 라이트 비트 그룹들을 복수의 리드 비트 그룹들로리드하고, 상기 리드 비트 그룹들을 병렬적으로 출력하고,

상기 변환부들은 상기 리드 비트 그룹들을 복수의 역변환 리드 비트 그룹들로 병렬적으로 각각 역변환하는 데이 터 저장 장치.

#### 청구항 16

메모리 영역의 어드레스 오프셋에 대응하는 시드에 기반하여 서로 다른 복수의 랜덤 패턴들을 각각 생성하고 상기 랜덤 패턴들에 근거하여 복수의 라이트 비트 그룹들을 복수의 변환 라이트 비트 그룹들로 병렬적으로 각각 변환하는 단계;

상기 변환 라이트 비트 그룹들을 불휘발성 메모리 장치로 병렬적으로 전송하는 단계; 및

상기 변환 라이트 비트 그룹들을 상기 메모리 영역에 저장하는 단계를 포함하는 데이터 저장 장치의 동작 방법.

#### 청구항 17

◈청구항 17은(는) 설정등록료 납부시 포기되었습니다.◈

제16항에 있어서,

상기 변환하는 단계 이전에, 상기 라이트 비트 그룹들을 병렬적으로 수신하는 단계를 더 포함하되,

상기 라이트 비트 그룹들은 복수의 라이트 비트들을 포함하고,

상기 라이트 비트들은 병렬적으로 수신되는 데이터 저장 장치의 동작 방법.

#### 청구항 18

◈청구항 18은(는) 설정등록료 납부시 포기되었습니다.◈

제16항에 있어서,

상기 변환 라이트 비트 그룹들은 복수의 변환 라이트 비트들을 포함하고,

상기 변환 라이트 비트들은 상기 불휘발성 메모리 장치로 병렬적으로 전송되는 데이터 저장 장치의 동작 방법.

#### 청구항 19

◈청구항 19은(는) 설정등록료 납부시 포기되었습니다.◈

제16항에 있어서,

상기 변환하는 단계는,

상기 시드에 응답하여 상기 서로 다른 복수의 랜덤 패턴들을 생성하는 단계; 및

상기 라이트 비트 그룹들을 상기 랜덤 패턴들과 각각 논리 연산하여, 상기 변환 라이트 비트 그룹들을 생성하는 단계를 포함하는 데이터 저장 장치의 동작 방법.

#### 청구항 20

◈청구항 20은(는) 설정등록료 납부시 포기되었습니다.◈

제16항에 있어서,

저장된 복수의 변환 라이트 비트 그룹들을 복수의 리드 비트 그룹들로 리드하는 단계;

상기 리드 비트 그룹들을 컨트롤러로 병렬적으로 전송하는 단계; 및

상기 리드 비트 그룹들을 복수의 역변환 리드 비트 그룹들로 병렬적으로 각각 역변환하는 단계를 더 포함하는 데이터 저장 장치의 동작 방법.

#### 발명의 설명

### 기 술 분 야

[0001] 본 발명은 데이터 저장 장치에 관한 것으로, 더욱 상세하게는 데이터를 랜더마이징하여 저장하는 데이터 저장 장치에 관한 것이다.

### 배경기술

- [0002] 데이터 저장 장치는 외부 장치의 라이트 요청에 응답하여, 외부 장치로부터 제공된 데이터를 저장하도록 구성될 수 있다. 또한, 데이터 저장 장치는 외부 장치의 리드 요청에 응답하여, 저장된 데이터를 외부 장치로 제공하도록 구성될 수 있다. 외부 장치는 데이터를 처리할 수 있는 전자 장치로서, 컴퓨터, 디지털 카메라 또는 휴대폰 등을 포함할 수 있다. 데이터 저장 장치는 외부 장치에 내장되어 동작하거나, 분리 가능한 형태로 제작되어 외부 장치에 연결됨으로써 동작할 수 있다.

- [0003] 데이터 저장 장치는 PCMCIA (Personal Computer Memory Card International Association) 카드, CF(Compact Flash) 카드, 스마트 미디어 카드, 메모리 스틱, 다양한 멀티 미디어 카드(MMC, eMMC, RS-MMC, MMC-micro), SD(Secure Digital) 카드(SD, Mini-SD, Micro-SD), UFS(Universal Flash Storage) 또는 SSD(Solid State Drive) 등을 포함할 수 있다.

- [0004] 데이터 저장 장치는 데이터를 저장하기 위해 불휘발성 메모리 장치를 포함할 수 있다. 불휘발성 메모리 장치는 전원이 인가되지 않더라도 저장된 데이터를 유지할 수 있다. 불휘발성 메모리 장치는 낸드 플래시(NAND Flash) 또는 노어 플래시(NOR Flash)와 같은 플래시 메모리 장치, FeRAM(Ferroelectrics Random Access Memory), PCRAM(Phase-Change Random Access Memory), MRAM(Magnetic Random Access Memory) 등을 포함할 수 있다.

## 발명의 내용

## 해결하려는 과제

[0005] 본 발명의 실시 예는 데이터를 랜더마이징함으로써 데이터 신뢰성을 보장할 수 있는 데이터 저장 장치를 제공하는데 있다.

#### 과제의 해결 수단

- [0006] 본 발명의 실시 예에 따른 데이터 처리 회로는 복수의 입력 비트 그룹들을 복수의 출력 비트 그룹들로 병렬적으로 각각 변환하도록 구성된 복수의 변환부들을 포함하되, 상기 변환부들 각각은 대응하는 입력 비트 그룹을 자신이 생성한 랜덤 패턴을 이용하여 대응하는 출력 비트 그룹으로 변환할 수 있다.

- [0007] 본 발명의 실시 예에 따른 데이터 저장 장치는 복수의 라이트 비트 그룹들을 복수의 변환 라이트 비트 그룹들로 병렬적으로 각각 변환하고, 상기 변환 라이트 비트 그룹들을 병렬적으로 각각 출력하는 복수의 변환부들, 및 상기 변환 라이트 비트 그룹들을 입력받고, 저장하도록 구성된 불휘발성 메모리 장치를 포함할 수 있다.

- [0008] 본 발명의 실시 예에 따른 데이터 저장 장치의 동작 방법은 복수의 라이트 비트 그룹들을 복수의 변환 라이트 비트 그룹들로 병렬적으로 각각 변환하는 단계, 상기 변환 라이트 비트 그룹들을 불휘발성 메모리 장치로 병렬적으로 전송하는 단계 및 상기 변환 라이트 비트 그룹들을 저장하는 단계를 포함할 수 있다.

#### 발명의 효과

[0009] 본 발명의 실시 예에 따른 데이터 저장 장치는 데이터 신뢰성을 보장할 수 있다.

## 도면의 간단한 설명

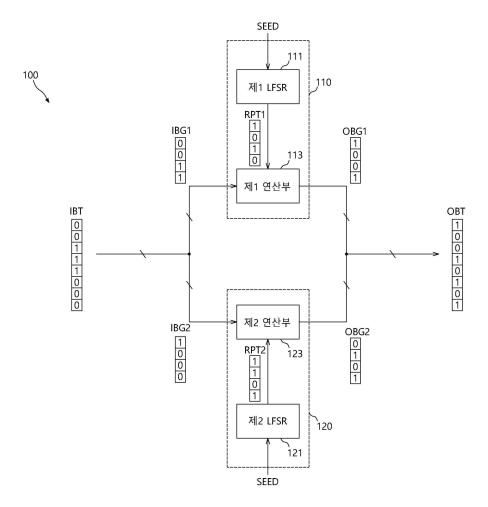

[0010] 도1은 본 발명의 실시 예에 따른 데이터 처리 회로를 예시적으로 도시한 블록도,

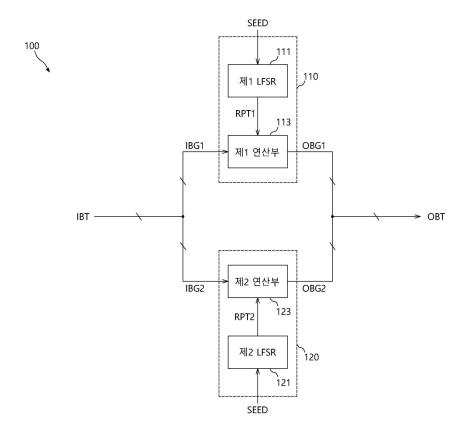

도2는 LFSR의 구조를 예시적으로 도시한 도면,

도3은 도1의 데이터 처리 회로가 병렬로 입력된 입력 비트들을 변환하는 방법을 예시적으로 설명하기 위한 도면.

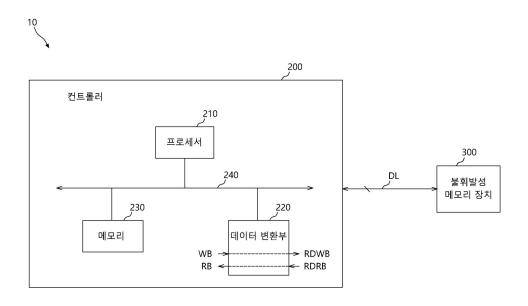

도4는 본 발명의 실시 예에 따른 데이터 저장 장치를 예시적으로 도시하는 블록도,

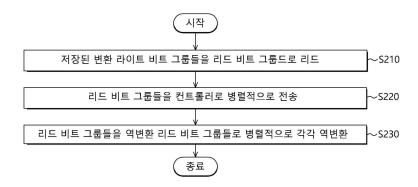

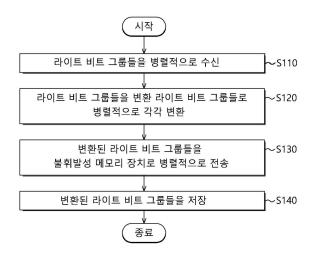

도5 본 발명의 실시 예에 따른 도4의 데이터 저장 장치의 동작 방법을 설명하기 위한 순서도,

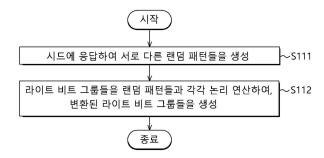

도6은 본 발명의 실시 예에 따라 도4의 데이터 처리부가 라이트 비트 그룹들을 변환 라이트 비트 그룹들로 병렬 적으로 변환하는 방법을 설명하기 위한 순서도,

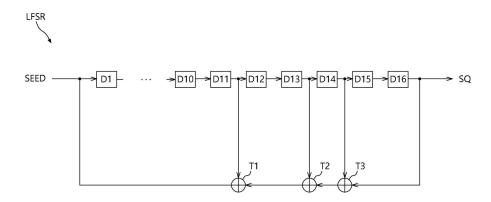

도7은 본 발명의 실시 예에 따른 도4의 데이터 저장 장치의 동작 방법을 설명하기 위한 순서도이다.

## 발명을 실시하기 위한 구체적인 내용

- [0011] 이하, 도면들을 참조하여 본 발명의 실시 예에 대해 상세히 설명하기로 한다.

- [0012] 도1은 본 발명의 실시 예에 따른 데이터 처리 회로(100)를 예시적으로 도시한 블록도이다.

- [0013] 도1을 참조하면, 데이터 처리 회로(100)는 복수의 입력 비트들(IBT)을 복수의 출력 비트들(OBT)로 변환하고, 출력 비트들(OBT)을 출력할 수 있다. 데이터 처리 회로(100)는 입력 비트들(IBT)을 랜더마이징함으로써 출력 비트들(OBT)을 생성할 수 있다. 즉, 데이터 처리 회로(100)는 데이터 간 영향을 최소화시켜 데이터 변형이 억제되도록, 입력 비트들(IBT)의 패턴을 랜덤화시켜 출력 데이터를 생성할 수 있다.

- [0014] 복수의 입력 비트들(IBT)은 데이터 처리 회로(100)로 병렬적으로 입력될 수 있다. 데이터 처리 회로(100)로 병렬적으로 입력되는 비트들의 총 개수는 데이터가 저장될 메모리 장치(미도시)의 규격에 따라, 예를 들어, 8개, 16개 등일 수 있다.

- [0015] 복수의 입력 비트들(IBT)은 복수의 입력 비트 그룹들, 예를 들어, 제1 및 제2 입력 비트 그룹들(IBG1, IBG2)로 그룹지어질 수 있다. 복수의 입력 비트들(IBT) 중, 예를 들어, 상위 절반의 비트들과 하위 절반의 비트들은 제1 및 제2 입력 비트 그룹들(IBG1, IBG2)로 각각 그룹지어질 수 있다. 그러나, 복수의 입력 비트들(IBT)이 그룹지 어지는 방식은 이에 한정되지 않을 것이다.

- [0016] 데이터 처리 회로(100)는 복수의 변환부들, 예를 들어, 제1 및 제2 변환부들(110, 120)을 포함할 수 있다.

- [0017] 제1 및 제2 입력 비트 그룹들(IBG1, IBG2)은 제1 및 제2 변환부들(110, 120)로 병렬적으로 각각 입력될 수

있다. 즉, 제1 입력 비트 그룹(IBG1)은 제1 변환부(110)로 입력될 수 있고, 실질적으로 동시에, 제2 입력 비트 그룹(IBG2)은 제2 변환부(120)로 입력될 수 있다. 제1 및 제2 입력 비트 그룹들(IBG1, IBG2)에 포함된 복수의 입력 비트들(IBT)은 제1 및 제2 변환부들(110, 120)로 병렬적으로 입력될 수 있다.

- [0018] 제1 및 제2 변환부들(110, 120)은 제1 및 제2 입력 비트 그룹들(IBG1, IBG2)을 제1 및 제2 출력 비트 그룹들 (OBG1, OBG2)로 병렬적으로 각각 변환할 수 있다. 즉, 제1 변환부(110)는 제1 입력 비트 그룹(IBG1)을 제1 출력 비트 그룹(OBG1)으로 변환할 수 있고, 실질적으로 동시에, 제2 변환부(120)는 제2 입력 비트 그룹(IBG2)을 제2 출력 비트 그룹(OBG2)으로 변환할 수 있다.

- [0019] 제1 및 제2 변환부들(110, 120)은 제1 및 제2 출력 비트 그룹들(OBG1, OBG2)을 병렬적으로 각각 출력할 수 있다. 제1 및 제2 변환부들(110, 120)은 제1 및 제2 출력 비트 그룹들(OBG1, OBG2)에 포함된 출력 비트들(OBT)을 병렬적으로 출력할 수 있다.

- [0020] 제1 변환부(110)는 제1 랜덤 패턴 생성부(111) 및 제1 연산부(113)를 포함할 수 있다.

- [0021] 제1 랜덤 패턴 생성부(111)는 시드(SEED)에 응답하여 제1 랜덤 패턴(RPT1)을 생성할 수 있다. 제1 랜덤 패턴 생성부(111)는 시드(SEED)에 응답하여 제1 랜덤 패턴(RPT1)을 생성하기 위한 제1 선형 되먹임 시프트 레지스터(이하, 제1 LFSR; Linear feedback shift register)로 구성될 수 있다.

- [0022] 제1 연산부(113)는 제1 입력 비트 그룹(IBG1)과 제1 랜덤 패턴(RPT1)을 논리 연산하여, 제1 출력 비트 그룹 (0BG1)을 생성할 수 있다. 제1 연산부(113)의 논리 연산은, 예를 들어, 배타적 오어일 수 있다.

- [0023] 제2 변환부(120)는 제2 랜덤 패턴 생성부(121) 및 제2 연산부(123)를 포함할 수 있다.

- [0024] 제2 랜덤 패턴 생성부(121)는 시드(SEED)에 응답하여 제2 랜덤 패턴(RPT2)을 생성할 수 있다. 제2 랜덤 패턴 생성부(121)는 시드(SEED)에 응답하여 제2 랜덤 패턴(RPT2)을 생성하기 위한 제2 선형 되먹임 시프트 레지스터(이하, 제2 LFSR)로 구성될 수 있다.

- [0025] 제2 연산부(123)는 제2 입력 비트 그룹(IBG2)과 제2 랜덤 패턴(RPT2)을 논리 연산하여, 제2 출력 비트 그룹 (0BG2)을 생성할 수 있다. 제2 연산부(123)의 논리 연산은, 예를 들어, 배타적 오어일 수 있다.

- [0026] 본 발명의 실시 예에 따라, 제1 및 제2 LFSR들(111, 121)은 서로 다른 특성 다항식들에 대응할 수 있다. 한편, 본 발명의 실시 예에 따라, 데이터 처리 회로(100)가 3개 이상의 LFSR들을 포함하는 경우, LFSR들은 적어도 두 개의 특성 다항식들에 대응할 수 있다.

- [0027] 본 발명의 실시 예에 따라, 제1 및 제2 LFSR들(111, 121) 각각은 최대 길이 시퀀스를 생성할 수 있다.

- [0028] 본 발명의 실시 예에 따라, 제1및 제2 LFSR들(111, 121) 각각의 특성 다항식의 차수는 제1 및 제2 변환부들 (110, 120) 각각으로 입력되는 비트 수의 배수일 수 있다. 본 발명의 실시 예에 따라, 제1및 제2 LFSR들(111, 121) 각각의 특성 다항식의 차수는 제1 및 제2 변환부들(110, 120)로 입력되는 총 비트 수의 배수일 수 있다.

- [0029] 실시 예에 따라, 데이터 처리 회로(100)는 상술된 데이터 변환 과정을 역으로 진행함으로써 변환된 데이터를 역 변환할 수 있다. 즉, 출력 비트들(OBT)이 제1 및 제2 변환부들(110, 120)로 병렬적으로 입력되면, 제1 및 제2 변환부들(110, 120)은 시드(SEED)에 응답하여 출력 비트들(OBT)이 그룹지어진 제1 및 제2 출력 비트 그룹들 (OBG1, OBG2)을 제1 및 제2 입력 비트 그룹들(IBG1, IBG2)로 병렬적으로 각각 변환할 수 있다. 그리고, 제1 및 제2 변환부들(110, 120)은 제1 및 제2 입력 비트 그룹들(IBG1, IBG2), 즉, 입력 비트들(IBT)을 병렬적으로 출력할 수 있다.

- [0030] 도1은 데이터 처리 회로(100)가 2개의 변환부들(110, 120)을 포함하는 것으로 도시하나, 데이터 처리 회로(10 0)에 포함되는 변환부들의 개수는 이에 제한되지 않는다. 한편, 데이터 처리 회로(100)에 포함되는 변환부들의 개수는 입력 비트들(IBT)이 입력 비트 그룹으로 그룹지어지는 단위 비트 수를 결정할 수 있다. 예를 들어, 데이터 처리 회로(100)에 포함되는 변환부들의 개수가 N개일 때, K개의 입력 비트들(IBT)이 하나의 입력 비트 그룹으로 그룹지어지는 단위 비트 수는 K/N개일 것이다. 그리고, 출력 비트 그룹의 비트 수는 입력 비트 그룹의 비트 수와 동일한 개수로 생성될 것이다.

- [0031] 도2는 LFSR의 구조를 예시적으로 도시한 도면이다. 도2는, 예시적으로, 피보나치 구현(Fibonacci implementation)의 LFSR를 도시하나, 본 발명의 실시 예는 이에 제한되지 않고, 다른 방식의 LFSR, 예를 들어, 갈루아 구현(Galois implementation)의 LFSR로 구현될 수도 있다.

- [0032] 도2를 참조하면, LFSR은 직렬로 연결된 16개의 레지스터들(D1~D16)을 포함할 수 있고, 최초의 레지스터(D1)로부터 시드(SEED)를 입력받고, 클럭 신호(미도시)가 활성화될 때마다 레지스터들(D1~D16)에 저장된 값을 그 다음 레지스터로 쉬프트시키고, 최후의 레지스터(D16)로부터 시퀀스(SQ)를 출력할 수 있다. 탭으로 지정된 레지스터 들(예를 들어, D16, D14, D13, D11)의 출력은 배타적 오어들(T1~T3)을 통해 순차적으로 배타적 오어 연산된 뒤 최초의 레지스터(D1)로 피드백될 수 있다. LFSR은 랜덤 패턴(예를 들어, 도1의 제1 및 제2 랜덤 패턴들(RPT1, RPT2))를 생성하기 위해서 사용될 수 있다. 예를 들어, LFSR은 클럭 신호가 활성화될 때마다 레지스터들 중 선택된 K개의 레지스터들에 저장된 값에 근거하여 K비트의 랜덤 패턴을 생성할 수 있다.

- [0033] 한편, N개의 레지스터들로 구성되는 LFSR은 아래와 같은 특성 다항식과 대응될 수 있다.

- [0034]  $f(x) = x^{N} + a_{(N-1)}x^{(N-1)} + a_{(N-2)}x^{(N-2)} + \dots + a_{1}x + 1$

- [0035] 상기 식에서 계수들(a<sub>1</sub>, a<sub>2</sub>, ..., a<sub>(N-1)</sub>)은 LFSR의 탭의 위치에 따라 0 또는 1일 수 있다. 예를 들어, 도2에 도 시된 LFSR은 아래와 같은 특성 다항식과 대응될 수 있다.

- [0036] f(x) = x16 + x14 + x13 + x11 + 1

- [0037] 또한, 도2에 도시된 LFSR은 탭의 위치를 가리키는 탭 수열 [16, 14, 13, 11]과 대응될 수 있다.

- [0038] 한편, 클럭 신호의 활성화에 응답하여 최후의 레지스터(D16)로부터 출력되는 값(SQ), 즉, LFSR의 출력은 일정한 주기로 반복되는 시퀀스를 형성할 수 있다..

- [0039] LFSR의 특성 다항식이 원시 다항식일 때, LFSR은 시퀀스(SQ)를 최대 길이로 출력할 수 있다. N개의 레지스터들로 구성되는 LFSR가 최대 길이로 시퀀스(SQ)를 출력할 때, 그 시퀀스의 길이는 2<sup>N</sup>-1일 수 있다. 다른 말로하면, LFSR가 최대 길이로 시퀀스(SQ)를 출력할 때, 그 시퀀스(SQ)는 2<sup>N</sup>-1의 주기로 반복되어 출력될 수 있다. LFSR가 최대 길이로 시퀀스(SQ)를 출력할 때, LFSR로부터 출력되는 시퀀스(SQ)는 "최대 길이 시퀀스(Maximum Length Sequence)" 또는 "M-시퀀스"라고 정의될 수 있다. M-시퀀스는 LFSR의 모든 레지스터들에 0이 저장되는 상태를 제외한 나머지 2<sup>N</sup>-1개의 상태들에서 출력되는 시퀀스일 것이다.

- [0040] 예를 들어, 4개의 탭을 포함하되 M-시퀀스를 출력하는 LFSR의 탭 수열들은 다음과 같다.

- [0041] [16, 15, 13, 4], [16, 15, 12, 10], [16, 15, 12, 1], [16, 15, 10, 4], [16, 15, 9, 6], [16, 15, 9, 4], [16, 15, 7, 2], [16, 15, 4, 2], [16, 14, 13, 11], [16, 14, 13, 5], [16, 14, 12, 7], [16, 14, 11, 7], [16, 14, 9, 7], [16, 14, 9, 4], [16, 14, 8, 3], [16, 13, 12, 11], [16, 13, 12, 7], [16, 13, 11, 6], [16, 13, 9, 6], [16, 13, 6, 4], [16, 12, 9, 7], [16, 12, 9, 6], [16, 11, 10, 5], [16, 11, 9, 8], [16, 11, 9, 7], [16, 10, 9, 6].

- [0042] M-시퀀스의 대표적인 특징으로서, 첫째로, 상술한 바와 같이, M-시퀀스는 2<sup>N</sup>-1의 최대 주기를 가질 수 있다. 그리고, 둘째로, M-시퀀스는 정확히 2<sup>(N-1)</sup>개의 "1"과 2<sup>(N-1)</sup>-1개의 "0"을 포함할 수 있다. 따라서, 데이터를 변환할때 M-시퀀스를 출력하는 LFSR로부터 생성되는 랜덤 패턴을 이용하는 경우, 데이터의 랜덤성 향상에 도움이 될수 있다.

- [0043] 다시 도1을 참조하면, 제1 및 제2 랜덤 패턴 생성부들(111, 121)은 제1 및 제2 LFSR들로 각각 구현될 수 있다.

- [0044] 본 발명의 실시 예에 따르면, 제1 및 제2 LFSR들(111, 121)은 서로 다른 특성 다항식들에 대응할 수 있다. 제1 및 제2 LFSR들(111, 121)은 서로 다른 특성 다항식들에 대응할 경우, 동일한 시드(SEED)에 응답하여 서로 다른 시퀀스들을 각각 출력할 수 있다. 또한, 제1 및 제2 LFSR들(111, 121)은 서로 다른 특성 다항식들에 대응할 경우, 동일한 시드(SEED)에 응답하여 서로 다른 랜덤 패턴들(RPT1, RPT2)을 각각 출력할 수 있다.

- [0045] 본 발명의 실시 예에 따르면, 제1 및 제2 LFSR들(111, 121) 각각의 특성 다항식의 차수는 제1 및 제2 변환부들 (110, 120) 각각으로 입력되는 비트 수의 배수일 수 있다. 다른 말로 하면, 제1 및 제2 LFSR들 각각이 N개의 레지스터들로 구성될 때, N은 제1 및 제2 변환부들(110, 120) 각각으로 입력되는 비트 수, 예를 들어, 제1 입력 비트 그룹(IBG1)에 포함된 비트 수의 배수일 수 있다.

- [0046] 본 발명의 실시 예에 따르면, 제1및 제2 LFSR들(111, 121) 각각의 특성 다항식의 차수는 제1 및 제2 변환부들 (110, 120)로 입력되는 총 비트 수의 배수일 수 있다. 다른 말로 하면, 제1 및 제2 LFSR들 각각이 N개의 레지스

터들로 구성될 때, N은 제1 및 제2 변환부들(110, 120)로 입력되는 총 비트 수, 예를 들어, 입력 비트들(IBT)에 포함된 비트 수의 배수일 수 있다.

- [0047] 본 발명의 실시 예에 따르면, 제1 및 제2 LFSR들 각각은 M-시퀀스를 출력할 수 있다. 다른 말로 하면, 제1 및 제2 LFSR들(111, 121) 각각은, N개의 레지스터들로 구성될 때 2<sup>N</sup>-1의 주기를 가지는 시퀀스를 출력할 수 있다.

- [0048] 도3은 도1의 데이터 처리 회로(100)가 병렬로 입력된 입력 비트들을 변환하는 방법을 예시적으로 설명하기 위한 도면이다. 도3을 참조하면, 8비트의 입력 비트들(IBT) 중 상위 4 비트와 하위 4비트가 제1 및 제2 입력 비트 그룹들(IBG1, IBG2)로 각각 그룹지어지는 경우를 도시한다.

- [0049] 입력 비트들(IBT)은 데이터 처리 회로(100)로 병렬적으로 입력될 수 있다. 제1 및 제2 입력 비트 그룹들(IBG1, IBG2)은 제1 및 제2 변환부들(110, 120)로 병렬적으로 각각 입력될 수 있다.

- [0050] 제1 및 제2 LFSR들(111, 121)은 시드(SEED)에 응답하여 서로 다른 제1 및 제2 랜덤 패턴들(RPT1, RPT2)을 생성할 수 있다. 제1 연산부(113)는 제1 입력 비트 그룹(IBG1)과 제1 랜덤 패턴(RPT1)을 대응하는 비트들에 대해 서로 배타적 오어 연산하여 제1 출력 비트 그룹(OBG1)을 생성하고, 실질적으로 동시에, 제2 연산부(123)는 제2 입력 비트 그룹(IBG2)과 제2 랜덤 패턴(RPT2)을 대응하는 비트들에 대해 서로 배타적 오어 연산하여 제2 출력 비트 그룹(OBG2)을 생성할 수 있다.

- [0051] 제1 및 제2 출력 비트 그룹들(OBG1, OBG2)은 제1 및 제2 변환부들(110, 120)로부터 병렬적으로 출력될 수 있다. 제1 및 제2 출력 비트 그룹들(OBG1, OBG2)에 포함된 출력 비트들(OBT)은 데이터 변환 회로(100)로부터 병렬적으로 출력될 수 있다.

- [0052] 도4는 본 발명의 실시 예에 따른 데이터 저장 장치(10)를 예시적으로 도시하는 블록도이다.

- [0053] 데이터 저장 장치(10)는 컨트롤러(200) 및 불휘발성 메모리 장치(300)를 포함할 수 있다.

- [0054] 컨트롤러(200)는 프로세서(210), 데이터 처리부(220) 및 메모리(230)를 포함할 수 있다. 컨트롤러(200)의 내부 구성 유닛들은 내부 버스(240)를 통해 서로 연결되고 통신할 수 있다.

- [0055] 프로세서(210)는 데이터 저장 장치(10)의 제반 동작을 제어할 수 있다. 프로세서(210)는 컨트롤러(200)의 내부 구성 유닛들이 설정된 특정 기능들을 수행하도록 각각 제어할 수 있다. 프로세서(210)는 외부 장치의 라이트 요청 또는 리드 요청에 응답하여 불휘발성 메모리 장치(300)의 라이트 동작 또는 리드 동작을 제어할 수 있다.

- [0056] 데이터 처리부(220)는 불휘발성 메모리 장치(300)에 저장될 라이트 비트들(WB)을 변환 라이트 비트들(RDWB)로 변환하고, 불휘발성 메모리 장치(300)로부터 리드된 리드 비트들(RDRB)을 역변환 리드 비트들(RB)로 역변환할 수 있다. 만일 변환 라이트 비트들(RDWB)과 리드 비트들(RDRB)이 동일한 경우, 역변환 리드 비트들(RB)은 라이트 비트들(WB)과 동일한 값으로 생성될 것이다.

- [0057] 데이터 처리부(220)는 복수의 라이트 비트들(WB)이 그룹지어진 복수의 라이트 비트 그룹들을 복수의 변환 라이트 비트 그룹들로 병렬적으로 각각 변환하고, 복수의 변환 라이트 비트 그룹들을 병렬적으로 각각 출력하는 복수의 변환부들(미도시)을 포함할 수 있다. 복수의 변환 라이트 비트 그룹들은 복수의 변환 라이트 비트들(RDW B)을 포함할 수 있다.

- [0058] 그리고, 데이터 처리부(220)는 복수의 리드 비트들(RDRB)이 그룹지어진 복수의 리드 비트 그룹들을 복수의 역변 환 리드 비트 그룹들로 병렬적으로 각각 역변환할 수 있다. 복수의 역변환 리드 비트 그룹들은 복수의 역변환 리드 비트들(RB)을 포함할 수 있다. 데이터 처리부(220)는 복수의 라이트 비트들(WB)에 대한 변환 처리를 복수의 리드 비트들(RDRB)에 대해 실질적으로 동일하게 처리함으로써 복수의 리드 비트들(RDRB)을 복수의 역변환 리드 비트들(RB)로 역변환할 수 있다.

- [0059] 데이터 처리부(220)는 도1에 도시된 데이터 처리 회로(100)와 실질적으로 동일하게 구성되고 동작할 수 있다. 이러한 경우, 예를 들어, 복수의 라이트 비트들(WB) 및 복수의 변환 라이트 비트들(RDWB)은 도1의 복수의 입력 비트들(IBT) 및 복수의 출력 비트들(OBT)과 각각 대응할 수 있다.

- [0060] 한편, 데이터 처리부(220)는 변환할 또는 역변환할 데이터가 저장될 또는 리드된 불휘발성 메모리 장치(300)의 메모리 영역에 대응하는 시드(SEED)를 입력받을 수 있다. 예를 들어, 시드(SEED)는, 해당 불휘발성 메모리 장치(300)의 메모리 영역의 어드레스 오프셋에 따라 데이터 처리부(220)로 제공될 수 있다. 따라서, 일정한 메모리 영역에 대응하는 시드(SEED)는 고정되므로, 시드(SEED)를 사용하여 변환된 데이터는 동일한 시드(SEED)를 사용

하여 원래대로 역변환될 수 있다.

- [0061] 메모리(230)는 프로세서(210)의 동작 메모리, 버퍼 메모리 또는 캐시 메모리 등의 기능을 수행할 수 있다. 메모리(230)는 동작 메모리로서 프로세서(210)를 구동시키기 위한 소프트웨어 프로그램 및 각종 프로그램 데이터를 저장할 수 있다. 메모리(230)는 버퍼 메모리로서 외부 장치 및 불휘발성 메모리 장치(300) 간에 전송되는 데이터를 버퍼링할 수 있다. 메모리(230)는 캐시 메모리로서 캐시 데이터를 임시 저장할 수 있다.

- [0062] 불휘발성 메모리 장치(300)는 복수의 변환 라이트 비트들(RDWB)을 병렬적으로 입력받고 라이트 동작을 통해 저장할 수 있다. 불휘발성 메모리 장치(300)는 저장된 복수의 변환 라이트 비트들(RDWB)을 복수의 리드 비트들(RDRB)을 병렬적으로 출력할 수 있다. 불휘발성 메모리 장치(300)는 컨트롤러(200)와 복수의 데이터 라인들(DL)을 통해서 데이터를 병렬로 송수신할 수 있다.

- [0063] 도4는 데이터 저장 장치(10)가 하나의 불휘발성 메모리 장치(300)를 포함하는 것으로 도시하나, 본 발명의 실시 예는 이에 제한되지 않고, 데이터 저장 장치(10)는 복수의 불휘발성 메모리 장치(300)들을 포함할 수 있다.

- [0064] 실시 예에 따라, 데이터 처리부(220)는 컨트롤러(200) 대신에 불휘발성 메모리 장치(300)에 배치될 수 있다. 이러한 경우, 데이터 처리부(220)는 컨트롤러(200)로부터 전송된 복수의 라이트 비트들(WB)을 변환 처리하고, 리드 비트들(RDRB)을 역변환 리드 비트들(RB)로 역변환 처리하여 컨트롤러(200)로 전송할 수 있다.

- [0065] 실시 예에 따라, 데이터 처리부(220)는 별도의 칩으로 집적되어 컨트롤러(200)와 불휘발성 메모리 장치(300) 사이에 구비될 수 있고, 컨트롤러(200)와 불휘발성 메모리 장치(300) 간에 변환/역변환 처리된 데이터를 전송할수 있다.

- [0066] 도5 본 발명의 실시 예에 따른 도4의 데이터 저장 장치(10)의 동작 방법을 설명하기 위한 순서도이다. 도5는 데이터 저장 장치(10)가 불휘발성 메모리 장치(300)에 저장될 데이터를 변환 처리하는 과정을 도시한다.

- [0067] 이하, 도4 및 도5를 참조하여 데이터 저장 장치(10)의 동작 방법이 설명될 것이다.

- [0068] S110 단계에서, 데이터 처리부(220)는 복수의 라이트 비트들(WB)이 그룹지어진 복수의 라이트 비트 그룹들을 병렬적으로 수신할 수 있다. 복수의 라이트 비트들(WB)은 데이터 처리부(220)로 병렬적으로 입력될 수 있다.

- [0069] S120 단계에서, 데이터 처리부(220)에 포함된 복수의 변환부들은 복수의 라이트 비트 그룹들을 변환 라이트 비트 그룹들로 병렬적으로 각각 변환할 수 있다. 복수의 변환부들은 서로 다른 랜덤 패턴들을 사용하여 복수의 라이트 비트 그룹들을 변환 라이트 비트 그룹들로 병렬적으로 각각 변환할 수 있다.

- [0070] S130 단계에서, 컨트롤러(200)는 복수의 변환 라이트 비트 그룹들을 불휘발성 메모리 장치(300)로 병렬적으로 전송할 수 있다. 복수의 변환 라이트 비트 그룹들은 복수의 변환 라이트 비트들(RDWB)을 포함할 수 있다.

- [0071] S140 단계에서, 불휘발성 메모리 장치(300)는 변환 라이트 비트 그룹들을 라이트 동작을 통해 저장할 수 있다.

- [0072] 도6은 본 발명의 실시 예에 따라 도4의 데이터 처리부(220)가 라이트 비트 그룹들을 변환 라이트 비트 그룹들로 병렬적으로 변환하는 방법을 설명하기 위한 순서도이다. 도6의 절차는 도5의 S120 단계의 실시 예일 수 있다.

- [0073] 이하, 도4 및 도6을 참조하여 데이터 처리부(220)의 동작 방법이 설명될 것이다.

- [0074] S111 단계에서, 데이터 처리부(220)에 포함된 복수의 랜덤 패턴 생성부들(예를 들어, 도1의 111, 121)은 시드 (SEED)에 응답하여 서로 다른 복수의 랜덤 패턴들을 생성할 수 있다.

- [0075] S112 단계에서, 데이터 처리부(220)에 포함된 복수의 연산부들(예를 들어, 도1의 113, 123)은 복수의 라이트 비트 그룹들을 복수의 랜덤 패턴들과 각각 논리 연산하여, 복수의 변화 라이트 비트 그룹들을 생성할 수 있다.

- [0076] 도7은 본 발명의 실시 예에 따른 도4의 데이터 저장 장치(10)의 동작 방법을 설명하기 위한 순서도이다. 도7은 데이터 저장 장치(10)가 불휘발성 메모리 장치(300)로부터 리드된 데이터를 역변환 처리하는 과정을 도시한다.

- [0077] 이하, 도4 및 도7을 참조하여 데이터 저장 장치(10)의 동작 방법이 설명될 것이다.

- [0078] S210 단계에서, 불휘발성 메모리 장치(300)는 저장된 복수의 변환 라이트 비트 그룹들을 복수의 리드 비트 그룹 들로 리드할 수 있다. 복수의 리드 비트 그룹들은 복수의 리드 비트들(RDRB)을 포함할 수 있다.

- [0079] S220 단계에서, 불휘발성 메모리 장치(300)는 복수의 리드 비트 그룹들을 컨트롤러(200)로 병렬적으로 전송할 수 있다.

- [0080] S230 단계에서, 데이터 처리부(220)에 포함된 복수의 변환부들은 복수의 리드 비트 그룹들을 복수의 역변환 리드 비트 그룹들로 병렬적으로 각각 역변환할 수 있다. 복수의 역변환 리드 비트 그룹들은 복수의 역변환 리드 비트들(RB)을 포함할 수 있다.

- [0081] 본 발명의 실시 예에 따르면, 향후 기술 발달에 따라 불휘발성 메모리 장치(300)의 페이지의 길이가 길어지더라 도, 병렬로 배치된 복수의 변환부들에 의한 데이터 처리를 통하여 페이지에 저장될 데이터의 랜덤성 악화를 효과적으로 방지할 수 있고, 따라서, 데이터 신뢰성 확보에 기여할 수 있다. 또한, 복수의 변환부들의 병렬 배치로 인한 데이터 처리부(220)의 하드웨어 사이즈 증가율은 시퀀스 길이를 늘리기 위해서 LFSR의 차수를 상향시키는 경우의 하드웨어 사이즈 증가율보다 훨씬 작기 때문에, 가격 경쟁력 유지에 도움이 될 수 있다.

- [0082] 본 발명이 속하는 기술분야의 통상의 기술자는 본 발명이 그 기술적 사상이나 필수적 특징을 변경하지 않고서 다른 구체적인 형태로 실시될 수 있으므로, 이상에서 기술한 실시 예들은 모든 면에서 예시적인 것이며 한정적인 것이 아닌 것으로서 이해해야만 한다. 본 발명의 범위는 상기 상세한 설명보다는 후술하는 특허청구범위에 의하여 나타내어지며, 특허청구범위의 의미 및 범위 그리고 그 등가개념으로부터 도출되는 모든 변경 또는 변형된 형태가 본 발명의 범위에 포함되는 것으로 해석되어야 한다.

## 부호의 설명

[0083] 100 : 데이터 처리 회로

110 : 제1 변환부

111 : 제1 랜덤 패턴 생성부

113 : 제1 연산부

120 : 제2 변환부

121 : 제2 랜덤 패턴 생성부

123 : 제2 연산부

# 도면

# 도면1

# 도면2

# 도면3

## *도면4*

## 도면5

## 도면6

## 도면7